Diversity IF to Baseband

a

GSM/EDGE Narrowband Receiver

Preliminary Technical Data AD6650

FEATURES

Digital VGA

I & Q Demodulators

Active Low Pass Filters

Dual Wideband ADC

Programmable Decimation and Channel Filters

Phase Locked Loop Circuitry

Serial Data Output Ports

IF Frequencies 70-300MHz

10 dB Noise Figure

+24 dBm Input IP2

-13 dBm Input IP3

3.3 Volt I/O and CMOS Core

2

I

C and Microprocessor Interface

JTAG Boundary Scan

APPLICATIONS

GSM/EDGE Single Carrier and Diversity Receivers

Micro and Pico Cell Systems

Wireless Local Loop

Smart Antenna Systems

Software Radios

In Building Wireless Telephony

PRODUCT DESCRIPTION

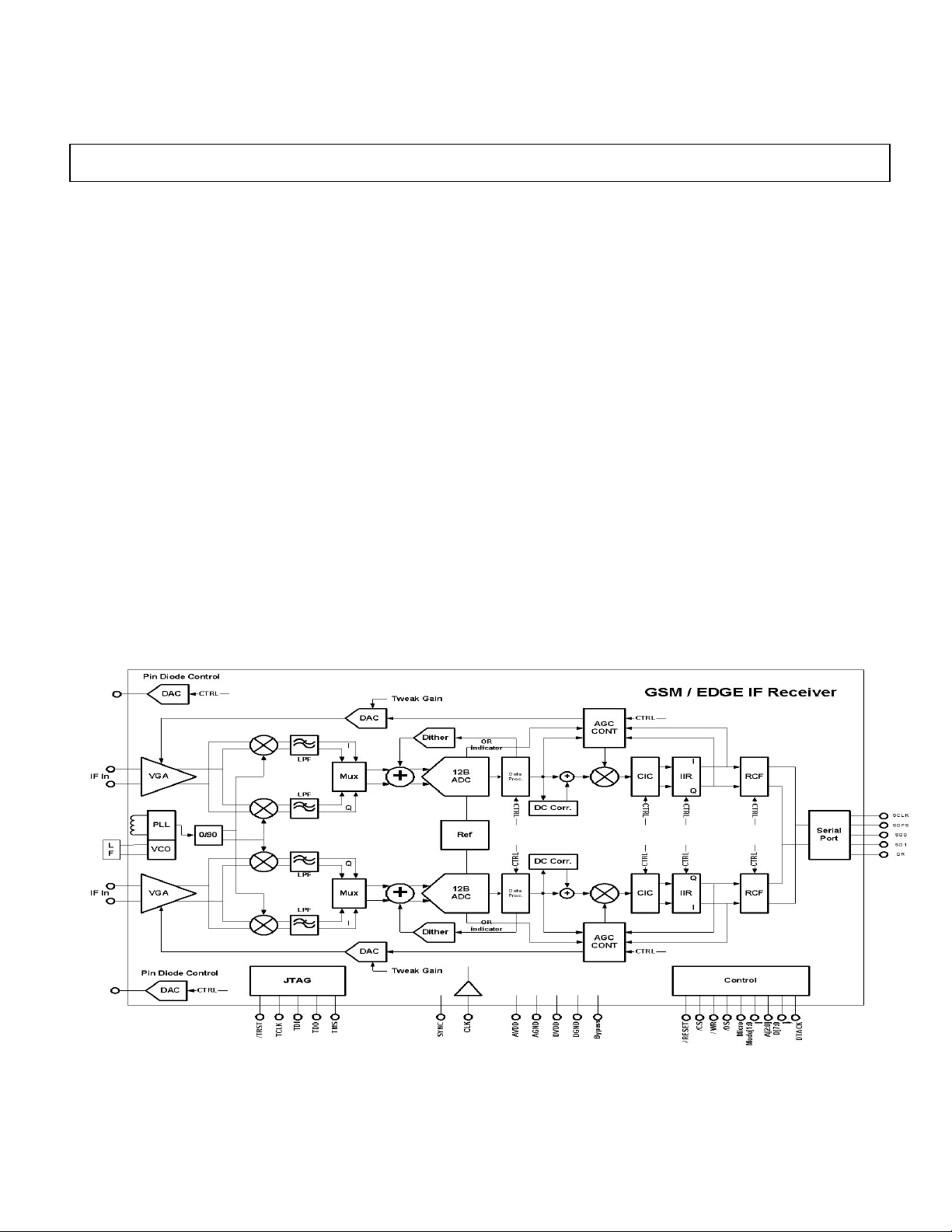

The AD6650 is a diversity, IF to baseband receiver for

GSM/EDGE. This narrow band receiver consists of an

integrated DVGA, IF-to-baseband I&Q demodulators, lowpass filtering, and a dual wideband ADC. The chip can

accommodate IF input frequencies from 70 MHz to 300 MHz.

This receiver architecture is designed such that only one

external SAW filter(one for main and one for diversity) is

required in the entire Rx signal path to meet GSM/EDGE

blocking requirements.

Digital decimation and filtering circuitry is embedded on chip

to generate serial output I&Q

filters remove unwanted signals and noise outside the channel

of interest. In addition, programmable RAM Coefficient

filters allow anti-aliasing, matched filtering, and static

equalization functions to be combined in a single, costeffective filter.

The AD6650 is part of a complete GSM/EDGE receive and

transmit chipset. Other components in this chipset are: RF to

IF amplifier/mixers, receive and transmit frequency hopping

synthesizers, and a baseband to IF transmit modulator and

ramping chip.

data streams. The decimating

Figure 1. AD6650 Functional Block Diagram

PrJ 02/27/03

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective companies.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © 2003 Analog Devices, Inc. All rights reserved.

Preliminary Technical Data AD6650

TABLE OF CONTENTS

FEATURES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xx

PRODUCT DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . .xx

FUNCTIONAL BLOCK DIAGRAM . . . . . . . . . . . . . . .. .xx

SPECIFICATIONS/CHARACTERISTICS . . . . . .. . . . . . xx

TIMING DIAGRAMS . . . . . . . . . . . . . . . . . . . . . . . . . . . . xx

ABSOLUTE MAXIMUM RATINGS . . . . . . . . . . . . . . . .xx

PIN FUNCTION DESCRIPTIONS . . . . . . . . . . . . . . . . xx

ARCHITECTURE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .xx

EXAMPLE FILTER RESPONSE . . . . . . . . . . . . . . . . . . .xx

AGC LOOP.......................................................................xx

DC CORRECTION...........................................................xx

FOURTH ORDER CASCADED INTEGRATOR COMB

FILTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xx

CIC4 Rejection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xx

INFINITE IMPULSE RESPONSE xx

RAM COEFFICIENT FILTER . . . . . . . . . . . . . . . . . . . . .xx

RCF Decimation Register . . . . . . .. . . . . .. . . . . xx

RCF Decimation Phase . . . . .. . . . . . . . . . . . . . xx

RCF Filter Length . . . . . .. . . . . . . . . . . . . . . . . .xx

RCF Output Scale Factor and Control Register . xx

USER-CONFIGURABLE BUILT-IN SELF-TEST

CHANNEL BIST...........................................xx

CHIP SYNCHRONIZATION . . . . . . . . . . . . . . . . . . . . .xx

Start . . . . . . . . . . . . . . . . .. . . . . . . . . . . . . . . . xx

SERIAL OUTPUT DATA PORT . . . . . . . . . . . . . . . . . . .xx

Serial Output Data Format . . . . . . . . . . . . . . . . . xx

Serial Data Frame (Serial Bus Master) .. . . . . . . . xx

Serial Data Frame (Serial Cascade) . . . . . . . . . xx

Configuring the Serial Ports . . . . . . . .. . . . . . . xx

Serial Port Data Rate . . . . . . . . . .. . . . . . . . . . . . xx

Serial Slave Operation . . . . . . . . . .. . . . . . . . . . . xx

Serial Ports Cascaded . . . . . . . .. . . . . . . . . . . . . . xx

Serial Output Frame Timing (Master and Slave) xx

Serial Port Timing Specifications . . . . . . ... . . . . xx

SCLK . . . . . . . .. . . . . . . . . . . . . . . . . . . . . . . . xx

SDO0 . . . . . . . . . . . . . . . . .. . . . . . . . . . . . . . xx

SDO1 . . . . . . . . . . . . . .. . . . . . . . . . . . . . . . xx

SDFS . . . . . . . . . . . . . .. . . . . . . . . . . . . . . . . . .. . xx

Serial Word Length . . . . . .. . . . . . . . . . . . . . . . . xx

SDFS Mode . . . . . . . . . . . . .. . . . . . . . . . . . . . . . xx

Mapping RCF Data to the BIST Registers . . . .. . xx

0x00: Clock Divider Control . .. . .xx

0x01-0x05: PLL Register[4:0] . . . . . . .. . . . . .. . xx

0x06: Clamp Control............................................xx

MICROPORT CONTROL . . . . . . . . . . . . . . . . . . . . . . . . xx

2

I

JTAG BOUNDARY SCAN . . . . . . . . . . . . . . . . . . . . .xx

INTERNAL WRITE ACCESS . . . . . . . . . . . . . . . .. . . . .xx

Write Pseudocode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xx

INTERNAL READ ACCESS . . . . . . . . . . . . . . . . . . . . . . xx

Read Pseudocode . . . . . . . . . . . . . . . . . . . . . . . xx

OUTLINE DIMENSIONS . . . . . . . . . . . . . .. . . . . xx

0x07: Aux DAC A ...............................................xx

0x08: Aux DAC B ................................................xx

0x09: Aux DAC Control.......................................xx

0x0A: ADC Dither Control.................................xx

0x0B: DC Correction BW.....................................xx

0x0C: DC Correction Control...............................xx

0x0D-0x14: AGC Control[7:0]............................xx

0x15: Start Hold-Off Counter...............................xx

0x16: CIC4 Decimation.......................................xx

0x17: CIC4 Scale.................................................xx

0x18: IIR Control Register...................................xx

0x19: RCF Decimation Register..........................xx

0x1A: RCF Decimation Phase..............................xx

0x1B: RCF Coefficient Offset..............................xx

0x1C: RCF Taps....................................................xx

0x1D: RCF Scale Register...................................xx

0x1E-0x1F: BIST For A-I/Q.................................xx

0x20-0x21: BIST for B-I/Q..................................xx

0x22: Serial Control Register...............................xx

0x23-0x29: Reserved............................................xx

0x30-0x5F: Coefficient Memory.........................xx

0x60-0xFF: Reserved...........................................xx

External Memory Map . . . . . .. . . . . . . . . . . . . . . xx

Access Control Register (ACR) . . . . .. . . . . . . . . xx

External Memory Map . . . . . . ... . . . . . . . . . . . . xx

Channel Address Register (CAR) . .. . . . . . . . . . xx

SOFT_SYNC Control Register . .. . . . . . . . . . xx

PIN_SYNC Control Register . . . ... . . . . . . . . . xx

SLEEP Control Register . . . . . . .. . . . . . . . . . . . xx

Data Address Registers . . . . . . .. . . . . . . . . . . . . xx

Write Sequencing . . . . . . . .. . . . . . . . . . . . . . . . . xx

Read Sequencing . . . . . . . .. . . . . . . . . . . . . . . . . xx

Read/Write Chaining . . . . .. . . . . . . . . . . . . . . . . xx

Intel Nonmultiplexed Mode (INM) . . . . . . . . . . . xx

Motorola Nonmultiplexed Mode (MNM) ... . . . . xx

C PORT CONTROL

REV. PrJ 02/27/2003 2

Preliminary Technical Data AD6650

AC Specifications

Parameter

Overall Function

Frequency Range 70 300 MHz

Gain Control

Gain Step Size .094 dB

Gain Step Accuracy +/- .5 Step

Baseband Filters

Group Delay 119 124 127 ns

Bandwidth 3.36 3.5 3.64 MHz

LO Phase Noise: @ 200KHz Offset -88 dBc/Hz

@ 400KHz Offset -108 dBc/Hz

@ 600KHz Offset -120 dBc/Hz

@ 800KHz Offset TBD dBc/Hz

@ 1600KHz Offset TBD dBc/Hz

@ 3000KHz Offset TBD dBc/Hz

F = 70 MHz

Min Gain 0 dB

Max Gain 36 dB

Noise Figure1 10.25 dB

Input IP2 +24 dBm

Input IP3 -13 dBm

Image Rejection 35 dBc

FullScale Input Power +4 dBm

Input Impedance 200+jx Ω

F = 150 MHz

Min Gain 0 dB

Max Gain 36 dB

Noise Figure1 10.25 dB

Input IP2 +24 dBm

Input IP3 -13 dBm

Image Rejection 35 dBc

FullScale Input Power +4 dBm

Input Impedance 200+jx Ω

F = 200 MHz

Min Gain 0 dB

Max Gain 36 dB

Noise Figure1 10.25 dB

Input IP2 +24 dBm

Input IP3 -13 dBm

Image Rejection 35 dBc

FullScale Input Power +4 dBm

Input Impedance 200+jx Ω

F = 250 MHz

Min Gain 0 dB

Max Gain 36 dB

Noise Figure1 10.25 dB

Input IP2 +24 dBm

REV. PrJ 02/27/2003 3

Temp

Test

Level

MIN

AD6650BBC

Typ

Max

Units

Preliminary Technical Data AD6650

Input IP3 -13 dBm

Image Rejection 35 dBc

FullScale Input Power +4 dBm

Input Impedance 200+jx Ω

F = 300 MHz

Min Gain 0 dB

Max Gain 36 dB

Noise Figure1 10.25 dB

Input IP2 +24 dBm

Input IP3 -13 dBm

Image Rejection 35 dBc

FullScale Input Power +4 dBm

Input Impedance 200+jx Ω

1

This Measurement applies in Maximum Gain (+36 dB)

REV. PrJ 02/27/2003 4

Preliminary Technical Data AD6650

DIGITAL SPECIFICATIONS

(TMIN to TMAX, AVDD, CLKVDD, DVDD = +3.3v, unless otherwise noted)

Parameter

VDD IV 3.0 3.3 3.6 V

VDDIO IV 3.0 3.3 3.6 V

AVDD IV 3.0 3.3 3.6 V

T

IV -40 +25 +85

AMBIENT

ELECTRICAL CHARACTERISTICS

Parameter (Conditions)

LOGIC INPUTS

Logic Compatibility Full 3.3V CMOS

Logic “1” Voltage VDD-0.9 VDD V

Logic “0” Voltage 0 0.9 V

Logic “1” Current –10 +10 µA

Logic “0” Current –10 10 µA

Input Capacitance 5 pF

LOGIC OUTPUTS

Logic Compatibility Full 3.3VCMOS/TTL

Logic “1” Voltage (IOH=0.25mA) Full IV 2.4 VDD-0.2 V

Logic “0” Voltage (IOL=0.25mA) Full IV 0.2 0.4 V

IDD SUPPLY CURRENT

CLK=104 MHz (GSM Example)

I

I

I

POWER DISSIPATION

CLK=104 MHz GSM/EDGE Example V 1.2 W

mA

VDD

mA

VDDIO

mA

AVDD

Temp

Temp

+25°C

Test

Level

Test

Level Min

V

MIN

AD6650BBC

Typ

AD6650BBC

Typ

Max

Max

Units

°C

Units

REV. PrJ 02/27/2003 5

Preliminary Technical Data AD6650

GENERAL TIMING CHARACTERISTICS

Parameter (Conditions)

CLK Timing Requirements:

t

CLK Period Full I 9.6 ns

CLK

t

CLK Width Low Full IV 0.5 x t

CLKL

t

CLK Width High Full IV 0.5 x t

CLKH

/RESET Timing Requirements:

t

/RESET Width Low Full IV 30 ns

RESL

SYNC Timing Requirements:

tSS

tHS

Master Mode Serial Port Timing Requirements (SBM=1):

Switching Characteristics

t

DSCLK1

t

DSCLKH

t

DSCLKL

t

t

t

t

t

DSCLKLL

DSDFS

DSDO

DSD1

DSDR

Slave Mode Serial Port Timing Requirements (SBM=0):

Switching Characteristics

t

SCLK Period Full IV 16.0 ns

SCLK

t

SCLK low time (when SDIV=1, divide by 1) Full IV 5.0 ns

SCLKL

t

SCLK high time (when SDIV=1, divide by 1) Full IV 5.0 ns

SCLKH

t

DSDO

t

DSD1

t

DSDR

SYNC to ↑CLK Setup Time

SYNC to ↑CLK Hold Time

2

↑CLK to ↑SCLK Delay (divide by 1)

↑CLK to ↑SCLK Delay (for any other divisor)

↑CLK to ↓SCLK Delay (divide by 2 or even #)

↓CLK to ↓SCLK Delay (divide by 3 or odd #)

↑SCLK to SDFS Delay

↑SCLK to SDO Delay

↑SCLK to SD1 Delay

↑SCLK to DR Delay

2

↑SCLK to SDO Delay

↑SCLK to SD1 Delay

↑SCLK to DR Delay

Input Characteristics

t

t

SSF

HSF

SDFS to ↑SCLK Setup Time

SDFS to ↑SCLK Hold Time

1

All Timing Specifications valid over VDD range of 3.0V to 3.6V and VDDIO range of 3.0V to 3.6V.

2

The timing parameters for SCLK, SDFS, SDO0, SDO1, and DR apply to both channels (0, 1). The Slave serial port’s (SCLK)

operating frequency is limited to 52 MHz.

3

Specification pertains to control signals: RW, (/WR), /DS, (/RD), /CS

4

(C

=40pF on all outputs unless otherwise specified)

LOAD

Temp

Test

Level Min

AD6650

Typ

CLK

CLK

Max

Units

ns

ns

Full IV ns

Full IV ns

Full IV

3.9

13.4

ns

Full IV 4.4 14.0 ns

Full IV 3.25 6.7 ns

Full IV 3.8 6.9 ns

Full IV 3.02 ns

Full IV 2.7 ns

Full IV 2.6 ns

Full IV 2.7 ns

Full IV 6.8 ns

Full IV 6.8 ns

Full IV 6.9 ns

Full IV 2.6 ns

Full IV -1.15 ns

REV. PrJ 02/27/2003 6

Preliminary Technical Data AD6650

MICROPROCESSOR PORT TIMING CHARACTERISTICS

Test

Temp

Level Min

MICROPROCESSOR PORT, MODE INM (MODE=0)

MODE INM Write Timing:

t

SC

tHC

t

HWR

t

Address/Data to /WR(RW) Setup Time Full IV -0.5 ns

SAM

t

Address/Data to RDY(/DTACK) Hold Time Full IV 7.0 ns

HAM

t

/WR(RW) to RDY(/DTACK) Delay Full IV 4.0 ns

DRDY

t

/WR(RW) to RDY(/DTACK) High Delay Full IV 4*t

ACC

Control

Control

/WR(RW) to RDY(/DTACK) Hold Time

MODE INM Read Timing:

t

SC

tHC

t

SAM

t

Address to Data Hold Time Full IV 7.0 ns

HAM

Control

Control

Address to /RD(/DS) Setup Time

3

to ↑CLK Setup Time

3

to ↑CLK Hold Time

3

to ↑CLK Setup Time

3

to ↑CLK Hold Time

Full

Full

Full

Full

Full

Full

IV

IV

IV

IV

IV

IV

5.5

1.0

8.0

CLK

4.0

2.0

0.0

tZD Data Tri-state Delay Full IV ns

tDD RDY(/DTACK) to Data Delay Full IV ns

t

/RD(/DS) to RDY(/DTACK) Delay Full IV 4.0 ns

DRDY

t

/RD(/DS) to RDY(/DTACK) High Delay Full IV 4*t

ACC

MICROPROCESSOR PORT, MODE MNM (MODE=1)

MODE MNM Write Timing:

t

SC

tHC

t

HDS

t

RW(/WR) to /DTACK(RDY) Hold Time Full IV 8.0 ns

HRW

t

Address/Data To RW(/WR) Setup Time Full IV -0.5 ns

SAM

t

Address/Data to RW(/WR) Hold Time Full IV 7.0 ns

HAM

t

/DS(/RD) to /DTACK(RDY) Delay Full IV ns

DDTACK

t

RW(/WR) to /DTACK(RDY) Low Delay Full IV 4*t

ACC

Control

Control

/DS(/RD) to /DTACK(RDY) Hold Time

MODE MNM Read Timing:

t

SC

tHC

t

HDS

t

Address to /DS(/RD) Setup Time Full IV 0.0 ns

SAM

t

Address to Data Hold Time Full IV 7.0 ns

HAM

Control

Control

/DS(/RD) to /DTACK(RDY) Hold Time

3

to ↑CLK Setup Time

3

to ↑CLK Hold Time

3

to ↑CLK Setup Time

3

to ↑CLK Hold Time

Temp

Full

Full

Full

Full

Full

Full

Test

Level Min

IV

IV

IV

IV

IV

IV

CLK

5.5

1.0

8.0

CLK

4.0

2.0

8.0

tZD Data Tri-State Delay Full IV ns

tDD /DTACK(RDY) to Data Delay Full IV ns

t

/DS(/RD) to /DTACK(RDY) Delay Full IV ns

DDTACK

t

/DS(/RD) to /DTACK(RDY) Low Delay Full IV 4*t

ACC

CLK

MODE I2C Timing:

t

DSCL

t

DSDA

5

t

SSCL

1

All Timing Specifications valid over VDD range of 3.0V to 3.6V and VDDIO range of 3.0V to 3.6V.

2

The timing parameters for SCLK, SDFS, SDO0, SDO1, and DR apply to both channels (0, 1)

3

Specification pertains to control signals: RW, (/WR), /DS, (/RD), /CS

4

(C

=40pF on all outputs unless otherwise specified)

LOAD

5

There is no hold time for SDA because as this waits for a negative transition (↓) on SCL to transition.

↑SCL to SDA Delay

SDA to ↑SCL Delay

↑CLK to ↑SCL Delay

Full IV 61 ns

Full IV 57 ns

Full IV 5 ns

AD6650

5*t

7*t

AD6650

5*t

7*t

1

Typ

Max

ns

CLK

ns

CLK

Max

Typ

ns

CLK

ns

CLK

Units

ns

ns

ns

ns

ns

ns

Units

ns

ns

ns

ns

ns

ns

REV. PrJ 02/27/2003 7

Preliminary Technical Data AD6650

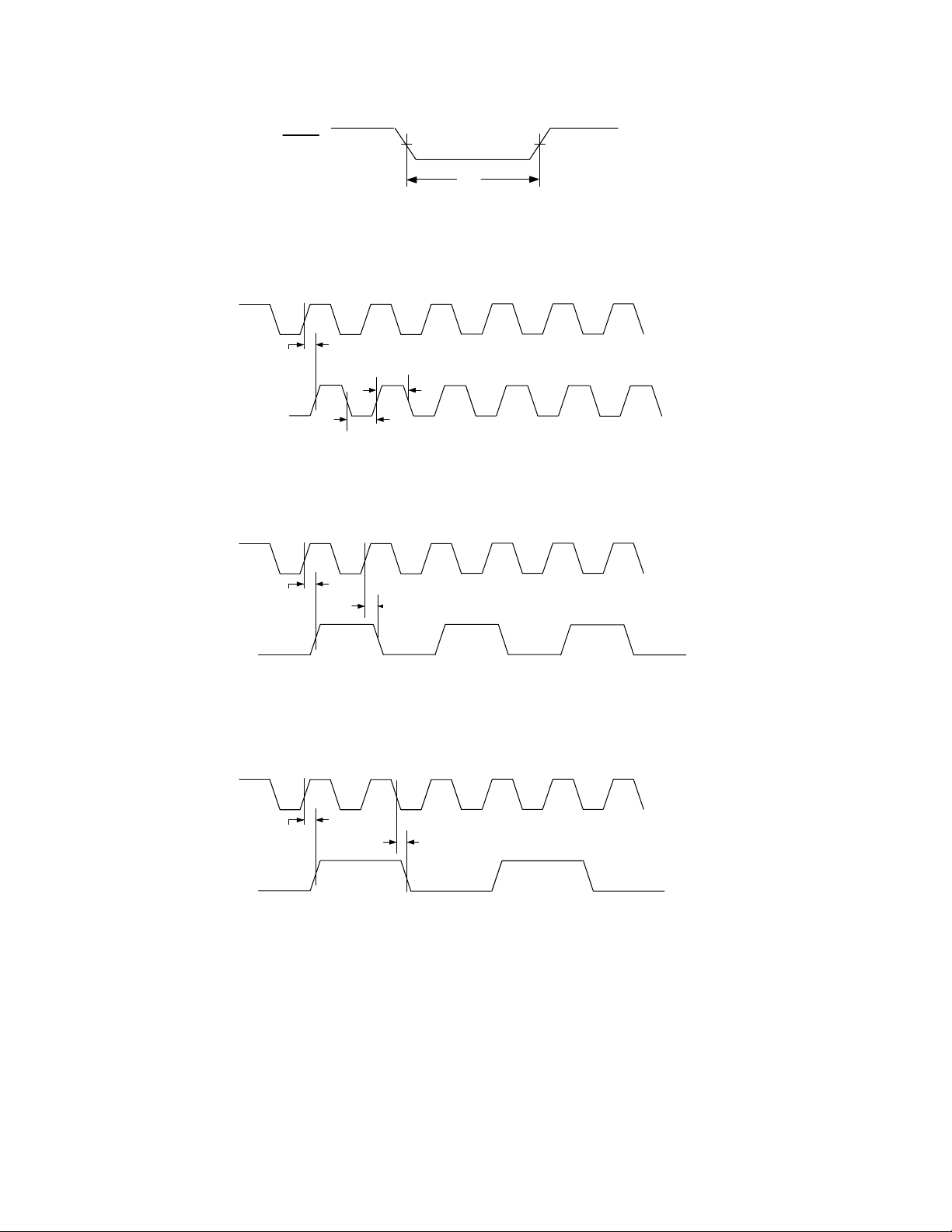

TIMING DIAGRAMS

RESET

t

CLK

SCLK

t

DSCLKH

SSF

Figure x. Reset Timing Requirements

t

SCLKH

t

SCLKL

Figure x. SCLK Switching Characteristics (Divide by 1)

CLK

t

DSCLKH

SCLK

Figure x. SCLK Switching Characteristics (Divide by 2 or EVEN integer)

CLK

t

DSCLKH

SCLK

t

DSCLKL

t

DSCLKLL

Figure x. SCLK Switching Characteristics (Divide by 3 or ODD integer)

REV. PrJ 02/27/2003 8

Preliminary Technical Data AD6650

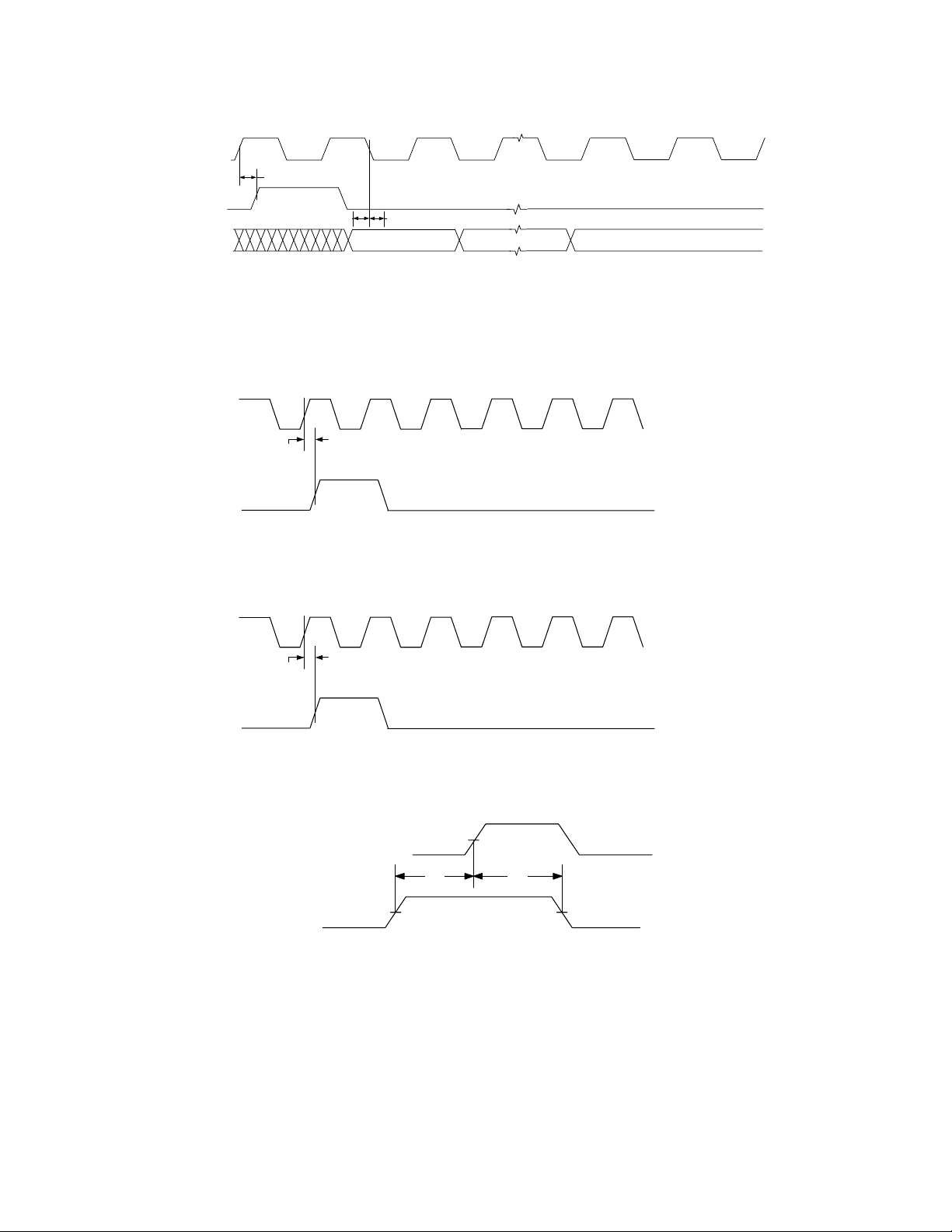

TIMING DIAGRAMS

SCLK

t

DSDFS

SDFS

t

SDI

t

SSI

HSI

DATAn

CLK

DR

SCLK

DR

t

DDR

t

DSDR

Figure x. Serial Port Switching Characteristics

Figure x. CLK, DR Switching Characteristics

Figure x. SCLK, DR Switching Characteristics

SCLK

SDFS

t

SSF

t

HSF

Figure x. SDFS Timing Requirements (SBM=0)

REV. PrJ 02/27/2003 9

Loading...

Loading...