Analog Devices AD6459 Datasheet

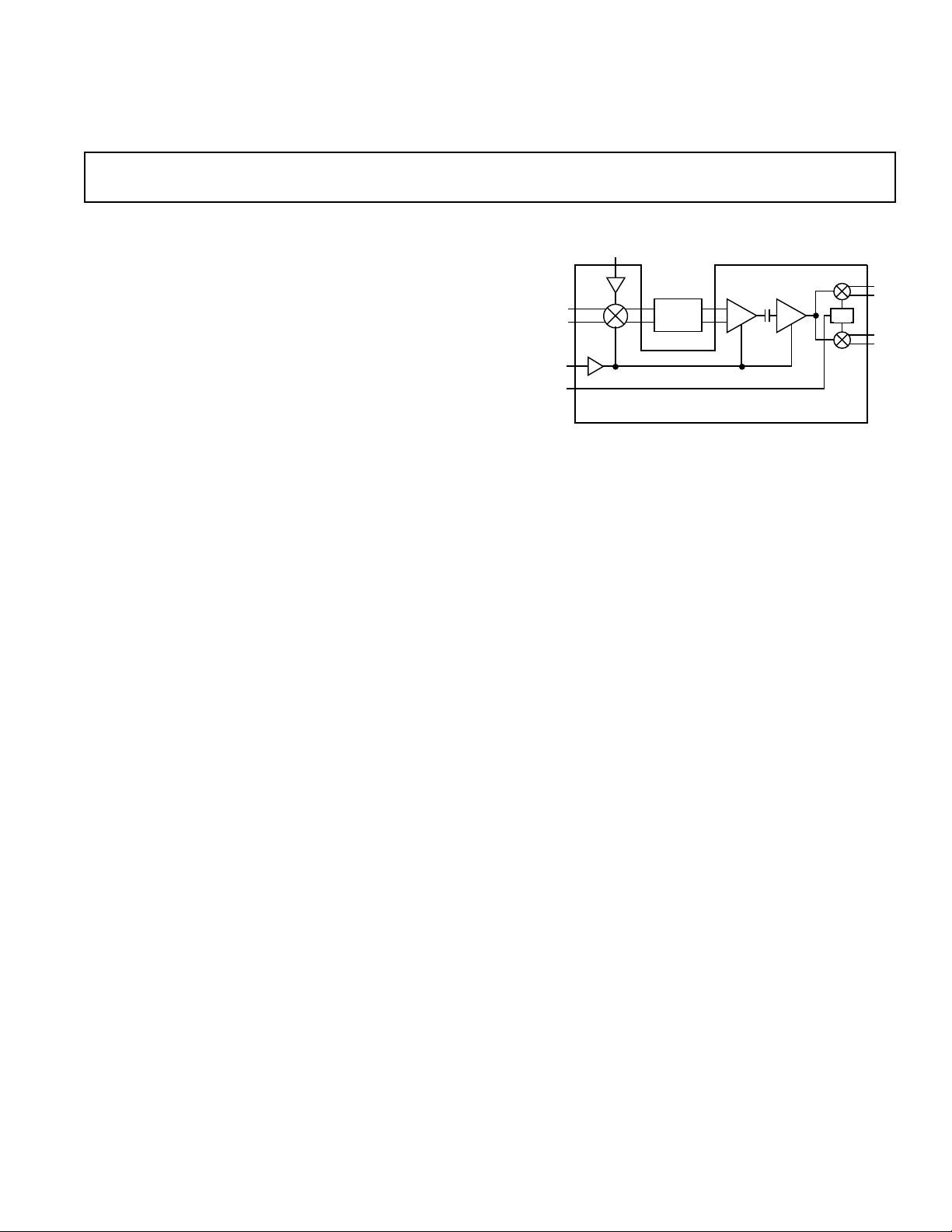

a

BPF

PLL

LO

I

Q

GAIN

CONTROL

FREF

RF

AD6459

GSM 3 V Receiver IF Subsystem

AD6459

FEATURES

Fully Compliant with Standard and Enhanced GSM

Specification

–11 dBm Input 1 dB Compression Point

0 dBm Input Third Order Intercept

10 dB SSB Noise Figure (50 V)

DC-500 MHz RF and LO Bandwidths

Linear IF Amplifier

Linear-in-dB and Stable over Temperature

Voltage Gain Control

Quadrature Demodulator

On-Board Phase-Locked Quadrature Oscillator

Demodulates IFs from 5 MHz to 50 MHz

Low Power

8 mA at Midgain

2 mA Sleep Mode Operation

2.7 V to 5.5 V Operation

Interfaces to AD7013, AD7015 and AD6421 Baseband

Converters

20-Lead SSOP

GENERAL DESCRIPTION

The AD6459 is a 3 V, low power receiver IF subsystem for

operation at input frequencies as high as 500 MHz and IFs

from 5 MHz up to 50 MHz. It is optimized for operation in

GSM, DCS1800 and PCS1900 receivers. It consists of a mixer,

an IF amplifier, I and Q demodulators, a phase-locked quadrature oscillator, a precise AGC subsystem, and a biasing system

with external power-down.

The AD6459’s low noise, high intercept mixer is a doublybalanced Gilbert-Cell type. It has a nominal –11 dBm inputreferred 1 dB compression point and a 0 dBm input-referred

third-order intercept. The mixer section of the AD6459 also

includes a local oscillator (LO) preamplifier, which lowers the

required LO drive to –16 dBm.

The gain control input accepts an external gain-control voltage

input from an external AGC detector or a DAC. It provides an

80 dB gain range with 27 mV/dB gain scaling.

The I and Q demodulators provide in-phase and quadrature

baseband outputs to interface with Analog Devices’ AD7013

FUNCTIONAL BLOCK DIAGRAM

(IS54, TETRA, MSAT) AD7015 and AD6421 (GSM,

DCS1800, PCS1900) baseband converters. An on-board

quadrature VCO that is externally phase-locked to the IF signal

drives the I and Q demodulators. This locked reference signal is

normally provided by an external VCTCXO under the control of

the radio’s digital processor. The AD6459 can also provide

demodulation of N-PSK and N-QAM in many non-TDMA

systems when used with external analog carrier recovery systems

such as the Costas Loop. Finally, the VCO can be phase-locked

to a frequency that is deliberately offset from the IF as in the

case of a Beat-Frequency oscillator (BFO) resulting in the

product detection of CW or SSB.

The AD6459 uses supply voltages from 2.7 V to 5.5 V over the

temperature range of –40°C to +85°C. Operation is enabled by a

CMOS logical level; response time is typically < 80 µs. When

disabled, the standby current is reduced to 2 µA.

The AD6459 comes in a 20-pin shrink small outline (SSOP)

surface mount package.

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700 World Wide Web Site: http://www.analog.com

Fax: 617/326-8703 © Analog Devices, Inc., 1996

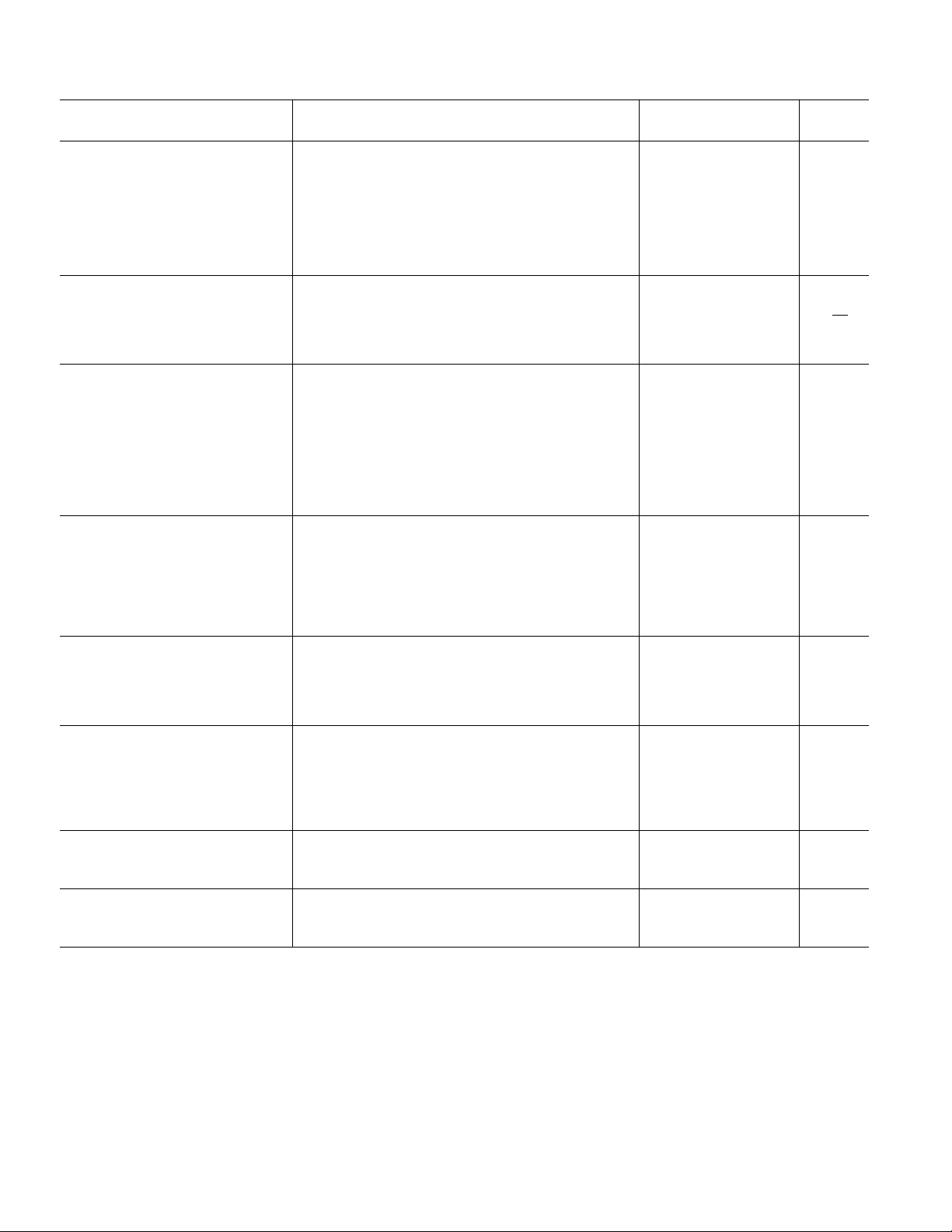

AD6459–SPECIFICATIONS

(@ TA = +258C, VP = 3.0 V, GREF = 1.2 V, unless otherwise noted)

Model AD6459ARS

Parameter Conditions Min Typ Max Units

DYNAMIC PERFORMANCE

MIXER

Maximum RF and LO Frequency 500 MHz

AGC Conversion Gain Variation 0.2 V < V

Input 1 dB Compression Point @ V

Input Third-Order Intercept @ V

SSB Noise Figure

1

GAIN

GAIN

@ ZS = 50 Ω, FRF = 240 MHz, F

< 2.25 V –3 to +16 dB

GAIN

= 0.2 V –11 dBm

= 0.2 V 0 dBm

= 229.3 MHz at –16 dBm 10 dB

LO

Mixer Output Bandwidth at MXOP @ –3 dB 80 MHz

IF AMPLIFIERS

AGC Gain Variation 0.2 V < V

Input Referred Noise AC Short Circuit Input 3 nV/√

Input Resistance @ V

GAIN

<2.25 V –13 to +46 dB

GAIN

= 0.2 V 5 kΩ

Hz

Bandwidth @ –3 dB 50 MHz

I AND Q DEMODULATORS

Demodulation Gain 17 dB

Output Voltage Range Differential, IRXP, IRXN, QRXP, QRXN 0.3 V

– 0.2 V

P

Output Voltage Common-Mode Level (Not Power Supply Dependent) 1.5 V

Output Offset Voltage Differential, V

= GREF –150 150 mV

GAIN

Error in Quadrature Differential from I to Q, IF = 13 MHz 1.5 3.5 Degree

Amplitude Match I to Q 0.25 dB

I/Q Output Bandwidth C

= 10 pF 2 MHz

LOAD

Output Resistance Each Pin 4.7 kΩ

GAIN CONTROL

Total Gain Control Range Mixer + IF + Demod, 0.2 V < V

<2.25 V 76 dB

GAIN

Control Voltage Range at GAIN 0.2 2.4 V

Gain Scaling 23 27 32 mV/dB

Gain Law Conformance ±0.5 dB

Bias Current at GREF 0.5 µA

Input Resistance at GAIN 20 kΩ

PLL

Frequency Range 5 50 MHz

Phase Noise 0.5 Degree rms

Acquisition Time IF = 19.5 MHz, Using Suggested Filter 80 µs

Input Drive Level (FREF) 100 VPOS mV

POWER-DOWN INTERFACE

Logical Threshold Power Up on Logical High 1.5 V

Input Current for Logical High 75 µA

Turn-On Response Time To Fully Meet Specifications (PLL Lock) 80 µs

Turn-Off Response time To 200 µA Supply Current 1 µs

Standby Current 2 µA

POWER SUPPLY

Supply Range 2.7 5.5 V

Supply Current @ V

= 1.2 V 8 mA

GAIN

OPERATING TEMPERATURE

to T

T

MIN

MAX

Operation to 3.3 V Minimum Supply Voltage –40 +85 °C

Operation to 2.7 V Minimum Supply Voltage –25 +85 °C

NOTES

1

Including IF noise and using suggested filter, at V

Specifications subject to change without notice.

GAIN

= 0.2 V.

–2–

REV. 0

AD6459

WARNING!

ESD SENSITIVE DEVICE

ABSOLUTE MAXIMUM RATINGS

Supply Voltage VPS1, VPS2 to COM1, COM2 . . . . . +5.5 V

Internal Power Dissipation

2

. . . . . . . . . . . . . . . . . . . 600 mW

1

PIN CONNECTION

20-Pin SSOP (RS-20)

Operating Temperature Range . . . . . . . . . . . –40°C to +85°C

Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C

Lead Temperature, Soldering (60 sec) . . . . . . . . . . . .+300°C

NOTES

1

Stresses above those listed under “Absolute Maximum Ratings” may cause

permanent damage to the device. This is a stress rating only, and functional

operation of the device at these or any other conditions above those indicated in the

operational section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended rating conditions for extended periods

may affect device reliability.

2

Thermal Characteristics: 20-lead SSOP package: θJA = 126°C/W.

ORDERING GUIDE

FREF

COM1

PRUP

LOIP

RFHI

COM2

GREF

MXOP

MXOM

1

2

3

4

5

AD6459

TOP VIEW

6

(Not to Scale)

7

8

9

10

20

VPS1

19

FLTR

18

VPS2

17

IRXP

16

IRXNRFLO

15

QRXP

14

QRXN

GAIN

13

IFIM

12

IFIP

11

Temperature Package Package

Model Range Description Option

AD6459ARS –25°C to +85°C 20-Pin Plastic RS-20

for 2.7 V to 5.5 V SSOP

–40°C to +85°C

for 3.3 V to 5.5 V

PIN DESCRIPTIONS

Pin

Pin Label Description Function

1 FREF Frequency Reference Input Demodulation LO Input. May either be 3 V CMOS input or >100 mV p-p.

AC-coupled for lowest stand by current.

2 COM1 Common 1 Ground.

3 PRUP Power Up Input CMOS Compatible Power-Up Control; <1.5 V = OFF, >1.5 V = ON.

4 LOIP Local Oscillator Input AC-Coupled LO Input. 50 mV p-p

drive needed, 500 mV p-p max.

5 RFLO RF “Low” Input Mixer Differential Input. AC-coupled.

6 RFHI RF “High” Input Mixer Differential Input. AC-coupled.

7 COM2 Common 2 Ground.

8 GREF Gain Reference Input High Impedance Input. Sets gain scaling, typically 1.2 V.

9 MXOP Mixer Output “Plus” Differential Output of the Mixer. See Figure 22.

10 MXOM Mixer Output “Minus” Differential Output of the Mixer. See Figure 22.

11 IFIP IF Input “Plus” Differential Input of Variable Gain Amplifier. AC-coupled.

12 IFIM IF Input “Minus” Differential Input of Variable Gain Amplifier. AC-coupled.

13 GAIN Gain Control Input 0.2 V–2.4 V Using 3 V Supply. Max gain at 0.2 V.

14 QRXN Q Output “Negative” Differential Q Output. Output resistance 4.7 kΩ.

15 QRXP Q Output “Positive” Differential Q Output. Output resistance 4.7 kΩ.

16 IRXN I Output “Negative” Differential I Output. Output resistance 4.7 kΩ.

17 IRXP I Output “Positive” Differential I Output. Output resistance 4.7 kΩ.

18 VPS2 VPOS Supply 2 Supply Voltage.

19 FLTR PLL Loop Filter Series RC Loop Filter. Connected to VPS2.

20 VPS1 VPOS Supply 1 Supply Voltage.

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD6459 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

REV. 0

–3–

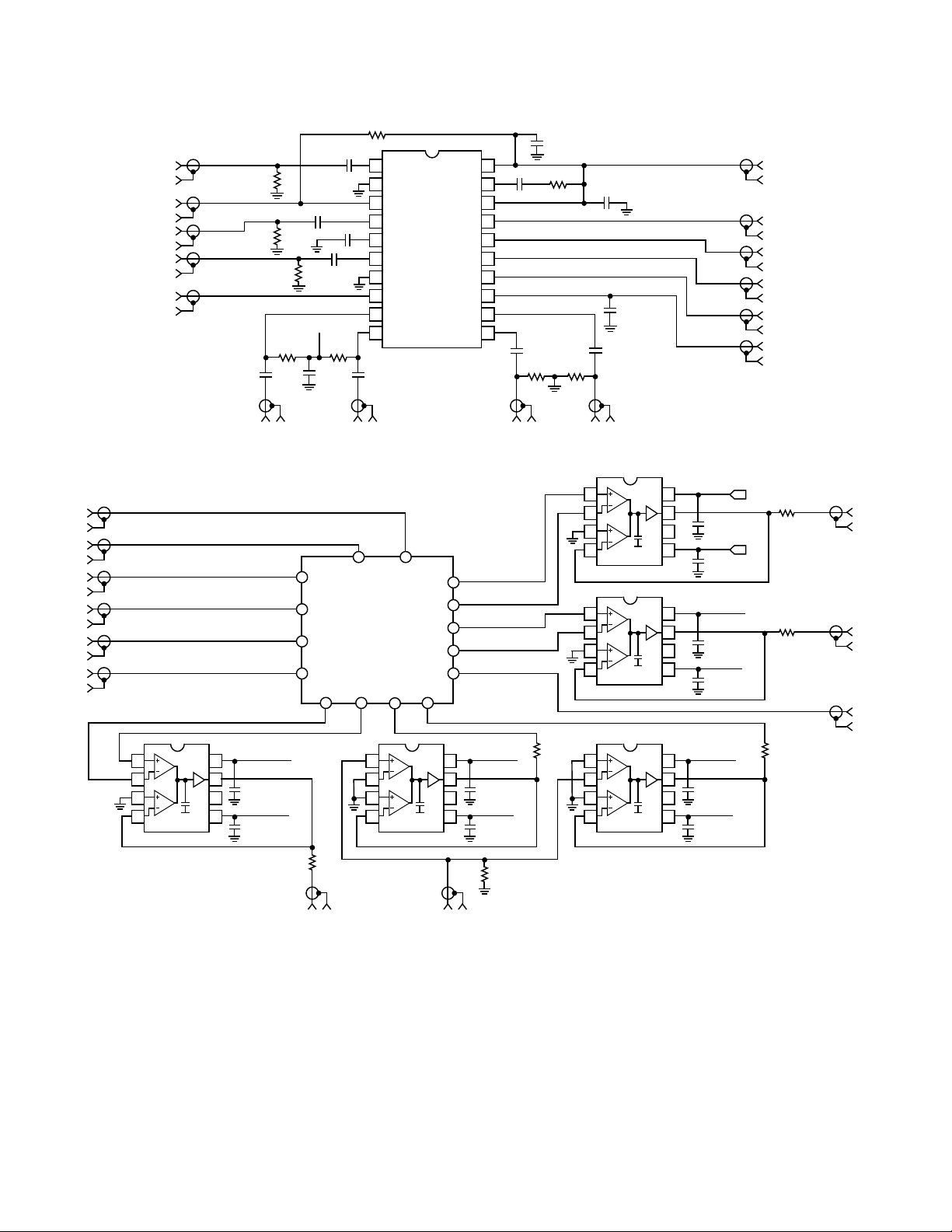

AD6459

VPOS

FREF

PRUP

LOIP

RFIP

GREF

FREF

PRUP

LOIP

RFHI

GREF

R9

50Ω

R2

50Ω

50Ω

OPENR4OPEN

C5

1nF

MXOP MXOM

R3

C13

10nF

R1

C2 1nF

VPOS

C4 1nF

C3

1nF

R5

C12

1nF

20kΩ

1

2

3

4

5

6

7

8

9

10

C6

1nF

FREF

COM1

PRUP

LOIP

RFLO

RFHI

COM2

GREF

MXOP

MXOM

AD6459

VSP1

FLTR

VSP2

IRXP

IRXN

QRXP

QRXN

GAIN

IFIM

IFIP

VPOS

20

19

18

17

16

15

14

13

12

11

1nF

C10 1nF

C7

IFIP

C1

0.1µF

R8 1kΩ

R6

50ΩR750Ω

Figure 1. AD6459 Characterization Board

FREF VPOS

PRUP

LOIP

AD6459

CHARACTERIZATION

RFIP

GREF

MXOP MXOM

BOARD

IFIP

IRXP

IRXN

QRXP

QRXN

GAIN

IFIN

IFIM

1

2

3

4

1

2

3

4

C11

0.1µF

C8

1nF

C9

10nF

(BOTTOM)

AD830

AD830

A=1

A=1

VPOS

IRXP

IRXN

QRXP

QRXN

GAIN

V

8

P

7

C6

0.1µF

6

V

5

N

V

P

V

N

C7

0.1µF

8

7

C4

0.1µF

6

5

C5

0.1µF

R4

V

P

50Ω

I

OUT

V

N

V

R3

P

50Ω I

OUT

V

N

GAIN

R6

50Ω

V

P

V

N

1

2

3

4

AD830

A=1

IFIN

V

8

P

7

C11

6

0.1µF

V

5

N

C10

0.1µF

R1

50Ω

V

A=1

8

P

7

C3

6

0.1µF

V

5

N

C2

0.1µF

V

V

N

MXOP

P

R2

50Ω

1

2

3

4

AD830

1

2

3

4

AD830

A=1

V

8

P

7

C9

6

0.1µF

V

5

N

C8

0.1µF

R5

50Ω

V

P

V

N

Figure 2. Characterization Test Set

–4–

REV. 0

Loading...

Loading...