Low Noise, Low Drift

INPUT OFFSET VOLTAGE DRIFT– µV/°C

–0.5–2.0

1.0 1.5 2.5

–2.5 –1.5 –1.0

0.5 2.0

0.0

NUMBER OF UNITS

0

15

5

10

30

25

20

OUTPUT

V

–

NOTE: CASE IS CONNECTED

TO PIN 8

OFFSET

NULL

IN+

IN–

CASE

3

4

5

6

7

8

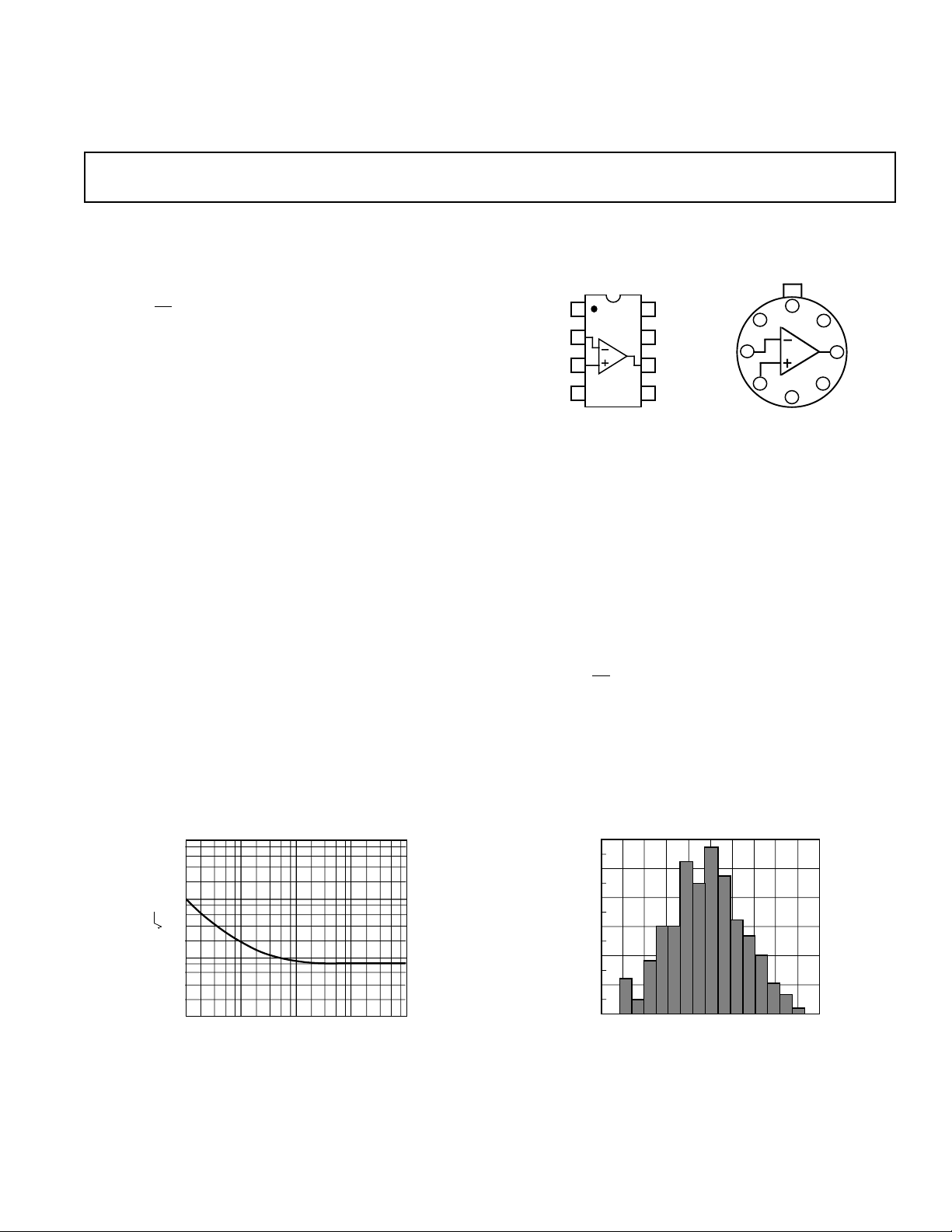

AD645

1

2

OFFSET

NULL

+V

8

7

6

5

TOP VIEW

AD645

1

4

2

3

NC = NO CONNECT

OFFSET

NULL

–IN

NC

OUTPUT

OFFSET

NULL

–V

S

+IN

+V

S

a

FEATURES

Improved Replacement for Burr-Brown

OPA-111 and OPA-121 Op Amp

LOW NOISE

2 mV p-p max, 0.1 Hz to 10 Hz

10 nV/√

11 fA p-p Current Noise 0.1 Hz to 10 Hz

HIGH DC ACCURACY

250 mV max Offset Voltage

1 mV/8C max Drift

1.5 pA max Input Bias Current

114 dB Open-Loop Gain

Available in Plastic Mini-DIP, 8-Pin Header Packages, or

APPLICATIONS

Low Noise Photodiode Preamps

CT Scanners

Precision I-V Converters

PRODUCT DESCRIPTION

The AD645 is a low noise, precision FET input op amp. It offers the pico amp level input currents of a FET input device

coupled with offset drift and input voltage noise comparable to a

high performance bipolar input amplifier.

The AD645 has been improved to offer the lowest offset drift in

a FET op amp, 1 µV/°C. Offset voltage drift is measured and

trimmed at wafer level for the lowest cost possible. An inherently low noise architecture and advanced manufacturing techniques result in a device with a guaranteed low input voltage

noise of 2 µV p-p, 0.1 Hz to 10 Hz. This level of dc performance

along with low input currents make the AD645 an excellent

choice for high impedance applications where stability is of

prime concern.

Hz max at 10 kHz

Chip Form

1k

IMPROVED

DRIFT

FET Op Amp

AD645

CONNECTION DIAGRAMS

8-Pin Plastic Mini-DIP

(N) Package

The AD645 is available in six performance grades. The AD645J

and AD645K are rated over the commercial temperature range

of 0°C to +70°C. The AD645A, AD645B, and the ultraprecision AD645C are rated over the industrial temperature

range of –40°C to +85°C. The AD645S is rated over the military

temperature range of –55°C to +125°C and is available

processed to MIL-STD-883B.

The AD645 is available in an 8-pin plastic mini-DIP, 8-pin

header, or in die form.

PRODUCT HIGHLIGHTS

1. Guaranteed and tested low frequency noise of 2 µV p-p max

and 20 nV/√

Hz at 100 Hz makes the AD645C ideal for low

noise applications where a FET input op amp is needed.

2. Low V

drift of 1 µV/°C max makes the AD645C an excel-

OS

lent choice for applications requiring ultimate stability.

3. Low input bias current and current noise (11 fA p-p 0.1 Hz to

10 Hz) allow the AD645 to be used as a high precision

preamp for current output sensors such as photodiodes, or as

a buffer for high source impedance voltage output sensors.

TO-99 (H) Package

100

nV/ Hz

10

VOLTAGE NOISE SPECTRAL DENSITY

1.0

FREQUENCY – Hz

Figure 1. AD645 Voltage Noise Spectral Density vs.

Frequency

REV. B

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

1k1 10 100

10k

Figure 2. Typical Distribution of Average Input Offset

Voltage Drift (196 Units)

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700 Fax: 617/326-8703

AD645–SPECIFICATIONS

(@ +258C, and 615 V dc, unless otherwise noted)

Model AD645J/A AD645K/B AD645C AD645S

Conditions

INPUT OFFSET VOLTAGE

1

1

Min Typ Max Min Typ Max Min Typ Max Min Typ Max Units

Initial Offset 100 500 50 250 50 250 100 500 µV

Offset T

MIN–TMAX

300 1000 100 400 75 300 500 1500 µV

Drift (Average) 3 10/5 1 5/2 0.5 1 4 10 µV/°C

vs. Supply (PSRR) 90 110 94 110 94 110 90 110 dB

vs. Supply T

INPUT BIAS CURRENT

2

MIN–TMAX

100 90 100 90 100 86 95 dB

Either Input VCM = 0 V 0.7/1.8 3/5 0.7/1.8 1.5/3 1.8 3 1.8 5 pA

Either Input

@ T

MAX

VCM = 0 V 16/115 16/115 115 1800 pA

Either Input VCM = +10 V 0.8/1.9 0.8/1.9 1.9 1.9 pA

Offset Current VCM = 0 V 0.1 1.0 0.1 0.5 0.1 0.5 0.1 1.0 pA

Offset Current

@ T

MAX

VCM = 0 V 2/6 2/6 6 100 pA

INPUT VOLTAGE NOISE 0.1 to 10 Hz 1.0 3.0 1.0 2.5 1 2 1.0 3.3 µV p-p

f = 10 Hz 20 50 20 40 20 40 20 50 nV/√Hz

f = 100 Hz 10 30 10 20 10 20 10 30 nV/√Hz

f = 1 kHz 9 15 9 12 9 12 9 15 nV/√Hz

f = 10 kHz 8 10 8 10 8 10 8 10 nV/√Hz

INPUT CURRENT NOISE f = 0.1 to 10 Hz 11 20 11 15 11 15 11 20 fA p-p

f = 0.1 thru 20 kHz 0.6 1.1 0.6 0.8 0.6 0.8 0.6 1.1 fA/√Hz

FREQUENCY RESPONSE

Unity Gain, Small Signal 2 2 2 2 MHz

Full Power Response VO = 20 V p-p

R

= 2 kΩ 16 32 16 32 16 32 16 32 kHz

Slew Rate, Unity Gain V

SETTLING TIME

3

LOAD

= 20 V p-p

OUT

R

= 2 kΩ 12 12 12 12 V/µs

LOAD

To 0.1% 6 6 6 6 µs

To 0.01% 8 8 8 8 µs

Overload Recovery

4

50% Overdrive 5 5 5 5 µs

Total Harmonic f = 1 kHz

Distortion R

LOAD

≥ 2 kΩ

VO = 3 V rms 0.0006 0.0006 0.0006 0.0006 %

INPUT IMPEDANCE

Differential V

= ±1 V 1012i110

DIFF

12

i110

12

i110

12

i1 ΩipF

Common-Mode 1014i2.2 1014i2.2 1014i2.2 1014i2.2 ΩipF

INPUT VOLTAGE RANGE

Differential

5

±20 ±20 ±20 ±20 V

Common-Mode Voltage ± 10 +11, –10.4 ±10 +11, –10.4 ±10 +11, –10.4 ±10 +11, –10.4 V

Over Max Oper. Range ±10 ±10 ±10 ±10 V

Common-Mode

Rejection Ratio VCM = ±10 V 90 110 94 110 94 110 90 110 dB

T

MIN–TMAX

100 90 100 90 100 86 100 dB

OPEN-LOOP GAIN VO = ±10 V

R

≥ 2 kΩ 114 130 120 130 120 130 114 130 dB

LOAD

T

MIN–TMAX

114 114 110 dB

OUTPUT CHARACTERISTICS

Voltage R

Current V

≥ 2 kΩ±10 ±11 ±10 ±11 ±10 ±11 ±10 ±11 V

LOAD

T

MIN–TMAX

= ±10 V ±5 ± 10 ±5 ±10 ±5 ±10 ±5 ±10 mA

OUT

±10 ±10 ±10 ±10 V

Short Circuit ±15 ±15 ±15 ±15 mA

POWER SUPPLY

Rated Performance ±15 ±15 ± 15 ±15 V

Operating Range ±5 ±18 ±5 ±18 ±5 ±18 ±5 ±18 V

Quiescent Current 3.0 3.5 3.0 3.5 3.0 3.5 3.0 3.5 mA

Transistor Count # of Transistors 62 62 62 62

NOTES

1

Input offset voltage specifications are guaranteed after 5 minutes of operation at TA = +25°C.

2

Bias current specifications are guaranteed maximum at either input after 5 minutes of operation at T

3

Gain = –1, R

4

Defined as the time required for the amplifier’s output to return to normal operation after removal of a 50% overload from the amplifier input.

5

Defined as the maximum continuous voltage between the inputs such that neither input exceeds ±10 V from ground.

LOAD

= 2 kΩ.

= +25°C. For higher temperature, the current doubles every 10°C.

A

All min and max specifications are guaranteed.

Specifications subject to change without notice.

–2–

REV. B

AD645

INPUT VOLTAGE NOISE – µV p-p

25

20

15

10

5

0

NUMBER OF UNITS

0.4 1.0

1.2

1.4

1.6

1.80.6 0.8

WARNING!

ESD SENSITIVE DEVICE

ABSOLUTE MAXIMUM RATINGS

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±18 V

Internal Power Dissipation

2

(@ T

8-Pin Header Package . . . . . . . . . . . . . . . . . . . . . . 500 mW

8-Pin Mini-DIP Package . . . . . . . . . . . . . . . . . . . . 750 mW

Input Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±V

Output Short Circuit Duration . . . . . . . . . . . . . . . . Indefinite

Differential Input Voltage . . . . . . . . . . . . . . . . . . +V

Storage Temperature Range (H) . . . . . . . . . –65°C to +150°C

Storage Temperature Range (N) . . . . . . . . . –65°C to +125°C

Operating Temperature Range

AD645J/K . . . . . . . . . . . . . . . . . . . . . . . . . . . 0°C to +70°C

1

= +25°C)

A

and –V

S

AD645A/B/C . . . . . . . . . . . . . . . . . . . . . . . –40°C to +85°C

AD645S . . . . . . . . . . . . . . . . . . . . . . . . . . –55°C to +125°C

Lead Temperature Range

(Soldering 60 sec) . . . . . . . . . . . . . . . . . . . . . . . . . . . +300°C

NOTES

1

S

Stresses above those listed under “Absolute Maximum Ratings” may cause

permanent damage to the device. This is a stress rating only and functional

operation of the device at these or any other conditions above those indicated

S

in the operational section of this specification is not implied. Exposure to

absolute maximum rating conditions for extended periods may affect device

reliability.

2

Thermal Characteristics:

8-Pin Plastic Mini-DIP Package: θJA = 100°C/Watt

8-Pin Header Package: θJA = 200°C/Watt

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD645 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

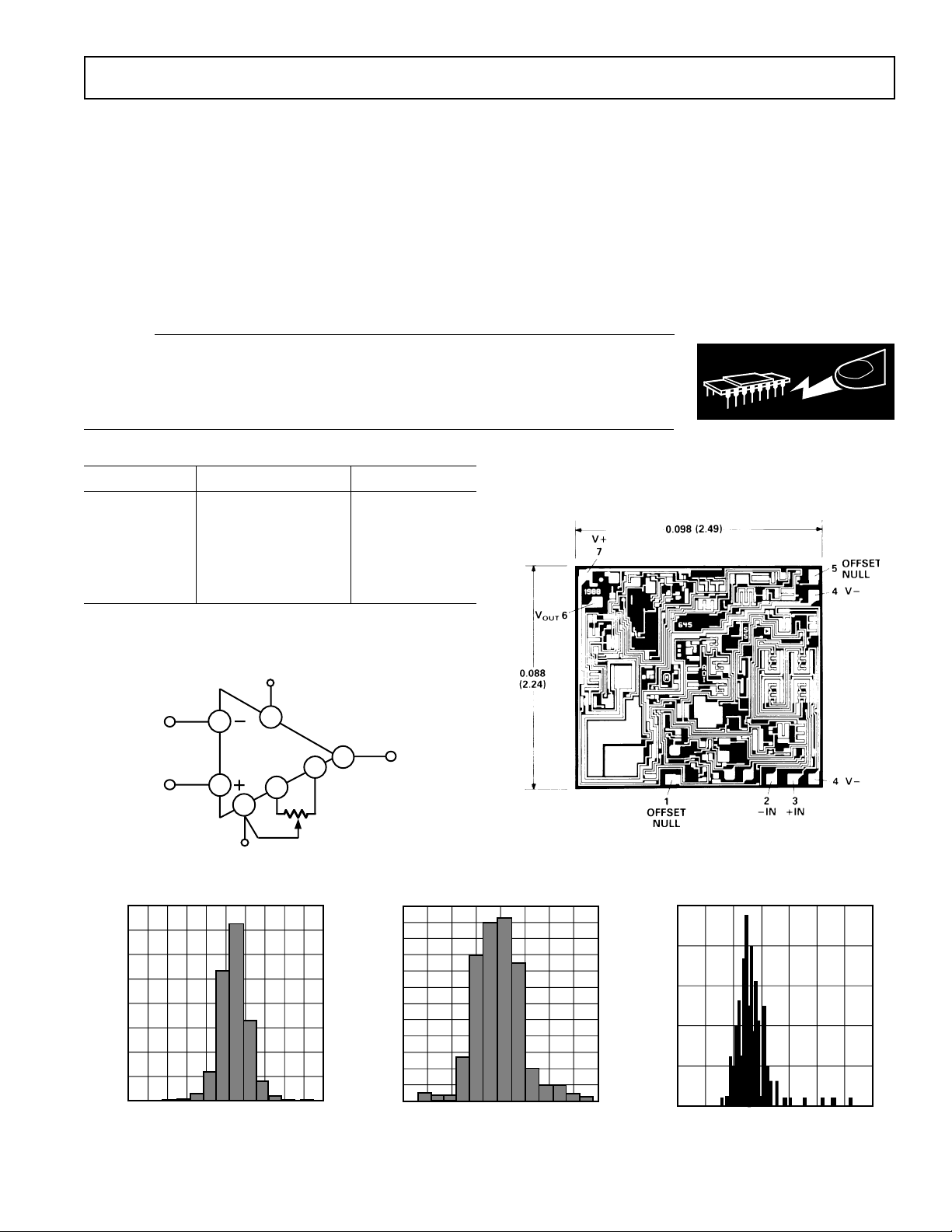

METALIZATION PHOTOGRAPH

Dimensions shown in inches and (mm).

Contact factory for latest dimensions.

Model

ORDERING GUIDE

1

Temperature Range Package Option

2

AD645JN 0°C to +70°C N-8

AD645KN 0°C to +70°C N-8

AD645AH –40°C to +85°C H-08A

AD645BH –40°C to +85°C H-08A

AD645CH –40°C to +85°C H-08A

AD645SH/883B –55°C to +125°C H-08A

NOTES

1

Chips are also available.

2

N = Plastic Mini-DIP; H = Metal Can.

+V

S

800

700

600

500

400

300

NUMBER OF UNITS

200

100

0

–1.0 0.8–0.4 –0.2 0.0 0.4 0.6 1.0–0.6 0.2–0.8

Figure 4. Typical Distribution of Input

Offset Voltage (1855 Units)

REV. B

AD645

4

–V

S

7

1

5

10k

V ADJUST

OS

6

2

3

Figure 3. AD645 Offset Null Configuration

120

110

100

90

80

70

60

50

40

NUMBER OF UNITS

30

20

10

0

0.0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0

INPUT OFFSET VOLTAGE – mV

Figure 5. Typical Distribution of Input

Bias Current (576 Units)

INPUT BIAS CURRENT – pA

Figure 6. Typical Distribution of 0.1 Hz

to 10 Hz Voltage Noise (202 Units)

–3–

Loading...

Loading...