Page 1

Introduction to Avalon Verification IP Suite

User Guide

Subscribe

Send Feedback

UG-01073

2014.06.30

101 Innovation Drive

San Jose, CA 95134

www.altera.com

Page 2

TOC-2

Introduction to Avalon Verification IP SuiteUser Guide

Contents

Introduction to Avalon Verification IP Suite ....................................................1-1

Clock Source BFM ..............................................................................................2-1

Advantages of Using BFMs and Monitors ..............................................................................................1-1

BFM Implementation .................................................................................................................................1-1

Application Programming Interface ........................................................................................................1-3

Application Example of BFMs ..................................................................................................................1-3

Parameters ....................................................................................................................................................2-1

Clock Source API.........................................................................................................................................2-1

Clock_stop() ....................................................................................................................................2-2

get_run_state() ................................................................................................................................2-2

get_version() ....................................................................................................................................2-2

Reset Source BFM ...............................................................................................3-1

Parameters ....................................................................................................................................................3-1

Reset Source API..........................................................................................................................................3-1

reset_deassert ...................................................................................................................................3-2

get_version() ....................................................................................................................................3-2

Avalon Interrupt Source and Interrupt Sink BFMs ..........................................4-1

Parameters ....................................................................................................................................................4-1

Interrupt Source and Sink API...................................................................................................................4-2

get_irq() ............................................................................................................................................4-2

get_version() ....................................................................................................................................4-2

set_irq() ............................................................................................................................................4-3

Avalon-MM Master BFM ...................................................................................5-1

Timing ..........................................................................................................................................................5-2

Block Diagram .............................................................................................................................................5-5

Parameters ....................................................................................................................................................5-6

Avalon-MM Master BFM API...................................................................................................................5-9

event_all_transactions_complete() ...............................................................................................5-9

Altera Corporation

Page 3

Introduction to Avalon Verification IP SuiteUser Guide

TOC-3

event_command_issued().............................................................................................................5-10

event_max_command_queue_size() .........................................................................................5-10

event_min_command_queue_size() ..........................................................................................5-10

event_read_response_complete() ...............................................................................................5-10

event_response_complete() .........................................................................................................5-11

event_write_response_complete()...............................................................................................5-11

get_command_issued_queue_size() ..........................................................................................5-11

get_command_pending_queue_size() .......................................................................................5-12

get_read_response_queue_size() ................................................................................................5-12

get_response_address() ................................................................................................................5-12

get_response_byte_enable() ........................................................................................................5-13

get_response_burst_size() ...........................................................................................................5-13

get_response_data() ......................................................................................................................5-13

get_response_latency() .................................................................................................................5-14

get_response_queue_size() ..........................................................................................................5-14

get_response_read_id() ................................................................................................................5-14

get_response_read_response() ....................................................................................................5-15

get_response_request() ................................................................................................................5-15

get_response_wait_time() ............................................................................................................5-15

get_response_write_id() ..............................................................................................................5-16

get_response_write_response() ..................................................................................................5-16

get_write_response_queue_size() ...............................................................................................5-16

get_version() ..................................................................................................................................5-17

init() ................................................................................................................................................5-17

pop_response() ..............................................................................................................................5-17

push_command() ..........................................................................................................................5-18

set_clken() ......................................................................................................................................5-18

set_command_address() ..............................................................................................................5-18

set_command_arbiterlock() ........................................................................................................5-19

set_command_byte_enable() ......................................................................................................5-19

set_command_burst_count() ......................................................................................................5-19

set_command_burst_size() .........................................................................................................5-20

set_command_data() ....................................................................................................................5-20

set_command_debugaccess() ......................................................................................................5-20

set_command_idle() .....................................................................................................................5-21

set_command_init_latency() ......................................................................................................5-21

set_command_lock() ....................................................................................................................5-21

set_command_request() ..............................................................................................................5-22

set_command_timeout() .............................................................................................................5-22

Altera Corporation

Page 4

TOC-4

Introduction to Avalon Verification IP SuiteUser Guide

set_command_transaction_id() ..................................................................................................5-22

set_command_write_response_request() .................................................................................5-23

set_max_command_queue_size() ..............................................................................................5-23

set_min_command_queue_size() ..............................................................................................5-23

set_response_timeout() ................................................................................................................5-24

signal_all_transactions_complete ...............................................................................................5-24

signal_command_issued ..............................................................................................................5-24

signal_fatal_error ..........................................................................................................................5-25

signal_max_command_queue_size ............................................................................................5-25

signal_min_command_queue_size ............................................................................................5-25

signal_read_response_complete .................................................................................................5-26

signal_response_complete ...........................................................................................................5-26

signal_write_response_complete ................................................................................................5-26

Avalon-MM Slave BFM ......................................................................................6-1

Timing ..........................................................................................................................................................6-2

Block Diagram .............................................................................................................................................6-6

Parameters ....................................................................................................................................................6-7

Avalon-MM Slave BFM API....................................................................................................................6-10

event_command_received() ........................................................................................................6-10

event_response_issued() ..............................................................................................................6-10

event_max_response_queue_size() ............................................................................................6-11

event_min_response_queue_size() ............................................................................................6-11

get_clken() .....................................................................................................................................6-11

get_command_address() .............................................................................................................6-11

get_command_arbiterlock() ........................................................................................................6-12

get_command_burst_count() .....................................................................................................6-12

get_command_burst_cycle() .......................................................................................................6-12

get_command_byte_enable() ......................................................................................................6-13

get_command_data() ...................................................................................................................6-13

get_command_debugaccess() .....................................................................................................6-13

get_command_queue_size() .......................................................................................................6-14

get_command_lock() ...................................................................................................................6-14

get_command_request() ..............................................................................................................6-14

get_command_transaction_id() .................................................................................................6-15

get_command_write_response_request() .................................................................................6-15

get_pending_read_latency_cycle() .............................................................................................6-15

get_pending_write_latency_cycle() ............................................................................................6-16

Altera Corporation

Page 5

Introduction to Avalon Verification IP SuiteUser Guide

TOC-5

get_response_queue_size() ..........................................................................................................6-16

vget_slave_bfm_status ..................................................................................................................6-16

get_version() ..................................................................................................................................6-17

init() ................................................................................................................................................6-17

pop_command() ...........................................................................................................................6-17

push_response() ............................................................................................................................6-18

set_command_transaction_mode() ...........................................................................................6-18

set_interface_wait_time() ............................................................................................................6-18

vset_max_response_queue_size() ..............................................................................................6-19

set_min_response_queue_size() .................................................................................................6-19

set_read_response_id() ................................................................................................................6-19

set_read_response_status() .........................................................................................................6-19

set_response_burst_size() ............................................................................................................6-20

set_response_data() ......................................................................................................................6-20

set_response_latency() .................................................................................................................6-20

set_response_request() .................................................................................................................6-21

set_response_timeout() ................................................................................................................6-21

set_write_response_id() ...............................................................................................................6-21

set_write_response_status() ........................................................................................................6-22

signal_command_received() .......................................................................................................6-22

signal_error_exceed_max_pending_reads ................................................................................6-22

signal_max_response_queue_size ..............................................................................................6-23

signal_min_command_queue_size ............................................................................................6-23

signal_fatal_error ..........................................................................................................................6-23

signal_response_issued ................................................................................................................6-24

Avalon-MM Monitor ..........................................................................................7-1

Parameters ....................................................................................................................................................7-2

Avalon-MM Monitor Assertion Checking API ......................................................................................7-4

set_enable_a_address_align_with_data_width() .......................................................................7-4

set_enable_a_beginbursttransfer_exist() .....................................................................................7-5

set_enable_a_beginbursttransfer_legal() .....................................................................................7-5

set_enable_a_beginbursttransfer_single_cycle() ........................................................................7-5

set_enable_a_begintransfer_exist() ..............................................................................................7-6

set_enable_a_begintransfer_legal() ..............................................................................................7-6

set_enable_a_begintransfer_single_cycle() .................................................................................7-6

set_enable_a_burst_legal() ............................................................................................................7-7

set_enable_a_byteenable_legal() ...................................................................................................7-7

Altera Corporation

Page 6

TOC-6

Introduction to Avalon Verification IP SuiteUser Guide

set_enable_a_constant_during_burst() .......................................................................................7-7

set_enable_a_constant_during_clk_disabled() ..........................................................................7-8

set_enable_a_constant_during_waitrequest() ............................................................................7-8

set_enable_a_exclusive_read_write() ...........................................................................................7-8

set_enable_a_half_cycle_reset_legal() .........................................................................................7-9

set_enable_a_less_than_burstcount_max_size() .......................................................................7-9

set_enable_a_less_than_maximumpendingreadtransactions() ...............................................7-9

set_enable_a_no_readdatavalid_during_reset() ......................................................................7-10

set_enable_a_no_read_during_reset() ......................................................................................7-10

set_enable_a_no_write_during_reset() .....................................................................................7-10

set_enable_a_readid_sequence() ................................................................................................7-11

set_enable_a_read_response_sequence() ..................................................................................7-11

set_enable_a_read_response_timeout() ....................................................................................7-11

set_enable_a_register_incoming_signals() ...............................................................................7-12

set_enable_a_waitrequest_during_reset() .................................................................................7-12

set_enable_a_waitrequest_timeout() .........................................................................................7-12

set_enable_a_write_burst_timeout() .........................................................................................7-13

set_enable_a_writeid_sequence() ...............................................................................................7-13

Coverage Group ............................................................................................................................7-13

Transaction Monitoring ...............................................................................................................7-24

Avalon-ST Source BFM ......................................................................................8-1

Timing ..........................................................................................................................................................8-1

Block Diagram .............................................................................................................................................8-2

Parameters ....................................................................................................................................................8-3

Avalon-ST Source API................................................................................................................................8-4

event_min_transaction_queue_size() ..........................................................................................8-5

event_response_done() ..................................................................................................................8-5

event_src_driving_transaction() ...................................................................................................8-5

event_src_not_ready() ...................................................................................................................8-5

event_src_ready() ............................................................................................................................8-6

event_src_transaction_complete() ...............................................................................................8-6

get_response_latency() ...................................................................................................................8-6

get_response_queue_size() ............................................................................................................8-7

get_src_ready() ................................................................................................................................8-7

get_src_transaction_complete() ...................................................................................................8-7

get_transaction_queue_size() ........................................................................................................8-7

get_version() ....................................................................................................................................8-8

Altera Corporation

Page 7

Introduction to Avalon Verification IP SuiteUser Guide

TOC-7

init() ..................................................................................................................................................8-8

pop_response() ................................................................................................................................8-8

push_transaction() ..........................................................................................................................8-9

set_max_transaction_queue_size() ..............................................................................................8-9

set_min_transaction_queue_size() ...............................................................................................8-9

set_response_timeout() ................................................................................................................8-10

set_transaction_channel() ...........................................................................................................8-10

set_transaction_data() ..................................................................................................................8-10

set_transaction_idles() .................................................................................................................8-11

set_transaction_eop() ...................................................................................................................8-11

set_transaction_empty() ..............................................................................................................8-11

set_transaction_error() ................................................................................................................8-11

set_transaction_sop() ...................................................................................................................8-12

signal_fatal_error ..........................................................................................................................8-12

signal_max_transaction_queue_size ..........................................................................................8-12

signal_min_transaction_queue_size ..........................................................................................8-12

signal_response_done ..................................................................................................................8-13

signal_src_driving_transaction ...................................................................................................8-13

signal_src_not_ready ....................................................................................................................8-13

signal_src_ready ............................................................................................................................8-13

signal_src_transaction_complete ...............................................................................................8-14

Avalon-ST Sink BFM ..........................................................................................9-1

Timing ..........................................................................................................................................................9-1

Block Diagram .............................................................................................................................................9-2

Parameters ....................................................................................................................................................9-3

Application Program Interface..................................................................................................................9-4

event_sink_ready_assert() .............................................................................................................9-5

event_sink_ready_deassert() .........................................................................................................9-5

get_transaction_channel() .............................................................................................................9-5

get_transaction_data() ...................................................................................................................9-5

get_transaction_idles() ...................................................................................................................9-6

get_transaction_eop() .....................................................................................................................9-6

get_transaction_empty() ................................................................................................................9-6

get_transaction_error() ..................................................................................................................9-7

get_transaction_queue_size() ........................................................................................................9-7

get_transaction_sop() .....................................................................................................................9-7

get_version() ....................................................................................................................................9-8

Altera Corporation

Page 8

TOC-8

Introduction to Avalon Verification IP SuiteUser Guide

init() ..................................................................................................................................................9-8

pop_transaction() ............................................................................................................................9-8

set_ready() ........................................................................................................................................9-9

signal_fatal_error ............................................................................................................................9-9

signal_sink_ready_assert ...............................................................................................................9-9

signal_sink_ready_deassert .........................................................................................................9-10

signal_transaction_received ........................................................................................................9-10

Avalon-ST Monitor ...........................................................................................10-1

Parameters .................................................................................................................................................10-2

Avalon-ST Monitor Assertion Checking API........................................................................................10-3

set_enable_a_empty_legal() ........................................................................................................10-3

set_enable_a_less_than_max_channel() ...................................................................................10-3

set_enable_a_no_data_outside_packet() ...................................................................................10-4

set_enable_a_non_missing_endofpacket() ...............................................................................10-4

set_enable_a_non_missing_startofpacket() ..............................................................................10-4

set_enable_a_valid_legal() ...........................................................................................................10-5

Coverage Group ............................................................................................................................10-5

Transaction Monitoring ............................................................................................................10-14

Conduit BFM ....................................................................................................11-1

Parameters .................................................................................................................................................11-2

Conduit BFM API......................................................................................................................................11-2

event_reset_asserted .....................................................................................................................11-3

get_<role name>().........................................................................................................................11-3

get_version() ..................................................................................................................................11-3

set_<role name>() .........................................................................................................................11-4

set_<role name>_oe() ...................................................................................................................11-4

signal_input_<role name>_change ............................................................................................11-4

Tri-State Conduit BFM.....................................................................................12-1

Parameters .................................................................................................................................................12-2

Tri-State Conduit BFM API.....................................................................................................................12-2

event_interface_granted() ............................................................................................................12-3

event_grant_deasserted_while_request_remain_asserted ......................................................12-3

event_max_transaction_queue_size() .......................................................................................12-3

event_min_transaction_queue_size() ........................................................................................12-4

Altera Corporation

Page 9

Introduction to Avalon Verification IP SuiteUser Guide

get_input_transaction_queue_size()...........................................................................................12-4

get_output_transaction_queue_size() .......................................................................................12-4

get_transaction_<role name>_in() .............................................................................................12-4

get_transaction_latency() ............................................................................................................12-5

get_version() ..................................................................................................................................12-5

pop_transaction() .........................................................................................................................12-5

push_transaction() ........................................................................................................................12-6

set_max_transaction_queue_size() ............................................................................................12-6

set_min_transaction_queue_size() .............................................................................................12-6

set_num_of_transactions() ..........................................................................................................12-7

set_transaction_<role name>_out() ...........................................................................................12-7

set_transaction_<role name>_outen() ......................................................................................12-7

set_transaction_idles() .................................................................................................................12-7

set_valid_transaction_<role name>_out() ................................................................................12-8

signal_all_transactions_complete ...............................................................................................12-8

signal_fatal_error ..........................................................................................................................12-8

signal_grant_deasserted_while_request_remain_asserted .....................................................12-9

signal_interface_granted ..............................................................................................................12-9

signal_max_transaction_queue_size ..........................................................................................12-9

signal_min_transaction_queue_size ........................................................................................12-10

TOC-9

External Memory BFM .....................................................................................13-1

Using the External Memory BFM ..........................................................................................................13-2

Parameters .................................................................................................................................................13-2

External Memory BFM API.....................................................................................................................13-5

read() ...............................................................................................................................................13-5

signal_api_call ...............................................................................................................................13-6

write() .............................................................................................................................................13-6

Nios II Custom Instruction Master BFM .........................................................14-1

Parameters .................................................................................................................................................14-2

Nios II Custom Instruction API..............................................................................................................14-3

event_result_received() ................................................................................................................14-3

Nios II Custom Instruction Slave BFM ............................................................15-1

Parameters .................................................................................................................................................15-2

Nios II Custom Instruction Slave BFM API..........................................................................................15-3

Altera Corporation

Page 10

TOC-10

Introduction to Avalon Verification IP SuiteUser Guide

event_instruction_inconsistent() ................................................................................................15-3

event_instruction_unchanged() .................................................................................................15-3

event_result_driven() ...................................................................................................................15-4

event_result_done() ......................................................................................................................15-4

event_unknown_instruction_received() ...................................................................................15-4

get_ci_clk_en() ..............................................................................................................................15-5

get_instruction_a() .......................................................................................................................15-5

get_instruction_b() .......................................................................................................................15-5

get_instruction_c() .......................................................................................................................15-5

get_instruction_dataa() ................................................................................................................15-6

get_instruction_datab() ...............................................................................................................15-6

get_instruction_idle() ...................................................................................................................15-6

get_instruction_n() .......................................................................................................................15-6

get_instruction_readra() ..............................................................................................................15-7

get_instruction_readrb() ..............................................................................................................15-7

get_instruction_writerc() .............................................................................................................15-7

get_version() ..................................................................................................................................15-8

insert_result() ................................................................................................................................15-8

retrieve_instruction() ...................................................................................................................15-9

set_clock_enable_timeout() ........................................................................................................15-9

set_instruction_a() ......................................................................................................................15-10

set_instruction_b() .....................................................................................................................15-10

set_instruction_c() ......................................................................................................................15-10

set_instruction_timeout() ..........................................................................................................15-10

set_result_delay() ........................................................................................................................15-11

set_result_err_inject() ................................................................................................................15-11

set_result_value() ........................................................................................................................15-11

signal_fatal_error ........................................................................................................................15-11

signal_instructions_inconsistent ..............................................................................................15-12

signal_known_instruction_received ........................................................................................15-12

signal_result_done ......................................................................................................................15-12

signal_result_driven ...................................................................................................................15-13

signal_unknown_instruction_received ...................................................................................15-13

Avalon-ST Verilog HDL Testbench .................................................................16-1

Altera Corporation

Verifying Avalon-ST DUT ......................................................................................................................16-1

Understanding the Test Steps .................................................................................................................16-2

Setting up the Test ........................................................................................................................16-3

Page 11

Introduction to Avalon Verification IP SuiteUser Guide

Running the Simulation ...............................................................................................................16-5

Observing the Results ...................................................................................................................16-6

TOC-11

Avalon-MM Verilog HDL and VHDL Testbenches.........................................17-1

Avalon-MM Verilog HDL Testbench Description...............................................................................17-1

Running the Verilog HDL Testbench for a Single Avalon-MM Master and Slave

Pair..............................................................................................................................................17-2

Running the Verilog HDL Testbench for the Two Avalon-MM Masters and Slaves..........17-4

Avalon-MM VHDL Testbench Description..........................................................................................17-6

Running the Testbench for a Single Avalon-MM Master and Slave Pair..............................17-7

Running the Testbench for Two Avalon-MM Masters Slaves................................................17-9

Using the VHDL BFMs .........................................................................................................................17-10

Document Revision History .............................................................................18-1

How to Contact Altera .............................................................................................................................18-2

Typographic Conventions .......................................................................................................................18-2

Altera Corporation

Page 12

Introduction to Avalon Verification IP Suite

www.altera.com

101 Innovation Drive, San Jose, CA 95134

1

Subscribe

Send Feedback

The Avalon®Verification IP Suite provides bus functional models (BFMs) to simulate the behavior and

facilitate the verification of IP. The Verification IP Suite includes BFMs for the following interfaces and

components:

• Avalon Memory-Mapped (Avalon-MM) master and slave interfaces

• Avalon Streaming (Avalon-ST) source and sink interfaces

• Conduit interfaces and Avalon Tri-State conduit (Avalon-TC) interfaces

• Clock source and reset source

• Interrupt source and sink

• Custom instruction master and slave

• External memory

This suite also provides the following monitors to verify the respective Avalon protocols:

• Avalon-MM monitor

• Avalon-ST monitor

Advantages of Using BFMs and Monitors

Using the Altera-provided BFMs and monitors has the following advantages:

• It accelerates the verification process by providing key components of the verification testbench.

• It provides AvalonBFM components that implement the standard Avalon-MM and Avalon-ST protocols,

serving as a reference for those protocols.

• For SystemVerilog users, the verification suite provides a platform that you can use to implement

constraint-driven randomized tests. For example, you can implement the following modules for random

testing:

• Traffic scenario drivers

• Scoreboard and coverage facilities

• Assertion checkers

BFM Implementation

Most components in the Avalon Verification IP Suite BFMs are implemented in SystemVerilog. The exceptions

are the Clock Source and Reset Source BFMs that are written in VHDL. The BFM components use primarily

©

2014 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words

and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other

words and logos identified as trademarks or service marks are the property of their respective holders as described at

www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with

Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes

no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly

agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published

information and before placing orders for products or services.

ISO

9001:2008

Registered

Page 13

1-2

BFM Implementation

Verilog HDL with a few basic SystemVerilog constructs that are supported by ModelSim®-Altera Edition

(AE).

The Quartus II software version 13.0 and higher extends VHDL BFM support in Qsys. The VHDL BFMs

wrap the SystemVerilog implementation and include additional logic to support VDHL.

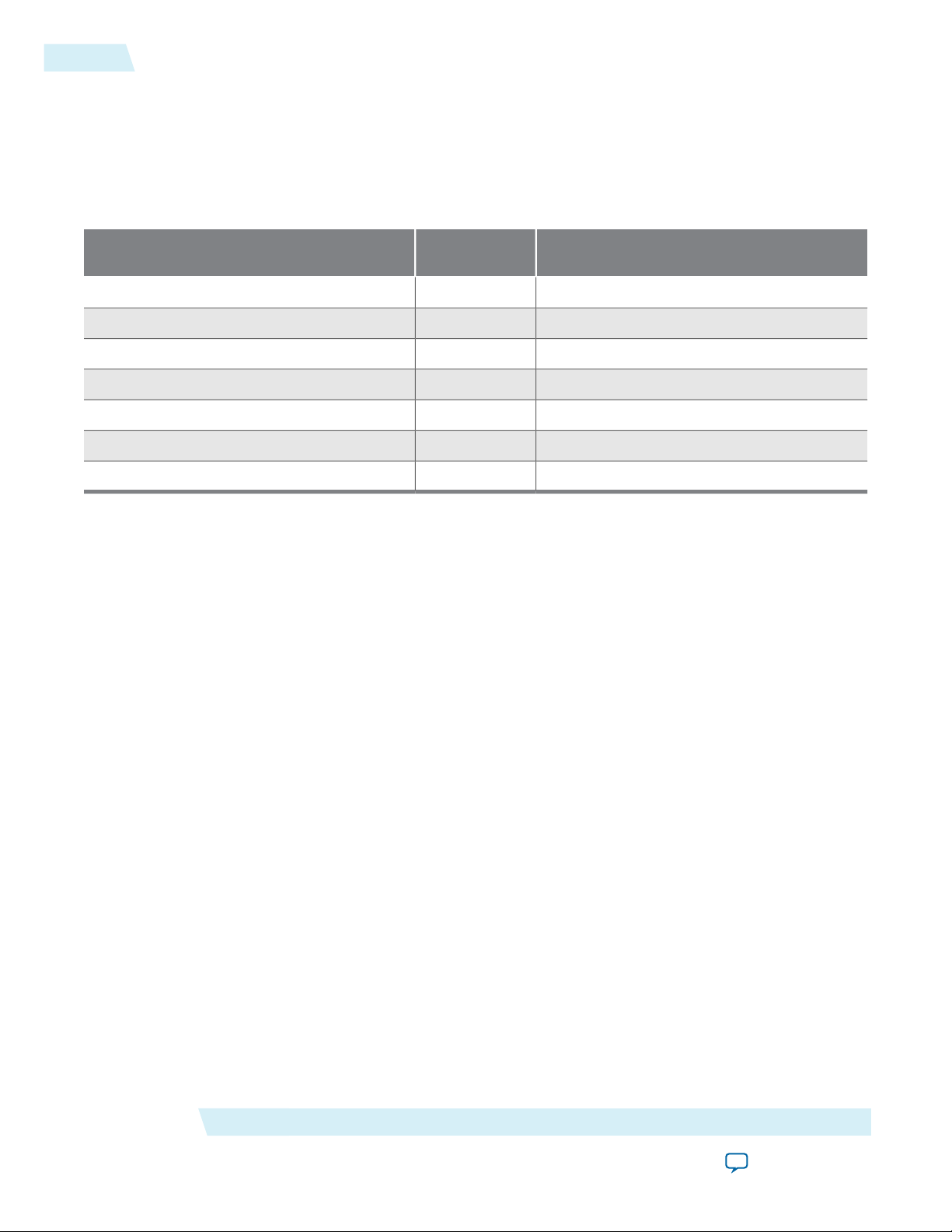

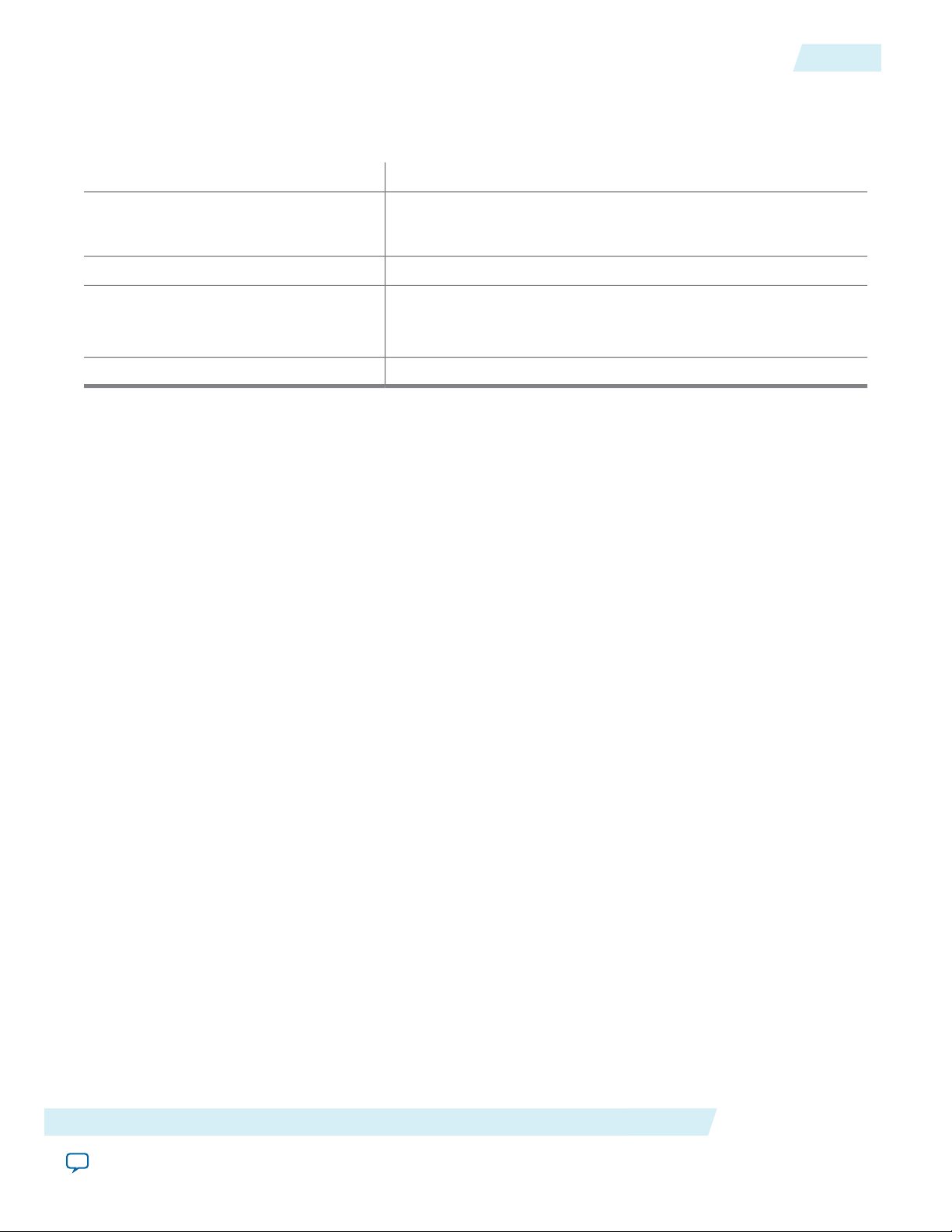

Table 1-1: BFM Language Support

BFM

Support

VHDL SupportVerilog HDL

YesYesClock Source and Reset Source

Version 13.0 and higherYesAvalon Interrupt Source and Sink

Version 13.0 and higherYesAvalon-MM Master, Slave, and Monitor

Version 13.0 and higherYesAvalon-ST Source, Sink, and Monitor

Version 14.0 and higherYesConduit and Tri-State Conduit

Version 13.0 and higherYesExternal Memory

Version 13.0 and higherYesNios II Custom Instruction Master and Slave

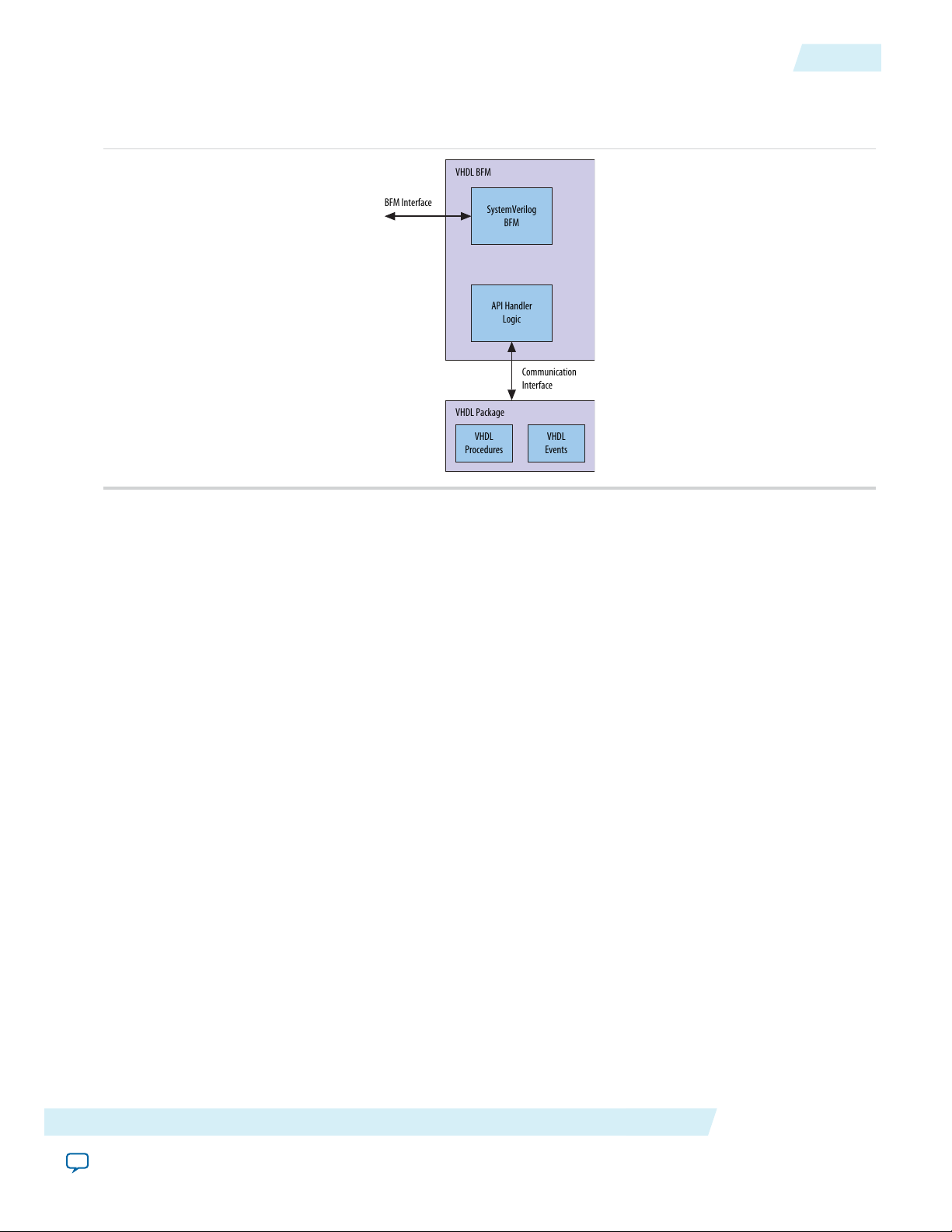

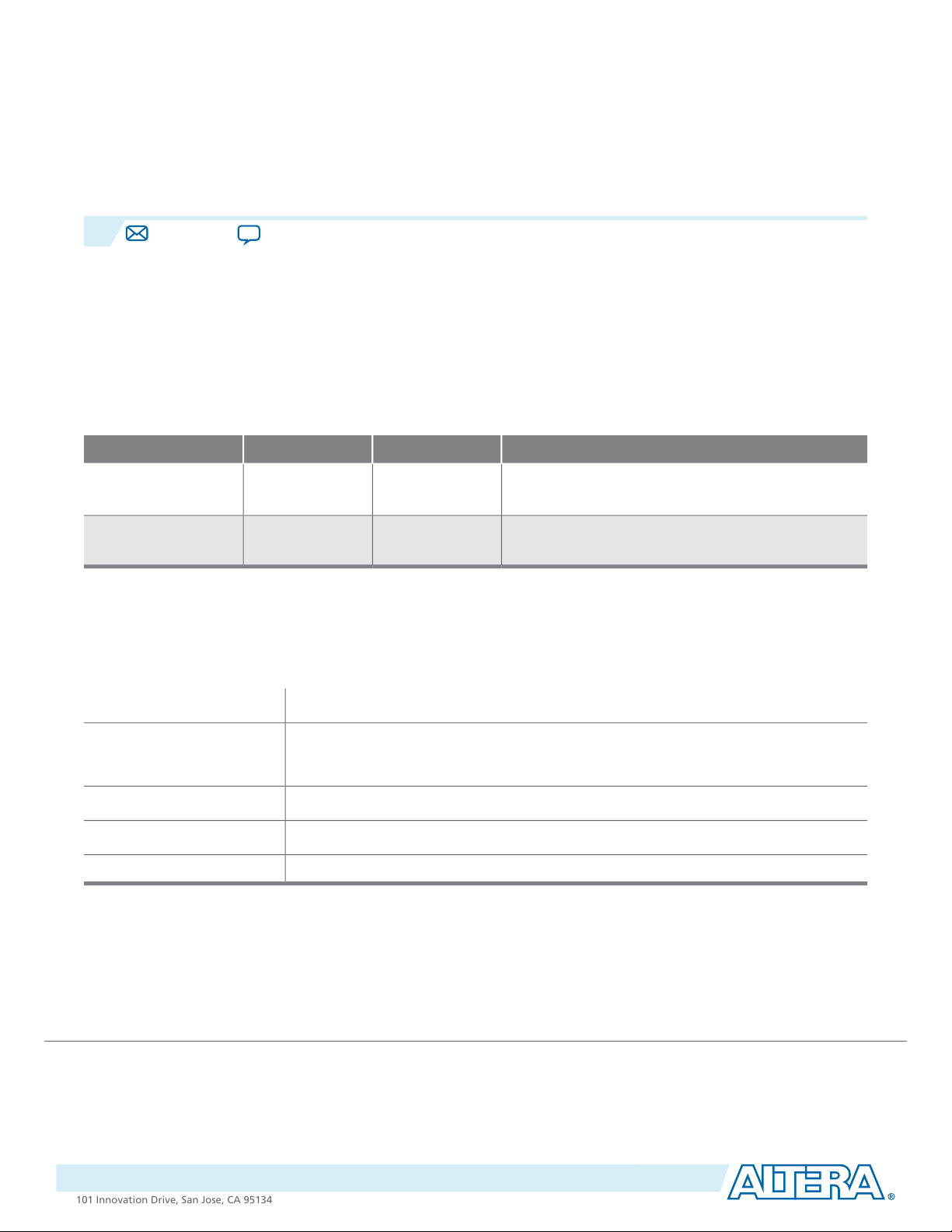

The VHDL BFM has four parts as shown in the figure below.

• SystemVerilog BFM—Contains the BFM implementation and behavioral model, and the SystemVerilog

API. The SystemVerilog code is IEEE encrypted for use in single-language simulators.

• VHDL package—Provides the VHDL API used to control the BFM and interface with your test program.

The package contains VHDL procedures and events.

• API handler logic—SystemVerilog logic block that translates your test program’s VHDL API calls to

SystemVerilog API calls. The SystemVerilog code is IEEE encrypted for use in single-language simulators.

Altera Corporation

Introduction to Avalon Verification IP Suite

Send Feedback

Page 14

API

Interaction

BFM Interface

VHDL BFM

Communication

Interface

VHDL

Procedures

VHDL

Events

VHDL Package

SystemVerilog

BFM

API Handler

Logic

Application Programming Interface

• API communication interface—Bridges the VHDL API to the API handler logic.

Figure 1-1: VHDL Component BFM

1-3

The monitor components use the SystemVerilog Assertion (SVA) language and are supported only by

simulators that support SVA, including:

• Modelsim-Altera Starter Edition (ASE)

• Synopsys VCS

• Mentor Graphics®Questa.

Application Programming Interface

Altera provides you with a set of application programming interfaces (API) for each Avalon Verification IP

Suite BFM. You can use the APIs to construct, instantiate, control, and query signals in all BFM components.

Your test programs must use only these public access methods and events to communicate with each BFM.

Note:

You can design custom verification environments that do not take advantage of the API. However,

Altera does not guarantee continued support or backwards compatibility custom methods.

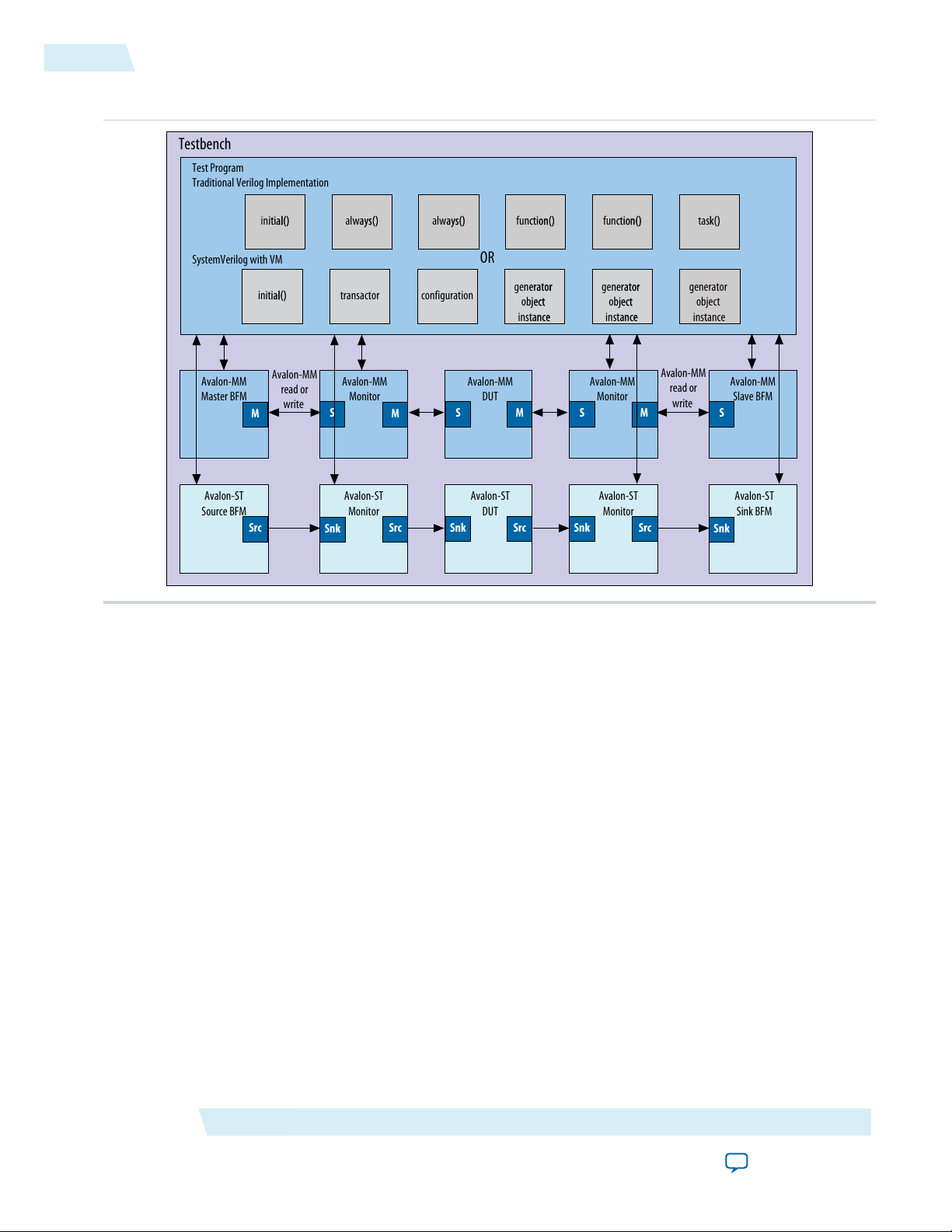

Application Example of BFMs

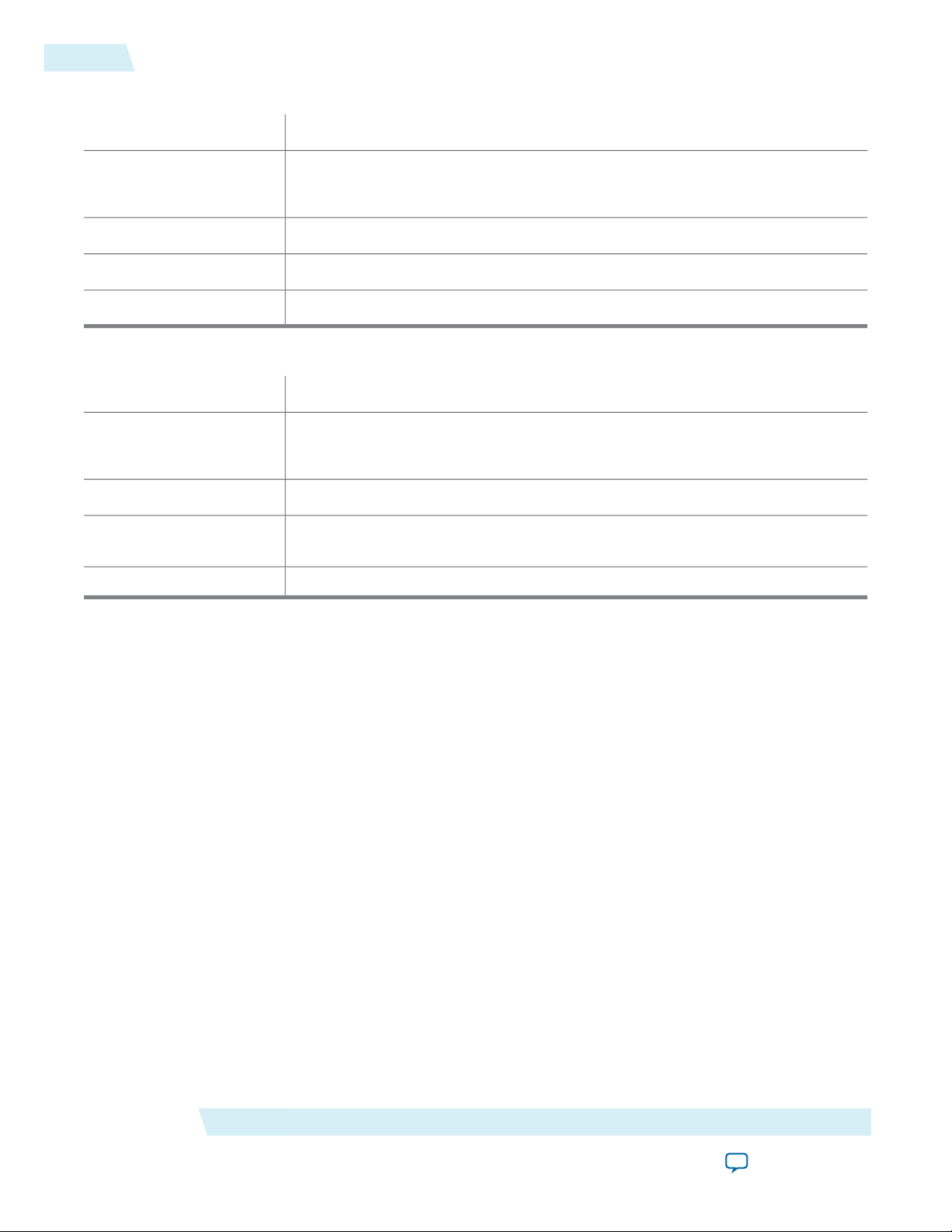

The figure below shows an Avalon-MM design with the following components:

• An Avalon-MM device under test (DUT) that includes both Avalon-MM master and slave interfaces

• An Avalon-ST DUT that includes both source and sink interfaces, although typical components might

include a single Avalon interface.

This figure illustrates it is possible to write a testbench using a traditional VerilogHDL implementation or

using SystemVerilog with VMM.

Introduction to Avalon Verification IP Suite

Send Feedback

Altera Corporation

Page 15

Testbench

Test Program

Traditional Verilog Implementation

OR

Avalon-MM

read or

write

SystemVerilog with VM

configuration

SRC

Avalon-MM

read or

write

S

Avalon-MM

Slave BFM

S

Avalon-MM

Monitor

Avalon-MM

Master BFM

Avalon-MM

DUT

M

SS

Avalon-MM

Monitor

Snk

Avalon-ST

Sink BFM

Snk

Avalon-ST

Monitor

Avalon-ST

Source BFM

Avalon-ST

DUT

Src

Src

Snk

Snk

Avalon-ST

Monitor

M

M

M

SrcSrc

transactor

generator

object

instance

generator

object

instance

generator

object

instance

generator

object

instance

initial()

initial() always() always() function() function() task()

1-4

Application Example of BFMs

Figure 1-2: Avalon Verification IP Suite Testbench for Avalon-MM and Avalon-ST Interfaces

To verify a component with Avalon-MM interfaces, insert a monitor between the master BFM and the slave

interface. To verify a component with Avalon-ST interfaces, insert a monitor between the source BFM and

sink interface. You can insert a second monitor between the slave or sink BFM and the master or source

interface of the DUT. You can inserted monitors anywhere in the system to provide protocol assertion

checking and functional coverage reporting.

The test program drives the stimulus to the DUTs. The test program also determines whether the DUT

behavior is correct, by analyzing the responses. The BFMs translate the test program stimuli. The BFMs

create the signalling for the Avalon-MM and Avalon-ST protocols. The monitors verify Avalon protocol

compliance and provide test coverage reports.

Altera Corporation

Introduction to Avalon Verification IP Suite

Send Feedback

Page 16

Clock Source BFM

www.altera.com

101 Innovation Drive, San Jose, CA 95134

2

Subscribe

Send Feedback

The Avalon Verification IP Suite includes a Clock Source BFM that you can use to generate a clock signal

for your testbench.

The Clock Source BFM is only supported in Qsys.Note:

Parameters

Table 2-1: Clock Source BFM Parameter Settings

Clock Source API

clock_start()

clock_start()Prototype:

DescriptionLegal ValuesDefault ValueOption

Specifies the clock rate in MHz.N/A10Clock rate

Arguments:

Verilog HDL: None

VHDL: N.A.

voidReturns:

Turns on the clock.Description:

Verilog HDLLanguage Support:

©

2014 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words

and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other

words and logos identified as trademarks or service marks are the property of their respective holders as described at

www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with

Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes

no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly

agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published

information and before placing orders for products or services.

ISO

9001:2008

Registered

Page 17

2-2

Clock_stop()

Clock_stop()

clock_stop()Prototype:

Arguments:

get_run_state()

Arguments:

get_version()

Verilog HDL: None

VHDL: N.A.

voidReturns:

Turns off the clock.Description:

Verilog HDLLanguage support:

get_run_state()Prototype:

Verilog HDL: None

VHDL: N.A.

bitReturns:

Returns the state of the clock source; 1=running, 0=stop.Description:

Verilog HDLLanguage support:

Arguments:

Description:

string get_version()Prototype:

Verilog HDL: None

VHDL: N.A.

stringReturns:

Returns BFM version as a string of three integers separated by periods. For example,

version 10.1 sp1 is encoded as "10.1.1".

Verilog HDLLanguage support:

Altera Corporation

Clock Source BFM

Send Feedback

Page 18

Reset Source BFM

www.altera.com

101 Innovation Drive, San Jose, CA 95134

3

Subscribe

Send Feedback

The Avalon Verification IP Suite includes a Reset Source BFM that you can use to generate a reset signal in

your testbench.

Parameters

Table 3-1: Reset Source BFM Parameter Settings

On/OffOnAssert reset high

reset

Reset Source API

reset_assert

DescriptionLegal ValuesDefault ValueOption

Specifies the polarity of the reset signal. Turn on

this option to set the reset signal active high.

N/A0Cycles of initial

Specifies the number of cycles that the reset signal

is asserted at the initial stage of the simulation.

reset_assertPrototype:

Arguments:

Verilog HDL: None

VHDL: N.A.

void.Returns:

Asserts the reset signal.Description:

Verilog HDLLanguage support:

©

2014 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words

and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other

words and logos identified as trademarks or service marks are the property of their respective holders as described at

www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with

Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes

no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly

agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published

information and before placing orders for products or services.

ISO

9001:2008

Registered

Page 19

3-2

reset_deassert

reset_deassert

reset_deassertPrototype:

Arguments:

get_version()

Arguments:

Description:

Verilog HDL: None

VHDL: N.A.

void.Returns:

Deasserts the reset signal.Description:

Verilog HDLLanguage support:

string get_version()Prototype:

Verilog HDL: None

VHDL: N.A.

String.Returns:

Returns BFM version as a string of three integers separated by periods. For example,

version 10.1 sp1 is encoded as "10.1.1".

Verilog HDLLanguage support:

Altera Corporation

Reset Source BFM

Send Feedback

Page 20

Avalon Interrupt Source and Interrupt Sink BFMs

www.altera.com

101 Innovation Drive, San Jose, CA 95134

4

Subscribe

Send Feedback

The Avalon Verification IP Suite includes Avalon Interrupt Source and Avalon Interrupt Sink BFMs for you

to generate interrupt signals in your testbench.

Parameters

Table 4-1: Clock Source BFM Parameter Settings

Interrupt Source

On/OffOnAssert IRQ high

On/OffOffAsynchronous

IRQ

DescriptionLegal ValuesDefault ValueOption

Specifies the polarity of the interrupt source signal.

Turn on this option to change the name of the

interrupt source signal port from irq to irq_n.

Specifies the width of the interrupt source signal.1–321IRQ width

Specifies whether the interrupt signal is asserted

or deasserted immediately after an API call or one

clock cycle after an API call. Turn on this option

to allow changes to the interrupt signal

immediately after an API call. Turn off this option

to allow changes to the interrupt signal on the

next clock edge.

©

2014 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words

and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other

words and logos identified as trademarks or service marks are the property of their respective holders as described at

www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with

Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes

no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly

agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published

information and before placing orders for products or services.

1–10230VHDL BFM ID

Interrupt Sink

On/OffOnAssert IRQ high

For VHDL BFMs only. Use this option to assign

a unique number to each BFM in the testbench

design.

Specifies the polarity of the interrupt sink signal.

Turn on this option to change the name of the

interrupt source signal port from irq to irq_n.

Specifies the width of the interrupt source signal.1–321IRQ width

ISO

9001:2008

Registered

Page 21

4-2

Interrupt Source and Sink API

Interrupt Source and Sink API

clear_irq()

int clear_irq()Prototype:

Arguments:

Description:

get_irq()

get_irq()

Arguments:

Description:

Verilog HDL: interrupt_bit

VHDL: interrupt_bit, bfm_id, req_if(bfm_id)

voidReturns:

Asserts the interrupt signal and sets the interrupt signal to 0,

regardless of the value you set for Assert IRQ high in the parameter

editor.

Verilog HDL, VHDLLanguage Support:

get_irq()Prototype:

Verilog HDL: None

VHDL: irq, bfm_id, req_if(bfm_id)

logic[AV_IRQ_W-1:0]voidReturns:

Returns the current value of the register holding the latched

interrupt signal.

get_version()

get_version()

Arguments:

Description:

Altera Corporation

Verilog HDL, VHDLLanguage Support:

string get_version()Prototype:

Verilog HDL: None

VHDL: N.A.

StringReturns:

Returns BFM version as a string of three integers separated by

periods. For example, version 13.1 sp1 is encoded as "13.1.1".

Verilog HDLLanguage Support:

Avalon Interrupt Source and Interrupt Sink BFMs

Send Feedback

Page 22

set_irq()

set_irq()

set_irq()

set_irq()Prototype:

4-3

Arguments:

Description:

Verilog HDL: int interrupt_bit

VHDL: int interrupt_bit, bfm_id, req_if(bfm_id)

voidReturns:

Asserts the interrupt signal and sets the interrupt signal to 1,

regardless of the value you set for Assert IRQ high in the parameter

editor.

Verilog HDL, VHDLLanguage Support:

Avalon Interrupt Source and Interrupt Sink BFMs

Send Feedback

Altera Corporation

Page 23

Avalon-MM Master BFM

Avalon-MM

Master BFM

Avalon-MM

Slave Component

DUT

Testbench

Avalon-MM

Test Program

HDL HDL

www.altera.com

101 Innovation Drive, San Jose, CA 95134

5

Subscribe

Send Feedback

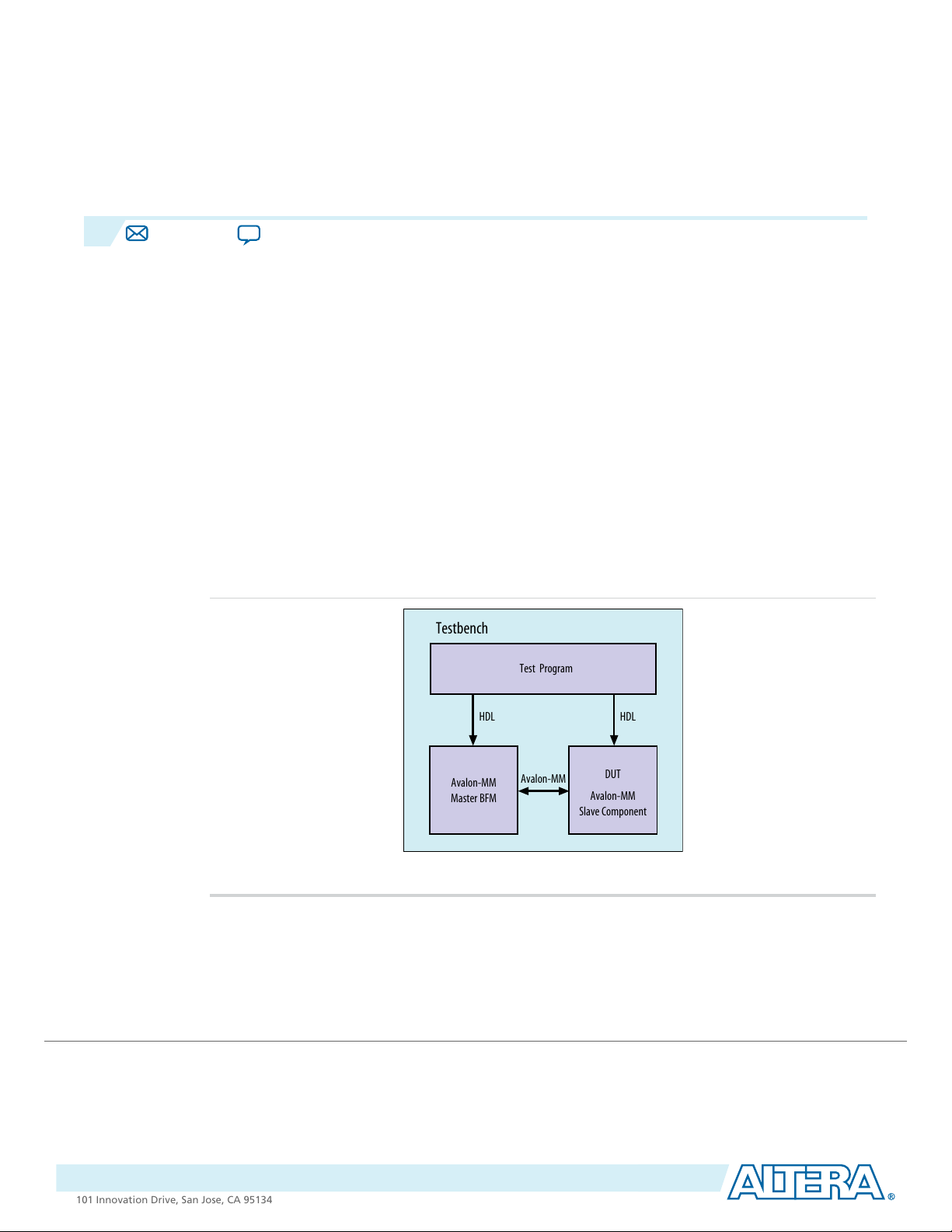

The Avalon-MM Master BFM implements the Avalon-MM interface protocol, including: read, write, burst

read, and burst write. The figure below shows the top-level modules for a testbench using the Avalon-MM

BFM to verify an Avalon-MM slave component. The typical testbench includes the folowing components:

• The Avalon-MM Master BFM

• A test program

• The DUT that includes an Avalon-MM slave interface

Using the Avalon-MM BFM created by Altera, third-party, has the following advantage. It highlights any

misinterpretation of the Avalon-MM protocol that might be missed in a testbench designed by a single

engineer.

Note:

The BFMs allow illegal transactions so that you can test the error-handling functionality of your

DUT. Consequently, the BFMs cannot be relied upon to guarantee protocol compliance. The Avalon

Monitor components verify protocol compliance.

Figure 5-1: Top-Level Module to Verify an Avalon-MM Slave Device

Related Information

Avalon Interface Specifications

©

2014 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words

and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other

words and logos identified as trademarks or service marks are the property of their respective holders as described at

www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with

Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes

no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly

agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published

information and before placing orders for products or services.

ISO

9001:2008

Registered

Page 24

writedata[31:0]

D1 D3

CLK

read

transaction1 transaction2

trans3

trans4

write

T

init

T

init

S

ci_1

T

idle

S

ci_2

S

ci_3

S

ci_4

transactionid

waitrequest

byteenable[3:0]

T

wr

T

wt_1

T

wt_2

T

ID_4

writeresponse

writeid

ID_1

ID_3

readdatavalid

readdata

D2 D4

T

rl_1

T

rl_2

S

rc_4,

S

rc_2

S

atc

readresponse

readid

ID_2

ID_4

writeresponsevalid

T

wrl_1

S

rc_1

T

ID_1

T

ID_2

T

ID_3

S

rc_3

D2 D4

5-2

Timing

Timing

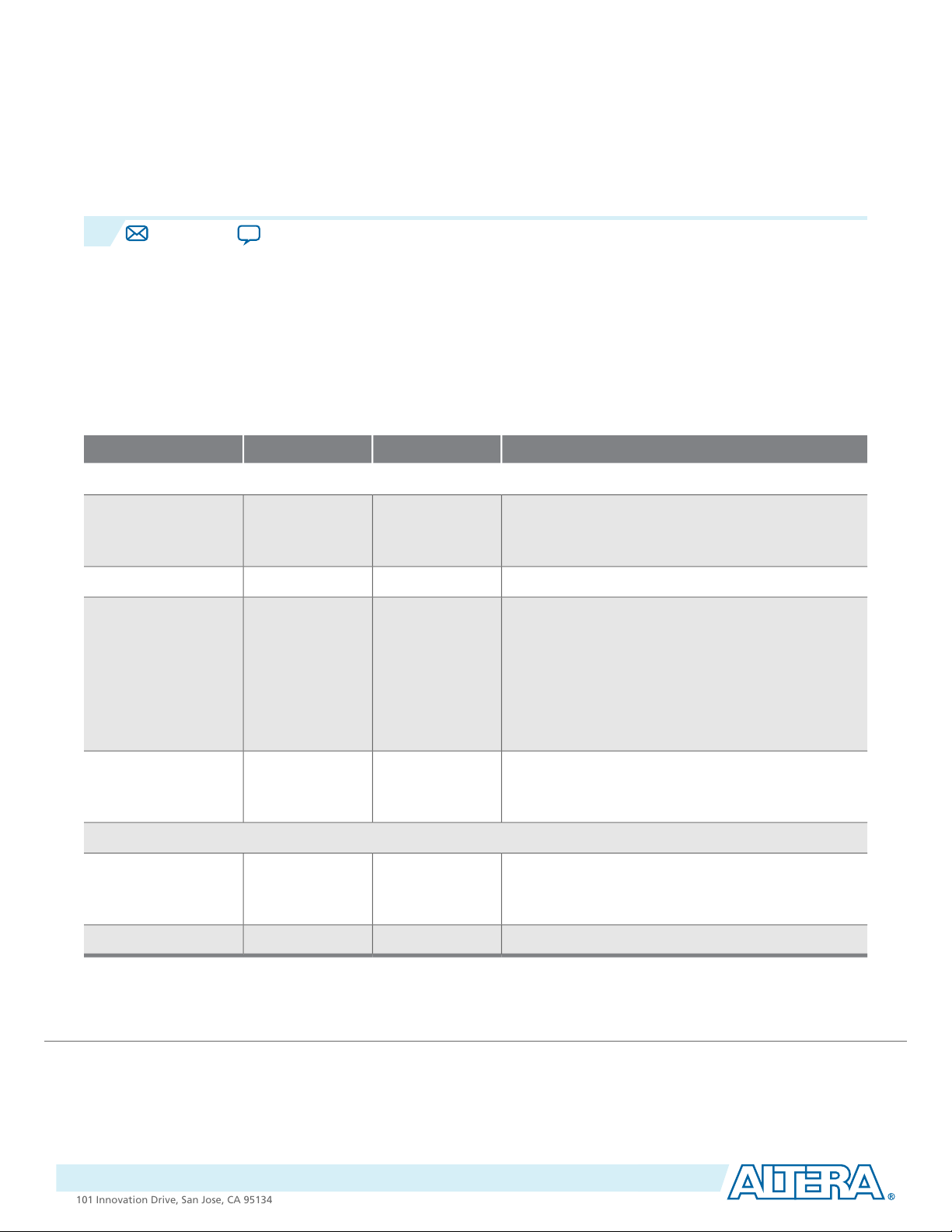

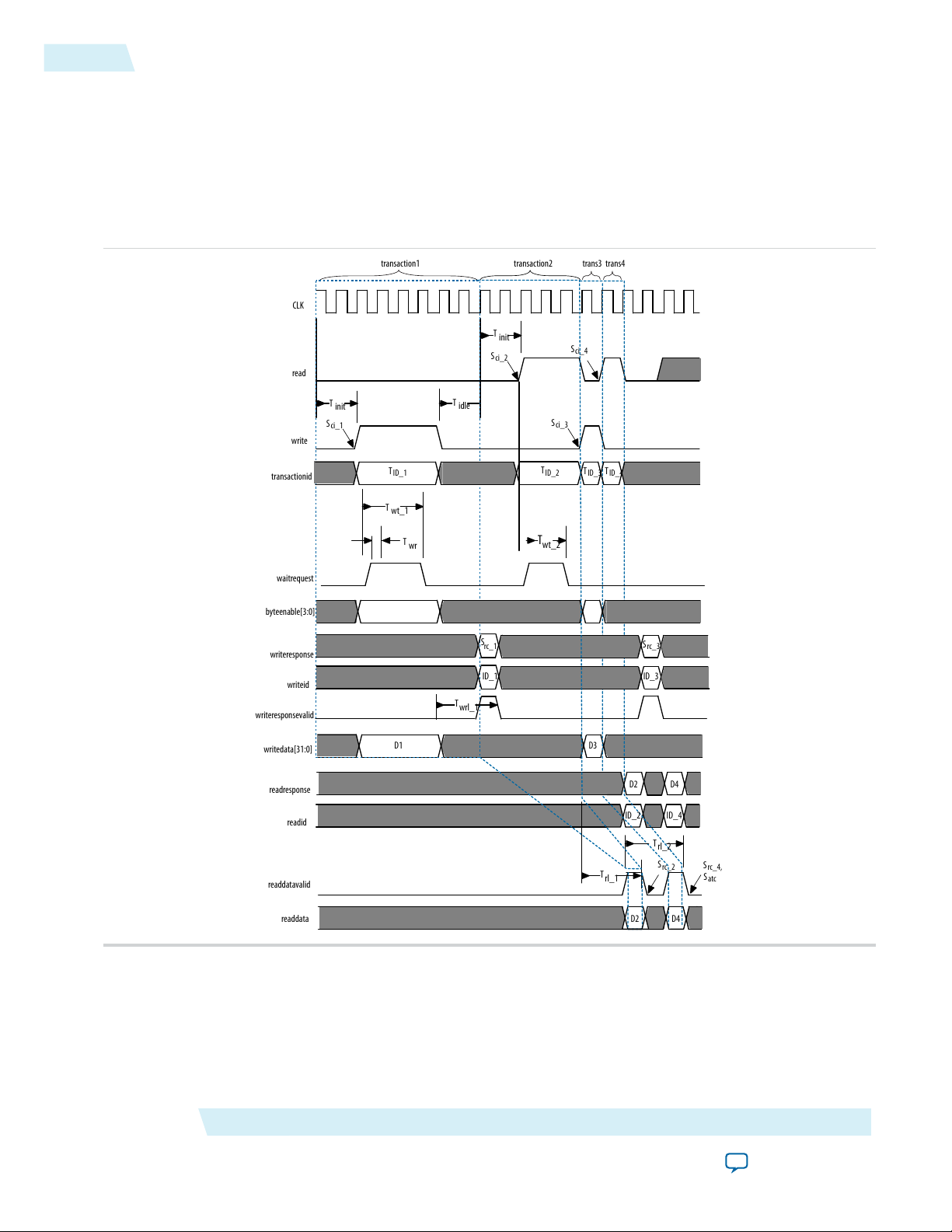

The following timing diagram illustrates the sequence of events for an Avalon-MM Master BFM. The Master

BFM drives interleaved writes and reads when the readdatavalid signal is present. This diagram serves as

a reference for the following discussion of API and events.

Figure 5-2: Avalon-MM Master Driving Interleaved Write and Read Transactions

Altera Corporation

Avalon-MM Master BFM

Send Feedback

Page 25

Table 5-1: Key to the Annotations

The following table lists the annotations used in the figure.

Timing

5-3

DescriptionSymbol

T

T

T

T

T

init

wt_1

wr

idle

rl_1

rl_2

wrl_1

The initial command latency, which is two cycles for transactions 1 and 2. This time is set by

the API command set_command_init_latency.

The response wait time, which is three cycles. This time is determined by the number of cycles

that the waitrequest signal is asserted by the slave.The program gets this value using the get_

response_wait_time command.

waitrequest is always sampled #1 after the falling edge of clk.T

The idle time after each transaction. This time is set by the command set_command_idle.T

The response latency for the first read, which is 3 cycles. This is the time between the read

command acceptance and the read response provided by the slave. The program gets this time

using the get_response_latency command.

If an Avalon-MM slave component defines the readLatency interface property, the

readdatavalid signal is not used. The readdatavalid signal is not necessary because the slave

component has a fixed read latency.

For more information refer to the Avalon Interface Specifications.

The response latency for the second read, which is 3 cycles. The program gets this time using

the get_response_latency command.

The write response latency for the first write, which is 3 cycles. This is the time between when

the write command acceptance and the write response is provided by the slave. The program

gets this time using the get_response_latency command.

S

ci_1–Sci_4

rc_1,Src_3

rc_2,Src_4

atc

ID_1–TID_

4

Signals when write or read commands are presented on the interface. The event name is signal_

command_issued.

Signals write responses. The event name is signal_response_complete.S

Signals read responses. The event name is signal_response_complete.S

Signals the end of the test. The event name is signal_all_transactions_completeS

Reference number to identify each read or write transaction.T

Reference number to identify each write transaction.ID_1, ID_3

Reference number to identify each read transaction.ID_2, ID_4

Avalon-MM Master BFM

Send Feedback

Altera Corporation

Page 26

CLK

read

write

waitrequest

byteenable[3:0]

writedata[31:0]

readdata

D1

D2

T

init

T

init

S

ci_1

T

wt_1

T

wt_2

S

ci_2

S

rc_1,

S

atc

T

wr

transaction5

transaction6

T

idle

5-4

Timing

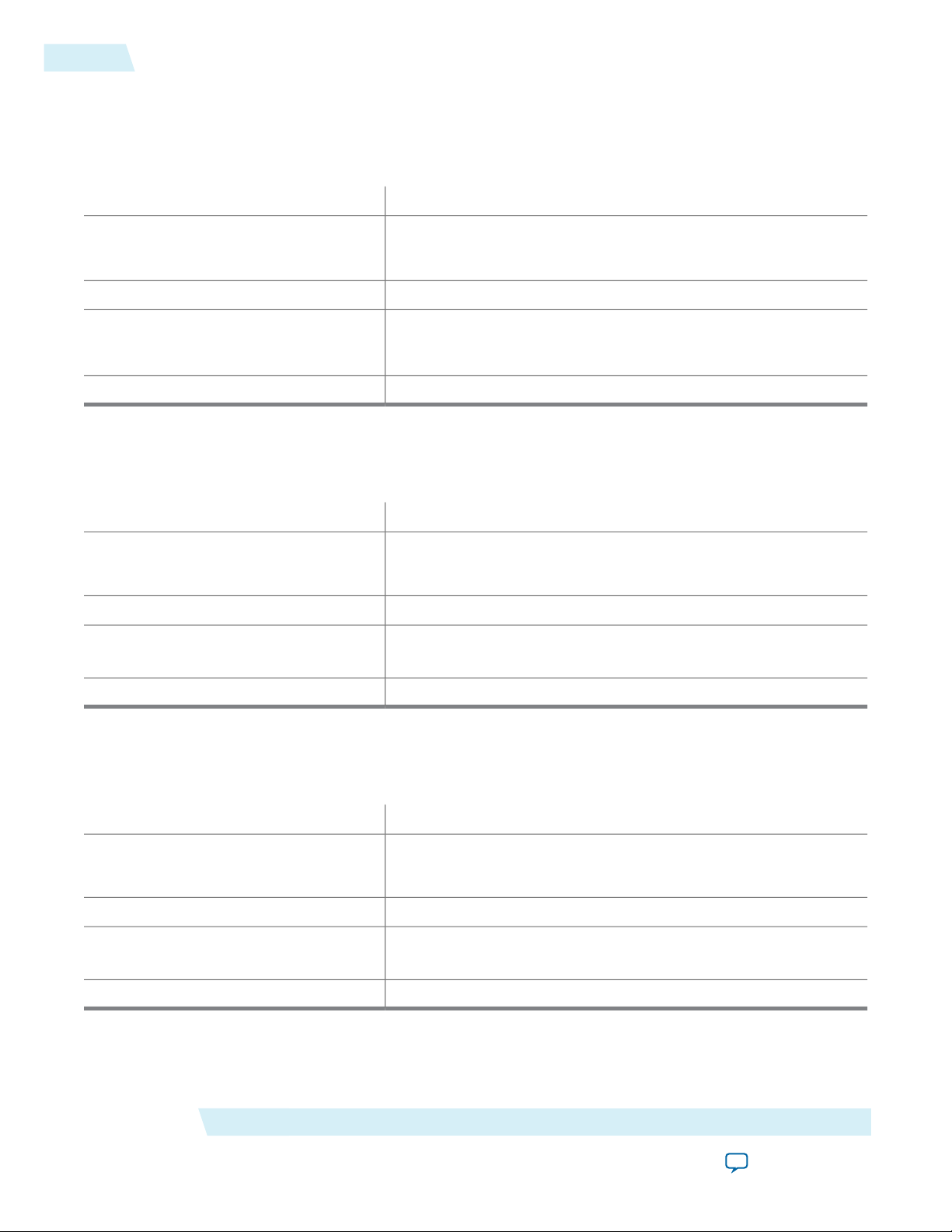

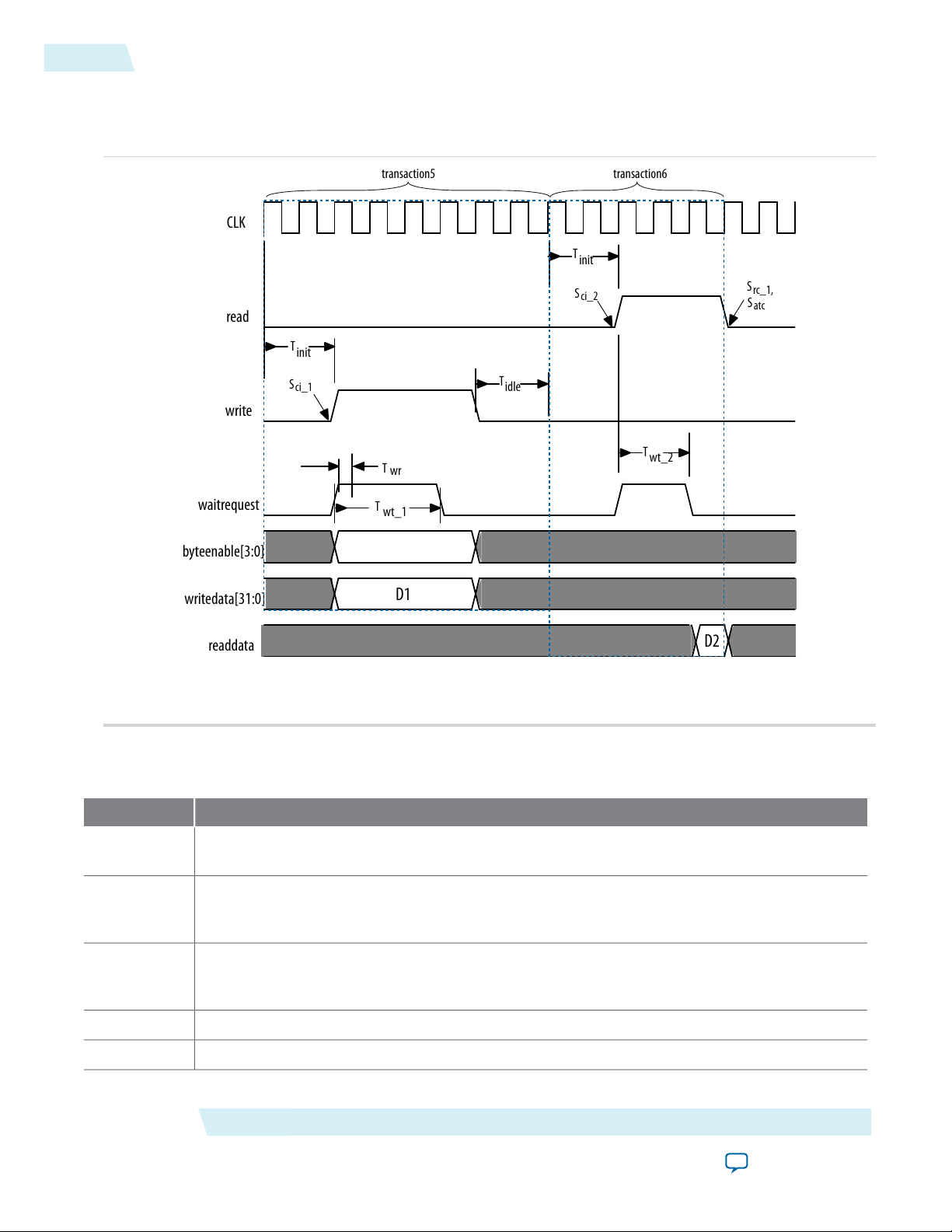

Figure 5-3: Avalon-MM Master Driving Write and Read Transactions with No readdatavalid Signal

The timing in the following figure shows the sequence of events for an Avalon-MM Master BFM. The

Avalon-MM Master BFM drives a write followed by a read when the readdatavalid signal is not present.

Table 5-2: Key to the Annotations

The following table lists the annotations used in this figure.

T

init

The initial command latency, which is 2 cycles for transactions 1 and 2. This time is set by the

API command set_command_init_latency.

T

wt_1

T

wt_2

The response wait time, which is 3 cycles. This time is determined by the number of cycles that

the waitrequest signal is asserted by the slave.The program gets this value using the get_

response_wait_time command.

The response wait time for the first read, which is 2 cycles. This time is determined by the

number of cycles that the waitrequest signal is asserted by the slave.The program gets this

value using the get_response_wait_time command.

waitrequest is always sampled #1 after the falling edge of clk.T

The idle time after a transaction. This time is set by the command set_command_idle.T

wr

idle

Altera Corporation

DescriptionSymbol

Avalon-MM Master BFM

Send Feedback

Page 27

Block Diagram

DescriptionSymbol

5-5

S

ci_1–Sci_2

rc_1

atc

Signals when write and read commands are presented on the interface. The event name is

signal_command_issued.

Signals the first read response. The event name is signal_response_complete.S

Signals the end of the test. The event name is signal_all_transactions_complete.S

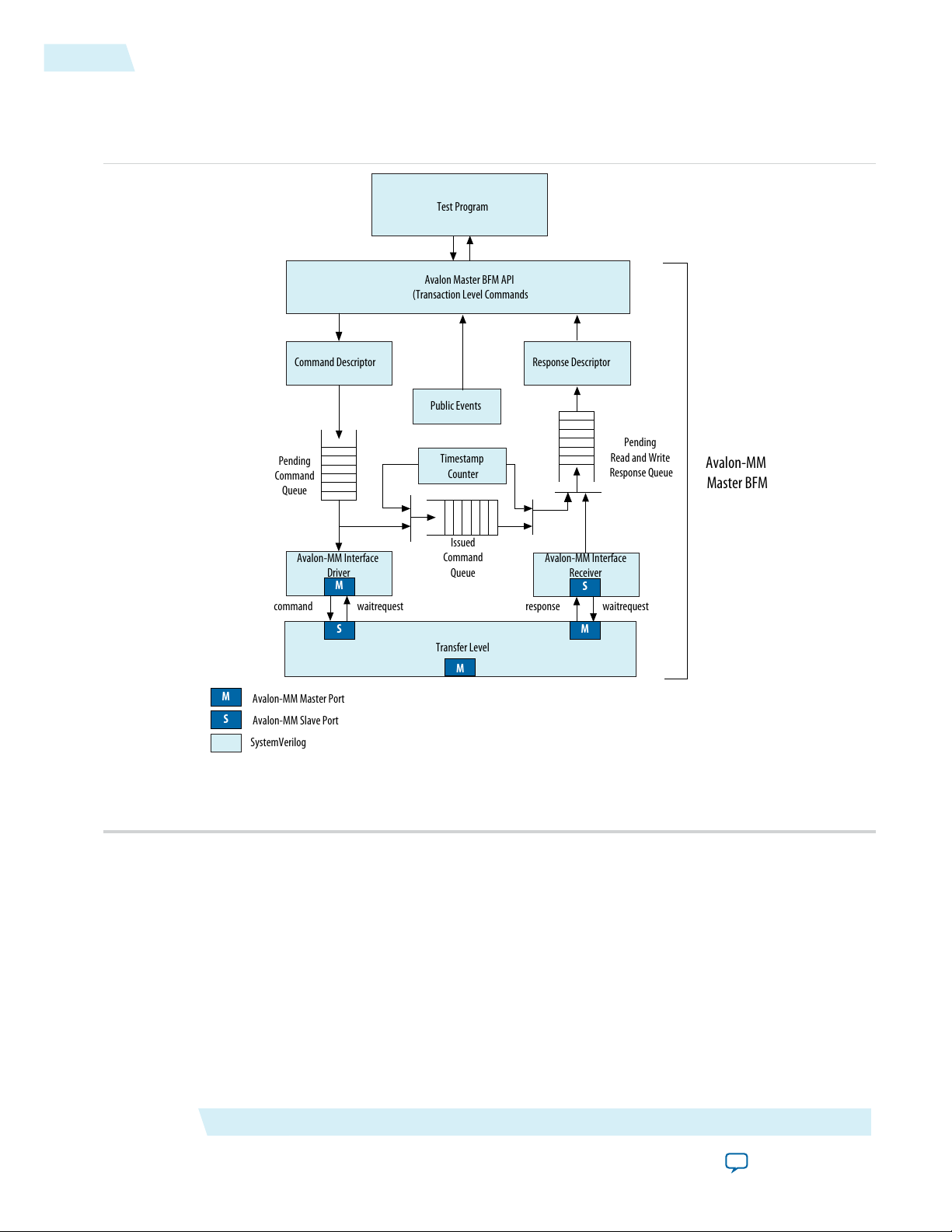

Block Diagram

The following figure provides a block diagram of the Avalon-MM Master BFM. As this figure illustrates,

the BFM includes the following major blocks:

• Avalon-MM Master API—Provides methods to create Avalon-MM transactions and query the state of

all queues.

• Command Descriptor—Accumulates the fields of an Avalon-MM command transaction using the

set_command API call. Inserts completed commands onto the pending command queue.

• Avalon-MM Interface Driver—Issues transfers to the system interconnect fabric and holds each transfer

until waitrequest is deasserted. For burst transfers, there is a separate transfer for each word of the

burst. The system interconnect fabric can assert waitrequest for each word of the burst, as necessary.

• Timestamp Counter—Records a timestamp with commands for use in timing calculations. The driver

and monitor both use the timestamp counter for timing calculations.

• Avalon-MM Interface Monitor—Monitors the system interconnect fabric and records responses for read

transfers in the response queue.

• Response Descriptor—Collects information about completed transactions using the

get_response_<rolename> API calls. The testbench uses this information for further analysis.

Avalon-MM Master BFM

Send Feedback

Altera Corporation

Page 28

Command Descriptor

Timestamp

Counter

Avalon Master BFM API

(Transaction Level Commands

Transfer Level

Avalon-MM Interface

Receiver

Response Descriptor

Pending

Command

Queue

Issued

Command

Queue

Pending

Read and Write

Response Queue

Avalon-MM Interface

Driver

command waitrequest response waitrequest

Test Program

M

S

M

M

S

S

M

Avalon-MM Master Port

Avalon-MM Slave Port

SystemVerilog

Avalon-MM

Master BFM

Public Events

5-6

Parameters

• Public Events—Provides status response that arrives together with the data. The public event signals

indicate the status of the Master’s request, such as successful completion, timeout, or error.

Figure 5-4: Block Diagram of the Avalon-MM Master BFM

Parameters

The Avalon-MM BFM supports the full range of signals defined for the Avalon-MM master interface. You

can customize the Avalon-MM master interface using the parameters described in the following table.

Altera Corporation

Avalon-MM Master BFM

Send Feedback

Page 29

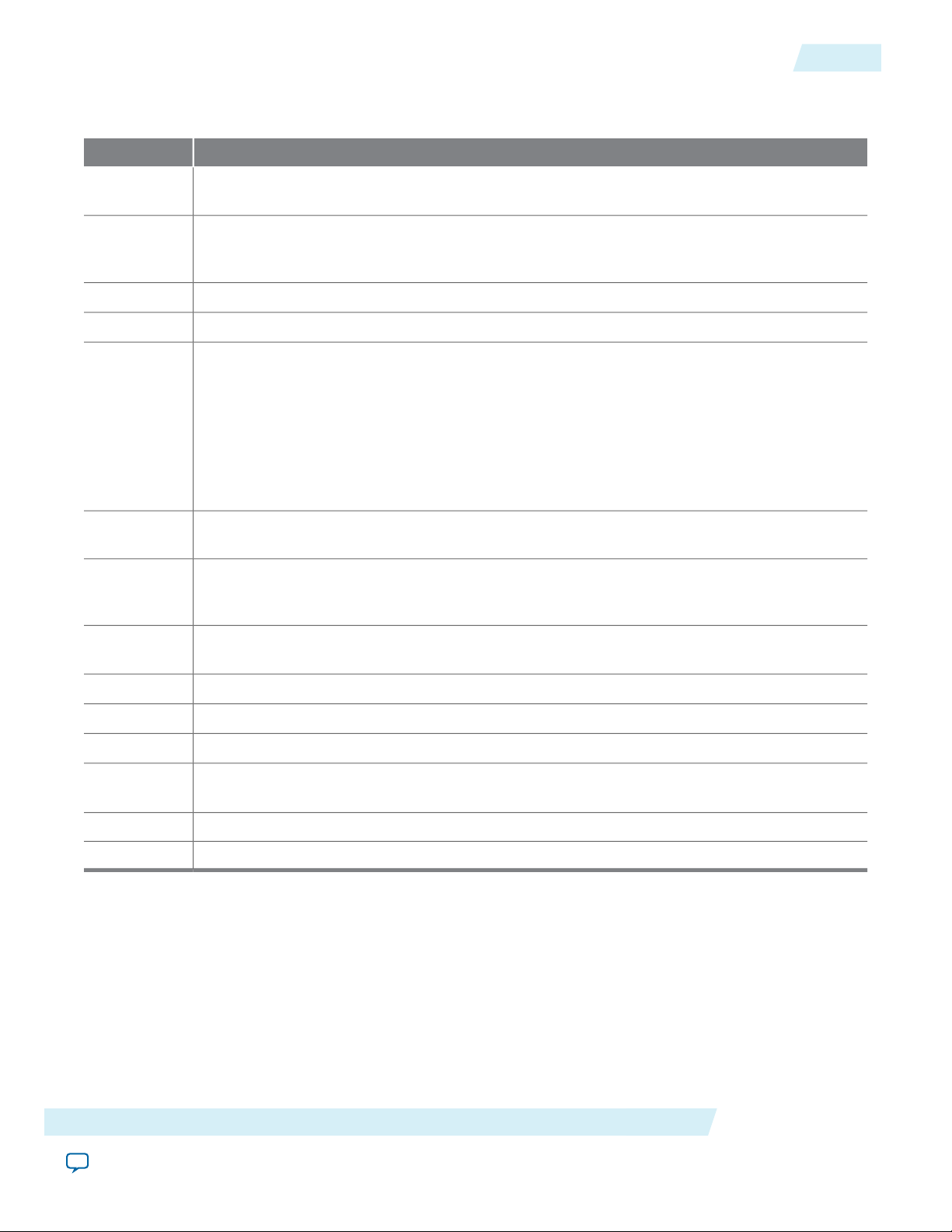

Table 5-3: Parameters for the Avalon-MM Master BFM

Parameters

5-7

signal

Parameter

Value

Port Widths

N/A8Symbol width

Port Enables

DescriptionLegal ValuesDefault

Address width in bits.N/A32Address width

Data symbol width in bits. The symbol width should be

8 for byte-oriented interfaces.

Read response signal width in bits.N/A8Read Response width

Write response signal width in bits.N/A8Write Response width

Parameters

Number of symbols per word.N/A4Number of symbols

The width of the burst count in bits.N/A3Burstcount width

When On, the interface includes a read pin.On/OffOnUse the read signal

When On, the interface includes a write pin.On/OffOnUse the write signal

When On, the interface includes address pins.On/OffOnUse the address signal

When On, the interface includes byteenable pins.On/OffOnUse the byteenable

signal

signal

signal

transfer signal

signal

signal

signal

signal

When On, the interface includes burstcount pins.On/OffOnUse the burstcount