Page 1

Avalon Tri-State Conduit Components User Guide

Avalon Tri-State Conduit Components

User Guide

101 Innovation Drive

San Jose, CA 95134

www.altera.com

UG-01100-1.0

Document last updated for Altera Complete Design Suite version:

Document publication date:

11.0

May 2011

Subscribe

Page 2

© 2011 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX are Reg. U.S. Pat.

& Tm. Off. and/or trademarks of Altera Corporation in the U.S. and other countries. All other trademarks and service marks are the property of their respective

holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance

with Altera’s standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or

liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera

customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or

services.

Avalon Tri-State Conduit Components User Guide May 2011 Altera Corporation

Page 3

Contents

Chapter 1. Avalon Tri-State Conduit Components

Chapter 2. Generic Tri-State Controller

Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–2

Example Read and Write Using Setup, Hold and Wait Times . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–5

Chapter 3. Tri-State Conduit Pin Sharer

Signal Naming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–1

Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–2

Signal Behavior During Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–2

Arbitration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–3

Hierarchical Pin Sharing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–4

Additional Information

Document Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Info–1

How to Contact Altera . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Info–1

Typographic Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Info–1

May 2011 Altera Corporation Avalon Tri-State Conduit Components User Guide

Preliminary

Page 4

iv Contents

Avalon Tri-State Conduit Components User Guide May 2011 Altera Corporation

Preliminary

Page 5

1. Avalon Tri-State Conduit Components

Altera FPGA

TCM

Tristate Conduit

Pin Sharer

addr_out[20:0]

data_outen

data_out[31:0]

data_in[31:0]

read_out

write_out

request

grant

grant

request

addr_out[22:0]

data_outen

data_out[15:0]

data_in[15:0]

read_out

write_out

TCS

Tristate Conduit

Bridge

S

Generic Tristate

Controller

Customized

for 2 MByte

x32 SSRAM

CS

A[20:0]

D_EN

D[31:0]

DI[31:0]

Rd

Wr

Request

Grant

TCM

S

Grant

Req

A[22:0]

D_EN

D[15:0]

DI[15:0]

Rd

Wr

TCM

chipselect_out

chipselect_out

irq_in

Generic Tristate

Controller

Customized

for 8 MByte

x16 Flash

addr_out<n>

data_out<n>

data_in<n>

data_outen<n>

chipselect_out

request

grant

irq_in

chipselect_out

write_out

read_out

clock

Note (1)

Avalon-MM

Master

TCS

TCS

CS

IRQ

Arb

Avalon-MM Slave

S

TCM

Tristate Conduit Master

Tristate Conduit Slave

TCS

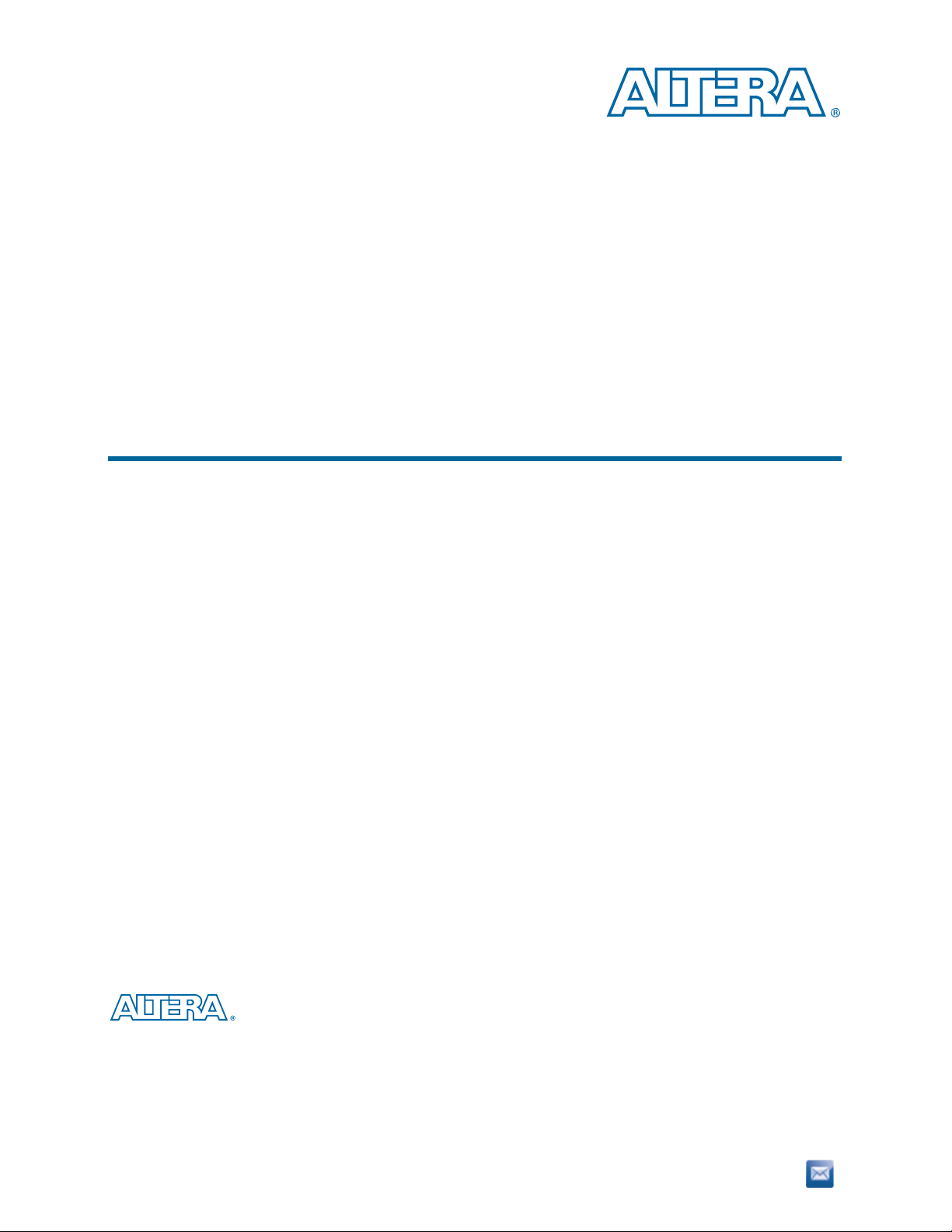

The Avalon® Tri-State Conduit components available in the Qsys component library

allow you to create on-chip controllers that connect to off-chip devices: The Generic

Tri-State Conduit Controller includes parameters that you can specify to control the

connected off-chip device, frequently a memory device. The Tri-State Conduit Pin

Sharer arbitrates between multiple connected tri-state controllers. It drives signals

from the selected controller to the Tri-State Conduit Bridge. The Tri-State Conduit

Bridge converts an on-chip encoding of tri-state signals into true bidirectional signals

on the PCB. Figure 1–1 illustrates the use of these three Qsys components in an

®

Altera

Figure 1–1. Qsys System Using the Generic Tri-State Controller, Tri-State Conduit Pin Sharer and Bridge

FPGA.

Note to Figure 1–1:

(1) Refer to Figure 3–3 on page 3–2 for details of the logic that controls

May 2011 Altera Corporation Avalon Tri-State Conduit Components User Guide

read_out

and

write_out

.

Preliminary

Page 6

1–2 Chapter 1: Avalon Tri-State Conduit Components

In Figure 1–1 two instances of the Generic Tri-State Controller are customized to

control off-chip SSRAM and flash memories. The Avalon Tri-state Conduit

(Avalon-TC) master interfaces of these components connect to separate Avalon-TC

slave interfaces of the Tri-State Conduit Pin Sharer. The Tri-State Conduit Pin Sharer

arbitrates between the connected masters and drives signals from the selected master

on its Avalon-TC interface which connects to the Avalon-TC slave interface of the

Tri-State Conduit Bridge. Finally, the Tri-State Conduit Bridge converts the on-chip

representation of the signals to bidirectional signals. It drives the bidirectional signals

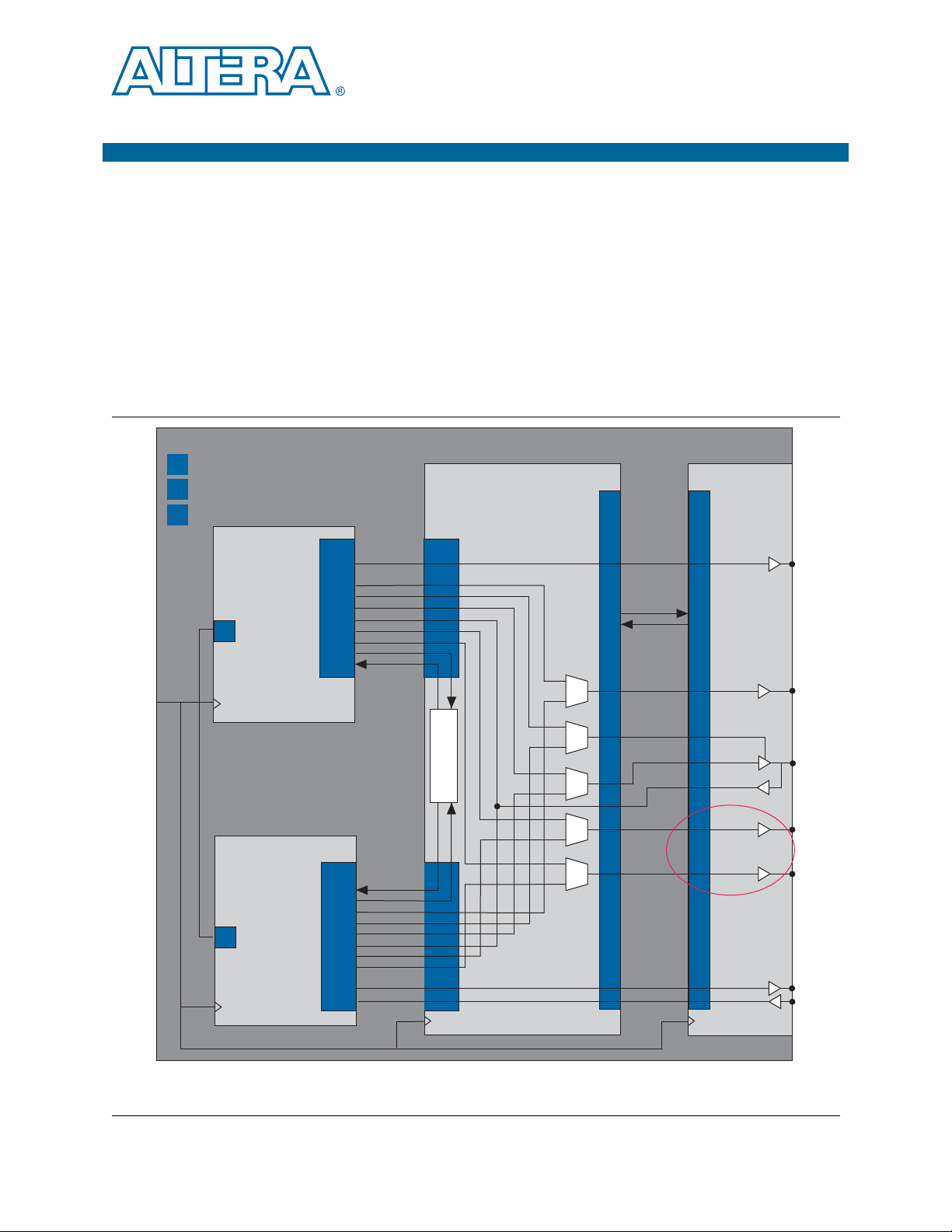

over its Avalon Conduit Interface to SSRAM and flash devices on the PCB. Figure 1–2

shows this system in Qsys with the addition of a Nios II processor that drives the

Avalon-MM slave interfaces of the customized controllers.

Figure 1–2. Qsys Tri-State Conduit System

This user guide explains how to use the Generic Tri-State Controller and Tri-State

Conduit Pin Sharer to create systems that interface to off-chip devices. It does not

include a separate chapter for the Tri-State Conduit Bridge because the sole purpose

of this device is to convert between the on-chip and off-chip representation of

connected signals. After reading this user guide, you should be able to define

controllers that interface with off-chip devices and identify signals that can be shared

between interfaces to reduce the total pin count of your FPGA. This document

includes the following chapters:

■ Generic Tri-State Controller

■ Tri-State Conduit Pin Sharer

Avalon Tri-State Conduit Components User Guide May 2011 Altera Corporation

Preliminary

Page 7

2. Generic Tri-State Controller

avalon_mm_address[<n>-1:0]

avalon_mm_byteenable[<n>-1:0]

avalon_mm_writedata[<n>-1:0]

avalon_mm_readdata[<n>-1:0]

readdatavalid

lock

avalon_mm_write

avalon_mm_read

avalon_mm_waitrequest

avalon_mm_clk

avalon_mm_clk_reset

Generic Tri-State Controller - Available Signals

request

grant

data[<n>-1:0]_in

data[<n>-1:0]_out

data_outen

read_out

write_out

begintransfer_out

byteenable[<n>-1:0]_out

chipselect_out

lock_out

address[<n>-1:0]_out

waitrequest_in

writebyteenable[<n>-1:0]_out

outputenable_out

resetrequest_in

irq_in_in

reset_out

Avalon-MM

Slave

Avalon-TC

to

Tri-state Conduit

Pin Sharer

Avalon Clock

Avalon Reset

Required

Optional

The Generic Tri-State Controller provides a template for a controller that you can

parameterize to reflect the behavior of an off-chip device. This component includes

the following four interfaces:

■ Avalon Memory-Mapped (Avalon-MM) slave—This is the interface that connects

to an Avalon-MM master, typically an embedded processor which sends read and

write requests to the Generic Tri-State Controller.

■ Avalon-TC master—This is an interface that connects to the Tri-State Conduit Pin

Sharer or Tri-State Conduit Bridge if pin multiplexing is not required. You easily

parameterize the core to utilize enable any subset of the available signals as

required by your off-chip device.

■ Avalon Clock sink—This is a clock sink interface. All Generic Tri-State Controllers

connected to a single Tri-State Conduit Pin Sharer must operate in the same clock

domain.

■ Avalon Reset sink—This a reset sink interface. All Generic Tri-State Controllers

connected to a single Tri-State Conduit Pin Sharer must operate in the same reset

domain.

Figure 2–1 illustrates the Generic Tri-State Controller interfaces and signals. This

figure shows a typical set of signals for the Avalon-MM slave interface. It shows all of

the possible signals for the Avalon-TC interface. Only the

request

and

grant

signals

of the Avalon-TC interface are required.

Figure 2–1. Available Signals for the Generic Tri-state Controller

May 2011 Altera Corporation Avalon Tri-State Conduit Components User Guide

Preliminary

Page 8

2–2 Chapter 2: Generic Tri-State Controller

Parameters

Parameters

The Generic Tri-State Controller provides preset configurations for many commonly

used external devices. If you select one of the preset configurations, all of the

parameters are automatically assigned the correct values. Many preset configurations

are available, including presets for all of the following devices:

■ Legacy AMD 29LV065D Flash

■ AMD 29LV128M Flash with Legacy SDK support

■ Intel 128P30 Flash

■ Intel 256P30 Flash

■ SST39VF20090 Flash

■ Flash Memory Interface (CFI)

■ ISSI IS61LPS25636A-200TQL1 SSRAM

■ Cypress CY7C1380C SSRAM

■ IDT71V416 SRAM

■ LAN91C111 Interface

■ C8900 Interface (Ethernet)

You can use the parameter editor to specify the required settings for other external

devices. The appropriate values for these parameters are typically listed in the

vendor’s data sheet for the device.

Tab le 2– 1 describes the parameters available on the Signal Selection tab of the

parameter editor for the Generic Tri-State Controller.

Table 2–1. Signal Selection Parameters

Parameter Value Description

Address Width

Data Width

Byteenable Width

Bytes per word

readdata On/Off

writedata On/Off

read On/Off Enables or disables the

write On/Off Enables or disables the

begintransfer On/Off

1–30

8,16,32,64,128,

256,512,1024

1,2,4,8,16,

32,64,128

1-128

Specifies the width of the

Specifies the width of the

Specifies the width of the

address

data

signal.

byteenable

Specifies the number of bytes per word.

Enables or disables the

readdata

signal which is driven from the external device

to the Generic Tri-State Controller in response to a read transfer.

Enables or disables the

writedata

Tri-state Controller to the external device during writes transfers.

read

signal. If present

write

signal. If present

Enables or disables the

begintransfer

first cycle of any transfer regardless of the value of the

signal.

signal.

signal which is driven from the Generic

readdata

writedata

is required.

is required.

signal, which is asserted during the

waitrequest

signal.

Avalon Tri-State Conduit Components User Guide May 2011 Altera Corporation

Preliminary

Page 9

Chapter 2: Generic Tri-State Controller 2–3

Parameters

Table 2–1. Signal Selection Parameters

Parameter Value Description

Enables or disables the

byteenable

signal, which enables specific byte lanes

during transfers on ports with widths greater than 8 bits. Each bit in the

byteenable On/Off

byteenable

of

byteenable

byteenable

should be ignored by the external device. During reads, the

signal corresponds to a byte in

writedata

and

readdata

. Bit <n>

indicates whether byte <n> is being written to. During writes, the

signal specifies which bytes are being written to; other bytes

byteenable

signal

indicates which bytes the Generic Tri-State Controller is reading.

chipselect On/Off

Enables or disables the

with the

read

or write

Enables or disables the

chipselect

signal

lock

signal, which is always used in conjunction

.

signal, which ensures that once a master wins

arbitration, it maintains access to the slave for multiple transactions. It is

lock On/Off

asserted coincident with the first

read

or

write

of a locked sequence of

transactions, and is deasserted on the final transaction of a locked sequence of

transactions.

address On/Off

waitrequest On/Off

writebyteenable On/Off

resetrequest On/Off

irq On/Off

resetoutput On/Off

Enables or disables the

regardless of the word size of the external device.

Enables or disables the

device when it is unable to respond to a

Enables or disables the

logical

AND

of the

signal is used, the

Enables or disables the

off-chip device requesting a system reset.

Enables or disables the

the Generic Tri-state Controller.

Enables or disables the a

Controller to the external device which requests that the external device be reset.

address

waitrequest

writebyteenable

byteenable

write

and

resetrequest

irq

signal, which allows the external device to interrupt

resetoutput

signal, which represents a byte address

signal, which is asserted by the external

read

or

write

request.

signal, which is equivalent to the

and

write

byteenable

signals. When the

signals are not used.

writebyteenable

signal, which is an input from the

signal, from the Generic Tri-state

embeddedsw.configuration.

isNonVolatileStorage

embeddedsw.configuration.

isPrintableDevice

embeddedsw.configuration.

isMemoryDevice

embeddedsw.configuration.

isFlash

embeddedsw.configuration.

isEthernetMacDevice

Tab le 2– 2 lists parameters that you can use to define the signal timing of an external

memory. The appropriate values for these parameters are typically listed in the

vendor’s data sheet for the memory device.

Other Parameters

These are configuration names that you can use to identify your components to

downstream embedded software tools. A value of 1 identifies the parameter as

true

, a value of 0 identifies it as

false

.

For more information about these configuration names, refer to the Publishing

Component Information to Embedded Software chapter in the Nios II Software

Developer’s Handbook.

May 2011 Altera Corporation Avalon Tri-State Conduit Components User Guide

Preliminary

Page 10

2–4 Chapter 2: Generic Tri-State Controller

Parameters

Refer to “Example Read and Write Using Setup, Hold and Wait Times” on page 2–5

for an example that illustrates the use of the parameters defined in Tab le 2– 2.

Table 2–2. Signal Timing

Parameter Value Description

Read wait time 0–10000

Write wait time 0–10000

Setup wait time 0–10000

Data hold time 0–1000

cycles

cycles

cycles

cycles

Specifies additional time in units of timing units read to be asserted to indicate a

read transfer.

Specifies additional time in units of timing units for write to be asserted to

indicate a write transfer.

Specifies time in timing units between the assertion of

and

data

and the assertion of

read

or

write

.

Specifies time in timing units between the deassertion of

deassertion of

chipselect, address

, and

data

chipselect, address

write

and the

. (Only applies to write

,

transactions.)

Maximum

pending read

1–64

transactions

Turn around time >=0

Timing units

Read latency

cycles

nanoseconds

cycles

Chip select

through read

On/Off

latency

,

Specifies the maximum number of read transactions that can be in progress at

one time. This value controls the amount of buffering in the interconnect fabric.

Specifies the number of clock cycles required to change access from a read to a

write.

Specifies the units for setup wait time, data hold time, write wait time, and

read wait time. Use cycles for synchronous devices and nanoseconds for

asynchronous devices.

Specifies the read latency for fixed-latency slaves.

When on, chipselect remains asserted until all pending read transfers have

completed; otherwise, chipselect is asserted for one cycle.

1 Because the Tri-State Conduit Pin Bridge registers incoming and out-going signals

you must add two cycles latency to the read latency numbers in the vendor’s data

sheet. In calculating delays, the Generic Tri-State Controller chooses the larger of the

turn around time and (read latency + two cycles). Turn around time is measured

from the time that a command is accepted, not from the time that the previous read

returned data.

Tab le 2– 3 allows you to specify whether a signal is asserted high or low.

Table 2–3. Signal Polarities (Part 1 of 2)

Parameter Value Description

read On/Off When On,

arbiterlock On/Off When On,

write On/Off When On,

chipselect On/Off When On,

byteenable On/Off When On,

outputenable On/Off When On,

writebyteenable On/Off When On,

waitrequest On/Off When On,

begintransfer On/Off When On,

read

is asserted low and is called

arbiterlock

write

chipselect

byteenable

outputenable

writebyteenable

waitrequest

begintransfer

is asserted low and is called

is asserted low and is called

is asserted low and is called

is asserted low and is called

is asserted low and is called

is asserted low and is called

is asserted low and is called

is asserted low and is called

read_n

write_n

.

arbiterlock_n

.

chipselect_n

byteenable_n

outputenable_n

writebyteenable_n

waitrequest_n

begintransfer_n

.

.

.

.

.

.

.

Avalon Tri-State Conduit Components User Guide May 2011 Altera Corporation

Preliminary

Page 11

Chapter 2: Generic Tri-State Controller 2–5

Example Read and Write Using Setup, Hold and Wait Times

Table 2–3. Signal Polarities (Part 2 of 2)

Parameter Value Description

resetrequest On/Off When On,

irq On/Off When On,

reset output On/Off When On,

resetrequest

irq

is asserted low and is called

resetoutput

is asserted low and is called

is asserted low and is called

irq_n

resetrequest_n

.

resetoutput_n

.

.

Example Read and Write Using Setup, Hold and Wait Times

Figure 2–2 on page 2–6 illustrates the timing for a memory device that has

asynchronous read and write transfers, assuming a 50 MHz clock. Tab le 2– 4 lists the

parameter values set in the Generic Tri-State Controller to access this device.

Table 2–4. Wait Times Expressed in Nanoseconds - 50 MHz Clock

Timing Parameter Time in Nanoseconds Read or Write Time

Setup wait time 50 ns 60 ns (3 clock periods)

Data hold time 10 ns 20 ns (1 clock period)

Write wait time 30 ns 40 ns (2 clock periods)

Read wait time 30 ns 40 ns (2 clock periods)

When the wait time is expressed in nanoseconds, the read or write period, as seen on

the FPGA pins, is the duration of the specified wait time, rounded up to the next clock

period as Example 2–1 illustrates.

Example 2–1. Cycles When Wait Time Equals 21 ns

clock cycles = ceil(wait time in ns /clock period in ns)

clock cycles = ceil(21/20) = ceil (1.05) = 2

May 2011 Altera Corporation Avalon Tri-State Conduit Components User Guide

Preliminary

Page 12

2–6 Chapter 2: Generic Tri-State Controller

clk

address

chipselect_n

outputenable_n

read_n

write_n

data

addr1 addr2

data writedata

setup time

write wait time

read wait time

setup time

234 5

67

1

data hold time

Example Read and Write Using Setup, Hold and Wait Times

Figure 2–2 illustrates the timing of reads and writes given parameter settings

specified in Tab le 2– 4.

Figure 2–2. Read and Write Transfers with Setup Time and Wait States

Notes to Figure 2–2:

(1) The master drives

(2) After 3 cycles setup wait time, the interconnect asserts

(3) The slave port deasserts

edge.

address

(4)

write_n

(5)

write_n

(6)

address, chipselect

(7)

address

and

writedata

and asserts

read_n

are driven.

chipselect_n

.

read_n

.

after 2 cycles (from 30 ns) of read wait time. Data is sampled at the rising clock

is driven after 3 cycles (from 50 ns) setup wait time.

is deasserted after two cycles (from 30 ns) of write wait time.

, and the data bus stop being driven after 1 cycle (from 10 ns) of hold time.

Avalon Tri-State Conduit Components User Guide May 2011 Altera Corporation

Preliminary

Page 13

Signal Naming

data_out data

data_in

data_outen

Altera FPGA

Bidirectional Pin

reset_out reset

Altera FPGA

Tri-State Output Pin

reset_outen

write_out write

Altera FPGA

Output Pin

busy_in busy

Altera FPGA

Input Pin

write_outen

3. Tri-State Conduit Pin Sharer

The Tri-State Conduit Pin Sharer multiplexes between the signals of the connected

tri-state controllers. You can connect controllers created by customizing the Generic

Tri-State Controller or your own custom controllers. When you instantiate the

Tri-State Conduit Pin Sharer, you specify the number of connected interfaces and

identify the signals that share pins. The pin sharer arbitrates between connected

masters using a round-robin algorithm. It drives the signals of the granted Avalon-TC

master to the Tri-State Conduit Bridge.

The following sections explain how to use the Tri-State Conduit Pin Sharer in more

detail.

The Avalon Interface Specifications for Avalon-TC interfaces requires that signal names

have the following two parts:

■ A role—The role defines the signal to Qsys and typically represents the function of

the signal. Signals with identical roles can be shared. Typical roles include:

address, data, read, and write.

■ A pin type—The pin type must be specified using a suffix appended to a signal’s

role. The Tri-State Conduit Pin Sharer recognizes three pin type suffixes:

_outen

■ Bidirectional—Bidirectional pins define three signals:

■ Tri-State output—Tri-State output pins define two signals:

■ Output—Output pins define a single signal: <

■ Input—Input pins define a single signal: <

Figure 3–1 illustrates the naming conventions for Avalon-TC shared pins.

Figure 3–1. Shared Pin Types

, and

_in

. Theses three suffixes define the following four pin types:

<

role>_out

<

role>_out

, and

<role>_in

.

. Use this pin type for outputs that should be driven to a high

impedance state during system reset.

role>_out

role>_in

<role>_outen

<role>_outen

.

.

_out

,

,

and

May 2011 Altera Corporation Avalon Tri-State Conduit Components User Guide

If the widths of shared signals differ, the Tri-State Conduit Pin Sharer aligns them on

th

their 0

control of the bus. Signals that are not shared propagate directly through the Tri-State

Conduit Pin Sharer. In Figure 3–1,

bit and drives the higher-order pins to 0 whenever the narrower signal has

Preliminary

chipselect_out

and

irq_in

are not shared.

Page 14

3–2 Chapter 3: Tri-State Conduit Pin Sharer

DQ

clock

data_out

data_in

data_outen

reset

DQ

clock

write_out

reset

Parameters

Parameters

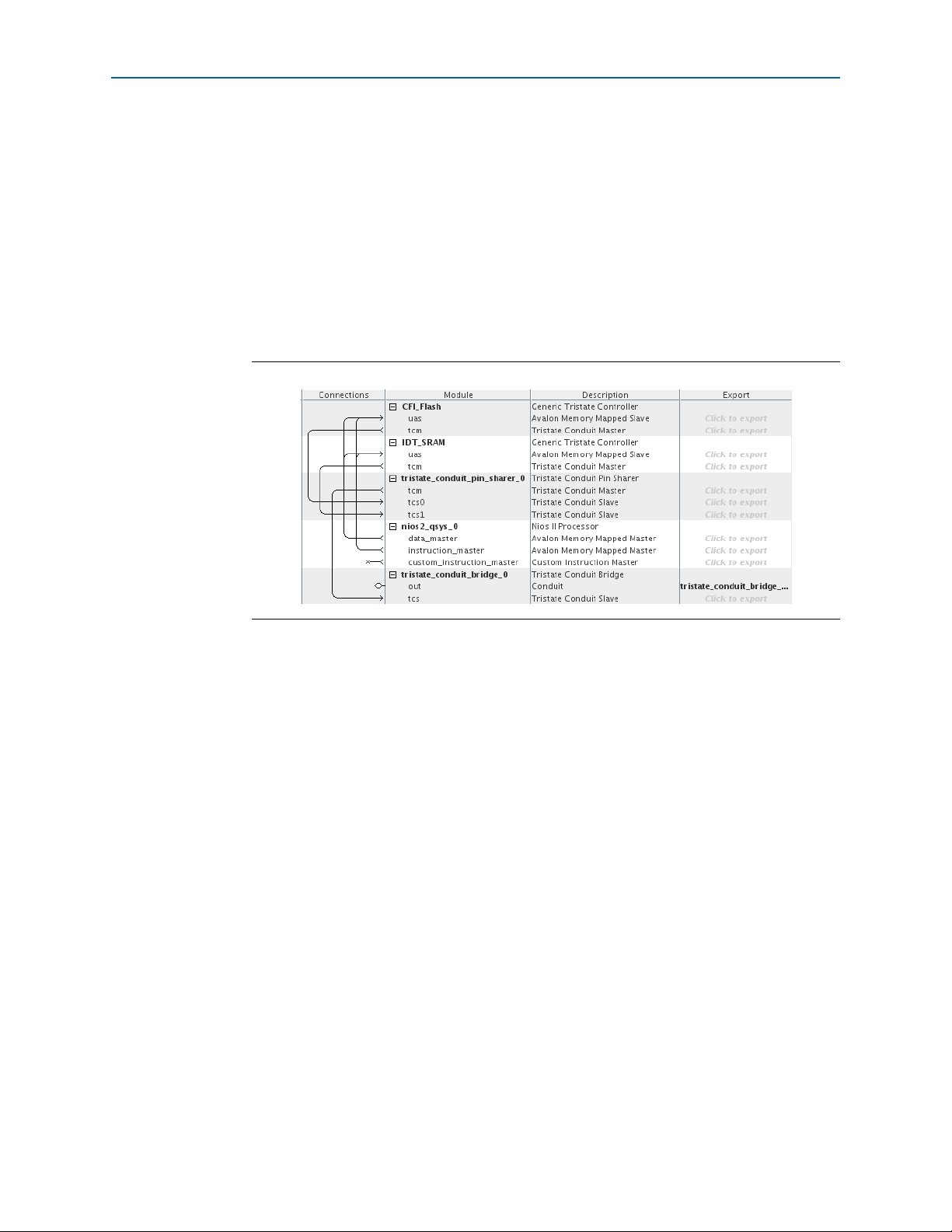

The parameter editor for the Tri-State Conduit Pin Sharer allows you to specify a

single parameter, the Number of Interfaces. This parameter specifies the number of

controllers that connect to the Tri-State Conduit Pin Sharer.

Complete the following steps to specify shared pins among connected controllers:

1. Add the Tri-State Conduit Pin Sharer to your Qsys design, specifying the number

of interfaces that connect to it.

2. In the Qsys Connections column, connect the tri-state conduit controllers to the

Tri-State Conduit Pin Sharer.

3. The Tri-State Conduit Pin Sharer parameter editor has a table with the following

columns: Interface, Signal Role, Signal Type, Signal Width, and Shared Signal

Name. To share a signal, type values in the Interface, Signal Role, and Shared

Signal Name columns for all controllers that share that signal.

4. You can use the Update Interface Table button to automatically populate these

values. Figure 3–2 shows that the CFI_Flash memory and IDT_SRAM memory

share the

address

signal.

Figure 3–2. Specifying Shared Signals Using the Tri-State Conduit Pin Sharer

Signal Behavior During Reset

At power-on reset, the enables for all bidirectional and tri-state output signals are

disabled. Figure 3–3 shows the logic that controls these signals.

Figure 3–3. Control of Bidirectional and Tri-State Output Signals

Avalon Tri-State Conduit Components User Guide May 2011 Altera Corporation

Preliminary

Page 15

Chapter 3: Tri-State Conduit Pin Sharer 3–3

clk

request

grant

data_out[31:0]

0

a b c d e f 10 11 12 13 14 15 16 17

13 62745 8 10 1391411 12 16 1715

.

Arbitration

Arbitration

Each Avalon-TC master and slave pair includes separate

request

and

grant

signals.

Arbitration logic in the Tri-State Conduit Pin Sharer grants requesting masters in

round-robin order. The meaning of the

grant

signal. The

request/grant

request

signal depends on the state of the

algorithm has the following dependency on the

current state:

1. When

request

is asserted and

grant

is deasserted,

request

is requesting access for

the current cycle.

2. When

request

is asserted and

the next cycle; consequently,

grant

is asserted,

request

request

is requesting access for

should be deasserted on the final cycle of an

access.

Because

request

is deasserted in the final cycle of a bus access, it can be reasserted

immediately following the final cycle of a transfer, making both rearbitration and

continuous bus access possible if no other masters are requesting access. After it is

asserted, request must remain asserted until granted; consequently, the shortest bus

access is two cycles.

The

grant

signal is asserted in response to the

until one cycle following the deassertion of

request

request

signal and remains asserted

. The design of the Avalon-TC

interface does not allow a default Avalon-TC master to be granted bus access when no

masters are requesting.

Figure 3–4 illustrates arbitration timing for the Tri-State Conduit Pin Sharer. As this

figure illustrates, a device can drive or receive valid data in the granted cycle.

Figure 3–4 shows the following sequence of events:

1. In cycle 1, the tri-state conduit master asserts grant. The granted slave drives valid

data in cycles 1 and 2.

2. In cycle 4, the tri-state conduit master asserts grant. The granted slave drives valid

data in cycles 4–7.

3. In cycle 8, the tri-state conduit master asserts grant. The granted slave drives valid

data in cycles 8–16.

4. Cycle 3 is the only cycle that does not contain valid data.

Figure 3–4. Arbitration Timing

May 2011 Altera Corporation Avalon Tri-State Conduit Components User Guide

Preliminary

Page 16

3–4 Chapter 3: Tri-State Conduit Pin Sharer

Tr i-state

Conduit

Pin Sharer

TCS

TCS

request

grant

Tr i-state

Controller 1

TCM

request

grant

Tr i-state

Controller 2

TCM

TCM

Tr i-state

Controller 3

TCM

request

grant

request

grant

addr

write

read

data

request

grant

Tr i-state

Controller 4

TCM

Tr i-state

Conduit

Pin Sharer

TCS

TCS

TCM

Tr i-state

Conduit

Pin Sharer

TCS

TCS

TCM

Tr i-state

Conduit

Bridge

Device 1

Device 2

Device 3

Device 4

TCS

CN

request

request

grant

grant

Altera FPGA

Sub-system A

Sub-system B

Top Level

PCB

Hierarchical Pin Sharing

Hierarchical Pin Sharing

Figure 1–1 on page 1–1 provides the simplest use of the Tri-State Conduit Pin Sharer;

it multiplexes between two controllers. You can also create a design that includes

hierarchy of Tri-State Conduit Pin Sharers that access the same pins on the FPGA. In

Figure 3–5, Sub-systems A and B each include two controllers that access off-chip

devices. The pin sharer in the Top Level system connects to a single Tri-State Conduit

Bridge that drives signals on the PCB.

Figure 3–5. Using The Tri-State Conduit Pin Sharer in Hierarchical Designs

Avalon Tri-State Conduit Components User Guide May 2011 Altera Corporation

Preliminary

Page 17

This chapter provides additional information about the document and Altera.

Document Revision History

The following table shows the revision history for this document.

Date Version Changes

May 2011 1.0 Initial release.

How to Contact Altera

To locate the most up-to-date information about Altera products, refer to the

following table.

Additional Information

Contact (1) Contact Method Address

Technical support Website www.altera.com/support

Technical training

Product literature Website www.altera.com/literature

Non-technical support (General) Email nacomp@altera.com

(Software Licensing) Email authorization@altera.com

Note to Table:

(1) You can also contact your local Altera sales office or sales representative.

Website www.altera.com/training

Email custrain@altera.com

Typographic Conventions

The following table shows the typographic conventions this document uses.

Visual Cue Meaning

Bold Type with Initial Capital

Letters

bold type

Italic Type with Initial Capital Letters Indicate document titles. For example, Stratix IV Design Guidelines.

italic type

Initial Capital Letters

Indicate command names, dialog box titles, dialog box options, and other GUI

labels. For example, Save As dialog box. For GUI elements, capitalization matches

the GUI.

Indicates directory names, project names, disk drive names, file names, file name

extensions, software utility names, and GUI labels. For example, \qdesigns

directory, D: drive, and chiptrip.gdf file.

Indicates variables. For example, n + 1.

Variable names are enclosed in angle brackets (< >). For example, <file name> and

<project name>.pof file.

Indicate keyboard keys and menu names. For example, the Delete key and the

Options menu.

May 2011 Altera Corporation Avalon Tri-State Conduit Components User Guide

Preliminary

Page 18

Info–2 Additional Information

Typographic Conventions

Visual Cue Meaning

“Subheading Title”

Quotation marks indicate references to sections within a document and titles of

Quartus II Help topics. For example, “Typographic Conventions.”

Indicates signal, port, register, bit, block, and primitive names. For example,

tdi

, and

input

. The suffix n denotes an active-low signal. For example,

data1

resetn

,

.

Indicates command line commands and anything that must be typed exactly as it

Courier type

appears. For example,

c:\qdesigns\tutorial\chiptrip.gdf

.

Also indicates sections of an actual file, such as a Report File, references to parts of

files (for example, the AHDL keyword

TRI

example,

).

SUBDESIGN

), and logic function names (for

r An angled arrow instructs you to press the Enter key.

1., 2., 3., and

a., b., c., and so on

■ ■ ■ Bullets indicate a list of items when the sequence of the items is not important.

Numbered steps indicate a list of items when the sequence of the items is important,

such as the steps listed in a procedure.

1 The hand points to information that requires special attention.

h A question mark directs you to a software help system with related information.

f The feet direct you to another document or website with related information.

c

w

A caution calls attention to a condition or possible situation that can damage or

destroy the product or your work.

A warning calls attention to a condition or possible situation that can cause you

injury.

The envelope links to the Email Subscription Management Center page of the Altera

website, where you can sign up to receive update notifications for Altera documents.

Avalon Tri-State Conduit Components User Guide May 2011 Altera Corporation

Preliminary

Loading...

Loading...