Page 1

Arria V Device Handbook Volume 1: Device Interfaces and Integration

Volume 1: Device Interfaces and Integration

Arria V Device Handbook

101 Innovation Drive

San Jose, CA 95134

www.altera.com

AV-5V2-2.0

Page 2

© 2012 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos

are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its

semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and

services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service

described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying

on any published information and before placing orders for products or services.

ISO

9001:2008

Registered

June 2012 Altera Corporation Arria V Device Handbook

Volume 1: Device Interfaces and Integration

Page 3

Contents

Chapter Revision Dates ...................................................................... xi

Section I. Device Core for Arria V Devices

Revision History ........................................................................ I–1

Chapter 1. Logic Array Blocks and Adaptive Logic Modules in Arria V Devices

LAB ...................................................................................1–2

MLAB ...............................................................................1–3

Interconnects .........................................................................1–4

LAB Control Signals ...................................................................1–5

ALM Registers ........................................................................1–6

ALM Outputs ........................................................................1–7

ALM Operating Modes ..................................................................1–9

Normal Mode ........................................................................1–9

Extended LUT Mode ..................................................................1–9

Arithmetic Mode .....................................................................1–10

Carry Chain ......................................................................1–11

Shared Arithmetic Mode ..............................................................1–12

Shared Arithmetic Chain ...........................................................1–12

Document Revision History .............................................................1–13

Chapter 2. Memory Blocks in Arria V Devices

Memory Types ..........................................................................2–1

Memory Features ........................................................................2–2

Memory Modes .........................................................................2–3

Mixed-Width Port Configurations .........................................................2–4

M10K Blocks Mixed-Width Configurations ...............................................2–4

MLABs Mixed-Width Configurations ....................................................2–5

Clocking Modes .........................................................................2–5

Clocking Modes for Each Memory Mode .................................................2–5

Asynchronous Clears ..................................................................2–5

Output Read Data in Simultaneous Read/Write ...........................................2–6

Independent Clock Enables ............................................................2–6

Parity Bit ...............................................................................2–6

Byte Enable .............................................................................2–6

byteena Controls ......................................................................2–7

Data Byte Output .....................................................................2–7

RAM Blocks Operations ...............................................................2–8

Design Considerations ...................................................................2–8

Memory Block Selection ...............................................................2–8

Conflict Resolution ....................................................................2–9

Read-During-Write Behavior ...........................................................2–9

Same-Port Read-During-Write Mode ..................................................2–9

Mixed-Port Read-During-Write Mode ................................................2–10

Power-Up State and Memory Initialization ..............................................2–12

Power Management ..................................................................2–13

Document Revision History .............................................................2–13

June 2012 Altera Corporation Arria V Device Handbook

Volume 1: Device Interfaces and Integration

Page 4

iv Contents

Chapter 3. Variable-Precision DSP Blocks in Arria V Devices

Features ................................................................................3–1

Supported Operational Modes ............................................................3–2

Design Considerations ...................................................................3–3

Operational Modes ....................................................................3–3

Pre-Adder ...........................................................................3–3

Internal Coefficient ....................................................................3–3

Accumulator .........................................................................3–3

Chainout Adder ......................................................................3–3

Block Architecture .......................................................................3–4

Input Register Bank ...................................................................3–5

Pre-Adder ...........................................................................3–6

Internal Coefficient ....................................................................3–6

Multipliers ...........................................................................3–7

Adder ...............................................................................3–7

Accumulator and Chainout Adder ......................................................3–7

Systolic Registers .....................................................................3–8

Double Accumulation Register .........................................................3–8

Output Register Bank ..................................................................3–8

Operational Mode Descriptions ...........................................................3–9

Independent Multiplier Mode ..........................................................3–9

Independent Complex Multiplier Mode .................................................3–12

Multiplier Adder Sum Mode ..........................................................3–13

18 x 18 Multiplication Summed with 36-Bit Input Mode ...................................3–14

Systolic FIR Mode ....................................................................3–15

Document Revision History .............................................................3–17

Chapter 4. Clock Networks and PLLs in Arria V Devices

Clock Networks in Arria V Devices ........................................................4–1

Global Clock Networks ................................................................4–3

Regional Clock Networks ..............................................................4–4

Periphery Clock Networks .............................................................4–5

Clock Sources Per Quadrant ............................................................4–6

Clock Regions ........................................................................4–7

Entire Device Clock Region ..........................................................4–7

Regional Clock Region ..............................................................4–7

Dual-Regional Clock Region .........................................................4–7

Clock Network Sources ................................................................4–8

Dedicated Clock Input Pins ..........................................................4–8

Internal Logic ......................................................................4–8

DPA Outputs ......................................................................4–8

HSSI Outputs ......................................................................4–8

PLL Clock Outputs .................................................................4–8

Clock Input Pin Connections to GCLK and RCLK Networks .............................4–9

Clock Output Connections ............................................................4–12

Clock Control Block ..................................................................4–12

GCLK Control Block ...............................................................4–13

RCLK Control Block ...............................................................4–14

PCLK Control Block ...............................................................4–14

External PLL Clock Output Control Block .............................................4–15

Clock Power Down ...................................................................4–16

Clock Enable Signals .................................................................4–16

Arria V PLLs ...........................................................................4–18

Arria V Device Handbook June 2012 Altera Corporation

Volume 1: Device Interfaces and Integration

Page 5

Contents v

Fractional PLL Architecture ...........................................................4–23

Fractional PLL Usage ..............................................................4–23

PLL External Clock I/O Pins ..........................................................4–23

PLL Control Signals ..................................................................4–25

pfdena ...........................................................................4–25

areset ............................................................................4–25

locked ............................................................................4–26

Clock Feedback Modes ...............................................................4–26

Source Synchronous Mode ..........................................................4–27

LVDS Compensation Mode .........................................................4–28

Direct Compensation Mode .........................................................4–29

NormalMode .....................................................................4–30

Zero-Delay Buffer Mode ............................................................4–30

External Feedback Mode ...........................................................4–32

Clock Multiplication and Division ......................................................4–33

Programmable Duty Cycle ............................................................4–34

Clock Switchover ....................................................................4–34

Automatic Clock Switchover ........................................................4–35

Manual Clock Switchover ..........................................................4–39

Guidelines ........................................................................4–39

PLL Reconfiguration and Dynamic Phase Shift ...........................................4–40

Document Revision History .............................................................4–41

Section II. I/O Interfaces for Arria V Devices

Revision History ....................................................................... II–1

Chapter 5. I/O Features in Arria V Devices

I/O Standards Support ...................................................................5–2

Design Considerations ...................................................................5–4

I/O Bank Restrictions .................................................................5–4

Non-Voltage-Referenced Standards ...................................................5–4

Voltage-Referenced Standards ........................................................5–4

Mixing Voltage-Referenced and Non-Voltage-Referenced Standards ......................5–4

V

V

V

3.3-V I/O Interface ....................................................................5–5

LVDS Channels .......................................................................5–6

I/O Banks ..............................................................................5–6

Modular I/O Banks ...................................................................5–8

IOE Structure ..........................................................................5–11

Current Strength .....................................................................5–12

MultiVolt I/O Interface ...............................................................5–13

Programmable IOE Features .............................................................5–14

Slew-Rate Control ....................................................................5–14

I/O Delay ...........................................................................5–14

Open-Drain Output ..................................................................5–15

Bus-Hold ...........................................................................5–15

Pull-Up Resistor .....................................................................5–16

Pre-Emphasis ........................................................................5–16

Differential Output Voltage ...........................................................5–16

Restriction .....................................................................5–5

CCPD

Restriction .....................................................................5–5

CCIO

Pin Restriction ...................................................................5–5

REF

Programmable IOE Delay ...........................................................5–14

Programmable Output Buffer Delay ..................................................5–15

June 2012 Altera Corporation Arria V Device Handbook

Volume 1: Device Interfaces and Integration

Page 6

vi Contents

OCT Schemes ..........................................................................5–17

OCT Calibration Block ................................................................5–18

Sharing an OCT Calibration Block on Multiple I/O Banks ...............................5–21

RSOCT with Calibration ..............................................................5–22

RSOCT Without Calibration ...........................................................5–22

RTOCT with Calibration ..............................................................5–23

Dynamic OCT .......................................................................5–24

LVDS Input RDOCT .................................................................5–25

I/O Standards Termination Schemes ......................................................5–26

Single-Ended I/O Standard Termination ................................................5–28

Differential I/O Standard Termination ..................................................5–29

LVDS, RSDS, and Mini-LVDS I/O Standard Termination ...............................5–31

LVPECL I/O Standard Termination ..................................................5–32

Emulated LVDS, RSDS, and Mini-LVDS I/O Standard Termination ......................5–32

Document Revision History .............................................................5–34

Chapter 6. High-Speed Differential I/O Interfaces and DPA in Arria V Devices

Dedicated High-Speed I/O Circuitries .....................................................6–1

SERDES and DPA Bank Locations .......................................................6–2

LVDS SERDES Circuitry ...............................................................6–3

LVDS Channels .......................................................................6–4

True LVDS Buffers ....................................................................6–4

Differential Transmitter ..................................................................6–6

Transmitter Blocks ....................................................................6–6

Transmitter Clocking ..................................................................6–6

Serializer Bypass for DDR and SDR Operations ...........................................6–7

Programmable V

Programmable Pre-Emphasis ...........................................................6–8

Differential Receiver .....................................................................6–9

Receiver Blocks ......................................................................6–10

DPA Block ........................................................................6–10

Synchronizer ......................................................................6–11

Data Realignment Block (Bit Slip) ....................................................6–12

Deserializer .......................................................................6–13

Receiver Modes ......................................................................6–13

Non-DPAMode ...................................................................6–14

DPAMode .......................................................................6–15

Soft-CDR Mode ...................................................................6–16

Receiver Clocking ....................................................................6–17

Differential I/O Termination ..........................................................6–17

PLLs and Clocking .....................................................................6–18

Source Synchronous Timing Budget ......................................................6–18

Differential Data Orientation ..........................................................6–19

Differential I/O Bit Position ...........................................................6–19

Transmitter Channel-to-Channel Skew ..................................................6–20

Receiver Skew Margin for Non-DPA Mode ..............................................6–21

Design Considerations ..................................................................6–21

Differential Pin Placement .............................................................6–21

DPA-Enabled Channels, DPA-Disabled Channels, and Single-Ended I/Os ................6–22

Guidelines for DPA-Enabled Differential Channels .....................................6–22

Guidelines for DPA-Disabled Differential Channels ....................................6–25

Document Revision History .............................................................6–28

OD .....................................................................................6–8

Arria V Device Handbook June 2012 Altera Corporation

Volume 1: Device Interfaces and Integration

Page 7

Contents vii

Chapter 7. External Memory Interfaces in Arria V Devices

Memory Interface Pin Support ............................................................7–2

Design Considerations ...................................................................7–5

Memory Interface .....................................................................7–5

Delay-Locked Loop ...................................................................7–5

DQ/DQS Pins ........................................................................7–6

Using the RZQ Pins in a DQ/DQS Group for Memory Interfaces ............................7–6

PHYCLK Networks ...................................................................7–6

DDR2 SDRAM Interface ...............................................................7–6

DDR3 SDRAM DIMM .................................................................7–7

Hard Memory Controller ..............................................................7–7

Bonding ...........................................................................7–7

External Memory Interface Features .......................................................7–8

DQS Phase-Shift Circuitry ..............................................................7–9

Delay-Locked Loop ................................................................7–11

DLL Phase-Shift ...................................................................7–11

PHY Clock (PHYCLK) Networks .......................................................7–13

DQS Logic Block .....................................................................7–16

Update Enable Circuitry ............................................................7–16

DQS Delay Chain ..................................................................7–17

DQS Postamble Circuitry ...........................................................7–17

HDR Block .......................................................................7–17

Dynamic OCT Control ................................................................7–18

IOE Registers ........................................................................7–19

Input Registers ....................................................................7–19

Output Registers ..................................................................7–19

Delay Chain .........................................................................7–21

Hard Memory Controllers .............................................................7–22

Features of the Hard Memory Controller .............................................7–22

Multiport Logic ...................................................................7–24

Bonding Support ..................................................................7–24

UniPHY IP ............................................................................7–28

Document Revision History .............................................................7–28

Section III. System Integration for Arria V Devices

Revision History ...................................................................... III–1

Chapter 8. Configuration, Design Security, and Remote System Upgrades in Arria V Devices

MSEL Pin Settings .......................................................................8–2

Configuration Sequence ..................................................................8–3

PowerUp ............................................................................8–4

V

CCPGM

V

CCPD

Reset ................................................................................8–4

Configuration ........................................................................8–4

Configuration Error Handling ..........................................................8–5

Initialization .........................................................................8–5

User Mode ...........................................................................8–5

Device Configuration Pins ................................................................8–6

Configuration Pins Summary ...........................................................8–6

Configuration Pin Options in the Quartus II Software ......................................8–7

Fast Passive Parallel Configuration ........................................................8–7

FPP Single-Device Configuration ........................................................8–8

June 2012 Altera Corporation Arria V Device Handbook

Pin........................................................................8–4

Pin .........................................................................8–4

Volume 1: Device Interfaces and Integration

Page 8

viii Contents

FPP Multi-Device Configuration ........................................................8–8

Pin Connections and Guidelines ......................................................8–8

Using Multiple Configuration Data ...................................................8–9

Configuring Multiple Devices Using One Configuration Data ...........................8–10

Active Serial Configuration ..............................................................8–11

DATA Clock (DCLK) .................................................................8–11

AS Single-Device Configuration .......................................................8–12

AS Multi-Device Configuration ........................................................8–13

Pin Connections and Guidelines .....................................................8–13

Using Multiple Configuration Data ..................................................8–14

Configuring Multiple Devices Using One Configuration Data ...........................8–15

Estimating the AS Configuration Time ..................................................8–15

Using EPCS and EPCQ Devices ........................................................8–16

Controlling EPCS and EPCQ Devices .................................................8–16

Trace Length and Loading ..........................................................8–16

Programming EPCS and EPCQ Devices ..............................................8–17

Passive Serial Configuration .............................................................8–21

PS Single-Device Configuration ........................................................8–21

PS Multi-Device Configuration ........................................................8–23

Pin Connections and Guidelines .....................................................8–23

Using Multiple Configuration Data ..................................................8–23

Configuring Multiple Devices Using One Configuration Data ...........................8–24

Using PC Host and Download Cable .................................................8–25

JTAG Configuration ....................................................................8–26

JTAG Single-Device Configuration .....................................................8–26

JTAG Multi-Device Configuration ......................................................8–29

CONFIG_IO JTAG Instruction .........................................................8–30

Configuration Data Compression .........................................................8–30

Enabling Compression Before Design Compilation .......................................8–30

Enabling Compression After Design Compilation ........................................8–31

Using Compression in Multi-Device Configuration .......................................8–31

Remote System Upgrades ...............................................................8–32

Configuration Images ................................................................8–32

Configuration Sequence ..............................................................8–33

Remote System Upgrade Circuitry .....................................................8–34

Enabling Remote System Upgrade Circuitry .............................................8–35

Remote System Upgrade Registers .....................................................8–35

Control Register ...................................................................8–36

Status Register ....................................................................8–36

Remote System Upgrade State Machine .................................................8–36

User Watchdog Timer ................................................................8–37

Design Security ........................................................................8–37

JTAG Secure Mode ...................................................................8–38

Security Key Types ...................................................................8–39

Security Modes ......................................................................8–39

Design Security Implementation Steps ..................................................8–40

Document Revision History .............................................................8–41

Chapter 9. SEU Mitigation in Arria V Devices

Basic Description ........................................................................9–1

Error Detection Features .................................................................9–1

Types of Error Detection .................................................................9–2

Configuration Error Detection ..........................................................9–2

User Mode Error Detection .............................................................9–2

Arria V Device Handbook June 2012 Altera Corporation

Volume 1: Device Interfaces and Integration

Page 9

Contents ix

Error Detection Components ..............................................................9–3

Error Detection Pin ....................................................................9–3

Error Detection Registers ...............................................................9–3

Error Message Register ................................................................9–5

Storage Size for Error Detection .........................................................9–5

Error Detection Timing ...................................................................9–6

Minimum EMR Update Interval ........................................................9–6

Error Detection Frequency .............................................................9–6

CRC Calculation Time .................................................................9–7

Using the Error Detection Feature .........................................................9–8

Enabling the User Mode Error Detection .................................................9–8

Error Detection Process ................................................................9–8

Reading the Error Location Bit Through JTAG ............................................9–9

Recovering From CRC Errors ...........................................................9–9

Testing the Error Detection Block ..........................................................9–9

Error Detection Instruction .............................................................9–9

JTAG Fault Injection Register ..........................................................9–10

Automating the Testing Process ........................................................9–10

Document Revision History .............................................................9–10

Chapter 10. JTAG Boundary-Scan Testing in Arria V Devices

BST Operation Control ..................................................................10–1

IDCODE ............................................................................10–1

Supported JTAG Instruction ...........................................................10–2

JTAG Secure Mode ................................................................10–4

JTAG Private Instruction ..............................................................10–4

I/O Voltage for JTAG Operation .........................................................10–4

Enabling and Disabling IEEE Std. 1149.1 BST Circuitry ......................................10–5

Performing BST ........................................................................10–5

Guidelines for IEEE Std. 1149.1 Boundary-Scan Testing ......................................10–6

IEEE Std. 1149.1 BST Architecture ........................................................10–7

IEEE Std. 1149.1 BST Functionality .....................................................10–7

IEEE Std. 1149.1 BST Circuitry Registers ................................................10–7

IEEE Std. 1149.1 BST Pin Function ......................................................10–8

IEEE Std. 1149.1 Boundary-Scan Register ................................................10–9

Boundary-Scan Cells of a Arria V Device I/O Pin ......................................10–9

IEEE Std. 1149.1 TAP Controller ......................................................10–11

IEEE Std. 1149.1 JTAG Mandatory Instruction .............................................10–14

SAMPLE/PRELOAD Instruction Mode ................................................10–14

EXTEST Instruction Mode ............................................................10–16

BYPASS Instruction Mode ............................................................10–18

Document Revision History ............................................................10–19

Chapter 11. Power Management in Arria V Devices

Power Consumption ....................................................................11–2

Internal Temperature Sensing Diode ......................................................11–2

Hot-Socketing Feature ..................................................................11–3

Hot-Socketing Implementation ...........................................................11–4

Power-Up Sequencing ..................................................................11–5

Power-On Reset Circuitry ...............................................................11–6

Document Revision History .............................................................11–8

June 2012 Altera Corporation Arria V Device Handbook

Volume 1: Device Interfaces and Integration

Page 10

x Contents

Additional Information

How to Contact Altera ................................................................ Info–1

Typographic Conventions ............................................................. Info–1

Arria V Device Handbook June 2012 Altera Corporation

Volume 1: Device Interfaces and Integration

Page 11

Chapter Revision Dates

The chapters in this document, Volume 1: Device Interfaces and Integration, were

revised on the following dates. Where chapters or groups of chapters are available

separately, part numbers are listed.

Part Number:

Chapter 1. Logic Array Blocks and Adaptive Logic Modules in Arria V Devices

Revised: June 2012

Part Number: AV-52001-2.0

Chapter 2. Memory Blocks in Arria V Devices

Revised: June 2012

Part Number: AV-52002-2.0

Chapter 3. Variable-Precision DSP Blocks in Arria V Devices

Revised: June 2012

Part Number: AV-52003-2.0

Chapter 4. Clock Networks and PLLs in Arria V Devices

Revised: June 2012

Part Number: AV-52004-2.0

Chapter 5. I/O Features in Arria V Devices

Revised: June 2012

Part Number: AV52005-2.0

Chapter 6. High-Speed Differential I/O Interfaces and DPA in Arria V Devices

Revised: June 2012

Part Number: AV52006-2.0

Chapter 7. External Memory Interfaces in Arria V Devices

Revised: June 2012

Part Number: AV52007-2.0

Chapter 8. Configuration, Design Security, and Remote System Upgrades in Arria V Devices

Revised: June 2012

Part Number: AV-52008-2.0

Chapter 9. SEU Mitigation in Arria V Devices

Revised: June 2012

Part Number: AV-52009-2.0

Chapter 10. JTAG Boundary-Scan Testing in Arria V Devices

Revised: June 2012

Part Number: AV-52010-2.0

Chapter 11. Power Management in Arria V Devices

Revised: June 2012

Part Number: AV-52011-2.0

June 2012 Altera Corporation Arria V Device Handbook

Volume 1: Device Interfaces and Integration

Page 12

xii

Arria V Device Handbook June 2012 Altera Corporation

Volume 1: Device Interfaces and Integration

Page 13

This section provides a complete overview of all features relating to the Arria®V

device family. This section includes the following chapters:

■ Chapter 1, Logic Array Blocks and Adaptive Logic Modules in Arria V Devices

■ Chapter 2, Memory Blocks in Arria V Devices

■ Chapter 3, Variable-Precision DSP Blocks in Arria V Devices

■ Chapter 4, Clock Networks and PLLs in Arria V Devices

Revision History

Refer to each chapter for its own specific revision history. For information about when

each chapter was updated, refer to the Chapter Revision Dates section, which appears

in this volume.

Section I. Device Core for Arria V Devices

© 2012 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos

are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its

semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and

services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service

described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying

on any published information and before placing orders for products or services.

Arria V Device Handbook

Volume 1: Device Interfaces and Integration

June 2012

ISO

9001:2008

Registered

Page 14

I–2

Revision History

Arria V Device Handbook June 2012 Altera Corporation

Volume 1: Device Interfaces and Integration

Page 15

June 2012

AV-52001-2.0

AV-52001-2.0

1. Logic Array Blocks and Adaptive Logic Modules in Arria V Devices

This chapter describes the features of the logic array block (LAB) in the Arria®V core

fabric.

The LAB is composed of basic building blocks known as adaptive logic modules

(ALMs) that you can configure to implement logic functions, arithmetic functions,

and register functions.

You can use a quarter of the available LABs in Arria V devices as a memory LAB

(MLAB).

The Quartus®II software and other supported third-party synthesis tools, in

conjunction with parameterized functions such as the library of parameterized

modules (LPM), automatically choose the appropriate mode for common functions

such as counters, adders, subtractors, and arithmetic functions.

This chapter contains the following sections:

■ “LAB”

■ “ALM Operating Modes” on page 1–9

© 2012 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos

are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its

semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and

services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service

described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying

on any published information and before placing orders for products or services.

Arria V Device Handbook

Volume 1: Device Interfaces and Integration

June 2012

Feedback Subscribe

ISO

9001:2008

Registered

Page 16

1–2 Chapter 1: Logic Array Blocks and Adaptive Logic Modules in Arria V Devices

LAB

LAB

The LABs are configurable logic blocks that consist of a group of logic resources. Each

LAB contains dedicated logic for driving control signals to its ALMs.

MLAB is a superset of the LAB and includes all the LAB features.

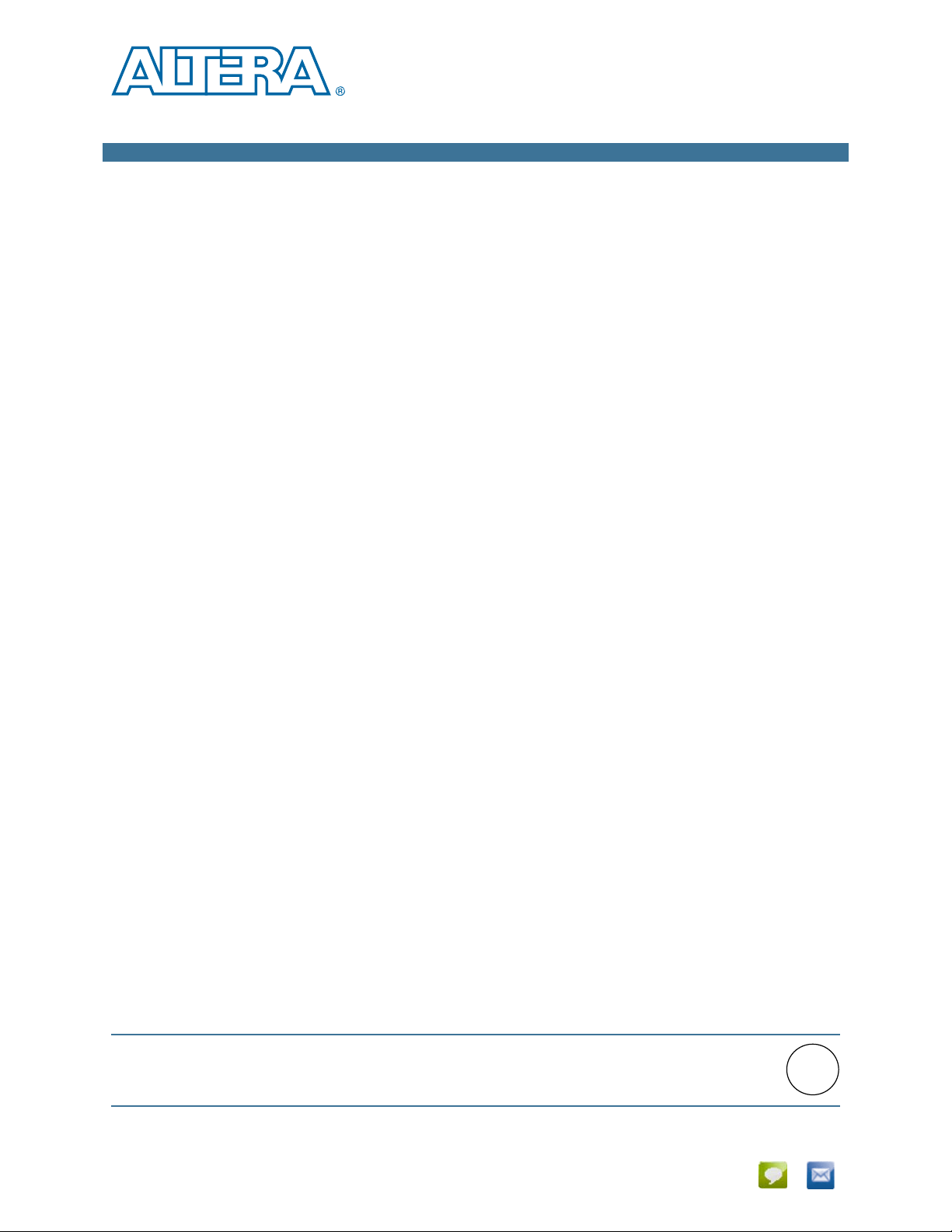

Figure 1–1 shows an overview of the Arria V LAB and MLAB structure with the LAB

interconnects.

Figure 1–1. LAB Structure and Interconnects Overview in Arria V Devices

R14

R3/R6

Direct link

interconnect from

adjacent block (1)

Direct link

interconnect to

adjacent block

C2/C4 C12

Fast local interconnect is driven

from either sides by column interconnect

and LABs, and from above by row interconnect

Row interconnects of

variable speed and length

ALMs

MLABLABLocal interconnect

Direct link

interconnect from

adjacent block

Direct link

interconnect to

adjacent block

Column interconnects of

variable speed and length

Note to Figure 1–1:

(1) Connects to adjacent LABs, memory blocks, digital signal processing (DSP) blocks, or I/O element (IOE) outputs.

Arria V Device Handbook June 2012 Altera Corporation

Volume 1: Device Interfaces and Integration

Page 17

Chapter 1: Logic Array Blocks and Adaptive Logic Modules in Arria V Devices 1–3

LAB

MLAB

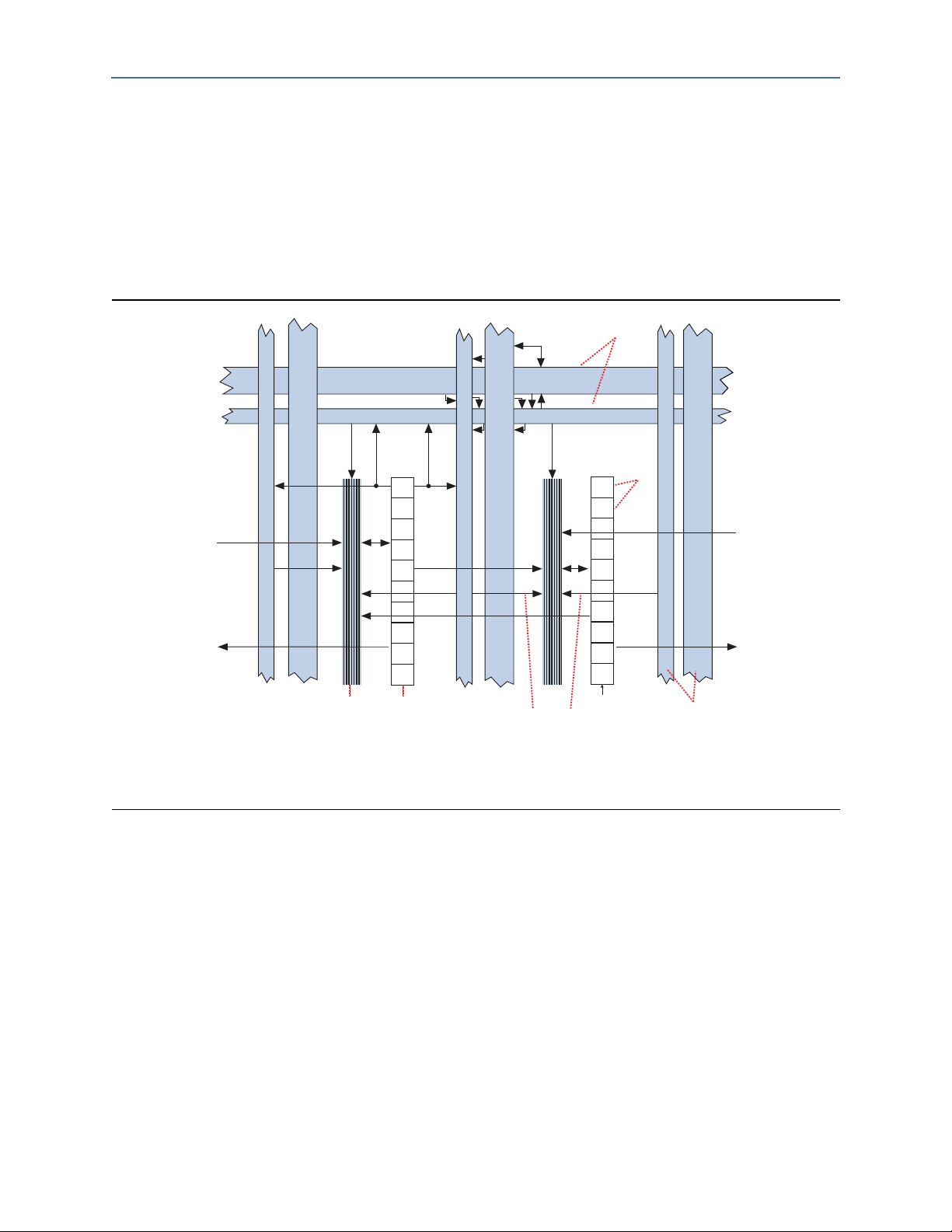

Each MLAB supports a maximum of 640 bits of simple dual-port SRAM.

You can configure each ALM in an MLAB as a 32 x 2 memory block, resulting in a

configuration of 32 x 20 simple dual-port SRAM blocks.

Figure 1–2 shows the LAB and MLAB topology.

Figure 1–2. LAB and MLAB Structure for Arria V Devices

LUT-based-32 x 2

Simple dual port SRAM

LUT-based-32 x 2

Simple dual port SRAM

LUT-based-32 x 2

Simple dual port SRAM

LUT-based-32 x 2

Simple dual port SRAM

LUT-based-32 x 2

Simple dual port SRAM

(1)

(1)

(1)

(1)

(1)

ALM

ALM

ALM

ALM

ALM

LAB Control Block LAB Control Block

LUT-based-32 x 2

Simple dual port SRAM

LUT-based-32 x 2

Simple dual port SRAM

LUT-based-32 x 2

Simple dual port SRAM

LUT-based-32 x 2

Simple dual port SRAM

(1)

(1)

(1)

(1)

ALM

ALM

ALM

ALM

LUT-based-32 x 2

Simple dual port SRAM

MLAB

(1)

ALM

LAB

Note to Figure 1–2:

(1) You can use an MLAB ALM as a regular LAB ALM or configure it as a dual-port SRAM.

June 2012 Altera Corporation Arria V Device Handbook

Volume 1: Device Interfaces and Integration

Page 18

1–4 Chapter 1: Logic Array Blocks and Adaptive Logic Modules in Arria V Devices

LAB

Interconnects

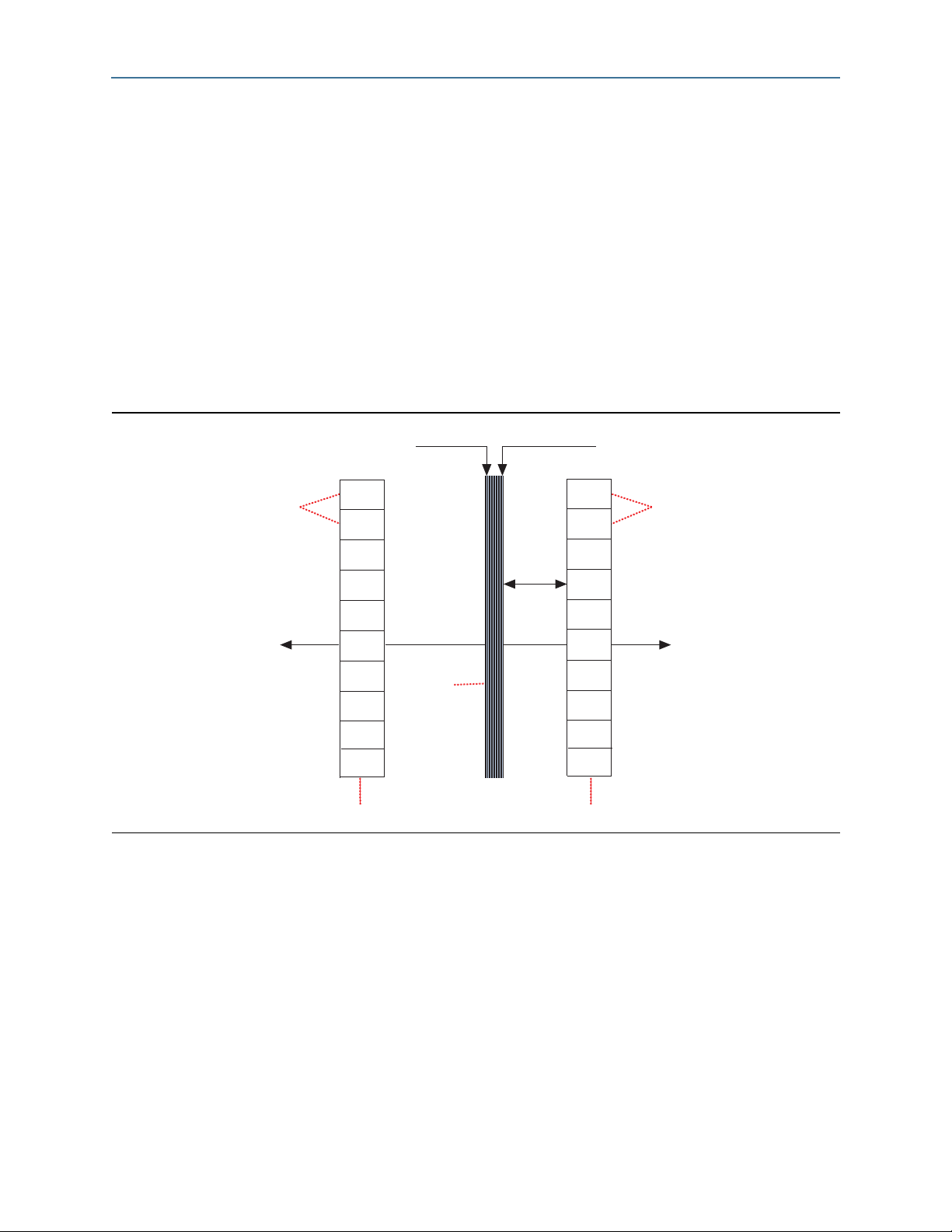

Each LAB can drive 30 ALMs through fast-local and direct-link interconnects. Ten

ALMs are in any given LAB and ten ALMs are in each of the adjacent LABs.

The local interconnect can drive ALMs in the same LAB using column and row

interconnects and ALM outputs in the same LAB.

Neighboring LABs, MLABs, M10K blocks, or digital signal processing (DSP) blocks

from the left or right can also drive the LAB’s local interconnect using the direct link

connection.

The direct link connection feature minimizes the use of row and column

interconnects, providing higher performance and flexibility.

Figure 1–3 shows the LAB fast-local and direct-link interconnects.

Figure 1–3. Direct Link and Fast Local Interconnects for Arria V Devices

Direct link interconnect from

left LAB, memory block,

DSP block, or IOE output

ALMs ALMs

Direct link

interconnect

to left

Fast local

interconnect

MLAB

LAB

Direct link interconnect from

right LAB, memory block,

DSP block, or IOE output

Direct link

interconnect

to right

Arria V Device Handbook June 2012 Altera Corporation

Volume 1: Device Interfaces and Integration

Page 19

Chapter 1: Logic Array Blocks and Adaptive Logic Modules in Arria V Devices 1–5

LAB

LAB Control Signals

Each LAB contains dedicated logic for driving the control signals to its ALMs, and has

two unique clock sources and three clock enable signals.

The LAB control block generates up to three clocks using the two clock sources and

three clock enable signals. Each clock and the clock enable signals are linked.

De-asserting the clock enable signal turns off the corresponding LAB-wide clock.

Figure 1–4 shows the clock sources and clock enable signals in an LAB.

Figure 1–4. LAB-Wide Control Signals for Arria V Devices

There are two unique

clock signals per LAB.

Dedicated Row LAB Clocks

Local Interconnect

Local Interconnect

Local Interconnect

Local Interconnect

6

6

6

(1)

labclk0

labclkena0

or asyncload

or labpreset

labclk1

labclkena1 labclkena2 labclr0 synclr

labclk2

syncload

labclr1

Note to Figure 1–4:

(1) For more information, refer to Figure 1–6 on page 1–8.

June 2012 Altera Corporation Arria V Device Handbook

Volume 1: Device Interfaces and Integration

Page 20

1–6 Chapter 1: Logic Array Blocks and Adaptive Logic Modules in Arria V Devices

LAB

ALM Registers

One ALM contains four programmable registers. Each register has data, clock,

synchronous and asynchronous clear, and synchronous load functions.

Global signals, general-purpose I/O (GPIO) pins, or any internal logic can drive the

clock and clear control signals of an ALM register.

GPIO pins or internal logic drives the clock enable signal.

For combinational functions, the registers are bypassed and the output of the look-up

table (LUT) drives directly to the outputs of an ALM.

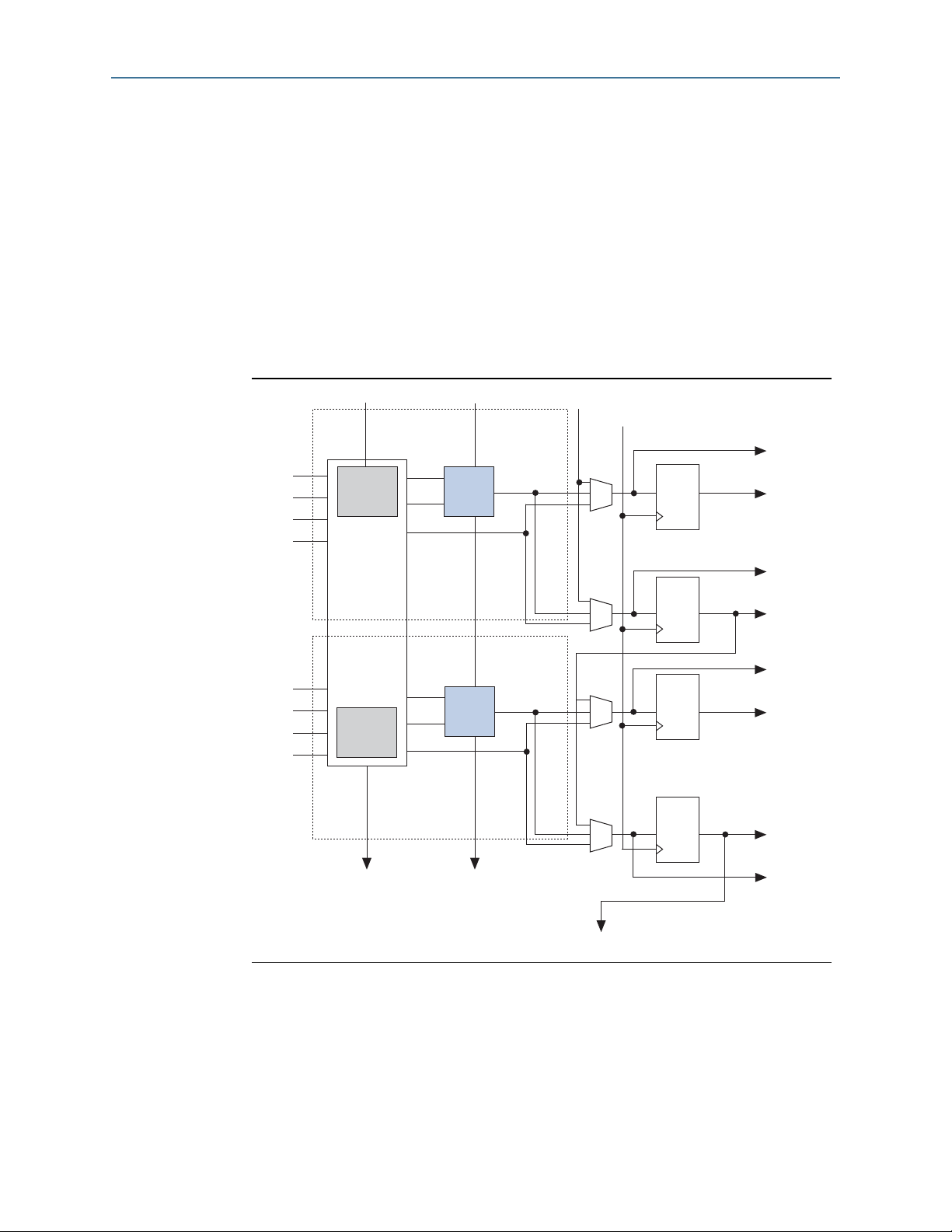

Figure 1–5 shows a high-level block diagram of the Arria V ALM.

Figure 1–5. High-Level Block Diagram of the Arria V ALM

dataf0

datae0

dataa

datab

datac

datad

datae1

dataf1

shared_arith_in

6-Input LUT

6-Input LUT

carry_in

adder0

adder1

Combinational/

Memory ALUT0

Combinational/

Memory ALUT1

reg_chain_in

labclk

DQ

reg0

DQ

reg1

DQ

reg2

DQ

reg3

To general or

local routing

To general or

local routing

To general or

local routing

To general or

local routing

To general or

local routing

To general or

local routing

To general or

local routing

shared_arith_out

carry_out

reg_chain_out

To general or

local routing

1 The Quartus II software automatically configures the ALMs for optimized

performance.

Arria V Device Handbook June 2012 Altera Corporation

Volume 1: Device Interfaces and Integration

Page 21

Chapter 1: Logic Array Blocks and Adaptive Logic Modules in Arria V Devices 1–7

LAB

ALM Outputs

The LUT, adder, or register output can drive the ALM outputs. There are two sets of

outputs—general routing outputs and register chain outputs.

For each set of output drivers, two ALM outputs can drive column, row, or direct link

routing connections, and one of these ALM outputs can also drive local interconnect

resources. The LUT or adder can drive one output while the register drives another

output.

Register packing improves device utilization by allowing unrelated register and

combinational logic to be packed into a single ALM. Another mechanism to improve

fitting is to allow the register output to feed back into the look-up table (LUT) of the

same ALM so that the register is packed with its own fan-out LUT. The ALM can also

drive out registered and unregistered versions of the LUT or adder output.

June 2012 Altera Corporation Arria V Device Handbook

Volume 1: Device Interfaces and Integration

Page 22

1–8 Chapter 1: Logic Array Blocks and Adaptive Logic Modules in Arria V Devices

LAB

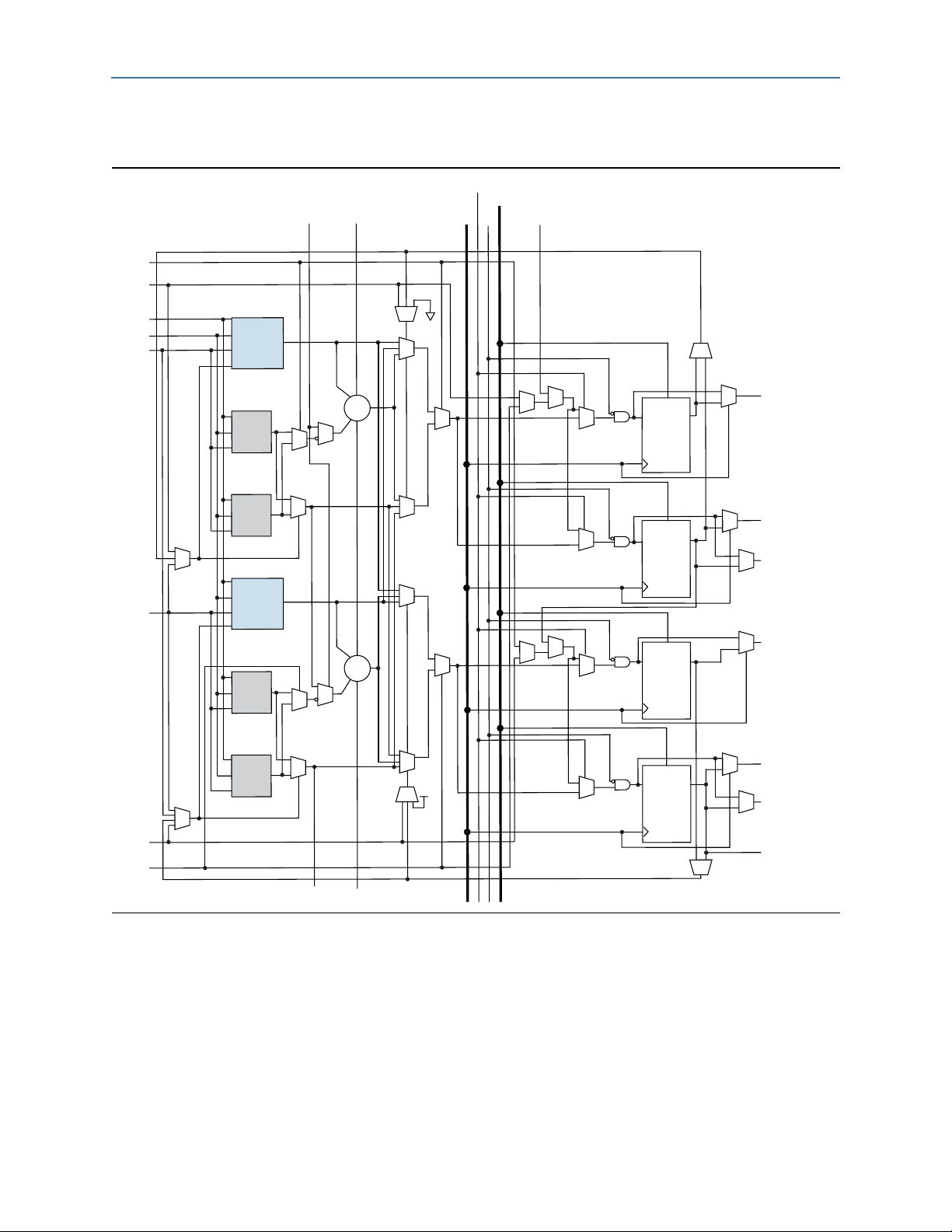

Figure 1–6 shows a detailed view of all the connections in an ALM.

Figure 1–6. ALM Connection Details for Arria V Devices

syncload

aclr[1:0]

dataf0

datae0

shared_arith_in

carry_in

clk[2:0]

sclr

reg_chain_in

dataa

datab

datac0

datac1

4-Input

LUT

3-Input

LUT

3-Input

LUT

4-Input

LUT

3-Input

LUT

3-Input

LUT

+

+

GND

VCC

CLR

Q

D

CLR

Q

D

direct link routing

row, column

direct link routing

local

interconnect

row, column

CLR

Q

D

row, column

direct link routing

row, column

CLR

Q

D

direct link routing

local

interconnect

datae1

reg_chain_out

dataf1

shared_arith_out

Arria V Device Handbook June 2012 Altera Corporation

Volume 1: Device Interfaces and Integration

carry_out

Page 23

Chapter 1: Logic Array Blocks and Adaptive Logic Modules in Arria V Devices 1–9

ALM Operating Modes

ALM Operating Modes

The Arria V ALM operates in any of the following modes:

■ Normal Mode

■ Extended LUT Mode

■ Arithmetic Mode

■ Shared Arithmetic Mode

Normal Mode

Up to eight data inputs from the LAB local interconnect are inputs to the

combinational logic. Normal mode allows two functions to be implemented in one

Arria V ALM, or a single function of up to six inputs.

The ALM can support certain combinations of completely independent functions and

various combinations of functions that have common inputs.

Extended LUT Mode

In this mode, if the 7-input function is unregistered, the unused eighth input is

available for register packing.

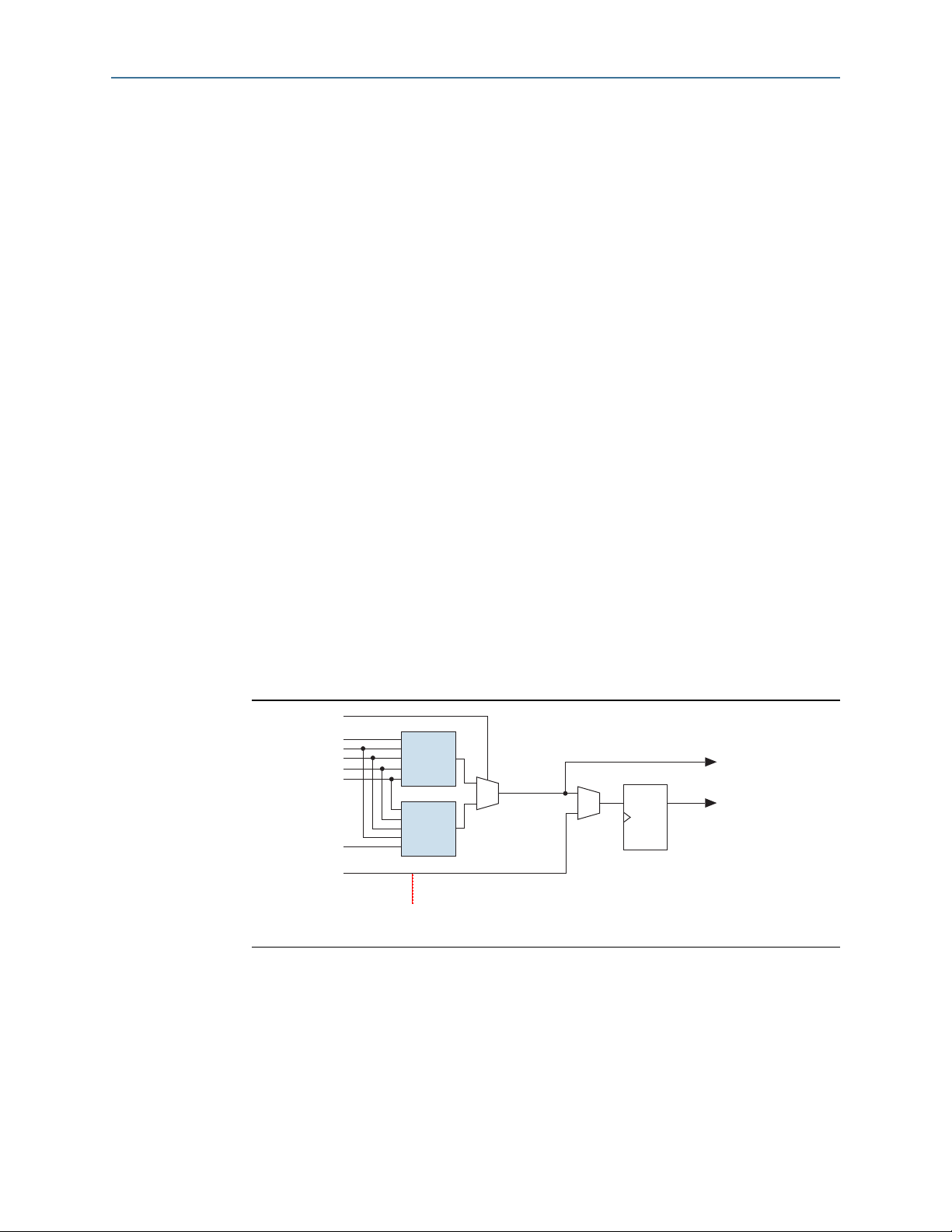

1 Functions that fit into the template, as shown in Figure 1–7, often appear in designs as

“if-else” statements in Verilog HDL or VHDL code.

Figure 1–7 shows the template of supported 7-input functions using extended LUT

mode.

Figure 1–7. Template for Supported 7-Input Functions in Extended LUT Mode in Arria V Devices

datae0

datac

dataa

datab

datad

dataf0

datae1

dataf1

5-Input

LUT

5-Input

LUT

This input is available

for register packing.

combout0

DQ

reg0

To gener al or

local routing

To gener al or

local routing

June 2012 Altera Corporation Arria V Device Handbook

Volume 1: Device Interfaces and Integration

Page 24

1–10 Chapter 1: Logic Array Blocks and Adaptive Logic Modules in Arria V Devices

ALM Operating Modes

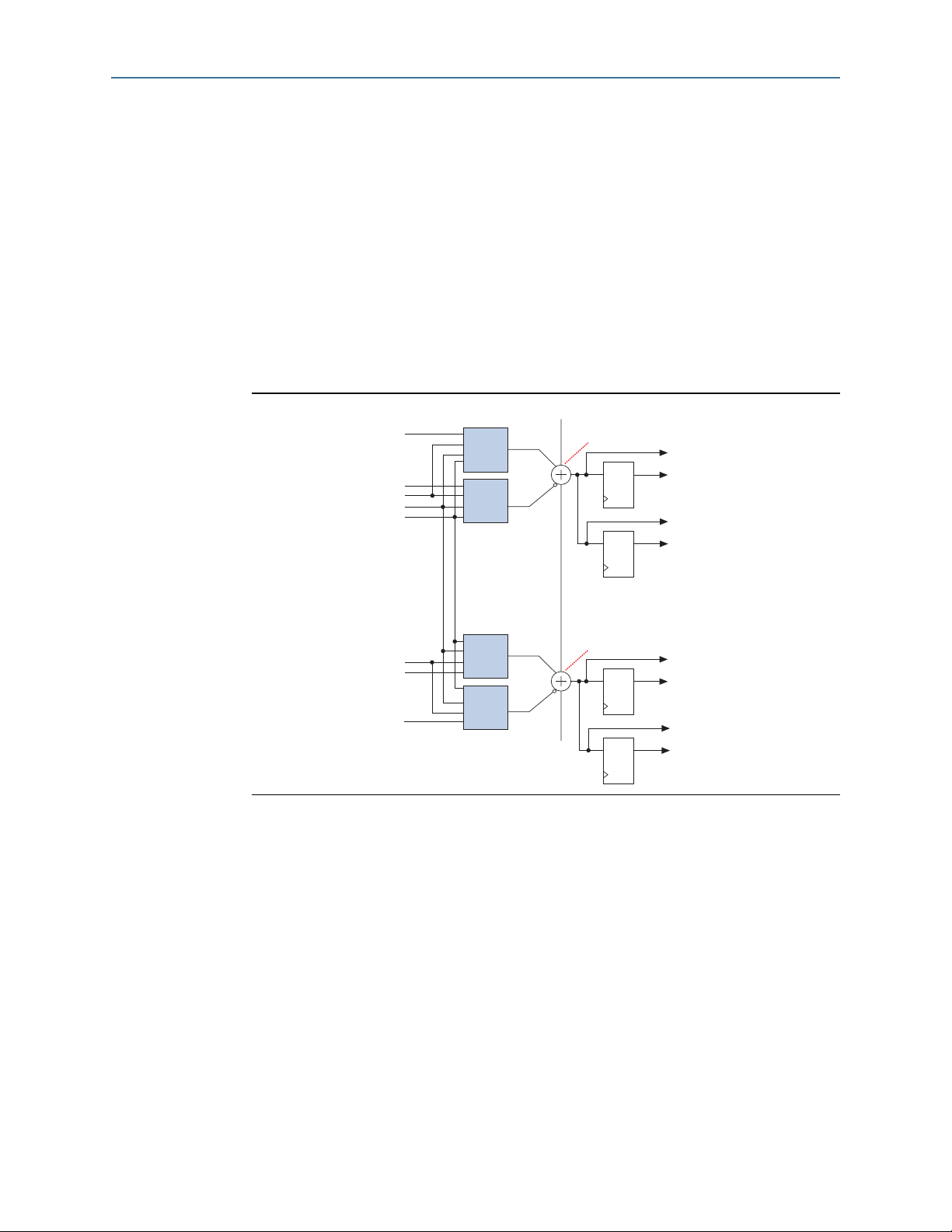

Arithmetic Mode

The ALM in arithmetic mode uses two sets of two 4-input LUTs along with two

dedicated full adders.

The dedicated adders allow the LUTs to perform pre-adder logic; therefore, each

adder can add the output of two 4-input functions.

The ALM supports simultaneous use of the adder’s carry output along with

combinational logic outputs. The adder output is ignored in this operation.

Using the adder with the combinational logic output provides resource savings of up

to 50% for functions that can use this mode.

Figure 1–8 shows an ALM in arithmetic mode.

Figure 1–8. ALM in Arithmetic Mode for Arria V Devices

carry_in

datae0

dataf0

datac

datab

dataa

4-Input

LUT

4-Input

LUT

adder0

DQ

reg0

DQ

reg1

To general or

local routing

To general or

local routing

To general or

local routing

To general or

local routing

datad

datae1

dataf1

4-Input

LUT

4-Input

LUT

carry_out

adder1

DQ

reg2

DQ

reg3

To general or

local routing

To general or

local routing

To general or

local routing

To general or

local routing

Arria V Device Handbook June 2012 Altera Corporation

Volume 1: Device Interfaces and Integration

Page 25

Chapter 1: Logic Array Blocks and Adaptive Logic Modules in Arria V Devices 1–11

ALM Operating Modes

Carry Chain

The carry chain provides a fast carry function between the dedicated adders in

arithmetic or shared arithmetic mode.

The two-bit carry select feature in Arria V devices halves the propagation delay of

carry chains within the ALM. Carry chains can begin in either the first ALM or the

fifth ALM in a LAB. The final carry-out signal is routed to an ALM, where it is fed to

local, row, or column interconnects.

To avoid routing congestion in one small area of the device when a high fan-in

arithmetic function is implemented, the LAB can support carry chains that only use

either the top half or bottom half of the LAB before connecting to the next LAB. This

leaves the other half of the ALMs in the LAB available for implementing narrower

fan-in functions in normal mode. Carry chains that use the top five ALMs in the first

LAB carry into the top half of the ALMs in the next LAB in the column. Carry chains

that use the bottom five ALMs in the first LAB carry into the bottom half of the ALMs

in the next LAB within the column. You can bypass the top-half of the LAB columns

and bottom-half of the MLAB columns.

The Quartus II Compiler creates carry chains longer than 20 ALMs (10 ALMs in

arithmetic or shared arithmetic mode) by linking LABs together automatically. For

enhanced fitting, a long carry chain runs vertically, allowing fast horizontal

connections to the TriMatrix memory and DSP blocks. A carry chain can continue as

far as a full column.

June 2012 Altera Corporation Arria V Device Handbook

Volume 1: Device Interfaces and Integration

Page 26

1–12 Chapter 1: Logic Array Blocks and Adaptive Logic Modules in Arria V Devices

ALM Operating Modes

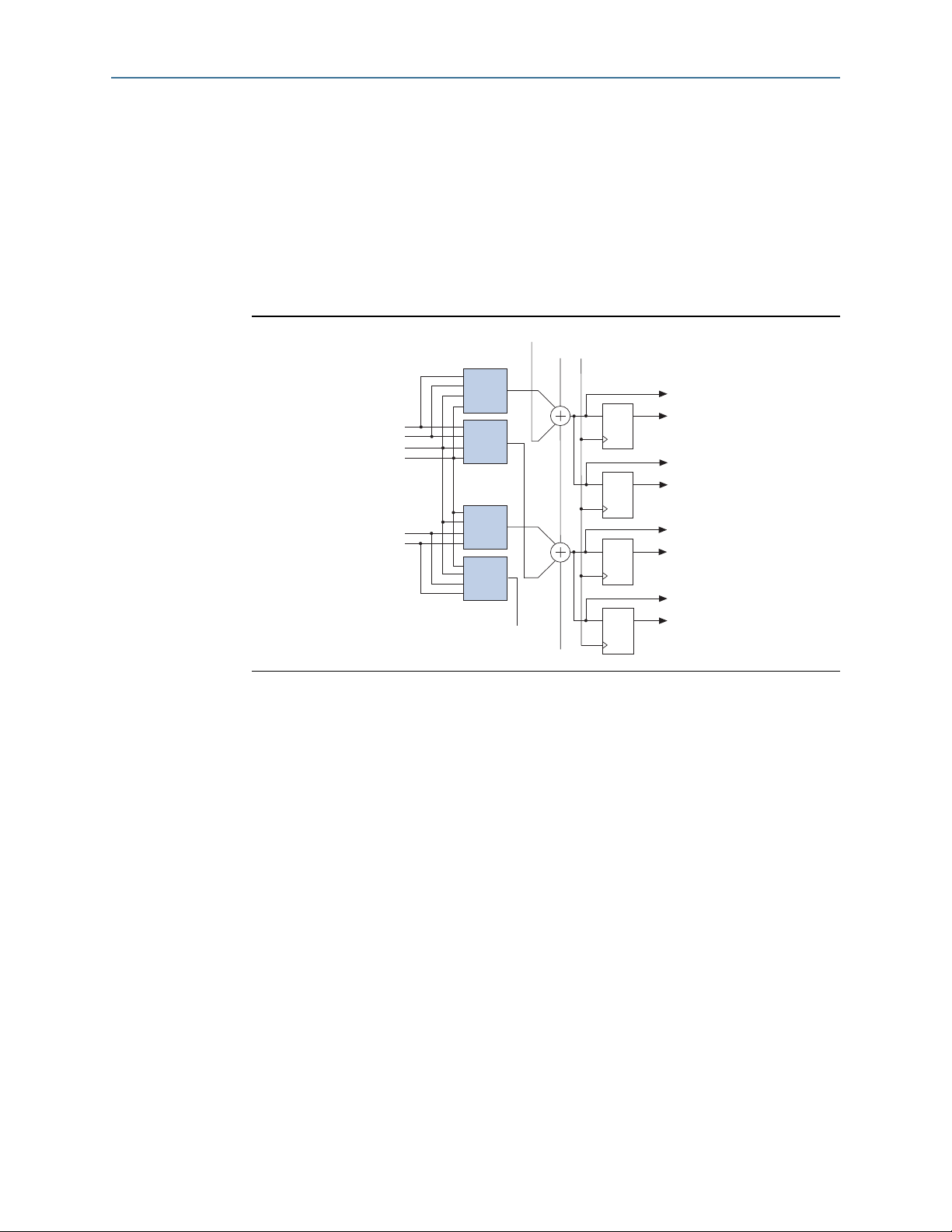

Shared Arithmetic Mode

The ALM in shared arithmetic mode can implement a 3-input add in the ALM.

This mode configures the ALM with four 4-input LUTs. Each LUT either computes

the sum of three inputs or the carry of three inputs. The output of the carry

computation is fed to the next adder using a dedicated connection called the shared

arithmetic chain.

Figure 1–9 shows the ALM using this feature.

Figure 1–9. ALM in Shared Arithmetic Mode for Arria V Devices

shared_arith_in

carry_in

labclk

datae0

datac

datab

dataa

datad

datae1

4-Input

LUT

4-Input

LUT

4-Input

LUT

4-Input

LUT

shared_arith_out

DQ

reg0

DQ

reg1

DQ

reg2

DQ

reg3

carry_out

To general or

local routing

To general or

local routing

To general or

local routing

To general or

local routing

To general or

local routing

To general or

local routing

To general or

local routing

To general or

local routing

Shared Arithmetic Chain

The shared arithmetic chain available in enhanced arithmetic mode allows the ALM

to implement a 3-input adder. This significantly reduces the resources necessary to

implement large adder trees or correlator functions.

Similar to carry chains, the top and bottom half of the shared arithmetic chains in

alternate LAB columns can be bypassed. This capability allows the shared arithmetic

chain to cascade through half of the ALMs in an LAB while leaving the other half

available for narrower fan-in functionality. In every LAB column is top-half

bypassable; while in MLAB columns are bottom-half bypassable.

The shared arithmetic chain can begin in either the first or sixth ALM in an LAB. The

Quartus II Compiler creates shared arithmetic chains longer than 20 ALMs (10 ALMs

in arithmetic or shared arithmetic mode) by linking LABs together automatically. To

enhanced fitting, a long shared arithmetic chain runs vertically, allowing fast

horizontal connections to the TriMatrix memory and DSP blocks. A shared arithmetic

chain can continue as far as a full column.

Arria V Device Handbook June 2012 Altera Corporation

Volume 1: Device Interfaces and Integration

Page 27

Chapter 1: Logic Array Blocks and Adaptive Logic Modules in Arria V Devices 1–13

Document Revision History

Document Revision History

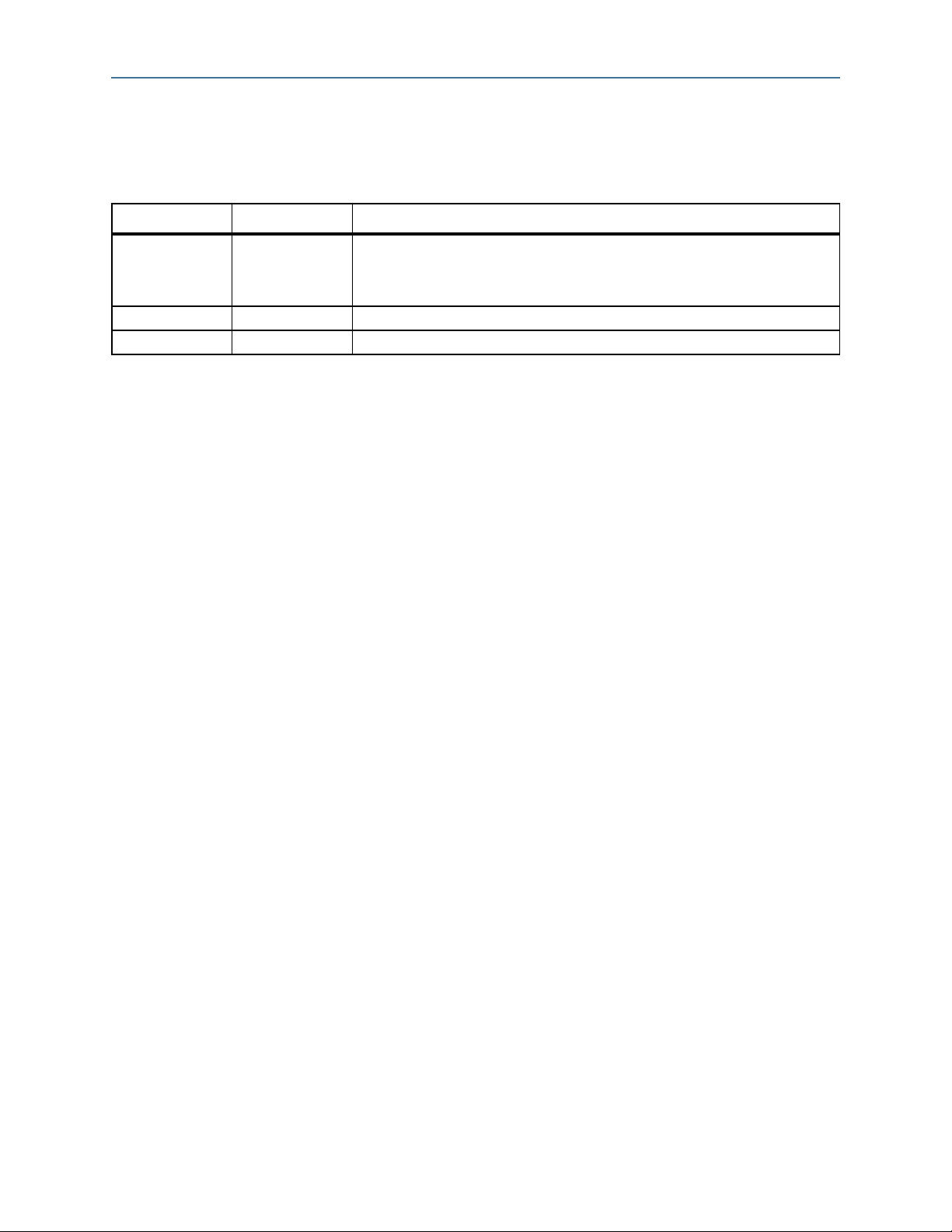

Table 1–1 lists the revision history for this chapter.

Table 1–1. Document Revision History

Date Version Changes

Updated for the Quartus II software v12.0 release:

June 2012 2.0

November 2011 1.1 Restructured chapter.

May 2011 1.0 Initial release.

■ Restructured chapter.

■ Updated Figure 1–6.

June 2012 Altera Corporation Arria V Device Handbook

Volume 1: Device Interfaces and Integration

Page 28

1–14 Chapter 1: Logic Array Blocks and Adaptive Logic Modules in Arria V Devices

Document Revision History

Arria V Device Handbook June 2012 Altera Corporation

Volume 1: Device Interfaces and Integration

Page 29

June 2012

AV-52002-2.0

AV-52002-2.0

2. Memory Blocks in Arria V Devices

This chapter describes the embedded memory blocks in Arria®V devices.

The memory blocks in Arria V devices provide different sizes of embedded SRAM to

fit your design requirements.

This chapter contains the following sections:

■ “Memory Types” on page 2–1

■ “Memory Features” on page 2–2

■ “Memory Modes” on page 2–3

■ “Mixed-Width Port Configurations” on page 2–4

■ “Clocking Modes” on page 2–5

■ “Parity Bit” on page 2–6

■ “Byte Enable” on page 2–6

Memory Types

f For information about the embedded memory capacity available in each Arria V

■ “Design Considerations” on page 2–8

The Arria V devices contain two types of memory blocks:

■ M10K blocks—10-kilobit (Kb) blocks of dedicated memory resources that you can

use to create designs with large memory configurations.

■ Memory logic array blocks (MLABs)—640-bit enhanced memory blocks that are

configured from dual-purpose logic array blocks (LABs). The MLABs are

optimized for implementation of shift registers for digital signal processing (DSP)

applications, wide shallow FIFO buffers, and filter delay lines. Each MLAB is

made up of ten adaptive logic modules (ALMs) that you can configure as ten

32 x 2 blocks, giving you one 32 x 20 simple dual-port SRAM block per MLAB.

device, refer to the Arria V Device Overview.

© 2012 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos

are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its

semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and

services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service

described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying

on any published information and before placing orders for products or services.

Arria V Device Handbook

Volume 1: Device Interfaces and Integration

June 2012

Feedback Subscribe

ISO

9001:2008

Registered

Page 30

2–2 Chapter 2: Memory Blocks in Arria V Devices

Memory Features

Memory Features

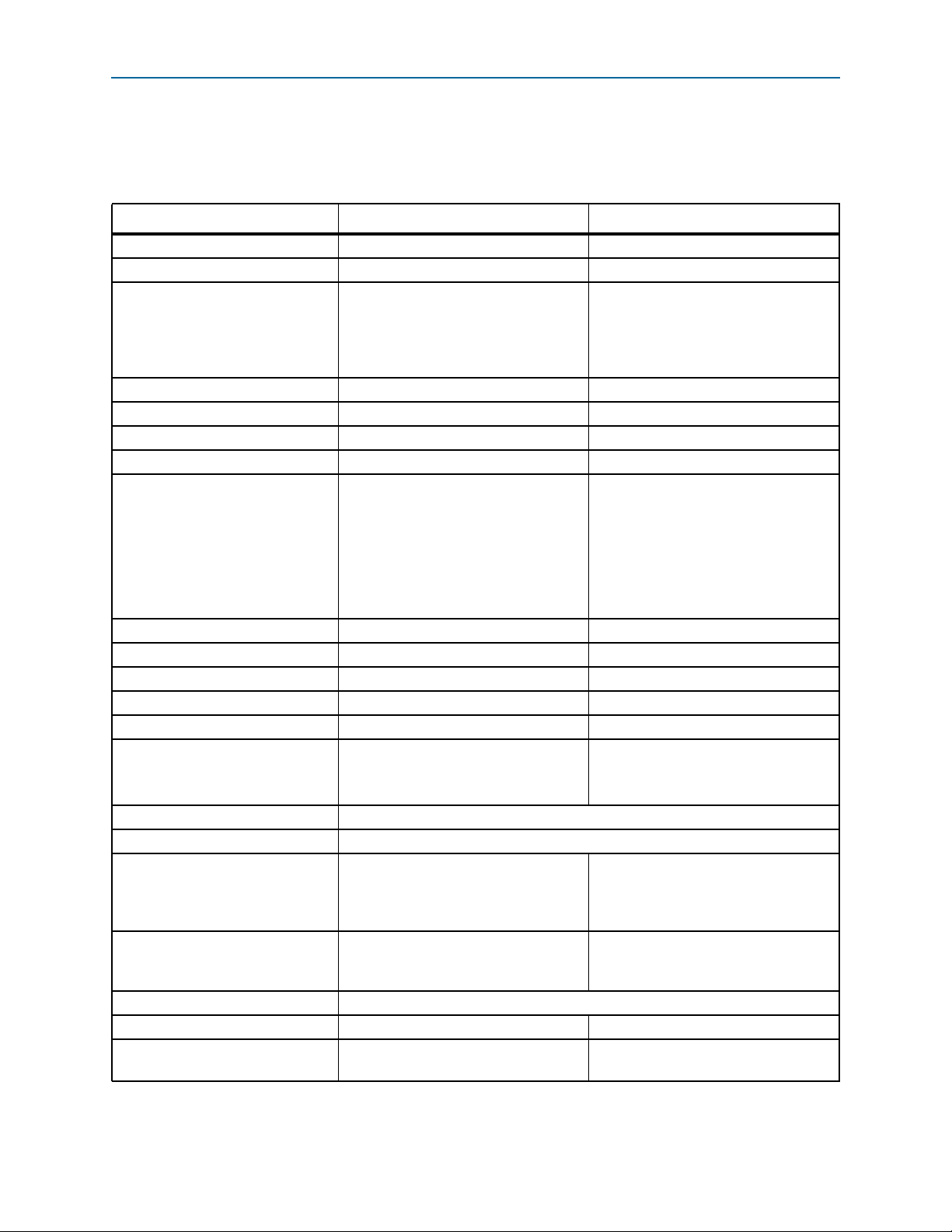

Table 2–1 summarizes the features supported by the memory blocks.

Table 2–1. Memory Features in Arria V Devices

Feature M10K MLAB

Maximum operating frequency 400 MHz 500 MHz

Total RAM bits (including parity bits) 10,240 640

256 x 32, 256 x 40,

512 x 16, 512 x 20,

Configuration (depth × width)

1K x 8, 1K x 10,

2K x 4, 2K x 5,

4K x 2, and 8K x 1

Parity bits Yes Yes

Byte enable Yes Yes

Packed mode Yes —

Address clock enable Yes Yes

■ Single-port memory

■ Simple dual-port memory

Memory modes

■ True dual-port memory

■ Embedded shift register

■ ROM

■ FIFO buffer

Simple dual-port mixed width Yes —

True dual-port mixed width Yes —

FIFO buffer mixed width Yes —

Memory Initialization File (.mif) Yes Yes

Mixed-clock mode Yes Yes

Power-up state Output ports are cleared.

Asynchronous clears Output registers

Write/Read operation triggering Rising clock edges

Output ports set to “new data” or

Same-port read-during-write

(The “don’t care” mode applies only for

“don’t care”.

the single-port RAM mode.)

Mixed-port read-during-write

Output ports set to “old data” or “don’t

care”.

ECC support Soft IP support using the Quartus

Fully synchronous memory Yes Yes

Asynchronous memory —

32 x 16, 32 x 18, and 32 x 20

■ Single-port memory

■ Simple dual-port memory

■ Embedded shift register

■ ROM

■ FIFO buffer

■ Registered output ports—Cleared.

■ Unregistered output ports—Read

memory contents.

Output ports set to “don’t care”.

Output ports set to “old data”, “new

data”, “don’t care”, or “constrained don’t

care”.

®

II software.

Only for flow-through read memory

operations.

Arria V Device Handbook June 2012 Altera Corporation

Volume 1: Device Interfaces and Integration

Page 31

Chapter 2: Memory Blocks in Arria V Devices 2–3

Memory Modes

Memory Modes

Table 2–2 lists and describes the memory modes that are supported in the Arria V

memory blocks.

c To avoid corrupting the memory contents, do not violate the setup or hold time on

any of the memory block input registers during read or write operations. This is

applicable if you use the memory blocks in single-port RAM, simple dual-port RAM,

true dual-port RAM, or ROM mode.

Table 2–2. Memory Modes Supported in the Memory Blocks

Memory Mode Description and Additional Information

You can perform only one read or one write operation at a time.

Use the read enable port to control the RAM output ports behavior during a write operation:

Single-port RAM

Simple dual-port

RAM

True dual-port RAM

Shift-register

ROM

FIFO

■ To retain the previous values that are held during the most recent active read enable—Create a

read-enable port and perform the write operation with the read enable port deasserted.

■ To show the new data being written, the old data at that address, or a “Don't Care” value when

read-during-write occurs at the same address location—Do not create a read-enable signal, or

activate the read enable during a write operation.

You can simultaneously perform one read and one write operations to different locations where the

write operation happens on port A and the read operation happens on port B.

You can perform any combination of two port operations: two reads, two writes, or one read and

one write at two different clock frequencies. This mode is available only for M10K blocks.

You can use the memory blocks as a shift-register block to save logic cells and routing resources.

This is useful in DSP applications that require local data storage such as finite impulse response

(FIR) filters, pseudo-random number generators, multi-channel filtering, and auto- and crosscorrelation functions. Traditionally, the local data storage is implemented with standard flip-flops

that exhaust many logic cells for large shift registers.

You can use the memory blocks as ROM.

■ Initialize the ROM contents of the memory blocks using a .mif or .hex.

■ The address lines of the ROM are registered on M10K blocks but can be unregistered on MLABs.

■ The outputs can be registered or unregistered.

■ The output registers can be asynchronously cleared.

■ The ROM read operation is identical to the read operation in the single-port RAM configuration.

You can use the memory blocks as FIFO buffers.

Use the SCFIFO and DCFIFO megafunctions to implement single- and dual-clock asynchronous FIFO

buffers in your design.

For designs with many small and shallow FIFO buffers, the MLABs are ideal for the FIFO mode.

However, the MLABs do not support mixed-width FIFO mode.

f For more information about each memory mode, refer to the Internal Memory (RAM

and ROM) User Guide.

f For more information about implementing the shift register mode, refer to the

RAM-Based Shift Register (ALTSHIFT_TAPS) Megafunction User Guide.

June 2012 Altera Corporation Arria V Device Handbook

Volume 1: Device Interfaces and Integration

Page 32

2–4 Chapter 2: Memory Blocks in Arria V Devices

Mixed-Width Port Configurations

f For more information about implementing FIFO buffers, refer to the SCFIFO and

DCFIFO Megafunctions User Guide.

Mixed-Width Port Configurations

The mixed-width port configuration is supported in the simple dual-port RAM and

true dual-port RAM memory modes.

f For more information about dual-port mixed width support, refer to the Internal

Memory (RAM and ROM) User Guide.

M10K Blocks Mixed-Width Configurations

Table 2–3 lists the mixed-width configurations of the M10K blocks in the simple dual-

port RAM mode.

Table 2–3. M10K Block Mixed-Width Configurations (Simple Dual-Port RAM Mode)

Write Port

Read Port

8K x 1

8K x 1 Yes Yes Yes — Yes — Yes — Yes —

4K x 2 Yes Yes Yes — Yes — Yes — Yes —

2K x 4 Yes Yes Yes — Yes — Yes — Yes —

2K x 5 — — — Yes — Yes — Yes — Yes

1K x 8 Yes Yes Yes — Yes — Yes — Yes —

1K x 10 — — — Yes — Yes — Yes — Yes

512 x 16 Yes Yes Yes — Yes — Yes — Yes —

512 x 20 — — — Yes — Yes — Yes — Yes

256 x 32 Yes Yes Yes — Yes — Yes — Yes —

256 x 40 — — — Yes — Yes — Yes — Yes

4K x 2

2K x 4

2K x 5

1K x 8

1K x 10

512 x 16

512 x 20

256 x 32

Table 2–4 lists the mixed-width configurations of the M10K blocks in true dual-port

mode.

Table 2–4. M10K Block Mixed-Width Configurations (True Dual-Port Mode) (Part 1 of 2)

Port A

Port B

8K x 1

8K x 1 Yes Yes Yes — Yes — Yes —

4K x 2 Yes Yes Yes — Yes — Yes —

2K x 4 Yes Yes Yes — Yes — Yes —

2K x 5 — — — Yes — Yes — Yes

1K x 8 Yes Yes Yes — Yes — Yes —

1K x 10 — — — Yes — Yes — Yes

4K x 2

2K x 4

2K x 5

1K x 8

1K x 10

512 x 16

256 x 40

512 x 20

Arria V Device Handbook June 2012 Altera Corporation

Volume 1: Device Interfaces and Integration

Page 33

Chapter 2: Memory Blocks in Arria V Devices 2–5

Clocking Modes

Table 2–4. M10K Block Mixed-Width Configurations (True Dual-Port Mode) (Part 2 of 2)

Port A

Port B

MLABs Mixed-Width Configurations

MLABs do not have native support for mixed-width operation. However, if you select

AUTO for your memory block type in the parameter editor, the Quartus II software

can implement mixed-width memories in MLABs by using more than one MLAB.

Clocking Modes

This section describes the clocking modes for the Arria V memory blocks.

c To avoid corrupting the memory contents, do not violate the setup or hold time on the

memory block address registers during read or write operations.

Clocking Modes for Each Memory Mode

Table 2–5 lists the memory blocks clocking modes supported in the Arria V devices

and the memory modes supported by each clocking mode.

Table 2–5. Memory Blocks Clocking Modes for Each Memory Mode

8K x 1

512 x 16 Yes Yes Yes — Yes — Yes —

512 x 20 — — — Yes — Yes — Yes

4K x 2

2K x 4

2K x 5

1K x 8

1K x 10

512 x 16

512 x 20

Memory Mode

Clocking Mode

Single-Port

Single clock mode Yes Yes Yes Yes Yes

Read/write clock mode — Yes — — Yes

Input/output clock mode Yes Yes Yes Yes —

Independent clock mode — — Yes Yes —

Simple

Dual-Port

True

Dual-Port

ROM FIFO

f For more information about each clocking mode, refer to the Internal Memory (RAM

and ROM) User Guide.

Asynchronous Clears

In all clocking modes, asynchronous clears are available only for output latches and

output registers. For the independent clock mode, this is applicable on both ports.

June 2012 Altera Corporation Arria V Device Handbook

Volume 1: Device Interfaces and Integration

Page 34

2–6 Chapter 2: Memory Blocks in Arria V Devices

Parity Bit

Output Read Data in Simultaneous Read/Write

If you perform a simultaneous read/write to the same address location using the

read/write clock mode, the output read data is unknown. If you require the output

read data to be a known value, use single-clock or input/output clock mode and

select the appropriate read-during-write behavior in the MegaWizard Plug-In

Manager.

Independent Clock Enables

Independent clock enables are supported in the following clocking modes:

■ Read/write clock mode—supported for both the read and write clocks.

■ Independent clock mode—supported for the registers of both ports.

To save power, you can control the shut down of a particular register using the clock

enables. For more information, refer to “Power Management” on page 2–13.

Parity Bit

Table 2–6 describes the parity bit support for the memory blocks.

Byte Enable

Table 2–6. Parity Bit Support for the Memory Blocks

M10K MLAB

■ The parity bit is the fifth bit associated with

each 4 data bits in data widths of 5, 10, 20,

and 40 (bits 4, 9, 14, 19, 24, 29, 34, and 39).

■ In non-parity data widths, the parity bits are

skipped during read or write operations.

■ Parity function is not performed on the parity

■ The parity bit is the ninth bit associated with

each byte.

■ The ninth bit can store a parity bit or serve as

an additional bit.

■ Parity function is not performed on the parity

bit.

bit.

The memory blocks support byte enable controls:

■ The byte enable controls mask the input data so that only specific bytes of data are

written. The unwritten bytes retain the values written previously.

■ The write enable (

control the write operations on the RAM blocks. By default, the

high (enabled) and only the

■ The byte enable registers do not have a

■ If you are using parity bits, on the M10K blocks, the byte enable function controls

wren

) signal, together with the byte enable (

wren

signal controls the writing.

clear

port.

byteena

byteena

) signal,

signal is

8 data bits and 2 parity bits; on the MLABs, the byte enable function controls all 10

bits in the widest mode.

■ The MSB and LSB of the

byteena

signal correspond to the MSB and LSB of the data

bus, respectively.

■ The byte enables are active high.

Arria V Device Handbook June 2012 Altera Corporation

Volume 1: Device Interfaces and Integration

Page 35

Chapter 2: Memory Blocks in Arria V Devices 2–7

Byte Enable

byteena Controls

Table 2–7 lists the

Table 2–7. byteena Controls in x20 Data Width

Table 2–8 lists the

Table 2–8. byteena Controls in x40 Data Width

byteena[3:0] Data Bits Written

1111 (default)

1000

0100 —

0010 — —

0001 — — —

Data Byte Output

byteena

byteena[1:0] Data Bits Written

11 (default)

10

01 —

byteena

controls in the x20 data widths.

[19:10] [9:0]

[19:10]

controls in the x40 data widths.

[39:30] [29:20] [19:10] [9:0]

[39:30]

———

[29:20]

——

[19:10]

—

[9:0]

—

[9:0]

In M10K blocks, the corresponding masked data byte output appears as a “don’t care”

value.

In MLABs, when a byte-enable bit is deasserted during a write cycle, the

corresponding data byte output appears as either a “don’t care” value or the current

data at that location. You can control the output value for the masked byte in MLABs

using the Quartus II software.

June 2012 Altera Corporation Arria V Device Handbook

Volume 1: Device Interfaces and Integration

Page 36

2–8 Chapter 2: Memory Blocks in Arria V Devices

Design Considerations

RAM Blocks Operations

Figure 2–1 shows how the

RAM blocks.

Figure 2–1. Byte Enable Functional Waveform

inclock

wren

address

data

byteena

contents at a0

contents at a1

contents at a2

contents at a3

contents at a4

don’t care: q (asynch)

an a0 a1 a2 a3 a4 a0

XXXXXXXX XXXXXXXXABCDEF12

XXXX XXXX1000 0100 0010 0001 1111

FFFFFFFF

FFFFFFFF

FFFFFFFF

ABXXXXXX XXCDXXXX XXXXEFXX XXXXXX12 ABCDEF12

(1)

FFFFFFFF

wren

FFFFFFFF

and

byteena

signals control the operations of the

ABFFFFFF

FFCDFFFF

FFFFEFFF

FFFFFF12

ABCDEF12

ABFFFFFFdoutn

current data: q (asynch)

Note to Figure 2–1:

(1) For the M10K blocks, the write-masked data byte output appears as a “don’t care” value because the “current data” value is not supported.

doutn

ABFFFFFF

FFCDFFFF

FFFFEFFF

FFFFFF12

ABFFFFFFABCDEF12

Design Considerations

To ensure the success of your designs using the memory blocks in Arria V devices,

take into consideration the following guidelines when you are designing with the

memory blocks.

Memory Block Selection

The Quartus II software automatically partitions the user-defined memory into the

memory blocks based on the speed and size constraints placed on your design. For

example, the Quartus II software may spread out the memory across multiple

available memory blocks to increase the performance of the design.

To assign the memory to a specific block size manually, use the RAM megafunction in

the MegaWizard™Plug-In Manager.

For the MLABs, you can implement single-port SRAM through emulation using the

Quartus II software. Emulation results in minimal additional use of logic resources.

Arria V Device Handbook June 2012 Altera Corporation

Volume 1: Device Interfaces and Integration

Page 37

Chapter 2: Memory Blocks in Arria V Devices 2–9

Design Considerations

Because of the dual-purpose architecture of the MLAB, only data input registers and

output registers are available in the block. The MLABs gain read address registers

from the ALMs. However, the write address and read data registers are internal to the

MLABs.

Conflict Resolution

In the true dual-port RAM mode, you can perform two write operations to the same

memory location. However, the memory blocks do not have internal conflict

resolution circuitry. To avoid unknown data being written to the address, implement