Page 1

Arria V Hard Processor System Technical

Reference Manual

Subscribe

Send Feedback

Last updated for Quartus Prime Design Suite: 20.1

av_5v4

2020.09.03

101 Innovation Drive

San Jose, CA 95134

www.altera.com

Page 2

TOC-2

Contents

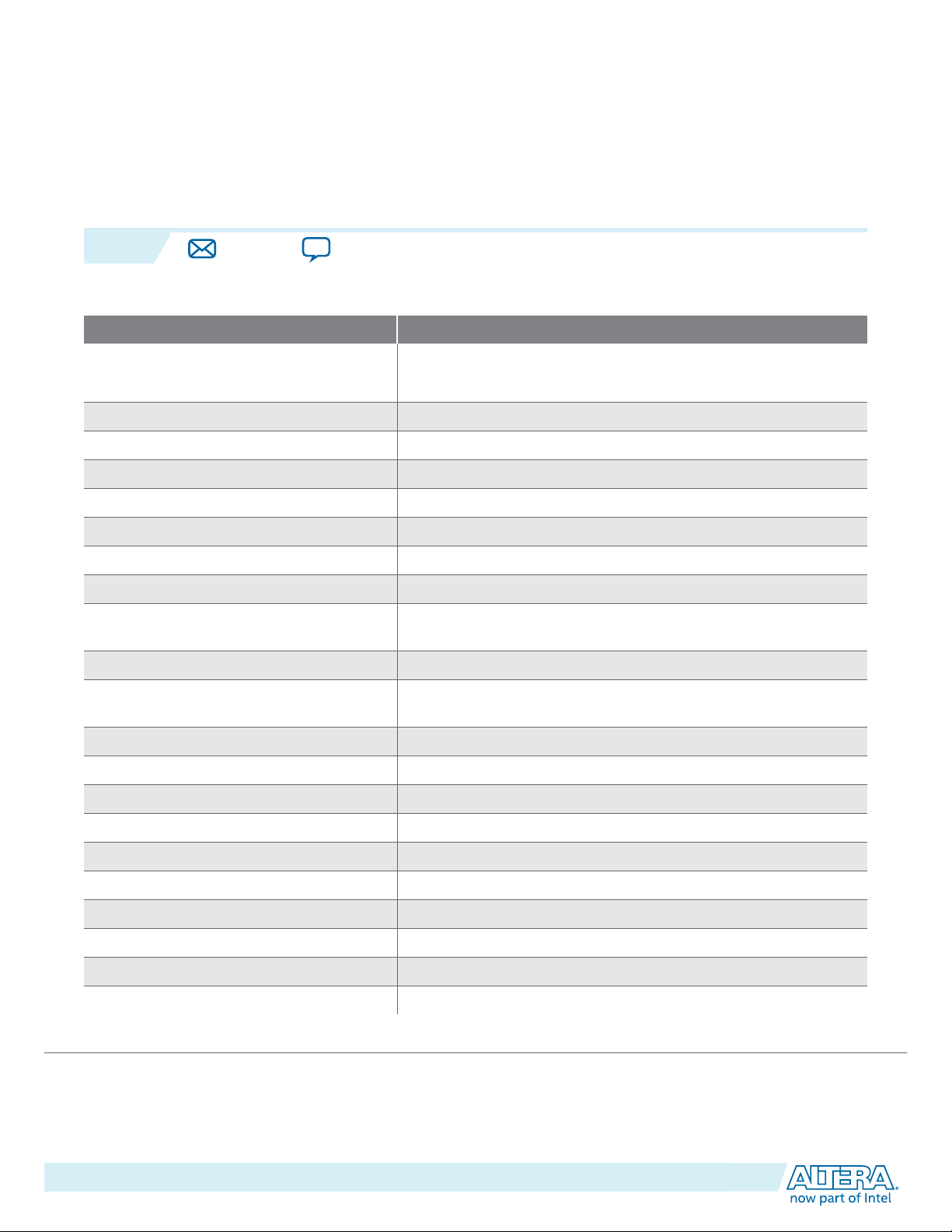

Arria® V Hard Processor System Technical Reference Manual Revision

History............................................................................................................. 1-1

Introduction to the Hard Processor System....................................................... 2-1

Features of the HPS......................................................................................................................................2-3

HPS Block Diagram and System Integration........................................................................................... 2-4

HPS Block Diagram.........................................................................................................................2-4

Cortex-A9 MPCore..........................................................................................................................2-5

HPS Interfaces.................................................................................................................................. 2-5

System Interconnect.........................................................................................................................2-6

On-Chip Memory............................................................................................................................ 2-7

Flash Memory Controllers..............................................................................................................2-8

Support Peripherals..........................................................................................................................2-9

Interface Peripherals......................................................................................................................2-11

CoreSight Debug and Trace..........................................................................................................2-14

Endian Support.......................................................................................................................................... 2-14

Introduction to the Hard Processor System Address Map...................................................................2-15

HPS Address Spaces.......................................................................................................................2-15

HPS Peripheral Region Address Map..........................................................................................2-17

Clock Manager.....................................................................................................3-1

Features of the Clock Manager...................................................................................................................3-1

Clock Manager Block Diagram and System Integration........................................................................ 3-2

L4 Peripheral Clocks........................................................................................................................3-3

Functional Description of the Clock Manager.........................................................................................3-5

Clock Manager Building Blocks.....................................................................................................3-5

Hardware-Managed and Soware-Managed Clocks...................................................................3-7

Clock Groups....................................................................................................................................3-7

Resets............................................................................................................................................... 3-17

Safe Mode........................................................................................................................................3-17

Interrupts.........................................................................................................................................3-18

Clock Usage By Module................................................................................................................ 3-18

Clock Manager Address Map and Register Denitions........................................................................3-23

Reset Manager..................................................................................................... 4-1

Reset Manager Block Diagram and System Integration.........................................................................4-2

HPS External Reset Sources............................................................................................................4-3

Reset Controller................................................................................................................................4-4

Module Reset Signals.......................................................................................................................4-5

Slave Interface and Status Register.............................................................................................. 4-10

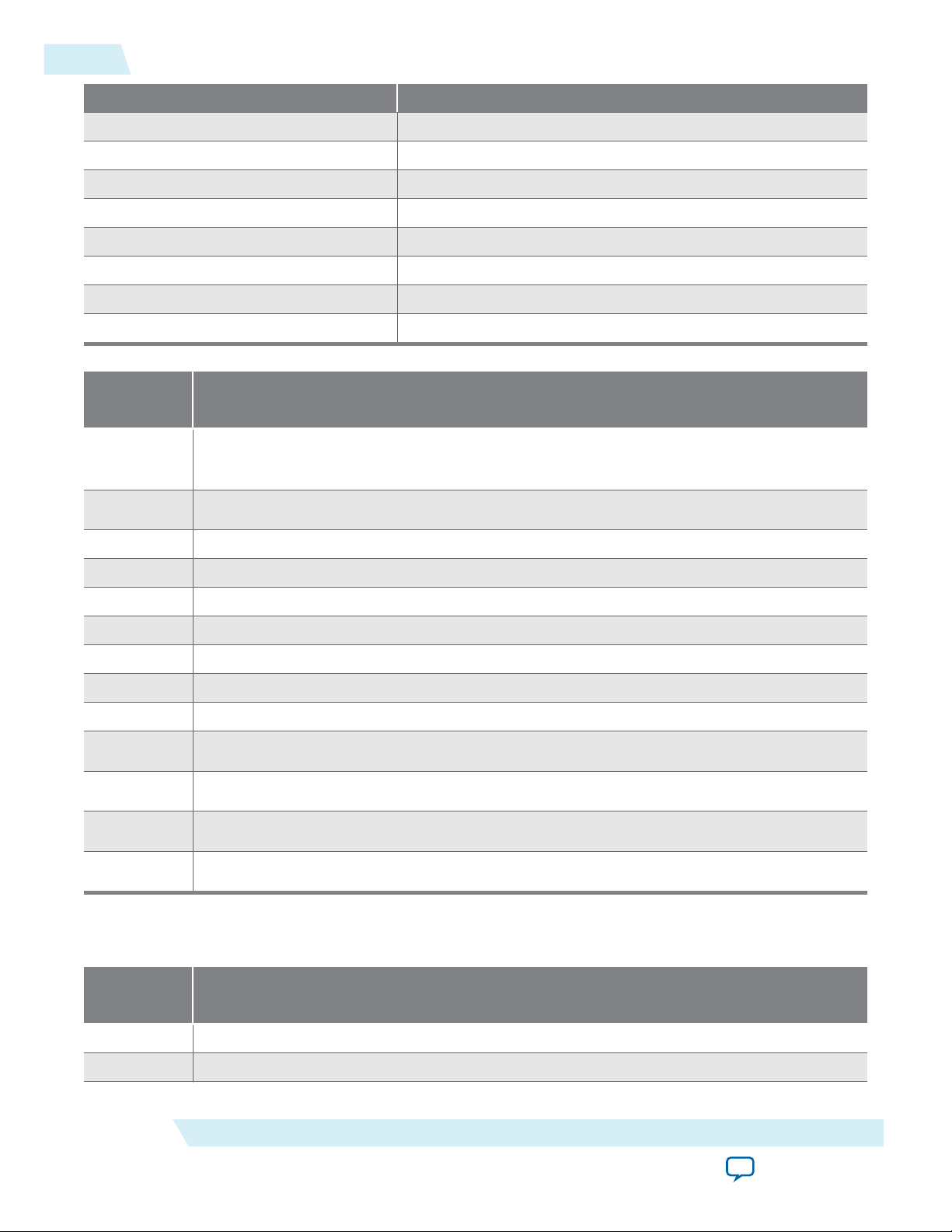

Altera Corporation

Page 3

TOC-3

Functional Description of the Reset Manager....................................................................................... 4-10

Reset Sequencing............................................................................................................................4-11

Reset Pins........................................................................................................................................ 4-15

Reset Eects.................................................................................................................................... 4-15

Altering Warm Reset System Response...................................................................................... 4-15

Reset Handshaking........................................................................................................................ 4-16

Reset Manager Address Map and Register Denitions.........................................................................4-16

FPGA Manager.................................................................................................... 5-1

Features of the FPGA Manager..................................................................................................................5-1

FPGA Manager Block Diagram and System Integration........................................................................5-2

Functional Description of the FPGA Manager........................................................................................5-3

FPGA Manager Building Blocks....................................................................................................5-3

FPGA Conguration....................................................................................................................... 5-4

FPGA Status......................................................................................................................................5-8

Error Message Extraction................................................................................................................5-8

Boot Handshake...............................................................................................................................5-8

General Purpose I/O........................................................................................................................5-9

Clock..................................................................................................................................................5-9

Reset...................................................................................................................................................5-9

FPGA Manager Address Map and Register Denitions.........................................................................5-9

System Manager...................................................................................................6-1

Features of the System Manager.................................................................................................................6-1

System Manager Block Diagram and System Integration......................................................................6-2

Functional Description of the System Manager.......................................................................................6-3

Boot Conguration and System Information.............................................................................. 6-3

Additional Module Control............................................................................................................6-3

Boot ROM Code...............................................................................................................................6-6

FPGA Interface Enables.................................................................................................................. 6-7

ECC and Parity Control..................................................................................................................6-8

Preloader Hando Information..................................................................................................... 6-8

Clocks................................................................................................................................................ 6-8

Resets................................................................................................................................................. 6-8

System Manager Address Map and Register Denitions........................................................................6-9

Scan Manager.......................................................................................................7-1

Features of the Scan Manager.....................................................................................................................7-1

Scan Manager Block Diagram and System Integration.......................................................................... 7-2

Arm JTAG-AP Signal Use in the Scan Manager..........................................................................7-2

Arm JTAG-AP Scan Chains............................................................................................................7-3

Functional Description of the Scan Manager...........................................................................................7-5

Conguring HPS I/O Scan Chains................................................................................................7-5

Communicating with the JTAG TAP Controller.........................................................................7-6

JTAG-AP FIFO Buer Access and Byte Command Protocol.................................................... 7-6

Clocks................................................................................................................................................ 7-7

Altera Corporation

Page 4

TOC-4

Resets................................................................................................................................................. 7-8

Scan Manager Address Map and Register Denitions............................................................................7-8

JTAG-AP Register Name Cross Reference Table......................................................................... 7-8

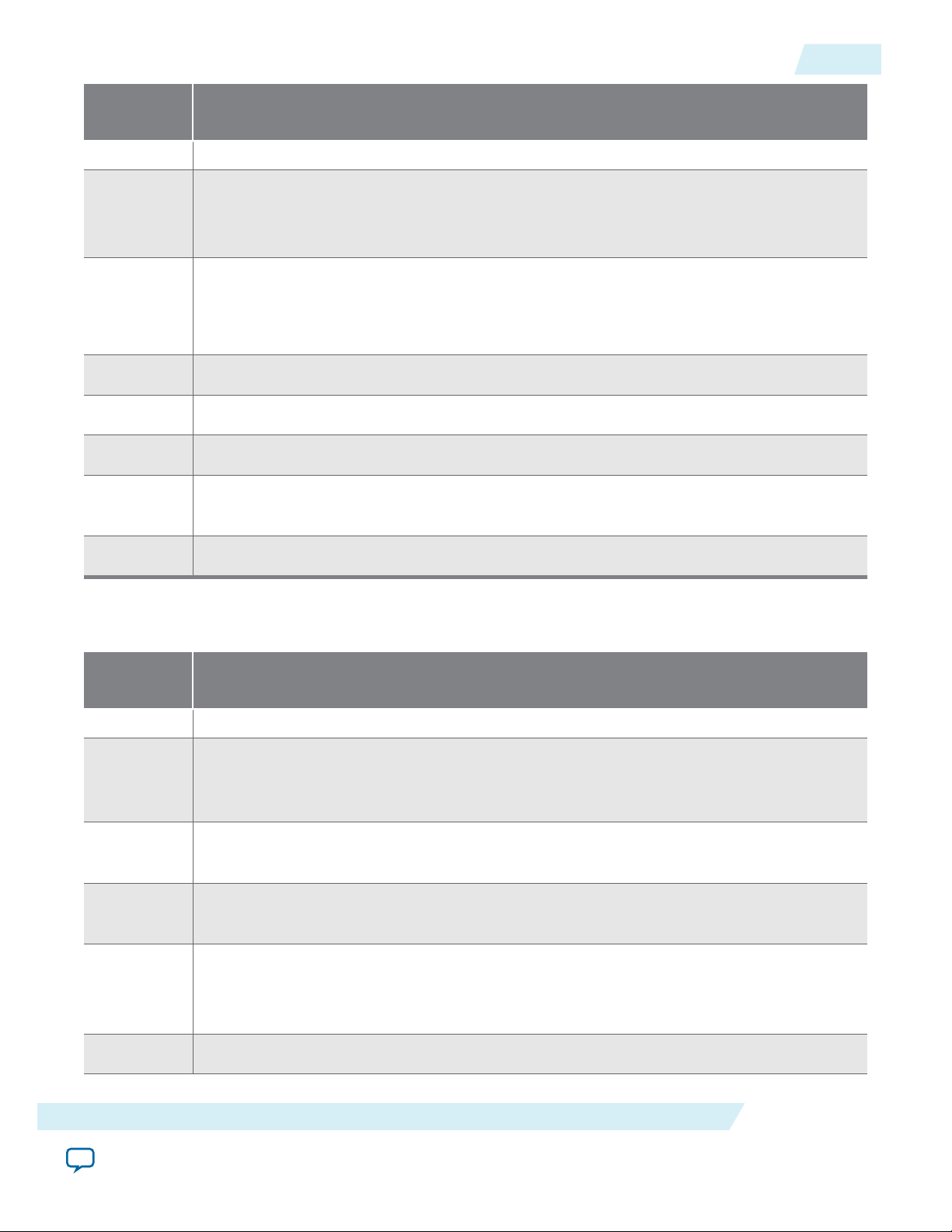

System Interconnect............................................................................................ 8-1

Features of the System Interconnect..........................................................................................................8-1

System Interconnect Block Diagram and System Integration............................................................... 8-2

Interconnect Block Diagram.......................................................................................................... 8-2

System Interconnect Architecture..................................................................................................8-2

Main Connectivity Matrix.............................................................................................................. 8-3

Functional Description of the Interconnect.............................................................................................8-4

Master to Slave Connectivity Matrix.............................................................................................8-4

System Interconnect Address Spaces.............................................................................................8-5

Master Caching and Buering Overrides...................................................................................8-13

Security............................................................................................................................................8-13

Conguring the Quality of Service Logic................................................................................... 8-14

Cyclic Dependency Avoidance Schemes.....................................................................................8-14

System Interconnect Master Properties...................................................................................... 8-15

Interconnect Slave Properties.......................................................................................................8-17

Upsizing Data Width Function....................................................................................................8-19

Downsizing Data Width Function...............................................................................................8-20

Lock Support...................................................................................................................................8-21

FIFO Buers and Clock Crossing................................................................................................8-21

System Interconnect Resets.......................................................................................................... 8-22

System Interconnect Address Map and Register Denitions...............................................................8-22

HPS-FPGA Bridges............................................................................................. 9-1

Features of the HPS-FPGA Bridges...........................................................................................................9-1

HPS-FPGA Bridges Block Diagram and System Integration.................................................................9-3

Functional Description of the HPS-FPGA Bridges.................................................................................9-4

e Global Programmers View......................................................................................................9-4

Functional Description of the FPGA-to-HPS Bridge..................................................................9-4

Functional Description of the HPS-to-FPGA Bridge..................................................................9-7

Functional Description of the Lightweight HPS-to-FPGA Bridge..........................................9-10

Clocks and Resets...........................................................................................................................9-14

Data Width Sizing..........................................................................................................................9-15

HPS-FPGA Bridges Address Map and Register Denitions................................................................9-16

Cortex-A9 Microprocessor Unit Subsystem..................................................... 10-1

Features of the Cortex-A9 MPU Subsystem...........................................................................................10-1

Cortex-A9 MPU Subsystem Block Diagram and System Integration................................................10-2

Cortex-A9 MPU Subsystem with System Interconnect............................................................10-2

Cortex-A9 MPU Subsystem Internals.........................................................................................10-3

Cortex-A9 MPCore....................................................................................................................................10-4

Functional Description..................................................................................................................10-4

Implementation Details.................................................................................................................10-5

Altera Corporation

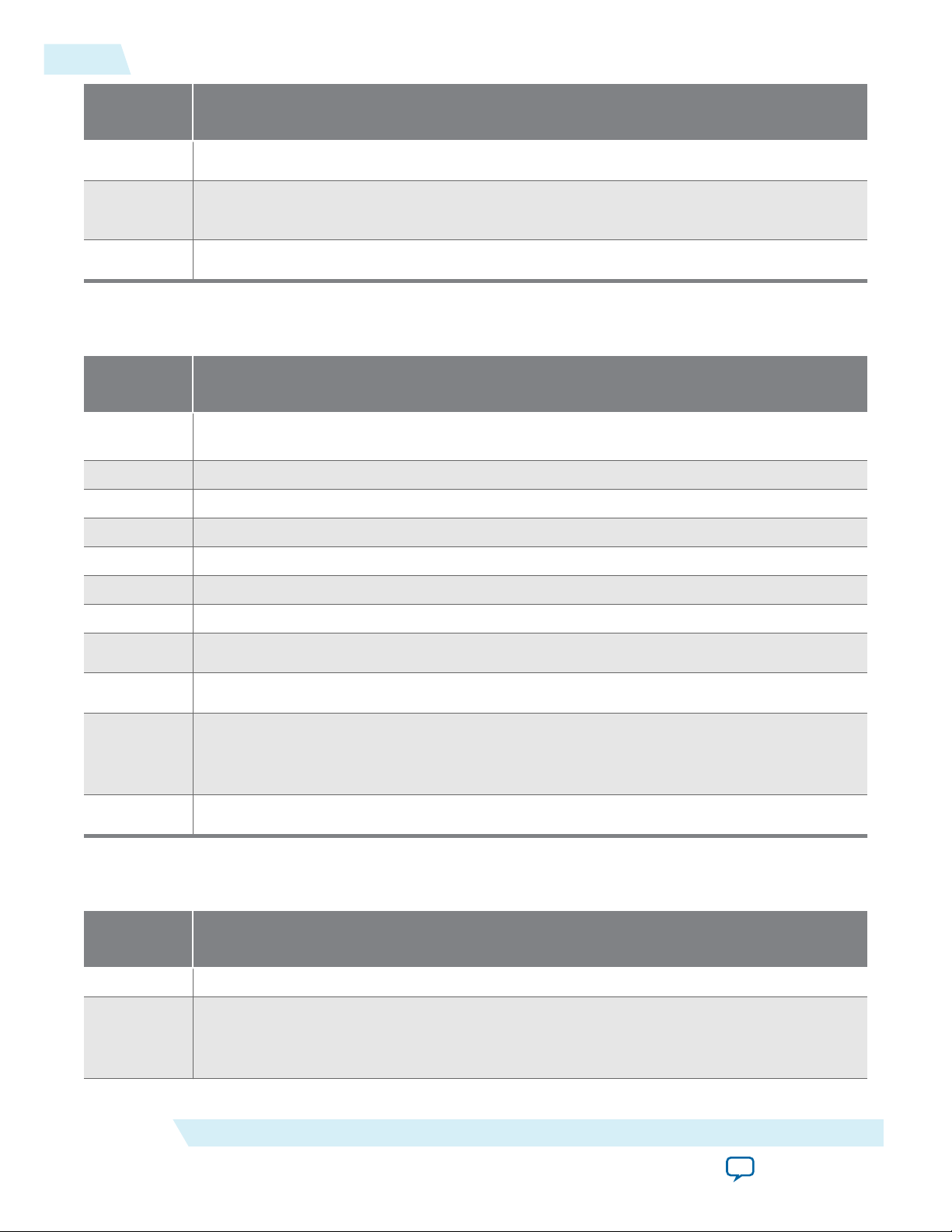

Page 5

TOC-5

Cortex-A9 Processor..................................................................................................................... 10-6

Interactive Debugging Features....................................................................................................10-7

L1 Caches........................................................................................................................................ 10-7

Preload Engine............................................................................................................................... 10-7

Floating Point Unit.........................................................................................................................10-8

NEON Multimedia Processing Engine....................................................................................... 10-8

Memory Management Unit..........................................................................................................10-9

Performance Monitoring Unit....................................................................................................10-12

Arm Cortex-A9 MPCore Timers...............................................................................................10-12

Generic Interrupt Controller......................................................................................................10-13

Global Timer.................................................................................................................................10-24

Snoop Control Unit..................................................................................................................... 10-25

Accelerator Coherency Port....................................................................................................... 10-27

ACP ID Mapper.......................................................................................................................................10-31

Functional Description............................................................................................................... 10-32

Implementation Details...............................................................................................................10-32

ACP ID Mapper Address Map and Register Denitions........................................................10-38

L2 Cache....................................................................................................................................................10-38

Functional Description............................................................................................................... 10-38

CPU Prefetch............................................................................................................................................10-45

Debugging Modules.................................................................................................................................10-45

Program Trace..............................................................................................................................10-45

Event Trace....................................................................................................................................10-46

Cross-Triggering.......................................................................................................................... 10-47

Clocks........................................................................................................................................................ 10-47

Cortex-A9 MPU Subsystem Register Implementation.......................................................................10-47

Cortex-A9 MPU Subsystem Address Map...............................................................................10-48

L2 Cache Controller Address Map............................................................................................ 10-49

CoreSight Debug and Trace...............................................................................11-1

Features of CoreSight Debug and Trace..................................................................................................11-2

Arm CoreSight Documentation...............................................................................................................11-2

CoreSight Debug and Trace Block Diagram and System Integration.................................................11-3

Functional Description of CoreSight Debug and Trace........................................................................11-4

Debug Access Port......................................................................................................................... 11-4

System Trace Macrocell.................................................................................................................11-4

Trace Funnel................................................................................................................................... 11-5

CoreSight Trace Memory Controller...........................................................................................11-5

AMBA Trace Bus Replicator.........................................................................................................11-6

Trace Port Interface Unit...............................................................................................................11-6

Embedded Cross Trigger System.................................................................................................11-6

Program Trace Macrocell............................................................................................................11-11

HPS Debug APB Interface..........................................................................................................11-11

FPGA Interface.............................................................................................................................11-11

Debug Clocks................................................................................................................................11-14

Debug Resets................................................................................................................................ 11-15

CoreSight Debug and Trace Programming Model..............................................................................11-16

Coresight Component Address..................................................................................................11-17

Altera Corporation

Page 6

TOC-6

STM Channels..............................................................................................................................11-18

CTI Trigger Connections to Outside the Debug System........................................................11-19

Conguring Embedded Cross-Trigger Connections..............................................................11-21

CoreSight Debug and Trace Address Map and Register Denitions................................................11-22

SDRAM Controller Subsystem..........................................................................12-1

Features of the SDRAM Controller Subsystem......................................................................................12-1

SDRAM Controller Subsystem Block Diagram.....................................................................................12-2

SDRAM Controller Memory Options.....................................................................................................12-3

SDRAM Controller Subsystem Interfaces.............................................................................................. 12-4

MPU Subsystem Interface.............................................................................................................12-4

L3 Interconnect Interface..............................................................................................................12-4

CSR Interface..................................................................................................................................12-5

FPGA-to-HPS SDRAM Interface.................................................................................................12-5

Memory Controller Architecture.............................................................................................................12-6

Multi-Port Front End.....................................................................................................................12-7

Single-Port Controller................................................................................................................... 12-8

Functional Description of the SDRAM Controller Subsystem..........................................................12-10

MPFE Operation Ordering.........................................................................................................12-10

MPFE Multi-Port Arbitration....................................................................................................12-10

MPFE SDRAM Burst Scheduling..............................................................................................12-13

Single-Port Controller Operation..............................................................................................12-14

SDRAM Power Management.................................................................................................................12-24

DDR PHY................................................................................................................................................. 12-25

DDR Calibration..........................................................................................................................12-25

Clocks........................................................................................................................................................ 12-25

Resets......................................................................................................................................................... 12-26

Taking the SDRAM Controller Subsystem Out of Reset .......................................................12-26

Port Mappings..........................................................................................................................................12-26

Initialization..............................................................................................................................................12-27

FPGA-to-SDRAM Protocol Details...........................................................................................12-28

SDRAM Controller Subsystem Programming Model........................................................................ 12-32

HPS Memory Interface Architecture.........................................................................................12-32

HPS Memory Interface Conguration......................................................................................12-32

HPS Memory Interface Simulation........................................................................................... 12-33

Generating a Preloader Image for HPS with EMIF.................................................................12-34

Debugging HPS SDRAM in the Preloader...........................................................................................12-35

Enabling UART or Semihosting Printout.................................................................................12-35

Enabling Simple Memory Test...................................................................................................12-36

Enabling the Debug Report........................................................................................................12-37

Writing a Predened Data Pattern to SDRAM in the Preloader...........................................12-40

SDRAM Controller Address Map and Register Denitions.............................................................. 12-41

On-Chip Memory.............................................................................................. 13-1

Altera Corporation

On-Chip RAM............................................................................................................................................13-1

Features of the On-Chip RAM.....................................................................................................13-1

On-Chip RAM Block Diagram and System Integration...........................................................13-1

Page 7

TOC-7

Functional Description of the On-Chip RAM...........................................................................13-2

Boot ROM...................................................................................................................................................13-3

Features of the Boot ROM............................................................................................................13-3

Boot ROM Block Diagram and System Integration..................................................................13-3

Functional Description of the Boot ROM..................................................................................13-3

On-Chip Memory Address Map and Register Denitions.................................................................. 13-4

NAND Flash Controller.................................................................................... 14-1

NAND Flash Controller Features............................................................................................................ 14-1

NAND Flash Controller Block Diagram and System Integration.......................................................14-2

NAND Flash Controller Signal Descriptions.........................................................................................14-2

Functional Description of the NAND Flash Controller.......................................................................14-3

Discovery and Initialization......................................................................................................... 14-3

Bootstrap Interface.........................................................................................................................14-4

Conguration by Host...................................................................................................................14-5

Local Memory Buer.....................................................................................................................14-6

Clocks.............................................................................................................................................. 14-6

Resets............................................................................................................................................... 14-7

Indexed Addressing....................................................................................................................... 14-7

Command Mapping...................................................................................................................... 14-8

Data DMA.....................................................................................................................................14-14

ECC................................................................................................................................................14-18

NAND Flash Controller Programming Model....................................................................................14-21

Basic Flash Programming...........................................................................................................14-22

Flash-Related Special Function Operations.............................................................................14-25

NAND Flash Controller Address Map and Register Denitions......................................................14-33

SD/MMC Controller..........................................................................................15-1

Features of the SD/MMC Controller.......................................................................................................15-1

SD Card Support Matrix............................................................................................................... 15-2

MMC Support Matrix....................................................................................................................15-3

SD/MMC Controller Block Diagram and System Integration............................................................ 15-3

SD/MMC Controller Signal Description................................................................................................15-4

Functional Description of the SD/MMC Controller.............................................................................15-5

SD/MMC/CE-ATA Protocol........................................................................................................ 15-5

BIU...................................................................................................................................................15-6

CIU.................................................................................................................................................15-20

Clocks............................................................................................................................................ 15-35

Resets............................................................................................................................................. 15-36

Voltage Switching.........................................................................................................................15-37

SD/MMC Controller Programming Model......................................................................................... 15-39

Soware and Hardware Restrictions†....................................................................................... 15-39

Initialization†................................................................................................................................15-41

Controller/DMA/FIFO Buer Reset Usage..............................................................................15-47

Enabling ECC...............................................................................................................................15-47

Enabling FIFO Buer ECC.........................................................................................................15-47

Non-Data Transfer Commands................................................................................................. 15-48

Altera Corporation

Page 8

TOC-8

Data Transfer Commands...........................................................................................................15-50

Transfer Stop and Abort Commands........................................................................................15-56

Internal DMA Controller Operations.......................................................................................15-58

Commands for SDIO Card Devices.......................................................................................... 15-60

CE-ATA Data Transfer Commands.......................................................................................... 15-62

Card Read reshold...................................................................................................................15-70

Interrupt and Error Handling.................................................................................................... 15-73

Booting Operation for eMMC and MMC................................................................................15-74

SD/MMC Controller Address Map and Register Denitions............................................................15-84

Quad SPI Flash Controller................................................................................ 16-1

Features of the Quad SPI Flash Controller.............................................................................................16-1

Quad SPI Flash Controller Block Diagram and System Integration...................................................16-2

Interface Signals......................................................................................................................................... 16-3

Functional Description of the Quad SPI Flash Controller...................................................................16-3

Overview......................................................................................................................................... 16-3

Data Slave Interface....................................................................................................................... 16-4

SPI Legacy Mode............................................................................................................................16-7

Register Slave Interface..................................................................................................................16-8

Local Memory Buer.....................................................................................................................16-8

DMA Peripheral Request Controller...........................................................................................16-9

Arbitration between Direct/Indirect Access Controller and STIG.......................................16-10

Conguring the Flash Device.....................................................................................................16-10

XIP Mode......................................................................................................................................16-12

Write Protection...........................................................................................................................16-12

Data Slave Sequential Access Detection................................................................................... 16-13

Clocks............................................................................................................................................ 16-13

Resets............................................................................................................................................. 16-13

Interrupts...................................................................................................................................... 16-14

Quad SPI Flash Controller Programming Model................................................................................16-15

Setting Up the Quad SPI Flash Controller................................................................................16-16

Indirect Read Operation with DMA Disabled.........................................................................16-16

Indirect Read Operation with DMA Enabled..........................................................................16-17

Indirect Write Operation with DMA Disabled........................................................................16-17

Indirect Write Operation with DMA Enabled.........................................................................16-18

XIP Mode Operations................................................................................................................. 16-18

Quad SPI Flash Controller Address Map and Register Denitions..................................................16-20

DMA Controller................................................................................................ 17-1

Altera Corporation

Features of the DMA Controller..............................................................................................................17-1

DMA Controller Block Diagram and System Integration....................................................................17-3

Functional Description of the DMA Controller....................................................................................17-3

Peripheral Request Interface.........................................................................................................17-4

DMA Controller Address Map and Register Denitions.....................................................................17-7

Address Map and Register Denitions........................................................................................17-9

Page 9

TOC-9

Ethernet Media Access Controller.................................................................... 18-1

Features of the Ethernet MAC..................................................................................................................18-2

MAC.................................................................................................................................................18-2

DMA................................................................................................................................................18-2

Management Interface...................................................................................................................18-3

Acceleration....................................................................................................................................18-3

PHY Interface.................................................................................................................................18-3

EMAC Block Diagram and System Integration.....................................................................................18-4

EMAC Signal Description.........................................................................................................................18-5

HPS EMAC I/O Signals.................................................................................................................18-6

FPGA EMAC I/O Signals..............................................................................................................18-8

PHY Management Interface.......................................................................................................18-11

EMAC Internal Interfaces.......................................................................................................................18-12

DMA Master Interface................................................................................................................ 18-12

Timestamp Interface....................................................................................................................18-13

Functional Description of the EMAC................................................................................................... 18-14

Transmit and Receive Data FIFO Buers.................................................................................18-15

DMA Controller...........................................................................................................................18-16

Descriptor Overview................................................................................................................... 18-29

IEEE 1588-2002 Timestamps.....................................................................................................18-46

IEEE 1588-2008 Advanced Timestamps...................................................................................18-52

IEEE 802.3az Energy Ecient Ethernet....................................................................................18-55

Checksum Ooad....................................................................................................................... 18-56

Frame Filtering.............................................................................................................................18-56

Clocks and Resets.........................................................................................................................18-61

Interrupts...................................................................................................................................... 18-63

Ethernet MAC Programming Model.................................................................................................... 18-63

System Level EMAC Conguration Registers..........................................................................18-63

EMAC FPGA Interface Initialization........................................................................................18-65

EMAC HPS Interface Initialization...........................................................................................18-66

DMA Initialization.......................................................................................................................18-66

EMAC Initialization and Conguration...................................................................................18-67

Performing Normal Receive and Transmit Operation........................................................... 18-68

Stopping and Starting Transmission......................................................................................... 18-69

Programming Guidelines for Energy Ecient Ethernet........................................................ 18-69

Programming Guidelines for Flexible Pulse-Per-Second (PPS) Output..............................18-70

Ethernet MAC Address Map and Register Denitions.......................................................................18-72

USB 2.0 OTG Controller................................................................................... 19-1

Features of the USB OTG Controller...................................................................................................... 19-2

Supported PHYS.............................................................................................................................19-3

USB OTG Controller Block Diagram and System Integration............................................................19-4

USB 2.0 ULPI PHY Signal Description...................................................................................................19-5

Functional Description of the USB OTG Controller............................................................................19-6

USB OTG Controller Block Description.................................................................................... 19-6

Local Memory Buer...................................................................................................................19-10

Altera Corporation

Page 10

TOC-10

Clocks............................................................................................................................................ 19-10

Resets............................................................................................................................................. 19-10

Interrupts...................................................................................................................................... 19-11

USB OTG Controller Programming Model.........................................................................................19-13

Enabling ECC...............................................................................................................................19-13

Enabling SPRAM ECCs.............................................................................................................. 19-13

Host Operation.............................................................................................................................19-14

Device Operation.........................................................................................................................19-15

USB 2.0 OTG Controller Address Map and Register Denitions.....................................................19-17

USB Data FIFO Address Map.................................................................................................... 19-17

USB Direct Access FIFO RAM Address Map..........................................................................19-19

SPI Controller....................................................................................................20-1

Features of the SPI Controller..................................................................................................................20-1

SPI Block Diagram and System Integration...........................................................................................20-2

SPI Block Diagram.........................................................................................................................20-2

SPI Controller Signal Description........................................................................................................... 20-3

Interface to HPS I/O......................................................................................................................20-3

FPGA Routing................................................................................................................................20-3

Functional Description of the SPI Controller........................................................................................20-4

Protocol Details and Standards Compliance..............................................................................20-4

SPI Controller Overview...............................................................................................................20-5

Transfer Modes...............................................................................................................................20-8

SPI Master.......................................................................................................................................20-9

SPI Slave........................................................................................................................................ 20-12

Partner Connection Interfaces...................................................................................................20-16

DMA Controller Interface.......................................................................................................... 20-21

Slave Interface...............................................................................................................................20-21

Clocks and Resets.........................................................................................................................20-22

SPI Programming Model........................................................................................................................ 20-23

Master SPI and SSP Serial Transfers..........................................................................................20-24

Master Microwire Serial Transfers.............................................................................................20-26

Slave SPI and SSP Serial Transfers............................................................................................. 20-28

Slave Microwire Serial Transfers................................................................................................20-29

Soware Control for Slave Selection......................................................................................... 20-29

DMA Controller Operation........................................................................................................20-30

SPI Controller Address Map and Register Denitions.......................................................................20-33

I2C Controller....................................................................................................21-1

Altera Corporation

Features of the I2C Controller..................................................................................................................21-1

I2C Controller Block Diagram and System Integration........................................................................21-2

I2C Controller Signal Description........................................................................................................... 21-3

Functional Description of the I2C Controller........................................................................................21-4

Feature Usage..................................................................................................................................21-4

Behavior...........................................................................................................................................21-5

Protocol Details..............................................................................................................................21-6

Multiple Master Arbitration.......................................................................................................21-11

Page 11

TOC-11

Clock Frequency Conguration................................................................................................ 21-13

SDA Hold Time............................................................................................................................21-15

DMA Controller Interface.......................................................................................................... 21-15

Clocks............................................................................................................................................ 21-15

Resets............................................................................................................................................. 21-15

I2C Controller Programming Model.....................................................................................................21-16

Slave Mode Operation.................................................................................................................21-16

Master Mode Operation..............................................................................................................21-19

Disabling the I2C Controller...................................................................................................... 21-20

DMA Controller Operation........................................................................................................21-20

I2C Controller Address Map and Register Denitions.......................................................................21-24

UART Controller............................................................................................... 22-1

UART Controller Features........................................................................................................................22-1

UART Controller Block Diagram and System Integration...................................................................22-2

UART Controller Signal Description...................................................................................................... 22-3

HPS I/O Pins...................................................................................................................................22-3

FPGA Routing................................................................................................................................22-3

Functional Description of the UART Controller...................................................................................22-4

FIFO Buer Support......................................................................................................................22-4

UART(RS232) Serial Protocol......................................................................................................22-5

Automatic Flow Control............................................................................................................... 22-5

Clocks.............................................................................................................................................. 22-7

Resets............................................................................................................................................... 22-7

Interrupts.........................................................................................................................................22-7

DMA Controller Operation....................................................................................................................22-10

Transmit FIFO Underow..........................................................................................................22-11

Transmit Watermark Level......................................................................................................... 22-11

Transmit FIFO Overow............................................................................................................ 22-12

Receive FIFO Overow...............................................................................................................22-13

Receive Watermark Level............................................................................................................22-13

Receive FIFO Underow.............................................................................................................22-13

UART Controller Address Map and Register Denitions..................................................................22-14

General-Purpose I/O Interface......................................................................... 23-1

Features of the GPIO Interface.................................................................................................................23-1

GPIO Interface Block Diagram and System Integration......................................................................23-2

Functional Description of the GPIO Interface.......................................................................................23-2

Debounce Operation..................................................................................................................... 23-2

Pin Directions.................................................................................................................................23-3

Taking the GPIO Interface Out of Reset ....................................................................................23-3

GPIO Pin State During Reset....................................................................................................... 23-3

GPIO Interface Programming Model..................................................................................................... 23-4

General-Purpose I/O Interface Address Map and Register Denitions.............................................23-4

Timer .................................................................................................................24-1

Altera Corporation

Page 12

TOC-12

Features of the Timer.................................................................................................................................24-1

Timer Block Diagram and System Integration...................................................................................... 24-1

Functional Description of the Timer.......................................................................................................24-2

Clocks.............................................................................................................................................. 24-3

Resets............................................................................................................................................... 24-3

Interrupts.........................................................................................................................................24-3

FPGA Interface...............................................................................................................................24-3

Timer Programming Model..................................................................................................................... 24-5

Initialization....................................................................................................................................24-5

Enabling the Timer........................................................................................................................24-5

Disabling the Timer.......................................................................................................................24-5

Loading the Timer Countdown Value.........................................................................................24-5

Servicing Interrupts.......................................................................................................................24-6

Timer Address Map and Register Denitions........................................................................................24-6

Watchdog Timer................................................................................................ 25-1

Features of the Watchdog Timer..............................................................................................................25-1

Watchdog Timer Block Diagram and System Integration................................................................... 25-2

Functional Description of the Watchdog Timer....................................................................................25-2

Watchdog Timer Counter.............................................................................................................25-2

Watchdog Timer Pause Mode......................................................................................................25-3

Watchdog Timer Clocks................................................................................................................25-3

Watchdog Timer Resets.................................................................................................................25-3

FPGA Interface...............................................................................................................................25-4

Watchdog Timer Programming Model...................................................................................................25-4

Setting the Timeout Period Values.............................................................................................. 25-4

Selecting the Output Response Mode......................................................................................... 25-4

Enabling and Initially Starting a Watchdog Timer....................................................................25-5

Reloading a Watchdog Counter...................................................................................................25-5

Pausing a Watchdog Timer...........................................................................................................25-5

Disabling and Stopping a Watchdog Timer................................................................................25-5

Watchdog Timer State Machine...................................................................................................25-5

Watchdog Timer Address Map and Register Denitions.....................................................................25-7

Introduction to the HPS Component............................................................... 26-1

Instantiating the HPS Component................................................................... 27-1

Altera Corporation

MPU Subsystem.........................................................................................................................................26-2

Arm CoreSight Debug Components.......................................................................................................26-2

Interconnect................................................................................................................................................26-2

HPS-to-FPGA Interfaces...........................................................................................................................26-2

Memory Controllers..................................................................................................................................26-3

Support Peripherals....................................................................................................................................26-3

Interface Peripherals..................................................................................................................................26-3

On-Chip Memories....................................................................................................................................26-4

FPGA Interfaces.........................................................................................................................................27-1

Page 13

TOC-13

General Interfaces..........................................................................................................................27-2

FPGA-to-HPS SDRAM Interface.................................................................................................27-3

DMA Peripheral Request.............................................................................................................. 27-5

Interrupts.........................................................................................................................................27-5

AXI Bridges.....................................................................................................................................27-7

Conguring HPS Clocks and Resets....................................................................................................... 27-8

User Clocks.....................................................................................................................................27-8

Reset Interfaces...............................................................................................................................27-9

PLL Reference Clocks..................................................................................................................27-10

Peripheral FPGA Clocks.............................................................................................................27-11

Conguring Peripheral Pin Multiplexing.............................................................................................27-11

Conguring Peripherals..............................................................................................................27-12

Connecting Unassigned Pins to GPIO......................................................................................27-12

Using Unassigned IO as LoanIO................................................................................................27-13

Resolving Pin Multiplexing Conicts........................................................................................27-13

Peripheral Signals Routed to FPGA ..........................................................................................27-14

Conguring the External Memory Interface........................................................................................27-14

Selecting PLL Output Frequency and Phase............................................................................ 27-15

Using the Address Span Extender Component....................................................................................27-15

Generating and Compiling the HPS Component............................................................................... 27-16

HPS Component Interfaces...............................................................................28-1

Memory-Mapped Interfaces.....................................................................................................................28-1

FPGA-to-HPS Bridge....................................................................................................................28-1

HPS-to-FPGA and Lightweight HPS-to-FPGA Bridges...........................................................28-2

FPGA-to-HPS SDRAM Interface.................................................................................................28-3

Clocks.......................................................................................................................................................... 28-4

Alternative Clock Inputs to HPS PLLs........................................................................................28-4

User Clocks.....................................................................................................................................28-4

AXI Bridge FPGA Interface Clocks.............................................................................................28-5

SDRAM Clocks.............................................................................................................................. 28-5

Peripheral FPGA Clocks............................................................................................................... 28-5

Resets........................................................................................................................................................... 28-6

HPS-to-FPGA Reset Interfaces....................................................................................................28-6

HPS External Reset Request......................................................................................................... 28-6

Peripheral Reset Interfaces............................................................................................................28-7

Debug and Trace Interfaces...................................................................................................................... 28-7

Trace Port Interface Unit...............................................................................................................28-7

FPGA System Trace Macrocell Events Interface........................................................................28-7

FPGA Cross Trigger Interface...................................................................................................... 28-7

Debug APB Interface.....................................................................................................................28-7

Peripheral Signal Interfaces...................................................................................................................... 28-7

DMA Controller Interface............................................................................................................ 28-7

Other Interfaces..........................................................................................................................................28-8

MPU Standby and Event Interfaces.............................................................................................28-8

General Purpose Signals............................................................................................................... 28-9

FPGA-to-HPS Interrupts..............................................................................................................28-9

Boot from FPGA Interface............................................................................................................28-9

Altera Corporation

Page 14

TOC-14

Input-only General Purpose Interface........................................................................................ 28-9

Simulating the HPS Component.......................................................................29-1

Simulation Flows........................................................................................................................................29-2

Setting Up the HPS Component for Simulation........................................................................29-3

Generating the HPS Simulation Model in Platform Designer (Standard).............................29-5

Running the Simulations...............................................................................................................29-5

Clock and Reset Interfaces........................................................................................................................29-9

Clock Interface............................................................................................................................... 29-9

Reset Interface..............................................................................................................................29-10

FPGA-to-HPS AXI Slave Interface........................................................................................................29-11

HPS-to-FPGA AXI Master Interface.....................................................................................................29-12

Lightweight HPS-to-FPGA AXI Master Interface...............................................................................29-12

FPGA-to-HPS SDRAM Interface.......................................................................................................... 29-13

HPS Memory Interface Simulation........................................................................................... 29-13

HPS-to-FPGA MPU Event Interface.....................................................................................................29-14

Interrupts Interface..................................................................................................................................29-14

HPS-to-FPGA Debug APB Interface.................................................................................................... 29-16

FPGA-to-HPS System Trace Macrocell Hardware Event Interface...................................................29-16

HPS-to-FPGA Cross-Trigger Interface.................................................................................................29-17

HPS-to-FPGA Trace Port Interface.......................................................................................................29-17

FPGA-to-HPS DMA Handshake Interface...........................................................................................29-18

Boot from FPGA Interface......................................................................................................................29-19

General Purpose Input Interface............................................................................................................29-20

Booting and Conguration................................................................................ A-1

Boot Overview.............................................................................................................................................A-1

FPGA Conguration Overview.................................................................................................................A-1

Booting and Conguration Options.........................................................................................................A-2

Boot Denitions.......................................................................................................................................... A-5

Reset.................................................................................................................................................. A-5

Boot ROM........................................................................................................................................ A-5

Boot Select........................................................................................................................................ A-6

Flash Memory Devices for Booting............................................................................................ A-13