Page 1

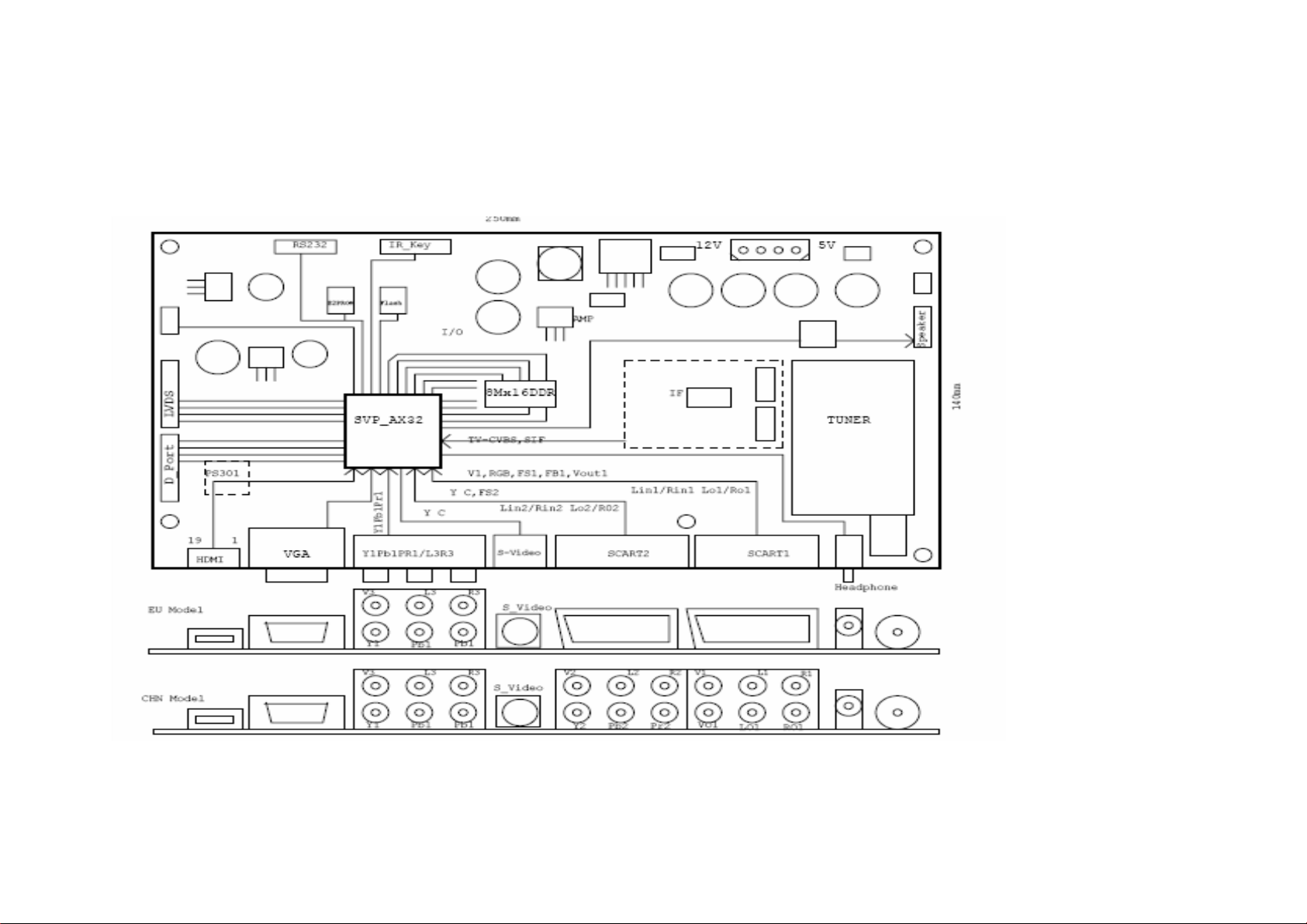

INDEX:

LH

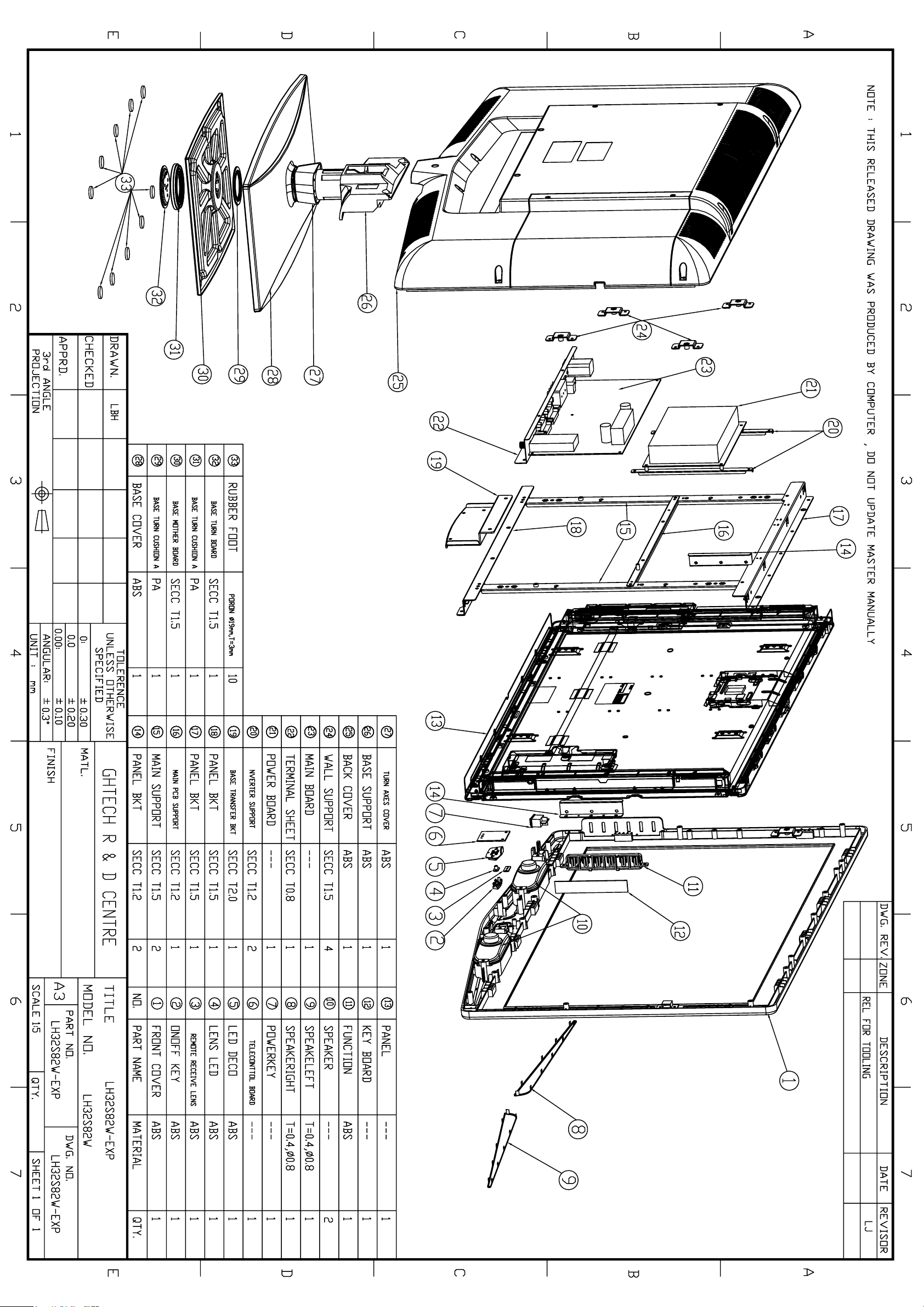

32SXXW SERVICE MANUAL

PART 1:

PART 2:

PART 3

PART 4:

PART 5: Components list

Brief Introduction Of The LH32SXXW

◆

Schematic Diagram Block

◆

Printed Circuit

Exploded view

:

IC Introduction

Detailed Circuit

PART 6: Debug Instruction

Page 2

Part1:

Schematic Diagram Block

Page 3

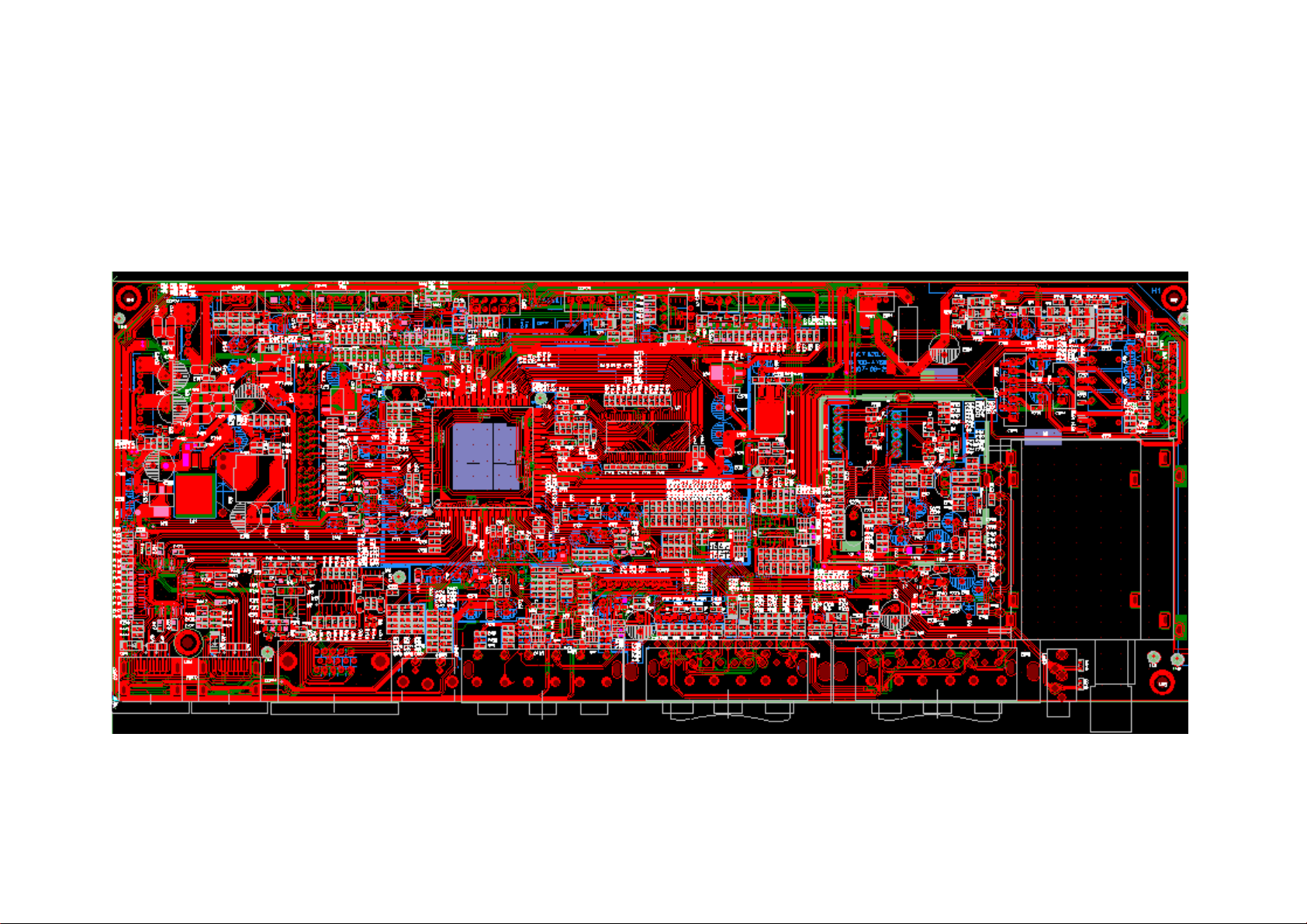

Printed circuit

TV Main Board

Page 4

Page 5

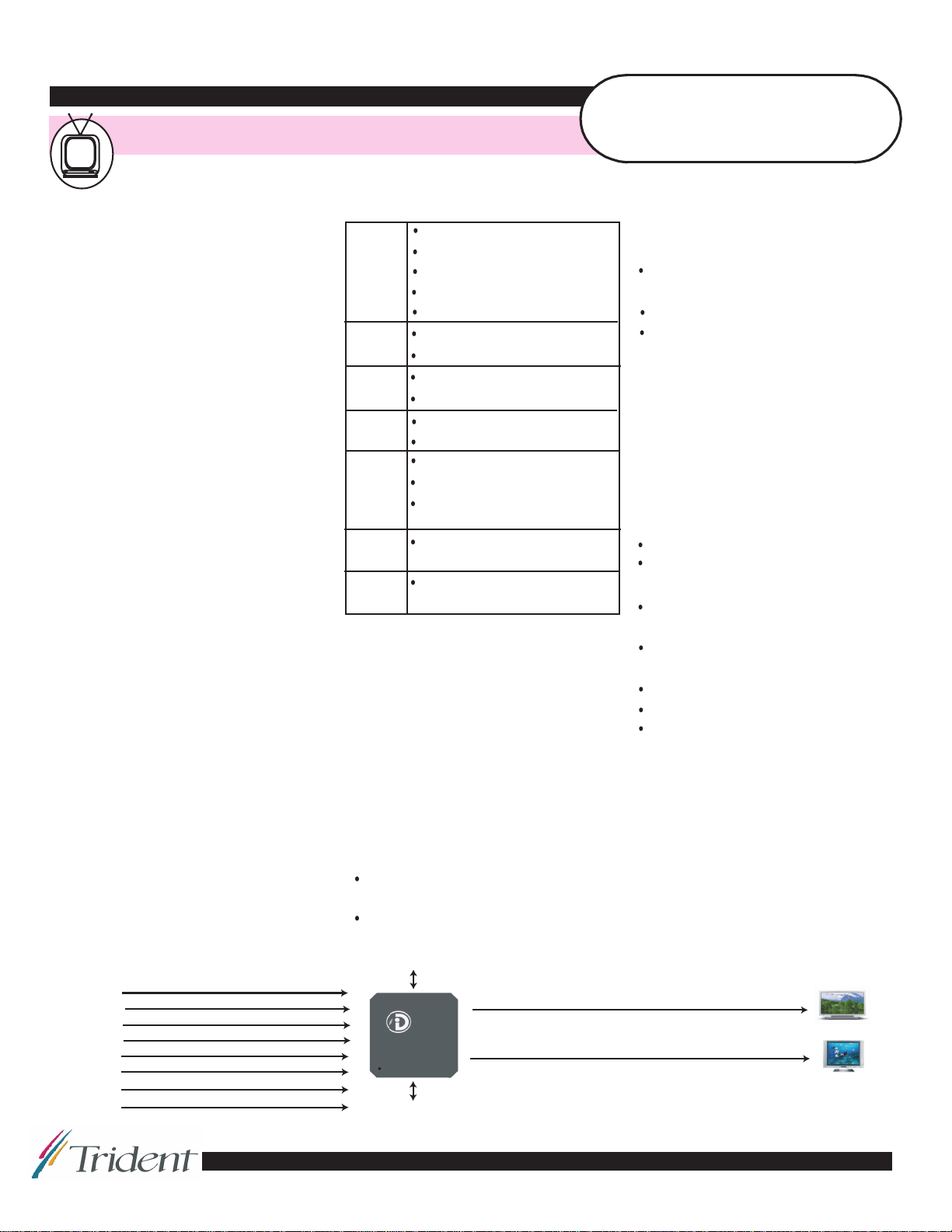

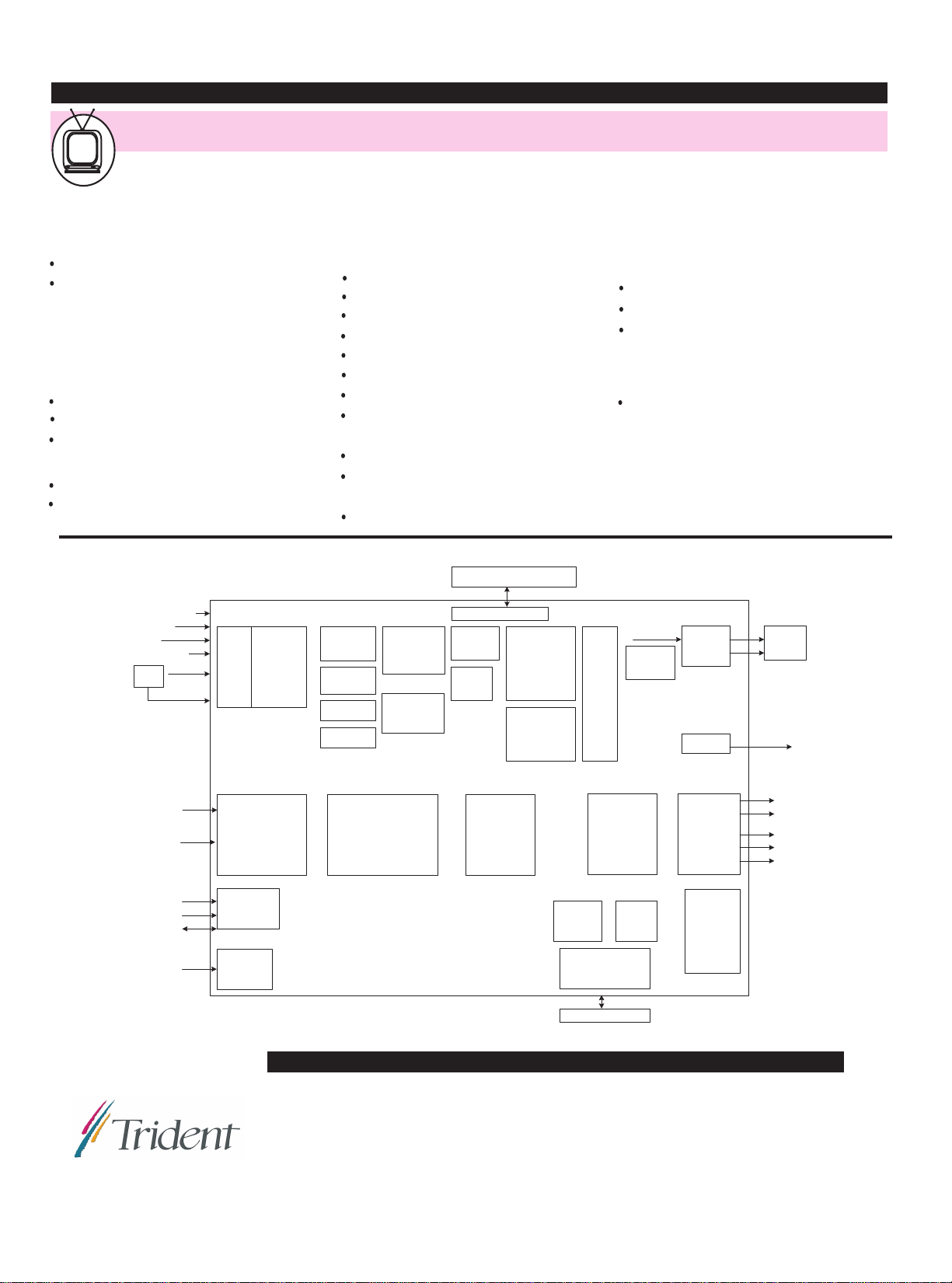

Highly Integrated Advanced 3D Comb Video Decoder + HDTV Total Solution

Part3:

TM

LVDS Panel HDTV-Ready Signal Processor

OVERVIEW

The SVPTMAX-32/68 video processor is a highly integrated systemon-a-chip device, designed for the advanced HDTV-ready LVDS

panel TV applications. SVP

advanced multi-standard audio decoders, advanced audio

processors, embedded MPU and HDMI, triple 10-bit high-precision

and high-speed video ADCs, the 7th generation high-performance

multi-format 3D digital comb video decoder that supports NTSC,

PAL and SECAM*, a HDTV sync separator, motion and edge

adaptive de-interlacing engine, and the video format conversion

engine, supporting many output modes.

Trident's DCRE

integrated inside the SVP

cinema-realistic images. The DCRE

advanced 3D-comb video decoding, advanced motion adaptive deinterlacing, object-based digital noise reduction, advanced 7th

generation scaling engine, film mode support, average picture level

(APL), edge smoothing and dynamic sharpness enhancement.

Trident's patented Unified Memory Architecture (UMA) allows

frame rate conversion, 3D comb video decoding, and video

enhancement processing to share the same frame buffer memory.

All these advanced digital processing techniques are combined

with a true 10-bit video data processing for the most optimal video

fidelity to provide the most natural and cinema-quality video

images.

Designed for maximum system design flexibility, SVP

integrates all video interfaces to support converging digital video,

analog video, and PC data applications. The users of Trident's

single chip SVP

many features while maintaining a price competitive advantage

over the existing solution(s).

* In SECAM, SVP™AX-32/68 video decoding mode is only 2D

TM

TM

P

TM

AX-32/68 contains embedded

engine--Digital Cinema Reality Engine, is

TM

AX-32/68 to provide the most natural

TM

technology integrates

TM

AX-32/68

AX-32/68 video processor(s) will benefit from

1 x CVBS, C

4 x Component

2 x FB for SCART

2 x FS for SCART

16-bit CCIR601

8/10-bit CCIR656

4 stereo Line In, 1 SIF

1 shared I2S/SPDIF

INPUTS/OUTPUTS

Analog Video

Inputs

Digital Video

Inputs

Analog

Outputs

Analog Audio

Inputs

Analog Audio

Outputs

Digital Audio

Inputs

Digital Audio

Outputs

1 x CVBS

1 X C

4 x Component

2 x FB (for SCART)

2 x FS (for SCART)

16-bit CCIR601

8/10 bit CCIR656

2 x CVBS outputs

Single 8/10/12/14 bit or Dual 8-bit LVDS

1 SIF

4 Stereo Line In

1 stereo speaker out

1 stereo audio out or SCART1 out

1 headphone out or SCART2 out (shared with

2nd audio out)

1 shared I2S/SPDIF

1 shared I2S/SPDIF

DESCRIPTIONS

Embedded 8051 MPU (up to 100 MHz SPI interface) with external

serial flash inteface

Embedded Advanced Multi-Standard Audio Decoder

Embedded Advanced Audio Processor with lip sync

Embedded HDMI 1.2a

Support for 1440 x 900 and 1080P panels (SVP

Advanced Color Management Engine

Integrated 7th Generation Motion and Edge Adaptive De-interlacing

7th generation adaptive edge smoothing algorithm for

enhancing image clarity and sharpness

Pixel-based motion and edge adaptive de-interlacing

Frame Buffer

TM

SVP

AX

Flash Memory

TM

AX-68)

SVP

AX-32/68

Integrated Triple ADC Port

High-precision 10-bit ADC mode up to 108 MHz for SD/HD

analog video input modes

Direct support of CVBS/S-video/Component and

HD-D1/D2/D3/D4 modes

Auto clock phase adjustment for PC & HD component inputs

Auto position for PC RGB inputs

Advanced 7th Generation Scaling Engine

Horizontal Mirror Image Inversion

DNR-Digital Temporal and Spatial Noise Reduction Filter

Advanced Chroma Processing

Green Color Stretch, blue color stretch, and skin color enhancement

Integrated 7th Generation Motion Adaptive 3D Digital Comb Video

Decoder with Programmable Filter

Supports NTSC, PAL, and SECAM formats

Smooth 3D/2D image transition with Trident's proprietary object

and motion adaptive detection

Programmable comb filter adapts to all possible

environments, and 2D Y/C separation

Color edge enhancement circuit improves the chroma transient

so that the chroma edge looks sharper than the original signal

High precision 10-bit ADC analog front-end

Enhanced NTSC/PAL/SECAM auto detection

Enhanced false color reduction circuitry

Inverse Color Space Conversion

PDP TV

DIGITAL TV

LCD TV

Preliminary Product Brief. December 2006

Page 6

True 10-Bit Video Processing Path

Preliminary Product Brief. December 2006

LVDS Panel HDTV-Ready Signal Processor

Frame Rate Conversion

Supports frame rate conversion for PC and video mode

Both free-running and line-lock modes are supported

14D: Dynamic Picture Enhancements

Advanced Film Mode Recovery-3:2/2:2 pull down

PWM

One high-precision PWM

Two GPIO shared PWM

18-bit PWM output for VS tuner

Memory Interface

Supports 16 bits DDR memory interface

Memory clock support up to 250 MHz

Trident's

SVP™AX

Solution

(PC Sync)

AIN_H/AIN_V

1xCVBS

1xC

4xComponents

(PC)

FB1/FB2

Audio

from

FS1/FS2

Tuner

SIFP/SIFN

ADCs

Analog

Mux

DCReTM Advanced Image Processing

Advanced LUMA processing for image enhancement

White peak limitation

Black and White extension

Horizontal and vertical sharpness control

User-friendly white balance adjustment

Advanced linear and non-linear panorama scaling algorithms

Integrated sync separator with line-locking PLL

Programmable zoom viewer allows partial still pictures and

live broadcast to be viewed in greater detail.

Gamma correction with 10-bit per color look-up table

Picture controls such as hue, saturation, brightness, and

contrast can be automatically adjusted to their optimal balance

sRGB support

ASS/DSS

LLPLL

3D Video

Decoder

VBI Slicer

(CC/Teletext)

ICSC

MP

Motion & Edge

Adaptive

Deinterlacer

PIP (OSD2)

before

framebuffer

scaling down

DDR upto 250 MHz

1Mx16, 2Mx16, 8Mx16

UMAC Memory Control

MP

th

7

generation

Noise

Reduction

scalar

MP

Chroma Processing

Color Management

adjustment

16-bit DDR interface

MP

Advanced Luma/

H/V Sharpness

Luma Dynamic

Contrast

CSC

PIP

Basic Brightness/

contrast/ hue/Sat.

DLP TV

OSD and VBI/Closed Caption

Advanced OSD Engine

1/4/8/16/32-bit color OSD display

Hardware scrolling for CC display

One OSD Plane

Horizontal Mirror

Packaging

256-Pin PQFP

Link1

Panel upto

Link2

1920 x 1080P

2 x CVBS Out

MP, PIP

OSD

blending

GAMMA

LUT

1024x10x3

LVDS TX

CVBS_OUT

SVPTMAX

(AL/AR) x 4

SPDIF / I2S

PWR5V

HDMi/DVI in (±)

(DDC) DSCL/DSDA

Audio Matrix

4 X Analog Audio Line

Input;

SPDIF or I2S input

supported (shared ports)

HDMi /HDCP

Rx 1.2

Digital Input

Port (165

MHz)

USA Taiwan

Trident Microsystems, Inc. (Headquarters)

3408 Garrett Drive

Santa Clara, CA 95054-2804, USA

Phone: (408) 764-8808

Fax: (408) 988-9178

Web site: http://www.tridentmicro.com

Audio Demodulation

(Worldwide format, NICAM

included)

Audio Processing

Audio LipSync

XRAM

16K + 8 K

Embedded 8051 CPU

powerful 2 cycle

SPI upto 100MHz

Cache

HongKong

Trident Microelectronics Ltd.

4F. No. 323, Yangguang St.,

Neihu,Taipei, Taiwan ROC

Phone: 886-2-2657-7686

Fax: 886-2-2627-8727

Web site: http://www.trident.com.tw

Audio Out

(DAC & SPDIF

encoder

PWM

I2C (slave &

Master)

UART x 2

JTAG

GPIO

Trident Microsystems (Far East), LTD.

No. 2, 3, & 5, 5/F., Futura Plaza,

111-113 How Ming Street, Kwun Tong,

Kowloon, Hong Kong

Phone: 852-2-756-9666

Fax: 852-2-796-9849

©2006. All rights reserved. Trident and its logo are registered trademarks of Trident Microsystems, Inc. All other trademarks and registered trademarks are acknowledged and are properties of their respective owners.

The information in this document is subject to change, as the Company may make changes to the product in order to improve reliability, design, or function, without prior written notice.

SPKOL/SPKOR

AOL1/AOR1

HPHO L/HPHOR(AO L1/

AOR2)

I2S or SPDIF

)

Mute

Page 7

5

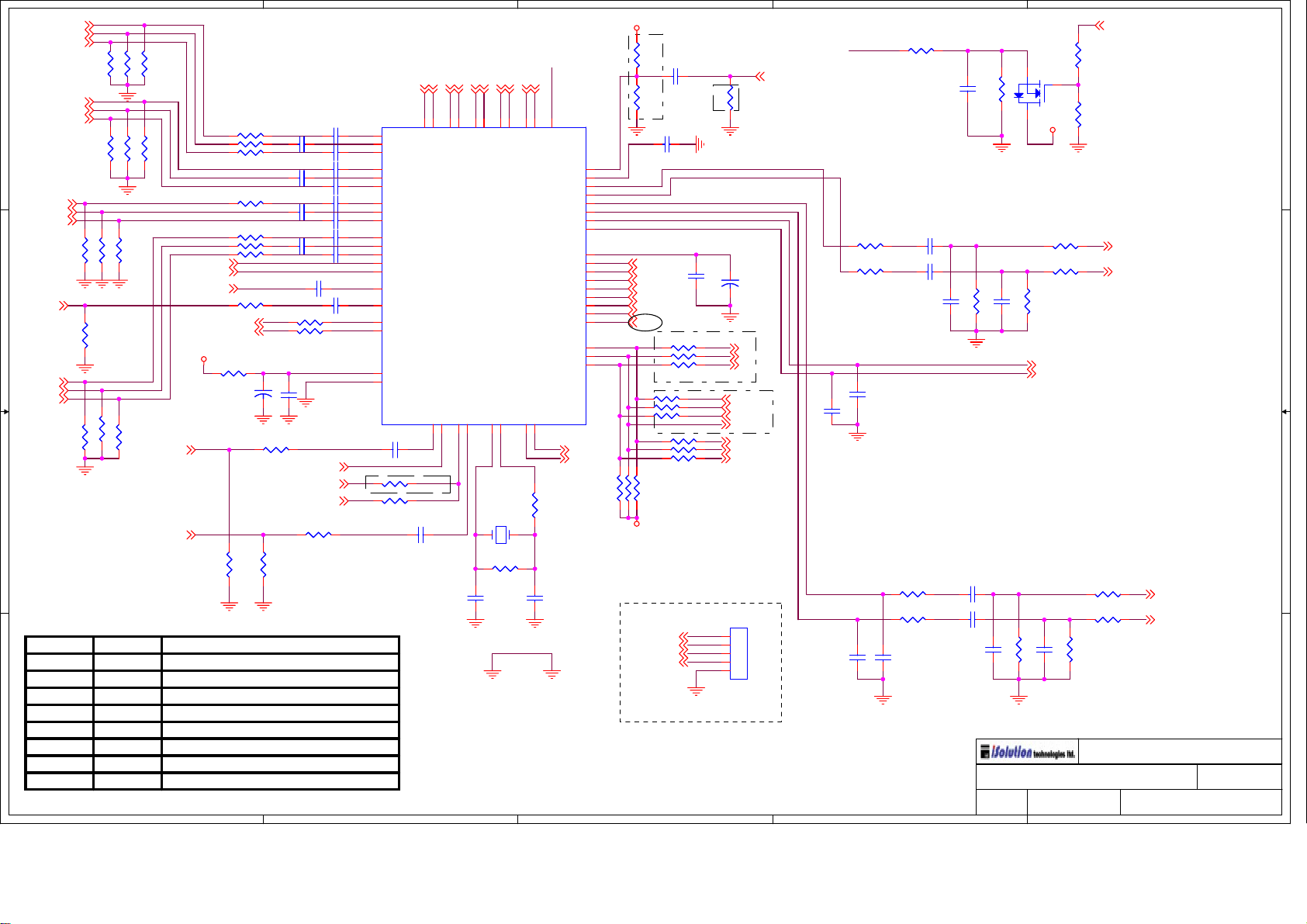

Part4:

Y1_IN

PB1_IN

PR1_IN

SC1_G

D D

C C

B B

SC1_B

SC1_R

SV_Y_MP

SC1_CVBS

SC2_Y_CVBS

SV_C_MP

PC_GIN

PC_BIN

PC_RIN

R10

R10

75R

75R

R17

R17

75R

75R

R22

R22

75R

75R

Pin Name

CVBS1

Y_G3

PB_B3

PR_R3

A A

FB1

FS1

FS2

R1

75RR175R

R7 75RR7 75R

R11

R11

R12

R12

75R

75R

75R

75R

R23

R23

R24

R24

75R

75R

75R

75R

Pin No.

52

42

43

44

57

56FB2

55

54

R3

R2

75RR375R

75RR275R

R9 75RR9 75R

R8 75RR8 75R

PC_HSIN

PC_VSIN

TV_CVBS1

AX_CVBS_OUT1

AX_CVBS_OUT2

AX_VCC33

SC2_C/R

VIDEO_2

DEFINITION IN LCD301

MAIN TUNER INPUT

SVIDEO Y INPUT

SCART1 CVBS INPUT

SCART2 CVBS INPUT

SCART1 FB INPUT

SCART2 or 3 Chroma INPUT

SCART1 FS INPUT

SCART2 FS INPUT

5

R4 10RR4 10R

R5 10RR5 10R

R6 10RR6 10R

R13 10RR13 10R

R14 10RR14 10R

R15 10RR15 10R

R16 10RR16 10R

R18 10RR18 10R

R21 0RR21 0R

C15

C15

10uF/16V

10uF/16V

R25 10RR25 10R

R26

R26

75R

75R

C2 0.1uFC2 0.1uF

C5 0.1uFC5 0.1uF

C8 0.1uFC8 0.1uF

C11 0.1uFC11 0.1uF

C13 0.1uFC13 0.1uF

R19 75RR19 75R

R20 75RR20 75R

C16

C16

0.1uF

0.1uF

TOUCH_IN

R28 10RR28 10R

R27

R27

75R

75R

C1 0.1uFC1 0.1uF

C3 0.1uFC3 0.1uF

C4 0.1uFC4 0.1uF

C6 0.1uFC6 0.1uF

C7 0.1uFC7 0.1uF

C9 0.1uFC9 0.1uF

C10 0.1uFC10 0.1uF

C12 0.1uFC12 0.1uF

C14 0.1uFC14 0.1uF

AX_VREFP_1

AX_VREFN_1

SC1_FB

SC2_FS

4

RX3V1_DDC_SCL

HDMI_RX1-

HDMI_RX2-

HDMI_RX2+

17

Y_G1

PB_B1

PR_R1

Y_G2

PB_B2

PR_R2

Y_G3

PB_B3

PR_R3

PC_G

PC_B

PC_R

AIN_HS

AIN_VS

CVBS

C

CVBS_OUT1

CVBS_OUT2

VREFP

VREFN

C18 0.1uFC18 0.1uF

4

16

RX2-

RX2+

SVP-AX

SVP-AX

56

U1A SVP-AX_256

U1A SVP-AX_256

33

34

35

36

37

38

42

43

44

29

28

30

26

27

52

45

61

60

71

69

C17 0.1uFC17 0.1uF

R29 100R_DNSR29 100R_DNS

R146 100RR146 100R

HDMI_RX0-

HDMI_RX1+

HDMI_RX0+

9

13

8

12

RX0-

RX1-

RX0+

RX1+

PQFP_256

PQFP_256

(1/4)

(1/4)

HDMI

HDMI

AUDIO IN

AUDIO IN

PLL

PLL

FS155FS254FB157FB2

XTALI

194

XI

Y1

24MHzY124MHz

R31 1MR31 1M

C19

C19

18pF

18pF

RX3V1_DDC_SDA

HDMI_RXC-

HDMI_RXC+

19

4

20

5

RXC-

DSCL

RXC+

DSDA

AUD_MCLK

XTALO

MLF1

PLF2

195

197

200

XO

R30

R30

33R

33R

LAYOUT: Place xtal

circuit as compact

and close to chip

as possible

C20

C20

18pF

18pF

AGND

PWR5V

21

PWR5V

HPHOL

HPHOR

SPKOL

SPKOR

AUD_SD

AUD_WS

SIFP

SIFN

AOL1

AOR1

VCM

AL1

AR1

AL2

AR2

AL3

AR3

AL4

AR4

AX_PLF2

AX_MLF1

R38

R38

4.7K_DNS

4.7K_DNS

50

51

63

64

81

82

66

67

70

73

74

75

76

77

78

79

80

85

86

87

AUD_MCLK

AUD_SD

AUD_WS

R684.7K R684.7K

3

AX_VCC33

C24

C24

0.1uF

0.1uF

R39

R39

4.7K_DNS

4.7K_DNS

C23

C23

AGND

0.1uF

0.1uF

A1_LIN

A1_RIN

A2_LIN

A2_RIN

A3_LIN

A3_RIN

A4_LIN

A4_RIN

R37 33R_DNSR37 33R_DNS

R36 33R_DNSR36 33R_DNS

R35 33R_DNSR35 33R_DNS

R34 33R_DNSR34 33R_DNS

R33 33R_DNSR33 33R_DNS

R32 33R_DNSR32 33R_DNS

R65 1KR65 1K

R66 1KR66 1K

R67 1KR67 1K

R694.7K R694.7K

R704.7K R704.7K

3.3V_SB

A_MCLK_IN

A_SD_IN

GPIO00

A_WS_IN

3

AGND

AGND

C21

C21

0.1uF

0.1uF

AGND

CON1

CON1

5x2.0MM_DNS

5x2.0MM_DNS

R40

R40

0R_DNS

0R_DNS

C22

C22

10uF/16V

10uF/16V

A_MCK_OUT

A_SD_OUT

A_WS_OUT

A_MCLK_IN

A_SD_IN

A_WS_IN

AUD_SD

L/R_SW1

L/R_SW2

LED_R

1

2

3

4

5

2

HDMI1_5VIN

PWR5V

R41 10KR41 10K

SIF

R45 220RR45 220R

R46 220RR46 220R

C31

C31

C30

C30

1000pF

1000pF

1000pF

1000pF

AGND

R58 220RR58 220R

R59 220RR59 220R

C36

C36

1000pF

1000pF

C37

C37

1000pF

1000pF

AGND AGND

2

0.01uF

0.01uF

C26 1uFC26 1uF

C27 1uFC27 1uF

C25

C25

R42

R42

10K

10K

C28

C28

R49

R49

100K

100K

470pF

470pF

AGND

C40 1uFC40 1uF

C41 1uFC41 1uF

Schematict Name Rev

Schematict Name Rev

Schematict Name Rev

Size

Size

Size

C38

C38

470pF

470pF

C29

C29

470pF

470pF

B

B

B

Q1

R62

R62

100K

100K

2

3

R50

R50

100K

100K

Q1

2N7002

2N7002

sot_23

sot_23

Audio_out_R

Sheet

Sheet

Sheet

R43

R43

10K

10K

1

R44

R44

10K

10K

3.3V_SB

R47220R R47220R

R48220R R48220R

Audio_out_L

R60 220RR60 220R

R61 220RR61 220R

R63

R63

C39

C39

100K

100K

470pF

470pF

Title

Title

Title

ANALOG CHANNEL

ANALOG CHANNEL

ANALOG CHANNEL

of

of

of

117

117

117

1

SC2_LOUT

SC2_ROUT

SC1_LOUT

SC1_ROUT

AX68 Solution Design

AX68 Solution Design

AX68 Solution Design

Date:

Date:

Date:

Friday, April 20, 2012

Friday, April 20, 2012

Friday, April 20, 2012

1

2.0.3

2.0.3

2.0.3

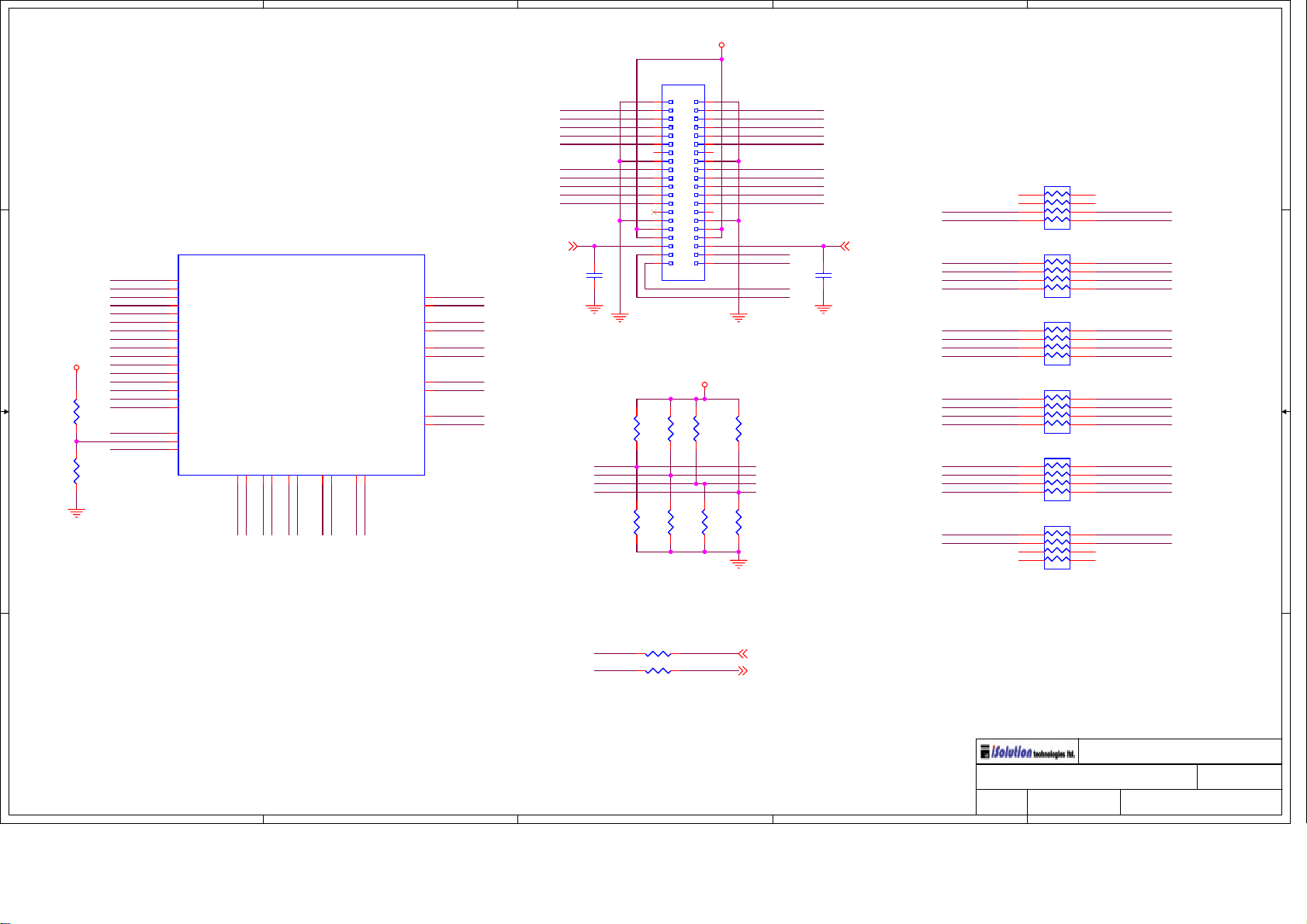

Page 8

5

D D

U1B SVP-AX_256

U1B SVP-AX_256

DPA_0

254

253

252

251

250

249

248

247

241

240

239

238

237

236

235

234

242

255

256

DP0

DP1

DP2

DP3

DP4

DP5

DP6

DP7

DP8

DP9

DP10

DP11

DP12

DP13

DP14

DP15

DP_CLK

DP_HS

DP_VS

SVP-AX

SVP-AX

PQFP_256

PQFP_256

LVDS OUT

LVDS OUT

Digital IN

Digital IN

TA2M

TA2P

TB2M

TB2P

213

212

211

210

AX_TA2-

AX_TA2+

AX_TB2+

AX_TB2-

(2/4)

(2/4)

TC2M

TC2P

209

208

AX_TC2+

AX_TC2-

207

AX_TCLK2-

TCLK2M

206

AX_TCLK2+

TCLK2P

DPA_1

DPA_2

DPA_3

C C

3.3V_SB

R71

R71

4.7K

4.7K

R72

R72

4.7K

4.7K

B B

DPA_4

DPA_5

DPA_6

DPA_7

DPA_8

DPA_9

DPA_10

DPA_11

DPA_12

DPA_13

DPA_14

DPA_15

DPA_CLK

DPA_HS

DPA_VS

4

LCD_TA1+

LCD_TB1+

LCD_TC1+

LCD_TCLK1+

LCD_TA2+

LCD_TB2+

LCD_TC2+

LCD_TCLK2+

LCD_TD2+

3V_SDA_MSTL

C50

C50

27pF_DNS

TA1M

TA1P

TB1M

TB1P

TC1M

TC1P

TCLK1M

TCLK1P

TD1M

TD1P

TD2M

TD2P

205

204

AX_TD2-

AX_TD2+

226

225

224

223

222

221

220

219

218

AX_TA1+

AX_TB1-

AX_TB1+

AX_TC1-

AX_TC1+

AX_TCLK1AX_TCLK1+

AX_TD1AX_TD1+

AX_TA1-

227

27pF_DNS

LINE1

LINE2

LINE3

LINE4

3

PVDD

CON2

CON2

BM40B-SRDS-G-TF

BM40B-SRDS-G-TF

12

34

56

78

910

1112

1314

1516

1718

1920

2122

2324

2526

2728

2930

3132

3334

3536

3738

3940

LVDS connector

3.3V_SB

R79

R75

R75

R73

R73

4.7K_DNS

4.7K_DNS

4.7K_DNS

4.7K_DNS

R76

R76

R74

R74

4.7K_DNS

4.7K_DNS

4.7K_DNS

4.7K_DNS

R79

R77

R77

4.7K_DNS

4.7K_DNS

4.7K_DNS

4.7K_DNS

R78

R78

R80

R80

4.7K_DNS

4.7K_DNS

4.7K_DNS

4.7K_DNS

LINE1

LINE2

LINE3

LINE4

LCD_TA1LCD_TB1LCD_TC1LCD_TCLK1LCD_TD1-LCD_TD1+

LCD_TA2LCD_TB2LCD_TC2LCD_TCLK2LCD_TD2-

3V_SCL_MSTL

C51

C51

27pF_DNS

27pF_DNS

2

RN1

RN1

0Rx4

0Rx4

1

8

2

7

LCD_TA1+ AX_TA1+

LCD_TB1LCD_TC1- AX_TC1-

LCD_TC1+

LCD_TCLK1-

LCD_TCLK1+ AX_TCLK1+

LCD_TD1LCD_TD1+

LCD_TA2LCD_TA2+

LCD_TB2LCD_TB2+

LCD_TC2LCD_TC2+

LCD_TCLK2LCD_TCLK2+

LCD_TD2LCD_TD2+ AX_TD2+

6

5

8

7

6

5

8

7

6

5

8

7

6

5

8

7

6

5

8

7

6

5

RN2

RN2

0Rx4

0Rx4

RN3

RN3

0Rx4

0Rx4

RN4

RN4

0Rx4

0Rx4

RN5

RN5

0Rx4

0Rx4

RN6

RN6

0Rx4

0Rx4

3

4

1

2

3

4

1

2

3

4

1

2

3

4

1

2

3

4

1

2

3

4

AX_TA1-LCD_TA1-

AX_TB1AX_TB1+LCD_TB1+

AX_TC1+

AX_TCLK1AX_TD1-

AX_TD1+

AX_TA2AX_TA2+

AX_TB2AX_TB2+

AX_TC2AX_TC2+

AX_TCLK2AX_TCLK2+

AX_TD2-

1

LINE3

R81 100R_DNSR81 100R_DNS

R82 100R_DNSR82 100R_DNS

LINE4

A A

5

4

3

BRT_CNTL

VBR_OUT

Title

Title

Title

AX68 Solution Design

AX68 Solution Design

AX68 Solution Design

Schematict Name Rev

Schematict Name Rev

Schematict Name Rev

Size

Size

Size

2

LVDS INTERFACE

LVDS INTERFACE

LVDS INTERFACE

Sheet

Sheet

Sheet

B

B

B

217

217

217

2.0.3

2.0.3

2.0.3

Date:

Date:

Date:

Friday, April 20, 2012

Friday, April 20, 2012

of

of

of

Friday, April 20, 2012

1

Page 9

5

4

3

2

1

AX_SDA_SLV

AX_SCL_SLV

RXD0

TXD0

DTV_CNTL

GPIO00

R108

R108

C71

C71

68pF_DNS

68pF_DNS

3

3.3V_SB3.3V_SB

R148

R148

27K

27K

RXD0

TXD0

GPIO01

GPIO02

GPIO03

GPIO04

AX_TPWM

R131 100RR131 100R

PWM0

DS_IO

GPIO00

3.3V_SB

R109

R109

4.7K_DNS

4.7K_DNS

CE_REMOTE

U1C SVP-AX_256

U1C SVP-AX_256

153

SDA

154

SCL

155

RXD0

156

TXD0

157

PSYNC

158

RXD1

159

TXD1

160

MSCL

161

MSDA

163

GPIO01

165

GPIO02

166

GPIO03

164

GPIO04

167

TPWM

168

PWM2

175

IRIN

176

POWERLOW

177

PPWR

182

PDOWN

183

KEY

184

SENSOR1

185

SENSOR2

186

FS3

187

FS4

188

AFT

189

PWM0

190

PWM1

R173 100RR173 100R

R114 100RR114 100R

E_PAGE

R113 100RR113 100R

R112 100RR112 100R

3.3V_SB

AX_SDA_SLV

AX_SCL_SLV

C72

C72

68pF_DNS

68pF_DNS

JTAG

CONNECTOR

R901KR90

1K

CON3

PAGE

PAGE

AGND

R101

R101

4.7K

4.7K

R100

R100

VCC

SCL

VCC

SCL

R921KR92

1K

+

+

0.1uF_DNS

0.1uF_DNS

CON3

A1

B1

A2

B2

A3

B3

A4

B4

A5

C66

C66

8

7

6

5

8

7

6

5

AGND

R93

R93

10R

10R

B5

3.3V_SB

R94

R94

4.7K

4.7K

10uF/16V_DNS

10uF/16V_DNS

HEADER_5*2_DNS

HEADER_5*2_DNS

5

R95

R95

4.7K_DNS

4.7K_DNS

E_PAGE

DAC_R

DAC_L

C67

C67

+

+

AGND

U5

U5

1

CE#

2

SO

3

WP#

VSS4SI

W25X80-VSSIG

W25X80-VSSIG

10

9

8

7

6

HOLD#

R96

R96

4.7K_DNS

4.7K_DNS

R97 100RR97 100R

R98 100RR98 100R

AOUTR

VA

GND

AOUTL

FILT+

VDD

SCK

3V_SDA_MST

3V_SCL_MST

3V_SDA_MSTL

3V_SCL_MSTL

REMOTE_3V

DEM/SCLK

8

7

6

5

RXD1

TXD1

PWM

AX_SCL_MST

AX_SDA_MST

C63

C63

100pF

100pF

U4CS4344_DNS U4CS4344_DNS

1

SDIN

2

3

LRCK

4

MCLK

5

VQ

10uF/16V_DNS

10uF/16V_DNS

3.3V_SB

C70

C70

0.1uF

0.1uF

100Rx4

100Rx4

5

6

7

8

AX_SCL_MST

AX_SDA_MST

C73

C73

100pF

100pF

C64

C64

100pF

100pF

SD2DAC

SCK2DAC

WS2DAC

MCLK2DAC

C68

C68

+

+

AGND

RN10

RN10

BKLT_CNTL

LVDS_PWR

LIGHT_SENSOR

HDMI_HOTPLUG

C69

C69

0.01uF_DNS

0.01uF_DNS

AGND

R102

R102

4.7K

4.7K

4

3

2

1

4

D D

C C

B B

A A

JTAG_TCK

JTAG_TDO

JTAG_TMS

JTAG_TDI

C62 22uF/16V

C62 22uF/16V

D1

D1

ZENER_3V9

ZENER_3V9

1

2

3

1

2

3

+5VA

FB1

FB1

150_Ohm_600mA_DNS

150_Ohm_600mA_DNS

10uF/16V_DNS

10uF/16V_DNS

WP_FSH

R99 100RR99 100R

R911KR91

1K

C61 1000pFC61 1000pF

+

+

U2 24C64_DIPU2 24C64_DIP

A0

A1

A2

GND4SDA

U3

U3

A0

A1

A2

GND4SDA

AT24C64_SO8_DNS

AT24C64_SO8_DNS

+5V_AV

12

C65

C65

4.7K_DNS

4.7K_DNS

3.3V_SB

R136 100RR136 100R

R135 100RR135 100R

R134 100R_DNSR134 100R_DNS

R133 100R_DNSR133 100R_DNS

SB_PWR

KEYA

S2

3.3V_SB

RN8 22Rx4_DNSRN8 22Rx4_DNS

4

5

3

6

2

7

1

8

R104

R104

4.7K

4.7K

R159

R159

R103

R103

4.7K

4.7K

4.7K

4.7K

R139

R139

2

4.7K_DNS

4.7K_DNS

VCC

SPI_DI

SPI_DO

SPI_CK

SPI_CZ

R140

R140

4.7K_DNS

4.7K_DNS

AFT

KEYB

GND

U6

3

DS2411U6DS2411

GPIO03

GPIO02

GPIO04

GPIO01

R1434.7K R1434.7K

R1414.7K R1414.7K

S1

1

I/O

R1424.7K R1424.7K

SC1_FS

SC2_FS

R1444.7K R1444.7K

C74

C74

100pF_DNS

100pF_DNS

3.3V_SB

RN9 0Rx4RN9 0Rx4

4

3

2

1

3V_SDA_SLV

3V_SCL_SLV

R138 100RR138 100R

R137 100RR137 100R

5

6

7

8

R118

R118

4.7K

4.7K

JTAG_TDI

JTAG_TMS

JTAG_TDO

JTAG_TCK

TP7TP7

R147 100RR147 100R

GPIO03

R132 100RR132 100R

R130 100RR130 100R

R129 100RR129 100R

R128 100RR128 100R

R127 100RR127 100R

R126 100RR126 100R

R125 100RR125 100R

R124 100RR124 100R

R123 100RR123 100R

R122 100RR122 100R

R121 100RR121 100R

R120 0RR120 0R

R117

R117

4.7K

4.7K

R188 4.7KR188 4.7K

R115 4.7KR115 4.7K

LED_G

MUTE

R106 10RR106 10R

R107 10RR107 10R

WP_FSH

4.7K_DNS

4.7K_DNS

AX_MD[0..15]

SPI_CZ

SPI_DI

SPI_CK

SPI_DO

AX_MD0

AX_MD2

AX_MD1

172

174

171

173

SPI_SI

SPI_SO

SPI_SCK

SPI_CEN

AX_MSCL

AX_MSDA

DDR & CPU INTERFACE

DDR & CPU INTERFACE

TUNE089TUNE190TUNE291MUTE

GPIO00

92

88

TUNER2

AX_RESET

R111 4.7KR111 4.7K

TUNER2

R110 4.7KR110 4.7K

1: I2C Slave Address = 0x7E/7F (*)

0: I2C Slave Address = 0x7C/7D

MD095MD196MD298MD399MD4

SVP-AX

SVP-AX

PQFP_256

PQFP_256

(3/4)

(3/4)

RESET

TESTMODE

178

179

R119

R119

470R

470R

AX_RESET

JP1

JP1

1

2

3

3-PIN_HEADER

3-PIN_HEADER

AGND

2

AX_MD3

AX_MD4

AX_MD6

AX_MD7

AX_MA11

102

132

AX_MD5

103

MA11

146

AX_MA10

DAC_L

DAC_R

105

MD5

MA10

133

AX_MA9

AX_MD12

AX_MD8

AX_MD11

AX_MD10

AX_MD14

AX_MD9

AX_MD13

AX_MD15

120

121

123

124

126

127

MD10

MD11

MD12

MD13

MD14

MD15

115

DQS1

108

DQS0

111

DQM1

109

DQM0

144

BA0

145

BA1

140

CASN

141

RASN

139

WEN

131

CLKE

130

MCK0P

129

MCK0N

113

MVREF

MA0

MA1

MA2

MA3

MA4

MA5

147

148

149

150

138

137

AX_MA3

AX_MA5

AX_MA2

AX_MA0

AX_MA4

AX_MA1

AX_MA[0..11]

C78

C78

3.3uF_DNS

3.3uF_DNS

R154

R154

270K_DNS

270K_DNS

AGND AGND

AGND

Schematict Name Rev

Schematict Name Rev

Schematict Name Rev

Size

Size

Size

3.3uF_DNS

3.3uF_DNS

R157

R157

270K_DNS

270K_DNS

B

B

B

C80

C80

AGND

DDR&CPU INTERFACE

DDR&CPU INTERFACE

DDR&CPU INTERFACE

Sheet

Sheet

Sheet

317

317

317

AX_DQS1

AX_DQS0

AX_DQM1

AX_DQM0

AX_BA0

AX_BA1

AX_CAS#

AX_RAS#

AX_WE#

AX_CLKE

R149 0RR149 0R

R150 0RR150 0R

AX_VDDMQ AX_VDDMQ

C76

C76

0.1uF

0.1uF

AX_MVREF

C77

C77

0.1uF

0.1uF

R153 470R_DNSR153 470R_DNS

R155

R155

10K_DNS

10K_DNS

R156 470R_DNSR156 470R_DNS

R158

R158

10K_DNS

10K_DNS

Title

Title

Title

AX68 Solution Design

AX68 Solution Design

AX68 Solution Design

Date:

Date:

of

of

of

Date:

MD6

MA9

AX_MA8

106

134

MD7

MA8

AX_MA7

117

135

MD8

MA7

AX_MA6

118

MD9

MA6

136

AX_MCK0

AX_MCK0#

R151

R151

1K 1%

1K 1%

R152

R152

820R 1%

820R 1%

C79

C79

2700pF_DNS

2700pF_DNS

AGND

C81

C81

2700pF_DNS

2700pF_DNS

AGND

Friday, April 20, 2012

Friday, April 20, 2012

Friday, April 20, 2012

1

AX_MVREF

C75

C75

0.1uF

0.1uF

AX_DDR_VREFA

A4_LIN

A4_RIN

2.0.3

2.0.3

2.0.3

Page 10

5

3.3V_SB

MCLK PLL POWER 3.3V

R170 22RR170 22R

C91

C91

C90

C90

+

+

10uF/16V

10uF/16V

D D

0.1uF

0.1uF

AX_PAVDD1

C92 2700pFC92 2700pF

AX_PAVSS1

AX_MLF1

AX_VDDMQ

PCLK PLL POWER 3.3V

C95 2700pFC95 2700pF

L1 2.2uH_1210L1 2.2uH_1210

L2 2.2uH_1210L2 2.2uH_1210

C101

C101

+

+

10uF/16V

10uF/16V

L3 2.2uH_1210L3 2.2uH_1210

L4 2.2uH_1210L4 2.2uH_1210

AX_VD33

FB2

FB2

1 2

150_Ohm_600mA

150_Ohm_600mA

AX_PAVDD2

AX_PLF2

AX_PAVSS2

AX_VA12

AX_VA12

AX_VD33

AX_VD33

0.1uF_DNS

0.1uF_DNS

R171 22RR171 22R

C94

C94

C93

C93

+

+

10uF/16V

10uF/16V

0.1uF

0.1uF

1.2V POWER FOR ADC

AX_AVDD_ADC1

C96

C96

0.1uF

0.1uF

AX_AVSS_ADC1

C C

AX_AVDD_ADC234

C99

C99

C98

C98

0.1uF

0.1uF

0.1uF

0.1uF

AX_AVSS_ADC234

B B

C100

C100

0.1uF

0.1uF

C97

C97

+

+

10uF/16V

10uF/16V

3.3V POWER FOR ADC

AX_AVDD3_ADC1

C102

C102

0.1uF

0.1uF

AX_AVDD3_ADC2

C104

C104

0.1uF

0.1uF

A A

C103

C103

+

+

10uF/16V

10uF/16V

C105

C105

+

+

10uF/16V

10uF/16V

3.3V POWER FOR

ADC

AX_AVDD3_BG_ASS

C106

C106

C107

C107

+

+

0.1uF

0.1uF

10uF/16V

10uF/16V

5

AX_PAVDD1

AX_PAVSS1

AX_PAVDD2

AX_PAVSS2

AX_AVDDAPLL

AX_AVSSAPLL

AX_AVDD_ADC1

AX_AVDD_ADC234

AX_AVSS_ADC1

AX_AVSS_ADC234

AX_AVDD3_ADC1

AX_AVDD3_ADC2

AX_AVDD3_BG_ASS

AX_AVSS_BG_ASS

1.2V POWER FOR STAND BY

AX_VSB12

AX_VSSC

3.3V POWER FOR STAND BY

AX_VSB33

3.3V POWER FOR

DIGITAL I/O

AX_VDDH

C112

C112

C113

C113

0.1uF

0.1uF

C114

C114

0.1uF

0.1uF

4

AX_AGND

AX_VDDMQ_LOCAL

107

116

128

142

104

110

125

U1D SVP-AX_256

U1D SVP-AX_256

VDDM94VDDM

VDDM

VDDM

FB3

FB3

1 2

+

+

FB4

FB4

1 2

+

+

C116

C116

+

+

10uF/16V

10uF/16V

VDDM

VDDC83VDDC

VDDC

23

150_Ohm_600mA

150_Ohm_600mA

150_Ohm_600mA

150_Ohm_600mA

FB5

FB5

1 2

150_Ohm_600mA

150_Ohm_600mA

198

PAVDD1

196

PAVSS1

201

PAVDD2

199

PAVSS2

230

PAVDD

231

PAVSS

49

AVDD_ADC1

40

AVDD_ADC2

32

AVDD_ADC3

47

AVDD_ADC4

48

AVSS_ADC1

39

AVSS_ADC234

31

AVSS_ADC234

46

AVSS_ADC234

53

AVDD3_ADC1

41

AVDD3_ADC2

59

AVDD3_BG_ASS

58

AVSS_BG_ASS

C108

C108

0.1uF

0.1uF

C110

C110

0.1uF

0.1uF

C115

C115

0.1uF

0.1uF

C109

C109

10uF/16V

10uF/16V

C111

C111

10uF/16V

10uF/16V

4

143

VSSM97VSSM

VSSM

VSSM

SVP-AX

SVP-AX

PQFP_256

PQFP_256

POWER/GROUND

POWER/GROUND

VDDC

VDDC

VDDC

VDDC

100

122

151

169

233

244

1.2V_SB

3.3V_SB

AX_VD33

AX_AVCC

11

15

AVCC3AVCC7AVCC

VSSM

VDDC

AVCC

(4/4)

(4/4)

VSSC84VSSC

VSSC

VSSC

22

101

119

AX_VD12_LOCAL

TMDS_GND6TMDS_GND10TMDS_GND14TMDS_GND

VSSC

VSSC

152

170

VSSC

181

AX_VD12

ANALOG PLL

1.2V POWER

AX_AVDDAPLL

C117

C117

0.1uF

0.1uF

AX_AVSSAPLL

ACR PLL 3.3V

POWER

AX_AVDD33AUDIO

C119

C119

0.1uF

0.1uF

AX_AVSS33AUDIO

3.3V POWER

FOR HP

AX_VCC33A_HP

C121

C121

0.1uF

AX_GND33A_HPAX_AVSS_BG_ASS

0.1uF

VSSC

191

18

VSSC

232

2

VSSC

243

245

C118

C118

10uF/16V

10uF/16V

C120

C120

10uF/16V

10uF/16V

PVCC(PLL)

VSSC

3

AX_PVCC

AX_PGND

AX_AVSS33AUDIO

AX_AVDD33AUDIO

25

24

1

AVSS33_AUDIO

AVDD33_AUDIO

TMDS_GND(PLL)

FB6

FB6

1 2

+

+

FB7

FB7

1 2

+

+

1 2

C122

C122

+

+

10uF/16V

10uF/16V

3

LVDS_VDDP

LVDS_VSSP

VCC33A_HP

GND33A_HP

150_Ohm_600mA

150_Ohm_600mA

150_Ohm_600mA

150_Ohm_600mA

FB8

FB8

LVDSVDDO

LVDSVDDO

LVDSVDDO

LVDSVSSO

LVDSVSSO

LVDSVSSO

VDDH

VDDH

VDDH

VDDR

VSSR

VCC33A

GND33A

VSB33

VSB12

VSB12_PLL

AX_VSSC

AX_VL12

AX_VCC33

AX_VCC33

150_Ohm_600mA

150_Ohm_600mA

216

202

217

228

215

203

214

229

93

162

246

114

112

AX_VCC33A_HP

62

AX_GND33A_HP

65

72

68

180

192

193

AGNDAGND

AX_LVDS_VDDP

AX_LVDS_VDDO

AX_LVDS_VSSP

AX_LVDS_VSSO

AX_VDDH

AX_VSSR

AX_VSSR

AX_VCC33A

AX_GND33A

AX_VSB33

AX_VSB12

1.2V POWER

FOR LVDS

AX_LVDS_VDDP

AX_LVDS_VSSP

3.3V POWER

FOR LVDS

AX_LVDS_VDDO

C125

C125

0.1uF

0.1uF

AX_LVDS_VSSO

C126

C126

0.1uF

0.1uF

C123

C123

0.1uF

0.1uF

R172

R172

33R

33R

C127

C127

0.1uF

0.1uF

2

AX_VDDMQ_LOCAL

C138

C138

22uF/16V

22uF/16V

C160

C160

1000pF

1000pF

1 2

C124

C124

+

+

10uF/16V

10uF/16V

1 2

C128

C128

+

+

10uF/16V

10uF/16V

2

+

+

AX_VD12_LOCAL

C146

C146

10uF/16V

10uF/16V

AX_VD12_LOCAL

C155

C155

0.1uF_DNS

0.1uF_DNS

150_Ohm_600mA

150_Ohm_600mA

1 2

C161

C161

0.1uF

0.1uF

AX_VD12

FB9

FB9

150_Ohm_600mA

150_Ohm_600mA

AX_VD33

FB10

FB10

150_Ohm_600mA

150_Ohm_600mA

1

C139

C139

0.1uF

0.1uF

+

+

FB33

FB33

C140

C140

0.1uF

0.1uF

C148

C148

C147

C147

0.1uF

0.1uF

0.1uF

0.1uF

C156

C156

0.1uF_DNS

0.1uF_DNS

C141

C141

0.1uF

0.1uF

C149

C149

0.1uF

0.1uF

0.1uF_DNS

0.1uF_DNS

AX_VDDMQ

C142

C142

0.1uF

0.1uF

C150

C150

0.1uF

0.1uF

C157

C157

C143

C143

390pF

390pF

C151

C151

470pF

470pF

0.1uF_DNS

0.1uF_DNS

C152

C152

470pF

470pF

C158

C158

C144

C144

390pF

390pF

470pF

470pF

C153

C153

0.1uF_DNS

0.1uF_DNS

HDMI Analog

3.3V POWER

AX_AVCC

C130

C130

C129

C129

0.1uF

0.1uF

0.1uF

0.1uF

AX_AGND

FB11 150_Ohm_600mAFB11 150_Ohm_600mA

C132

C132

C131

C131

0.1uF

0.1uF

0.1uF

0.1uF

HDMI PLL

3.3V POWER

FB12 150_Ohm_600mAFB12 150_Ohm_600mA

AX_PVCC

C134

C134

0.1uF

AX_PGND

0.1uF

C135

C135

+

+

10uF/16V

10uF/16V

AX_HDMI33

1 2

AUDIO AN 3.3V

POWER

AX_VCC33A

C136

C136

0.1uF

0.1uF

AX_GND33A

Schematict Name Rev

Schematict Name Rev

Schematict Name Rev

Size

Size

Size

Sheet

Sheet

Sheet

B

B

B

AX68 POWER

AX68 POWER

AX68 POWER

417

417

417

FB13

FB13

1 2

C137

C137

150_Ohm_600mA

150_Ohm_600mA

+

+

10uF/16V

10uF/16V

Title

Title

Title

AX68 Solution Design

AX68 Solution Design

AX68 Solution Design

Date:

Date:

of

of

of

Date:

1

C145

C145

0.1uF_DNS

0.1uF_DNS

C154

C154

470pF

470pF

C159

C159

AX_HDMI33

1 2

C133

C133

+

+

10uF/16V

10uF/16V

AX_VCC33

AGND

Friday, April 20, 2012

Friday, April 20, 2012

Friday, April 20, 2012

2.0.3

2.0.3

2.0.3

Page 11

5

4

3

2

1

AX_MD[0..15]

AX_MD0

4 5

AX_MD1

D D

C C

B B

AX_MD2

AX_MD3

AX_MD4

AX_MD5

AX_MD6

AX_MD7

AX_MD8

AX_MD9

AX_MD10

AX_MD11

AX_MD12

AX_MD13

AX_MD14

AX_MD15

3

2

1

RN11 22Rx4RN11 22Rx4

4 5

3

2

1

RN12 22Rx4RN12 22Rx4

4 5

3

2

1

RN13 22Rx4RN13 22Rx4

4 5

3

2

1

RN14 22Rx4RN14 22Rx4

6

7

8

6

7

8

6

7

8

6

7

8

100pF_DNS

100pF_DNS

100pF_DNS

100pF_DNS

DDR_DQ0

DDR_DQ1

DDR_DQ2

DDR_DQ3

DDR_DQ4

DDR_DQ5

DDR_DQ6

DDR_DQ7

DDR_DQ8

DDR_DQ9

DDR_DQ10

DDR_DQ11

DDR_DQ12

DDR_DQ13

DDR_DQ14

DDR_DQ15

AX_MCK

C170

C170

C171

C171

AX_MCK#

AX_MA[0..11]

AX_MA0

AX_MA1

AX_MA2

AX_MA3

AX_MA4

AX_MA5

AX_MA6

AX_MA7

AX_MA8

AX_MA9

AX_MA10

AX_MA11

R180

R180

56R

56R

AX_CK0_TRM

R181

R181

56R

56R

AX_DQM0

AX_DQS0 AX_DQS1

AX_DQM0

AX_DQS0 AX_DDR_DQS1

R105 22RR105 22R

AX_BA0

AX_BA1

AX_WE#

AX_CAS#

AX_RAS#

AX_CLKE

AX_MCK0

C172

C172

0.01uF

0.01uF

AX_MCK0#

DDR_DQ0

DDR_DQ1

DDR_DQ2

DDR_DQ3

DDR_DQ4

DDR_DQ5

DDR_DQ6

DDR_DQ7 DDR_DQ8

AX_DDR_DQS0

AX_BA0

AX_BA1

AX_WE#

AX_CAS#

AX_RAS#

AX_CKE

AX_MCK

AX_MCK#

U7 DDR_8Mx16

U7 DDR_8Mx16

2

DQ0

4

DQ1

5

DQ2

7

DQ3

8

DQ4

10

DQ5

11

DQ6

13

DQ7

20

LDM

16

LDQS

29

A0

30

A1

31

A2

32

A3

35

A4

36

A5

37

A6

38

A7

39

A8

40

A9

28

A10_AP

41

A11

42

A12_NC

26

BA0

27

BA1

21

WE#

22

CAS#

23

RAS#

24

CS#

44

CKE

45

CK

46

CK#

19

NC_19

50

NC_50

AX_VDDMQ AX_VDDMQ AX_VDDMQ AX_VDDMQ AX_VDDMQ

AX_VDDMQ AX_VDDMQ AX_VDDMQ

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

DQ9

DQ8

UDM

HDQS

TSOP66

TSOP66

NC_53

NC_43

NC_25

NC_17

NC_14

VREF

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDD

VDD

8Mx16 DDR

8Mx16 DDR

VDD

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSS

VSS

VSS

C175

C175

0.1uF

0.1uF

C181

C181

0.1uF

0.1uF

C176

C176

0.1uF

0.1uF

C182

C182

0.1uF

0.1uF

65

63

62

60

59

57

56

54

47

51

53

43

25

17

14

49

3

9

15

55

61

1

18

33

6

12

52

58

64

34

48

66

DDR_DQ15

DDR_DQ14

DDR_DQ13

DDR_DQ12

DDR_DQ11

DDR_DQ10

DDR_DQ9

AX_DQM1

DDR_VREFA

C177

C177

0.01uF

0.01uF

C183

C183

0.1uF

0.1uF

R182 22RR182 22R

C173

C173

0.1uF

0.1uF

AX_VDDMQ

C178

C178

0.01uF

0.01uF

AX_VDDMQ

R183

R183

1K 1%

1K 1%

R116 0R_DNSR116 0R_DNS

R184

R184

1K 1%

1K 1%

C179

C179

4700pF

4700pF

AX_DQS1

AX_DQM1

AX_DDR_VREFA

DDR DECOUPLING CAPACITORS

A A

Title

Title

Title

AX68 Solution Design

AX68 Solution Design

AX68 Solution Design

Schematict Name Rev

Schematict Name Rev

Schematict Name Rev

Size

Size

Size

5

4

3

2

Sheet

Sheet

Sheet

B

B

B

DDR MEMORY

DDR MEMORY

DDR MEMORY

Date:

Date:

of

of

of

517

517

517

Date:

Friday, April 20, 2012

Friday, April 20, 2012

Friday, April 20, 2012

1

2.0.3

2.0.3

2.0.3

Page 12

5

4

3

2

1

C223

C223

0.47uF

0.47uF

L8 5.6uH_1206L8 5.6uH_1206

C225

C225

15pF

15pF

R222

R222

C228

C228

1000pF

1000pF

1

TUNER&IF

TUNER&IF

TUNER&IF

Sheet

Sheet

Sheet

617

617

617

5V_TUNER

12

C224

C224

10uF/16V

10uF/16V

C226

C226

15pF

15pF

47R

47R

TUNER_AGC

C229

C229

30pF

30pF

C235 100pFC235 100pF

Add

2

4

Title

Title

Title

of

of

of

3

1 2

Y2

Y2

4.000MHz

4.000MHz

SIF

R213 1KR213 1K

P1

P1

shield box

shield box

3

AX68 Solution Design

AX68 Solution Design

AX68 Solution Design

Date:

Date:

Date:

1

TV_CVBS1

R221

R221

75R

75R

Friday, April 20, 2012

Friday, April 20, 2012

Friday, April 20, 2012

2.0.3

2.0.3

2.0.3

FB18

2

0.47uF

0.47uF

1000pF

1000pF

19

VPLL

C234

C234

0.47uF

0.47uF

FB18

1 2

17

18

AGND

150_Ohm_600mA

150_Ohm_600mA

C222

C222

1000pF

1000pF

Q9

Q9

MMBT3904

MMBT3904

R219 75RR219 75R

R220

R220

220R

220R

0.47uF_DNS

0.47uF_DNS

C227

CVBS

C227

16

NC(VC)

13

14

15

NC

REF

TAGC

12

R214 47RR214 47R

R211 47RR211 47R

R212 47RR212 47R

Schematict Name Rev

Schematict Name Rev

Schematict Name Rev

Size

Size

Size

B

B

B

D D

5V_TUNER

C201

C201

0.1uF

0.1uF

C206 0.1uFC206 0.1uF

C207 1000pFC207 1000pF

C C

150_Ohm_600mA

150_Ohm_600mA

FB16

FB16

12

ADDR: 0xC0

MAIN TUNER

C193

C193

100pF

100pF

C194

C194

100pF

100pF

R191 12KR191 12K

C192

C192

0.1uF

0.1uF

R192 47RR192 47R

U8 AFT7/W103U8 AFT7/W103

C195

C195

0.1uF

0.1uF

12

47R

47R

R193

R193

C198

C198

1000pF

1000pF

12

C196

C196

220uF/16V

220uF/16V

FB14

FB14

150_Ohm_600mA

150_Ohm_600mA

5V_TUNER

12

C199

C199

220uF/16V

220uF/16V

14

17

G3

G6

AGC1TU2AS3SCL4SDA5NC6VCC7ADC/NC8VT/NC9IF2/NC10IF111G1

G4

G7

15

18

B B

R190

R190

100K

100K

C190

C190

0.1uF

0.1uF

5V_SCL_MST

A A

5V_SDA_MST

12

C191

C191

10uF/16V

10uF/16V

TUNER_AGC

5

13

19

C208 0.047uFC208 0.047uF

G2

G8

G5

C209 1000pFC209 1000pF

12

16

C197

C197

12pF

12pF

0.16Amax

<--------

FB15

FB15

12

150_Ohm_2A

150_Ohm_2A

+5VA

C200

C200

0.1uF

0.1uF

C236

C236

0.01uF_DNS

0.01uF_DNS

4

R200 3KR200 3K

12

C211

C211

10uF/16V

10uF/16V

C213 1000pFC213 1000pF

R194

R194

75R

75R

1 2

R223 33K_DNSR223 33K_DNS

D5

D5

BZM55C33_DNS

BZM55C33_DNS

FB17

FB17

1 2

C202

C202

1000pF

1000pF

C205

C205

1000pF

1000pF

D2 BA277D2 BA277

BA277D3BA277

D3

Q5

Q5

MMBT3904

MMBT3904

R208 47RR208 47R

D4 BA277D4 BA277

R199

2.2K_DNS

2.2K_DNS

Q6

Q6

2SC388A

2SC388A

R1951KR195

1K

C237

C237

1000PF_DNS

1000PF_DNS

150_Ohm_600mA

150_Ohm_600mA

C203

C203

1000pF

1000pF

R2021KR202

1K

C212

C212

0.01uF_DNS

0.01uF_DNS

C215

C215

0.01uF_DNS

0.01uF_DNS

R196

R196

33R

33R

2

1

BAV99_DNS

BAV99_DNS

C204

C204

0.047uF

0.047uF

R203

R203

3.3K

3.3K

R206

R206

10K_DNS

10K_DNS

C210

C210

1000pF_DNS

1000pF_DNS

R198 470RR198 470RR199

2.2uH_1210

2.2uH_1210

C214 0.01uFC214 0.01uF

C239

C239

4700PF_DNS

4700PF_DNS

D6

D6

3

R201

R201

3.3K

3.3K

R204

R204

3.3K

3.3K

Q4

L5

L5

C238

C238

0.01uF_DNS

0.01uF_DNS

R205

R205

3.3K

3.3K

R207

R207

3.3K

3.3K

MMBT3904_DNSQ4MMBT3904_DNS

Q8

Q8

MMBT3904

MMBT3904

R197

R197

470R

470R

R224 100K_DNSR224 100K_DNS

Q7

Q7

MMBT3904_DNS

MMBT3904_DNS

C240

C240

100PF_DNS

100PF_DNS

3

R2091KR209

1K

L6

L6

1000nH_0603_DNS

1000nH_0603_DNS

Z1

Z1

HDAF389A2D

HDAF389A2D

IN11IN22GND3OUT14OUT2

Z2

Z2

HDVF389A1DC

HDVF389A1DC

IN11IN22GND3OUT14OUT2

C230

C230

1000pF

1000pF

1000nH_DNS

1000nH_DNS

C241

C241

1500PF_DNS

1500PF_DNS

R218

R218

330R

330R

C220

C220

C216

C216

1500pF

1500pF

0.22uF

0.22uF

C221

C221

100pF

100pF

5

24

SIF123SIF2

U9 TDA9885T/TDA9886TU9 TDA9885T/TDA9886T

5

VIF11VIF22OP13FMPLL4DEEM5AFD6DGND7AUD8TOP9SDA10SCL11SIOMAD

R210

R210

C231

C231

0.01uF

0.01uF

C232

C232

5.6K

5.6K

390pF

390pF

R225

L7

L7

R225

220_DNS

220_DNS

C242

C242

0.033uF_DNS

0.033uF_DNS

OPTIONAL FOR +33V

22

21

OP2

C217

C217

220uF/16V

220uF/16V

1 2

C218

C218

C219

C219

20

VP

AFC

C233

C233

0.01uF

0.01uF

TV_AUD_MONO

5V_SDA_MST

5V_SCL_MST

+5VA

Page 13

5

C251M0.1uF C251M0.1uF

C250M0.1uF C250M0.1uF

U10

U10

LA42102_DNS

LA42102_DNS

13

12

11

10

9

8

7

6

5

4

3

2

1

C262

C262

47uF/16V

47uF/16V

+

+

R2302.2R R2302.2R

C410

C410

10uF/16V

10uF/16V

D D

NC

+OUT1

-OUT1

PWR GND

-OUT2

+OUT2

VCC

MUTE

LA42102

LA42102

STBY

IN2

C C

B B

A A

PRE GND

RIPPLE FILTER

U27

U27

TDA7266

TDA7266

ROUT+

ROUT-/MUTE

+14V

RIN/REF

MUTE/ROUT

STBY

PW_GND/GND

S GND

NC/LOUT

LIN/+24V

+14V

LOUT-/REF

LOUT+

IN1

1

2

3

4

5

NC

6

7

8

9

10

11

NC

12

13

14

15

5

C252M0.1uF C252M0.1uF

C253M0.1uF C253M0.1uF

C2541500pF C2541500pF

C2551500pF C2551500pF

R2332.2R R2332.2R

R2322.2R R2322.2R

R2312.2R R2312.2R

R23475R R23475R

R242

R242

7.5K

7.5K

12

5V_SB

D231N4148 D231N4148

R439

R439

47K

47K

Q28

Q28

MMBT3904

MMBT3904

1

2 3

C2581500pF C2581500pF

R23975R R23975R

D221N4148 D221N4148

R44047K R44047K

C2591500pF C2591500pF

C267

C267

10uF/16V

10uF/16V

4

C256

C256

10uF/16V

10uF/16V

1 2

1 2

C257

C257

10uF/16V

10uF/16V

C260 1uFC260 1uF

C261 1uFC261 1uF

12

R249

R249

4.7K

4.7K

4

C2651500pF C2651500pF

R24310K R24310K

R2484.7K R2484.7K

D10

D10

1N4148

1N4148

R251 10KR251 10K

R250

R250

10K

10K

R235

R235

120R

120R

R236

R236

120R

120R

Q10

Q10

MMBT3904

MMBT3904

2 3

R245

R245

4.7K

4.7K

1N4148D81N4148

1

D8

MMBT3906

MMBT3906

MMBT3906

MMBT3906

R2370R_DNS R2370R_DNS

R2471KR247

1K

1N4148D91N4148

D9

R2380R_DNS R2380R_DNS

C2661500pF C2661500pF

10uF/16V

10uF/16V

Q12

Q12

Q13

Q13

ROUTROUT+

LOUTLOUT+

R24410K R24410K

C268

C268

2 3

2 3

2 3

1

1

CON4

CON4

1

2

3

4

4x2.5MM

4x2.5MM

TO SPEAKER

CON5

CON5

7x2.0MM

7x2.0MM

1

2

3

4

5

6

7

TO SIDE

AV&S-VIDEO BOARD

+12VA

C263

C263

0.01uF

0.01uF

R240

R240

15K

15K

R241

R241

15K

15K

Q11

Q11

MMBT3904

MMBT3904

1

R246

R246

4.7K

4.7K

D7

1N4148D71N4148

D12

D12

+

+

1N4148

1N4148

R254 220RR254 220R

R253 100RR253 100R

R252 220RR252 220R

D11 1N4148D11 1N4148

C269

C269

+

+

100uF/16V

100uF/16V

Audio_out_L

Audio_out_R

R255 220RR255 220R

3

3

L2_IN

R2_IN

SC2_LIN

SC2_RIN

MUTE

+5VA

+12VA

R256 470R_DNSR256 470R_DNS

R257 470R_DNSR257 470R_DNS

470pF_DNS

470pF_DNS

R264 470RR264 470R

R265 470RR265 470R

C280

C280

470pF

470pF

R272 470RR272 470R

R273 470RR273 470R

C288

C288

470pF

470pF

AGND

AGND

C272

C272

AGND

R266

R266

100K

100K

R274

R274

100K

100K

SCART1_LIN

SCART2_LIN

SCART1_RIN

SCART2_RIN

R258100K_DNS R258100K_DNS

C281

C281

470pF

470pF

C289

C289

470pF

470pF

TV_LIN

PC_LIN1

TV_RIN

PC_RIN1

R259100K_DNS R259100K_DNS

R275

R275

100K

100K

R267

R267

100K

100K

C273

C273

470pF_DNS

470pF_DNS

C278

C278

1uF

1uF

C279

C279

1uF

1uF

C286

C286

1uF

1uF

C287

C287

1uF

1uF

876

123

876

123

C270

C270

1uF_DNS

1uF_DNS

C271

C271

1uF_DNS

1uF_DNS

SCART2_LIN

SCART2_RIN

5

RN15

RN15

10K X 4

10K X 4

4

5

RN17

RN17

10K X 4

10K X 4

4

2

876

123

876

123

L3_IN

R260 470RR260 470R

R261 470RR261 470R

R3_IN

SC1_LIN

R268 470RR268 470R

R269 470RR269 470R

SC1_RIN

TV_AUD_MONO

R276 470RR276 470R

R277 470RR277 470R

5

RN16

RN16

10K X 4

10K X 4

4

U11

U11

1

2 Y0

5

2 Y1

2

2 Y2

4

2 Y3

12

1 Y0

14

1 Y1

15

1 Y2

1 Y3111-COM

74HC4052

74HC4052

5

RN18

RN18

10K X 4

10K X 4

4

Schematict Name Rev

Schematict Name Rev

Schematict Name Rev

Size

Size

Size

B

B

B

C276

C276

470pF

470pF

2-COM

VCC

GND

GND

INH

R262

R262

100K

100K

AGND

C284

C284

470pF

470pF

AGND

C292

C292

470pF

470pF

AGND

3

16

10

A

9

B

8

7

6

13

AUDIO

AUDIO

AUDIO

Sheet

Sheet

Sheet

717

717

717

C277

C277

470pF

470pF

C285

C285

R270

R270

100K

100K

470pF

470pF

R278

R278

C293

C293

100K

100K

470pF

470pF

+

+

C294

C294

100uF/16V

100uF/16V

R281 470RR281 470R

R282 470RR282 470R

Title

Title

Title

of

of

of

A4_LIN

A4_RINDVB_RIN

A2_LIN

A2_RIN

2

1

A3_LINDVB_LIN

C274

C274

1uF

1uF

C275

C275

1uF

1uF

R263

R263

100K

100K

C282

C282

1uF

1uF

C283

C283

1uF

1uF

R271

R271

100K

100K

C290

C290

1uF

1uF

C291

C291

1uF

1uF

R279

R279

100K

100K

R280 100RR280 100R

C295

C295

0.1uF

0.1uF

C296

C296

1uF

1uF

L/R_SW1 4

L/R_SW2 4

C297

C297

1uF

1uF

AX68 Solution Design

AX68 Solution Design

AX68 Solution Design

Date:

Date:

Date:

1

A3_RIN

SCART1_LIN

SCART1_RIN

+5VA

A1_LIN 6

A1_RIN 6

Friday, April 20, 2012

Friday, April 20, 2012

Friday, April 20, 2012

TV_LIN

TV_RIN

2.0.3

2.0.3

2.0.3

Page 14

5

4

3

2

1

SC1_CVBS#

CON6

CON6

21

SHD

20

VIN

19

VOUT

GND

17

GND

FB

15

R

GND

13

GND

RSV2

11

G

RSV1

9

GND

SW

7

B

AIL

5

GND

GND

3

AOL

AIR

1

AOR

SCART

SCART

L13 2.2uHL13 2.2uH

C308

C308

R300 10KR300 10K

C309

C309

100pF_DNS

100pF_DNS

R3012KR301

2K

18

16

14

12

10

8

6

4

2

R295

R295

75R

75R

SC2_Y_CVBS

D15

D15

ZENER_2V7

ZENER_2V7

1 2

SC1_LIN

SC1_RIN

20

18

16

14

12

10

8

6

4

2

CVBS_OUT1

SC1_R#

SC1_G#

SC1_B#

SC2_Y_CVBS#

SC2_LIN

SC2_RIN

100pF_DNS

100pF_DNS

D D

C301

C301

100pF_DNS

100pF_DNS

SC2_LOUT

SC2_ROUT

L10 2.2uHL10 2.2uH

L11 2.2uHL11 2.2uH

L12 2.2uHL12 2.2uH

C302

C302

100pF_DNS

100pF_DNS

100pF_DNS

100pF_DNS

CVBS_OUT2

DM1

DM1

ESD

ESD

C303

C303

100pF_DNS

100pF_DNS

C304

C304

21

19

17

15

13

11

9

7

5

3

1

C305

C305

100pF_DNS

100pF_DNS

CON7

CON7

SHD

VOUT

GND

R

GND

G

GND

B

GND

AOL

AOR

SCART

SCART

SC1_LOUT

SC1_ROUT

VIN

GND

FB

GND

RSV2

RSV1

SW

AIL

GND

AIR

SC1_R

SC1_G

SC1_B

C300

C300

100pF_DNS

100pF_DNS

C C

SC2_C/R

B B

L14 2.2uHL14 2.2uH

C306

C306

100pF_DNS

100pF_DNS

R291 100RR291 100R

68R_DNS

68R_DNS

R293 10KR293 10K

SC2_FS

R292

R292

R2942KR294

2K

ADC-slices

SC1_CVBS

C307

C307

100pF_DNS

100pF_DNS

SC1_FB

D13

D13

ZENER_2V7

ZENER_2V7

1 2

SC1_FS

D14

D14

ZENER_2V7

ZENER_2V7

1 2

AV

MODE

37.5...58.3%

of 1.304V

SCART

input

voltage

range

0...12 V

Middle

Wide screen

App

lication

0...16.7%

of 1.304V

LOW

TV mode A/V_MODE

voltage

range

at pin

0...1.304V

79.2...100%

of 1.304V

High

7189101112

CON8 RCA-6P_DNSCON8 RCA-6P_DNS

PCB EDGE

AV2_INPUT

1314

YPbPr2

23456

DM3

DM2

DM2

ESD_DNS

ESD_DNS

7189101112

CON9 RCA-6P_DNSCON9 RCA-6P_DNS

DM3

ESD_DNS

ESD_DNS

PCB EDGE

AV1_INPUT

1314

AV_OUTPUT

23456

DM4

DM4

ESD_DNS

ESD_DNS

AGND

SC2_Y_CVBS#

CVBS_OUT1

7

8 9

13

2

1

PCB Bottom View

SC1_CVBS#

SC1_R#

SC1_B#

SC1_G#

DM5

DM5

ESD_DNS

ESD_DNS

7

8 9

13

2

1

PCB Bottom View

SC2_RIN

SC2_LIN

SC1_ROUT

SC1_LOUT

3

3

10

4

SC1_RIN

SC1_LIN

10

4

1211

14

6

5

1211

14

6

5

+5VA+5VA

R310

C310

C310

0.1uF

0.1uF

A A

R302

R302

100R

100R

1

5

R304

R304

R303

R303

0R_DNS

0R_DNS

680R

680R

R307 75RR307 75R

23

Q14

Q14

2SA1015M-Y

2SA1015M-Y

C311

C311

470uF/16V

470uF/16V

+

+

R306

R306

100K

100K

CVBS_OUT1

4

C312

C312

0.1uF

0.1uF

1

23

2SA1015M-Y

2SA1015M-Y

R308

R308

100R

AX_CVBS_OUT2AX_CVBS_OUT1

100R

0R_DNS

0R_DNS

R309

R309

680R

680R

R312 75RR312 75R

Q15

Q15

3

R310

C313

C313

470uF/16V

470uF/16V

+

+

R313

R313

100K

100K

CVBS_OUT2

DM6

DM6

ESD_DNS

ESD_DNS

AGND

Title

Title

Title

AX68 Solution Design

AX68 Solution Design

AX68 Solution Design

Schematict Name Rev

Schematict Name Rev

Schematict Name Rev

Size

Size

Size

2

B

B

B

SCART&AV

SCART&AV

SCART&AV

Sheet

Sheet

Sheet

817

817

817

2.0.3

2.0.3

2.0.3

Date:

Date:

Date:

Friday, April 20, 2012

Friday, April 20, 2012

of

of

of

Friday, April 20, 2012

1

Page 15

5

HDMI INPUT

CON10

CON10

21

SHELL2

HSDA1

HSCL1

HSDA2

HSCL2

23

22

20

21

23

22

20

D D

C C

B B

HDMI_HOTPLUG

A A

SHELL4

SHELL3

SHELL1

HDMI_con

HDMI_con

CON27

CON27

SHELL2

SHELL4

SHELL3

SHELL1

HDMI_con

HDMI_con

R441 47KR441 47K

R442 47KR442 47K

R443 47KR443 47K

R444 47KR444 47K

R445 47KR445 47K

5

HP DET

+5V

GND

DDC DATA

DDC CLK

CE Remote

CK-

CK Shield

CK+

D0-

D0 Shield

D0+

D1-

D1 Shield

D1+

D2-

D2 Shield

D2+

HP DET

+5V

GND

DDC DATA

DDC CLK

CE Remote

CK-

CK Shield

CK+

D0-

D0 Shield

D0+

D1-

D1 Shield

D1+

D2-

D2 Shield

D2+

HDMI_VCC

NC

NC

3.3V_SB

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

R446 10KR446 10K

R448 10KR448 10K

R450 10KR450 10K

R452 NCR452 NC

R454 10KR454 10K

R456 10KR456 10K

RX1_HOTPLUG

2

112

1N4001

1N4001

D24

D24

CE_REMOTE

1RXC1RXC+

1RX01RX0+

1RX11RX1+

1RX21RX2+

RX2_HOTPLUG

2

112

1N4001

1N4001

D25

D25

CE_REMOTE

2RXC2RXC+

2RX02RX0+

2RX12RX1+

2RX22RX2+

PC0

PC1

PRE

OE#

S1

S2

HSDA1

HSCL1

HSDA2

HSCL2

R447 10KR447 10K

R449 10KR449 10K

R451 10KR451 10K

R453 10KR453 10K

R455 10KR455 10K

R457 10KR457 10K

HDMI1_5VIN

HDMI1_5VIN

4

1RXC1RXC+

1RX01RX0+

1RX11RX1+

1RX21RX2+

RX2_HOTPLUG

RX1_HOTPLUG

4

3.3V_SB

R320 1KR320 1K

HSDA2

HSCL2

B21

A21

3.3V_SB

B22

A22

B23

A23

3.3V_SB

B24

A24

3.3V_SB

R321 1KR321 1K

3

U28

U28

1

LINE1

2

LINE2

3

GND

4

LINE3

5

LINE4

Rclamp0524P

Rclamp0524P

U29

U29

1

LINE1

2

LINE2

3

GND

4

LINE3

5

LINE4

Rclamp0524P

Rclamp0524P

58

60

59

U32

U32

NC

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

GND_10

VCC_9

HPD2

SDA2

SCL2

GND_11

GND_12

B21

A21

VCC_10

B22

A22

GND_13

B23

A23

VCC_11

B24

A24

GND_14

VCC_12

HPD1

PC01SDA12SCL13GND_14B115A116VCC_17B128A129GND_210B1311A1312VCC_213B1414A1415GND_316VCC_317VSADJ18PRE19PC1

PC0

HSCL1

HSDA1

0.1uF

C411

C411

0.01uF

0.01uF

C412

C412

0.001uF

0.001uF

C413

C413

0.1uF

0.1uF

0.1uF

3.3V_SB

56

B3457A34

B11

C414

C414

VCC_8

A11

0.01uF

0.01uF

55

NC1

NC2

GND

NC3

NC4

NC1

NC2

GND

NC3

NC4

3.3V_SB

C415

C415

53

B3354A33

PS201

PS201

B12

0.001uF

0.001uF

10

9

8

7

6

10

9

8

7

6

3.3V_SB

49

52

47

46

45

50

B3148A31

B3251A32

SCL3

SDA3

VCC_7

0.1uF

0.1uF

B13

C417

C417

A13

0.01uF

0.01uF

B14

3.3V_SB

0.001uF

0.001uF

C418

C418

GND_8

A14

0.1uF

0.1uF

C419

C419

3

GND_9

A12

C416

C416

3.3V_SB

44

43

HPD3

3.3V_SB

R3932.5K_1%R3932.5K_1%

0.01uF

0.01uF

C420

C420

OE#

41

42

NC

OE*

VCC_6

HPDSINK

SDA_SINK

SCL_SINK

GND_7

GND_6

VCC_5

GND_5

VCC_4

GND_4

20

PC1

PRE

0.001uF

0.001uF

C421

C421

C422

C422

B11

A11

B12

A12

B13

A13

B14

A14

Z1

Y1

Z2

Y2

Z3

Y3

Z4

Y4

S3

S2

S1

3.3V_SB

0.1uF

0.1uF

C423

C423

0.01uF

0.01uF

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

0.001uF

0.001uF

C424

C424

HDMI_HOTPLUG

RX5V1_DDC_SDA

RX5V1_DDC_SCL

0.1uF

0.1uF

C425

C425

3.3V_SB

3.3V_SB

S2

S1

0.01uF

0.01uF

C426

C426

C427

C427

0.001uF

0.001uF

C428

C428

2RXC2RXC+

2RX02RX0+

2RX12RX1+

2RX22RX2+

0.1uF

0.1uF

C429

C429

0.01uF

0.01uF

HDMI_HOTPLUG

HDMI_RXCHDMI_RXC+

HDMI_RX0HDMI_RX0+

HDMI_RX1HDMI_RX1+

HDMI_RX2HDMI_RX2+

S2

S1

0.001uF

0.001uF

C430

C430

C431

C431

2

I2C Address: 1010 000x

0.1uF

0.1uF

0.01uF

0.01uF

0.001uF

0.001uF

C432

C432

C433

C433

C434

C434

2

R322

R322

4.7K

4.7K

U30

U30

1

LINE1

2

LINE2

3

GND

4

LINE3

5

LINE4

Rclamp0524P

Rclamp0524P

U31

U31

1

LINE1

2

LINE2

3

GND

4

LINE3

5

LINE4

Rclamp0524P

Rclamp0524P

R323

R323

4.7K

4.7K

10

NC1

9

NC2

8

GND

7

NC3

6

NC4

10

NC1

9

NC2

8

GND

7

NC3

6

NC4

3.3V_SB

RX3V1_DDC_SCL

3.3V_SB

RX3V1_DDC_SDA

HDMI_VCC

U12

U12

1

2

3

RX5V1_DDC_SDA

RX5V1_DDC_SCL

Schematict Name Rev

Schematict Name Rev

Schematict Name Rev

Size

Size

Size

A0

VCC

A1

A2

SCL

VSS4SDA

24LC02

24LC02

B

B

B

8

7

WP

6

5

HDMI INTERFACE

HDMI INTERFACE

HDMI INTERFACE

Sheet

Sheet

Sheet

917

917

917

3.3V_SB

R325

R325

4.7K

4.7K

2

3.3V_SB

R326

R326

4.7K

4.7K

2

150_Ohm_600mA

150_Ohm_600mA

C315 0.1uFC315 0.1uF

R324

R324

4.7K

4.7K

3-PIN_HEADER

3-PIN_HEADER

Title

Title

Title

AX68 Solution Design

AX68 Solution Design

AX68 Solution Design

of

of

of

B21

A21

B22

A22

B23

A23

B24

A24

1

1

FB19

FB19

JP2

JP2

1

2

3

Date:

Date:

Date:

1

RX5V1_DDC_SCL

3

Q17

Q17

2SK1399

2SK1399

Q18

Q18

2SK1399

2SK1399

RX5V1_DDC_SDA

3

D16

D16

CMPSH-3C

CMPSH-3C

12

3

Friday, April 20, 2012

Friday, April 20, 2012

Friday, April 20, 2012

1

2

HDMI1_5VIN

1

5V_SB

2.0.3

2.0.3

2.0.3

Page 16

5

7189101112

CON21 RCA-6PCON21 RCA-6P

7

8 9

D D

1314

13

2

1

10

4

3

PCB Bottom View

23456

4

PCB EDGEPCB EDGE

1211

14

6

5

R3_IN

L3_IN

3

R334

R336

R336

22R

22R

R337

R337

22R

22R

R334

2.0K

2.0K

TXD0

FB20

FB20

1 2

150_Ohm_600mA

150_Ohm_600mA

FB21

FB21

1 2

150_Ohm_600mA

150_Ohm_600mA

R333

R333

2.0K

2.0K

R335 22R_DNSR335 22R_DNS

VGA_SDA_IN

VGA_SCL_IN

2

CON14

CON14

16

DB15_female

DB15_female

G

6

6

11

11

12

12

13

13

14

14

15

15

1

1

7

7

2

2

8

8

3

3

9

9

4

4

10

10

5

5

G

17

R338 22_DNSR338 22_DNS

DM17

DM17

ESD

ESD

RXD0

DM18

DM18

ESD

ESD

DM19

DM19

ESD

ESD

C326

C326

470pF

470pF

1

C327

C327

470pF

470pF

C328

C328

470pF

470pF

PC_RIN

PC_GIN

PC_BIN

MAIN_PR1

MAIN_PB1

MAIN_Y1

R352 0RR352 0R

C321

C321

100pF_DNS

100pF_DNS

AGND

CON12

CON12

CONN_S-Video_7_P

CONN_S-Video_7_P

4

2

6

5

7

AGND

SIDE_AV

R331 0RR331 0R

C322

DM13

DM13

ESD

ESD

3

1

DM16

DM16

ESD

ESD

C322

100pF_DNS

100pF_DNS

R332 0RR332 0R

C324

C324

100pF_DNS

100pF_DNS

DM12

DM12

ESD

ESD

R330 0RR330 0R

C320

C320

100pF_DNS

100pF_DNS

4

C C

DM7

DM7

DM8

DM8

DM9

ESD

ESD

L2_IN

R2_IN

DM9

ESD

ESD

ESD

ESD

CON28

CON28

SIDE AV&S-VIDEO IN

B B

1

2

3

4

5

6

7

7x2.0MM

7x2.0MM

AGND

A A

5

DM11

DM11

DM10

DM10

ESD

ESD

ESD

ESD

AGND

R355 0R_DNSR355 0R_DNS

R356 0R_DNSR356 0R_DNS

R357 0R_DNSR357 0R_DNS

SIDE_AV

SV_Y_MP

SV_C_MP

R187

R187

33R

33R

AGND

AGND

3

R353 0RR353 0R

C323

C323