1

Z86C90/C89

ROMLESS CMOS

Z8® 8-BIT MICROCONTROLLER

The Z86C90/C89 CCP™ (Consumer Controller Processor) introduces a new level of sophistication to single-chip architecture.

The Z86C90/C89 are ROMless members of the Z8 single-chip

microcontroller family with 236 bytes of general purpose RAM.

The only difference that exists between the Z86C89 and the

Z86C90 is that the on-chip oscillator of the Z86C89 can accept an

external RC network or other external clock source, while the

Z86C90's on-chip oscillator accepts a crystal, ceramic resonator,

LC, or external clock source drive. The CCP controllers are

housed in a 40-pin DIP, 44-pin Leaded Chip Carrier, or a 44-pin

Quad Flat Pack, and are CMOS compatible. The CCP offers the

use of external memory which enables this Z8 microcomputer to

be used where code flexibility is required. Zilog's CMOS microcomputer offers fast execution, efficient use of memory, sophisticated interrupts, input/output bit manipulation capabilities, and

easy hardware/software system expansion along with low cost

and low power consumption.

The Z86C90/C89 architecture is based on Zilog's 8-bit

microcontroller core with an Expanded Register File to allow

access to register mapped peripheral and I/O circuits. The CCP

offers a flexible I/O scheme, an efficient register and address

space structure, and a number of ancillary features that are useful

in many industrial, automotive, computer peripherals, and advanced scientific applications.

The CCP applications demand powerful I/O capabilities. The

Z86C90/C89 fulfills this with 32 pins dedicated to input and

output. These lines are grouped into four ports. Each port consists

of eight lines, and is configurable under software control to

provide timing, status signals, parallel I/O with or without handshake, and an address/data bus for interfacing external memory.

There are four basic address spaces available to support this wide

range of configurations: Program Memory, Register File, Data

Memory, and Expanded Register File. The Register File is

composed of 236 bytes of general purpose registers, four I/O port

registers, and fifteen control and status registers. The Expanded

Register File consists of two control registers.

To unburden the program from coping with the real-time problems, such as counting/timing and data communication, the

Z86C90/C89 offers two on-chip counter/timers. Included are a

large number of user selectable modes, and two on-board comparators to process analog signals with a common reference

voltage (see Functional Block Diagram).

Notes:

All Signals with a preceding front slash, "/", are active Low, e.g.: B//W

(WORD is active Low); /B/W (BYTE is active Low, only).

Power connections follow conventional descriptions below:

Connection Circuit Device

Power V

CC

V

DD

Ground GND V

SS

CUSTOMER PROCUREMENT SPECIFICATION

GENERAL DESCRIPTION

DC-4054-01 (10-17-91)

2

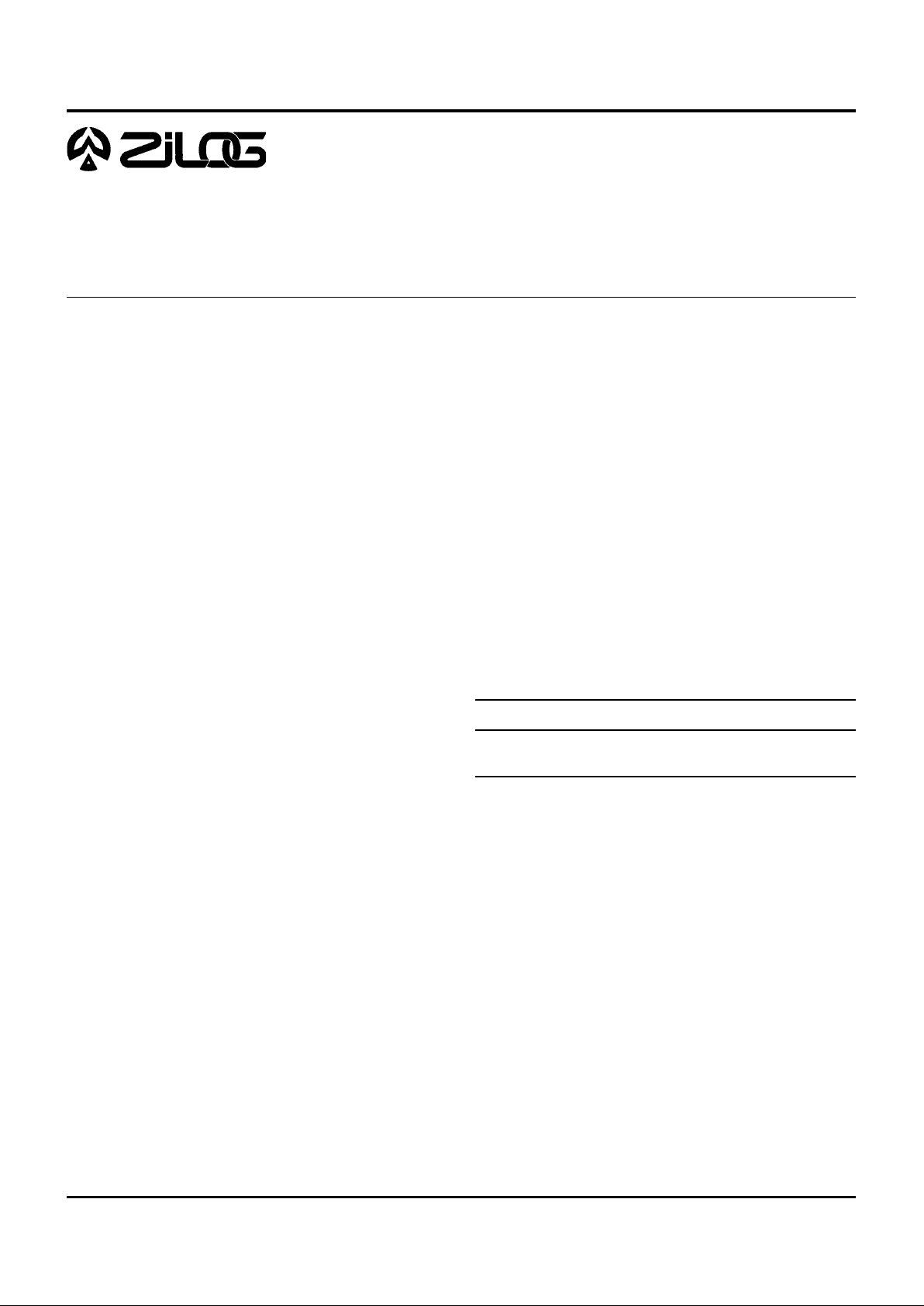

GENERAL DESCRIPTION (Continued)

Port 3

Counter/

Timers (2)

Interrupt

Control

Two Analog

Comparators

Port 2

I/O

(Bit Programmable)

ALU

FLAGS

Register

Pointer

Register File

256 x 8-Bit

Machine Timing

&

Instruction Control

Program

Counter

Vcc GND XTAL

44

Port 0

Output Input

Address or I/O

(Nibble Programmable)

8

Port 1

Address/Data or I/O

(Byte Programmable)

/AS /DS

R//W

/RESET

RESET

WDT, POR

Functional Block Diagram

3

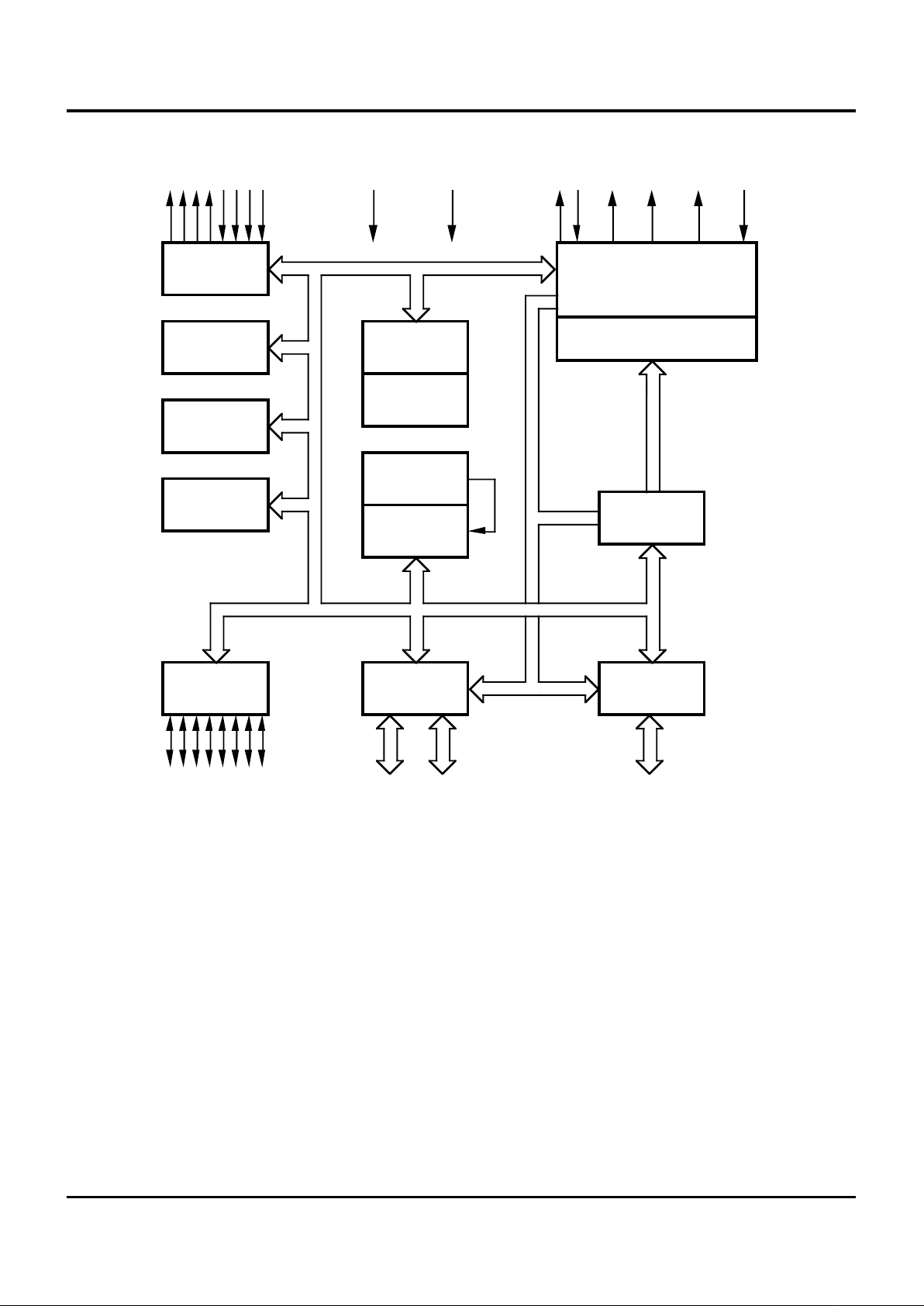

1

2

9

3

4

5

6

7

8

40

39

38

37

36

35

34

33

32

/DS

P24

P12

P23

P22

P21

P20

P03

P13

R//W

XTAL2

P27

P04

P05

P06

P14

31

30

29

28

27

14

10

11

12

13

XTAL1

VCC

P16

P17

P25

GND

P02

P11

P10

P01

Z86C90/C89

DIP

15 26

25

24

23

22

21

20

16

17

18

19

P15

P07

P26

P31

P34

/AS

P33

P32

P36

P00

P30

P37

P35

/RESET

PIN DESCRIPTION

40-Pin DIP Pin Assignments

4

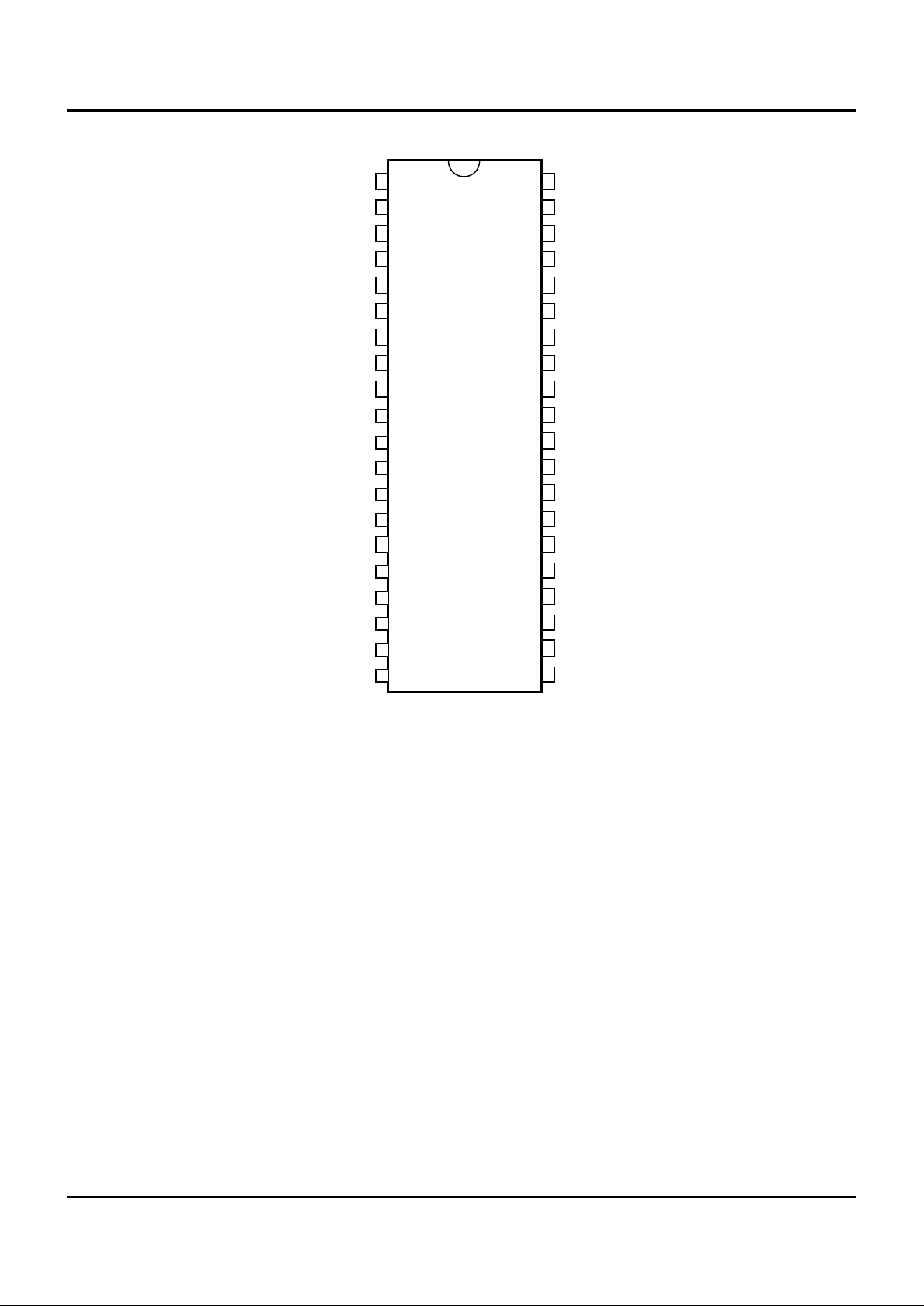

PIN DESCRIPTION (Continued)

P20

P03

P13

P12

GND

GND

P02

P11

P10

P01

P00

P05

P06

P14

P15

P07

VCC

VCC

P16

P17

P30

P36

P37

P35

/RESET

GND

/AS

P34

P33

P32

P31

P21

P22

P23

P24

/DS

N/C

R//W

P25

P26

P27

P04

XTAL1

XTAL2

7

8

9

10

11

12

13

14

15

16

17

38

37

36

35

34

33

32

31

30

29

39

Z86C90/C89

PLCC

6543214443424140

18 19 20 21 22 23 24 25 26 27 28

44-Pin PLCC Pin Assignments

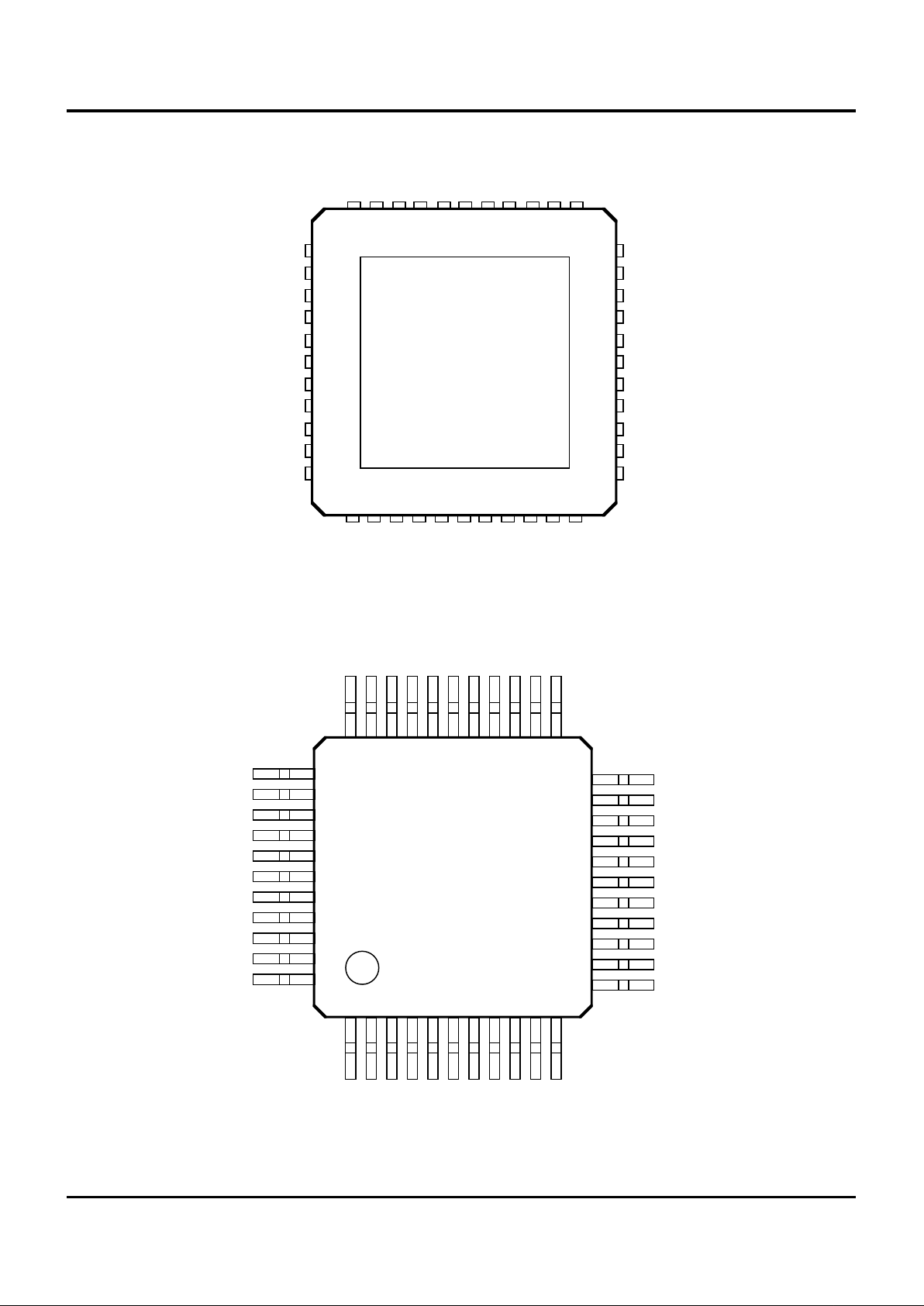

34

35

36

37

38

39

40

41

42

43

44

21

20

19

18

17

16

15

14

13

12

22

33 32 31 30 29 28 27 26 25 24 23

1234567891011

Z86C90/C89

QFP

P20

P03

P13

P12

GND

GND

P02

P11

P10

P01

P00

P21

P22

P23

P24

/DS

N/C

R//W

P25

P26

P27

P04

P30

P36

P37

P35

/RESET

GND

/AS

P34

P33

P32

P31

P05

P06

P14

P15

P07

VCC

VCC

P16

P17

XTAL1

XTAL2

44-Pin QFP Pin Assignments

5

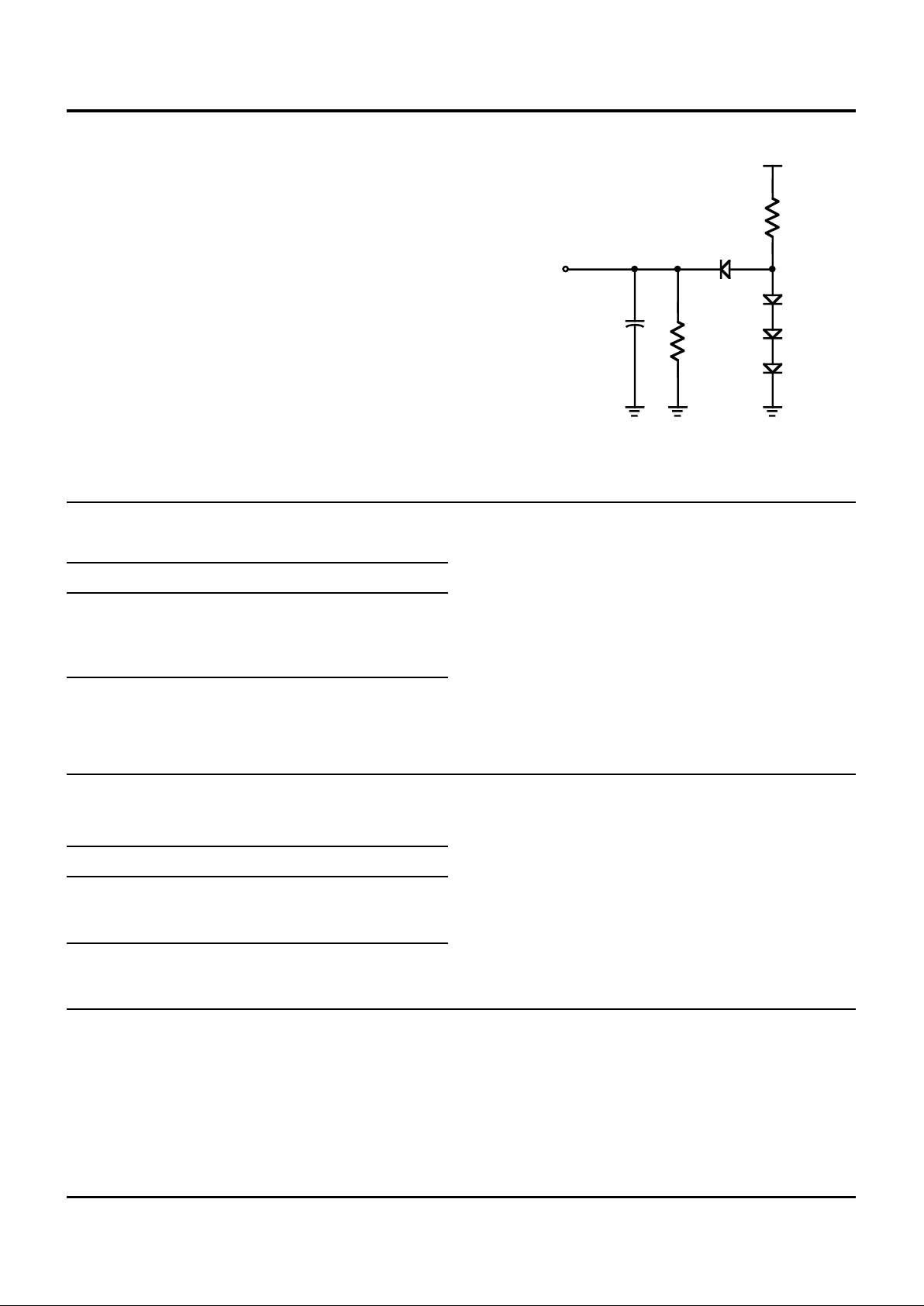

STANDARD TEST CONDITIONS

The characteristics listed below apply for standard test conditions

as noted. All voltages are referenced to GND. Positive current

flows into the referenced pin (Test Load Diagram).

Symbol Description Min Max Units

V

CC

Supply Voltage (*) -0.3 +7.0 V

T

STG

Storage Temp -65° +150° C

T

A

Oper Ambient Temp † C

Power Dissipation 2.2 W

Notes:

* Voltage on all pins with respect to GND.

† See Ordering Information.

Stress greater than those listed under Absolute Maximum Rat-

ings may cause permanent damage to the device. This is a stress

rating only; operation of the device at any condition above those

indicated in the operational sections of these specifications is not

implied. Exposure to absolute maximum rating conditions for an

extended

period may affect device reliability.

+5V

From Output

Under Test

150 pF

9.1 KΩ

2.1 KΩ

ABSOLUTE MAXIMUM RATINGS

Test Load Diagram

CAPACITANCE

TA = 25°C, VCC = GND = 0V, f = 1.0 MHz, unmeasured pins to GND

Parameter Max

Input capacitance 12 pF

Output capacitance 12 pF

I/O capacitance 12 pF

PLEASE NOTE

These devices will not operate in extended timing mode. Set Register 248, D5 = 0.

Loading...

Loading...