Yamaha AD-8-HR Service Manual

AD8HR

AD CONVERTER WITH REMOTE PREAMP

SERVICE MANUAL

011722

PA

200403-260000

CONTENTS

SPECIFICATIONS .................................................. 3

DIMENSIONS .................................................. 6

PANEL LAYOUT .................................... 7

CIRCUIT BOARD LAYOUT ................. 8

DISASSEMBLY PROCEDURE .............................. 9

LSI PIN DESCRIPTION .............................. 13

IC BLOCK DIAGRAM ................................... 19

CIRCUIT BOARD .......................................... 22

GAIN SETUP ..................................................... 30

TEST PROGRAM ............................. 32/43

INSPECTIONS ................................................. 54/58

UPGRADE ........................................ 62/65

ERROR MESSAGES ............................. 68

PARTS LIST

BLOCK DIAGRAM

CIRCUIT DIAGRAM

Copyright (c) Yamaha Corporation. All rights reserved. PDF-K6341 ’04.03

(目次)

(総合仕様)

(寸法図)

(パネルレイアウト)

(ユニットレイアウト)

(分解手順)

(LSI端子機能表)

(ICブロック図)

(シート基板図)

(GAIN設定)

(テストプログラム)

(総合検査)

(バージョンアップ)

(エラーメッセージ)

(ブロックダイアグラム)

(回路図)

HAMAMATSU, JAPAN

1

AD8HR

IMPORTANT NOTICE

This manual has been provided for the use of authorized Yamaha Retailers and their service personnel. It has been assumed that basic

service procedures inherent to the industry, and more specifically Yamaha Products, are already known and understood by the users,

and have therefore not been restated.

WARNING : Failure to follow appropriate service and safety procedures when servicing this product may result in personal injury,

IMPORTANT : This presentation or sale of this manual to any individual or firm does not constitute authorization certification,

The data provided is belived to be accurate and applicable to the unit(s) indicated on the cover. The research engineering, and service

departments of Yamaha are continually striving to improve Yamaha products. Modifications are, therefore, inevitable and changes in

specification are subject to change without notice or obligation to retrofit. Should any discrepancy appear to exist, please contact the

distributor’s Service Division.

WARNING : Static discharges can destroy expensive components. Discharge any static electricity your body may have accumulated

destruction of expensive components and failure of the product to perform as specified. For these reasons, we advise

all Yamaha product owners that all service required should be performed by an authorized Yamaha Retailer or the

appointed service representative.

recognition of any applicable technical capabilities, or establish a principal-agent relationship of any form.

by grounding yourself to the ground bus in the unit (heavy gauge black wires connect to this bus.)

IMPORTANT : Turn the unit OFF during disassembly and parts replacement. Recheck all work before you apply power to the unit.

WARNING: CHEMICAL CONTENT NOTICE!

The solder used in the production of this product contains LEAD. In addition, other electrical/electronic and/or plastic (Where applicable)

components may also contain traces of chemicals found by the California Health and Welfare Agency (and possibly other entities) to cause

cancer and/or birth defects or other reproductive harm.

DO NOT PLACE SOLDER, ELECTRICAL/ELECTRONIC OR PLASTIC COMPONENTS IN YOUR MOUTH FOR ANY REASON WHAT SO EVER!

Avoid prolonged, unprotected contact between solder and your skin! When soldering, do not inhale solder fumes or expose eyes to solder/

flux vapor!

If you come in contact with solder or components located inside the enclosure of this product, wash your hands before handling food.

LITHIUM BATTERY HANDLING

This product uses a lithium battery for memory back-up.

WARNING : Lithium batteries are dangerous because they can be exploded by improper handling. Observe the following precautions

Leave lithium battery replacement to qualified service personnel.

Always replace with batteries of the same type.

When installing on the PC board by soldering, solder using the connection terminals provided on the battery cells.

Never solder directly to the cells. Perform the soldering as quickly as possible.

Never reverse the battery polarities when installing.

Do not short the batteries.

Do not attempt to recharge these batteries.

Do not disasemble the batteries.

Never heat batteries or throw them into fire.

ADVARSEL!

Lithiumbatteri-Eksplosionsfare ved fejlagtig håndtering. Udskiftning må kun ske med batteri af samme fabrikat og type. levér det brugte batteri tilbage

til leverandren.

VARNING

Explosionsfara vid felaktigt batteribyte.

Använd samma batterityp eller en ekvivalent typ som rekommenderas av apparattillverkaren.

Kassera använt batteri enligt fabrikantens instruktion.

VAROITUS

Paristo voi räjähtää, jos se on virheellisesti asennettu.

Vaihda paristo ainoastaan laitevalmistajan suosittelemaan tyyppiiin.

Hävitä käytetty paristo valmistajan ohjeiden mukaisesti.

The following information complies with Dutch official Gazette 1995. 45; ESSENTIALS OF ORDER ON THE COLLECTION OF BATTERIES.

• Please refer to the diassembly procedure for the removal of Back-up Battery.

• Leest u voor het verwijderen van de backup batterij deze beschrijving.

when handling or replacing lithium batteries.

リチウム電池の取り扱い

<注意>

リチウム電池を誤って交換すると爆発する危険があります。交換する場合は、サービスマニュアルで指定された部品を使用して

ください。

WARNING

Components having special characteristics are marked and must be replaced with parts having specification equal to those

originally installed.

印の商品は、安全を維持するために重要な部品です。交換する場合は、安全のために必ず指定の部品をご使用ください。

2

AD8HR

SPECIFICATIONS

(総合仕様)

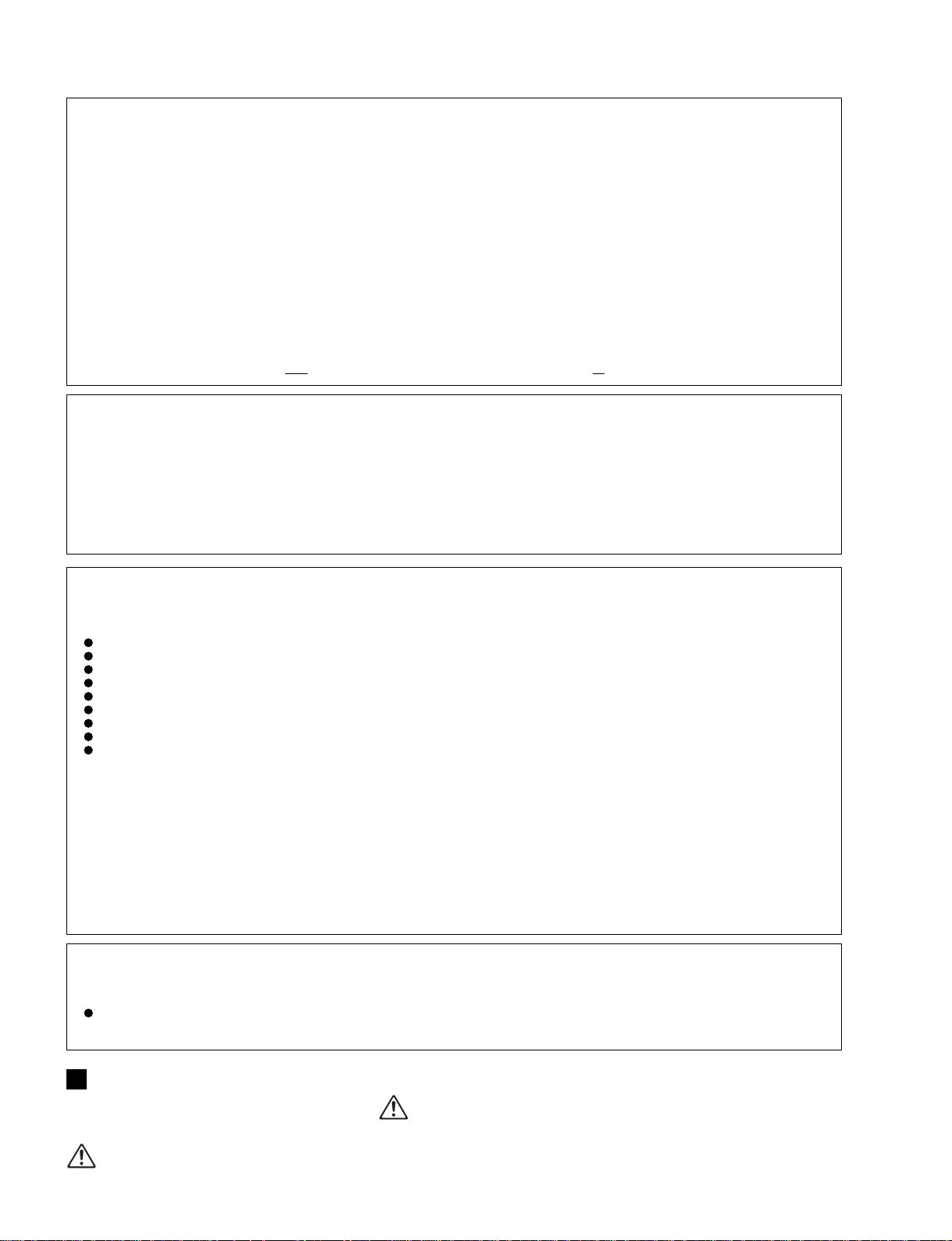

General Specifications

Analog Input

INPUT 1–8

XLR-3-31 Balanced

AD converter 24-bit linear

128-times Oversampling

Digital Output

DIGITAL OUT A, B

D-Sub 25-pin Balanced

Connectors

WORD CLOCK IN (75Ω Auto Terminated): BNC

WORD CLOCK OUT: BNC

HA REMOTE (PC-RS422): D-Sub 9-pin with PC-RS422

HA REMOTE (RS422): D-Sub 9-pin

switch

Controls

+48V Master Switch

GAIN/DATA encoder

Keys

[WORD CLOCK]

[SELECT1]–[SELECT8]

[+48V]

[HPF]

I/O Characteristics

Analog Input Specifications

LEDs

WORD CLOCK [44.1kHz]/[48kHz]/[88.2kHz]/[96kHz]

/[WORD CLOCK IN]/[DIGITAL OUT A]

LEVEL METER 1–8 8x6 Segment

SELECT 1–8

+48V 1–8, Selected Channel

HPF 1–8, Selected Channel

GAIN/DATA Display 7seg x3

Functions

HPF Frequency

GAIN

INPUT GAIN TRIM –1.5 dB to 1.5 dB (0.1 dB step)

AES/EBU Higher Sampling Rate Data Output Format

Panel Lock

Panel Brightness 7 steps

20Hz–600Hz

–62 dB to +10 dB (1 dB step)

Double Speed / Double Channel

Miscellaneous

Power Requirements 100 V 35 W, 50/60 Hz

Dimensions (HxDxW) 45 x 383.5 x 480 mm

Net Weight 5 kg

Operation free-air temperature range

Storage temperature –20 to 60 °C

Accessories AC Cable

J:

120 V 35 W, 60 Hz

U/C:

230 V 35 W, 50 Hz

Others:

5 to 40 °C

(J: 3P/2P AC Plug Adaptor)

Rubber Feet x 4

Owner’s Manual

Input T erminals GAIN

INPUT 1–8

*1. XLR-3-31 type connectors are balanced. (1=GND, 2=HOT, 3=COLD)

*2. In these specifications, when dBu represents a specific voltage, 0dBu is referenced to 0.775 Vrms.

*3. AD converters are 24-bit linear, 128-times oversampling.

–62 dB

+10 dB +10 dBu (2.45 V) +30 dBu (24.5 V)

Actual Load

Impedance

3kΩ

For Use With

Nominal

50~600 Mics &

600 Lines

Nominal Max. before clip

–62 dBu (615 µV) –42 dBu (6.15 mV)

Input level

Digital I/O Specifications

Input/Output Terminals Format Level Connector in Console

Input 1/2 (word clock only)

Output 1–8 x 2

HA REMOTE x 2 — RS422 D-SUB 9p Male

WORD CLOCK IN — TTL / 75Ω BNC

WORD CLOCK OUT — TTL / 75Ω BNC

*1. Input 1/2 on DIGITAL OUT A can be selected for word clock master.

*2. Fs= 44.1, 48, 88.2 and 96 kHz is supported.

*3. Double Channel mode is supported (Fs= 88.2, 96 kHz).

*4. When locked to the word clock received via WORD CLOCK IN, the word clock will be output from WORD CLOCK OUT.

*1

AES/EBU RS422 D-SUB 25p Female

Connector

XLR-3-31 type

(Balanced)

*1

3

AD8HR

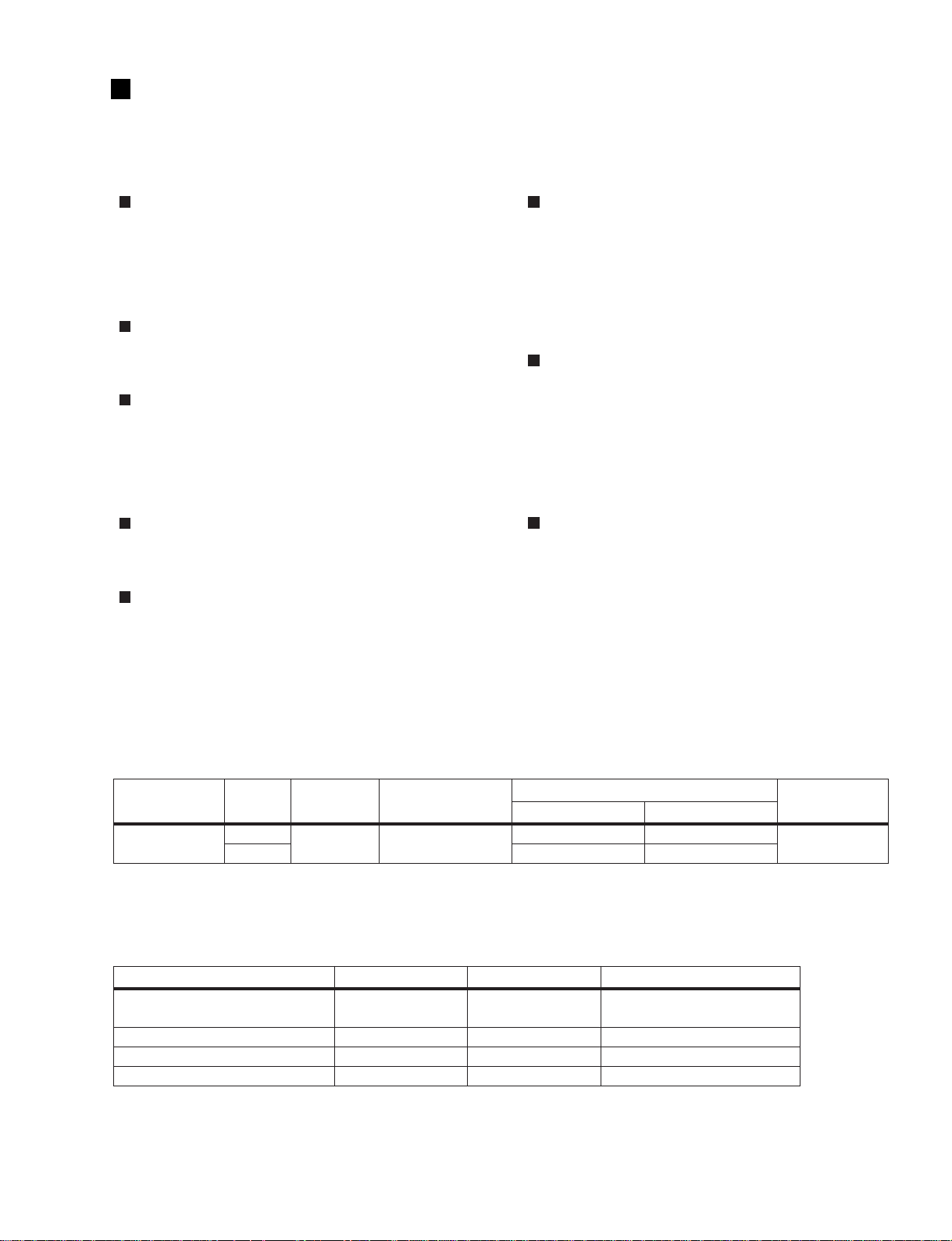

Electrical Characteristics

Measured at DIGITAL OUT. Output impedance of signal generator: 150Ω.

Frequency Response

fs=44.1kHz or 48kHz @20Hz–20kHz, with reference to –1dBFs @1kHz

Input Output Conditions MIN TYP MAX UNITS

INPUT 1–8 DIGITAL OUT 1–8 GAIN: –62 dB –3 1 dB

INPUT 1–8 DIGITAL OUT 1–8 GAIN: +10 dB –1.5 1 dB

fs=88.2kHz or 96kHz@20Hz-40kHz, with reference to –1dBFs @1kHz

Input Output Conditions MIN TYP MAX UNITS

INPUT 1–8 DIGITAL OUT 1–8 GAIN: –62 dB –3 1 dB

INPUT 1–8 DIGITAL OUT 1–8 GAIN: +10 dB –1.5 1 dB

Gain Error @1kHz

Input Output Conditions MIN TYP MAX UNITS

INPUT 1–8 DIGITAL OUT 1–8 GAIN: –62dB to +10dB –1 1 dB

Total Harmonic Distortion

fs=44.1kHz or 48kHz

Input Output Conditions MIN TYP MAX UNITS

INPUT 1–8 DIGITAL OUT 1–8 –1 dBFs output @1kHz GAIN: –62 dB 0.05 %

INPUT 1–8 DIGITAL OUT 1–8 –1 dBFs output @1kHz GAIN: +10 dB 0.01 %

fs=88.2kHz or 96kHz

Input Output Conditions MIN TYP MAX UNITS

INPUT 1–8 DIGITAL OUT 1–8 –1 dBFs output @1kHz GAIN: –62 dB 0.05 %

INPUT 1–8 DIGITAL OUT 1–8 –1 dBFs output @1kHz GAIN: +10 dB 0.01 %

Hum & Noise

fs=44.1kHz, 48kHz, 88.2kHz or 96kHz

Input Output Conditions MIN TYP MAX UNITS

INPUT 1–8 DIGITAL OUT 1–8 Rs=150Ω, GAIN: –62 dB –80 dBFs

INPUT 1–8 DIGITAL OUT 1–8 Rs=150Ω, GAIN: +10 dB –110 dBFs

* Hum & Noise are measured with an A-weighting filter.

EIN Measured with DA824 EIN=Equivalent Input Noise

Input Output Conditions MIN TYP MAX UNITS

INPUT 1–8 DIGITAL OUT 1–8 Rs=150Ω, GAIN: –62 dB –128 dB

* EIN is measured with a 6 dB/octave filter @12.7 kHz; equivalent to a 20 kHz filter with infinite dB/octave attenuation.

Dynamic Range

Input Output Conditions MIN TYP MAX UNITS

INPUT 1–8 DIGITAL OUT 1–8 GAIN: +10 dB 110 dB

* Dynamic Range is measured with an A-weighting filter.

Crosstalk @1kHz

From/To To/From Conditions MIN TYP MAX UNITS

CH N CH (N-1) or (N+1) adjacent inputs GAIN: +10dB –80 dB

Phantom Voltage

Output Conditions MIN TYP MAX UNITS

INPUT 1–8 hot & cold: No load 46 48 50 V

4

LED Level Meter

Input Output Conditions MIN TYP MAX UNITS

OVER red LED: ON 0 dBFs

–6 amber LED: ON –6 dBFs

INPUT 1–8 DIGITAL OUT 1–8

Parameter Conditions MIN TYP MAX UNITS

Frequency Range

Sampling

Frequency

Internal

Clock

Signal Delay

Jitter of PLL

Frequency

Accuracy

Jitter

–12 amber LED: ON –12 dBFs

–18 amber LED: ON –18 dBFs

–30 green LED: ON –30 dBFs

–48 green LED: ON –48 dBFs

Normal Rate 39.69 50.88 kHz

Double Rate 79.38 101.76 kHz

DIGITAL IN fs=44.1kHz 10 ns

DIGITAL IN fs=48 kHz 10 ns

DIGITAL IN fs=39.69–50.88 kHz 20 ns

DIGITAL IN fs=88.2 kHz 10 ns

DIGITAL IN fs=96 kHz 10 ns

DIGITAL IN fs=79.38–101.76 kHz 20 ns

word clock : int 44.1 kHz 44.1 kHz

word clock : int 48 kHz 48 kHz

word clock : int 88.2 kHz 88.2 kHz

word clock : int 96 kHz 96 kHz

word clock : int 44.1 kHz 50 ppm

word clock : int 48 kHz 50 ppm

word clock : int 88.2 kHz 50 ppm

word clock : int 96 kHz 50 ppm

word clock : int 44.1 kHz 5 ns

word clock : int 48 kHz 5 ns

word clock : int 88.2 kHz 5 ns

word clock : int 96 kHz 5 ns

analog input to digital output @fs=48 kHz 0.9 ms

@fs=96 kHz 0.45 ms

AD8HR

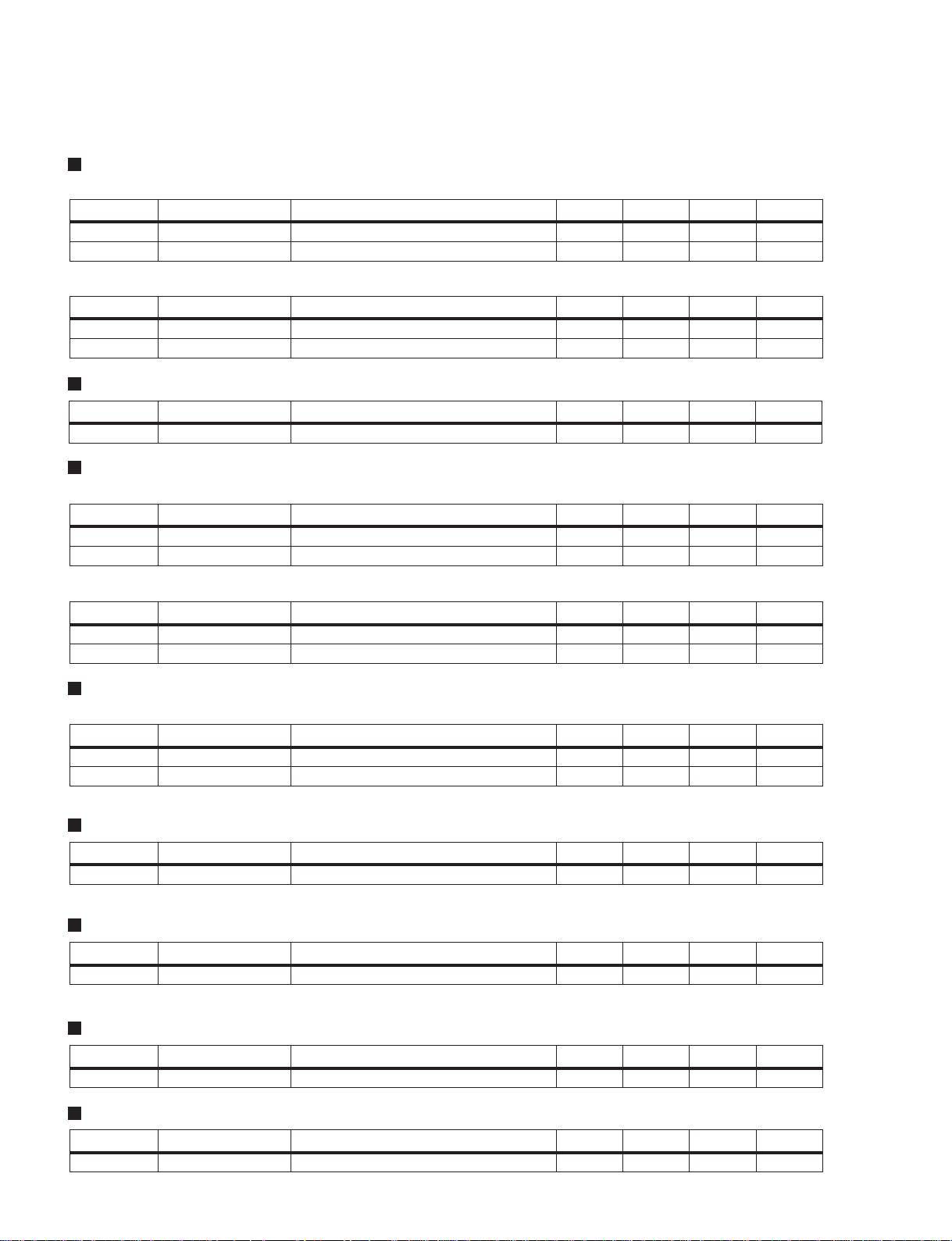

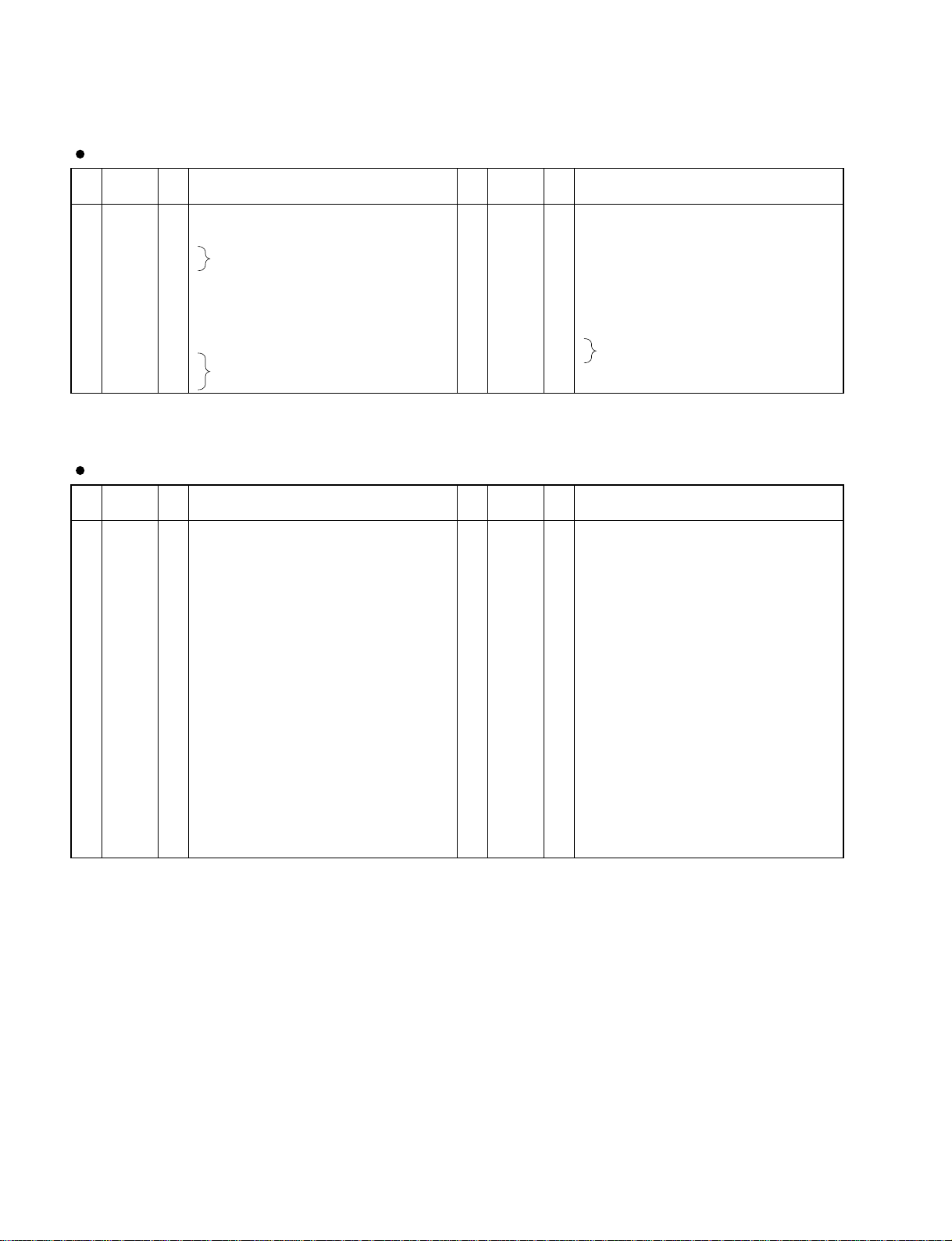

DIGITAL OUT A/B Pin Assignment Table

13

25

D-SUB 25 Pin female(メス)

1

14

Signal

Pin

Cold 14 18 19 20 21

*1. Data In Ch can be received only on DIGITAL OUT A.

Data In Ch

Hot 1 5678

*1

1

-

21

HA REMOTE Pin Assignment Table

Pin Signal Name Pin Signal Name

1 N.C. 6

2

RX-/RXD

3

TX-/TXD

4

TX+/DTR

5 GND

*1. RS422/PC

*1

*1

*1

RX+/DSR

7 RTS

8 CTS

9 N.C.

*1

12345

D-SUB 9 Pin male

Data Out Ch

-

23-45-67-8

6789

(オス)

Open GND

2, 3, 4, 9,11,

15, 16, 17

22, 23, 24, 25

10, 12, 13,

5

AD8HR

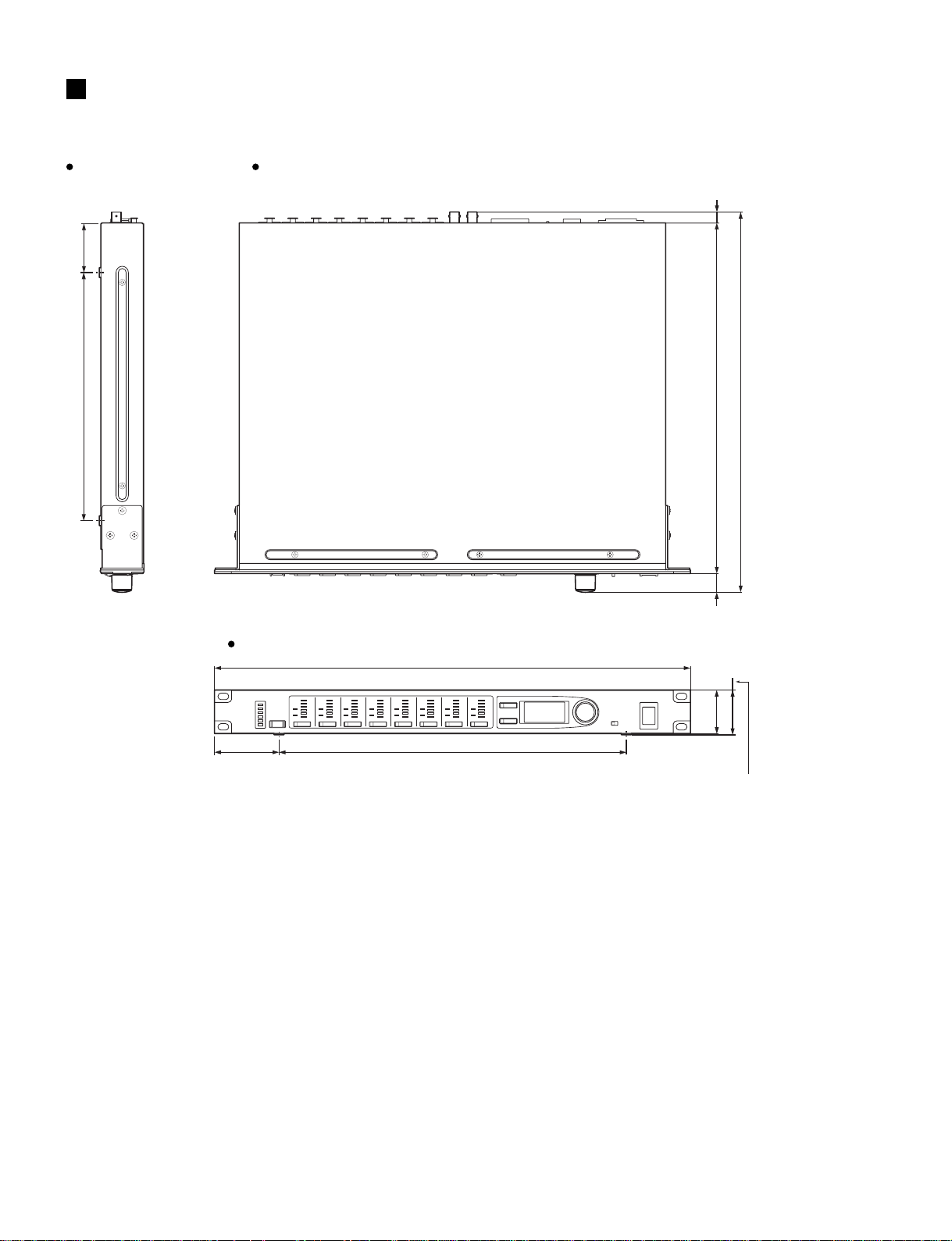

DIMENSIONS

Side view

50

250

(寸法図)

Top View

11

353.5

383.5

Front view

65

19

480

45

44

350

When the included rubber feet are attached.

(付属のゴム脚取り付け時*)

Unit: mm

(単位)

6

AD8HR

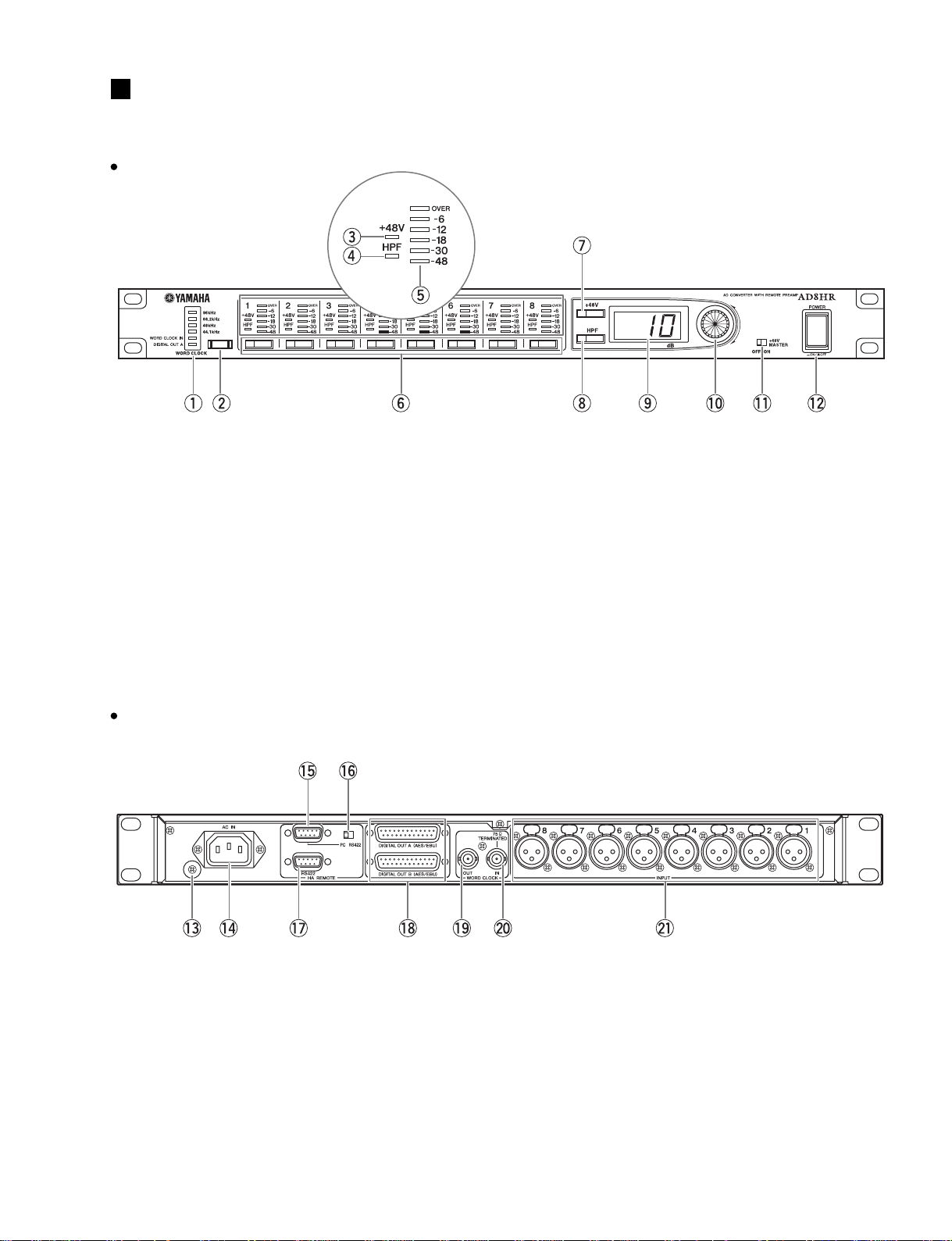

PANEL LAYOUT

Top Panel

(トップパネル)

(パネルレイアウト)

q WORD CLOCK indicators

w [WORD CLOCK] button

e +48V indicators

r HPF indicators

t Level meters

y Channel Select buttons

u [+48V] button

i [HPF] button

o Gain display

!0 Gain control

!1 [+48V MASTER] switch

!2 [POWER] switch

(+48Vインジケーター)

(HPFインジケーター)

(レベルメーター)

([+48V]ボタン)

([HPF]ボタン)

(GAINディスプレイ)

(GAINコントロール)

([POWER]スイッチ)

(WORDCLOCKインジケーター)

([WORDCLOCK]ボタン)

(チャンネル選択ボタン)

([+48VMASTER]スイッチ)

Rear Panel

(リアパネル)

!3 Grounding screwswitch

!4 [AC IN] connector

!5 [HA REMOTE] connector 1

!6 [PC RS422] switch

!7 [HA REMOTE] connector 2

!8 [DIGITAL OUT A/B] connector

!9 [WORD CLOCK OUT] connector

@0 [WORD CLOCK IN] connector

@1 INPUT 1–8 connectors

(アース用ネジ)

([ACIN]端子)

([HAREMOTE]1 端子)

([PCRS422]スイッチ)

([HAREMOTE]2 端子)

([DIGITALOUTA/B]端子)

([WORDCLOCKOUT]端子)

([WORDCLOCKIN]端子)

(INPUT1〜 8端子)

7

AD8HR

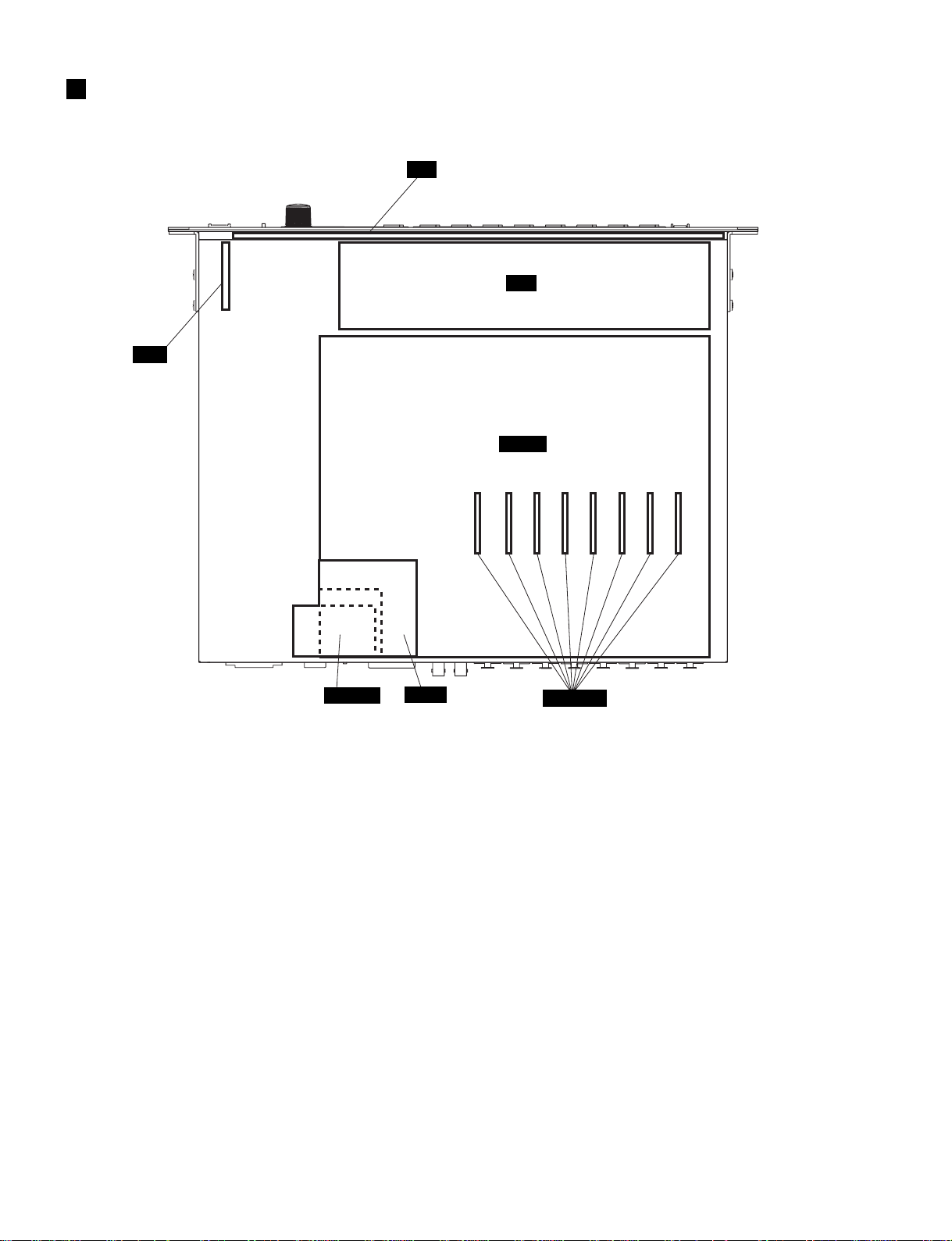

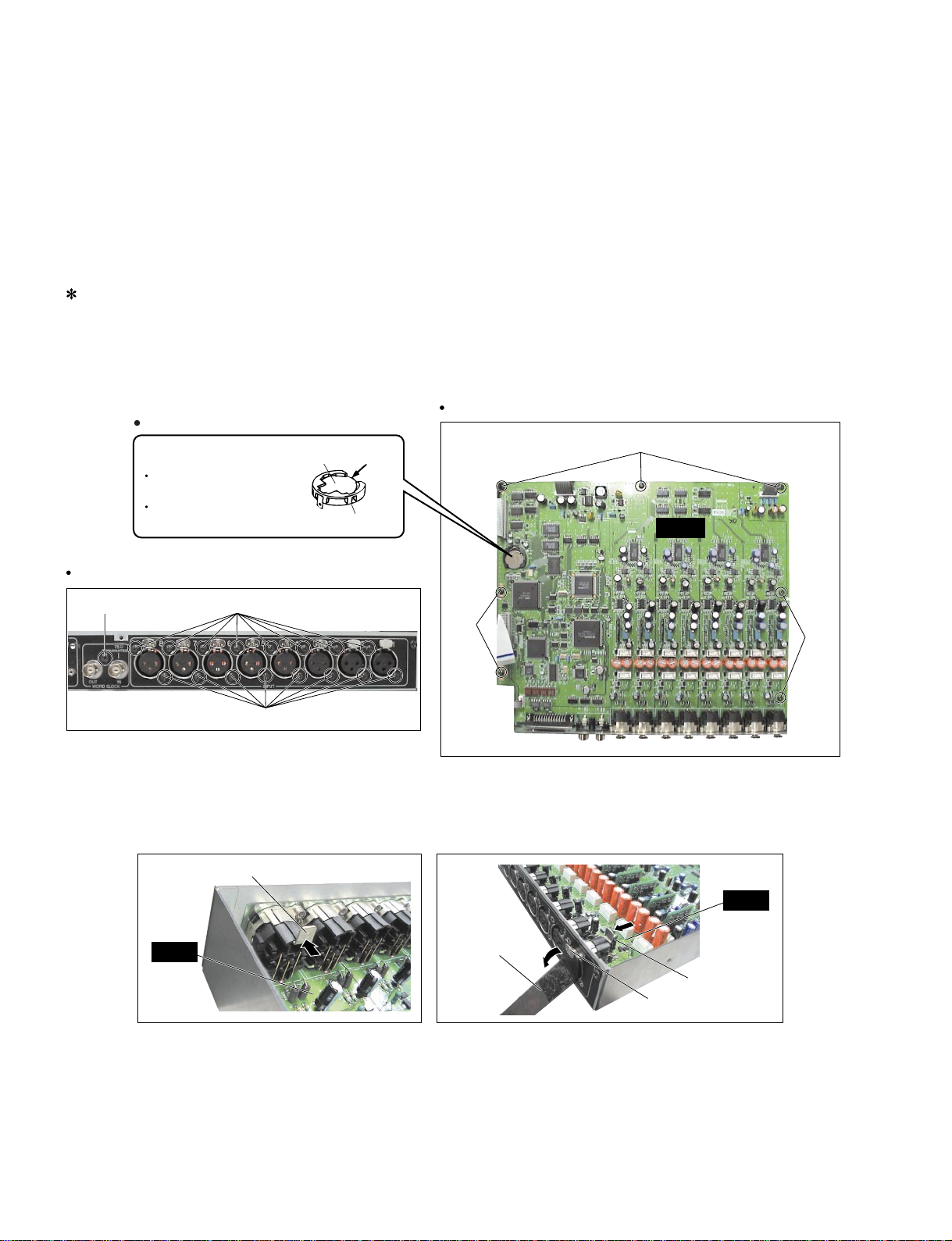

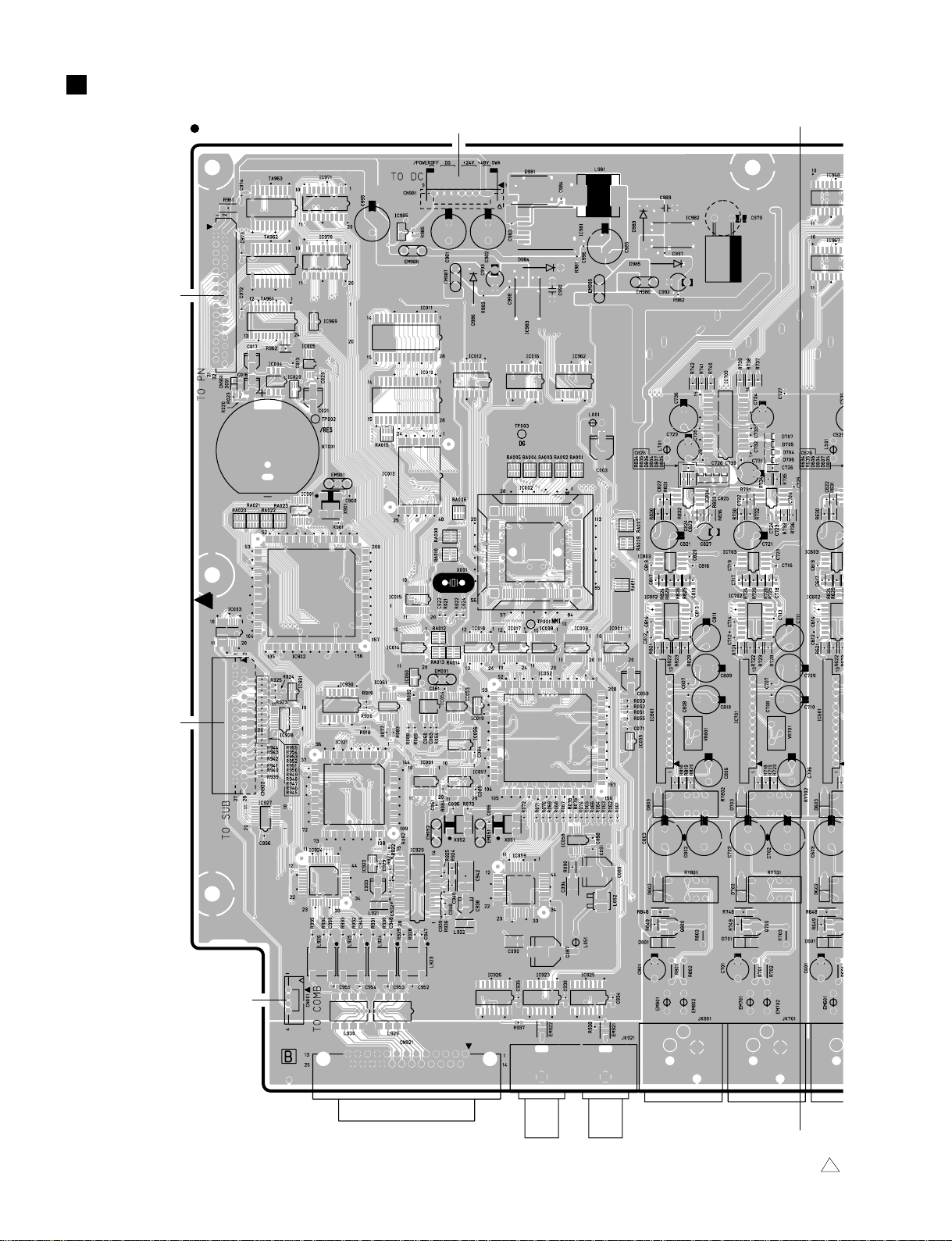

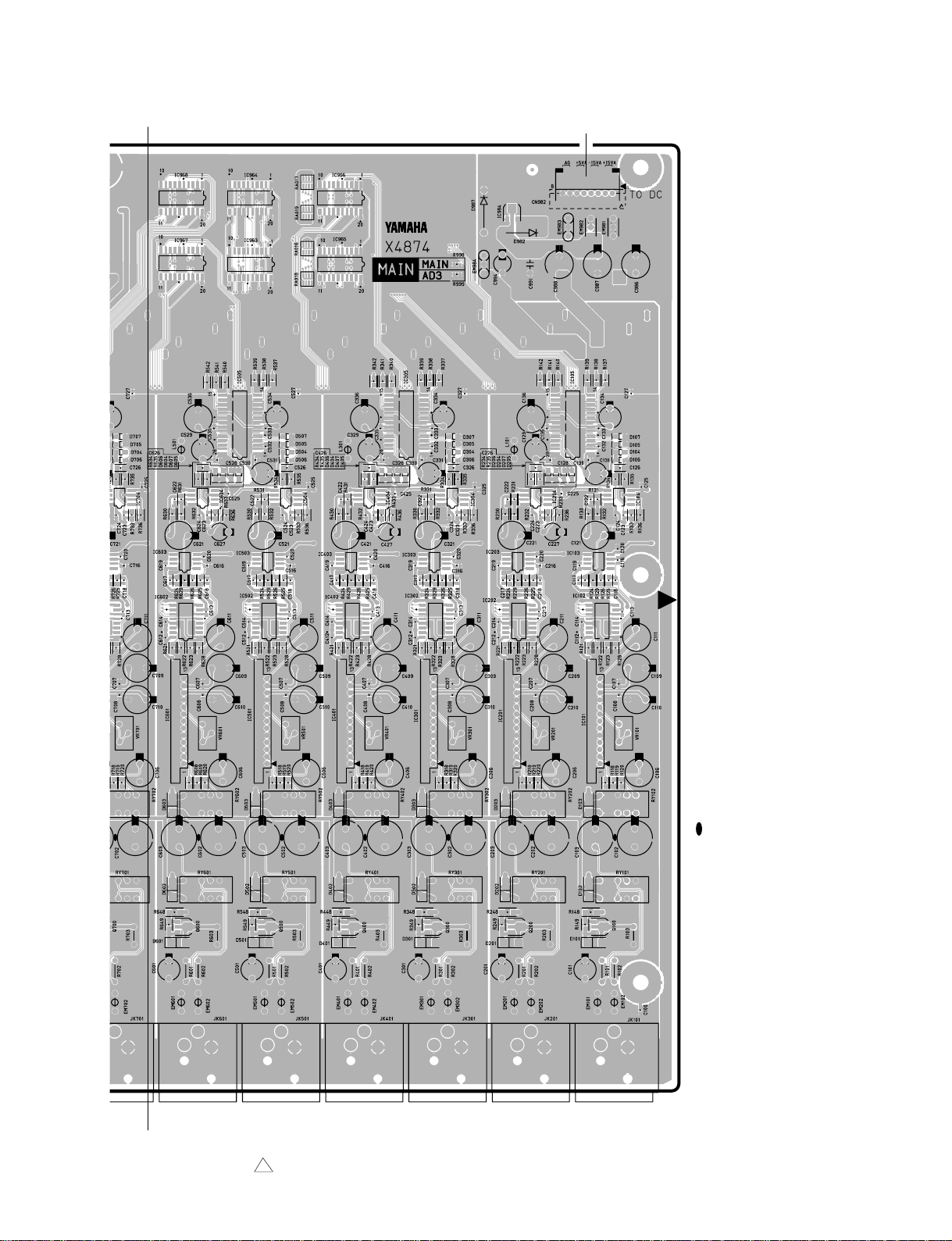

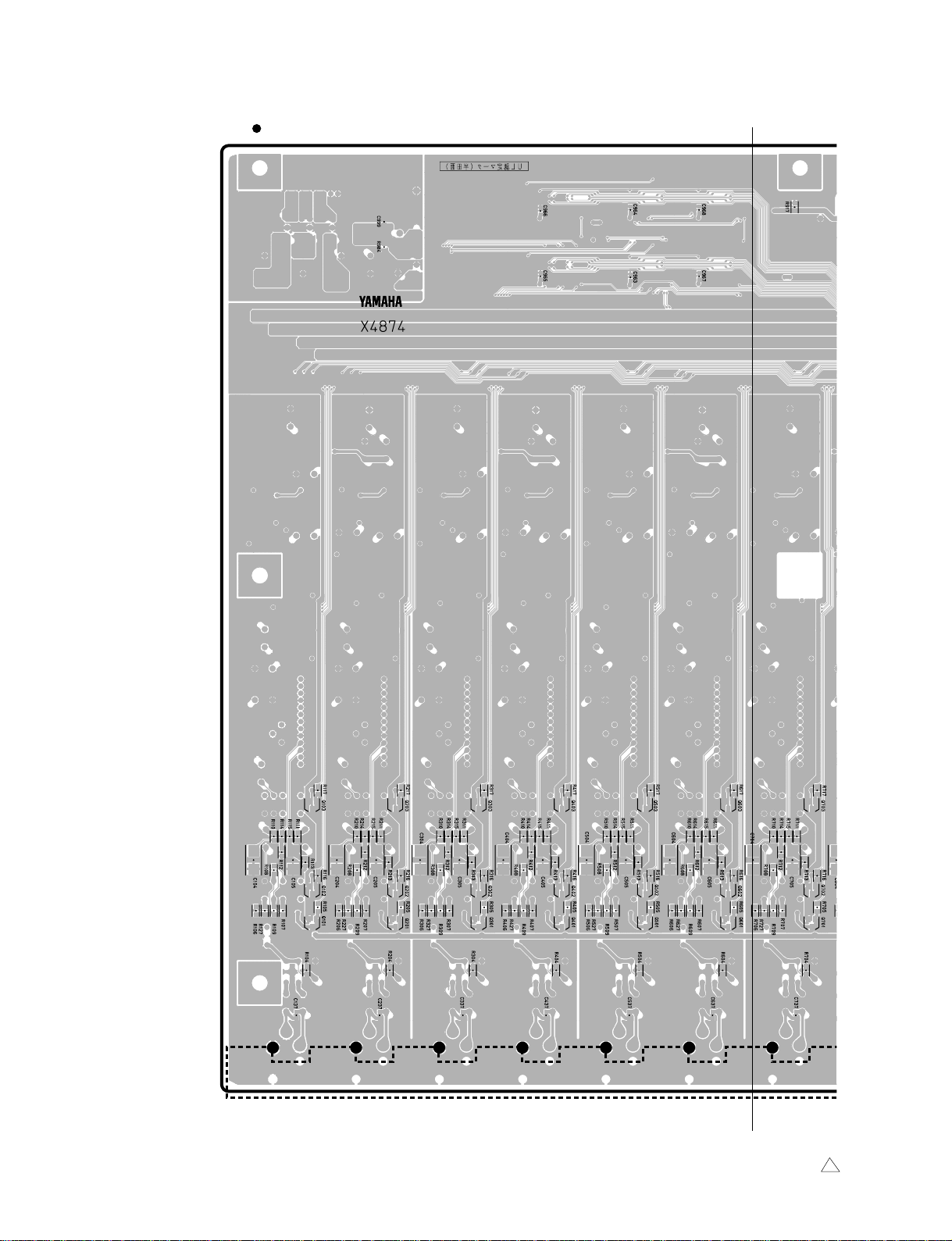

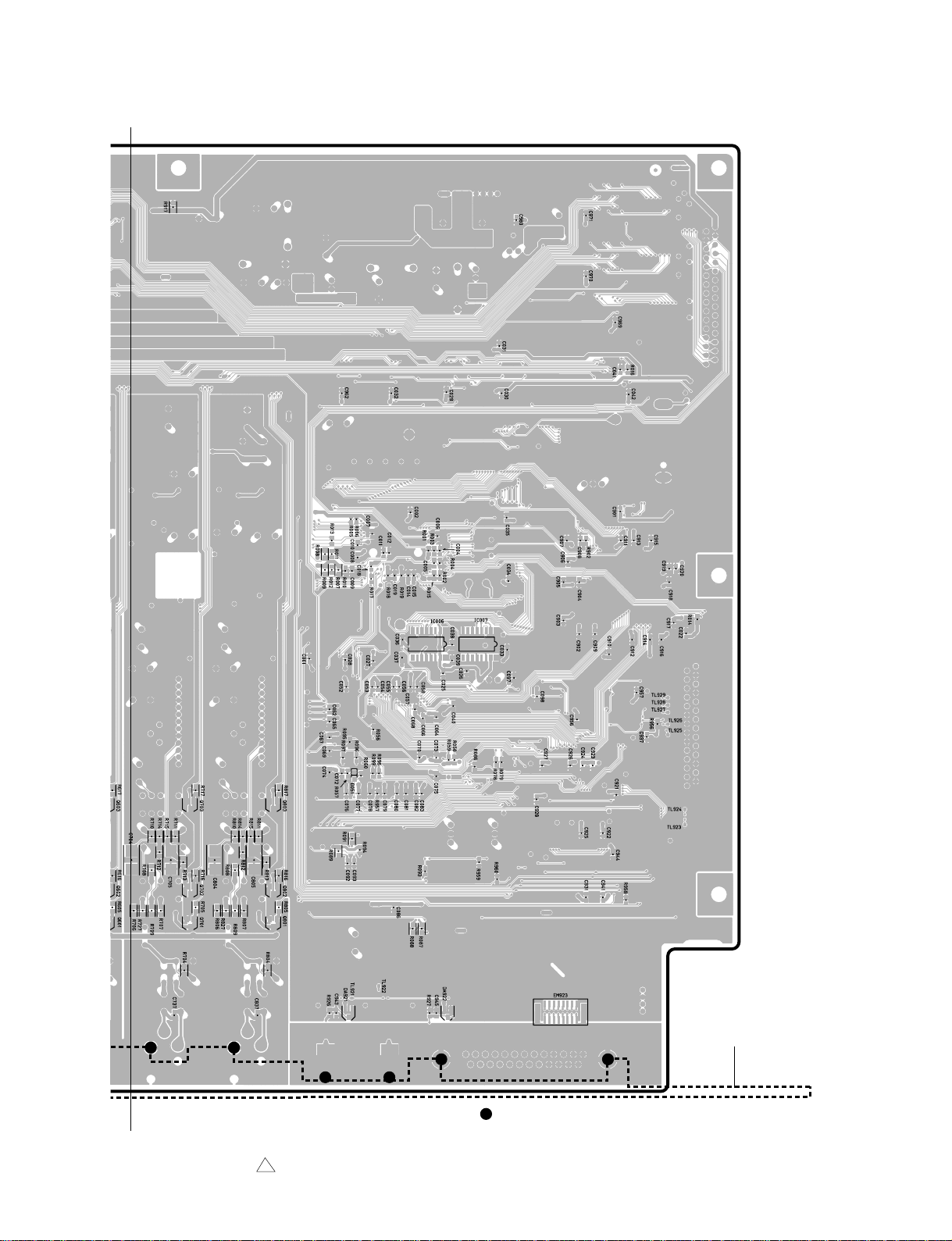

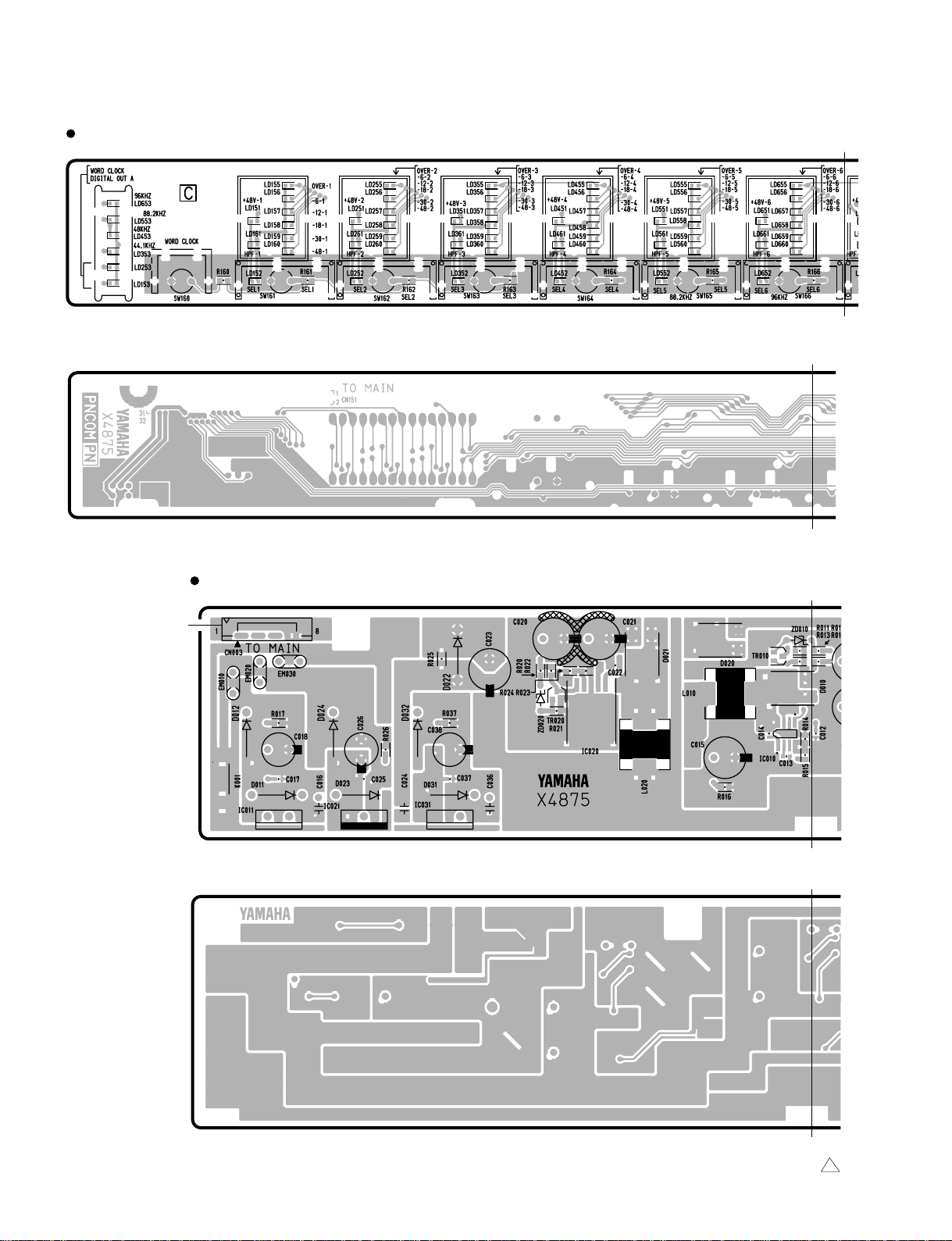

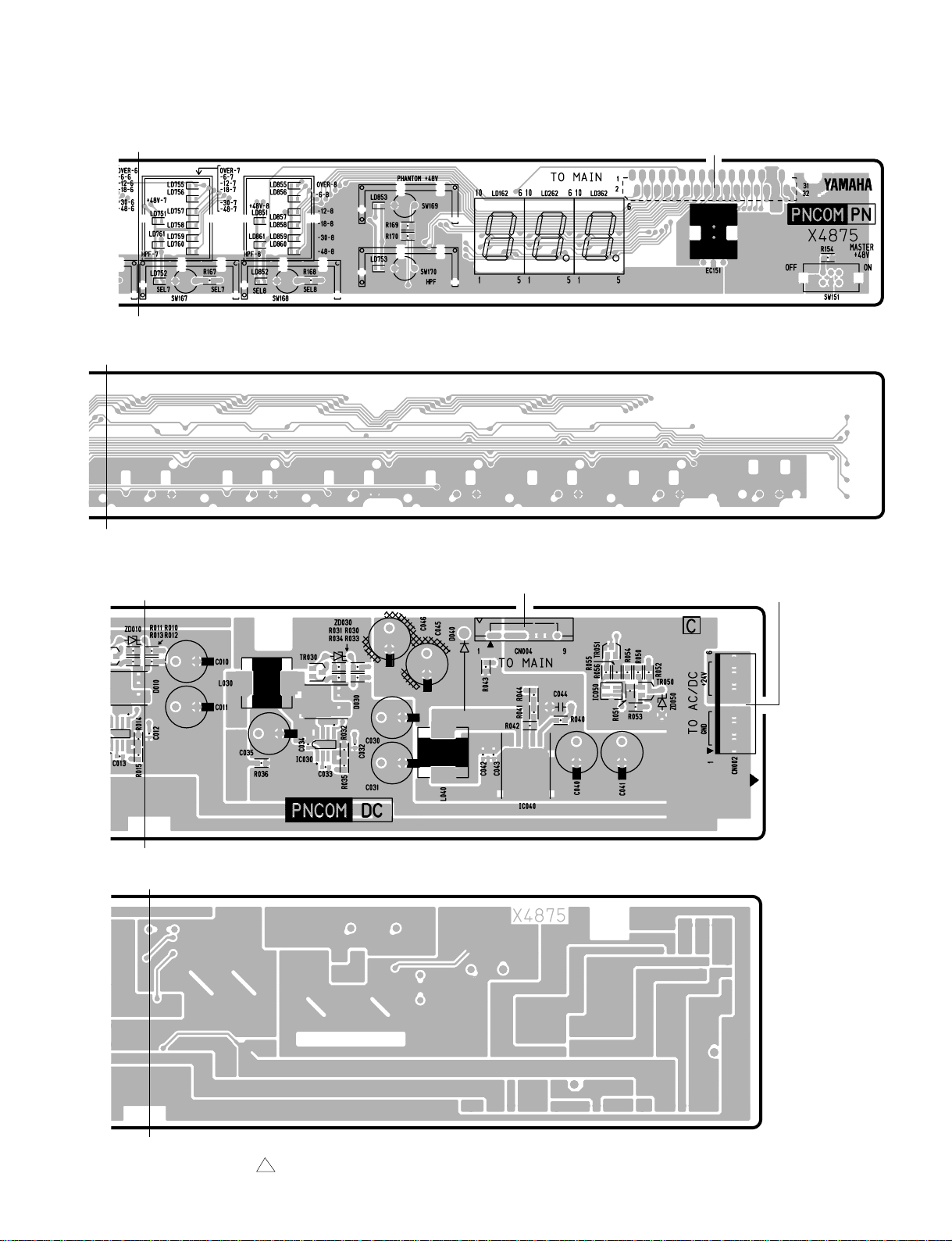

CIRCUIT BOARD LAYOUT

SW

(PNCOM)

(ユニットレイアウト)

PN (PNCOM)

(PNCOM)

DC

MAIN

COMB

(PNCOM) (PNCOM)

SUB

HIC-HA

8

AD8HR

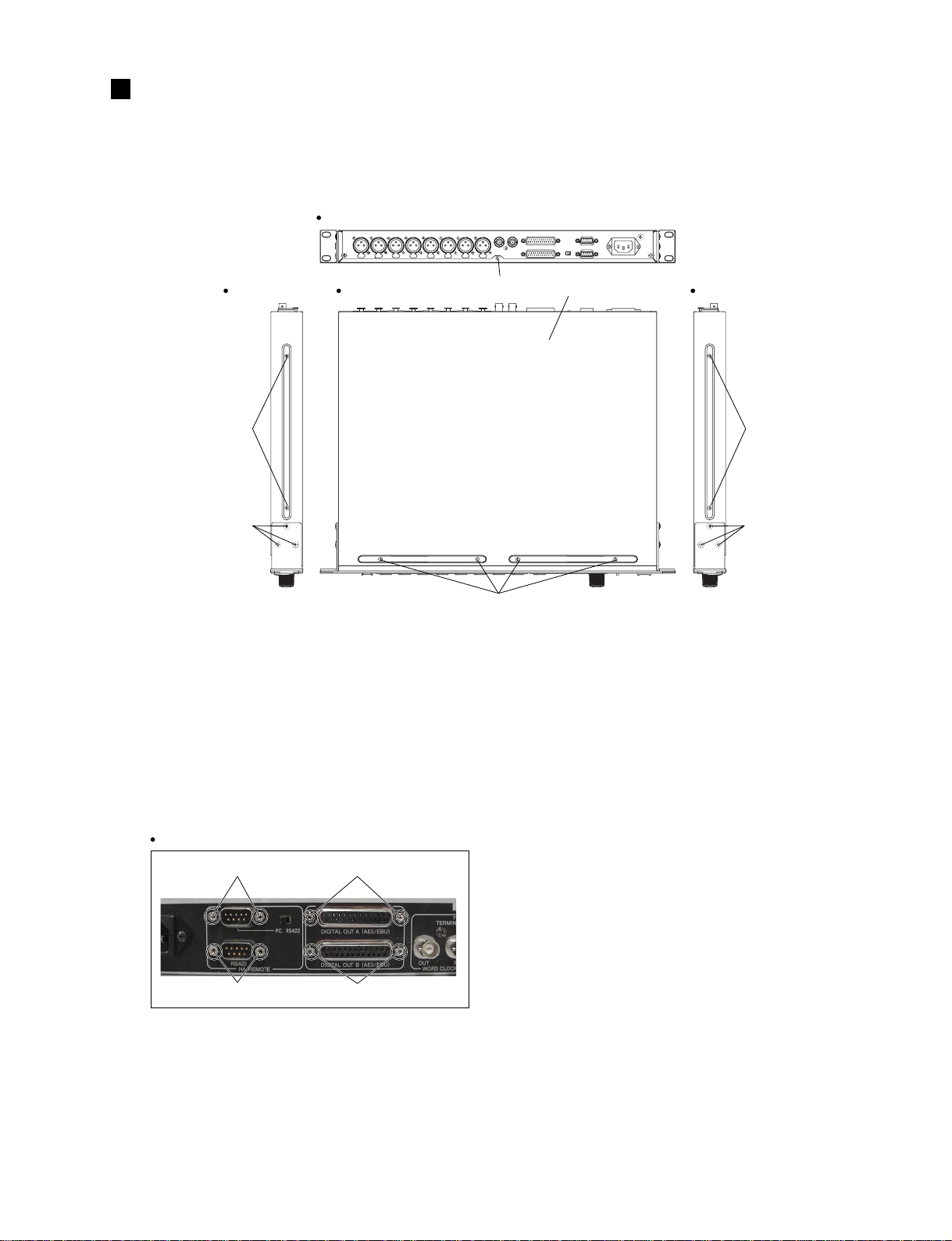

DISASSEMBLY PROCEDURE

(分解手順)

1. Top cover (Time required: About 3 minute)

1-1. Remove the nine (9) screws marked [500] and the

six (6) screws marked [530]. The top cov er can then

be removed. (Fig.1)

Rear view

Side view

[500]

[530] [530]

Top view

1. トップカバー(所要時間:約3 分)

1-1. [500]のネジ 9 本と[530]のネジ 6 本を外し、トップ

カバーを外します。(図1)

[500]

Top cover

(トップカバー)

Side view

[500]

[500]: Bind Head Tapping Screw-S 3.0X6 MFZN2BL (EP630210)

[530]: Bind Head Tapping Screw-S 4.0X8 MFZN2BL (VI693100)

(+バインドSタイト)

(+バインドSタイト)

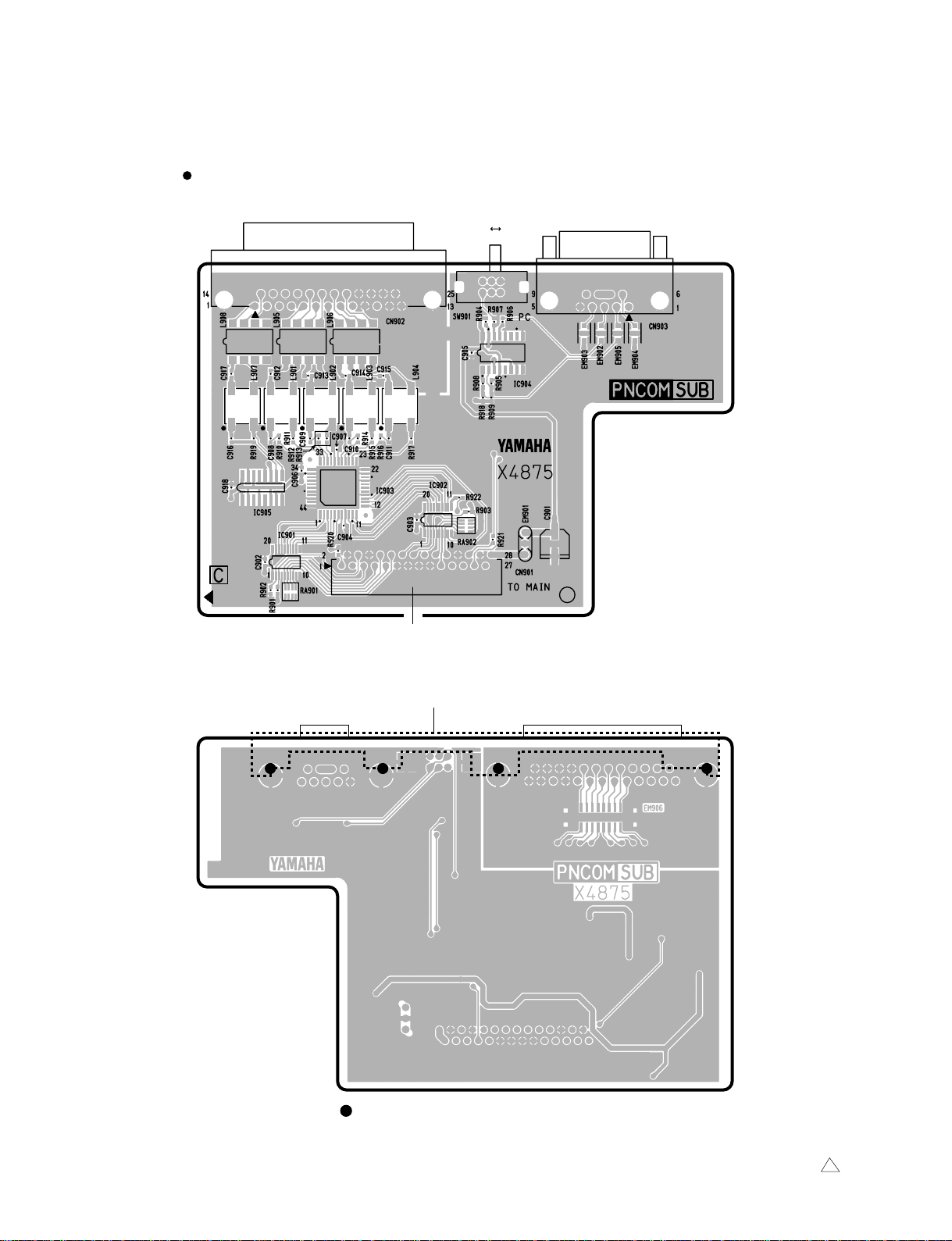

2. SUB Circuit board

(Time required: About 4 minute)

2-1. Remove the top cover. (See Procedure 1.)

2-2. Remov e the tw o (2) screws marked [A] and the two

(2) screws marked [B]. The SUB circuit board can

then be removed. (Photo. 1)

Rear view

[A][B]

[D][C]

(写真1)

Photo. 1

[500]

Fig.1

(図1)

2. SUBシート(所要時間:約4分)

2-1. トップカバーを外します。(1項参照)

2-2. [A]のネジ2本と[B]のネジ2本を外し、SUBシート

を外します。(写真1)

[A], [D]: Hex Locking Screw JFS-2.6S-BIWL (VS604900)

[B], [C]: Hex Locking Screw

(六角ロックネジ)

(六角ロックネジ)

3. COMB Circuit board

(Time required: About 4 minute)

3-1. Remove the top cover. (See Procedure 1.)

3-2. Remove the SUB circuit board. (See Procedure 2.)

3-3. Removr the tw o (2) screws marked [C]. The COMB

circuit board can then be removed. (Photo. 1)

3. COMBシート(所要時間:約4分)

3-1. トップカバーを外します。(1項参照)

3-2. SUB シートを外します。(2項参照)

3-3. [C]のネジ 2 本を外し、COMB シートを外します。

(写真1)

9

AD8HR

4. MAIN Circuit board

(Time required: About 7 minute)

4-1. Remove the top cover. (See Procedure 1.)

4-2. Remove the SUB circuit board. (See Procedure 2.)

4-3. Remove the COMB circuit board. (See Procedure 3.)

4-4. Remove the sixteen (16) screws marked [50], the

screw marked [60], the sev en (7) screws marked [70]

and the two (2) screws marked [D]. The MAIN circuit

board can then be removed. (Photo. 1, 2, 3)

First of all, remove the push lever of the INPUT

terminal for easy removal of the main circuit board.

1. Insert with a latch-removing tool as shown in (A).

(Photo 4)

2. Remove the push lever, using a knob extractor lever

as shown in (B). (Photo 4)

Lithium Battery(リチウム電池)

Battery VN103500

Rear view

VN103600(Battery holder for VN103500)

Notice for back-up battery removal

Push the battery as shown in figure,

then the battery will pop up.

Druk de batterij naar beneden zoals

aangeven in de tekening de batterij

springt dan naar voren.

Battery

Battery holder

4. MAINシート(所要時間:約7分)

4-1. トップカバーを外します。(1項参照)

4-2. SUB シートを外します。(2項参照)

4-3. COMB シートを外します。(3項参照)

4-4. [50]のネジ 16 本、[60]のネジ1本、[70]のネジ7本、

[D]のネジ2 本を外し、MAINシートを外します。

(写真1,2,3)

※ MAINシートを外す時は、INPUT端子のプッシュレ

バーを先に外すと、外しやすくなります。

1. ラッチ外し工具で A のように差し込みます。

(写真 4)

2. プッシュレバーを B のようにツマミ抜き取りレ

バーで外します。(写真 4)

Top view

[70]

MAIN

[50][60]

[50]: Bind Head Tapping Screw-B

2.6X8 MFZN2BL (VB096700)

[60]: Bind Head Tapping Screw-B

3.0X8 MFZN2BL (EP600190)

Photo. 2

AB

Tool (AAX52710)

MAIN

[50]

(+バインドBタイト)

(+バインドBタイト)

(写真2)

[70]

[70]: Bind Head Tapping Screw-S

3.0X6 MFZN2BL (EP630210)

Tool (AAX000021)

Photo. 4

(写真4)

(+バインドSタイト)

(写真3)

Photo. 3

Push lever

[70]

MAIN

Tool (AAX52710)

(プ ッシュ レバー)

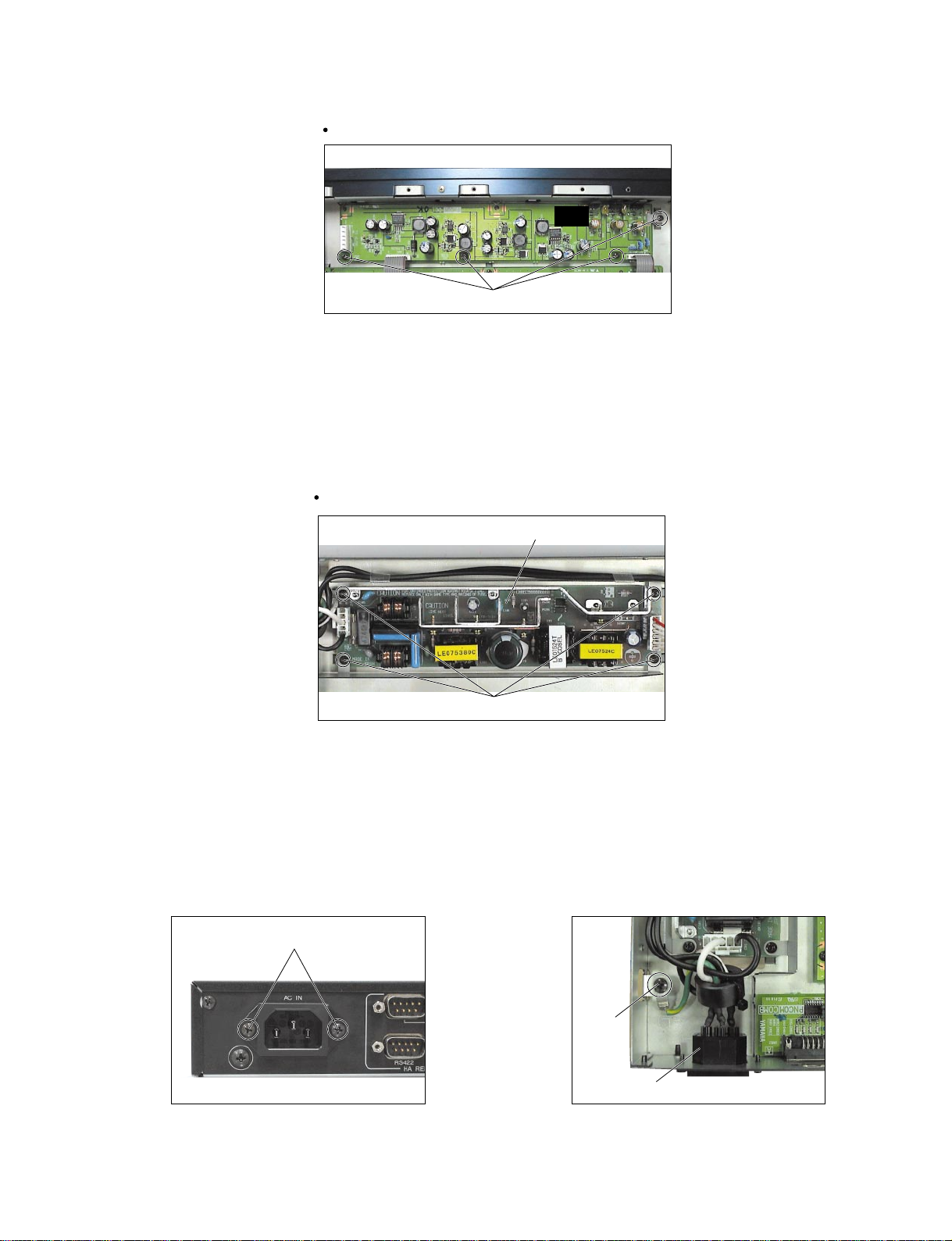

5. DC Circuit board

(Time required: About 3 minute)

5-1. Remove the top cover. (See Procedure 1.)

5-2. Remove the four (4) screws marked [230]. The DC

circuit board can then be removed. (Photo. 5)

10

5. DCシート(所要時間:約3 分)

5-1. トップカバーを外します。(1 項参照)

5-2. [230]のネジ 4 本を外し、DC シートを外します。

(写真 5)

Top view

AD8HR

DC

[230]

[230]: Bind Head Tapping Screw-S 3.0X6 MFZN2BL (EP630210)

(+バインドSタイト)

Photo. 5

6. Power supply unit

(Time required: About 4 minute)

6-1. Remove the top cover. (See Procedure 1.)

6-2. Remov e the four (4) scre ws marked [130]. The power

supply unit can then be removed. (Photo. 6)

Top view

[130]: Bind Head Tapping Screw-S 3.0X6 MFZN2BL (EP630210)

(+バインドSタイト)

Photo. 6

(写真5)

6. 電源ユニット(所要時間:約4 分)

6-1. トップカバーを外します。(1 項参照)

6-2. [130]のネジ4本を外し、電源ユニットを外します。

(写真6)

Power supply unit(電源ユニット)

[130]

(写真6)

7. AC inlet assembly

(Time required: About 3 minute)

7-1. Remove the top cover. (See Procedure 1.)

7-2. Remove the two (2) screws marked [210] and the

screw marked [220]. The AC inlet assemb ly can then

be removed. (Photo. 7, 8)

[210]

[210]: Bind Head Tapping Screw-B

3.0X8 MFZN2BL (EP600190)

Photo. 7

(+バインドBタイト)

(写真7)

7. インレットAss'y(所要時間:約3分)

7-1. トップカバーを外します。(1 項参照)

7-2. [210]のネジ2本、[220]のネジ1本を外し、インレッ

ト Ass'y を外します。

(写真 7,8)

[220]

AC inlet assembly(インレットAss'y)

[220]: Bind Head Screw

4.0X8 MFZN2BL (EG340360)

Photo. 8

(+バインド小ネジ)

(写真8)

11

AD8HR

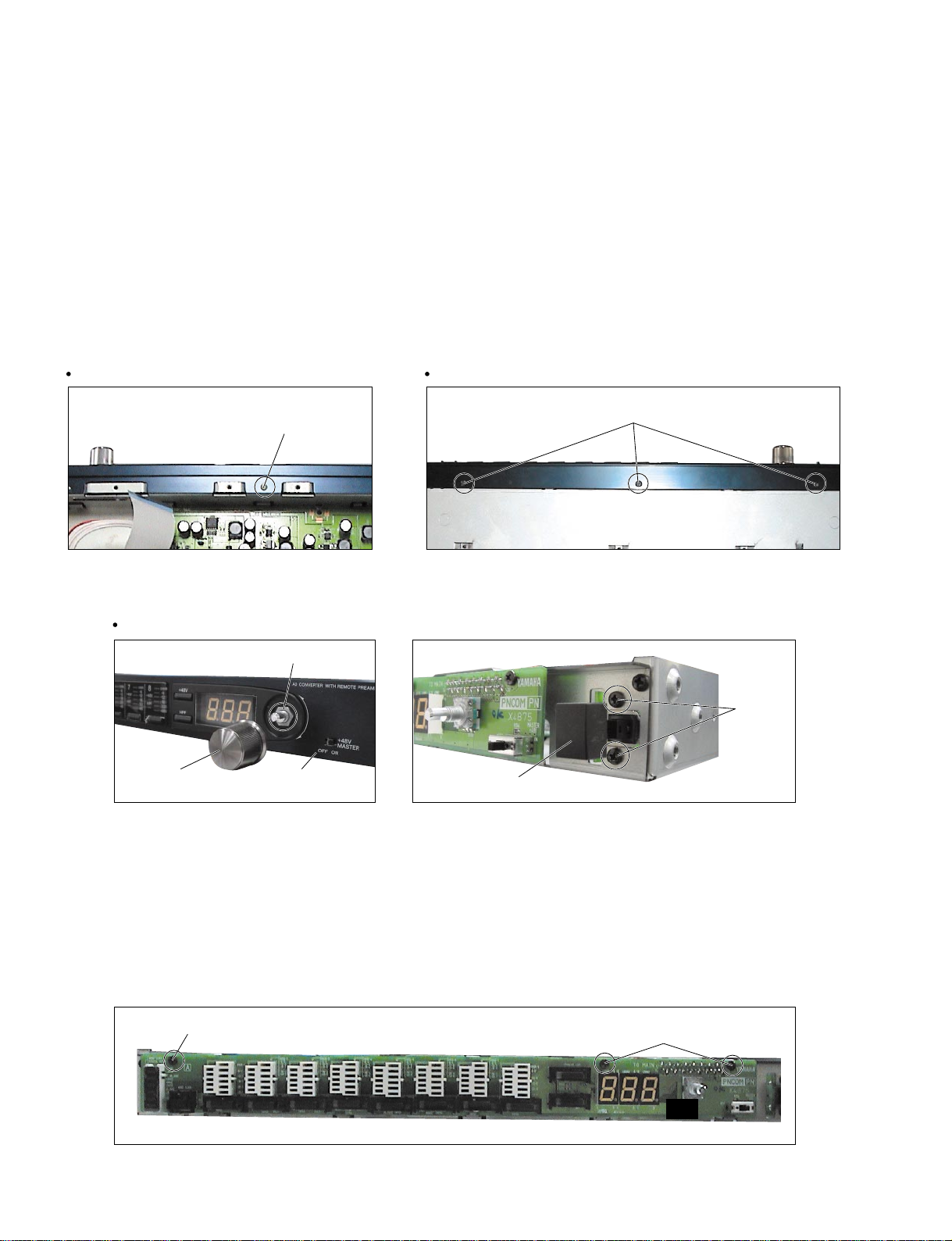

8. Front panel (Time required: About 4 minute)

8-1. Remove the top cover. (See Procedure 1.)

8-2. Remove the screw marked [460], the three (3)

screws marked [470], the knob (GAIN control) and

the hexagonal nut of a front panel side. The front

panel can then be removed. (Photo. 9, 10, 11)

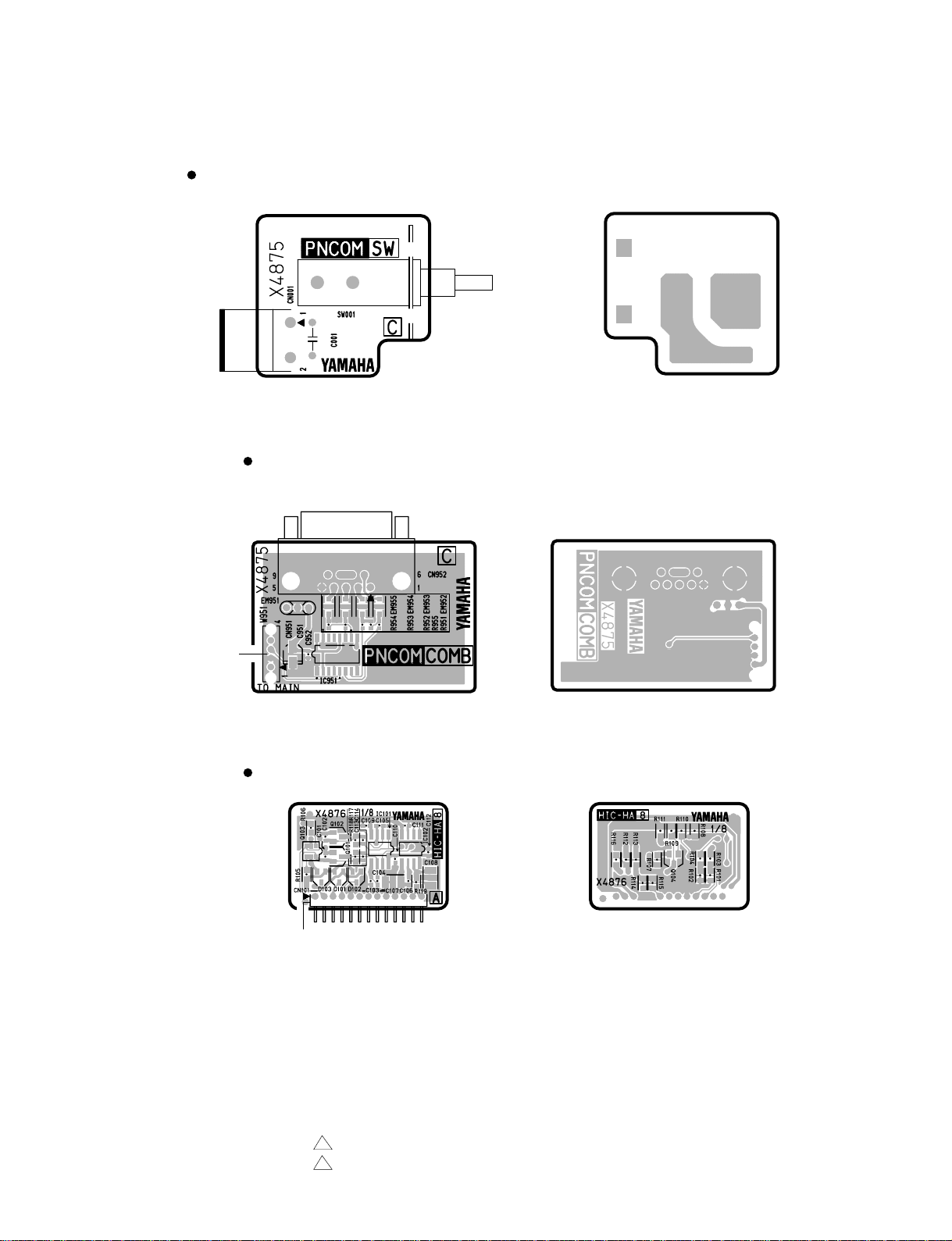

9. SW Circuit board

(Time required: About 4 minute)

9-1. Remove the top cover. (See Procedure 1.)

9-2. Remove the front panel. (See Procedure 8.)

9-3. Remove the button PSW. (Photo. 12)

9-4. Remove the two (2) screws marked [280]. The SW

circuit board can then be removed. (Photo. 12)

Top view

[460]

8. フロントパネル(所要時間:約4 分)

8-1. トップカバーを外します。(1 項参照)

8-2. [460]のネジ1本、[470]のネジ3本を外し、フロント

9. SWシート(所要時間:約4分)

9-1. トップカバーを外します。(1 項参照)

9-2. フロントパネルを外します。(8 項参照)

9-3. ボタン PSW を外します。(写真 12)

9-4. [280]のネジ 2 本を外し、SW シートを外します。

Bottom view

パネル面のツマミ(GAINコントロール)と特殊六角

ナット 1個を外し、フロントパネルを外します。

(写真9,10,11)

(写真12)

[470]

[460]: Flat Head Screw-S

3.0X6 MFAN2Y (WB451000)

Front view

Knob assembly

(ノブAss'y)

(Sタイト平頭)

Photo. 9

(写真9)

Hexagonal nut

Photo. 11

(写真11)

(特殊六角ナット)

Front panel

(フロントパネル)

[280]: Bind Head Tapping Screw-S

10. PN Circuit board

(Time required: About 4 minute)

10-1. Remove the top cover. (See Procedure 1.)

10-2. Remove the front panel. (See Procedure 8.)

10-3. Remove the three (3) screws marked [300]. The PN

circuit board can then be removed. (Photo. 13)

[470]: Bind Head Tapping Screw-S

3.0X6 MFZN2BL (EP630210)

Photo. 10

Button PSW

(ボタンPSW)

(+バインドSタイト)

3.0X6 MFZN2BL (EP630210)

Photo. 12

10. PNシート(所要時間:約 4 分)

10-1. トップカバーを外します。(1項参照)

10-2. フロントパネルを外します。(8 項参照)

10-3. [300]のネジ3本を外し、PN シートを外します。

(写真13)

(+バインドSタイト)

(写真10)

[280]

(写真12)

12

[300] [300]

[300]: Bind Head Tapping Screw-S 3.0X6 MFZN2BL (EP630210)

(+バインドSタイト)

Photo. 13

(写真13)

PN

AD8HR

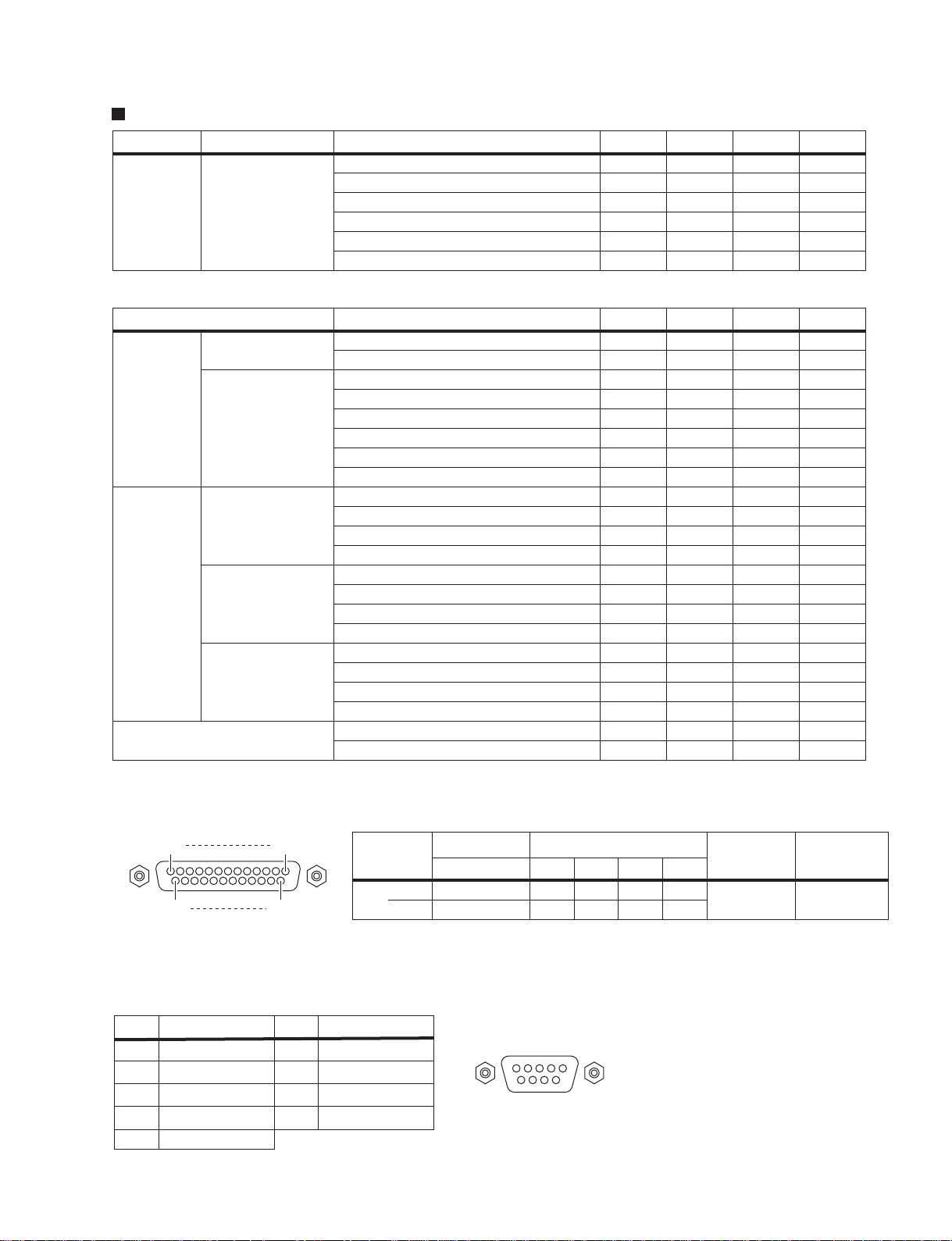

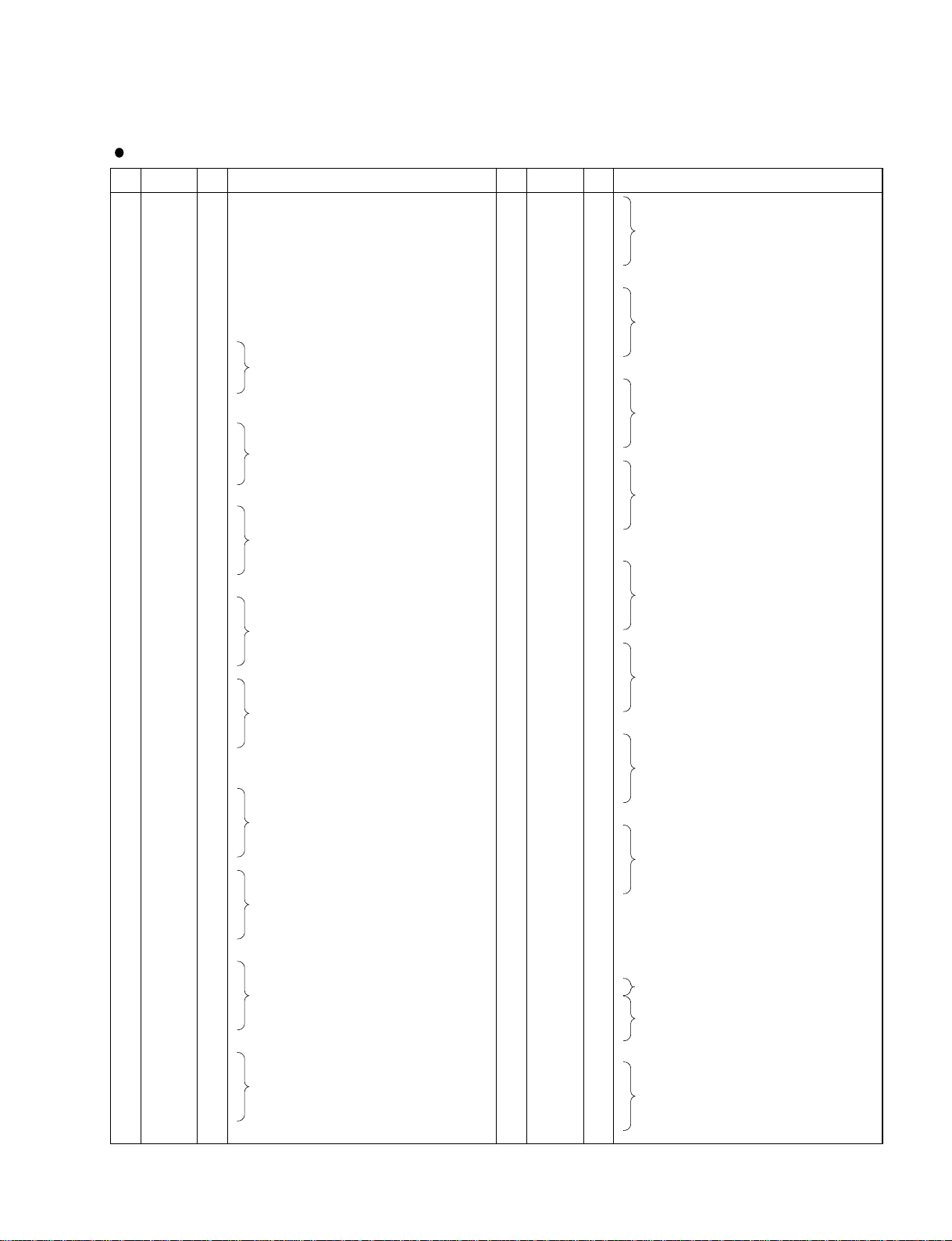

LSI PIN DESCRIPTION

(LSI端子機能表)

HD6437042AF53 (XY721A00) CPU

PIN

NO.

1

TIOC4/DACK0/PE14

2

PE15

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

/RAS/PB2

25

/CASL/PB3

26

/CASH/PB4

27

28

/RDWR / PB5

29

A18//BACK/PB6

30

A19//BREQ/PB7

31

A20/PB8

32

A21/PB9

33

34

35

/WDTOVF

36

/WRH

37

38

/WRL

39

40

/CS1

41

/CS0

42

/IRQ3/TCLKD/PA9

43

TCLKC//IRQ2 /PA8

44

/CS3

45

/CS2

46

/IRQ1/PA5

47

TXD1

48

RXD1

49

/IRQ0/PA2

50

TXD0

51

RXD0

52

53

54

55

56

VSS

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

VCC

A17

VSS

VSS

VSS

/RD

VCC

VSS

D15

D14

D13

VSS

D12

I/O FUNCTIONNAME

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

MTU I/O / DMA acknowledge / Port E

Port E

I

Ground

Address bus

I

Power supply

Address bus

I

Ground

Row address strobe / Port B

Column address strobe (low) / Port B

Column address strobe (high) / Port B

I

Ground

DRAM read / write / Port B

Address bus / Bus acknowledge / Port B

Address bus / Bus request / Port B

Address bus/ Port B

I

Ground

Read

Watch dog timer overflow

High write

I

Power supply

Low write

I

Ground

Chip select

Chip select

Interrupt request / Timer clock/ Port A

Timer clock / Interrupt request / Port A

Chip select

Chip select

Interrupt request / Port A

Data transmission

I

Data reception

Interrupt request / Port A

Data transmission

I

Data reception

Data bus

I

Ground

Data bus

PIN

NO.

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

PLLVCC

81

PLLCAP

82

PLLVSS

83

PA15 / CK

84

85

PE0/DREQ0

86

PE1/DRAK0

87

88

89

90

91

PF0 / AN0

92

PF1 / AN1

93

PF2 / AN2

94

PF3 / AN3

95

PF4 / AN4

96

PF5 / AN5

97

98

PF6 / AN6

99

PF7 / AN7

100

101

102

103

104

105

106

107

108

109

110

111

112

D11

D10

D9

D8

VSS

D7

D6

D5

VCC

D4

D3

D2

D1

D0

VSS

XTAL

MD3

EXTAL

MD2

NMI

VCC

MD1

MD0

/RES

PE2

PE3

PE4

VSS

AVSS

AVCC

VSS

PE5

VCC

PE6

PE7

PE8

PE9

PE10

VSS

PE11

PE12

/MRES

I/O FUNCTIONNAME

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

O

I/O

O

O

O

O

O

I/O

I/O

I/O

O

O

O

O

MAIN: IC2

Data bus

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

Ground

Data bus

Power supply

Data bus

Ground

Crystal oscillator

Mode control

Crystal oscillator

Mode control

Non-maskable interrupt request

Power supply

Mode control

Mode control

PLL Power supply

PLL capacitor

PLL Ground

Port A / Clock

Power on reset

Port E / DMA request

Port E / DMA acknowledge

Port E

Ground

Port F / Analog input

Analog ground

Port F / Analog input

Power supply

Ground

Port E

Power supply

Port E

Ground

Port E

Manual reset

13

AD8HR

S1L51252F32S000 (X3775A00) PLLP2 (Gate Array)

PIN

NO.

100

101

102

103

104

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

(NC)

(NC)

PB8

PB9

VDD

VSS

PA0

NCSIN6

NCSIN5

NRD

NWRH

NWRL

PA1

ADH1

ADH2

ADH3

ADH4

ADH5

PA2

VSS

VDD

VDD

VSS

ADL1

ADL2

ADL3

ADL4

ADL5

ADL6

ADL7

ADL8

VSS

VDD

VDD

VSS

DT0

DT1

DT2

DT3

DT4

DT5

VDD

VSS

DT6

DT7

DT8

DT9

VDD

VSS

(NC)

(NC)

(NC)

DT10

DT11

DT12

DT13

DT14

DT15

VSS

PA3

NTCWAIT

NCSIO3V

NCSIO5V

NCSJK1

NCSCONT

VDD

NCSSLOT1

NCSSLOT2

NCSSIO4

NCSREC2

NCSMTLED

VDD

NCSUSB

NCSSMPTE

NCSUART

VSS

VDD

NRES

CPUCLK

(NC)

VSS

VSS

NCSATSC1

VDD

NCSATSC2

PA4

PA5

PA6

NCTSYNCO

NCTSYNCI

VDD

NCSDSP71

NCSDSP72

NCSDSP73

NCSDSP74

NCSDSP75

NCSDSP76

VDD

PA7

PA8

NCSDSP61

NCSDSP62

NCSDSP63

NCSDSP64

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

FUNCTIONNAME

-

O

O

-

O

I

I

I

I

I

O

I

I

I

I

I

O

-

-

-

-

I

I

I

I

I

I

I

I

-

-

-

-

-

-

-

-

-

-

-

O

O

O

O

O

O

O

O

O

O

O

O

O

O

-

-

I

I

-

-

O

O

O

O

O

O

I

O

O

O

O

O

O

O

O

O

O

O

O

(Connected to VSS on P.C.B.)

(Pulled up on P.C.B.)

Output port B8

Output port B9

IO power supply (3.3V)

Ground

Output port A0

CPU chip select 6

CPU chip select 5

CPU read enable

CPU write enable H

CPU write enable L

Output port A1

CPU address bus 11

CPU address bus 12

CPU address bus 13

CPU address bus 14

CPU address bus 15

Output port A2

Ground

Internal power supply (2.5V)

IO power supply (3.3V)

Ground

CPU address bus 1

CPU address bus 2

CPU address bus 3

CPU address bus 4

CPU address bus 5

CPU address bus 6

CPU address bus 7

CPU address bus 8

Ground

Internal power supply (2.5V)

IO power supply (3.3V)

Ground

CPU data bus 0

CPU data bus 1

CPU data bus 2

CPU data bus 3

CPU data bus 4

CPU data bus 5

IO power supply (3.3V)

Ground

CPU data bus 6

CPU data bus 7

CPU data bus 8

CPU data bus 9

Internal power supply (2.5V)

Ground

(Connected to VDD on P.C.B.)

(Connected to VDD on P.C.B.)

(Pulled up on P.C.B.)

CPU data bus 10

CPU data bus 11

CPU data bus 12

CPU data bus 13

CPU data bus 14

CPU data bus 15

Ground

Output port A3

CPU wait signal

Chip select (103V)

Chip select (105V)

Chip select (JK1)

Chip select (CONT)

Power supply

Chip select (SLOT1)

Chip select (SLOT2)

Chip select (S104)

Chip select (REC2)

Chip select (MTLED)

Power supply

Chip select (USB)

Chip select (SMPTE)

Chip select (UART)

Ground

Power supply

System reset

CPU clock

(Connected to VSS on P.C.B.)

Ground

Ground

Chip select (ATSC1)

Power supply

Chip select (ATSC2)

Output port A4

Output port A5

Output port A6

Internal counter synchronous signal output

Internal counter synchronous signal input

Power supply

Chip select (DSP7_1)

Chip select (DSP7_2)

Chip select (DSP7_3)

Chip select (DSP7_4)

Chip select (DSP7_5)

Chip select (DSP7_6)

Power supply

Output port A7

Output port A8

Chip select (DSP6_1)

Chip select (DSP6_2)

Chip select (DSP6_3)

Chip select (DSP6_4)

PIN

NO.

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173

174

175

176

177

178

179

180

181

182

183

184

185

186

187

188

189

190

191

192

193

194

195

196

197

198

199

200

201

202

203

204

205

206

207

208

EXTWC2561

EXTWC2562

FS256_SLOT1

FS256_SLOT2

(NC)

VDD

(NC)

(NC)

VSS

VDD

NCSDSP7

NCSDSP6

PA9

MCK256O

MCK256MI

MCK256SI

VSS

VDD

ICK45

ICK49

DIR2XI

PA10

VSS

VDD

EXTWC1

EXTWC2

EXTWC3

EXTWC4

VSS

VDD

PA11

DIRMCA

DIRMCB

DIRWC

VSS

VDD

DIRMCC

DIRSYNC

EXTWCSEL

DIRWCSEL

PA12

PLLOUT

VSS

VDD

PCPOUT

PA13

M256FS

M128FS

VSS

VDD

(NC)

(NC)

(NC)

(NC)

M64FS

MWC

MSYNC

PA14

WCO_BNC

PA15

VDD

SYNC_SLOT1

SYNC_SLOT2

PB0

SLOT_12M

SLOT_6M

VSS

SLOT_3M

PB1

SLOT_48K

SLOT_48S

PB2

ANA256FS

VDD

NLOCK

NDIRLOCK

VSS

SCANEN

ATPGEN

TSTEN

VDD

TRRERR1

TRRERR2

VSS

PB3

NMLOCKSEL

NLOCKRTN

PB4

MUTEIN

VDD

MUTEOUT1

MUTEOUT2

MUTEOUT3

MUTEOUT4

MUTEOUT5

NMUTEOUT6

VDD

PB5

DOUBLE

K48K96

PB6

SLOT1_16CH

SLOT2_16CH

PB7

MAIN: IC52

I/O

-

-

-

-

-

O

O

O

O

-

-

O

O

-

-

-

-

O

-

-

O

O

O

-

O

O

O

O

-

-

-

-

-

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

-

-

-

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

(Pulled up on P.C.B.)

Power supply

(Connected to VSS on P.C.B.)

(Connected to VSS on P.C.B.)

Ground

Power supply

Chip select (DSP7_ALL)

Chip select (DSP6_ALL)

Output port A9

256FS synchronous clock output

I

256FS synchronous clock input (Master)

I

256FS synchronous clock input (Slave)

Ground

Power supply

I

For internal clock 88.2k, 44.1k

I

For internal clock 96k, 48k

Clock for X1 of DIR2

Output port A10

Ground

Power supply

I

External word clock input 1

I

External word clock input 2

I

External word clock input 3

I

External word clock input 4

Ground

Power supply

I

External WC (256FS) input 1

I

External WC (256FS) input 2

Output port A11

I

MCA input of DIR2

I

MCB input of DIR2

I

WC input of DIR2

Ground

Power supply

I

MCC input of DIR2

I

SYNC input of DIR2

EXTWC clock select output

DIRWC clock select output

Output port A12

I

PLL VCO OUT input

Ground

Power supply

EXT WC SEL to MWC comparison circuit output

Output port A13

Master clock (256FS)

System clock (128FS)

Ground

Power supply

(Connected to VDD on P.C.B.)

(Connected to VSS on P.C.B.)

(Pulled up on P.C.B.)

(Pulled up on P.C.B.)

System clock (64FS)

Word clock

Synchronous signal

Output port A14

WC output for BNC connector

Output port A15

Clock (256FS) for MY SLOT1

Clock (256FS) for MY SLOT2

Power supply

Synchronous signal for MY SLOT1

Synchronous signal for MY SLOT2

Output port 80

Clock (12MHz) for MY SLOT

Clock (6MHz) for MY SLOT

Ground

Clock (3MHz) for MY SLOT

Output port B1

Word clock (48/44) for MY SLOT

Synchronous signal (48/44) for MY SLOT

Output port B2

Clock for analog circuit

Power supply

I

PLL lock detect signal

I

DIR2 PLL lock signal

Ground

I

Scan test input

I

ATPG test input

I

Test mode selection

Power supply

I

2TR DIN UNLOCK input

I

2TR DIN UNLOCK input

Ground

Output port B3

Lock select output

I

Lock delay input

Output port B4

I

Mute input

Power supply

Mute output 1

Mute output 2

Mute output 3

Mute output 4

Mute output 5

Mute output 6

Power supply

Output port B5

Register setting value output

Register setting value output

Output port B6

SLOT1 16/8 ch selection

SLOT2 16/8 ch selection

Output port B7

FUNCTIONNAME

14

AD8HR

PIN

NO.

I/O

FUNCTIONNAME

PIN

NO.

I/O

FUNCTIONNAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

PLLEN

/TEST

AVdd

Vss

Vdd

/IC

/MUTE

/SSYNC

MCKS

XI

BTYP

/CS

/WR

/RD

CA7

CA6

CA5

CA4

CA3

CA2

Vss

Vdd

CD31/CA1

CD30

CD29

CD28

CD27

CD26

CD25

CD24

Vdd

Vss

CD23

CD22

CD21

CD20

CD19

CD18

CD17

CD16

Vss

Vdd

CD15

CD14

CD13

CD12

CD11

CD10

CD09

CD08

Vss

CD07

CD06

CD05

CD04

CD03

CD02

CD01

CD00

/WAIT

Vdd

Vss

Vdd

SIO00

SIO01

SIO02

SIO03

SIO04

SIO05

SIO06

SIO07

SIO08

SIO09

SIO10

SIO11

SIO12

SIO13

SIO14

SIO15

SIO16

SIO17

SIO18

SIO19

SIO20

SIO21

SIO22

SIO23

SIO24

SIO25

SIO26

SIO27

SIO28

SIO29

SIO30

SIO31

Vss

Vss

Vdd

Vss

Vss

Vdd

Vdd

I

I

I

Analog ground

Power supply (3.3 V)

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173

174

175

176

177

178

179

180

181

182

183

184

185

186

187

188

189

190

191

192

193

194

195

196

197

198

199

200

201

202

203

204

205

206

207

208

SIO32

SIO33

SIO34

SIO35

SIO36

SIO37

SIO38

SIO39

SIO40

SIO41

SIO42

SIO43

SIO44

SIO45

SIO46

SIO47

SIO48

SIO49

SIO50

SIO51

SIO52

SIO53

SIO54

SIO55

SIO56

SIO57

SIO58

SIO59

SIO60

SIO61

SIO62

SIO63

Vss

Vdd

Vss

Vdd

Vss

Vss

Vss

Vdd

Vss

Vdd

Vdd

Vss

/WE

/CAS

SDCK

CKE

/RAS

Vdd

Vss

BA1

BA0

A12

A11

A10

A09

A08

A07

A06

A05

A04

A03

A02

A01

A00

Vss

Vdd

Vss

YSS919B-H (XZ693B00) DSP7 (Digital Signal Processor)

AVss

CPO

Vdd

DA00

DA01

DA02

DA03

DA04

DA05

DA06

DA07

Vss

DA08

DA09

DA10

DA11

DA12

DA13

DA14

DA15

DA16

DA17

DA18

DA19

DA20

DA21

DA22

DA23

DA24

DA25

DA26

DA27

DA28

DA29

DA30

DA31

Vdd

Test mode setting (0: TEST, 1: Normal)

PLL enable input (0: PLL unuse, 1: PLL use)

PLL filter

Initial clear

Power supply (2.5 V)

Ground

I

Mute control (0: SIO mute, 1: SIO normal in-out)

Serial I/O Sync. signal input

Serial I/O master clock input (128 x Fs)

System master clock input (60 MHz or 15 MHz)

Data bus type select (0: 16 bits, 1: 32 bits)

Chip select

Write enable input

Read enable input

CPU data bus / CPU address bus

CPU data bus

Wait output

I/O

Power supply (2.5 V)

Ground

Memory write enable signal

Column address strobe

O

Clock (SDRAM)

O

CKE (SDRAM)

Row address strobe

O

O

Power supply (3.3 V)

Ground

Ground

Power supply (2.5 V)

Power supply (3.3 V)

Ground

Ground

Ground

Power supply (3.3 V)

Power supply (2.5 V)

Ground

Power supply (3.3 V)

Ground

Power supply (2.5 V)

Ground

Power supply (3.3 V)

Ground

Ground

Ground

Power supply (3.3 V)

Ground

Power supply (2.5 V)

Ground

Power supply (3.3 V)

Ground

Ground

Power supply (2.5 V)

Power supply (3.3 V)

Ground

Ground

Power supply (3.3 V)

Power supply (2.5 V)

Ground

Ground

Power supply (3.3 V)

I

I

I

I

I

I

I

I

I

I

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

O

I

CPU address bus

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

CPU data bus

CPU data bus

CPU data bus

Serial data bus

Serial data bus

Serial data bus

Serial data bus

Serial data bus

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

O

O

I

O

O

O

O

O

O

O

O

O

O

O

O

O

O

I

Serial data bus

Serial data bus

Serial data bus

Memory data bus

Memory data bus

Memory data bus

Memory data bus

Memory address (SDRAM, DRAM)

Memory address (SDRAM, DRAM)

Bank select (SDRAM)

MAIN: IC902

15

AD8HR

MBCG61594-130 (X3299A00) ATSC2A

PIN

NO.

1

2

XTST

3

4

WT_X

5

RD_X

6

CS_X

7

HS_SEL

8

RES_X

9

10

ADD[0]

11

ADD[1]

12

ADD[2]

13

ADD[3]

14

ADD[4]

15

ADD[5]

16

ADD[6]

17

ADD[7]

18

19

20

DAT[0]

21

DAT[1]

22

DAT[2]

23

DAT[3]

24

25

26

DAT[4]

27

DAT[5]

28

DAT[6]

29

DAT[7]

30

31

32

PA_I_H_MODE[0]

33

PA_I_H_MODE[1]

34

PA_I_H_MODE[2]

35

PA_O_H_MODE[0]

36

PA_O_H_MODE[1]

37

PA_O_H_MODE[2]

38

PA_SI0_ATI

39

PA_SI1

40

PA_SI2

41

PA_SI3

42

PA_I_SW_SEL

43

PA_SYNC_WC_SI

44

PA_FS256_SI

45

46

PA_FS256_SO

47

PA_SYNC_WC_SO

48

PA_O_SW_SEL

49

50

PA_SO0

51

PA_SO1

52

PA_SO2

53

PA_SO3

54

55

56

PA_CLK_ATI

57

PA_H_M4_SEL

58

PA_O_MUTE

59

PB_SI0

60

PB_SI1

61

PB_SI2

62

PB_SI3

63

PB_I_SW_SEL

64

PB_SYNC_WC_SI

65

PB_FS256_SI

66

67

PB_FS256_SO

68

PB_SYNC_WC_SO

69

PB_O_SW_SEL

70

PB_I_H_MODE[0]

71

PB_I_H_MODE[1]

72

PB_I_H_MODE[2]

I/O FUNCTIONNAME

V

DD

I

V

SS

I

I

I

I

I

V

SS

Power supply +3.3V

LSI test pin

Ground

CPU interface write input

CPU interface read input

CPU interface chip select input

Chip active select

System reset input

Ground

I

I

I

I

I

CPU interface address bus

I

I

I

V

DD

V

SS

Power supply +3.3V

Ground

I/O

I/O

I/O

CPU interface data bus

I/O

V

DD

V

SS

Power supply +3.3V

Ground

I/O

I/O

I/O

CPU interface data bus

I/O

V

SS

V

DD

Ground

Power supply +3.3V

I

I

Port A audio data input mode select

I

I

I

Port A audio data output mode select

I

I

I

I

Port A audio data input

I

I

I

I

V

SS

I

I

I

V

SS

Port A audio data input sync/wc select

Port A audio data input sync/wc input

Port A audio data input bit clock input (256fs)

Ground

Port A audio data output bit clock input (256fs)

Port A audio data output sync/wc input

Port A audio data output sync/wc select

Ground

O

O

O

Port A audio data output

O

V

DD

V

SS

I

I

I

Power supply +3.3V

Ground

Port A ADAT clock input

Port A audio data input buffer active select

Port A mute

I

I

I

Port B audio data input

I

I

I

I

V

SS

I

I

I

Port B audio data input sync/wc select

Port B audio data input sync/wc input

Port B audio data input bit clock input (256fs)

Ground

Port B audio data output bit clock input (256fs)

Port B audio data output sync/wc input

Port B audio data output sync/wc select

I

I

Port B audio data input mode select

I

PIN

NO.

73

V

DD

74

PB_H_M4_SEL

75

PB_O_MUTE

76

V

SS

77

PB_SO0_ATO

78

PB_SO1

79

PB_SO2

80

PB_SO3

81

V

SS

82

PB_O_H_MODE[0]

83

PB_O_H_MODE[1]

84

PB_O_H_MODE[2]

85

PC_I_H_MODE[0]

86

PC_I_H_MODE[1]

87

PC_I_H_MODE[2]

88

PC_H_M4_SEL

89

PC_SI0_ATI

90

V

DD

91

V

SS

92

PC_SI1

93

PC_SI2

94

PC_SI3

95

PC_I_SW_SEL

96

PC_SYNC_WC_SI

97

PC_FS256_SI

98

V

SS

99

PC_FS256_SO

100

PC_SYNC_WC_SO

101

PC_O_SW_SEL

102

V

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

SS

PC_SO0

PC_SO1

PC_SO2

PC_SO3

V

SS

PC_O_MUTE

PC_O_H_MODE[0]

PC_O_H_MODE[1]

PC_O_H_MODE[2]

PC_CLK_ATI

V

SS

PD_I_H_MODE[0]

PD_I_H_MODE[1]

PD_I_H_MODE[2]

V

SS

PD_H_M4_SEL

PD_SI0

PD_SI1

PD_SI2

PD_SI3

PD_I_SW_SEL

PD_SYNC_WC_SI

PD_FS256_SI

V

DD

V

SS

PD_FS256_SO

PD_SYNC_WC_SO

PD_O_SW_SEL

V

SS

PD_SO0_ATO

PD_SO1

PD_SO2

PD_SO3

V

SS

PD_O_MUTE

V

SS

PD_O_H_MODE[0]

PD_O_H_MODE[1]

PD_O_H_MODE[2]

XSM

PA_WC_ATI

PC_WC_ATI

MAIN: IC921

I/O FUNCTIONNAME

Power supply +3.3V

I

I

Port B audio data input buffer active select

Port B mute

Ground

O

O

O

Port B audio data output

O

Ground

I

I

Port B audio data output mode select

I

I

I

Port C audio data input mode select

I

I

I

Port C audio data input buffer active select

Port C audio data input

Power supply +3.3V

Ground

I

I

Port C audio data input

I

I

I

I

Port C audio data input sync/wc select

Port C audio data input sync/wc input

Port C audio data input bit clock input (256fs)

Ground

I

I

I

Port C audio data output bit clock input (256fs)

Port C audio data output sync/wc input

Port C audio data output sync/wc select

Ground

O

O

O

Port C audio data output

O

Ground

I

Port C mute

I

I

Port C audio data output mode select

I

I

Port C ADAT clock input

Ground

I

I

Port D audio data input mode select

I

Ground

I

Port D audio data input buffer active select

I

I

I

Port D audio data input

I

I

I

I

Port D audio data input sync/wc select

Port D audio data input sync/wc input

Port D audio data input bit clock input (256fs)

Power supply +3.3V

Ground

I

I

I

Port D audio data output bit clock input (256fs)

Port D audio data output sync/wc input

Port D audio data output sync/wc select

Ground

O

O

O

Port D audio data output

O

Ground

I

Port D mute

Ground

I

I

Port D audio data output mode select

I

I

O

O

LSI test pin

Port A ADAT word clock output

Port C ADAT word clock output

16

AD8HR

PIN

NO.

I/O FUNCTIONNAME

PIN

NO.

I/O FUNCTIONNAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

DAUX

HDLT

DOUT

VFL

OPT

SYNC

MCC

WC

MCB

MCA

SKSY

XI

XO

P256

LOCK

Vss

TC

DIM1

DIM0

DOM1

DOM0

KM1

I

O

O

O

O

O

O

O

O

O

I

I

O

O

O

O

I

I

I

I

I

Auxiliary input for audio data

Asynchronous buffer operation flag

Audio data output

Parity flag output

Fs x 1 Synchronous output signal for DAC

Fs x 1 Synchronous output signal for DSP

Fs x 64 Bit clock output

Fs x 1 Word clock output

Fs x 128 Bit clock output

Fs x 256 Bit clock output

Clock synchronization control input

Crystal oscillator connection or external

clock input

Crystal oscillator connection

VCO oscillating clock connection

PLL lock flag

Logic section power (GND)

PLL time constant switching output

Data input mode selection

Data input mode selection

Data output mode selection

Data output mode selection

Clock mode switching input 1

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

RSTN

Vdda

CTLN

PCO

(NC)

CTLP

Vssa

TSTN

KM2

KM0

FS1

FS0

CSM

EXTW

DDIN

LR

Vdd

ERR

EMP

CD0

CCK

CLD

I

I

O

I

I

I

I

O

O

I

I

I

O

O

O

O

I

I

System reset input

VCO section power (+5V)

VCO control input N

PLL phase comparison output

VCO control input P

VCO section power (GND)

Test terminal. Open for normal use

Clock mode switching input 2

Clock mode switching input 0

Channel status sampling frequency

display output 1

Channel status sampling frequency

display output 0

Channel status output method selection

External synchronous auxiliary input

word clock

EIAJ (AES/EBU) data input

PLL word clock output

Logic section power (+5 V)

Data error flag output

Channel status emphasis control code

output

3-wire type microcomputer interface data

output

3-wire type microcomputer interface clock

input

3-wire type microcomputer interface load

input

YM3436DK (XG948E00) DIR2 (Digital Format Interface Receiver)

MAIN: IC59

PIN

NO.

I/O FUNCTIONNAME

PIN

NO.

I/O FUNCTIONNAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

VREFL

AV

SS

VCOM

LIN+

LIN-

CKS0

DV

DD

DV

SS

OVF

PDN

DIF

M/S

LRCK

BICK

I

-

O

I

I

I

-

-

O

I

I

I

I/O

I/O

Lch Voltage Reference Input Pin, AVDD

Analog Ground Pin

Common Voltage Output Pin, AVDD/2

Lch Analog Positive Input Pin

Lch Analog Negative Input Pin

Master Clock Select 0 Pin

Digital Power Supply (3.0~5.25V)

Digital Ground

Analog Input Overflow Detect Pin

Power Down Mode Pin

Audio Interface Format Pin

Master / Slave Mode Pin

Output Channel Clock Pin

Audio Serial Data Clock Pin

15

16

17

18

19

20

21

22

23

24

25

26

27

28

SDTO

CKS1

MCLK

DFS0

HPFE

DFS1

BV

SS

AV

SS

AV

DD

RIN-

RIN+

TEST

AV

SS

VREFR

O

I

I

I

I

I

-

-

I

I

I

I

Audio Serial Data Output Pin

Master Clock Select 1 Pin

Master Clock Input Pin

Sampling Speed Select 0 Pin

High Pass Filter Enable Pin

Sampling Speed Select 1 Pin

Substrate Ground Pin

Analog Ground Pin

Analog Power Supply Pin (4.75~5.25V)

Rch Analog Negative Input Pin

Rch Analog Positive Input Pin

Test Pin

Analog Ground

Rch Voltage Reference Input Pin, AVDD

AK5385AVS-E2 (X4662A00) ADC

MAIN: IC105, 305, 505, 705

17

AD8HR

CS8415A-CS (X2089A00) DIR (Digital Audio Interface Receiver)

PIN

NO.

10

11

12

13

14

1

2

3

4

5

6

7

8

9

CDOUT

/CS

/EMPH

RXP0

RXN0

VA+

AGND

FILT

/RST

RMCK

RERR

RXP1

RXP2

RXP3

I/O FUNCTIONNAME

I/O

O

I

O

I

I

Data out (SPI)

Control port chip select (SPI)

Pre-emphasis

AES3/SPDIF receiver port

Positive analog power supply +5V

Analog ground

O

O

PLL loop filter

Reset

Input section recovered master clock

O

Receiver error

I

I

Additional AES3/SPDIF receiver port

I

PIN

NO.

15

16

17

18

19

20

21

22

23

24

25

26

27

28

RXP4

OSCLK

OLRCK

SDOUT

INT

U

OMCK

DGND

VL+

H//S

RXP5

RXP6

CDIN

CCLK

I/O FUNCTIONNAME

I

I/O

I/O

O

O

O

I

I

I

I

I

I

AK4101AVQ (X3813B00) DIT

PIN

NO.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

PDN

MCLK

SDTI1

SDTI2

SDTI3

SDTI4

DD

V

V

SS

BICK

LRCK

FS0/CSN

FS1/CDTI

FS2/CDTO

FS3/CDTO

C1

C2

C3

C4

ANS

BLS

CKS0

I/O FUNCTIONNAME

I/O

I/O

I/O

I/O

I

I

I

I

I

I

-

-

I

I

I

I

I

I

I

I

I

Power Down & Reset Pin

Master Clock Input Pin

Audio Serial Data Input 1 Pin

Audio Serial Data Input 2 Pin

Audio Serial Data Input 3 Pin

Audio Serial Data Input 4 Pin

Power supply (4.75V~5.25V)

Ground

Audio Serial Data Clock Input / Output Pin

Input / Output Channel Clock Pin

Sampling Frequency Select 0 Pin at Synchronous mode /

Host Interface Chip Select Pin at Asynchronous mode

Sampling Frequency Select 1 Pin at Synchronous mode /

Host Interface Data Input Pin at Asynchronous mode

Sampling Frequency Select 2 Pin at Synchronous mode /

Host Interface Bit Clock Input Pin at Asynchronous mode

Sampling Frequency Select 3 Pin at Synchronous mode /

Host Interface Data Output Pin at Asynchronous mode

Channel Status Bit Input Pin for Channel 1

Channel Status Bit Input Pin for Channel 2

Channel Status Bit Input Pin for Channel 3

Channel Status Bit Input Pin for Channel 4

Asynchronous / Synchronous Mode Select Pin

Block Start Input / Output Pin

Clock Mode Select 0 Pin

PIN

NO.

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

V

SS

CKS1

TXN4

TXP4

TXN3

TXP3

DD

V

V

SS

TXN2

TXP2

TXN1

TXP1

DIF0

DD

V

DIF1

DIF2

U1

U2

U3

U4

V12

V34

TRANS

I/O FUNCTIONNAME

-

I

O

O

O

O

-

O

O

O

O

I

-

I

I

I

I

I

I

I

I

I

MAIN: IC929

Additional AES3/SPDIF receiver port

Serial audio output bit clock

Serial audio output left/right clock

Serial audio output data

Interrupt

User data

System clock

Digital ground

Positive logic power supply +5V

Hardware/software mode control

Additional AES3/SPDIF receiver port

Serial control data in (SPI)

Control port clock

MAIN: IC924, SUB: IC903

Ground

Clock Mode Select 1 Pin

Negative Differential Output Pin for Channel 4

Positive Differential Output Pin for Channel 4

Negative Differential Output Pin for Channel 3

Positive Differential Output Pin for Channel 3

Power supply (4.75V~5.25V)

Ground

Negative Differential Output Pin for Channel 2

Positive Differential Output Pin for Channel 2

Negative Differential Output Pin for Channel 1

Positive Differential Output Pin for Channel 1

Audio Serial Interface Select 0 Pin

Power supply (4.75V~5.25V)

Audio Serial Interface Select 1 Pin

Audio Serial Interface Select 2 Pin

User Data Bit Input Pin for Channel 1

User Data Bit Input Pin for Channel 2

User Data Bit Input Pin for Channel 3

User Data Bit Input Pin for Channel 4

Validity Bit Input Pin for Channel 1 & Channel 2

Validity Bit Input Pin for Channel 3 & Channel 4

Audio Routing Mode (Transparent Mode)

Pin at Synchronous mode

18

AD8HR

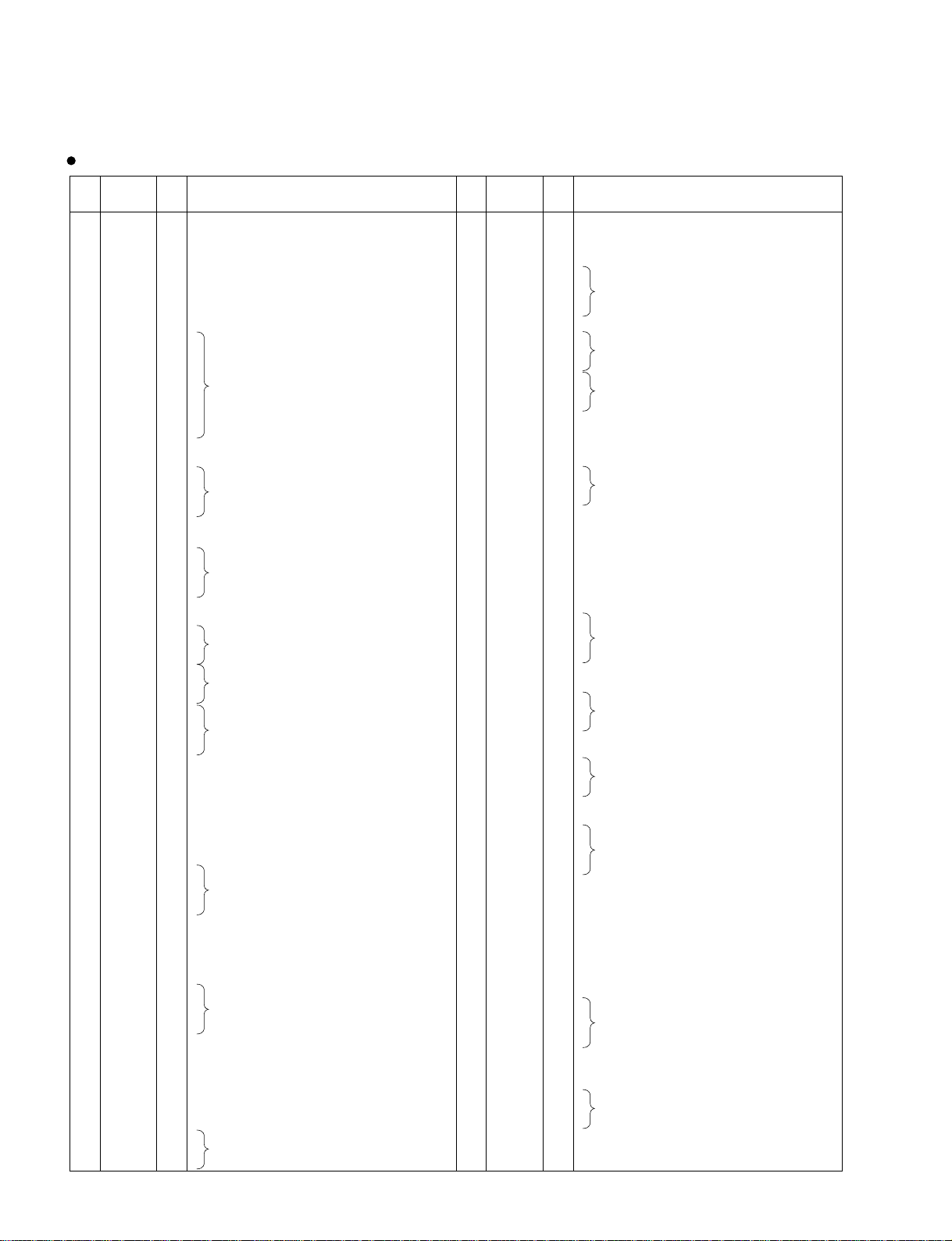

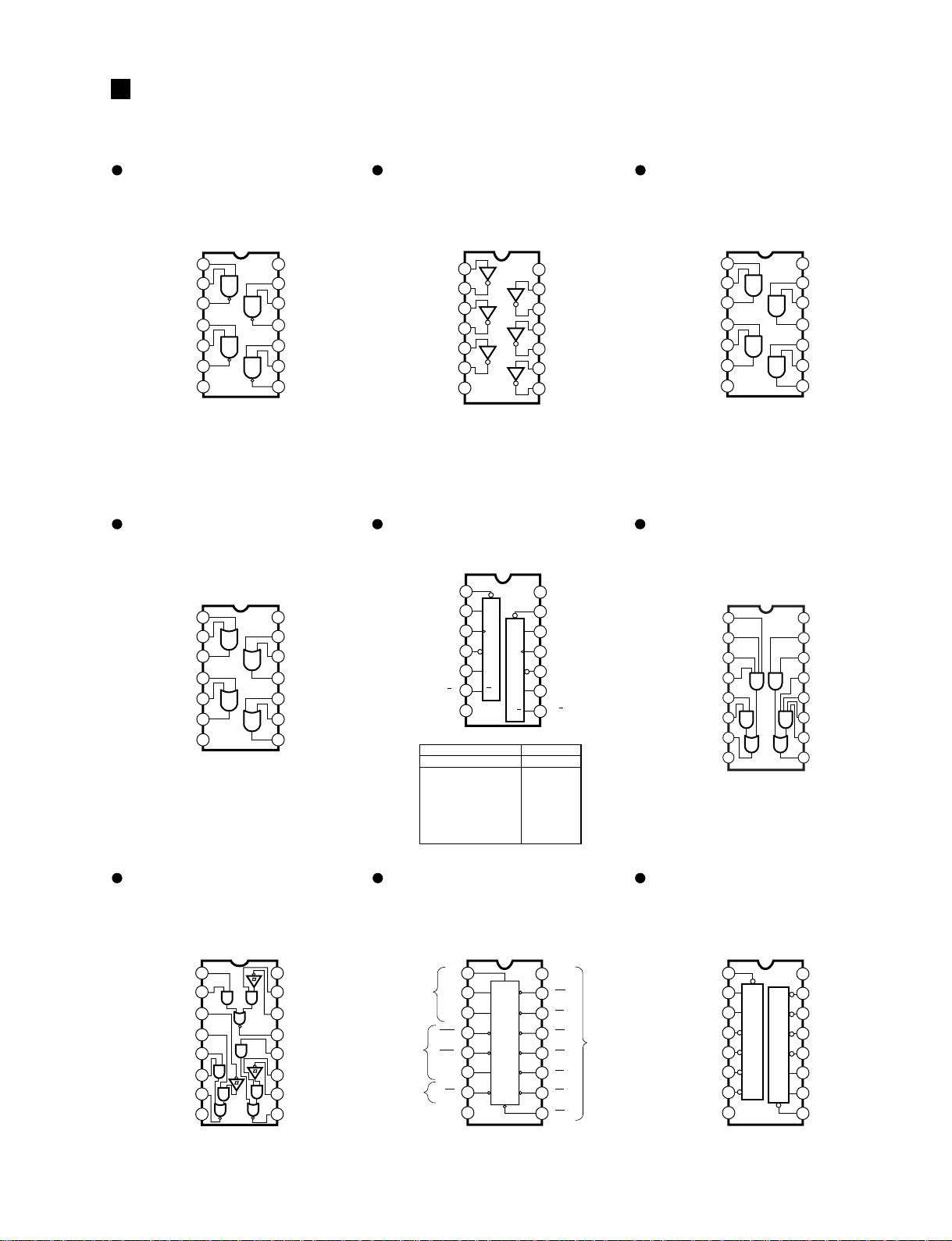

IC BLOCK DIAGRAM

TC74VHC00FT

Quad 2 Input NAND

MAIN: IC53

1A

1B

1Y

HD74LV32AFPEL

Quad 2 Input OR

MAIN: IC12

(X2313A00)

1

2

3

42A

52B

62Y

7Vss

14

VDD

4B

13

4A

12

11 4Y

10 3B

9 3A

8 3Y

(IS003200)

(ICブロック図)

HD74LVU04AFPEL

Hex Inverter

MAIN: IC7

1

1A

2

1Y

3

2A

4

2Y

5

3A

6

3Y

7

Vss

HD74LV74AFPEL

Dual D-Type Flip-Flop

MAIN: IC6

(IS007400)

(XY102A00)

14

VDD

13

6A

12

6Y

11

5A

10

5Y

9

4A

8

4Y

TC74VHC08FT

(XV891A00)

Quad 2 Input AND

MAIN: IC61,901

1

1A

1B

2

1Y

3

42A

52B

62Y

7

VSS

SN75121NSR

(XU816A00)

Dual Line Driver

MAIN: IC926

14

13

12

11 4Y

10 3B

9 3A

8 3Y

VDD

4B

4A

1

1A

1B

2

1Y

3

42A

52B

62Y

7GND

SN75124NSR

(XV930A00)

Triple Line Receiver

MAIN: IC925

1A

1 16

2 15

1B

3 14

2R

4 13

2S

5 12

2A

6 11

2B

7 10

2Y

8 9

GND

14

13

12

11 4Y

10 3B

9 3A

8 3Y

Vcc

4B

4A

Vcc

1S

1R

1Y

3A

3S

3R

3Y

1

1CLR

2

CLR

D

1D

3

1CK

4

1PR

5

1Q

6

1Q

7

GND

INPUTS OUTPUTS

PR CLR CLK D Q Q

H

L

L

H

L

L

H

H

H

H

H

H

D

CK

CLR

PR

CK

Q

Q

Q

Q

X

X

X

X

X

X

H

f

L

f

X

L

SN74LV138ANSR

3 to 8 Demultiplexer

MAIN: IC962

1

A

Select

Enable

Output

G2A

G2B

GND

2

B

3

C

4

5

6

G1

7

Y7

8

B

C

G2A

G2B

G1

Y7 Y5

A

Y0

Y1

Y2

Y3

Y4

Y6

14

VCC

13

2CLR

12

2D

11

2CK

10

2PRPR

9

2Q

8

2Q

H

L

L

H

H

H

H

L

L

H

O

O

Q

Q

(IS013810)

16

Vcc

15

YO

14

Y1

13

Y2

12

11

10

9

Output

Y3

Y4

Y5

Y6

16

1

1A

2

1B

3

1C

4

1D

5

1E

6

1F

7

1Y

8

GND

SN74LV139ANSR

Vcc

15

2F

14

2E

13

2D

12

2C

11

2B

10

2A

9

2Y

(IS013910)

Dual 2 to 4 Demultiplexer

MAIN: IC16

1Y0

1Y1

1Y2

1Y3

GND

1

1G

G

2

A

1A

3

B

1B

4

Y0

5

Y1

6

Y2

7

Y3

8

16

Vcc

G

15

2G

A

14

2A

B

13

2B

Y0

12

2Y0

Y1

11

2Y1

Y2

10

2Y2

Y3

9

2Y3

19

AD8HR

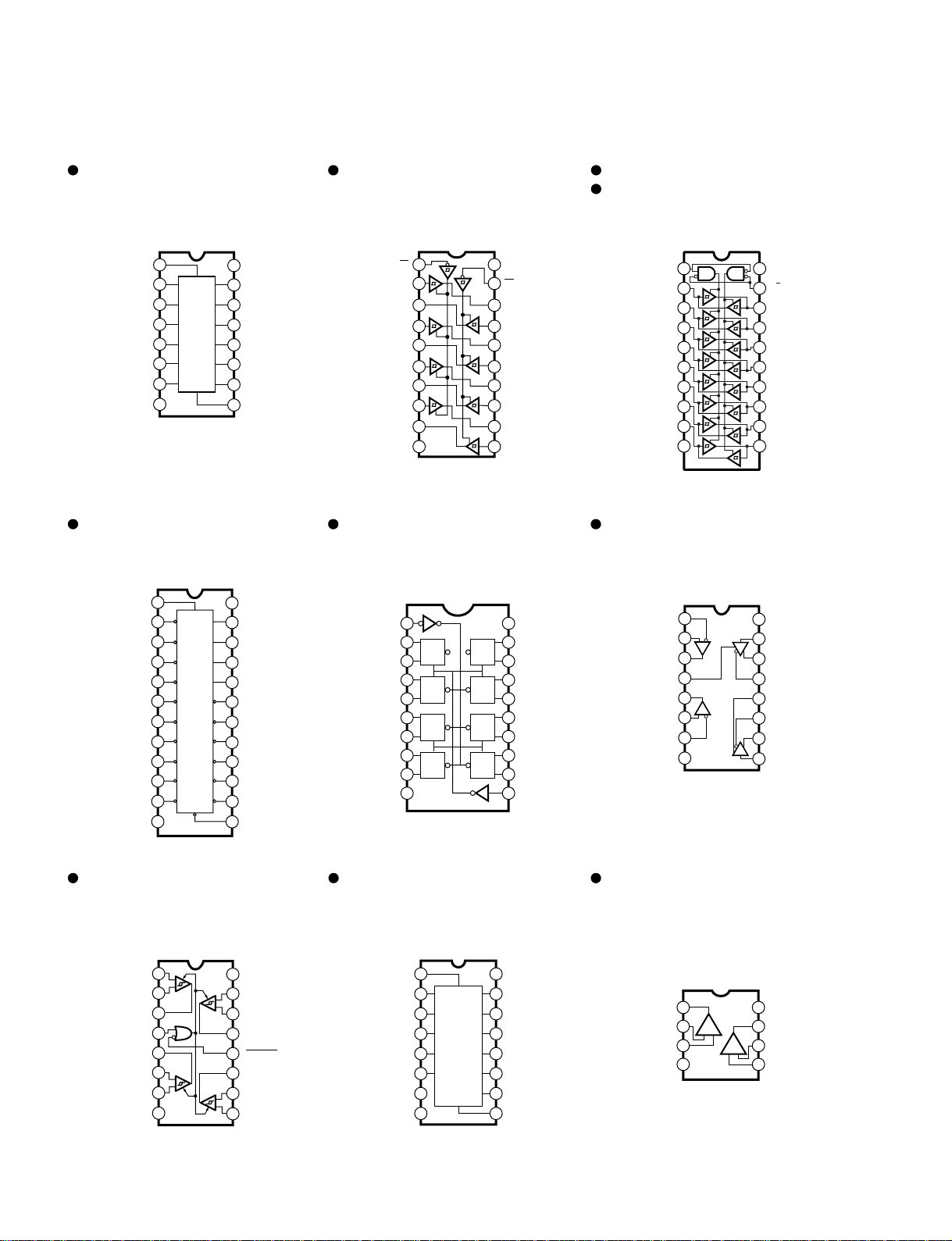

HD74LV157AFPEL

(IS015700)

Quad 2 to 1 Multiplexer

MAIN: IC923,930

1

SELECT

2

1A

1A

3

1B

1B

4

1Y

1Y

5

2A

2A

6

2B

2B

7

2Y

2Y

8

GND

74LVX4245MTCX

16

S3Y

Vcc

G

15

STROBE

4A

14

4A

4B

13

4B

4Y

12

4Y

3A

11

3A

3B

10

3B

9

3Y

(X3097A00)

Dual Supply Octal Bus Transceiver

MAIN: IC17,18

1

VCCA

DIR

GND

GND

2

1

3

A1

2

4

A2

3

A3

5

4

6

A4

5

A5

7

6

8

7

A6

9

A7

8

10

9

A8

11

10 12

12

24

0

11

VCCB

23

VCCB

A

/G

22

B

B1

21

D

20

D

B2

19

G2

B3

18

G1

B4

15

17

B5

16

14

B6

15

13

B7

14

B8

13

GND

TC74VHC244FT

(XW234A00)

Octal 3-State Bus Buffer

MAIN: IC3

1 20

1G

2 19

1A1

3 18

2Y4

4 17

1A2

5 16

2Y3

6 15

1A3

7 14

2Y2

8 13

1A4

9 12

2Y1

10 11

(GND) Vss

HD74LV273AFPEL

VDD (Vcc)

2G

1Y1

2A4

1Y2

2A3

1Y3

2A2

1Y4

2A1

(IS027300)

Octal D-Type Flir Flop

MAIN: IC963-968,970,971

1 20

CLEAR

2 19

Q

1Q

1D

2D

2Q

3Q

3D

4D

4Q

GND

CL

3 18

DCK

4 17

D

CK

CL

5 16

Q

6 15

Q

CL

7 14

DCK

8 13

D

CK

CL

9 12

Q

10 11

Q

CL

DCK

D

CK

CL

Q

Q

CL

DCK

D

CK

CL

Q

VCC

8Q

8D

7D

7Q

6Q

6D

5D

5Q

CLOCK

TC74VHC245FT

TC74VHCT245AFT

(XU797A00)

(XT744A00)

Octal 3-State Bus Transceiver

MAIN: IC1,8,9,14,15,51,56,57,927,928

SUB: IC901,902

1D1R

A1

2

A2

3

A3

4

A4

5

A5

6

A6

7

A7

8

A8

9

GND

10

SN75C1168NSR

(XU073A00)

Line Driver / Receiver

SUB: IC904

COMB: IC951

1

1B

2

1A

3

1R

4

1DE

5

2R

6

2A

7

2B

8

GND

V

CC

20

G

19

B1

18

B2

17

B3

16

B4

15

B5

14

B6

13

B7

12

11

B8

16

Vcc

15

1D

14

1Y

13

1Z

12

2DE

11

2Z

10

2Y

9

2D

DS26C32ATMX

(XU815A00)

Quad Differential Line Receiver

SUB: IC905

1

INPUT A

INPUT A

OUTPUT A

ENABLE

OUTPUT C

INPUT C

INPUT C

GND

+

2

3

4

5

6

+

-

7

8

20

+

+

-

16

15

14

13

12

11

10

9

Vcc

INPUT B

INPUT B

OUTPUT B

ENABLE

OUTPUT D

INPUT D

INPUT D

TC74HC4053AF (EL)

(XY879A00)

Triple 2-Channel

Multiplexer/Demultiplexer

MAIN: IC102,202,302,402,502,602,702,802

Switches IN/OUT

Switches IN/OUT

Switches IN/OUT

Commons OUT/IN

Swiches IN/OUT

Control Inhibit

V

V

1

Y1

Y0

Z1

Z

Z0

EE

SS

Y1

2

Y0

3

Z1

4

Z

5

Z0

6

INH

7

C

8

Y

X

X1

X0

A

B

V

CC

16

Commons OUT/IN

15

Y

Commons OUT/IN

14

X

Swiches IN/OUT

13

X1

Swiches IN/OUT

12

X0

Control Input

11

A

Control Input

10

B

Control Input

9

C

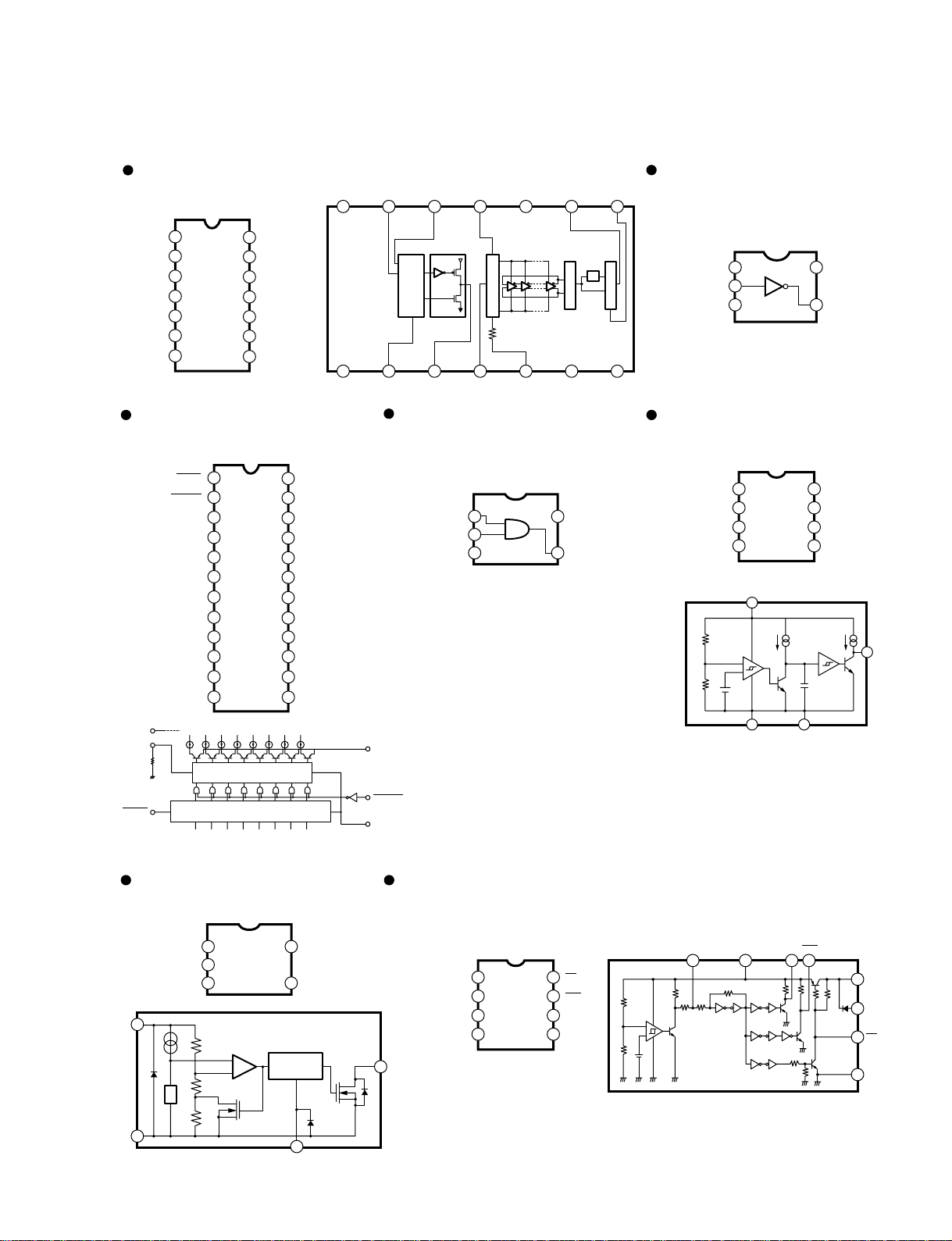

NJM2904V (TE)

NJM2068MD-TE2

(XR532A00)

(X3505A00)

Dual Operational Amplifier

HIC-HA: IC101,102

MAIN: IC5,103,104,203,204,303,304,403,404,

503,504,603,604,703,704,803,804

+DC Voltage

+-

+-

+V

8

Supply

7

Output B

Inverting

6

Input B

Non-Inverting

5

Input B

Output A

Inverting

Input A

Non-Inverting

Input A

Ground

1

2

3

4-V

AD8HR

TLC2932IPWR

PLL

MAIN: IC58

SELECT

VCO OUT

IN-A

F

FIN-B

PFD OUT

1

2

3

4

5

6

7

LOGIC VDD

LOGIC GND

TB62707F (EL)

LED DRIVER

MAIN: TA961

LATCH

ENABLE

NC

IN0

IN1

IN2

IN3

IN4

IN5

IN6

IN7

L-GND

VDD

REXT

LATCH

OUT0

IN0 IN1 IN2 IN3 IN4 IN5 IN6 IN7

(XV064A00)

14

VCO VDD

13

RBIAS

12

VCOIN

11

VCO GND

10

VCO INHBIT

9

PFD INHIBIT

8

NC

(X5127A00)

1

2

3

4

5

6

7

8

9

10

11

12

OUT1 OUT2 OUT3 OUT4 OUT5 OUT6 OUT7

constant currend drivers

8-bit latch

24

23

22

21

20

19

18

17

16

15

14

13

LOGIC V

LOGIC GND4F

DD

V

REXT

P-GND

OUT0

OUT1

OUT2

OUT3

OUT4

OUT5

OUT6

OUT7

P-GND

TC7SH04FU

DD

IN-B

F

1

7

PFD INHIBIT10VCO INHBIT14VCO V

5

9

CHARGE PUMPDETECTOR

6

PFD OUT12V

IN-A

COIN

TC7SH08FU

DD

VCO OUT2SELECT

3

BLAS CONTROL

13

R

BIAS

VCO OUTPUT

11

VCO GND8NC

(XR680A00)

1/2

MUX

2 Input AND

MAIN: IC19,985

Vcc

4

OUT Y

P-GND

ENABLE

L-GND

IN B

1 5

2

IN A

3

GND

Inverter

MAIN: IC20,55,60,922,931,969

IN A

GND

M51953AFP

RESET

MAIN: IC54

R1

R2

NC

N.C.

N.C.

N.C.

GND

1.25V

1

2

3

1

2

3

4

V

CC

7

-

+

4 5

GND CP

(XS775A00)

5

VCC

4

OUT Y

(XW422A00)

8

N.C.

7

V

CC

6

OUT

5

CP

5uA 25uA

-

6

OUT

S-80142ANMC

SYSTEM RESET

DC: IC050

DS

VSS

NC

5

VDD

*1

REF

V

2

SS

V

*1: Parasitic diode

(X3847A00)

1 5

2

3

Delay circuit

Oscillator

+

counter

-

timer

M62021FP

(XI686A00)

SYSTEM RESET

MAIN: IC4

DD

V

1

4

VOUT

4

VOUT

*1

*1

1

DS

VOUT

V

2

BAT

3

VIN

4

Ct

8

CS

7

RES

6

GND

5

RES

R1

60.94k

VR

R2

24k

Vref