XILINX XCF01S, XCF02S, XCF04S, XCF08P, XCF32P User Manual

35

R

Platform Flash In-System Programmable

Configuration PROMs

DS123 (v2.17) October 26, 2009 Product Specification

Features

• In-System Programmable PROMs for Configuration of

Xilinx® FPGAs

• Low-Power Advanced CMOS NOR Flash Process

• Endurance of 20,000 Program/Erase Cycles

• Operation over Full Industrial Temperature Range

(–40°C to +85°C)

• IEEE Standard 1149.1/1532 Boundary-Scan (JTAG)

Support for Programming, Prototyping, and Testing

• JTAG Command Initiation of Standard FPGA

Configuration

• Cascadable for Storing Longer or Multiple Bitstreams

•

Dedicated Boundary-Scan (JTAG) I/O Power Supply (V

CCJ

• I/O Pins Compatible with Voltage Levels Ranging From

1.8V to 3.3V

• Design Support Using the Xilinx ISE® Alliance and

Foundation™ Software Packages

Description

Xilinx introduces the Platform Flash series of in-system

programmable configuration PROMs. Available in

1 to 32 Mb densities, these PROMs provide an easy-to-use,

cost-effective, and reprogrammable method for storing large

Xilinx FPGA configuration bitstreams. The Platform Flash

PROM series includes both the 3.3V XCFxxS PROM and

the 1.8V XCFxxP PROM. The XCFxxS version includes

4 Mb, 2 Mb, and 1 Mb PROMs that support Master Serial

and Slave Serial FPGA configuration modes (Figure 1,

page 2). The XCFxxP version includes 32 Mb, 16 Mb, and

• XCF01S/XCF02S/XCF04S

♦ 3.3V Supply Voltage

♦ Serial FPGA Configuration Interface

♦ Available in Small-Footprint VO20 and VOG20

Packages

• XCF08P/XCF16P/XCF32P

♦ 1.8V Supply Voltage

♦ Serial or Parallel FPGA Configuration Interface

♦ Available in Small-Footprint VO48, VOG48, FS48,

and FSG48 Packages

)

♦ Design Revision Technology Enables Storing and

Accessing Multiple Design Revisions for

Configuration

♦ Built-In Data Decompressor Compatible with Xilinx

Advanced Compression Technology

8 Mb PROMs that support Master Serial, Slave Serial,

Master SelectMAP, and Slave SelectMAP FPGA

configuration modes (Figure 2, page 2).

When driven from a stable, external clock, the PROMs can

output data at rates up to 33 MHz. Refer to "AC Electrical

Characteristics," page 16 for timing considerations.

A summary of the Platform Flash PROM family members

and supported features is shown in Tab le 1 .

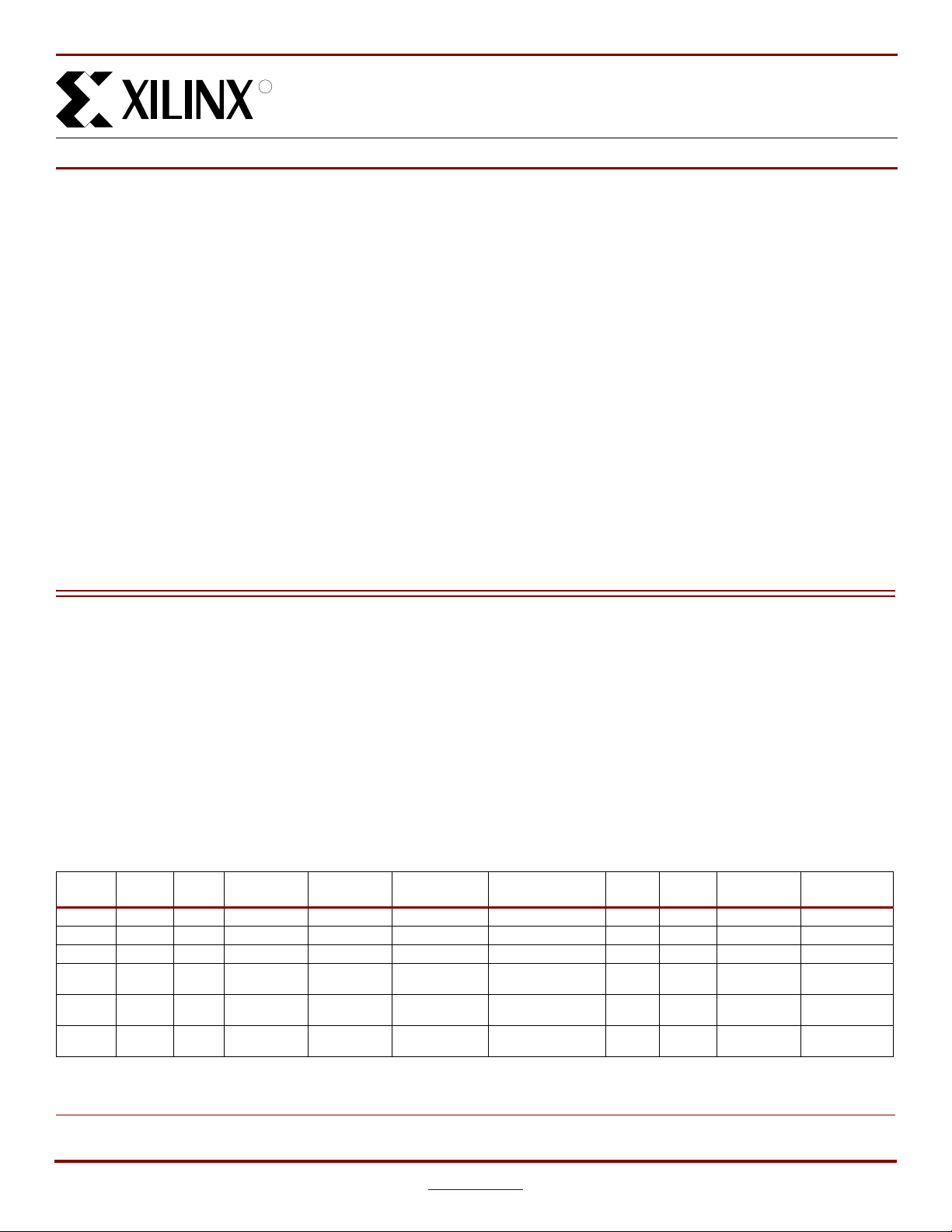

Tab le 1 : Platform Flash PROM Features

Device

XCF01S 1 3.3 1.8 – 3.3 2.5 – 3.3 VO20/VOG20 33

XCF02S 2 3.3 1.8 – 3.3 2.5 – 3.3 VO20/VOG20 33

XCF04S 4 3.3 1.8 – 3.3 2.5 – 3.3 VO20/VOG20 33

XCF08P 8 1.8 1.8 – 3.3 2.5 – 3.3

XCF16P 16 1.8 1.8 – 3.3 2.5 – 3.3

XCF32P 32 1.8 1.8 – 3.3 2.5 – 3.3

Notes:

1. XCF08P supports storage of a design revision only when cascaded with another XCFxxP PROM. See "Design Revisioning," page 8 for details.

© Copyright 2003–2009 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, and other designated brands included herein are trademarks of Xilinx in the United States and

other countries. All other trademarks are the property of their respective owners.

DS123 (v2.17) October 26, 2009 www.xilinx.com

Product Specification 1

Density

(Mb)

V

CCINT

(V)

V

CCO

Range

(V)

V

CCJ

Range

(V)

Packages

VO48/VOG48

FS48/FSG48

VO48/VOG48

FS48/FSG48

VO48/VOG48

FS48/FSG48

Program In-system

via JTAG

3333

3333 3

3333 3

Serial

Config.

Parallel

Config.

Design

Revisioning

(1)

Compression

3

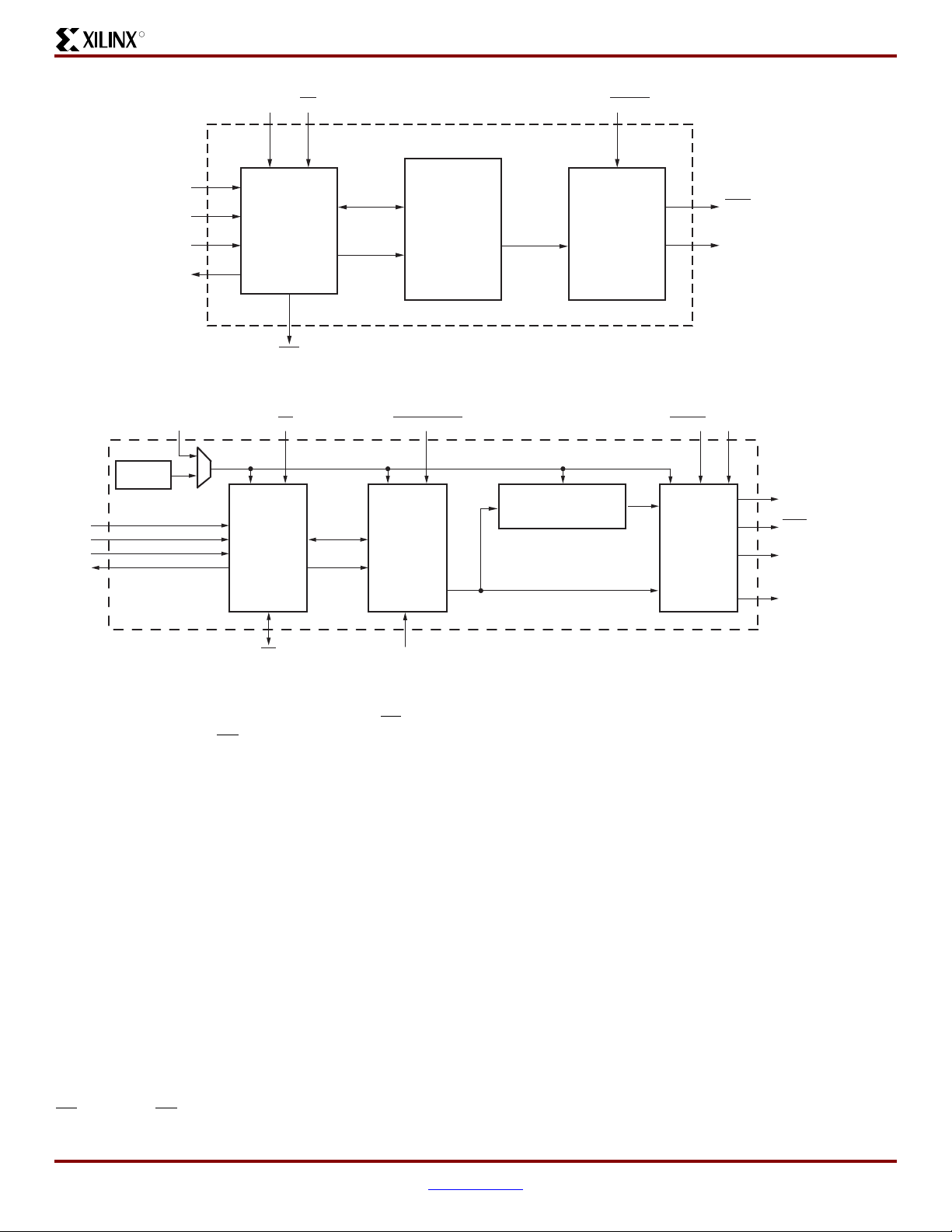

X-Ref Target - Figure 1

R

CLK CE

Platform Flash In-System Programmable Configuration PROMs

OE/RESET

X-Ref Target - Figure 2FI

TCK

TMS

TDI

TDO

TCK

TMS

TDI

TDO

Control

and

JTAG

Interface

CF

Data

Address

Memory

Data

Serial

Interface

Figure 1: XCFxxS Platform Flash PROM Block Diagram

CLK CE EN_EXT_SEL OE/RESET BUSY

OSC

Control

and

JTAG

Interface

Data

Address

Memory

Data

Decompressor

Serial

or

Parallel

Interface

CEO

DATA (D0)

Serial Mode

ds123_01_30603

CLKOUT

CEO

DATA (D0)

(Serial/Parallel Mode)

D[1:7]

(Parallel Mode)

CF

REV_SEL [1:0]

Figure 2: XCFxxP Platform Flash PROM Block Diagram

When the FPGA is in Master Serial mode, it generates a

configuration clock that drives the PROM. With CF

short access time after CE

and OE are enabled, data is

High, a

available on the PROM DATA (D0) pin that is connected to

the FPGA DIN pin. New data is available a short access

time after each rising clock edge. The FPGA generates the

appropriate number of clock pulses to complete the

configuration.

When the FPGA is in Slave Serial mode, the PROM and the

FPGA are both clocked by an external clock source, or

optionally, for the XCFxxP PROM only, the PROM can be

used to drive the FPGA’s configuration clock.

The XCFxxP version of the Platform Flash PROM also

supports Master SelectMAP and Slave SelectMAP (or

Slave Parallel) FPGA configuration modes. When the FPGA

is in Master SelectMAP mode, the FPGA generates a

configuration clock that drives the PROM. When the FPGA

is in Slave SelectMAP Mode, either an external oscillator

generates the configuration clock that drives the PROM and

the FPGA, or optionally, the XCFxxP PROM can be used to

drive the FPGA’s configuration clock. With BUSY Low and

CF

High, after CE and OE are enabled, data is available on

the PROMs DATA (D0-D7) pins. New data is available a

DS123_19_031908

short access time after each rising clock edge. The data is

clocked into the FPGA on the following rising edge of the

CCLK. A free-running oscillator can be used in the Slave

Parallel/Slave SelectMAP mode.

The XCFxxP version of the Platform Flash PROM provides

additional advanced features. A built-in data decompressor

supports utilizing compressed PROM files, and design

revisioning allows multiple design revisions to be stored on

a single PROM or stored across several PROMs. For design

revisioning, external pins or internal control bits are used to

select the active design revision.

Multiple Platform Flash PROM devices can be cascaded to

support the larger configuration files required when

targeting larger FPGA devices or targeting multiple FPGAs

daisy chained together. When utilizing the advanced

features for the XCFxxP Platform Flash PROM, such as

design revisioning, programming files which span cascaded

PROM devices can only be created for cascaded chains

containing only XCFxxP PROMs. If the advanced XCFxxP

features are not enabled, then the cascaded chain can

include both XCFxxP and XCFxxS PROMs.

DS123 (v2.17) October 26, 2009 www.xilinx.com

Product Specification 2

R

Platform Flash In-System Programmable Configuration PROMs

See UG161, Platform Flash PROM User Guide, for detailed

guidelines on PROM-to-FPGA configuration hardware

connections, for software usage, for a reference list of Xilinx

FPGAs, and for the respective compatible Platform Flash

PROMs. Ta bl e 2 lists the Platform Flash PROMs and their

capacities.

Tab le 2 : Platform Flash PROM Capacity

Platform

Flash PROM

XCF01S 1,048,576 XCF08P 8,388,608

XCF02S 2,097,152 XCF16P 16,777,216

XCF04S 4,194,304 XCF32P 33,554,432

Configuration

Bits

Platform

Flash PROM

Configuration

Bits

Programming

The Platform Flash PROM is a reprogrammable NOR flash

device (refer "Quality and Reliability Characteristics,"

page 14 for the program/erase specifications).

Reprogramming requires an erase followed by a program

operation. A verify operation is recommended after the

program operation to validate the correct transfer of data

from the programmer source to the Platform Flash PROM.

Several programming solutions are available.

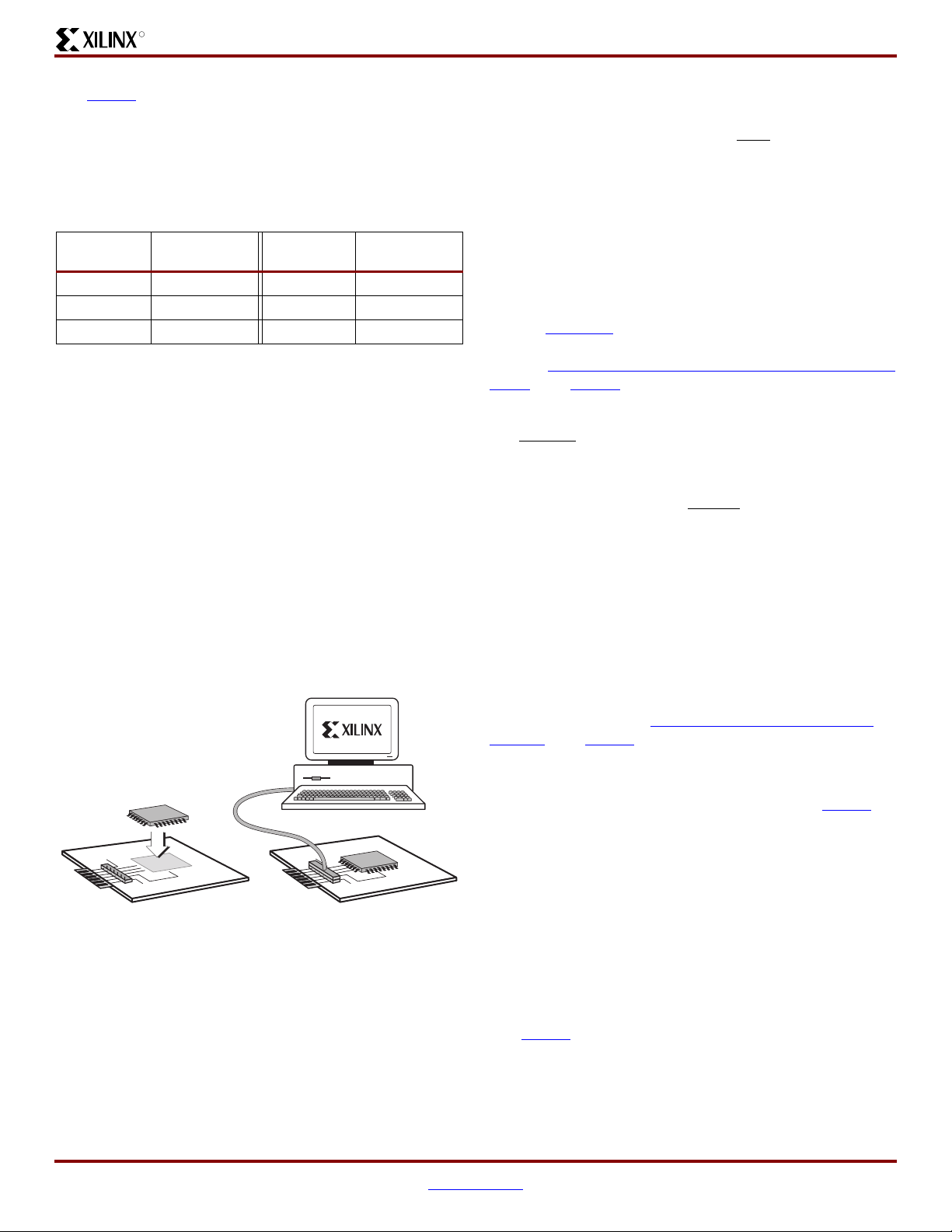

In-System Programming

In-System Programmable PROMs can be programmed

individually, or two or more can be daisy-chained together

and programmed in-system via the standard 4-pin JTAG

protocol as shown in Figure 3.

X-Ref Target - Figure 3

instruction sequence. The iMPACT software also outputs

serial vector format (SVF) files for use with any tools that

accept SVF format, including automatic test equipment.

During in-system programming, the CEO

output is driven

High. All other outputs are held in a high-impedance state or

held at clamp levels during in-system programming. All

non-JTAG input pins are ignored during in-system

programming, including CLK, CE, CF, OE/RESET, BUSY,

EN_EXT_SEL, and REV_SEL[1:0]. In-system programming

is fully supported across the recommended operating

voltage and temperature ranges.

Embedded, in-system programming reference designs,

such as X

APP058, Xilinx In-System Programming Using an

Embedded Microcontroller, are available on the Xilinx web

page for P

ROM Programming and Data Storage Application

Notes. See UG161, Platform Flash PROM User Guide, for

an advanced update methodology that uses the Design

Revisioning feature in the Platform Flash XCFxxP PROMs.

OE/RESET

The 1/2/4 Mb XCFxxS Platform Flash PROMs in-system

programming algorithm results in issuance of an internal

device reset that causes OE/RESET

to pulse Low.

External Programming

In traditional manufacturing environments, third-party

device programmers can program Platform Flash PROMs

with an initial memory image before the PROMs are

assembled onto boards. Contact a preferred third-party

programmer vendor for Platform Flash PROM support

information. A sample list of third-party programmer

vendors with Platform Flash PROM support is available on

the Xilinx web page for T

Support. See UG161, Platform Flash PROM User Guide,

for the PROM data file format required for programmers.

hird-Party Programmer Device

Pre-programmed PROMs can be assembled onto boards

using the typical soldering process guidelines in UG112

,

Device Package User Guide. A pre-programmed PROM’s

memory image can be updated after board assembly using

V

CC

GND

an in-system programming solution.

Reliability and Endurance

(a) (b)

Figure 3: JTAG In-System Programming Operation

(a)SolderDevicetoPCB

(b) Program Using Download Cable

In-system programming offers quick and efficient design

iterations and eliminates unnecessary package handling or

socketing of devices. The programming data sequence is

delivered to the device using either Xilinx iMPACT software

and a Xilinx download cable, a third-party JTAG

development system, a JTAG-compatible board tester, or a

simple microprocessor interface that emulates the JTAG

DS123 (v2.17) October 26, 2009 www.xilinx.com

Product Specification 3

DS123_33_031908

Xilinx in-system programmable products provide a

guaranteed endurance level of 20,000 in-system

program-erase cycles and a minimum data retention of 20

years. Each device meets all functional, performance, and

data retention specifications within this endurance limit.

See UG116

, Xilinx Device Reliability Report, for device

quality, reliability, and process node information.

R

Design Security

Platform Flash In-System Programmable Configuration PROMs

The Xilinx in-system programmable Platform Flash PROM

devices incorporate advanced data security features to fully

protect the FPGA programming data against unauthorized

reading via JTAG. The XCFxxP PROMs can also be

programmed to prevent inadvertent writing via JTAG.

Ta bl e 3 and Ta b l e 4 show the security settings available for

the XCFxxS PROM and XCFxxP PROM, respectively.

Read Protection

The read protect security bit can be set by the user to

prevent the internal programming pattern from being read or

copied via JTAG. Read protection does not prevent write

operations. For the XCFxxS PROM, the read protect

security bit is set for the entire device, and resetting the read

protect security bit requires erasing the entire device. For

the XCFxxP PROM the read protect security bit can be set

for individual design revisions, and resetting the read

protect bit requires erasing the particular design revision.

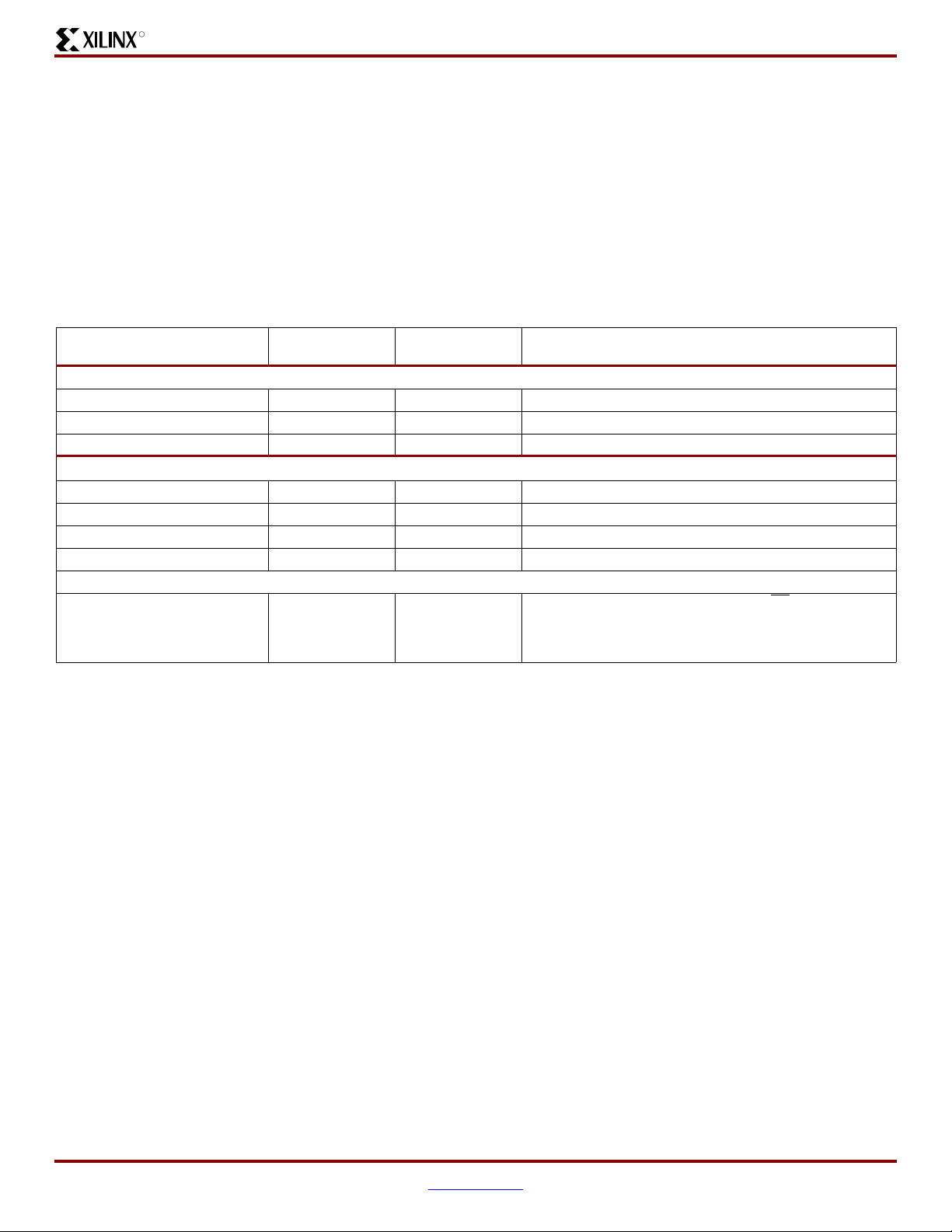

Tab le 4 : XCFxxP Design Revision Data Security Options

Read Protect Write Protect

Reset (default) Reset (default)

Reset (default) Set

Set Reset (default)

Set Set

Write Protection

The XCFxxP PROM device also allows the user to write

protect (or lock) a particular design revision or PROM option

settings. Write protection helps to prevent an inadvertent

JTAG instruction from modifying an area by write protecting

the area and by locking the erase instruction. The writeprotection setting can be cleared by erasing the protected

area. However, an XSC_UNLOCK instruction must first be

issued to the XCFxxP PROM to unlock the ISC_ERASE

instruction. Refer to the XCFxxP PROM BSDL file for the

XSC_UNLOCK and ISC_ERASE instructions.

Caution!

XSC_UNLOCK when performing an Erase operation on an

XCFxxP PROM and, thus, always unlocks the write

protection.

Tab l e 3 : XCFxxS Device Data Security Options

Read Protect

Reset (default)

Set

Read/Verify

Inhibited

The iMPACT software always issues a

Read/Verify

Inhibited

Program

Inhibited

Erase

Inhibited

3

Program Inhibited Erase Inhibited

33

3

333

DS123 (v2.17) October 26, 2009 www.xilinx.com

Product Specification 4

R

IEEE 1149.1 Boundary-Scan (JTAG)

Platform Flash In-System Programmable Configuration PROMs

The Platform Flash PROM family is compatible with the IEEE

1149.1 Boundary-Scan standard and the IEEE 1532 insystem configuration standard. A Test Access Port (TAP) and

registers are provided to support all required Boundary-Scan

instructions, as well as many of the optional instructions

specified by IEEE Std. 1149.1. In addition, the JTAG interface

is used to implement in-system programming (ISP) to facilitate

configuration, erasure, and verification operations on the

Platform Flash PROM device. Ta b le 5 lists the required and

optional Boundary-Scan instructions supported in the

Platform Flash PROMs. Refer to the IEEE Std. 1149.1

specification for a complete description of Boundary-Scan

architecture and the required and optional instructions.

Caution!

compliant with the JTAG 1149.1 specification. If a temporary

pause of a JTAG shift operation is required, then stop the

JTAG TCK clock and maintain the JTAG TAP within the JTAG

Shift-IR or Shift-DR TAP state. Do not transition the XCFxxP

JTAG TAP through the JTAG Pause-IR or Pause-DR TAP state

to temporarily pause a JTAG shift operation.

The XCFxxP JTAG TAP pause states are not fully

Tab le 5 : Platform Flash PROM Boundary-Scan Instructions

Boundary-Scan Command

Required Instructions

BYPASS FF FFFF Enables BYPASS

SAMPLE/PRELOAD 01 0001 Enables Boundary-Scan SAMPLE/PRELOAD operation

EXTEST 00 0000 Enables Boundary-Scan EXTEST operation

Optional Instructions

CLAMP FA 00FA Enables Boundary-Scan CLAMP operation

HIGHZ FC 00FC Places all outputs in high-impedance state simultaneously

IDCODE FE 00FE Enables shifting out 32-bit IDCODE

USERCODE FD 00FD Enables shifting out 32-bit USERCODE

Platform Flash PROM Specific Instructions

CONFIG EE 00EE

XCFxxS IR[7:0]

(hex)

XCFxxP IR[15:0]

(hex)

Instruction Description

Initiates FPGA configuration by pulsing CF

(For the XCFxxP this command also resets the selected

design revision based on either the external REV_SEL[1:0]

pins or on the internal design revision selection bits.)

pin Low once.

(1)

Notes:

1. For more information see "Initiating FPGA Configuration," page 10.

Instruction Register

The Instruction Register (IR) for the Platform Flash PROM

is connected between TDI and TDO during an instruction

scan sequence. In preparation for an instruction scan

sequence, the instruction register is parallel loaded with a

fixed instruction capture pattern. This pattern is shifted out

onto TDO (LSB first), while an instruction is shifted into the

instruction register from TDI.

XCFxxS Instruction Register (8 bits wide)

The Instruction Register (IR) for the XCFxxS PROM is eight

bits wide and is connected between TDI and TDO during an

instruction scan sequence. The detailed composition of the

instruction capture pattern is illustrated in Table6, page6.

The instruction capture pattern shifted out of the XCFxxS

device includes IR[7:0]. IR[7:5] are reserved bits and are set

to a logic 0. The ISC Status field, IR[4], contains logic 1 if

the device is currently in In-System Configuration (ISC)

mode; otherwise, it contains logic 0. The Security field,

IR[3], contains logic 1 if the device has been programmed

with the security option turned on; otherwise, it contains

logic 0. IR[2] is unused, and is set to '0'. The remaining bits

IR[1:0] are set to '01' as defined by IEEE Std. 1149.1.

XCFxxP Instruction Register (16 bits wide)

The Instruction Register (IR) for the XCFxxP PROM is sixteen

bits wide and is connected between TDI and TDO during an

instruction scan sequence. The detailed composition of the

instruction capture pattern is illustrated in Table 7, page 6.

The instruction capture pattern shifted out of the XCFxxP

device includes IR[15:0]. IR[15:9] are reserved bits and are set

to a logic 0. The ISC Error field, IR[8:7], contains a 10 when an

ISC operation is a success; otherwise a 01 when an In-System

Configuration (ISC) operation fails. The Erase/Program

(ER/PROG) Error field, IR[6:5], contains a 10 when an erase

or program operation is a success; otherwise a 01 when an

erase or program operation fails. The Erase/Program

(ER/PROG) Status field, IR[4], contains a logic 0 when the

device is busy performing an erase or programming operation;

otherwise, it contains a logic 1. The ISC Status field, IR[3],

contains logic 1 if the device is currently in In-System

Configuration (ISC) mode; otherwise, it contains logic 0. The

DONE field, IR[2], contains logic 1 if the sampled design

revision has been successfully programmed; otherwise, a logic

0 indicates incomplete programming. The remaining bits

IR[1:0] are set to 01 as defined by IEEE Std. 1149.1.

DS123 (v2.17) October 26, 2009 www.xilinx.com

Product Specification 5

R

Platform Flash In-System Programmable Configuration PROMs

Tab le 6 : XCFxxS Instruction Capture Values Loaded into IR as part of an Instruction Scan Sequence

TDI →

IR[7:5] IR[4] IR[3] IR[2] IR[1:0]

Reserved ISC Status Security 0 0 1

Tab le 7 : XCFxxP Instruction Capture Values Loaded into IR as part of an Instruction Scan Sequence

IR[15:9] IR[8:7] IR[6:5] IR[4] IR[3] IR[2] IR[1:0]

TDI →

Reserved ISC Error

ER/PROG

Error

ER/PROG

Status

ISC Status DONE 0 1

Boundary-Scan Register

→ TDO

→ TDO

The Boundary-Scan register is used to control and observe

the state of the device pins during the EXTEST,

SAMPLE/PRELOAD, and CLAMP instructions. Each output

pin on the Platform Flash PROM has two register stages which

contribute to the Boundary-Scan register, while each input pin

has only one register stage. The bidirectional pins have a total

of three register stages which contribute to the Boundary-Scan

register. For each output pin, the register stage nearest to TDI

controls and observes the output state, and the second stage

closest to TDO controls and observes the High-Z enable state

of the output pin. For each input pin, a single register stage

controls and observes the input state of the pin. The

bidirectional pin combines the three bits, the input stage bit is

first, followed by the output stage bit and finally the output

enable stage bit. The output enable stage bit is closest to TDO.

See Table 12, page 24 and Table 13, page 26 for the

Boundary-Scan bit order for all connected device pins, or see

the appropriate BSDL file for the complete Boundary-Scan bit

order description under the “attribute

BOUNDARY_REGISTER” section in the BSDL file. The bit

assigned to Boundary-Scan cell 0 is the LSB in the BoundaryScan register, and is the register bit closest to TDO.

Identification Registers

IDCODE Register

The IDCODE is a fixed, vendor-assigned value that is used to

electrically identify the manufacturer and type of the device

being addressed. The IDCODE register is 32 bits wide. The

IDCODE register can be shifted out for examination by using

the IDCODE instruction. The IDCODE is available to any

other system component via JTAG. Ta bl e 8 lists the IDCODE

register values for the Platform Flash PROMs.

The IDCODE register has the following binary format:

vvvv:ffff:ffff:aaaa:aaaa:cccc:cccc:ccc1

where

v = the die version number

f = the PROM family code

a = the specific Platform Flash PROM product ID

c = the Xilinx manufacturer's ID

The LSB of the IDCODE register is always read as logic 1

as defined by IEEE Std. 1149.1.

Tab l e 8 : IDCODES Assigned to Platform Flash PROMs

Device IDCODE

XCF01S <v>5044093

XCF02S <v>5045093

XCF04S <v>5046093

XCF08P <v>5057093

XCF16P <v>5058093

XCF32P <v>5059093

Notes:

1. The <v> in the IDCODE field represents the device’s revision

code (in hex) and can vary.

(1)

(hex)

USERCODE Register

The USERCODE instruction gives access to a 32-bit user

programmable scratch pad typically used to supply

information about the device's programmed contents. By

using the USERCODE instruction, a user-programmable

identification code can be shifted out for examination. This

code is loaded into the USERCODE register during

programming of the Platform Flash PROM. If the device is

blank or was not loaded during programming, the

USERCODE register contains FFFFFFFFh.

Customer Code Register

For the XCFxxP Platform Flash PROM, in addition to the

USERCODE, a unique 32-byte Customer Code can be

assigned to each design revision enabled for the PROM.

The Customer Code is set during programming, and is

typically used to supply information about the design

revision contents. A private JTAG instruction is required to

read the Customer Code. If the PROM is blank, or the

Customer Code for the selected design revision was not

loaded during programming, or if the particular design

revision is erased, the Customer Code contains all ones.

DS123 (v2.17) October 26, 2009 www.xilinx.com

Product Specification 6

R

Platform Flash In-System Programmable Configuration PROMs

Platform Flash PROM TAP Characteristics

The Platform Flash PROM family performs both in-system

programming and IEEE 1149.1 Boundary-Scan (JTAG) testing

via a single 4-wire Test Access Port (TAP). This simplifies

system designs and allows standard Automatic Test

Equipment to perform both functions. The AC characteristics

of the Platform Flash PROM TAP are described as follows.

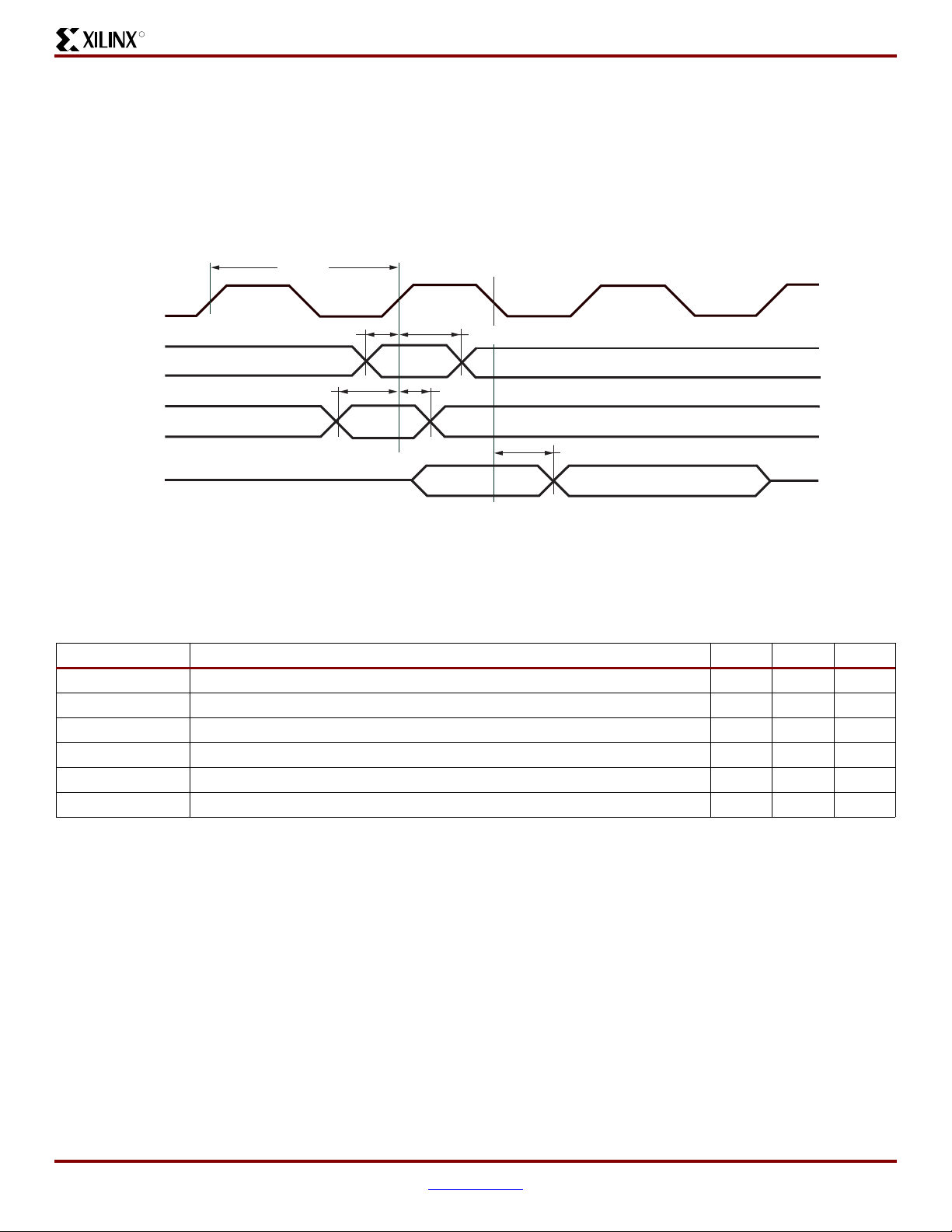

X-Ref Target - Figure 4

T

CKMIN

TCK

T

MSS

TMS

T

DIS

T

TDI

TDO

Figure 4: Test Access Port Timing

TAP AC Parameters

TAP Timing

Figure 4 shows the timing relationships of the TAP signals.

These TAP timing characteristics are identical for both

Boundary-Scan and ISP operations.

T

MSH

DIH

T

DOV

DS123_04_031808

Ta bl e 9 shows the timing parameters for the TAP waveforms shown in Figure 4.

Tab le 9 : Test Access Port Timing Parameters

Symbol Description Min Max Units

T

CKMIN

T

MSS

T

MSH

T

DIS

T

DIH

T

DOV

TCK minimum clock period when V

TMS setup time when V

TMS hold time when V

TDI setup time when V

TDI hold time when V

TDO valid delay when V

= 2.5V or 3.3V 8 – ns

CCJ

= 2.5V or 3.3V 25 – ns

CCJ

= 2.5V or 3.3V 8 – ns

CCJ

= 2.5V or 3.3V 25 – ns

CCJ

= 2.5V or 3.3V – 22 ns

CCJ

= 2.5V or 3.3V 67 – ns

CCJ

DS123 (v2.17) October 26, 2009 www.xilinx.com

Product Specification 7

R

Additional Features for the XCFxxP

Platform Flash In-System Programmable Configuration PROMs

Internal Oscillator

The 8/16/32 Mb XCFxxP Platform Flash PROMs include an

optional internal oscillator which can be used to drive the

CLKOUT and DATA pins on FPGA configuration interface.

The internal oscillator can be enabled when programming

the PROM, and the oscillator can be set to either the default

frequency or to a slower frequency. Refer to the “XCFxxP

Decompression and Clock Options” chapter of UG161

Platform Flash PROM User Guide, for internal oscillator

recommendations.

,

CLKOUT

The 8/16/32 Mb XCFxxP Platform Flash PROMs include the

programmable option to enable the CLKOUT signal which

allows the PROM to provide a source synchronous clock

aligned to the data on the configuration interface. The

CLKOUT signal is derived from one of two clock sources: the

CLK input pin or the internal oscillator. The input clock source

is selected during the PROM programming sequence. Output

data is available on the rising edge of CLKOUT.

The CLKOUT signal is enabled during programming, and is

active when CE

rising edge transition, if OE/RESET

terminal count has not been reached, then CLKOUT

remains active for an additional eights clock cycles before

being disabled. On a OE/RESET

CLKOUT is immediately disabled. When disabled, the

CLKOUT pin is put into a high-impedance state and should

be pulled High externally to provide a known state.

When cascading Platform Flash PROMs with CLKOUT

enabled, after completing it's data transfer, the first PROM

disables CLKOUT and drives the CEO

PROM in the PROM chain. The next PROM begins driving

the CLKOUT signal once that PROM is enabled and data is

available for transfer.

During high-speed parallel configuration without

compression, the FPGA drives the BUSY signal on the

configuration interface. When BUSY is asserted High, the

PROMs internal address counter stops incrementing, and

the current data value is held on the data outputs. While

BUSY is High, the PROM continues driving the CLKOUT

signal to the FPGA, clocking the FPGA’s configuration logic.

When the FPGA deasserts BUSY, indicating that it is ready

to receive additional configuration data, the PROM begins

driving new data onto the configuration interface.

is Low and OE/RESET is High. On CE

is High and the PROM

falling edge transition,

pin enabling the next

SelectMAP (parallel) configuration modes are supported for

FPGA configuration when using a XCFxxP PROM

programmed with a compressed bitstream. Compression

rates vary depending on several factors, including the target

device family and the target design contents.

The decompression option is enabled during the PROM

programming sequence. The PROM decompresses the

stored data before driving both clock and data onto the

FPGA's configuration interface. If Decompression is

enabled, then the Platform Flash clock output pin

(CLKOUT) must be used as the clock signal for the

configuration interface, driving the target FPGA's

configuration clock input pin (CCLK). Either the PROM's

CLK input pin or the internal oscillator must be selected as

the source for CLKOUT. Any target FPGA connected to the

PROM must operate as slave in the configuration chain,

with the configuration mode set to Slave Serial mode or

Slave SelectMap (parallel) mode.

When decompression is enabled, the CLKOUT signal

becomes a controlled clock output with a reduced maximum

frequency. When decompressed data is not ready, the

CLKOUT pin is put into a high-Z state and must be pulled

High externally to provide a known state.

The BUSY input is automatically disabled when

decompression is enabled.

See the "Decompression Setups" section in the Platform

Flash PROM User Guide for setup details.

Design Revisioning

Design Revisioning allows the user to create up to four

unique design revisions on a single PROM or stored across

multiple cascaded PROMs. Design Revisioning is supported

for the 8/16/32 Mb XCFxxP Platform Flash PROMs in both

serial and parallel modes. Design Revisioning can be used

with compressed PROM files, and also when the CLKOUT

feature is enabled. The PROM programming files along with

the revision information files (.cfi) are created using the

iMPACT software. The .cfi file is required to enable design

revision programming in iMPACT.

A single design revision is composed of from 1 to n 8Mb

memory blocks. If a single design revision contains less

than 8 Mb of data, then the remaining space is padded with

all ones. A larger design revision can span several 8 Mb

memory blocks, and any space remaining in the last 8 Mb

memory block is padded with all ones.

Decompression

The 8/16/32 Mb XCFxxP Platform Flash PROMs include a

built-in data decompressor compatible with Xilinx advanced

compression technology. Compressed Platform Flash

PROM files are created from the target FPGA bitstream(s)

using the iMPACT software. Only Slave Serial and Slave

DS123 (v2.17) October 26, 2009 www.xilinx.com

Product Specification 8

• A single 32 Mb PROM contains four 8 Mb memory

blocks, and can therefore store up to four separate

design revisions: one 32 Mb design revision, two 16 Mb

design revisions, three 8 Mb design revisions, four

8 Mb design revisions, and so on.

R

Platform Flash In-System Programmable Configuration PROMs

• Because of the 8 Mb minimum size requirement for

each revision, a single 16 Mb PROM can only store up

to two separate design revisions: one 16 Mb design

revision, one 8 Mb design revision, or two 8 Mb design

revisions.

• A single 8 Mb PROM can store only one 8 Mb design

revision.

Larger design revisions can be split over several cascaded

PROMs. For example, two 32 Mb PROMs can store up to four

separate design revisions: one 64 Mb design revision, two

32 Mb design revisions, three 16 Mb design revisions, four

16 Mb design revisions, and so on. When cascading one

16 Mb PROM and one 8 Mb PROM, there are 24 Mb of

available space, and therefore up to three separate design

revisions can be stored: one 24 Mb design revision, two 8 Mb

design revisions, or three 8 Mb design revisions.

See Figure 5 for a few basic examples of how multiple

revisions can be stored. The design revision partitioning is

handled automatically during file generation in iMPACT.

During the PROM file creation, each design revision is

assigned a revision number:

Revision 0 = '00'

Revision 1 = '01'

Revision 2 = '10'

Revision 3 = '11'

After programming the Platform Flash PROM with a set of

design revisions, a particular design revision can be

selected using the external REV_SEL[1:0] pins or using the

internal programmable design revision control bits. The

EN_EXT_SEL

pin determines if the external pins or internal

bits are used to select the design revision. When

EN_EXT_SEL

is Low, design revision selection is controlled

by the external Revision Select pins, REV_SEL[1:0]. When

EN_EXT_SEL

is High, design revision selection is

controlled by the internal programmable Revision Select

control bits. During power up, the design revision selection

inputs (pins or control bits) are sampled internally. After

power up, the design revision selection inputs are sampled

again when any of the following events occur:

• On the rising edge of CE.

• On the falling edge of OE/RESET (when CE is Low).

• On the rising edge of CF

(when CE is Low).

• When reconfiguration is initiated by using the JTAG

CONFIG instruction.

The data from the selected design revision is then

presented on the FPGA configuration interface.

DS123 (v2.17) October 26, 2009 www.xilinx.com

Product Specification 9

X-Ref Target - Figure 5

R

PROM 0 PROM 0 PROM 0 PROM 0 PROM 0

REV 0

(8 Mbits)

REV 1

(8 Mbits)

REV 2

(8 Mbits)

REV 3

(8 Mbits)

4 Design Revisions 3 Design Revisions 2 Design Revisions 1 Design Revision

(a) Design Revision storage examples for a single XCF32P PROM

PROM 0 PROM 0 PROM 0 PROM 0 PROM 0

REV 0

(16 Mbits)

REV 1

(16 Mbits)

REV 0

(8 Mbits)

REV 1

(8 Mbits)

REV 2

(16 Mbits)

REV 0

(16 Mbits)

REV 1

(16 Mbits)

Platform Flash In-System Programmable Configuration PROMs

REV 0

REV 0

(16 Mbits)

REV 1

(16 Mbits)

REV 0

(32 Mbits)

(8 Mbits)

REV 1

(24 Mbits)

REV 0

(16 Mbits)

REV 1

(16 Mbits)

REV 0

(32 Mbits)

REV 0

(32 Mbits)

PROM 1 PROM 1 PROM 1 PROM 1 PROM 1

REV 2

(16 Mbits)

REV 3

(16 Mbits)

4 Design Revisions 3 Design Revisions 2 Design Revisions 1 Design Revision

(b) Design Revision storage examples spanning two XCF32P PROMs

REV 2

(32 Mbits)

Figure 5: Design Revision Storage Examples

Initiating FPGA Configuration

The options for initiating FPGA configuration via the

Platform Flash PROM include:

• Automatic configuration on power up

• Applying an external pulse to the FPGA PROGRAM_B

pin

• Applying the JTAG CONFIG instruction to the PROM

Following the FPGA’s power-on sequence or the assertion

of the PROGRAM_B pin, the FPGA’s configuration memory

is cleared, the configuration mode is selected, and the

FPGA is ready to accept a new configuration bitstream. The

FPGA’s PROGRAM_B pin can be controlled by an external

source, or alternatively, the Platform Flash PROMs

incorporate a CF

PROGRAM_B pin. Executing the CONFIG instruction

through JTAG pulses the CF

300-500 ns, resetting the FPGA and initiating configuration.

The iMPACT software can issue the JTAG CONFIG

command to initiate FPGA configuration by setting the

“Load FPGA” option.

pin that can be tied to the FPGA’s

output Low once for

REV 1

(32 Mbits)

REV 1

(32 Mbits)

REV 0

(32 Mbits)

ds123_20_102103

When using the XCFxxP Platform Flash PROM with design

revisioning enabled, the CF

pin should always be connected

to the PROGRAM_B pin on the FPGA to ensure that the

current design revision selection is sampled when the

FPGA is reset. The XCFxxP PROM samples the current

design revision selection from the external REV_SEL pins

or the internal programmable Revision Select bits on the

rising edge of CF

. When the JTAG CONFIG command is

executed, the XCFxxP samples the new design revision

selection before initiating the FPGA configuration

sequence. When using the XCFxxP Platform Flash PROM

without design revisioning, if the CF

pin is not connected to

the FPGA PROGRAM_B pin, then the XCFxxP CF

be tied High.

pin must

DS123 (v2.17) October 26, 2009 www.xilinx.com

Product Specification 10

R

Reset and Power-On Reset Activation

Platform Flash In-System Programmable Configuration PROMs

At power up, the device requires the V

power supply to

CCINT

monotonically rise to the nominal operating voltage within

the specified V

rise time. If the power supply cannot

CCINT

meet this requirement, then the device might not perform

power-on reset properly. During the power-up sequence,

OE/RESET

is held Low by the PROM. Once the required

supplies have reached their respective POR (Power On

Reset) thresholds, the OE/RESET

release is delayed (T

OER

minimum) to allow more margin for the power supplies to

stabilize before initiating configuration. The OE/RESET

pin

is connected to an external 4.7 kΩ pull-up resistor and also

to the target FPGA's INIT pin. For systems utilizing slowrising power supplies, an additional power monitoring circuit

can be used to delay the target configuration until the

system power reaches minimum operating voltages by

holding the OE/RESET

pin Low. When OE/RESET is

released, the FPGA’s INIT pin is pulled High allowing the

FPGA's configuration sequence to begin. If the power drops

X-Ref Target - Figure 6

V

CCINT

Recommended Operating Range

below the power-down threshold (V

and OE/RESET

is again held Low until the after the POR

threshold is reached. OE/RESET

), the PROM resets

CCPD

polarity is not

programmable. These power-up requirements are shown

graphically in Figure 6.

For a fully powered Platform Flash PROM, a reset occurs

whenever OE/RESET

(High). The address counter is reset, CEO

is asserted (Low) or CE is deasserted

is driven High, and

the remaining outputs are placed in a high-impedance state.

Note:

1. The XCFxxS PROM only requires V

to rise above

CCINT

its POR threshold before releasing OE/RESET

2. The XCFxxP PROM requires both V

POR threshold and for V

to reach the recommended

CCO

to rise above its

CCINT

operating voltage level before releasing OE/RESET

.

.

Delay or Restart

200 µs ramp

V

CCPOR

V

CCPD

T

OER

Figure 6: Platform Flash PROM Power-Up Requirements

Configuration

T

OER

A slow-ramping V

be below the minimum operating

voltage when OE/RESET is released.

In this case, the configuration

sequence must be delayed until both

and V

V

CCINT

recommended operating conditions.

I/O Input Voltage Tolerance and Power Sequencing

The I/Os on each re-programmable Platform Flash PROM

are fully 3.3V-tolerant. This allows 3V CMOS signals to

connect directly to the inputs without damage. The core

power supply (V

output power supply (V

signals can be applied in any order.

Additionally, for the XCFxxS PROM only, when V

supplied at 2.5V or 3.3V and V

I/Os are 5V-tolerant. This allows 5V CMOS signals to

connect directly to the inputs on a powered XCFxxS PROM

without damage. Failure to power the PROM correctly while

supplying a 5V input signal can result in damage to the

XCFxxS device.

), JTAG pin power supply (V

CCINT

), and external 3V CMOS I/O

CCO

is supplied at 3.3V, the

CCINT

CCJ

CCO

),

is

50 ms ramp

supply may still

CCINT

have reached their

CCO

TIME (ms)

T

RST

ds123_21_103103

DS123 (v2.17) October 26, 2009 www.xilinx.com

Product Specification 11

Loading...

Loading...