TMS320VC33

DIGITAL SIGNAL PROCESSOR

SPRS087A – FEBRUARY 1999 – REVISED DECEMBER 1999

1

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

D High-Performance Floating-Point Digital

Signal Processor (DSP):

– TMS320VC33-150

13-ns Instruction Cycle Time

150 MFLOPS, 75 MIPS

– TMS320VC33-120

17-ns Instruction Cycle Time

120 MFLOPS, 60 MIPS

D 34K × 32-Bit (1.1-Mbit) On-Chip Words of

Dual Access SRAM Configured in 2 × 16K

plus 2 × 1K Blocks to improve Internal

Performance

D x5 PLL Clock Generator

D Very Low Power: < 200 mW @ 150 MFLOPS

D 32-Bit High-Performance CPU

D 16-/32-Bit Integer and 32-/40-Bit

Floating-Point Operations

D Four Internally Decoded Page Strobes to

Simplify Interface to I/O and Memory

Devices

D 32-Bit Instruction Word, 24-Bit Addresses

D EDGEMODE Selectable External Interrupts

D Boot-Program Loader

D On-Chip Memory-Mapped Peripherals:

– One Serial Port

– Two 32-Bit Timers

– Direct Memory Access (DMA)

Coprocessor for Concurrent I/O and CPU

Operation

D Fabricated Using the 0.18-Micron

(l

eff

-effective gate length) TImeline

Technology by Texas Instruments (TI)

D 144-Pin Thin Quad Flat Pack (TQFP)

(PGE Suffix)

D Eight Extended-Precision Registers

D T wo Address Generators With Eight

Auxiliary Registers and Two Auxiliary

Register Arithmetic Units (ARAUs)

D Two Low-Power Modes

D Two- and Three-Operand Instructions

D Parallel Arithmetic/Logic Unit (ALU) and

Multiplier Execution in a Single Cycle

D Block-Repeat Capability

D Zero-Overhead Loops With Single-Cycle

Branches

D Conditional Calls and Returns

D Interlocked Instructions for

Multiprocessing Support

D Bus-Control Registers Configure

Strobe-Control Wait-State Generation

D 1.8-V (Core) and 3.3-V (I/O) Supply Voltages

D On-Chip Scan-Based Emulation Logic,

IEEE Std 1149.1† (JTAG)

description

The TMS320VC33 DSP is a 32-bit, floating-point processor manufactured in 0.18-micron four-level-metal

CMOS (TImeline) technology. The TMS320VC33 is part of the TMS320C3x generation of DSPs from Texas

Instruments.

The TMS320C3x’s internal busing and special digital-signal-processing instruction set have the speed and

flexibility to execute up to 150 million floating-point operations per second (MFLOPS). The TMS320C3x

optimizes speed by implementing functions in hardware that other processors implement through software or

microcode. This hardware-intensive approach provides performance previously unavailable on a single chip.

The TMS320C3x can perform parallel multiply and ALU operations on integer or floating-point data in a single

cycle. Each processor also possesses a general-purpose register file, a program cache, dedicated ARAUs,

internal dual-access memories, one DMA channel supporting concurrent I/O, and a short machine-cycle time.

High performance and ease of use are results of these features.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PR

O

DU

C

T PREVIEW

PRODUCT PREVIEW information concerns products in the formative or

design phase of development. Characteristic data and other

specifications are design goals. Texas Instruments reserves the right to

change or discontinue these products without notice.

TImeline and TI are trademarks of Texas Instruments Incorporated.

Copyright 1999, Texas Instruments Incorporated

†

IEEE Standard 1149.1-1990 Standard-Test-Access Port and Boundary Scan Architecture.

TMS320VC33

DIGITAL SIGNAL PROCESSOR

SPRS087A – FEBRUARY 1999 – REVISED DECEMBER 1999

2

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

description (continued)

General-purpose applications are greatly enhanced by the large address space, multiprocessor interface,

internally and externally generated wait states, one external interface port, two timers, one serial port, and

multiple-interrupt structure. The TMS320C3x supports a wide variety of system applications from host

processor to dedicated coprocessor. High-level-language support is easily implemented through a

register-based architecture, large address space, powerful addressing modes, flexible instruction set, and

well-supported floating-point arithmetic.

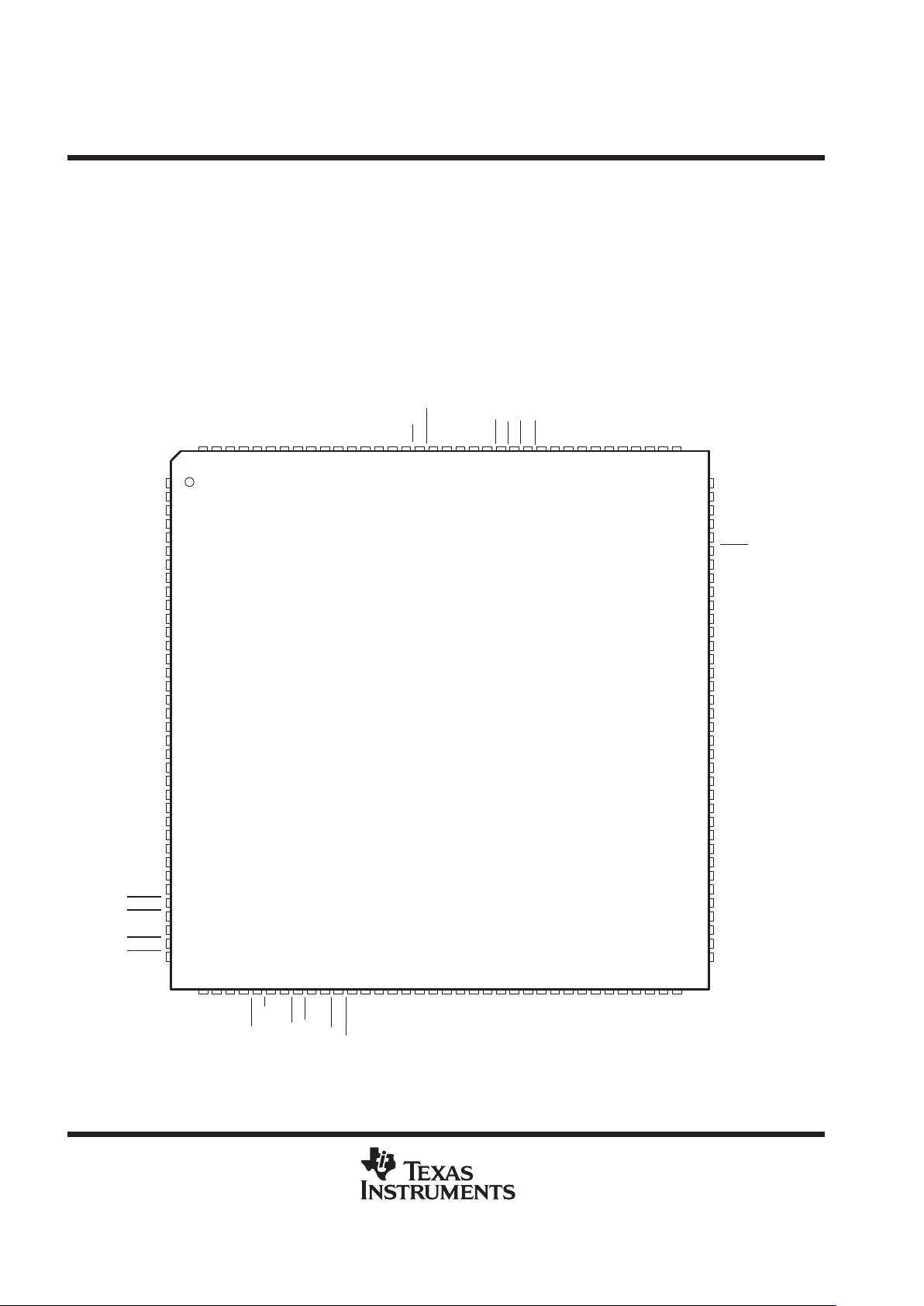

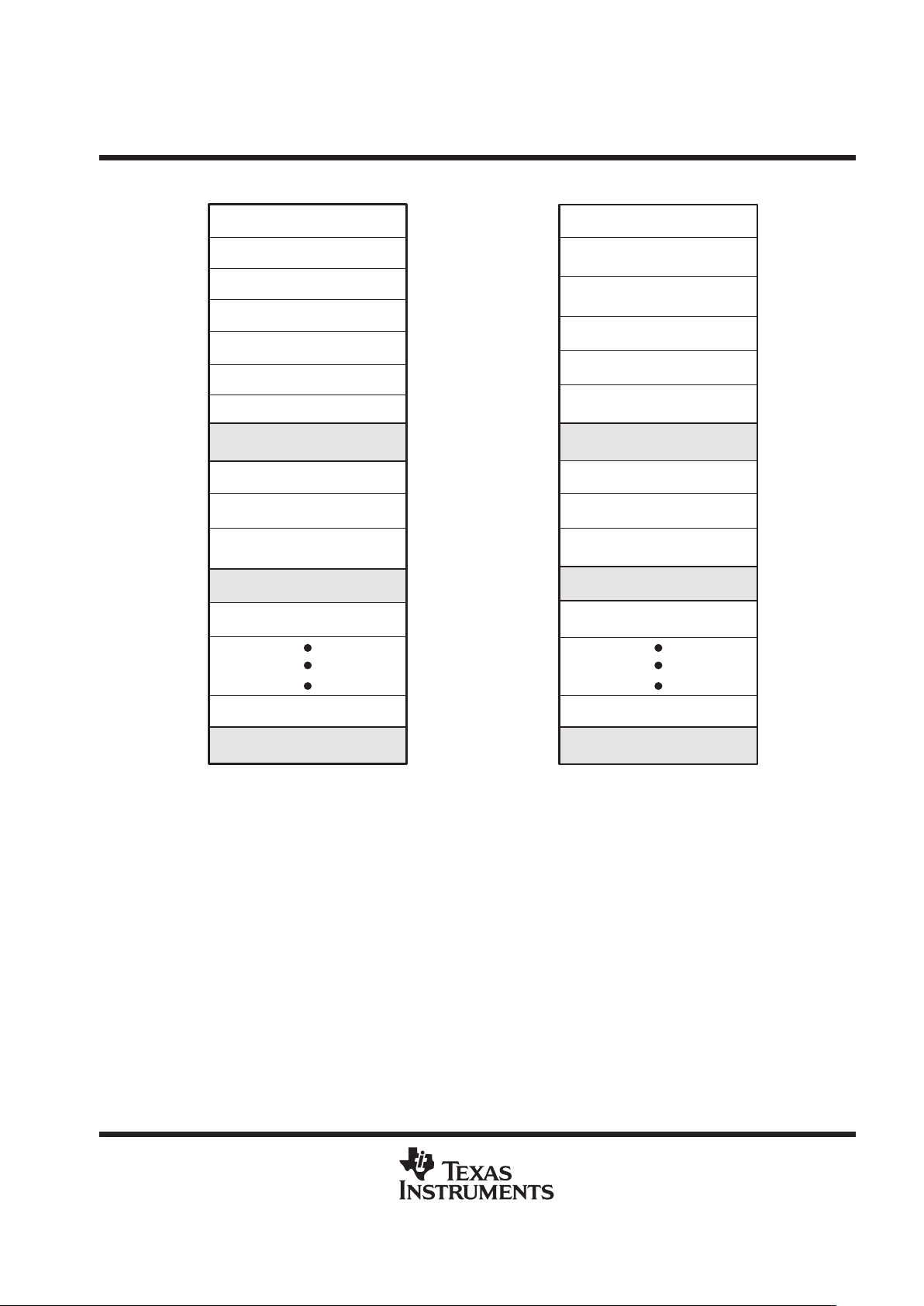

TMS320VC33 pinout (top view)

MCBL/MP

RESET

DV

DD

CLKR0

FSR0

V

SS

DR0

TRST

TMS

CV

DD

TDI

TDO

TCK

V

SS

EMU0

EMU1

DV

DD

D0

D1

D2

D3

V

SS

D4

D5

DV

DD

D6

D7

CV

DD

D8

D9

V

SS

D10

D11

DV

DD

D12

D13

D14

D15

A20

V

SS

A19

A18

A17

DV

DD

A16

A15

V

SS

A14

A13

CV

DD

A12

A11

DV

DD

A10

A9

V

SS

A8

A7

A6

A5

DV

DD

A4

V

SS

A3

A2

CV

DD

A1

A0

DV

DD

PAGE3

PAGE2

V

SS

PAGE1

PAGE0

144

A22

143

142

141

140

RSV0

139

RSV1

138

137

CLKMD0

136

CLKMD1

135

134

XIN

133

XOUT

132

131

EXTCLK

130

129

128

127

126

125

EDGEMODE

124

123

INT0

122

INT1

121

INT2

120

INT3

119

118

117

XF1

116

115

TCLK0

114

TCLK1

113

112

373839404142434445464748495051525354555657585960616263646566676869

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

H1

H3

STRB

R/W

IACK

RDY

HOLD

HOLDA

D25

D24

D23

D22

D21

D20

D19

D17

D27

D30

111

DX0

110

CLKX0

109

707172

D16

XF0

FSX0

DD

DV

SHZ

TMS320VC33 PGE PACKAGE

†‡

(TOP VIEW)

A23

D28

A21

DD

DV

DD

DV

DD

PLLV

DD

DV

DD

DV

DD

DV

DD

DV

DD

CV

DD

CV

DD

CV

DD

CV

D31

SS

V

SS

V

SS

PLLV

SS

V

SS

V

SS

V

SS

V

D29

D26

D18

DD

DV

SS

V

SS

V

SS

V

†

DVDD is the power supply for the I/O pins while CVDD is the power supply for the core CPU. VSS is the ground for both the I/O

pins and the core CPU.

‡

PLLVDD and PLLVSS are isolated PLL supply pins that should be externally connected to CVDD and V

SS,

respectively.

The TMS320VC33 device is packaged in 144-pin thin quad flatpacks (PGE Suffix).

PR

O

DU

C

T PREVIEW

TMS320VC33

DIGITAL SIGNAL PROCESSOR

SPRS087A – FEBRUARY 1999 – REVISED DECEMBER 1999

3

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

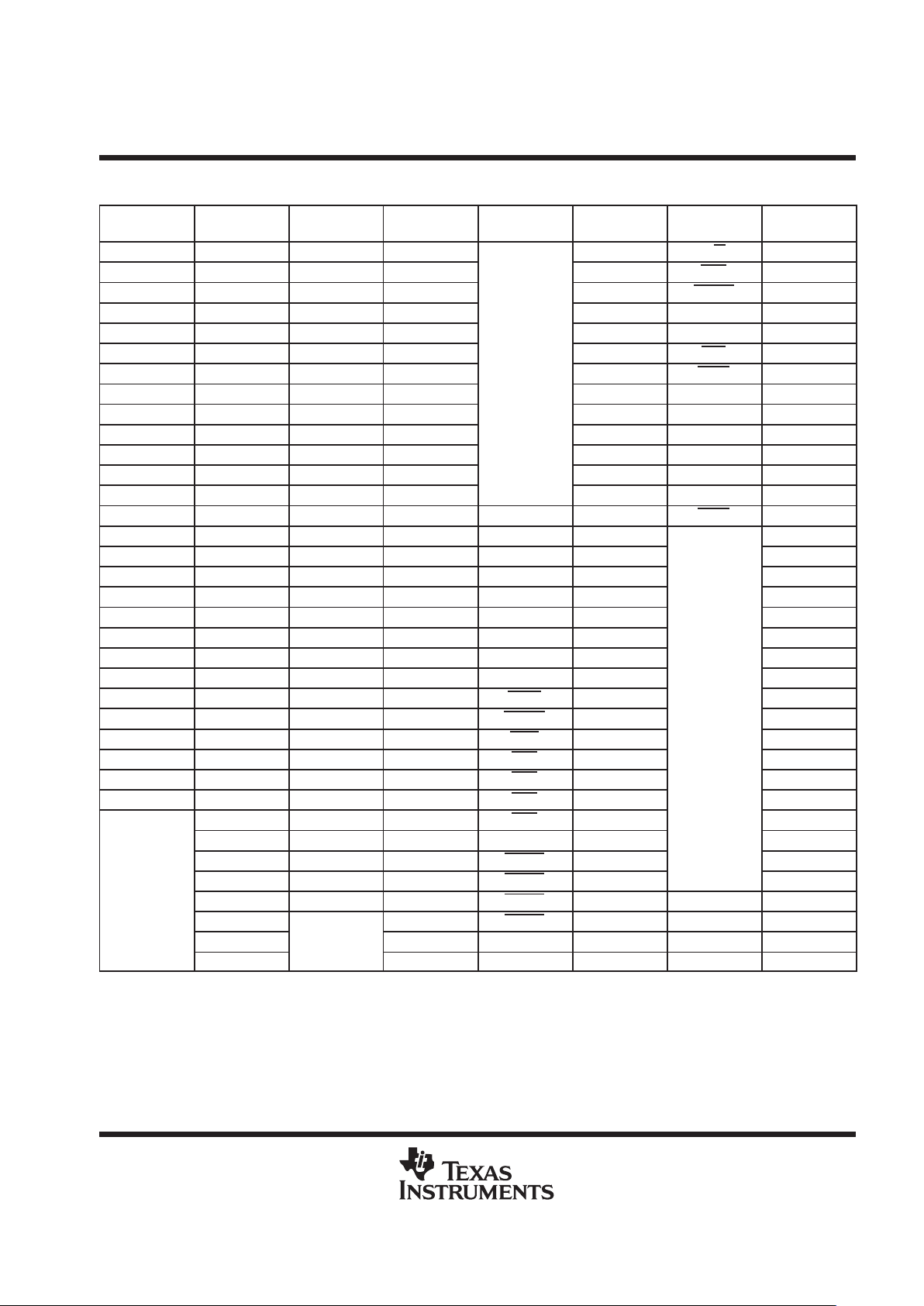

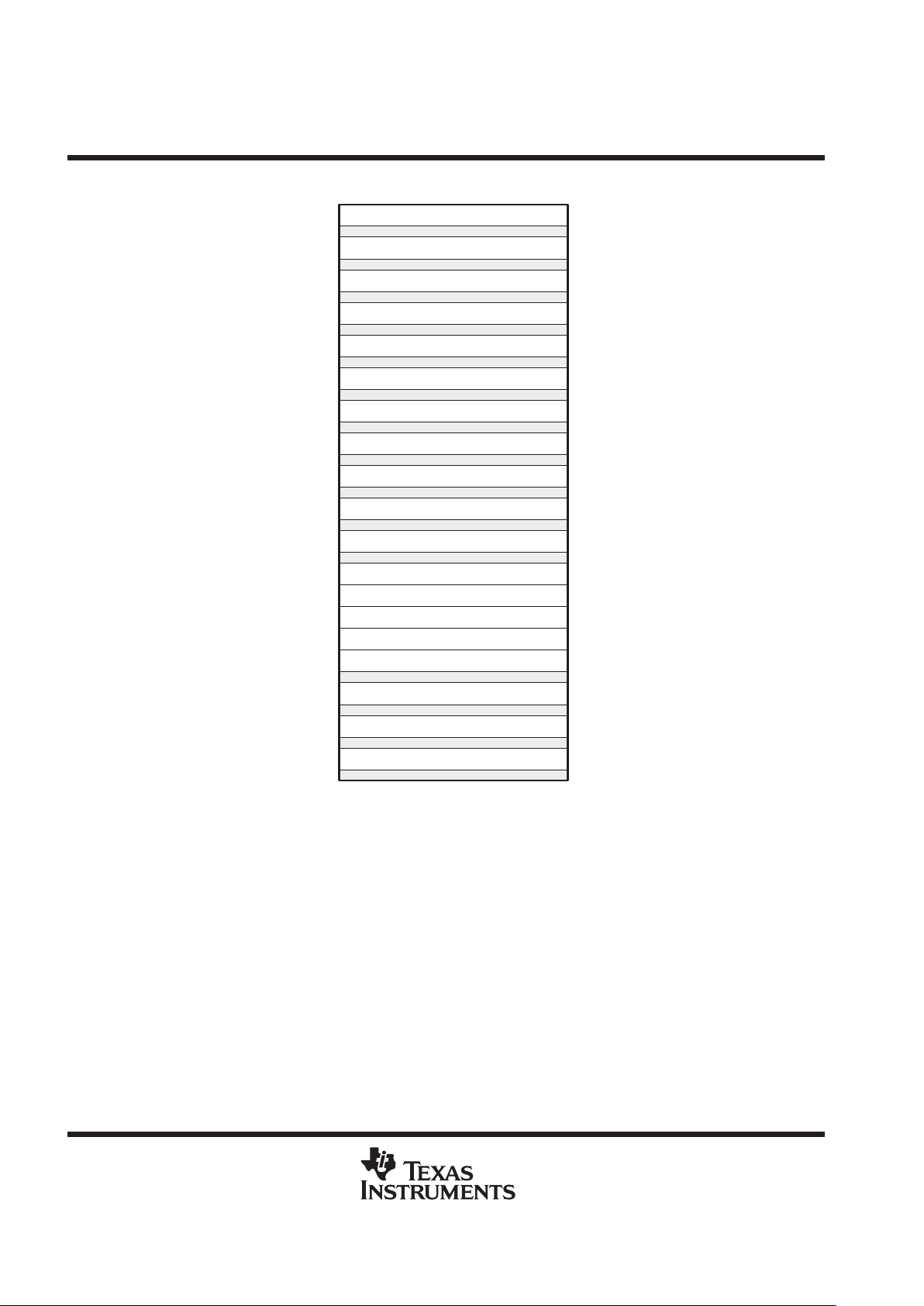

TMS320VC33 Terminal Assignments (Alphabetical)

SIGNAL

NAME

PIN

NUMBER

SIGNAL

NAME

PIN

NUMBER

SIGNAL

NAME

PIN

NUMBER

SIGNAL

NAME

PIN

NUMBER#

A0 30 D0 93 31 R/W 42

A1 29 D1 92 37 RDY 45

A2 27 D2 91 43 RESET 127

A3 26 D3 90 53 RSV0 139

A4 24 D4 88 60 RSV1 138

A5 22 D5 87 69 SHZ 128

A6 21 D6 85

DV

DD

†

77 STRB 41

A7 20 D7 84

DV

DD

†

86 TCK 98

A8 19 D8 82 94 TCLK0 114

A9 17 D9 81 108 TCLK1 113

A10 16 D10 79 115 TDI 100

A11 14 D11 78 129 TDO 99

A12 13 D12 76 143 TMS 102

A13 11 D13 75 DX0 111 TRST 103

A14 10 D14 74 EDGEMODE 124 2

A15 8 D15 73 EMU0 96 9

A16 7 D16 71 EMU1 95 18

A17 5 D17 70 EXTCLK 130 25

A18 4 D18 68 FSR0 106 34

A19 3 D19 67 FSX0 110 40

A20 1 D20 65 H1 38 49

A21 144 D21 64 H3 39 56

A22 142 D22 62 HOLD 47

63

A23 141 D23 61 HOLDA 48

V

SS

72

CLKMD0 136 D24 59 IACK 44 80

CLKMD1 135 D25 58 INT0 122 89

CLKR0 107 D26 57 INT1 121 97

CLKX0 109 D27 55 INT2 120 105

12 D28 54 INT3 119 112

28 D29 52 MCBL/MP 125 118

46 D30 51 PAGE0 36 126

66 D31 50 PAGE1 35 140

CV

DD

83 DR0 104 PAGE2 33 XIN 133

101 6 PAGE3 32 XOUT 132

123

DV

DD

15 PLLV

DD

‡

131 XF0 117

137

DV

DD

23 PLLV

SS

‡

134 XF1 116

†

DVDD is the power supply for the I/O pins while CVDD is the power supply for the core CPU. VSS is the ground for both the I/O pins and the core

CPU.

‡

PLLVDD and PLLVSS are isolated PLL supply pins that should be externally connected to CVDD and VSS respectively.

PR

O

DU

C

T PREVIEW

TMS320VC33

DIGITAL SIGNAL PROCESSOR

SPRS087A – FEBRUARY 1999 – REVISED DECEMBER 1999

4

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

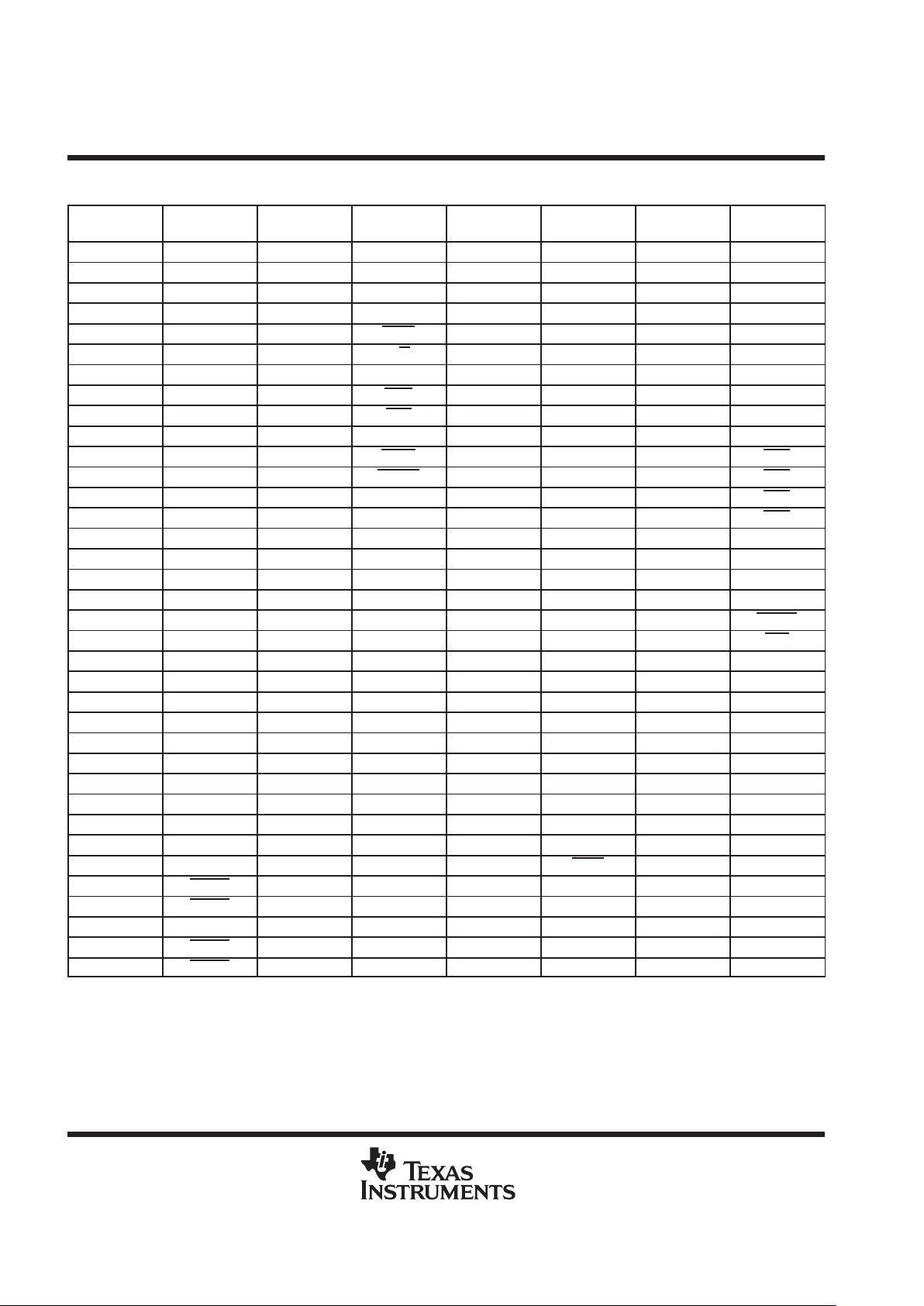

TMS320VC33 Terminal Assignments† (Numerical)

PIN

NUMBER

SIGNAL

NAME

PIN

NUMBER

SIGNAL

NAME

PIN

NUMBER

SIGNAL

NAME

PIN

NUMBER

SIGNAL

NAME

1 A20 37 DV

DD

73 D15 109 CLKX0

2 V

SS

38 H1 74 D14 110 FSX0

3 A19 39 H3 75 D13 111 DX0

4 A18 40 V

SS

76 D12 112 V

SS

5 A17 41 STRB 77 DV

DD

113 TCLK1

6 DV

DD

42 R/W 78 D11 114 TCLK0

7 A16 43 DV

DD

79 D10 115 DV

DD

8 A15 44 IACK 80 V

SS

116 XF1

9 V

SS

45 RDY 81 D9 117 XF0

10 A14 46 CV

DD

82 D8 118 V

SS

11 A13 47 HOLD 83 CV

DD

119 INT3

12 CV

DD

48 HOLDA 84 D7 120 INT2

13 A12 49 V

SS

85 D6 121 INT1

14 A11 50 D31 86 DV

DD

122 INT0

15 DV

DD

51 D30 87 D5 123 CV

DD

16 A10 52 D29 88 D4 124 EDGEMODE

17 A9 53 DV

DD

89 V

SS

125 MCBL/MP

18 V

SS

54 D28 90 D3 126 V

SS

19 A8 55 D27 91 D2 127 RESET

20 A7 56 V

SS

92 D1 128 SHZ

21 A6 57 D26 93 D0 129 DV

DD

22 A5 58 D25 94 DV

DD

130 EXTCLK

23 DV

DD

59 D24 95 EMU1 131 PLLV

DD

‡

24 A4 60 DV

DD

96 EMU0 132 XOUT

25 V

SS

61 D23 97 V

SS

133 XIN

26 A3 62 D22 98 TCK 134 PLLV

SS

‡

27 A2 63 V

SS

99 TDO 135 CLKMD1

28 CV

DD

64 D21 100 TDI 136 CLKMD0

29 A1 65 D20 101 CV

DD

137 CV

DD

30 A0 66 CV

DD

102 TMS 138 RSV1

31 DV

DD

67 D19 103 TRST 139 RSV0

32 PAGE3 68 D18 104 DR0 140 V

SS

33 PAGE2 69 DV

DD

105 V

SS

141 A23

34 V

SS

70 D17 106 FSR0 142 A22

35 PAGE1 71 D16 107 CLKR0 143 DV

DD

36 PAGE0 72 V

SS

108 DV

DD

144 A21

†

DVDD is the power supply for the I/O pins while CVDD is the power supply for the core CPU. VSS is the ground for both the I/O pins and the core

CPU.

‡

PLLVDD and PLLVSS are isolated PLL supply pins that should be externally connected to CVDD and VSS respectively.

PR

O

DU

C

T PREVIEW

TMS320VC33

DIGITAL SIGNAL PROCESSOR

SPRS087A – FEBRUARY 1999 – REVISED DECEMBER 1999

5

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

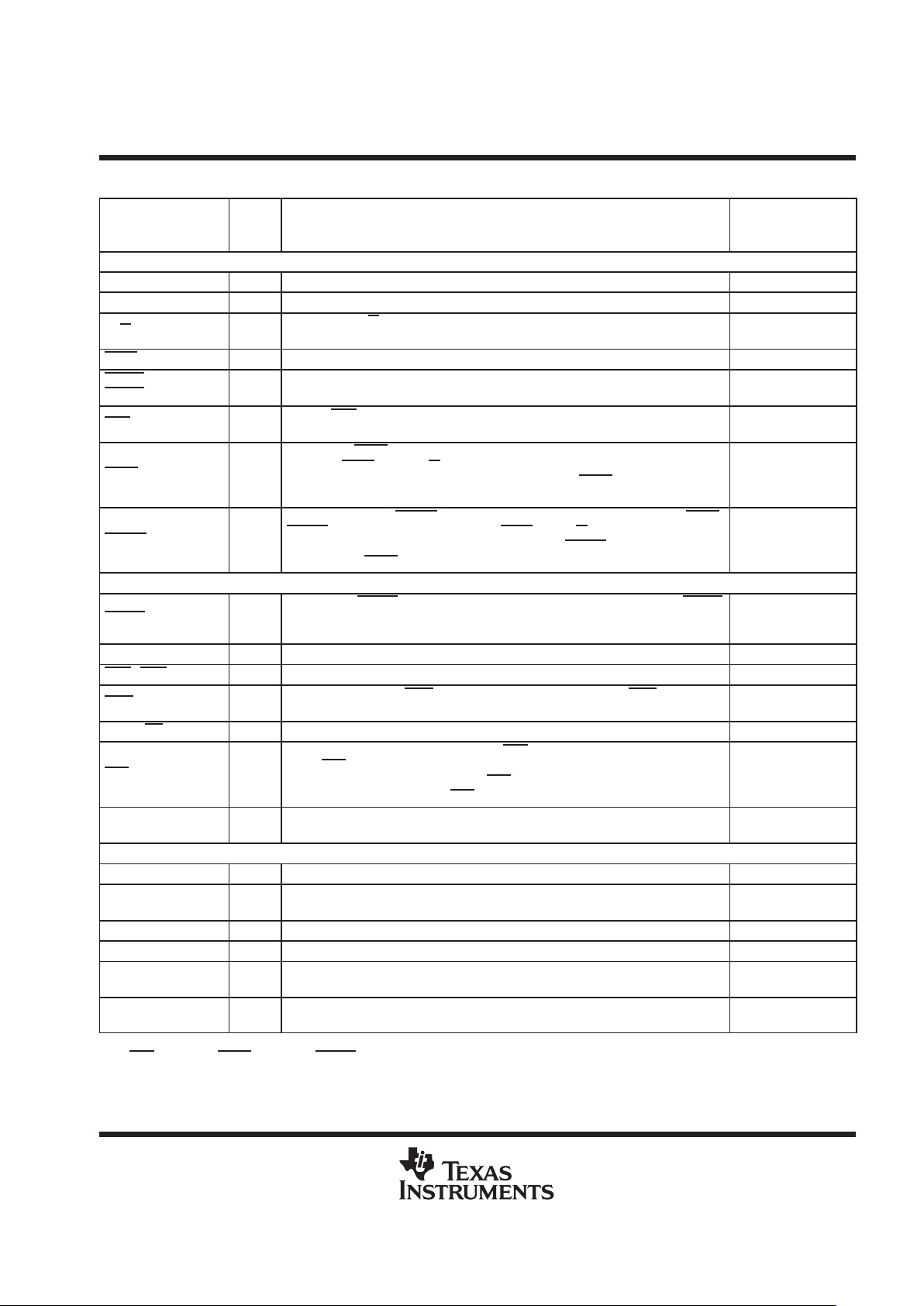

TMS320VC33 Terminal Functions

TERMINAL

CONDITIONS

NAME QTY

TYPE

†

DESCRIPTION

WHEN

SIGNAL IS Z TYPE

‡

PRIMARY-BUS INTERFACE

D31–D0 32 I/O/Z 32-bit data port S H R

A23–A0 24 O/Z 24-bit address port S H R

R/W 1 O/Z

Read/write. R/W is high when a read is performed and low when a write is performed

over the parallel interface.

S H R

STRB 1 O/Z Strobe. For all external-accesses S H

PAGE0 –

PAGE3

1 O/Z Page strobes. Four decoded page strobes for external access S H

RDY 1 I

Ready. RDY indicates that the external device is prepared for a transaction

completion.

HOLD 1 I

Hold. When HOLD is a logic low, any ongoing transaction is completed. A23 –A0,

D31–D0, STRB

, and R/W are placed in the high-impedance state and all

transactions over the primary-bus interface are held until HOLD

becomes a logic high

or until the NOHOLD bit of the primary-bus-control register is set.

HOLDA 1 O/Z

Hold acknowledge. HOLDA is generated in response to a logic low on HOLD.

HOLDA

indicates that A23–A0, D31–D0, STRB, and R/W are in the high-impedance

state and that all transactions over the bus are held. HOLDA

is high in response to

a logic high of HOLD

or the NOHOLD bit of the primary-bus-control register is set.

S

CONTROL SIGNALS

RESET 1 I

Reset. When RESET is a logic low, the device is in the reset condition. When RESET

becomes a logic high, execution begins from the location specified by the reset vec-

tor.

EDGEMODE 1 I Edge mode. Enables interrupt edge mode detection.

INT3–INT0 4 I External interrupts

IACK 1 O/Z

Internal acknowledge. IACK is generated by the IACK instruction. IACK can be used

to indicate when a section of code is being executed.

S

MCBL/MP 1 I Microcomputer Bootloader/microprocessor mode-select

SHZ 1 I

Shutdown high impedance. When active, SHZ places all pins in the high-impedance

state. SHZ

can be used for board-level testing or to ensure that no dual-drive

conditions occur. CAUTION: A low on SHZ

corrupts the device memory and register

contents. Reset the device with SHZ

high to restore it to a known operating condition.

XF1, XF0 2 I/O/Z

External flags. XF1 and XF0 are used as general-purpose I/Os or to support

interlocked processor instruction.

S R

SERIAL PORT 0 SIGNALS

CLKR0 1 I/O/Z Serial port 0 receive clock. CLKR0 is the serial shift clock for the serial port 0 receiver. S R

CLKX0 1 I/O/Z

Serial port 0 transmit clock. CLKX0 is the serial shift clock for the serial port 0

transmitter.

S R

DR0 1 I/O/Z Data-receive. Serial port 0 receives serial data on DR0. S R

DX0 1 I/O/Z Data-transmit output. Serial port 0 transmits serial data on DX0. S R

FSR0 1 I/O/Z

Frame-synchronization pulse for receive. The FSR0 pulse initiates the data-receive

process using DR0.

S R

FSX0 1 I/O/Z

Frame-synchronization pulse for transmit. The FSX0 pulse initiates the data-transmit

process using DX0.

S R

†

I = input, O = output, Z = high-impedance state

‡

S = SHZ

active, H = HOLD active, R = RESET active

§

Recommended decoupling. Four 0.1 µF for V

DDL

and eight 0.1 µF for V

DDP

.

PR

O

DU

C

T PREVIEW

TMS320VC33

DIGITAL SIGNAL PROCESSOR

SPRS087A – FEBRUARY 1999 – REVISED DECEMBER 1999

6

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

TMS320VC33 Terminal Functions (Continued)

TERMINAL

CONDITIONS

NAME QTY

TYPE

†

DESCRIPTION

WHEN

SIGNAL IS Z TYPE

‡

TIMER SIGNALS

TCLK0 1 I/O/Z

Timer clock 0. As an input, TCLK0 is used by timer 0 to count external pulses. As

an output, TCLK0 outputs pulses generated by timer 0.

S R

TCLK1 1 I/O/Z

Timer clock 1. As an input, TCLK0 is used by timer 1 to count external pulses. As

an output, TCLK1 outputs pulses generated by timer 1.

S R

SUPPLY AND OSCILLATOR SIGNALS

H1 1 O/Z External H1 clock S

H3 1 O/Z External H3 clock S

CV

DD

10 I

+VDD. Dedicated 1.8-V power supply for the core CPU. All must be connected to

a common supply plane.

§

DV

DD

10 I

+VDD. Dedicated 3.3-V power supply for the I/O pins. All must be connected to a

common supply plane.

§

V

SS

24 I Ground. All grounds must be connected to a common ground plane.

PLLV

DD

1 I Internally isolated PLL supply. Connect to CVDD (1.8 V)

PLLV

SS

1 I Internally isolated PLL ground. Connect to V

SS

EXTCLK 1 I

External clock. Logic level compatible clock input. If an oscillator is used, tie this pin

to ground.

XOUT 1 O

Clock out. Output from the internal-crystal oscillator. If a crystal is not used, X1

should be left unconnected.

XIN 1 I

Clock in. Internal-oscillator input from a crystal. If EXTCLK is used, tie this pin to

ground.

RSV0 – RSV1 2 I Reserved. Use individual pullups to DVDD.

JTAG EMULATION

EMU1–EMU0 2 I Emulation pins 0 and 1

TDI 1 I Test data input

TDO 1 O Test data output

TCK 1 I Test clock

TMS 1 I Test mode select

TRST 1 I Test reset

†

I = input, O = output, Z = high-impedance state

‡

S = SHZ

active, H = HOLD active, R = RESET active

§

Recommended decoupling. Four 0.1 µF for V

DDL

and eight 0.1 µF for V

DDP

.

PR

O

DU

C

T PREVIEW

TMS320VC33

DIGITAL SIGNAL PROCESSOR

SPRS087A – FEBRUARY 1999 – REVISED DECEMBER 1999

7

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

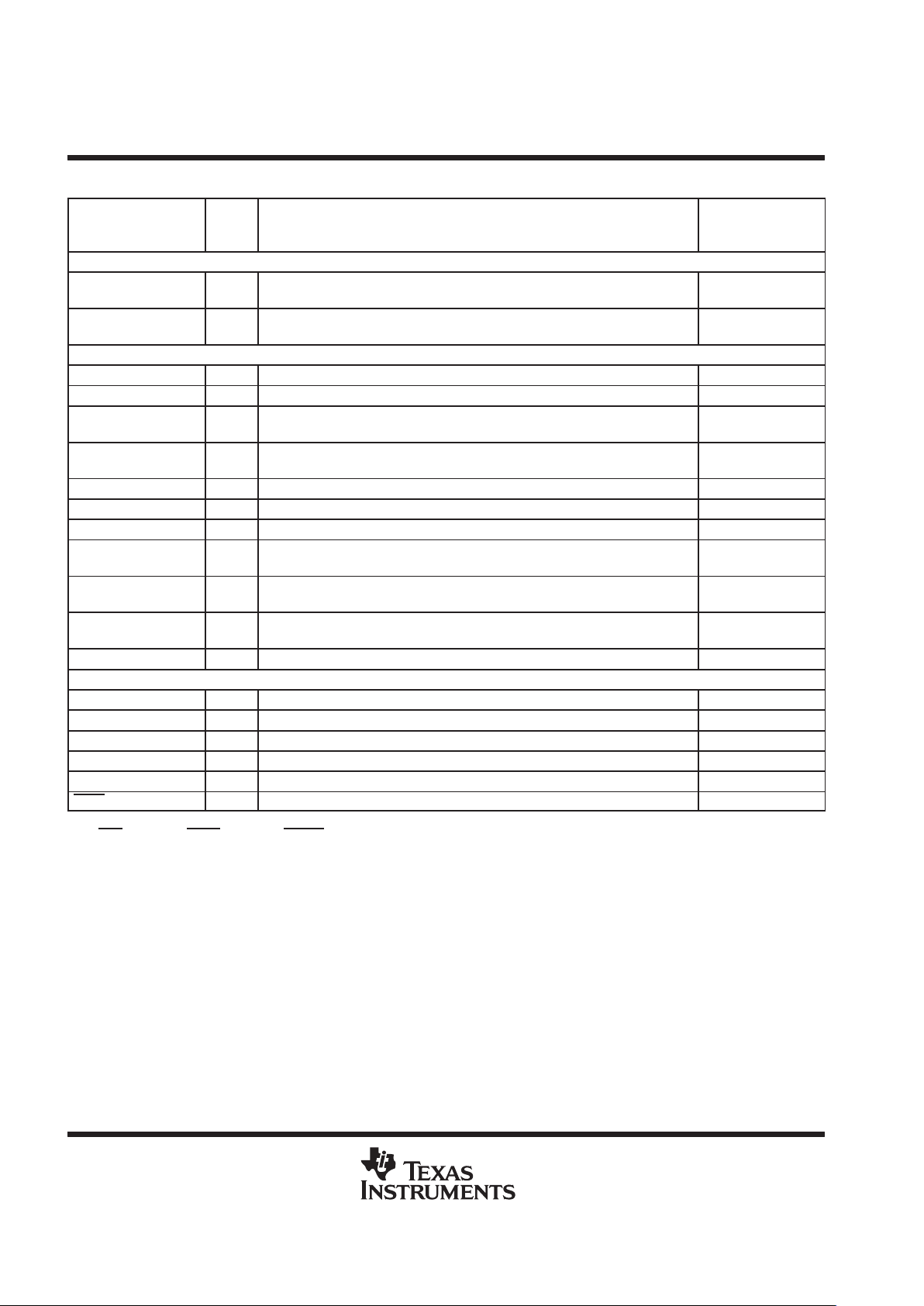

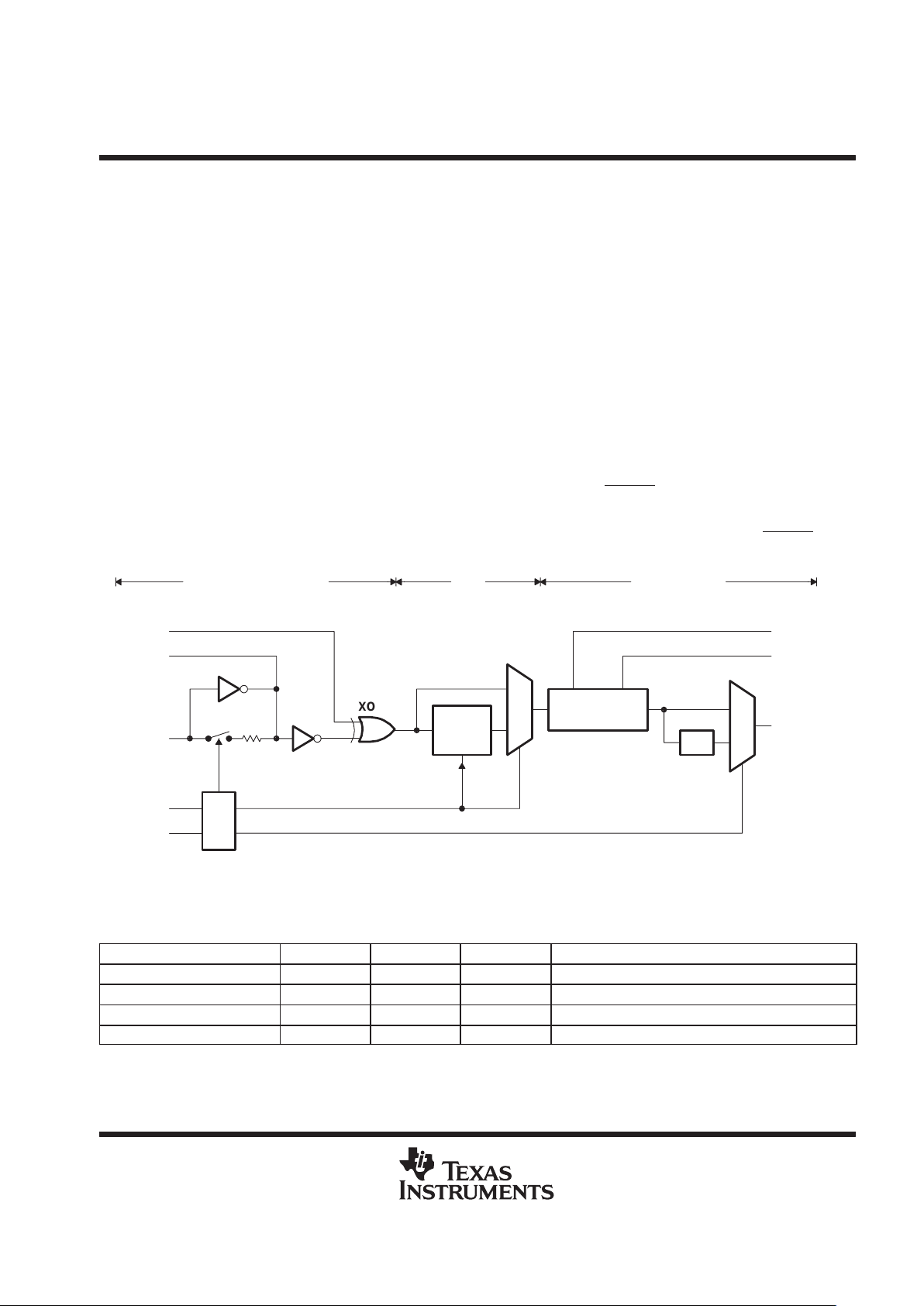

functional block diagram

24

ÉÉÉ

Boot

Loader

Cache

(64

× 32)

RAM

Block 0

(1K

× 32)

RAM

Block 1

(1K

× 32)

RDY

HOLD

HOLDA

STRB

R/W

D31–D0

A23–A0

RESET

CPU1

REG1

REG2

MUX

40

32

32

32

32

32

32

32

24

24

24

24

BK

ARAU0 ARAU1

DISP0, IR0, IR1

Extended-

Precision

Registers

(R7–R0)

Auxiliary

Registers

(AR0–AR7)

Other

Registers

(12)

40

40

40

40

Multiplier

32-Bit

Barrel

Shifter

ALU

DMA Controller

Global-Control

Register

Source-Address

Register

Destination-

Address

Register

Serial Port 0

Serial-Port-Control

Register

Receive/Transmit

(R/X) Timer Register

Data-Transmit

Register

Data-Receive

Register

FSX0

DX0

CLKX0

FSR0

DR0

CLKR0

Timer 0

Global-Control

Register

Timer-Period

Register

Timer-Counter

Register

TCLK0

Timer 1

Global-Control

Register

Timer-Period

Register

Timer-Counter

Register

TCLK1

Port Control

STRB

-Control

Register

Transfer-

Counter

Register

PDATA Bus

PADDR Bus

DDATA Bus

DADDR1 Bus

DADDR2 Bus

DMADATA Bus

DMAADDR Bus

24

40

32

32

24

24

32

INT(3–0)

IACK

MCBL/MP

XF(1,0)

32 24 24

24 2432 32 32

CPU2

32 32 40 40

Peripheral Data Bus

CPU1

REG1

REG2

RAM

Block 2

(16K

× 32)

24

32

RAM

Block 3

(16K

× 32)

24

32

MUX

Peripheral Address Bus

XOUT

XIN

H1

H3

PAGE_0

PAGE_1

PAGE_2

PAGE_3

Peripheral Data Bus

TDI

TDO

TCK

EMU0

EMU1

TMS

TRST

MUX

EDGEMODE

ControllerPLL CLK

JTAG Emulation

IR

PC

PR

O

DU

C

T PREVIEW

TMS320VC33

DIGITAL SIGNAL PROCESSOR

SPRS087A – FEBRUARY 1999 – REVISED DECEMBER 1999

8

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

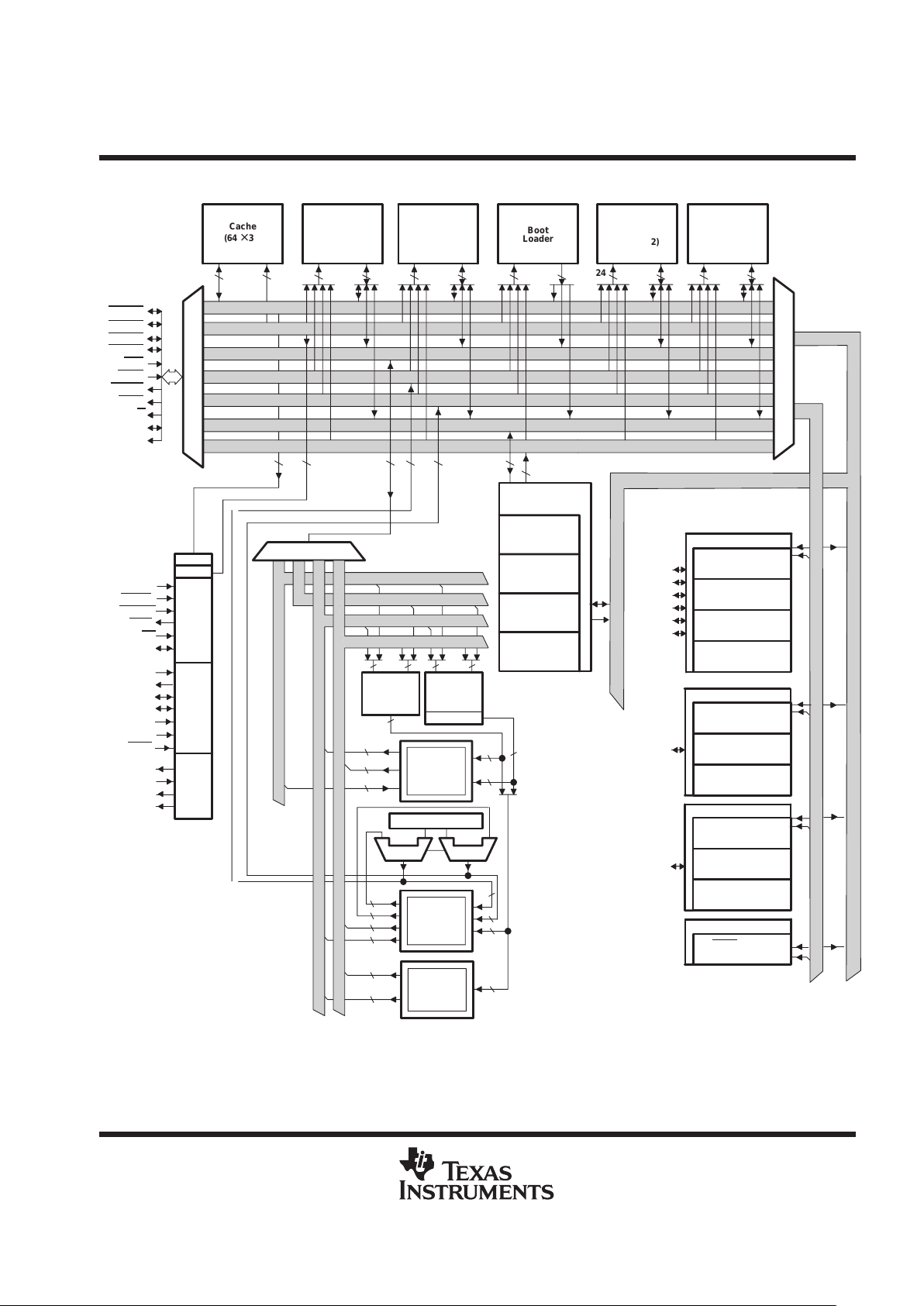

memory map

Peripheral Bus

Memory-Mapped Registers

(6K Words Internal)

Reset, Interrupt, Trap V ector, and

Reserved Locations (64)

(External STRB

Active)

0h

03Fh

040h

External

STRB

Active

(8M Words – 64 Words)

7FFFFFh

800000h

807FFFh

808000h

8097FFh

RAM Block 0

(1K Words Internal)

809800h

809BFFh

809C00h

809FFFh

80A000h

External

STRB

Active

(8M Words – 40K Words)

FFFFFFh

0h

FFFh

1000h

7FFFFFh

800000h

807FFFh

Peripheral Bus

Memory-Mapped Registers

(6K Words Internal)

808000h

8097FFh

RAM Block 0

(1K Words Internal)

809800h

809BFFh

809C00h

809FFFh

80A000h

External

STRB

Active

(8M Words –

40K Words)

FFFFFFh

Boot 1

Boot 2

400000h

RAM Block 1

(1K Words – 63 Words Internal)

809FC0h

809FC1h

User-Program Interrupt

and Trap Branches

(63 Words Internal)

Boot 3

FFF000h

External

STRB

Active

(8M Words –

4K Words)

Reserved for Bootloader

Operations

(a) Microprocessor Mode

(b) Microcomputer/Bootloader Mode

RAM Block 1

(1K Words Internal)

RAM Block 3

(16K Words Internal)

RAM Block 2

(16K Words Internal)

RAM Block 3

(16K Words Internal)

RAM Block 2

(16K Words Internal)

803FFFh

804000h

803FFFh

804000h

NOTE A: STRB is active over all external memory ranges. PAGE_0 to PAGE_3 are configured as external bus strobes. These are simple

decoded strobes that have no configuration registers and are active only during external bus activity over the following ranges:

Name Active range

PAGE_0

0000000h – 03FFFFFh

PAGE_1

0400000h – 07FFFFFh

PAGE_2

0800000h – 0BFFFFFh

PAGE_3

0C00000h – 0FFFFFFh

STRB

0000000h – 0FFFFFFh

Figure 1. TMS320C33 Memory Maps

PR

O

DU

C

T PREVIEW

TMS320VC33

DIGITAL SIGNAL PROCESSOR

SPRS087A – FEBRUARY 1999 – REVISED DECEMBER 1999

9

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

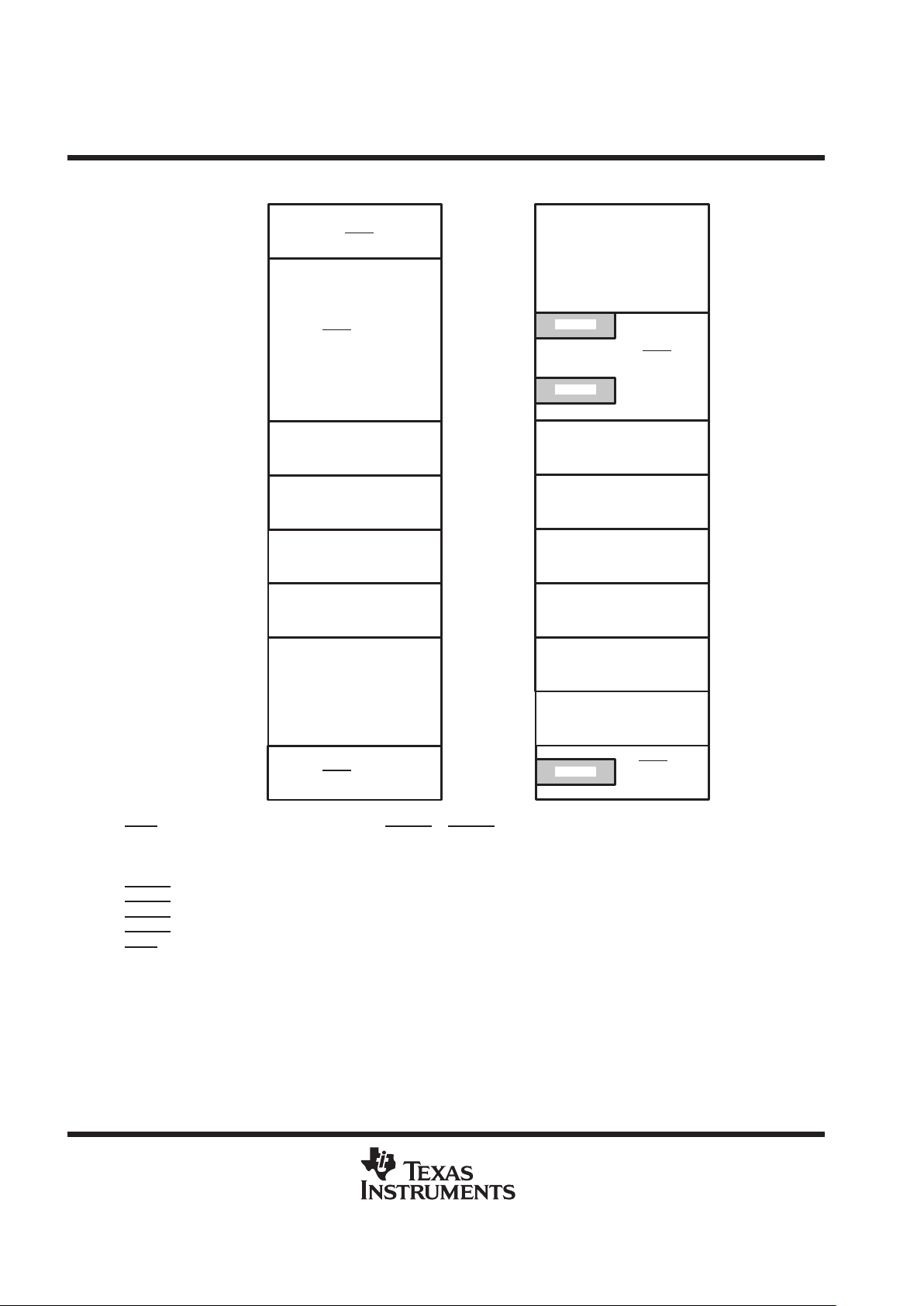

memory map (continued)

Reset

00h

INT0

809FC1h

INT1

01h

INT1

809FC2h

INT2

02h

INT2

809FC3h

INT3

03h

INT3

809FC4h

XINT0

04h

XINT0

809FC5h

RINT0

06h

RINT0

809FC6h

07h

809FC7h

809FC8h

08h

TINT0

09h

809FC9h

TINT1

0Ah

809FCAh

DINT

0Bh

809FCBh

0Ch

809FDFh

1Fh

809FCCh

TRAP 020h

809FE0h

TRAP 273Bh 809FFBh

3Ch

809FFFh

3Fh

809FFCh

(a) Microprocessor Mode (b) Microcomputer/Bootloader Mode

INT0

05h

TINT0

TRAP 27

TRAP 0

DINT

TINT1

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Figure 2. Reset, Interrupt, and Trap Vector/Branches Memory-Map Locations

PR

O

DU

C

T PREVIEW

TMS320VC33

DIGITAL SIGNAL PROCESSOR

SPRS087A – FEBRUARY 1999 – REVISED DECEMBER 1999

10

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

memory map (continued)

FSX/DX/CLKX Serial Port Control

FSR/DR/CLKR Serial Port Control

Serial R/X Timer Control

Serial R/X Timer Counter

Serial R/X Timer Period Register

Data-Transmit

Data-Receive

Primary-Bus Control

DMA Global Control

DMA Source Address

DMA Destination Address

DMA Transfer Counter

Timer 0 Global Control

Timer 0 Counter

Timer 0 Period Register

Timer 1 Global Control

Timer 1 Counter

Timer 1 Period Register

Serial Global Control

808000h

808004h

808006h

808008h

808020h

808024h

808028h

808030h

808034h

808038h

808040h

808042h

808043h

808044h

808045h

808046h

808048h

80804Ch

808064h

NOTE A: Shading denotes reserved address locations.

Figure 3. Peripheral Bus Memory-Mapped Registers

clock generator

The clock generator provides clocks to the ’VC33 device, and consists of an internal oscillator and a

phase-locked loop (PLL) circuit. The clock generator requires a reference clock input, which can be provided

by using a crystal resonator with the internal oscillator, or from an external clock source. The PLL circuit

generates the device clock by multiplying the reference clock frequency by a scale factor, allowing use of a clock

source with a lower frequency than that of the CPU.The PLL is an adaptive circuit that, once synchronized, locks

onto and tracks an input clock signal.

PR

O

DU

C

T PREVIEW

TMS320VC33

DIGITAL SIGNAL PROCESSOR

SPRS087A – FEBRUARY 1999 – REVISED DECEMBER 1999

11

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

PLL and clock oscillator control

The clock mode control pins are decoded into four operational modes as shown in Figure 4. These modes

control clock divide ratios, oscillator, and PLL power (see Table 1).

When an external clock input or crystal is connected, the opposite unused input is simply grounded. An XOR

gate then passes one of the two signal sources to the PLL stage. This allows the direct injection of a clock

reference into EXTCLK, or 1–20 MHz crystals and ceramic resonators with the oscillator circuit. The two clock

sources include:

D A crystal oscillator circuit, where a crystal or ceramic resonator is connected across the XOUT and XIN pins

and EXTCLK is grounded.

D An external clock input, where an external clock source is directly connected to the EXTCLK pin, and XOUT

is left unconnected and XIN is grounded.

When the PLL is initially started, it enters a transitional mode during which the PLL acquires lock with the input

signal. Once the PLL is locked, it continues to track and maintain synchronization with the input signal. The PLL

is a simple x5 reference multiplier with bypass and power control.

The clock divider, under CPU control, reduces the clock reference by 1 (MAXSPEED), 1/16 (LOWPOWER), or

clock stop (IDLE2). Wakeup from the IDLE2 state is accomplished by a RESET or interrupt pin logic low state.

A divide-by-two TMS320C31 equivalent mode of operation is also provided. In this case, the clock output

reference is further divided by two with clock synchronization being determined by the timing of RESET falling

relative to the present H1/H3 state.

Clock DividerPLLClock & Crystal OSC

CLKMD1

CLKMD0

PLL PWR and Bypass

Oscillator Enable

C31 DIV2 Mode

LOWPOWER

MAXSPEED/

IDLE2

H1 CLK

1/2

U

M

X

X1, 1/16, Off

XOR

SEL

X

U

M

PLLX5

EXTCLK

XIN

XOUT

RFS1

Figure 4. Clock Generation

Table 1. Clock Mode Select Pins

CLKMD0 CLKMD1 FEEDBACK PLLPWR RATIO NOTES

0 0 Off Off 1 Fully static, very low power

0 1 On Off 1/2 Oscillator enabled

1 0 On Off 1 Oscillator enabled

1 1 On On 5 10 mA @ 1.8 V PLL power. Oscillator enabled

PR

O

DU

C

T PREVIEW

TMS320VC33

DIGITAL SIGNAL PROCESSOR

SPRS087A – FEBRUARY 1999 – REVISED DECEMBER 1999

12

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

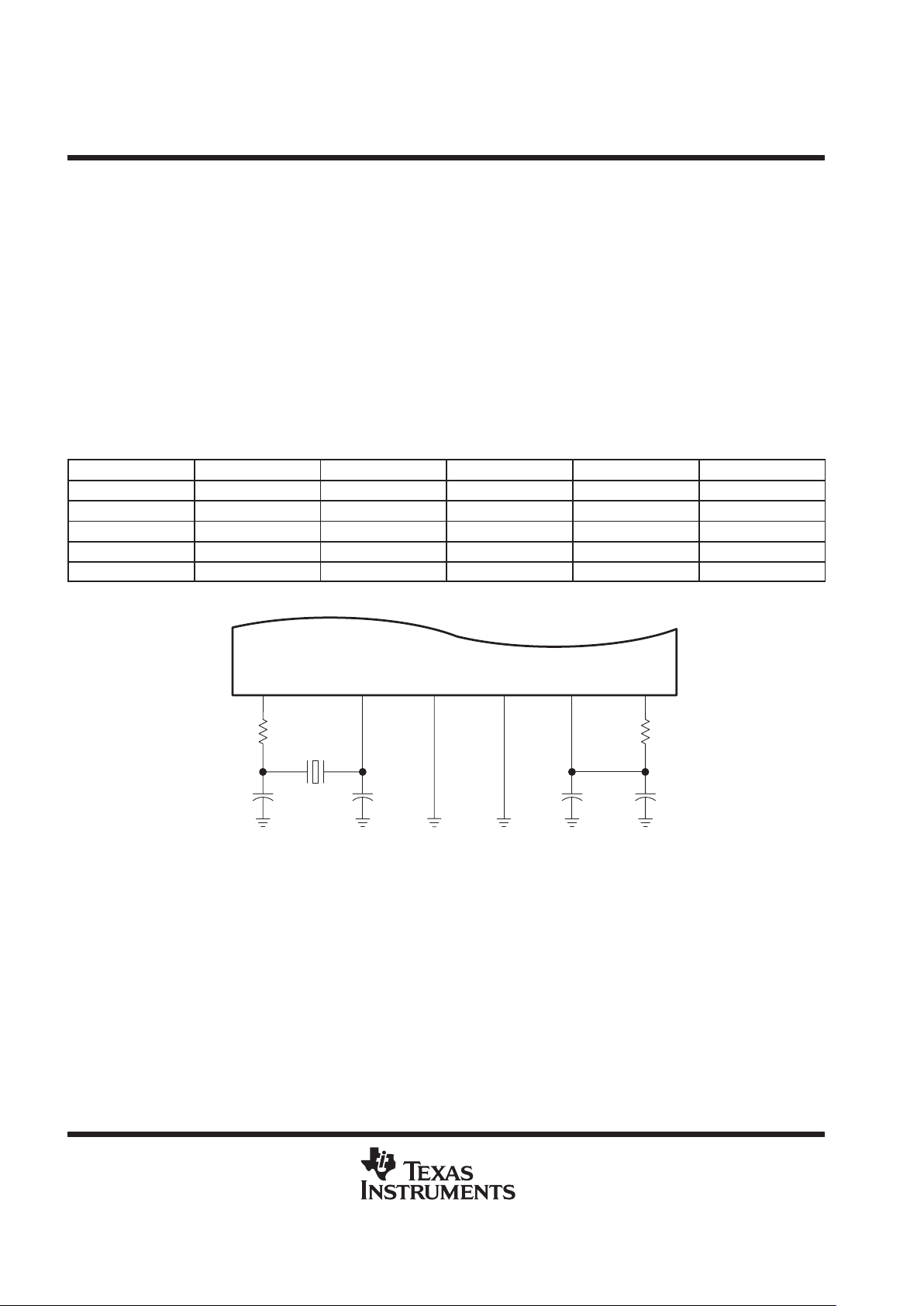

PLL and clock oscillator control (continued)

Typical crystals in the 8 – 30 MHz range have a series resistance of 25 Ω which increases below 8 MHz. To

maintain proper filtering and phase relationships, R

d

and Z

out

of the oscillator circuit should be 10x – 40x that

of the crystal. A series compensation resistor (Rd), shown in Figure 5, is recommended when using lower

frequency crystals. The XOUT output, the square wave inverse of XIN, is then filtered by the XOUT output

impedance, C1 load capacitor, and R

d

(if present). The crystal and C2 input load capacitor then refilters this

signal resulting in a XIN signal that is 30 – 80% of the oscillator supply voltage.

NOTE: Some ceramic resonators are available in a low-cost, three-terminal package that includes C1 and C2

internally. Typically ceramic resonators do not provide the frequency accuracy of crystals.

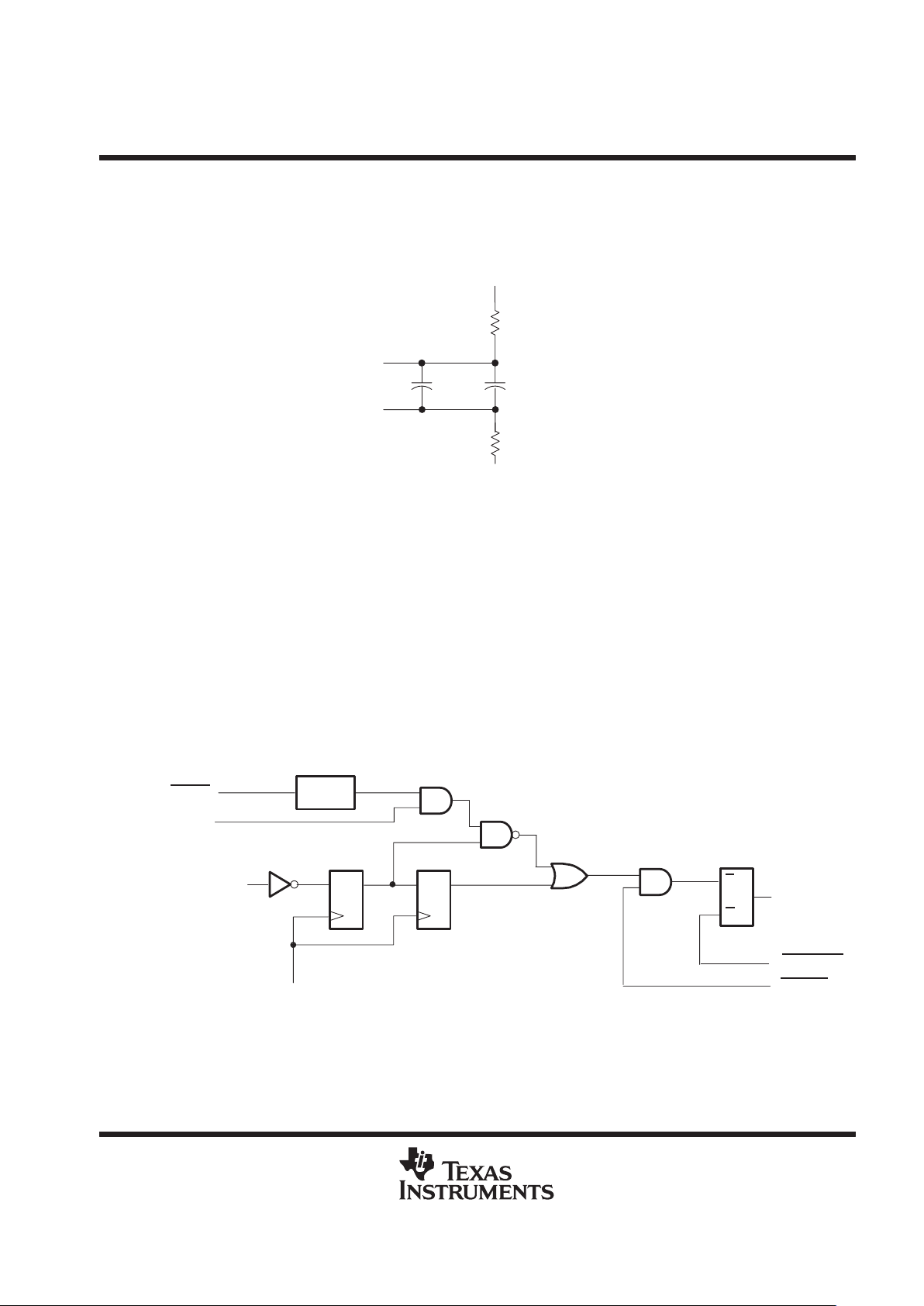

NOTE: Better PLL stability can be achieved using the optional power supply isolation circuit shown in Figure 5.

A similar filter can be used to isolate the PLLV

SS

, as shown in Figure 6. PLLVDD can also be directly connected

to CVDD.

Table 2. Typical Crystal Circuit Loading

FREQUENCY (MHz) Rd (Ω) C1 (pF) C2 (pF) CL† (pF) RL† (Ω)

2 4.7K 18 18 12 200

5 2.2K 18 18 12 60

10 470 15 15 12 30

15 0 15 12 12 25

20 0 9 9 10 25

†

CL and RL are typical internal series load capacitance and resistance of the crystal.

XOUT XIN

C1 C2

Crystal

EXTCLKRdPLLV

SS

CV

DD

100 Ω

PLLV

DD

0.1 µF

0.01 µF

Figure 5. Self-Oscillation Mode

PR

O

DU

C

T PREVIEW

TMS320VC33

DIGITAL SIGNAL PROCESSOR

SPRS087A – FEBRUARY 1999 – REVISED DECEMBER 1999

13

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

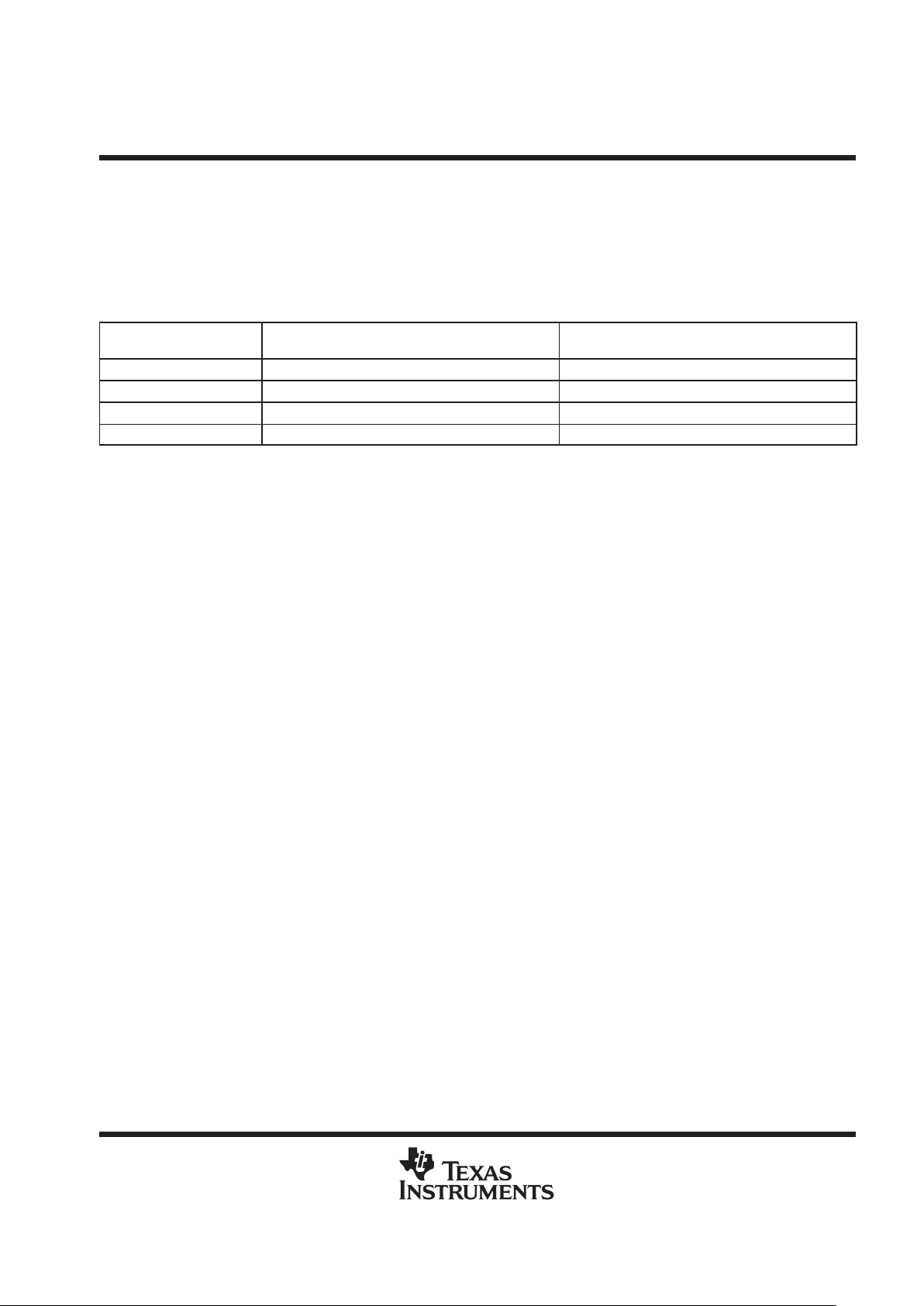

PLL isolation

The internal PLL supplies can be directly connected to CV

DD

and VSS (0 Ω case) or fully isolated as shown in

Figure 6. The RC network prevents the PLL supplies from turning high frequency noise in the CVDD and V

SS

supplies into jitter.

CV

DD

0 –100 Ω

0.1 µF

0.01 µF

0 –100 Ω

V

SS

PLLV

DD

PLLV

SS

Figure 6. PLL Isolation Circuit Diagram

EDGEMODE

When EDGEMODE = 1 a sampled digital delay line is decoded to generate a pulse on the falling edge of the

interrupt pin. T o guarantee interrupt recognition, input signal logic high and logic low states must be held longer

than the synchronizer delay of one CPU clock cycle. Holding these inputs to no less than two cycles in both the

logic low and logic high states is sufficient.

When EDGEMODE = 0, a logic low interrupt pin will continually set the corresponding interrupt flag. The CPU

or DMA can clear this flag within two cycles of it being set. This is the maximum interrupt width that can be applied

if only one interrupt is to be recognized. The CPU can manually clear IF bits within an ISR, effectively lengthening

the maximum ISR width.

After reset, EDGEMODE is temporarily disabled allowing logic low INT pins to be detected for bootload

operation.

CPU Set

IF Bit

RESET

EDGEMODE

CPU Reset

INTn

H1

Delay

DDQQ

Q

R

S

Figure 7. EDGEMODE and Interrupt Flag CIrcuit

PR

O

DU

C

T PREVIEW

TMS320VC33

DIGITAL SIGNAL PROCESSOR

SPRS087A – FEBRUARY 1999 – REVISED DECEMBER 1999

14

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

reset operation

When RESET

is applied, the CPU attempts to safely exit any pending read or write operations that may be in

progress. This can take as much as 10 CPU cycles, after which, the address, data, and control pins will be in

a high-impedance state.

When both RESET and SHZ are applied, the device will immediately enter the reset state with the pins held in

high impedance mode. SHZ

should then be disabled at least 10 CPU cycles before RESET is set high. SHZ

can be used during power-up sequencing to prevent undefined address, data, and control pins, avoiding system

conflicts.

PAGE0 – PAGE3 select lines

To facilitate simpler and higher speed connection to external devices, the TMS320VC33 includes four

predecoded select pins that have the same timings as STRB. These pins are decoded from A22, A23, and STRB

and are active only during external accesses over the ranges shown in Table 3. All external bus accesses are

controlled by a single bus control register.

T able 3. PAGE0 – PAGE3 Ranges

START END

PAGE0 0x000000 0x3FFFFF

PAGE1 0x400000 0x7FFFFF

PAGE2 0x800000 0xBFFFFF

PAGE3 0xC00000 0xFFFFFF

PR

O

DU

C

T PREVIEW

TMS320VC33

DIGITAL SIGNAL PROCESSOR

SPRS087A – FEBRUARY 1999 – REVISED DECEMBER 1999

15

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

boot loader operation

When MCBL/MP = 0, an internal ROM is decoded into the address range of 0x000000–0x001000. Therefore,

when reset occurs, execution begins within the internal ROM program and vector space. No external activity

will be evident until one of the boot options is enabled. These options are enabled by pulling an external interrupt

pin low, which the boot load software then detects, causing a particular routine to be executed (see Table 4).

Table 4. INT0 – INT3 Sources

ACTIVE INTERRUPT

ADDRESS/SOURCE WHERE BOOT DATA IS

READ FROM

DATA FORMAT

INT0 0x001000 8, 16, or 32-bit width

INT1 0x400000 8, 16, or 32-bit width

INT2 0xFFF000 8, 16, or 32-bit width

INT3 Serial Port 32-bit, external clock, and frame synch

When MCBL/MP = 0, the reset and interrupt vectors are hard coded within the internal ROM. Since this is a

read-only device, these vectors cannot be modified. To enable user defined interrupt routines, the internal

vectors contain fixed values that point to an internal section of SRAM beginning at 0x809FC1. Code execution

begins at these locations so it is important to place branch instructions (to the interrupt routine) at these locations

and not vectors.

The bootloader program requires a small stack space for calls and returns. Two SRAM locations a 0x809800

and 0x809801 are used for this stack. Y ou should not try to bootload data into these locations as it will corrupt

the boot loader program run time stack. After the bootload operation is complete, your program can reclaim

these locations. The simplest solution is to begin your programs uninitialized data section at this location.

For additional detail on boot loader operation including the boot loader source code, see the

TMS320C3x Users

Guide

(literature number SPRU031).

PR

O

DU

C

T PREVIEW

Loading...

Loading...