Page 1

www.DataSheet4U.com

www.ti.com

TMS320DM647/TMS320DM648

1 TMS320DM647/TMS320DM648 Digital Media Processor

1.1 Features

• High-Performance Digital Media Processor • C64x+ L1/L2 Memory Architecture

(DM647/DM648)

– 720, 900-MHz C64x+™ Clock Rate [Direct Mapped]

– 1.39, 1.11-ns Instruction Cycle Time – 256K-bit (32K-byte) L1D Data Cache

– 5760, 7200 MIPS

– Eight 32-Bit C64x+ Instructions/Cycle

– Fully Software-Compatible With

C64x/Debug

– Commercial Temperature Ranges

• VelociTI.2™ Extensions to VelociTI™

Advanced Very-Long-Instruction-Word (VLIW)

TMS320C64x+™ DSP Core

– Eight Highly Independent Functional Units

With VelociTI.2 Extensions:

• Six ALUs (32-/40-Bit), Each Supports

Single 32-bit, Dual 16-bit, or Quad 8-bit

Arithmetic per Clock Cycle

• Two Multipliers Support Four 16 x 16-bit

Multiplies (32-bit Results) per Clock

Cycle or Eight 8 x 8-bit Multiplies (16-Bit

Results) per Clock Cycle

– Load-Store Architecture With Non-Aligned

Support

– 64 32-bit General-Purpose Registers

– Instruction Packing Reduces Code Size

– All Instructions Conditional

– Additional C64x+™ Enhancements

• Protected Mode Operation

• Exceptions Support for Error Detection

and Program Redirection

• Hardware Support for Modulo Loop

Auto-Focus Module Operation

• C64x+ Instruction Set Features

– Byte-Addressable (8-/16-/32-/64-bit Data)

– 8-bit Overflow Protection

– Bit-Field Extract, Set, Clear

– Normalization, Saturation, Bit-Counting

– VelociTI.2 Increased Orthogonality

– C64x+ Extensions • Multichannel Audio Serial Port (McASP)

• Compact 16-bit Instructions – Ten Serializers and SPDIF (DIT) Mode

• Additional Instructions to Support

Complex Multiplies

– 256K-bit (32K-byte) L1P Program Cache

[2-Way Set-Associative]

– 2M-bit/256K-byte (DM647) or

4M-Bit/512K-byte) (DM648) L2 Unified

Mapped RAM/Cache [Flexible Allocation]

• Supports Little Endian Mode Only

• Five Configurable Video Ports

– Providing a Glueless I/F to Common Video

Decoder and Encoder Devices

– Supports Multiple Resolutions/Video Stds

• VCXO Interpolated Control Port (VIC)

– Supports Audio/Video Synchronization

• External Memory Interfaces (EMIFs)

– 32-Bit DDR2 SDRAM Memory Controller

With 256M-Byte Address Space (1.8-V I/O)

– Asynchronous 16-Bit Wide EMIF (EMIFA)

With up to 64M-Byte Address Reach

– Glueless Interface to Asynchronous

Memories (SRAM, Flash, and EEPROM)

– Synchronous Memories (SBSRAM and ZBT

SRAM)

– Supports Interface to Standard Sync

Devices and Custom Logic (FPGA, CPLD,

ASICs, etc)

• Enhanced Direct-Memory-Access (EDMA)

Controller (64 Independent Channels)

• 3-Port Gigabit Ethernet Switch

• Four 64-Bit General-Purpose Timers (Each

Configurable as Two 32-Bit Timers)

• One UART (With RTS and CTS Flow Control)

• One 4-wire Serial Port Interface (SPI) With Two

Chip-Selects

• Master/Slave Inter-Integrated Circuit (I2C

Bus™)

• 16/32-Bit Host-Port Interface (HPI)

• 32-Bit 33-/66-MHz, 3.3-V Peripheral Component

Interconnect (PCI) Master/Slave Interface

Conforms to PCI Specification 2.3

• VLYNQ™ Interface (FPGA Interface)

• On-Chip ROM Bootloader

Digital Media Processor

SPRS372 – MAY 2007

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this document.

PRODUCT PREVIEW information concerns products in the

formative or design phase of development. Characteristic data and

other specifications are design goals. Texas Instruments reserves

the right to change or discontinue these products without notice.

Copyright © 2007, Texas Instruments Incorporated

Page 2

www.ti.com

PRODUCT PREVIEW

TMS320DM647/TMS320DM648

Digital Media Processor

SPRS372 – MAY 2007

• Individual Power-Saving Modes – 529-pin nFBGA (ZUT suffix)

• Flexible PLL Clock Generators

• IEEE-1149.1 (JTAG™)

Boundary-Scan-Compatible

• 32 General-Purpose I/O (GPIO) Pins

(Multiplexed With Other Device Functions)

• Package:

1.1.1 Trademarks

TMS320C64x+, C64x, C64x+, VelociTI, VelociTI.2, VLYNQ, TMS320C6000, C6000, TI, and TMS320 are

trademarks of Texas Instruments.

I2C Bus is a registered trademark of Koninklijke Philips Electronics N.V.

Windows is a registered trademark of Microsoft Corporation in the United States and/or other countries.

All trademarks are the property of their respective owners.

1.2 Description

The TMS320C64x+™ DSPs (including the TMS320DM647/TMS320DM648 devices) are the

highest-performance fixed-point DSP generation in the TMS320C6000™ DSP platform. The

DM647/DM648 devices are based on the third-generation high-performance, advanced VelociTI™

very-long-instruction-word (VLIW) architecture developed by Texas Instruments (TI), making these DSPs

an excellent choice for digital media applications. The C64x+™ devices are upward code-compatible from

previous devices that are part of the C6000™ DSP platform. The C64x™ DSPs support added

functionality and have an expanded instruction set from previous devices.

– 19x19 mm 0.8 mm pitch BGA

– 0.09- µ m/6-Level Cu Metal Process (CMOS)

• 3.3-V and 1.8-V I/O, 1.2-V Internal (-720, -900)

• Applications:

– Digital Video Recording

Any reference to the C64x DSP or C64x CPU also applies, unless otherwise noted, to the C64x+ DSP and

C64x+ CPU, respectively.

With performance of up to 7200 million instructions per second (MIPS) at a clock rate of 900 MHz, the

C64x+ core offers solutions to high-performance DSP programming challenges. The DSP core possesses

the operational flexibility of high-speed controllers and the numerical capability of array processors. The

C64x+ DSP core processor has 64 general-purpose registers of 32-bit word length and eight highly

independent functional units—two multipliers for a 32-bit result and six arithmetic logic units (ALUs). The

eight functional units include instructions to accelerate the performance in video and imaging applications.

The DSP core can produce four 16-bit multiply-accumulates (MACs) per cycle for a total of 2400 million

MACs per second (MMACS), or eight 8-bit MACs per cycle for a total of 4800 MMACS. For more details

on the C64x+ DSP, see the TMS320C64x/C64x+ DSP CPU and Instruction Set Reference Guide

(literature number SPRU732 ).

The DM647/DM648 devices also have application-specific hardware logic, on-chip memory, and additional

on-chip peripherals similar to the other C6000 DSP platform devices. The DM647/DM648 core uses a

two-level cache-based architecture. The Level 1 program cache (L1P) is a 256K-bit direct mapped cache

and the Level 1 data cache (L1D) is a 256K-bit 2-way set-associative cache. The Level 2 memory/cache

(L2) consists of a 4M-bit (DM648) or 2M-bit (DM647) memory space that is shared between program and

data space. L2 memory can be configured as mapped memory, cache, or combinations of the two.

The peripheral set includes: The DM647/DM648 devices have five configurable 16-bit video port

peripherals (VP0, VP1, VP2, VP3, and VP4). These video port peripherals provide a glueless interface to

common video decoder and encoder devices. The DM647/DM648 video port peripherals support multiple

resolutions and video standards (e.g., CCIR601, ITU-BT.656, BT.1120, SMPTE 125M, 260M, 274M, and

296M), a VCXO interpolated control port (VIC); a 1000 Mbps 3-port switch with a management data

input/output (MDIO) module and two SGMII ports (DM648 only); an 1000 Mbps Ethernet media access

controller (EMAC) and a management data input/output (MDIO) module (only DM647); a 4-bit transmit,

TMS320DM647/TMS320DM648 Digital Media Processor2 Submit Documentation Feedback

Page 3

www.ti.com

TMS320DM647/TMS320DM648

Digital Media Processor

SPRS372 – MAY 2007

4-bit receive VLYNQ interface; an inter-integrated circuit (I2C) bus interface; a multichannel audio serial

port (McASP) with ten serializers; four 64-bit general-purpose timers each configurable as two

independent 32-bit timers; a user-configurable 16-bit or 32-bit host-port interface (HPI); 32 pins for

general-purpose input/output (GPIO) with programmable interrupt/event generation modes, multiplexed

with other peripherals; one UART; and two glueless external memory interfaces: a synchronous and

asynchronous external memory interface (EMIFA) for slower memories/peripherals, and a higher DDR2

SDRAM interface.

The video port peripherals provide a glueless interface to common video decoder and encoder devices.

The video port peripherals support multiple resolutions and video standards (e.g., CCIR601, ITU-BT.656,

BT.1120, SMPTE 125M, 260M, 274M, and 296M).

The video port peripherals are configurable and can support either video capture and/or video display

modes. Each video port consists of two channels (A and B) with a 5120-byte capture/display buffer that is

splittable between the two channels.

For more details on the video port peripherals, see the TMS320C64x DSP Video Port/VCXO Interpolated

Control (VIC) Port Reference Guide (literature number SPRU629).

The management data input/output (MDIO) module continuously polls all 32 MDIO addresses to

enumerate all PHY devices in the system.

The I2C and VLYNQ ports allow the device to easily control peripheral modules and/or communicate with

host processors.

The rich peripheral set provides the ability to control external peripheral devices and communicate with

external processors. For details on each of the peripherals, see the related sections later in this document

and the associated peripheral reference guides.

The DM647/DM648 devices have a complete set of development tools. These include C compilers, a DSP

assembly optimizer to simplify programming and scheduling, and a Windows™ debugger interface for

visibility into source code execution.

Submit Documentation Feedback TMS320DM647/TMS320DM648 Digital Media Processor 3

Page 4

www.ti.com

PRODUCT PREVIEW

Timers

(464-bit

or832-bit)

EDMA 3.0

CC

TC TCTCTC

SwitchedCentralResource

or

PCI66

UHPI

3-portEthernet

Switch

Subsystem

SGMII

(x2,DM648)

(x1,DM647)

L1D 32KB

C64x+

Mega

L1P 32KB

L2 RAM

256KB

(DM647)

512KB

(DM648)

L2 ROM

64KB

ImagingCoprocessor

VLYNQ

DDR2

EMIFA 16-bit

VideoPorts(5)

UART

McASP

SPI

I2C

PLL

JTAG

GPIOx32

VIC

DM647/DM648

TMS320DM647/TMS320DM648

Digital Media Processor

SPRS372 – MAY 2007

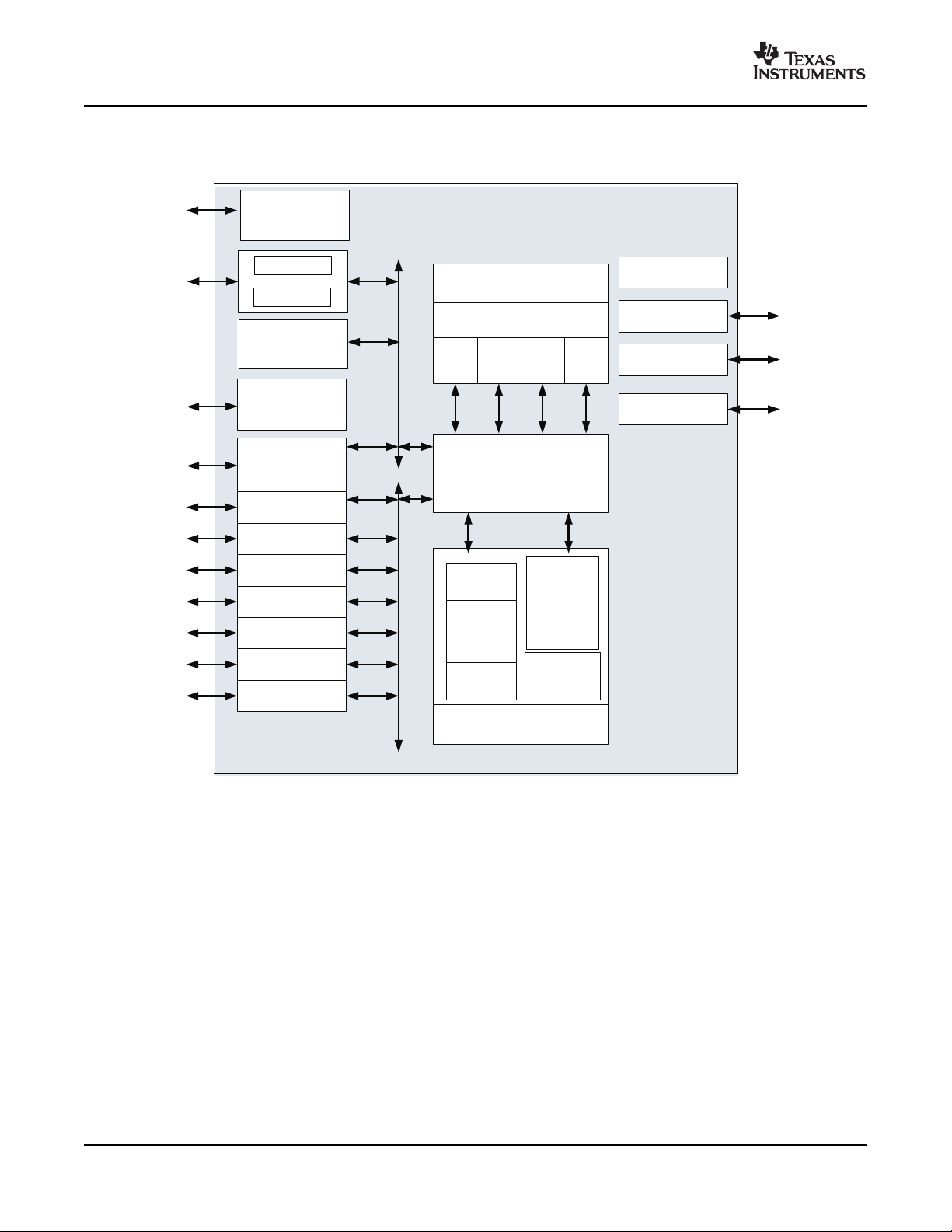

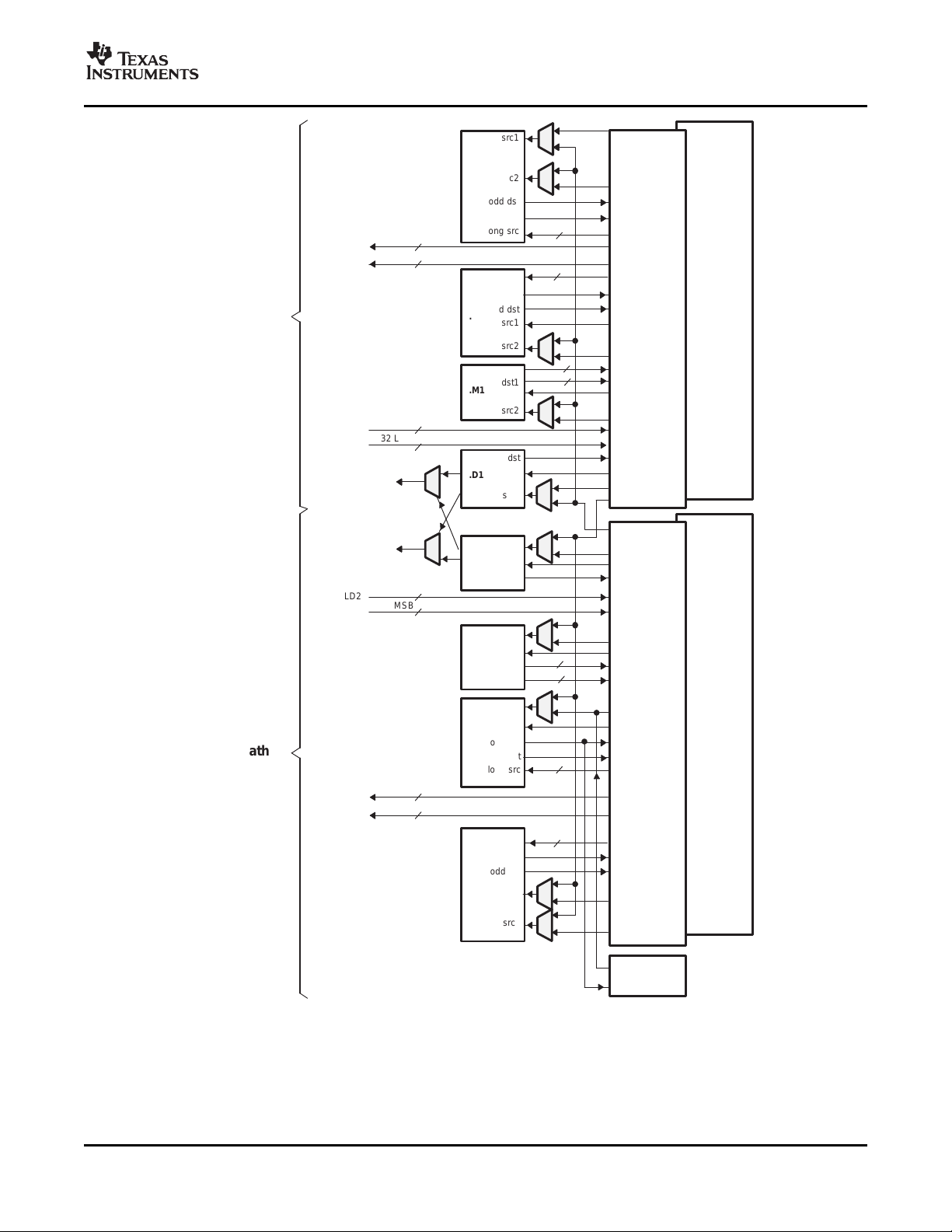

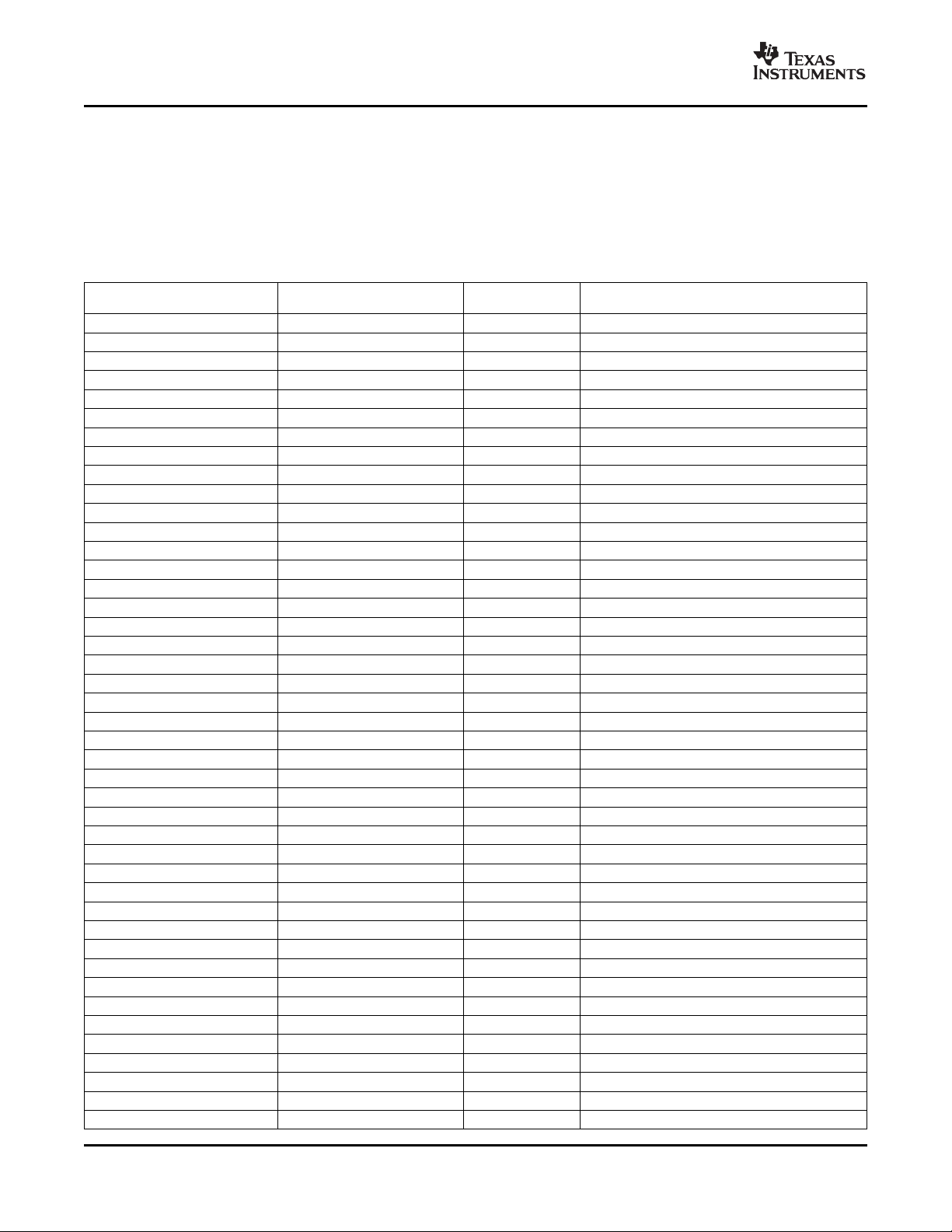

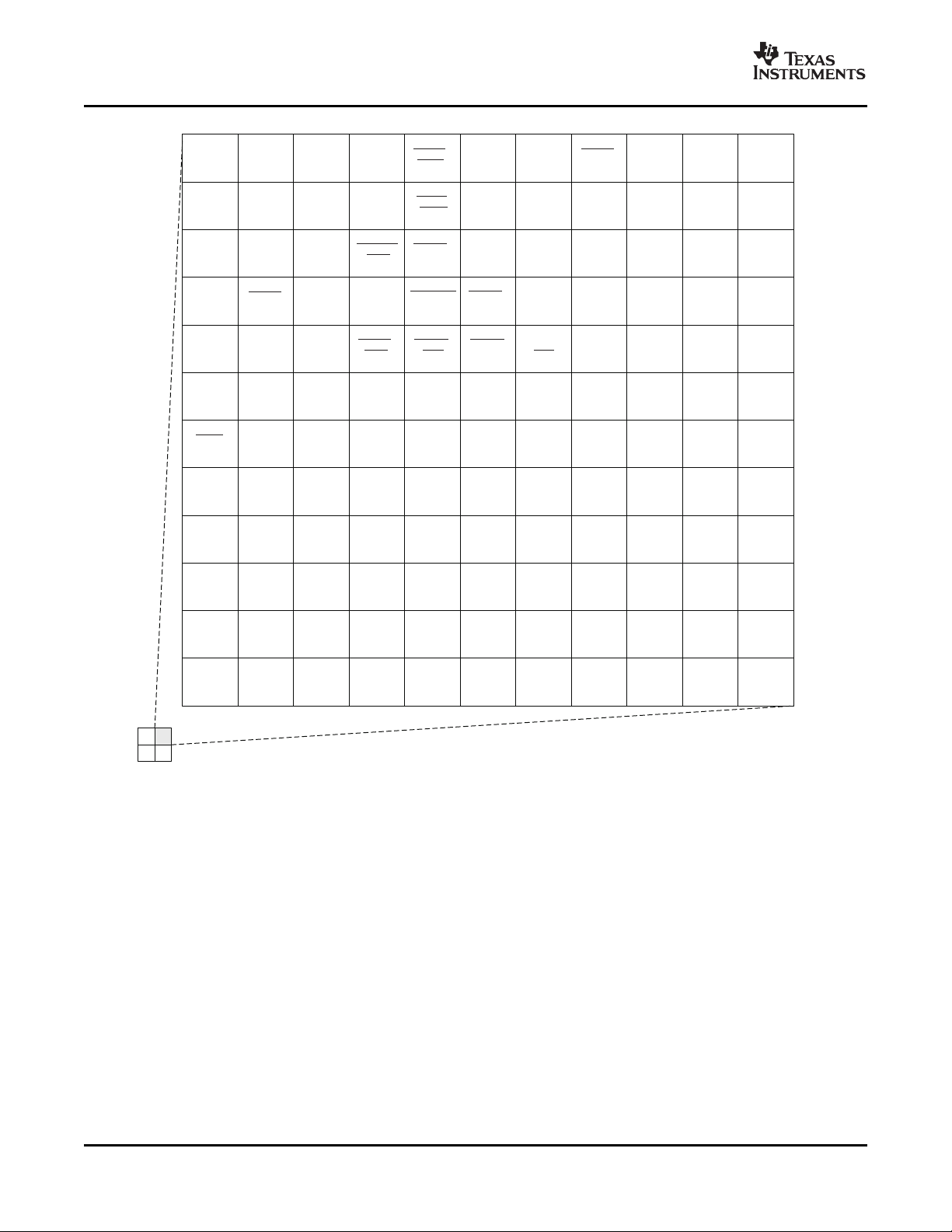

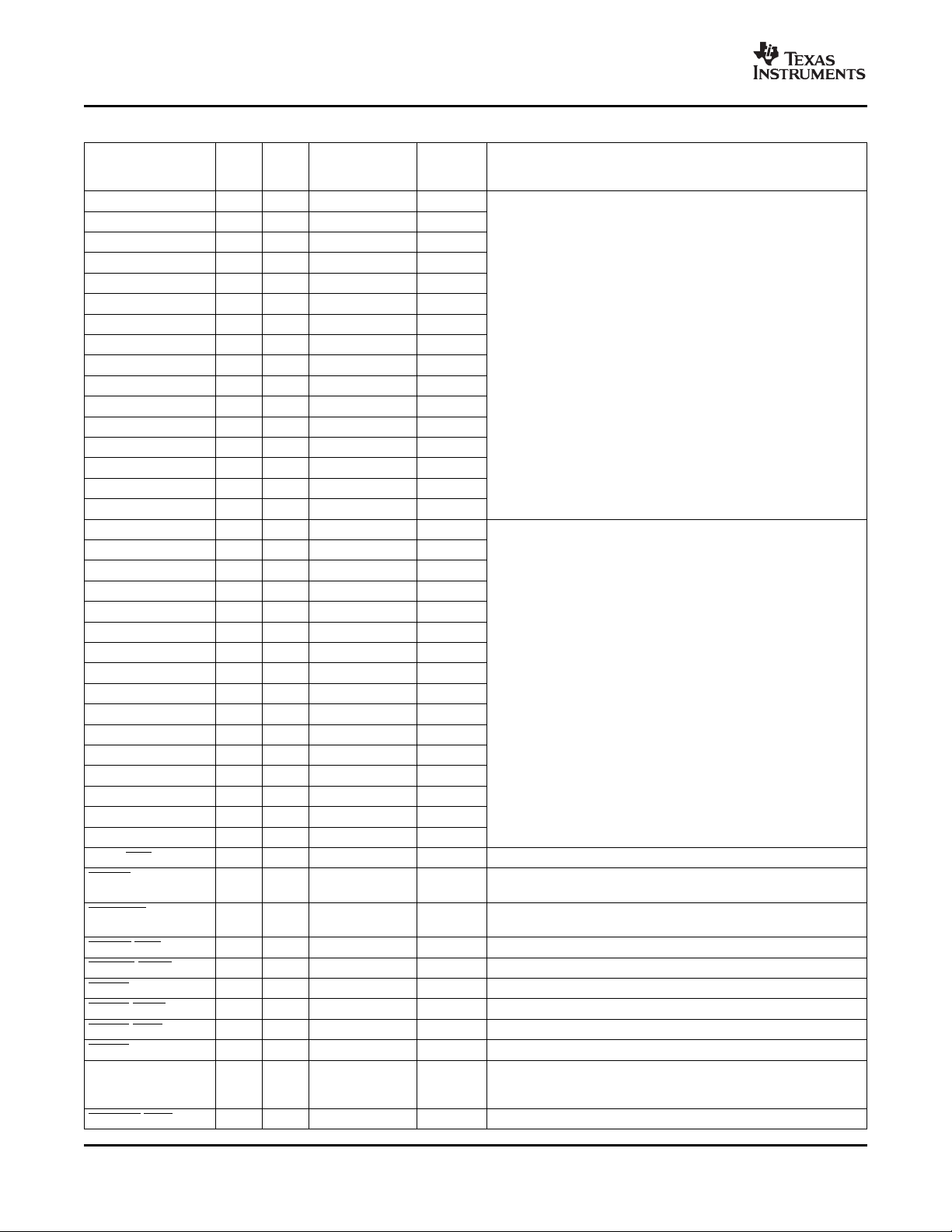

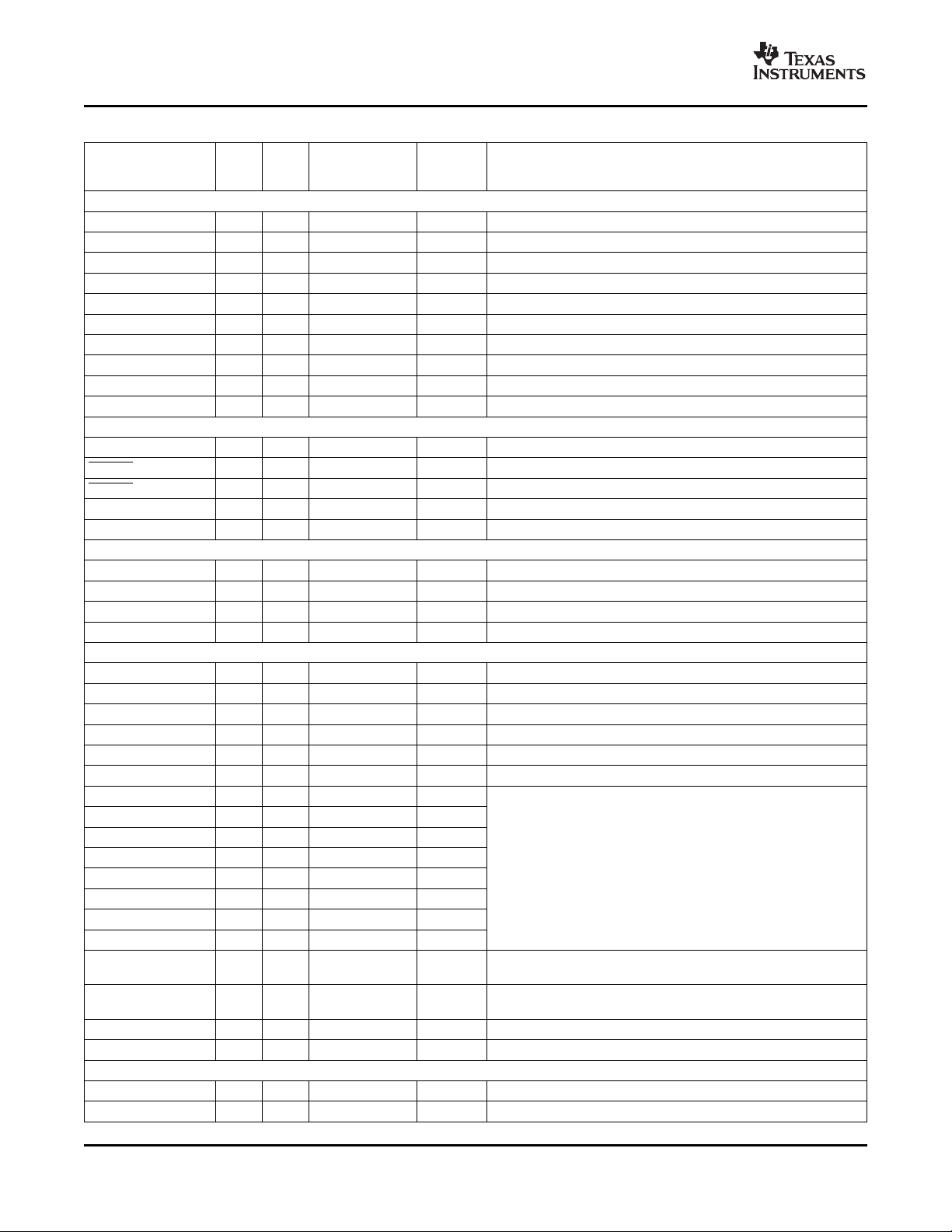

1.3 Functional Block Diagram

Figure 1-1 shows the functional block diagram of the DM647/DM648 device.

TMS320DM647/TMS320DM648 Digital Media Processor4 Submit Documentation Feedback

Figure 1-1. TMS320DM647/TMS320DM648 Functional Block Diagram

Page 5

www.ti.com

TMS320DM647/TMS320DM648

Digital Media Processor

SPRS372 – MAY 2007

Contents

1 TMS320DM647/TMS320DM648 Digital Media 6 Peripheral Information and Electrical

Processor .................................................. 1 Specifications ........................................... 56

1.1 Features .............................................. 1 6.1 Parameter Information .............................. 56

1.1.1 Trademarks .......................................... 2

1.2 Description ............................................ 2

1.3 Functional Block Diagram ............................ 4

2 Device Overview ......................................... 6

2.1 Device Characteristics ................................ 6

2.2 CPU (DSP Core) Description ......................... 7

2.3 C64x+ CPU .......................................... 10

2.4 Memory Map Summary ............................. 12

2.5 Pin Assignments .................................... 15

2.6 Terminal Functions .................................. 19

2.7 Device Support ...................................... 33

2.8 Device and Development-Support Tool

Nomenclature ....................................... 35

2.9 Documentation Support ............................. 36

3 Device Configuration .................................. 38

3.1 System Module Registers ........................... 38

3.2 Bootmode Registers ................................ 38

3.3 Debugging Considerations .......................... 47

3.4 Pullup/Pulldown Resistors ........................... 47

4 System Interconnect ................................... 49

4.1 Internal Buses, Bridges, and Switch Fabrics ........ 49

4.2 Data Switch Fabric Connections .................... 49

4.3 Configuration Switch Fabric ......................... 51

5 Device Operating Conditions ........................ 53

5.1 Absolute Maximum Ratings Over Operating

Temperature Range (Unless Otherwise Noted) ..... 53

5.2 Recommended Operating Conditions ............... 54

5.3 Electrical Characteristics Over Recommended

Ranges of Supply Voltage and Operating

Temperature (Unless Otherwise Noted) ............ 55

6.2 Recommended Clock and Control Signal Transition

Behavior ............................................. 58

6.3 Power Supplies ...................................... 58

6.4 PLL1 and PLL1 Controller ........................... 63

6.5 PLL2 and PLL2 Controller ........................... 67

6.6 Enhanced Direct Memory Access (EDMA3)

Controller ............................................ 70

6.7 Reset Controller ..................................... 83

6.8 Interrupts ............................................ 90

6.9 DDR2 Memory Controller ........................... 94

6.10 External Memory Interface A (EMIFA) .............. 96

6.11 Video Port .......................................... 104

6.12 VCXO Interpolated Control (VIC) .................. 112

6.13 Universal Asynchronous Receiver/Transmitter

(UART) ............................................. 114

6.14 Inter-Integrated Circuit (I2C) ....................... 116

6.15 Host-Port Interface (HPI) Peripheral ............... 120

6.16 Peripheral Component Interconnect (PCI) ......... 131

6.17 Multichannel Audio Serial Port (McASP)

Peripheral .......................................... 136

6.18 3-Port Ethernet Switch Subsystem (3PSW) ....... 144

6.19 Management Data Input/Output (MDIO) ........... 153

6.20 Timers .............................................. 155

6.21 VLYNQ Peripheral ................................. 157

6.22 General-Purpose Input/Output (GPIO) ............. 160

6.23 IEEE 1149.1 JTAG ................................. 163

7 Mechanical Data ....................................... 165

7.1 Thermal Data for ZUT .............................. 165

7.1.1 Packaging Information ............................. 165

Submit Documentation Feedback Contents 5

Page 6

www.ti.com

PRODUCT PREVIEW

TMS320DM647/TMS320DM648

Digital Media Processor

SPRS372 – MAY 2007

2 Device Overview

2.1 Device Characteristics

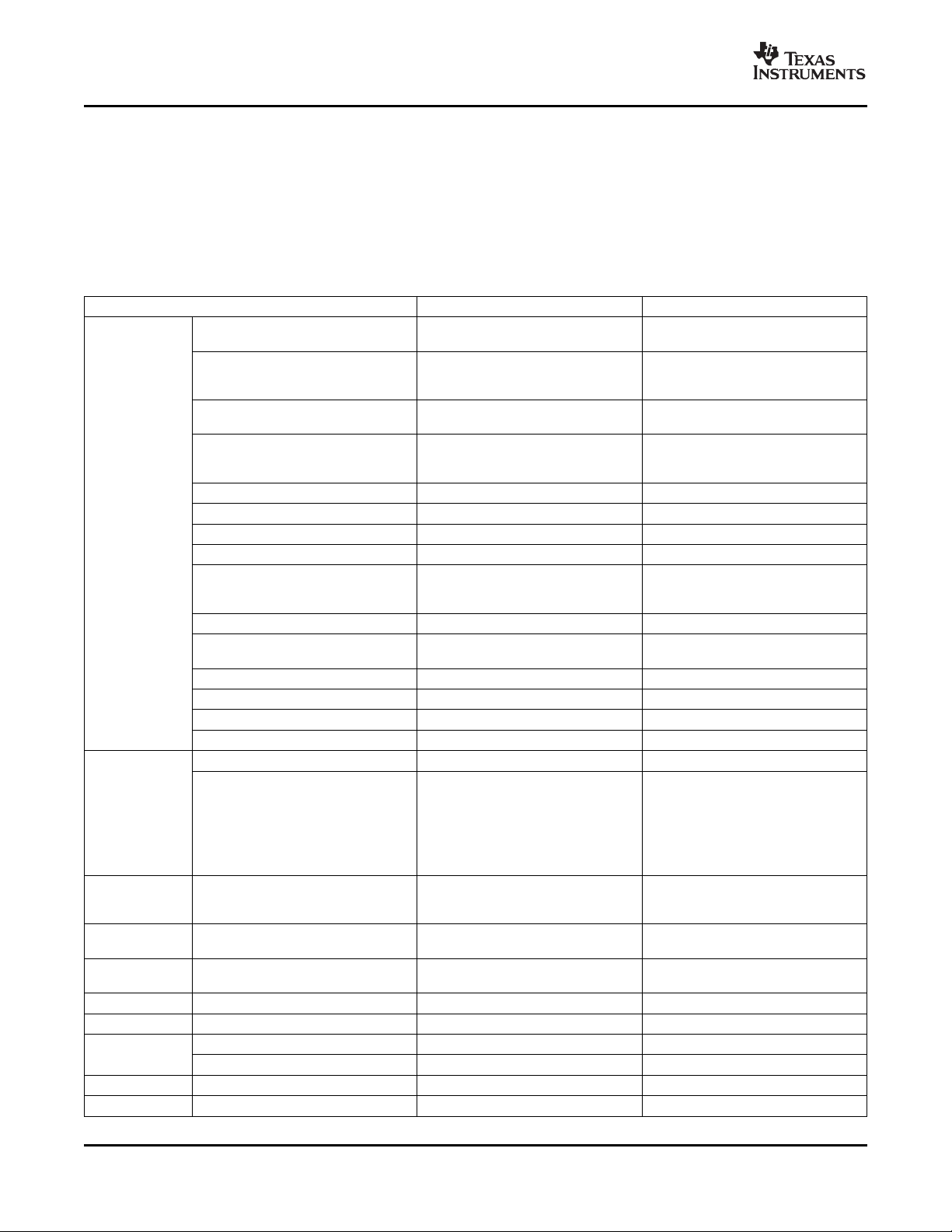

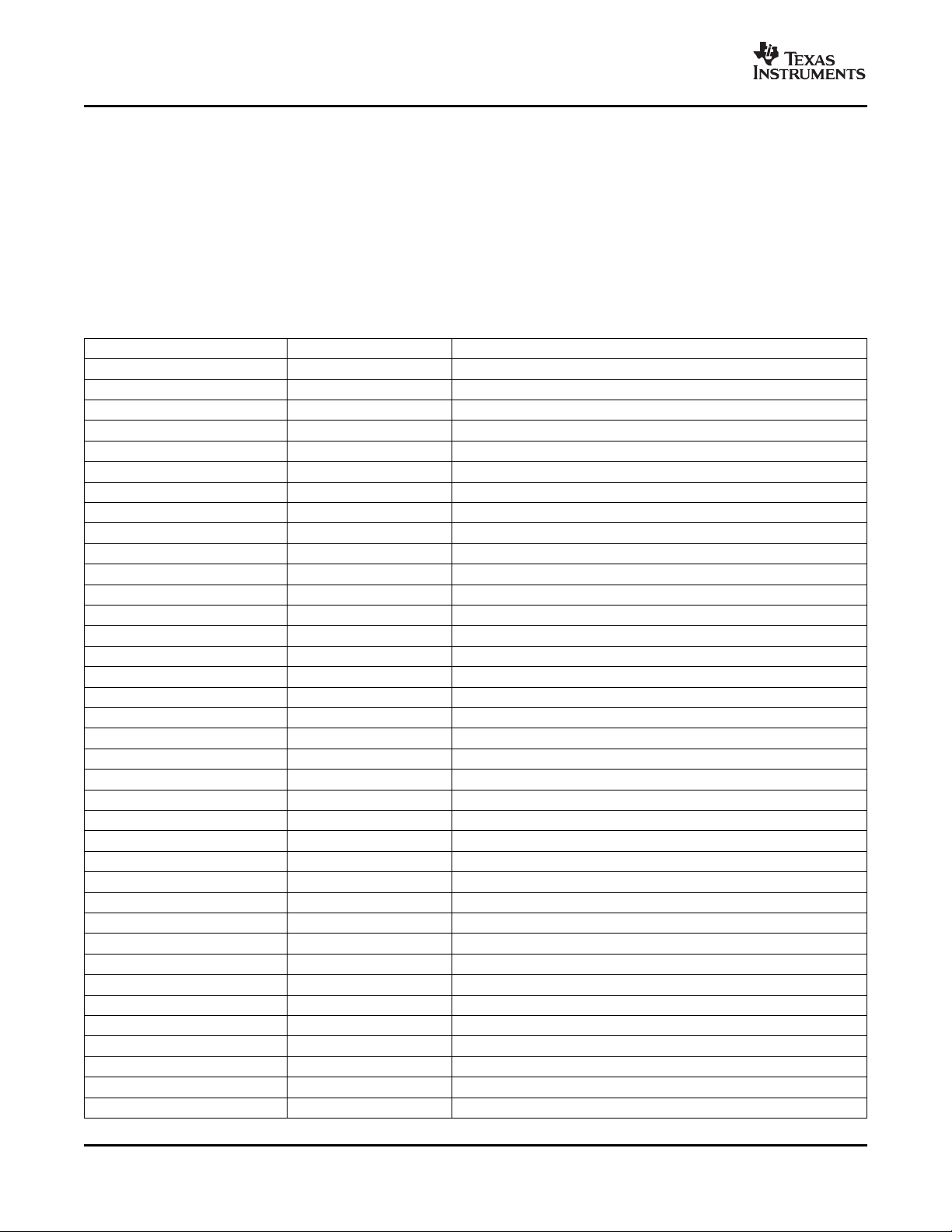

Table 2-1 , provides an overview of the TMS320DM647/TMS320DM648 DSPs. The tables show significant

features of the DM647/DM648 devices, including the capacity of on-chip RAM, the peripherals, the CPU

frequency, and the package type with pin count.

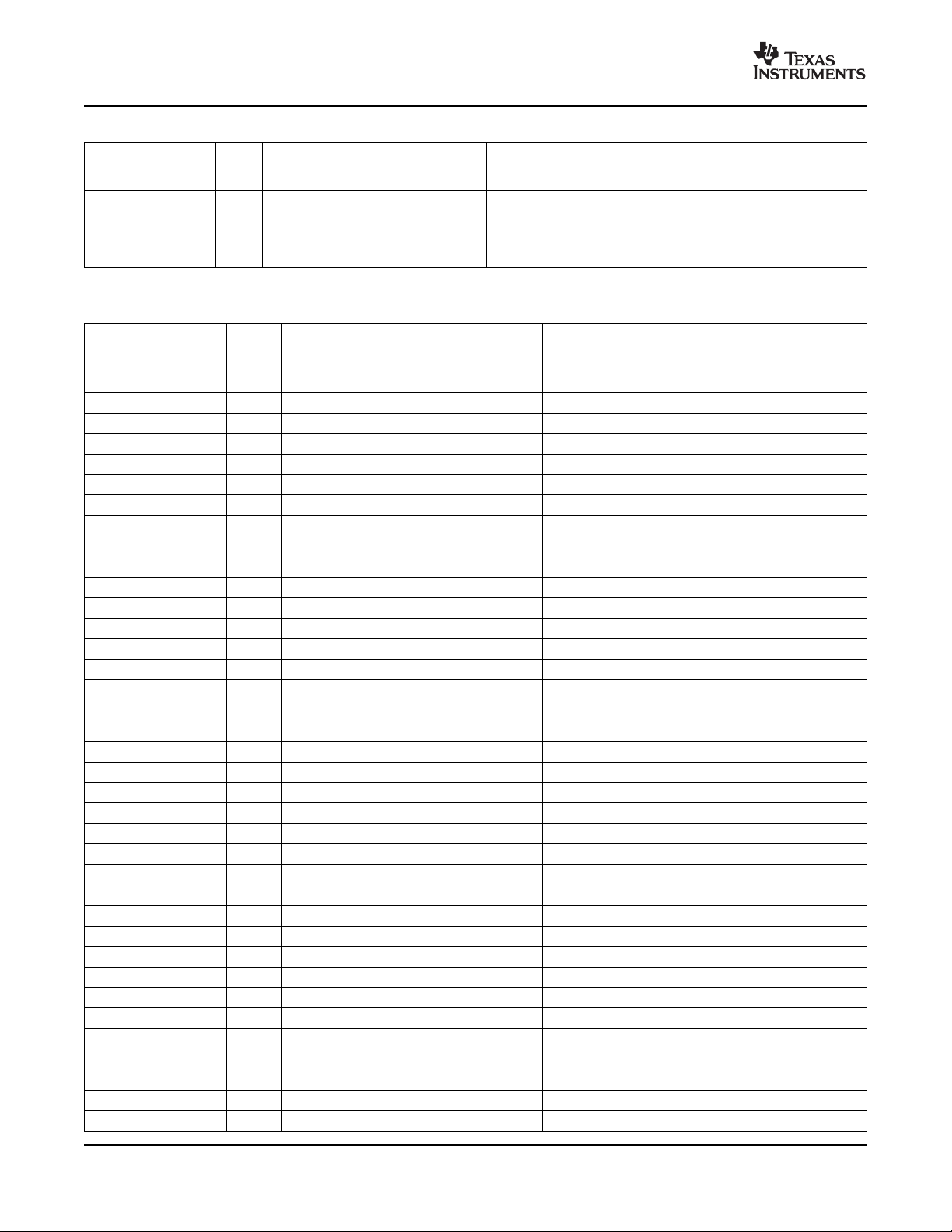

Table 2-1. Characteristics of the DM647/DM648 Processor

HARDWARE FEATURES DM647 DM648

DDR2 memory controller (32-bit bus

width) [1.8 V I/O]

16-bit bus width

synchronous/asynchronous EMIF 1 1

[EMIFA]

EDMA3 (64 independent channels, 8

QDMA channels)

Timers (each configurable as 1 64-bit or 2 (each configurable as 1 64-bit or 2

Peripherals

Not all peripheral

pins are available

at the same time

(For more detail,

see Section 3 .)

On-Chip Memory

MegaModule Rev

ID

CPU ID + CPU

Rev ID

JTAG BSDL_ID 0x0B77 A02F 0x0B77 A02F

CPU Frequency MHz 720, 900 720, 900

Cycle Time ns 1.39 ns (-720), 1.11 ns (-900) 1.39 ns (-720), 1.11 ns (-900)

Voltage

PLL Options CLKIN1 frequency multiplier x1 (Bypass), x15, x20, x25, x30, x32 x1 (Bypass), x15, x20, x25, x30, x32

BGA Package 529-Pin Flip Chip Plastic BGA (ZUT) 529-Pin Flip Chip Plastic BGA (ZUT)

UART (with RTS and CTS flow control) (with RTS and CTS flow control)

I2C 1 (Master/Slave) 1 (Master/Slave)

SPI 1 (4-wire, 2 chip select) 1 (4-wire, 2 chip select)

McASP 1 (10 serailizers) 1 (10 serailizers)

3-port Ethernet Switch Subsystem

supporting 10/100/1000 Base-T 1 SGMII port available 2 SGMII ports available

Management data input/output (MDIO)

VLYNQ 1 1

General-purpose input/output port

(GPIO)

HPI (16/32-bit) 1 1

PCI (32 bit) (33 MHz or 66 MHz) 1 (PCI33 or PCI66) 1 (PCI33 or PCI66)

VIC 1 1

Configurable video ports 5 5

Size (bytes) 320KB RAM, 64KB ROM 576KB RAM, 64KB ROM

Organization to 32KB) 32KB)

Revision ID Register

(MM_REVID[15:0]) 0x0003 0x0003

(address location 0x0181 2000)

Control Status Register (CSR.[31:16]) 0x1000 0x1000

JTAGID register

(address location: 0x0204 9018)

Core (V) 1.2 V (-720, 900) 1.2 V (-720, 900)

I/O (V) 1.8 V, 3.3 V 1.8 V, 3.3 V

1 1

1 1

4 64-bit General Purpose 4 64-bit General Purpose

32-bit) 32-bit)

Up to 32 pins Up to 32 pins

32KB L1 program (L1P)/cache (Cache 32KB L1 program (L1P)/cache (up to

up to 32KB) 32KB)

32KB L1 data (L1D)/cache (Cache up 32KB L1 data (L1D)/cache (up to

256KB unified mapped RAM/Cache 512 KB unified mapped RAM/Cache

(L2) (L2)

64KB Boot ROM 64KB Boot ROM

Device Overview6 Submit Documentation Feedback

Page 7

www.ti.com

TMS320DM647/TMS320DM648

Digital Media Processor

SPRS372 – MAY 2007

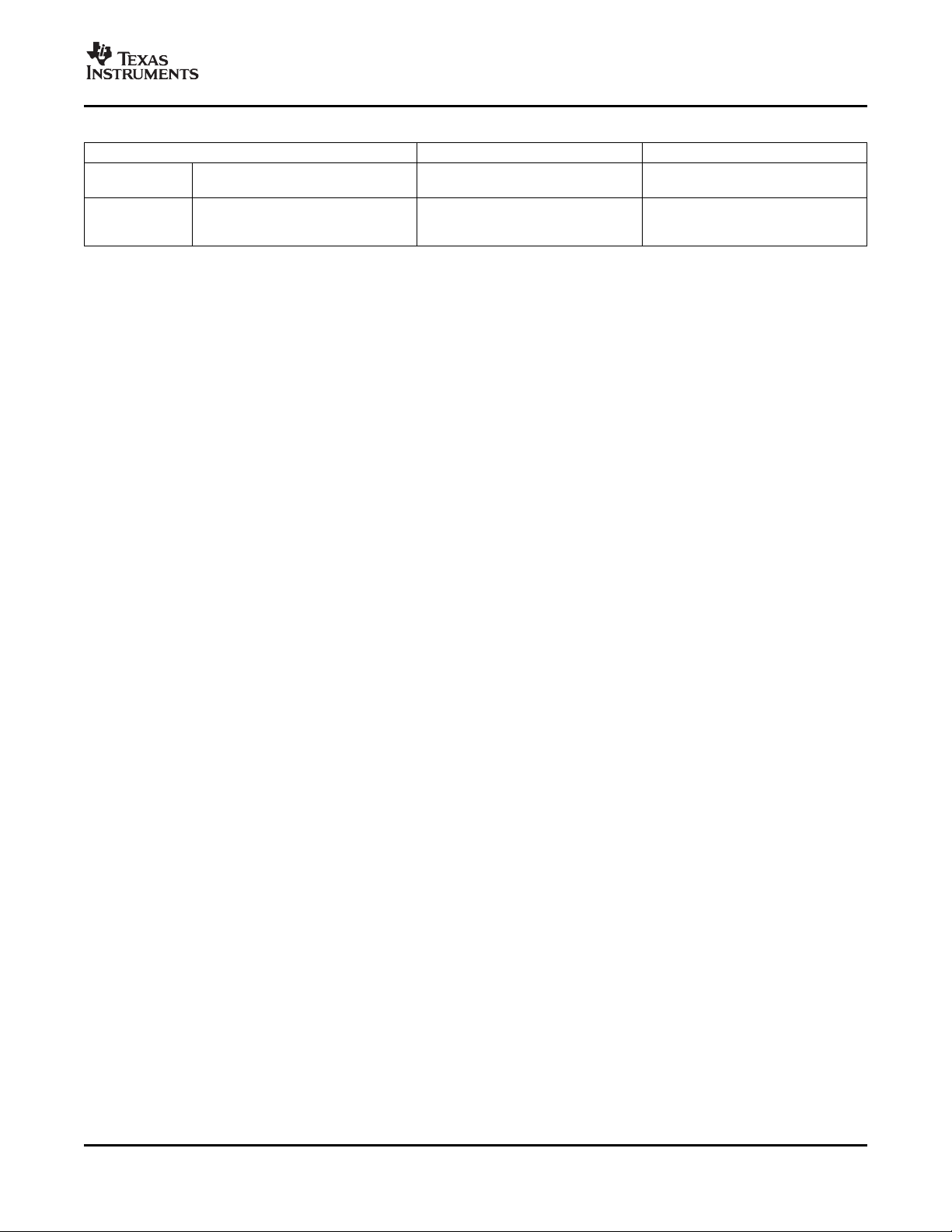

Table 2-1. Characteristics of the DM647/DM648 Processor (continued)

HARDWARE FEATURES DM647 DM648

Process 0.09- µ m/6-Level Cu Metal Process

Technology (CMOS)

Product Preview (PP), Advance

Product Status

(1) PRODUCT PREVIEW information concerns experimental products (designated as TMX) that are in the formative or design phase of

development. Characteristic data and other specifications are design goals. Texas Instruments reserves the right to change or

discontinue these products without notice.

(1)

Information (AI), PP PP

or Production Data (PD)

2.2 CPU (DSP Core) Description

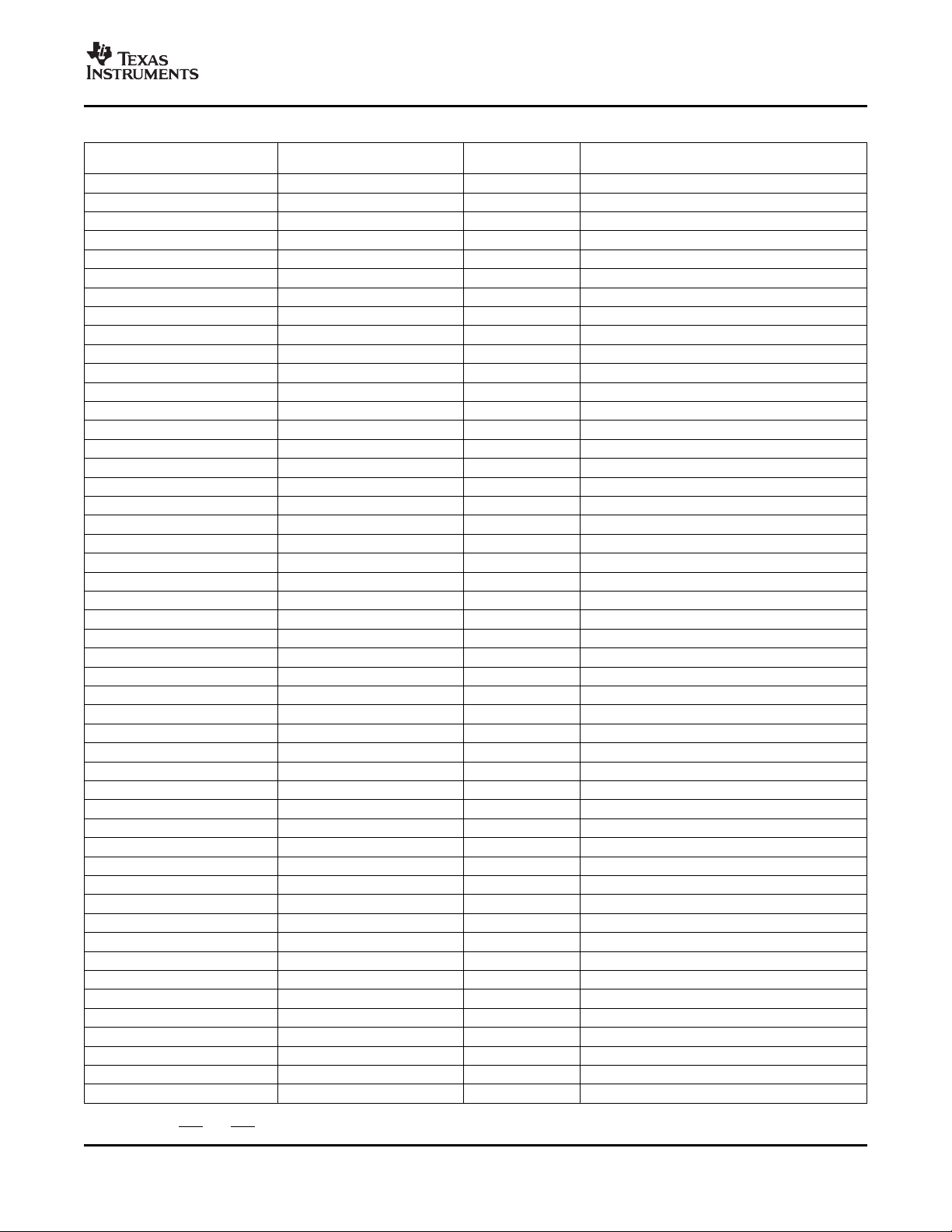

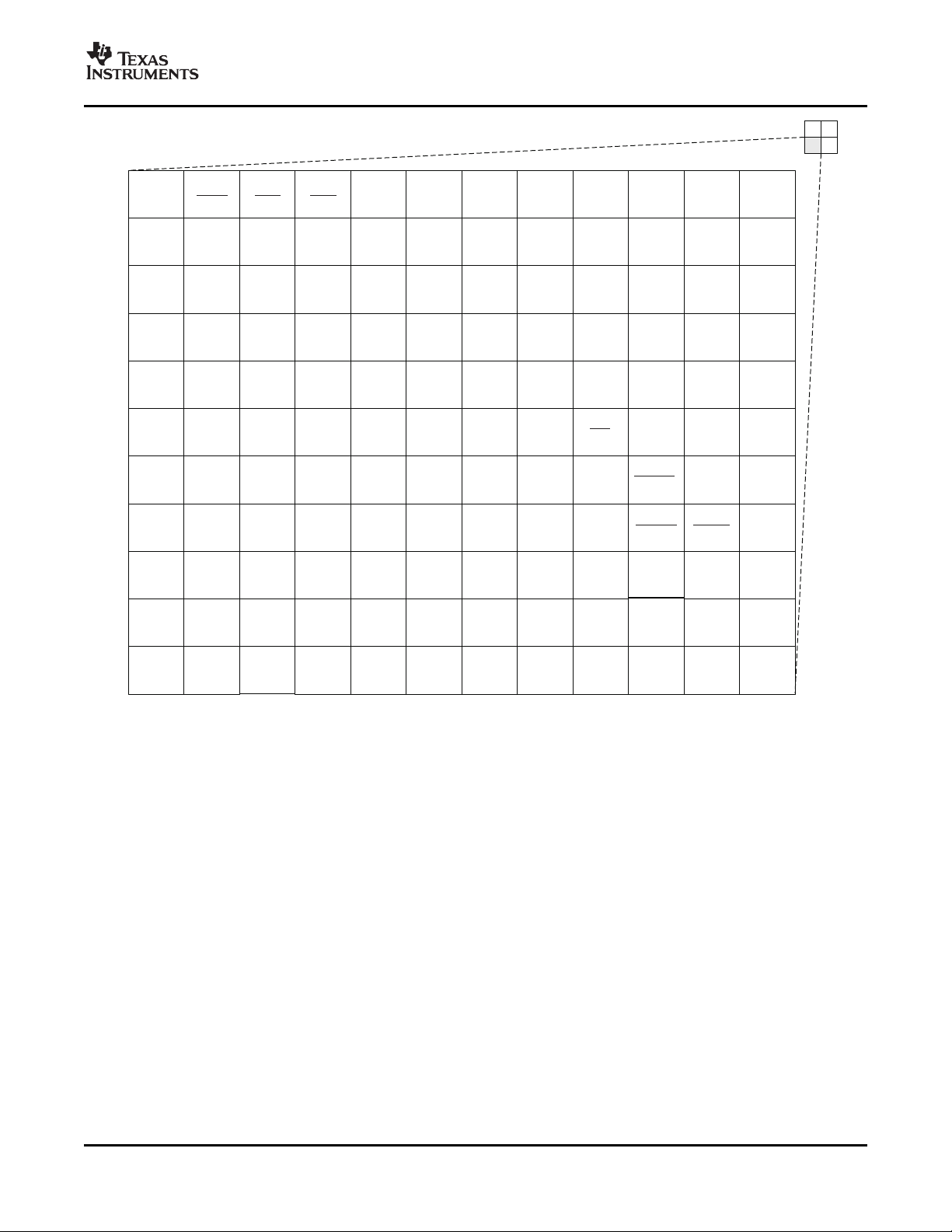

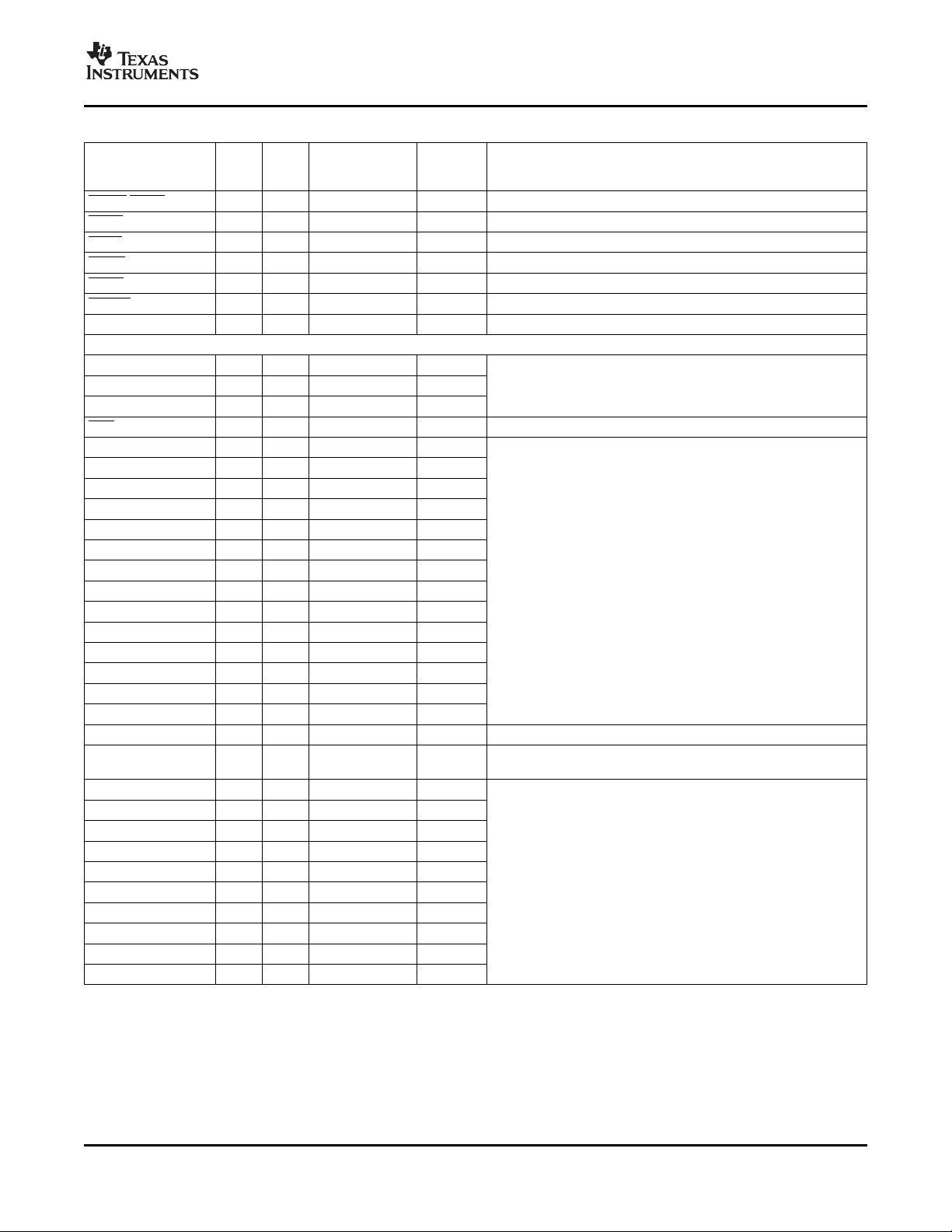

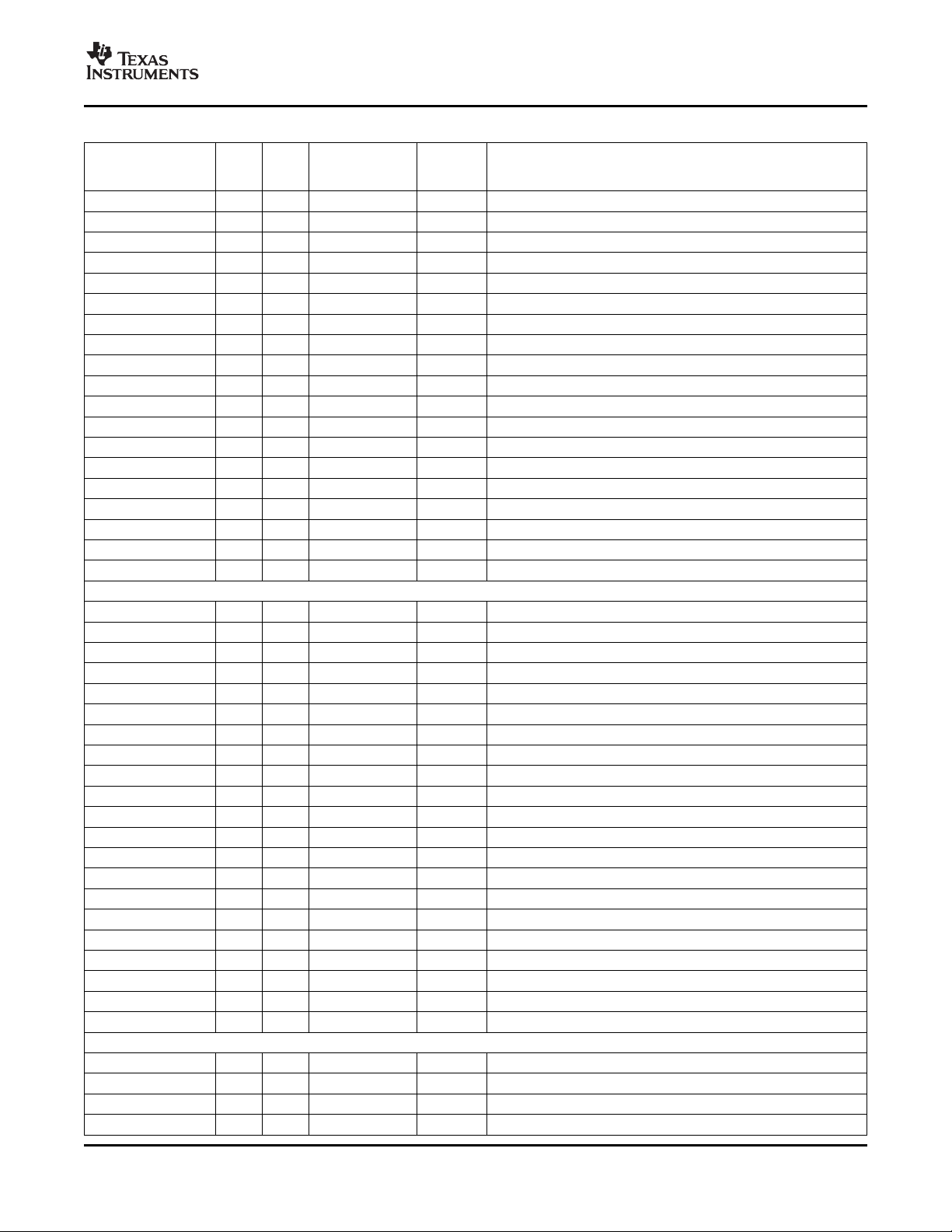

The C64x+ central processing unit (CPU) consists of eight functional units, two register files, and two data

paths as shown in Figure 2-1 . The two general-purpose register files (A and B) each contain 32 32-bit

registers for a total of 64 registers. The general-purpose registers can be used for data or can be data

address pointers. The data types supported include packed 8-bit data, packed 16-bit data, 32-bit data,

40-bit data, and 64-bit data. Values larger than 32 bits, such as 40-bit-long or 64-bit-long values are stored

in register pairs, with the 32 LSBs of data placed in an even register and the remaining 8 or 32 MSBs in

the next upper register (which is always an odd-numbered register).

The eight functional units (.M1, .L1, .D1, .S1, .M2, .L2, .D2, and .S2) are each capable of executing one

instruction every clock cycle. The .M functional units perform all multiply operations. The .S and .L units

perform a general set of arithmetic, logical, and branch functions. The .D units primarily load data from

memory to the register file and store results from the register file into memory.

0.09 µ m 0.09 µ m

The C64x+ CPU extends the performance of the C64x core through enhancements and new features.

Each C64x+ .M unit can perform one of the following each clock cycle: one 32 x 32 bit multiply, one 16 x

32 bit multiply, two 16 x 16 bit multiplies, two 16 x 32 bit multiplies, two 16 x 16 bit multiplies with

add/subtract capabilities, four 8 x 8 bit multiplies, four 8 x 8 bit multiplies with add operations, and four

16 x 16 multiplies with add/subtract capabilities (including a complex multiply). There is also support for

Galois field multiplication for 8-bit and 32-bit data. Many communications algorithms such as FFTs and

modems require complex multiplication. The complex multiply (CMPY) instruction takes for 16-bit inputs

and produces a 32-bit real and a 32-bit imaginary output. There are also complex multiplies with rounding

capability that produces one 32-bit packed output that contain 16-bit real and 16-bit imaginary values. The

32 x 32 bit multiply instructions provide the extended precision necessary for audio and other

high-precision algorithms on a variety of signed and unsigned 32-bit data types.

The .L or (Arithmetic Logic Unit) now incorporates the ability to do parallel add/subtract operations on a

pair of common inputs. Versions of this instruction exist to work on 32-bit data or on pairs of 16-bit data

performing dual 16-bit add and subtracts in parallel. There are also saturated forms of these instructions.

The C64x+ core enhances the .S unit in several ways. In the C64x core, dual 16-bit MIN2 and MAX2

comparisons were available only on the .L units. On the C64x+ core they are also available on the .S unit

which increases the performance of algorithms that do searching and sorting. Finally, to increase data

packing and unpacking throughput, the .S unit allows sustained high performance for the quad 8-bit/16-bit

and dual 16-bit instructions. Unpack instructions prepare 8-bit data for parallel 16-bit operations. Pack

instructions return parallel results to output precision including saturation support.

Other new features include:

• SPLOOP - A small instruction buffer in the CPU that aids in creation of software pipelining loops where

multiple iterations of a loop are executed in parallel. The SPLOOP buffer reduces the code size

associated with software pipelining. Furthermore, loops in the SPLOOP buffer are fully interruptible.

• Compact Instructions - The native instruction size for the C6000 devices is 32 bits. Many common

instructions such as MPY, AND, OR, ADD, and SUB can be expressed as 16 bits if the C64x+

compiler can restrict the code to use certain registers in the register file. This compression is

performed by the code generation tools.

Submit Documentation Feedback Device Overview 7

Page 8

www.ti.com

PRODUCT PREVIEW

TMS320DM647/TMS320DM648

Digital Media Processor

SPRS372 – MAY 2007

• Instruction Set Enhancement - As noted above, there are new instructions such as 32-bit

multiplications, complex multiplications, packing, sorting, bit manipulation, and 32-bit Galois field

multiplication.

• Exceptions Handling - Intended to aid the programmer in isolating bugs. The C64x+ CPU is able to

detect and respond to exceptions, both from internally detected sources (such as illegal opcodes) and

from system events (such as a watchdog time expiration).

• Privilege - Defines user and supervisor modes of operation, allowing the operating system to give a

basic level of protection to sensitive resources. Local memory is divided into multiple pages, each with

read, write, and execute permissions.

• Time-Stamp Counter - Primarily targeted for real-time operating system (RTOS) robustness, a

free-running time-stamp counter is implemented in the CPU which is not sensitive to system stalls.

For more details on the C64x+ CPU and its enhancements over the C64x architecture, see the following

documents:

• TMS320C64x/C64x+ DSP CPU and Instruction Set Reference Guide (literature number SPRU732 )

• TMS320C64x+ DSP Megamodule Reference Guide (literature number SPRU871 )

• TMS320C64x to TMS320C64x+ CPU Migration Guide Application Report (literature number SPRAA84 )

• TMS320C64x+ DSP Cache User's Guide (literature number SPRU862 )

Device Overview8 Submit Documentation Feedback

Page 9

www.ti.com

src2

src2

.D1

.M1

.S1

.L1

long src

odd dst

src2

src1

src1

src1

src1

even dst

even dst

odd dst

dst1

dst

src2

src2

src2

long src

DA1

ST1b

LD1b

LD1a

ST1a

Data path A

Odd

register

file A

(A1, A3,

A5...A31)

Odd

register

file B

(B1, B3,

B5...B31)

.D2

src1

dst

src2

DA2

LD2a

LD2b

src2

.M2

src1

dst1

.S2

src1

even dst

long src

odd dst

ST2a

ST2b

long src

.L2

even dst

odd dst

src1

Data path B

Control Register

32 MSB

32 LSB

dst2

(A)

32 MSB

32 LSB

2x

1x

32 LSB

32 MSB

32 LSB

32 MSB

dst2

(B)

(B)

(A)

8

8

8

8

32

32

32

32

(C)

(C)

Even

register

file A

(A0, A2,

A4...A30)

Even

register

file B

(B0, B2,

B4...B30)

(D)

(D)

(D)

(D)

A. On .M unit, dst2 is 32 MSB.

B. On .M unit, dst1 is 32 LSB.

C. On C64x CPU .M unit, src2 is 32 bits; on C64x+ CPU .M unit, src2 is 64 bits.

D. On .L and .S units, odd dst connects to odd register files and even dst connects to even register files.

TMS320DM647/TMS320DM648

Digital Media Processor

SPRS372 – MAY 2007

Figure 2-1. TMS320C64x+™ CPU (DSP Core) Data Paths

Submit Documentation Feedback Device Overview 9

Page 10

www.ti.com

PRODUCT PREVIEW

TMS320DM647/TMS320DM648

Digital Media Processor

SPRS372 – MAY 2007

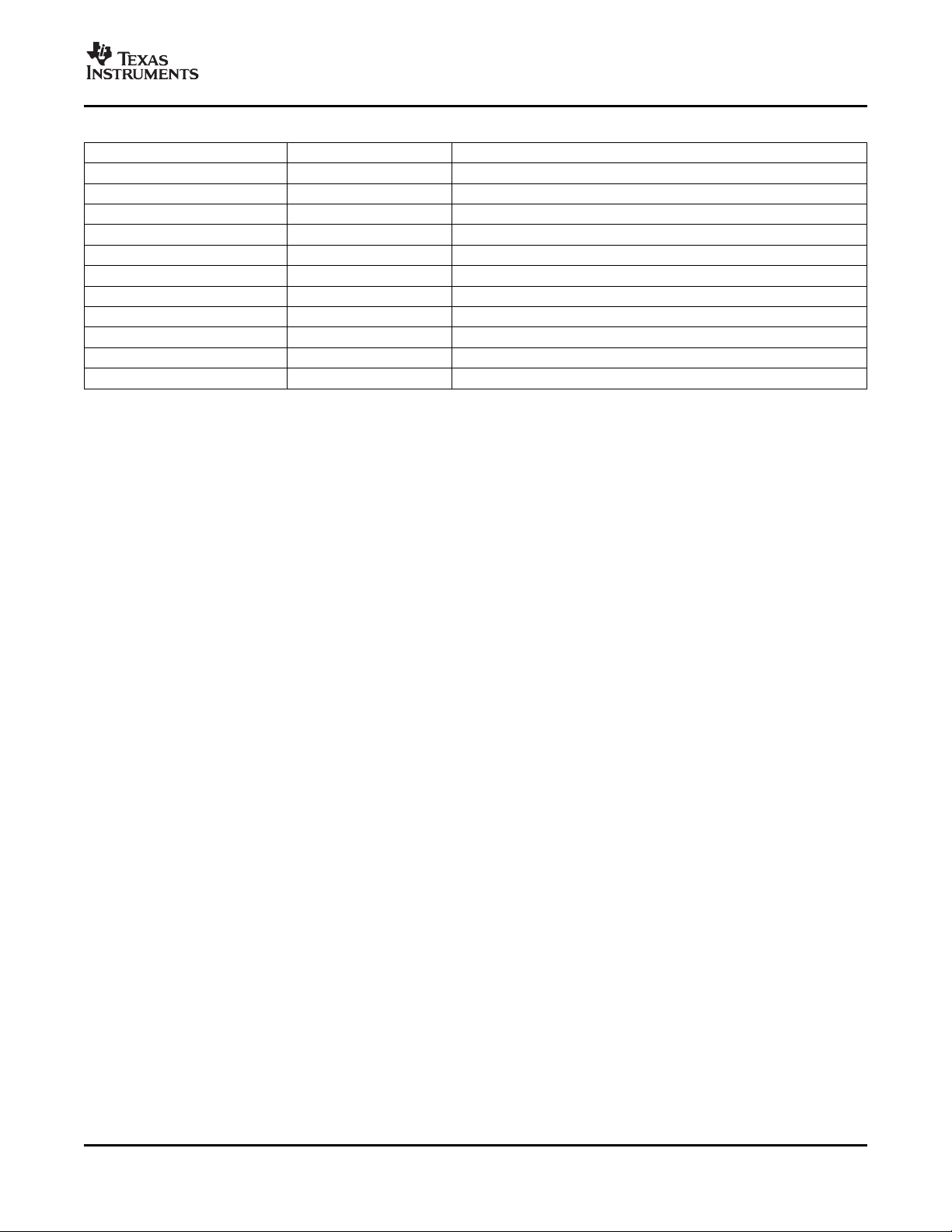

2.3 C64x+ CPU

The C64x+ core uses a two-level cache-based architecture. The Level 1 program memory/cache (L1P)

consists of 32-KB memory space that can be configured as mapped memory or direct mapped cache. The

Level 1 data memory/cache (L1D) consists of 32 KB that can be configured as mapped memory or 2-way

associated cache. The Level 2 memory/cache (L2) consists of a 256 KB (DM647)/512 KB (DM648)

memory space that is shared between program and data space. L2 memory can be configured as mapped

memory, cache, or a combination of both.

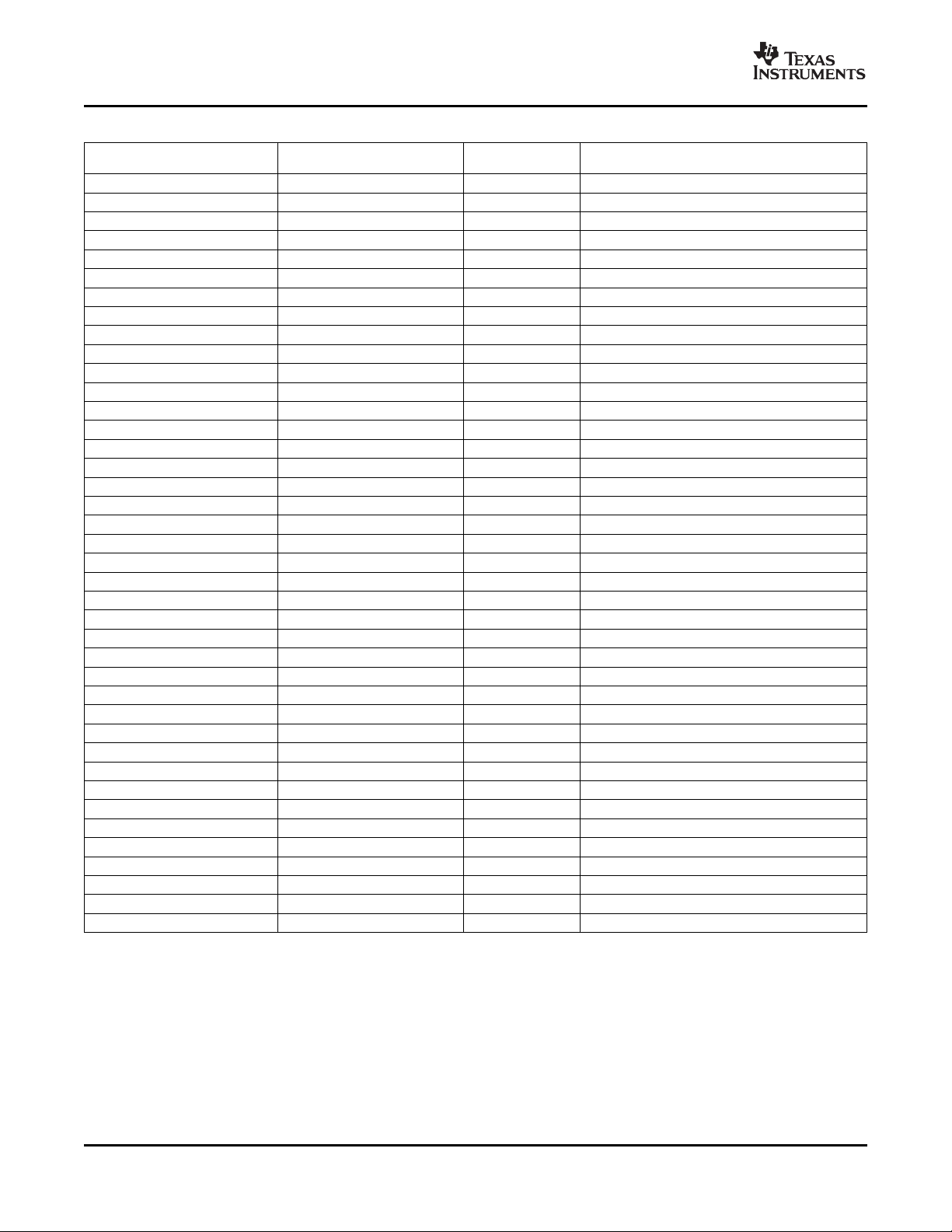

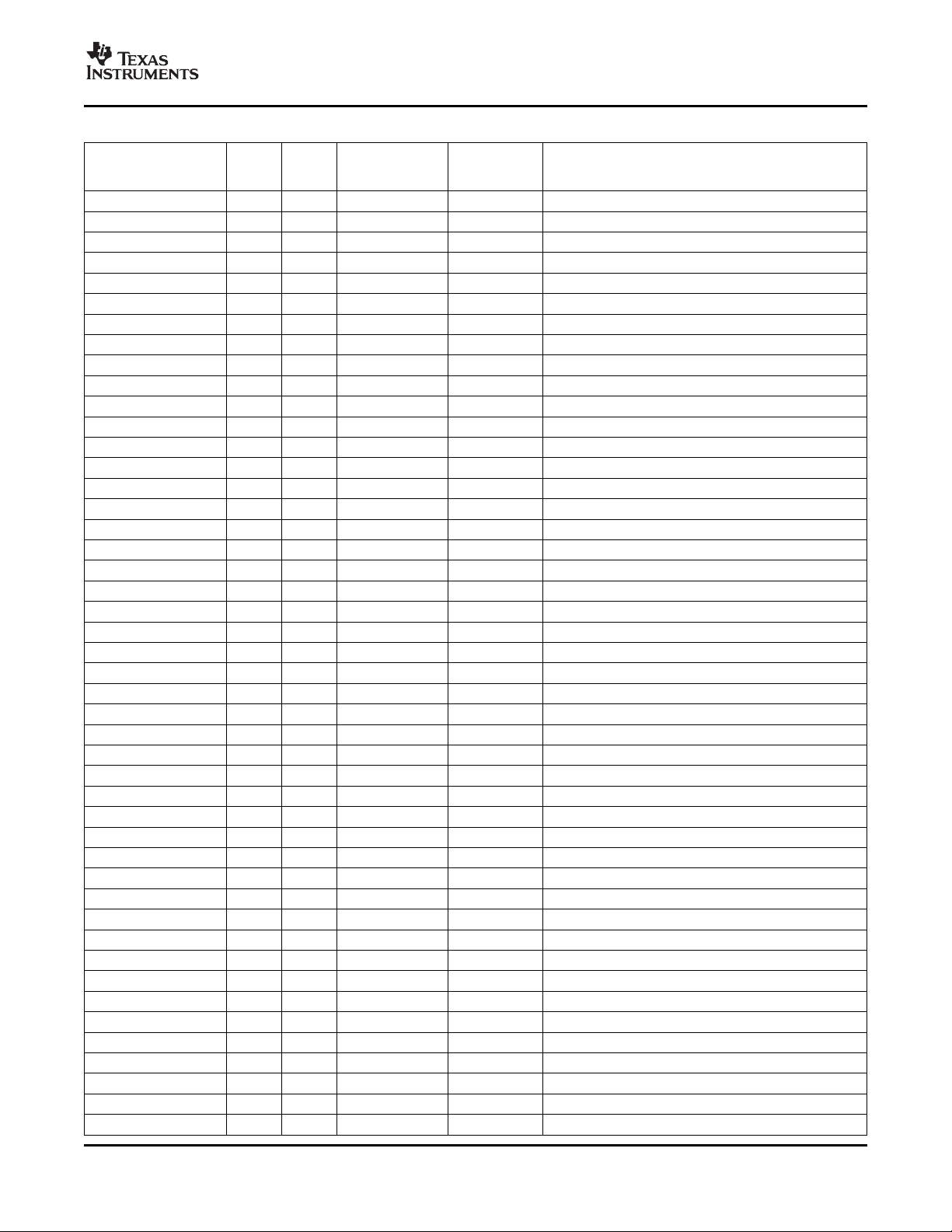

Table 2-2 shows a memory map of the C64x+ CPU cache registers for the device.

HEX ADDRESS RANGE REGISTER ACRONYM DESCRIPTION

0x0184 0000 L2CFG L2 cache configuration register

0x0184 0020 L1PCFG L1P size cache configuration register

0x0184 0024 L1PCC L1P freeze mode cache configuration register

0x0184 0040 L1DCFG L1D size cache configuration register

0x0184 0044 L1DCC L1D freeze mode cache configuration register

0x0184 0048 - 0x0184 0FFC - Reserved

0x0184 1000 EDMAWEIGHT L2 EDMA access control register

0x0184 1004 - 0x0184 1FFC - Reserved

0x0184 2000 L2ALLOC0 L2 allocation register 0

0x0184 2004 L2ALLOC1 L2 allocation register 1

0x0184 2008 L2ALLOC2 L2 allocation register 2

0x0184 200C L2ALLOC3 L2 allocation register 3

0x0184 2010 - 0x0184 3FFF - Reserved

0x0184 4000 L2WBAR L2 writeback base address register

0x0184 4004 L2WWC L2 writeback word count register

0x0184 4010 L2WIBAR L2 writeback invalidate base address register

0x0184 4014 L2WIWC L2 writeback invalidate word count register

0x0184 4018 L2IBAR L2 invalidate base address register

0x0184 401C L2IWC L2 invalidate word count register

0x0184 4020 L1PIBAR L1P invalidate base address register

0x0184 4024 L1PIWC L1P invalidate word count register

0x0184 4030 L1DWIBAR L1D writeback invalidate base address register

0x0184 4034 L1DWIWC L1D writeback invalidate word count register

0x0184 4038 - Reserved

0x0184 4040 L1DWBAR L1D block writeback

0x0184 4044 L1DWWC L1D block writeback

0x0184 4048 L1DIBAR L1D invalidate base address register

0x0184 404C L1DIWC L1D invalidate word count register

0x0184 4050 - 0x0184 4FFF - Reserved

0x0184 5000 L2WB L2 writeback all register

0x0184 5004 L2WBINV L2 writeback invalidate all register

0x0184 5008 L2INV L2 global invalidate without writeback

0x0184 500C - 0x0184 5027 - Reserved

0x0184 5028 L1PINV L1P global invalidate

0x0184 502C - 0x0184 5039 - Reserved

0x0184 5040 L1DWB L1D global writeback

0x0184 5044 L1DWBINV L1D global writeback with invalidate

Table 2-2. C64x+ Cache Registers

Device Overview10 Submit Documentation Feedback

Page 11

www.ti.com

TMS320DM647/TMS320DM648

Digital Media Processor

SPRS372 – MAY 2007

Table 2-2. C64x+ Cache Registers (continued)

HEX ADDRESS RANGE REGISTER ACRONYM DESCRIPTION

0x0184 5048 L1DINV L1D global invalidate without writeback

0x0184 8000 - 0x0184 80FC MAR0 - MAR63 Reserved 0x0000 0000 - 0x3FFF FFFF

0x0184 80C0 - 0x0184 80FC MAR48 - MAR63 Reserved 0x3000 0000 - 0x3FFF FFFF

0x0184 8100 - 0x0184 813C MAR64 - MAR79 Memory attribute registers for PCI Data 0x4000 0000 - 0x4FFF FFFF

0x0184 8140 - 0x0184 827C MAR80 - MAR159 Reserved 0x5000 0000 - 0x9FFF FFFF

0x0184 8280 - 0x0184 82BC MAR160 - MAR175 Memory attribute registers for EMIFA CE2 0xA000 0000- 0xA3FF FFFF

0x0184 8130 - 0x0184 813C MAR76 - MAR79 Memory Attribute Registers for VLYNQ 0x4C00 0000 - 0x4FFF FFFF

0x0184 82C0 - 0x0184 82FC MAR176 - MAR191 Memory attribute registers for EMIFA CE3 0xB000 0000- 0xB3FF FFFF

0x0184 8300- 0x0184 837C MAR192 - MAR223 Reserved 0xC000 0000 - 0xDFFF FFFF

0x0184 8380 - 0x0184 83BC MAR224 - MAR239 Memory attribute registers for DDR2 0xE000 0000 - 0xEFFF FFFF

0x0184 83C0 - 0x0184 83FC MAR240 - MAR255 Reserved 0xF000 0000 - 0xFFFF FFFF

Submit Documentation Feedback Device Overview 11

Page 12

www.ti.com

PRODUCT PREVIEW

TMS320DM647/TMS320DM648

Digital Media Processor

SPRS372 – MAY 2007

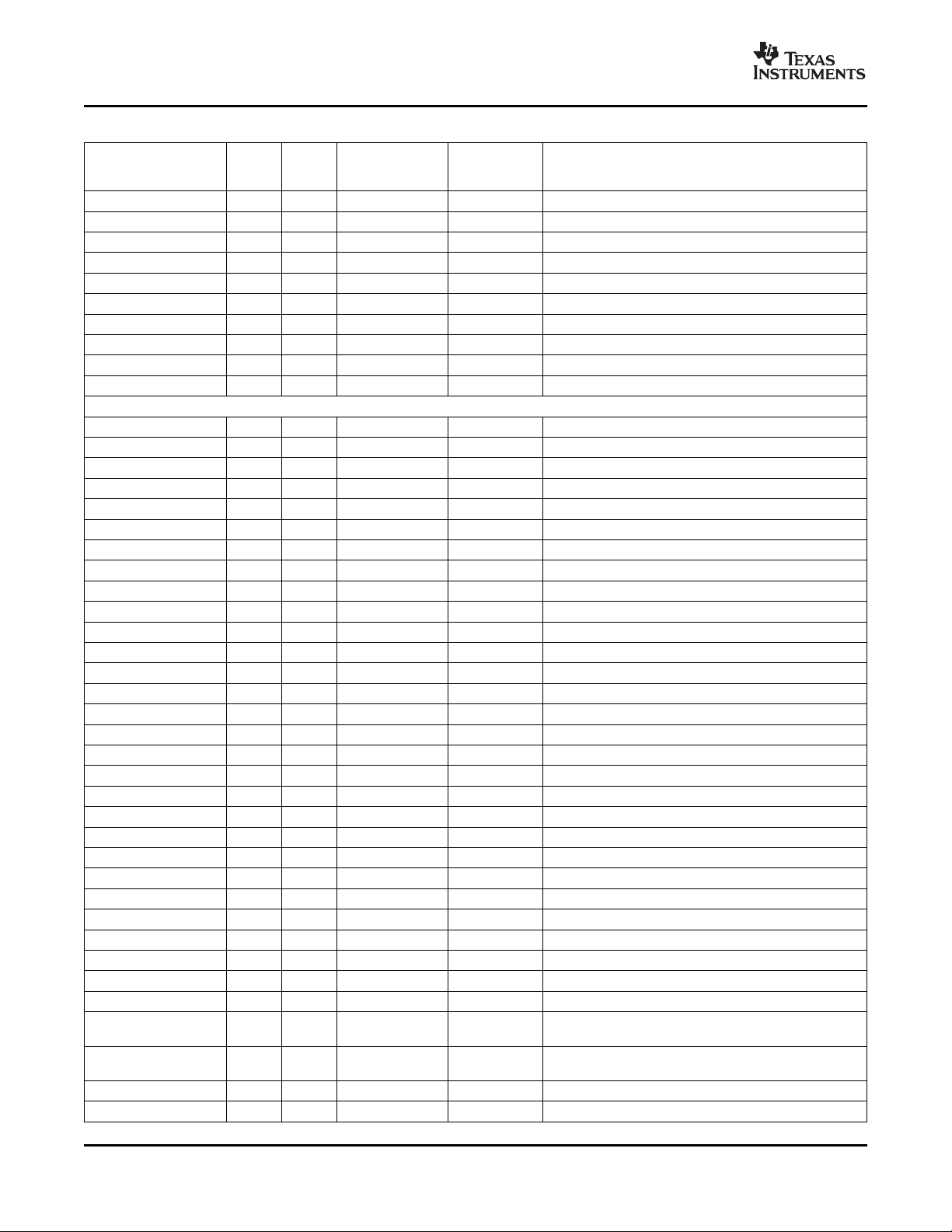

2.4 Memory Map Summary

Table 2-3 shows the memory map address ranges of the device. The device has multiple on-chip

memories associated with its two processors and various subsystems. To help simplify software

development, a unified memory map is used where possible to maintain a consistent view of device

resources across all bus masters.

START END SIZE C64x+

ADDRESS ADDRESS (Bytes) MEMORY MAP

0x0000 0000 0x000F FFFF 1M Reserved

0x0010 0000 0x0011 FFFF 128K VICP

0x0012 0000 0x001F FFFF 1M-128K Reserved

0x0020 0000 0x007F FFFF 6M Reserved

0x0080 0000 0x008B FFFF 768K Internal ROM

0x008C 0000 0x009F 7FFF 2M-768K Reserved

0x00A0 0000 0x00A3 FFFF 256K L2 SRAM (For both DM647 and DM648)

0x00A4 0000 0x00A7 FFFF 256K L2 SRAM (For DM648 only)

0x00B6 0000 0x00DF FFFF 4M-1408K Reserved

0x00E0 0000 0x00E0 7FFF 32K L1P SRAM

0x00E0 8000 0x00EF FFFF 1M – 32K Reserved

0x00F0 0000 0x00F0 7FFF 32K L1D SRAM

0x00F0 8000 0x00FF FFFF 1M – 32K Reserved

0x0100 0000 0x017F FFFF 8M Reserved

0x0180 0000 0x0180 FFFF 64K C64x+ Interrupt Controller

0x0181 0000 0x0181 0FFF 4K C64x+ Power-down Control

0x0181 1000 0x0181 1FFF 4K C64x+ Security ID

0x0181 2000 0x0181 2FFF 4K C64x+ Revision ID

0x0181 3000 0x0181 FFFF 52K Reserved

0x0182 0000 0x0182 040F 1040B C64x+ EMC

0x0182 0410 0x 0182 FFFF 64K – 16 Reserved

0x0183 0000 0x 0183 FFFF 64K Reserved

0x0184 0000 0x 0184 FFFF 64K C64x+ Memory control

0x0185 0000 0x 01BB FFFF 3, 520K Reserved

0x01BC 0000 0x 01BC FFFF 64K Emulation

0x01BD 0000 0x 01BD FFFF 64K Reserved

0x01BE 0000 0x 01BF FFFF 128K Reserved

0x01BE 0000 0x 01FF FFFF 4.125M Reserved

0x0200 0000 0x0200 0007F 128B HPI Control

0x0200 0080 0x0203 FFFF 256K – 128 Reserved

0x0204 0000 0x0204 3FFF 16K McASP Control

0x0204 4000 0x0204 43FF 1K McASP Data

0x0204 4400 0x0204 47FF 1K Timer0

0x0204 4800 0x0204 4BFF 1K Timer1

0x020 44C00 0x0204 4FFF 1K Timer2

0x0204 5000 0x0204 53FF 1K Timer3

0x0204 5400 0x0204 5FFF 3K Reserved

0x0204 6000 0x0204 6FFF 4K PSC

0x0204 7000 0x0204 73FF 1K UART

0x0204 7400 0x0204 77FF 1K VIC Control

0x0204 7800 0x0204 7BFF 1K SPI

0x0204 7C00 0x0204 7FFF 1K I2C Data and Control

0x0204 8000 0x0204 83FF 1K GPIO

Table 2-3. Memory Map Summary

Device Overview12 Submit Documentation Feedback

Page 13

www.ti.com

TMS320DM647/TMS320DM648

Digital Media Processor

Table 2-3. Memory Map Summary (continued)

START END SIZE C64x+

ADDRESS ADDRESS (Bytes) MEMORY MAP

0x0204 8400 0x0204 87FF 1K PCI Control

0x0204 8800 0x0204 8FFF 2K Reserved

0x0204 9000 0x0204 9FFF 4K Chip-Level Registers

0x0204 A000 0x0207 FFFF 216K Reserved

0x0208 0000 0x0209 FFFF 128K VICP Configuration

0x020A 0000 0x020D FFFF 256K Reserved

0x020E 0000 0x020E 01FF 512 PLL Controller 1

0x020E 0200 0x0211 FFFF 256K – 512 Reserved

0x0212 0000 0x0212 01FF 512 PLL Controller 2

0x0212 0200 0x0215 FFFF 256K – 512 Reserved

0x0216 0000 0x029C FFFF 9M-576K Reserved

0x02A0 0000 0x02A0 7FFF 32K EDMA3CC

0x02A0 8000 0x02A1 FFFF 96K Reserved

0x02A2 0000 0x02A2 7FFF 32K EDMA3TC0

0x02A2 8000 0x02A2 FFFF 32K EDMA3TC1

0x02A3 0000 0x02A3 7FFF 32K EDMA3TC2

0x02A3 8000 0x02A3 FFFF 32K EDMA3TC3

0x02A4 0000 0x02A7 FFFF 256K Reserved

0x02A8 0000 0x02A8 04FF 1.25K Reserved

0x02A8 0500 0x02AB FFFF 256K – 1.25K Reserved

0x02AC 0000 0x02AD FFFF 128K Reserved

0x02AE 0000 0x02AF FFFF 128K Reserved

0x02B0 0000 0x02B0 00FF 256 Reserved

0x02B0 0100 0x02B0 3FFF 16K – 256 Reserved

0x02B0 4000 0x02B0 407F 128 Reserved

0x02B0 4080 0x02B3 FFFF 256K – 128 Reserved

0x02B4 0000 0x02B4 01FF 512 Reserved

0x02B4 0200 0x02B7 FFFF 256K – 512 Reserved

0x02B8 0000 0x02B9 FFFF 128K Reserved

0x02BA 0000 0x02BB FFFF 128K Reserved

0x02BC 0000 0x02BF FFFF 256K Reserved

0x02C0 0000 0x02C0 3FFF 16K VP0 Control

0x02C0 4000 0x02C0 7FFF 16K VP1 Control

0x02C0 8000 0x02C0 BFFF 16K VP2 Control

0x02C0 C000 0x02C0 FFFF 16K VP3 Control

0x02C1 0000 0x02C1 3FFF 16K VP4 Control

0x02C1 4000 0x02C3 FFFF 176K Reserved

0x02C4 0000 0x02C7 FFFF 256K Reserved

0x02C8 0000 0x02CB FFFF 256K Reserved

0x02CC 0000 0x02CF FFFF 256K Reserved

0x02D0 0000 0x02D0 1FFF 8K Ethernet Subsystem CPPI RAM

0x02D0 2000 0x02D0 2FFF 4K Ethernet Subsystem Control

0x02D0 3000 0x02D0 3FFF 4K Ethernet Subsystem 3PSW

0x02D0 4000 0x02D0 47FF 2K Ethernet Subsystem MDIO

0x02D0 4800 0x02D0 4BFF 1K Ethernet Subsystem SGMII0

0x02D0 4C00 0x02D0 4FFF 1K Ethernet Subsystem SGMII1 (DM648 only)

0x02D0 5000 0x02D0 57FF 2K Reserved

0x02D0 5800 0x02DB FFFF 746K Reserved

0x02DC 0000 0x02DF FFFF 256K Reserved

(1)

(1)

SPRS372 – MAY 2007

(1) The EMIFA CS0 and CS1 are not functionally supported on the DM648 device, and therefore, are not pinned out.

Submit Documentation Feedback Device Overview 13

Page 14

www.ti.com

PRODUCT PREVIEW

TMS320DM647/TMS320DM648

Digital Media Processor

SPRS372 – MAY 2007

Table 2-3. Memory Map Summary (continued)

START END SIZE C64x+

ADDRESS ADDRESS (Bytes) MEMORY MAP

0x02E0 0000 0x02E0 3FFF 16K Reserved

0x02E0 4000 0x02FF FFFF 2M – 16K Reserved

0x0300 0000 0x03FF FFFF 16M Reserved

0x0400 0000 0x0FFF FFFF 192M Reserved

0x1000 0000 0x1FFF FFFF 256M Reserved

0x2000 0000 0x2FFF FFFF 256M Reserved

0x3000 0000 0x3000 00FF 256 Reserved

0x3000 0100 0x33FF FFFF 64M – 256 Reserved

0x3400 0000 0x3400 00FF 256 Reserved

0x3400 0100 0x37FF FFFF 64M – 256 Reserved

0x3800 0000 0x3BFF FFFF 64M VLYNQ

0x3C00 0000 0x3CFF FFFF 16M Reserved

0x3D00 0000 0x3DFF FFFF 16M Reserved

0x3E00 0000 0x3FFF FFFF 32M Reserved

0x4000 0000 0x4FFF FFFF 256M PCI Data

0x5000 0000 0x51FF FFFF 32M VP0 ChannelA Data

0x5200 0000 0x53FF FFFF 32M VP0 ChannelB Data

0x5400 0000 0x55FF FFFF 32M VP1 ChannelA Data

0x5600 0000 0x57FF FFFF 32M VP1 ChannelB Data

0x5800 0000 0x59FF FFFF 32M VP2 ChannelA Data

0x5A00 0000 0x5BFF FFFF 32M VP2 ChannelB Data

0x5C00 0000 0x5DFF FFFF 32M Reserved

0x5E00 0000 0x5FFF FFFF 32M Reserved

0x6000 0000 0x61FF FFFF 32M VP3 ChannelA Data

0x6200 0000 0x63FF FFFF 32M VP3 ChannelB Data

0x6400 0000 0x65FF FFFF 32M VP4 ChannelA Data

0x6600 0000 0x67FF FFFF 32M VP4 ChannelB Data

0x6800 0000 0x6FFF FFFF 128M Reserved

0x7000 0000 0x77FF FFFF 128M EMIFA Config

0x7800 0000 0x7FFF FFFF 128M DDR2 EMIF Config

0x8000 0000 0x8FFF FFFF 256M Reserved

0x9000 0000 0x9FFF FFFF 256M Reserved

0xA000 0000 0xA3FF FFFF 64M EMIFA CE2

0xA400 0000 0xAFFF FFFF 256-64M Reserved

0xB000 0000 0xB3FF FFFF 64M EMIFA CE3

0xB400 0000 0xBFFF FFFF 256-64M Reserved

0xC000 0000 0xCFFF FFFF 256M Reserved

0xD000 0000 0xDFFF FFFF 256M Reserved

0xE000 0000 0xEFFF FFFF 256M DDR2 SDRAM

0xF000 0000 0xFFFF FFFF 256M Reserved

Device Overview14 Submit Documentation Feedback

Page 15

www.ti.com

2.5 Pin Assignments

V

SS

D

VDD33

D

VDD33

AHCLKX AHCLKR ACLKR ACLKX

V

SS

SGMII1RXN

REFCLKN

V

SS

VP2CLK0 VP2CTL1

AMUTEIN

AMUTE

V

SS

AFSR

A

VDDT

SGMII0RXP

A

VDDR

REFCLKP

VP2CTL0

VP2D07

V

SS

AXR7

AXR6

VDAC/

AXR9

AFSX

V

SS

SGMII1RXP

SGMII0RXN

V

SS

PREQ/

GP03

VP2CTL2/

VSCRUN

VP2D04

VP2D03

STCLK/

AXR8

AXR4

AXR0

V

SS

SGMII1TXP

VP2CLK1/

VCLK

VP2D12/

VRXD0

VP2D06

VP2D09 VP2D02

AXR3

V

SS

SGMII0TXP

SGMII0TXN

A

VDDA

SGMII1TXN

RSV22

V

SS

VP2D13

/VRXD1

VP2D14/

VRXD2

VP2D08

AXR5

AXR1

RSV17

VP2D15/

VRXD3

VP2D17/

VTXD1

VP2D16/

VTXD0

VP2D19/

VTXD3

VP2D18/

VTXD2

VP2D05

AXR2

MDIO

MDCLK

D

VDDD

PINTA/

GP02

PRST/

GP01

VP3CLK0/

AECLKIN

VP3CTL0/

ASDWE

VP3D05/

AED03

VP3D04/

AED02

VP3D03/

AED01

VP3D02/

AED00

V

SS

V

SS

V

SS

VP3CTL1/

ARNW

VP3D12/

AED08

VP3D09/

AED07

VP3D08/

AED06

VP3D07/

AED05

VP3D06/

AED04

AC

AB

AA

Y

W

V

U

T

R

P

N

M

V

SS

C

VDDESS

V

SS

VP3CLK1/

AECLK

OUT

VP3CTL2/

AOE

VP3D16/

AED12

VP3D15/

AED11

VP3D14/

AED10

VP3D13/

AED09

V

SS

V

SS

V

SS

V

SS

PLLV1

VP3D17/

AED13

VP3D19/

AED15

VP3D18/

AED14

V

SS

V

SS

V

SS

CLKIN1

RSV9

SYSCLK4

VP4D03/

ABE01

VP4D04/

AEA10

VP4D05 V

SS

V

SS

V

SS

C

VDD

1 2

3

4

5 6

7

8 9 10

11 12

D

VDD33

D

VDD33

D

VDD33

D

VDD33

D

VDD33

D

VDD33

D

VDD33

V

SS

RSV21

A

VDDA

C

VDD

C

VDD

C

VDD

C

VDD

D

VDD33

C

VDD

D

VDD33

D

VDD33

D

VDD33

A

VDDA

D

VDD33

V

SS

C

VDDESS

A

VDDT

V

SS

C

VDD

C

VDD

Extensive use of pin multiplexing is used to accommodate the largest number of peripheral functions in

the smallest possible package. Pin multiplexing is controlled using a combination of hardware

configuration at device reset and software programmable register settings. For more information on pin

muxing, see Section 3.2.6 , PINMUX Register.

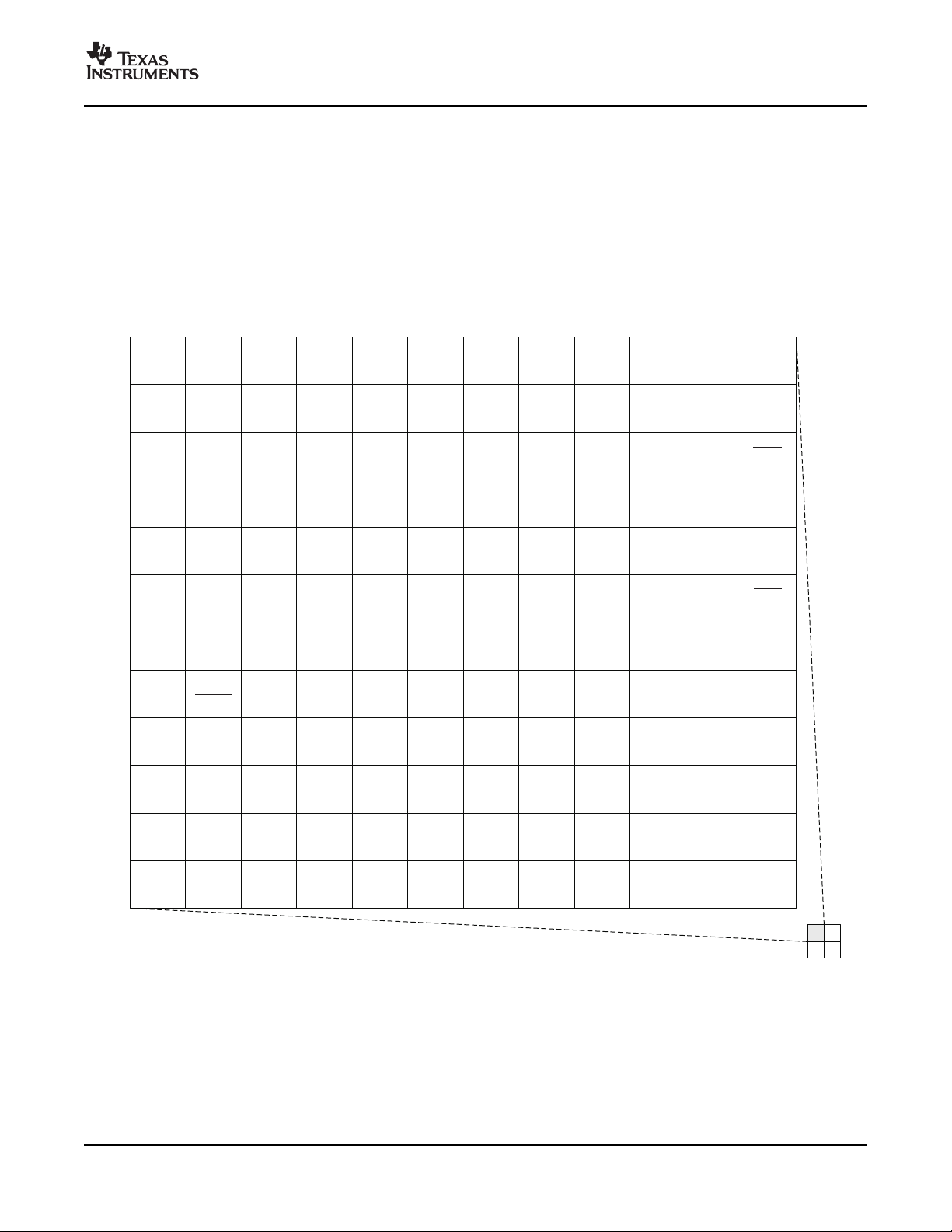

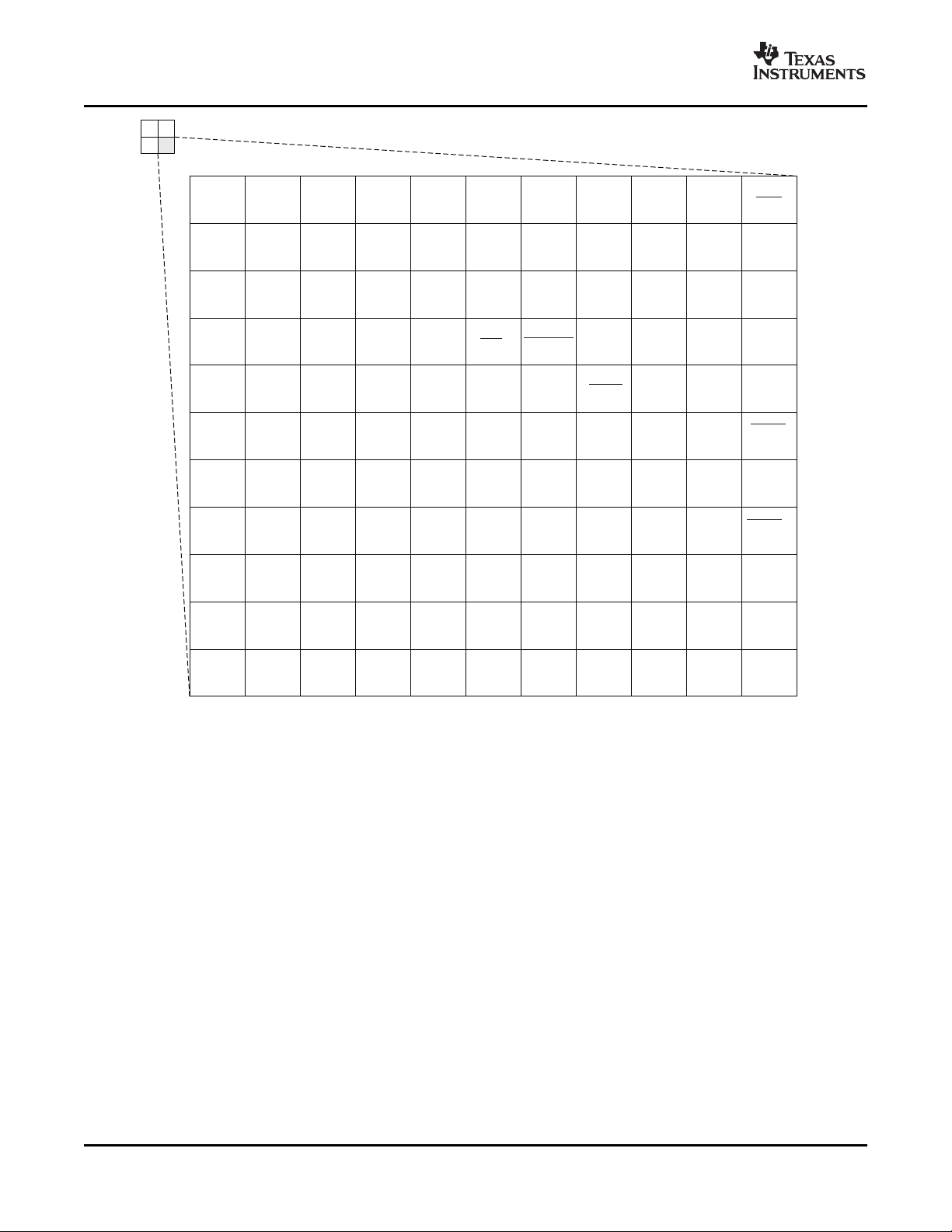

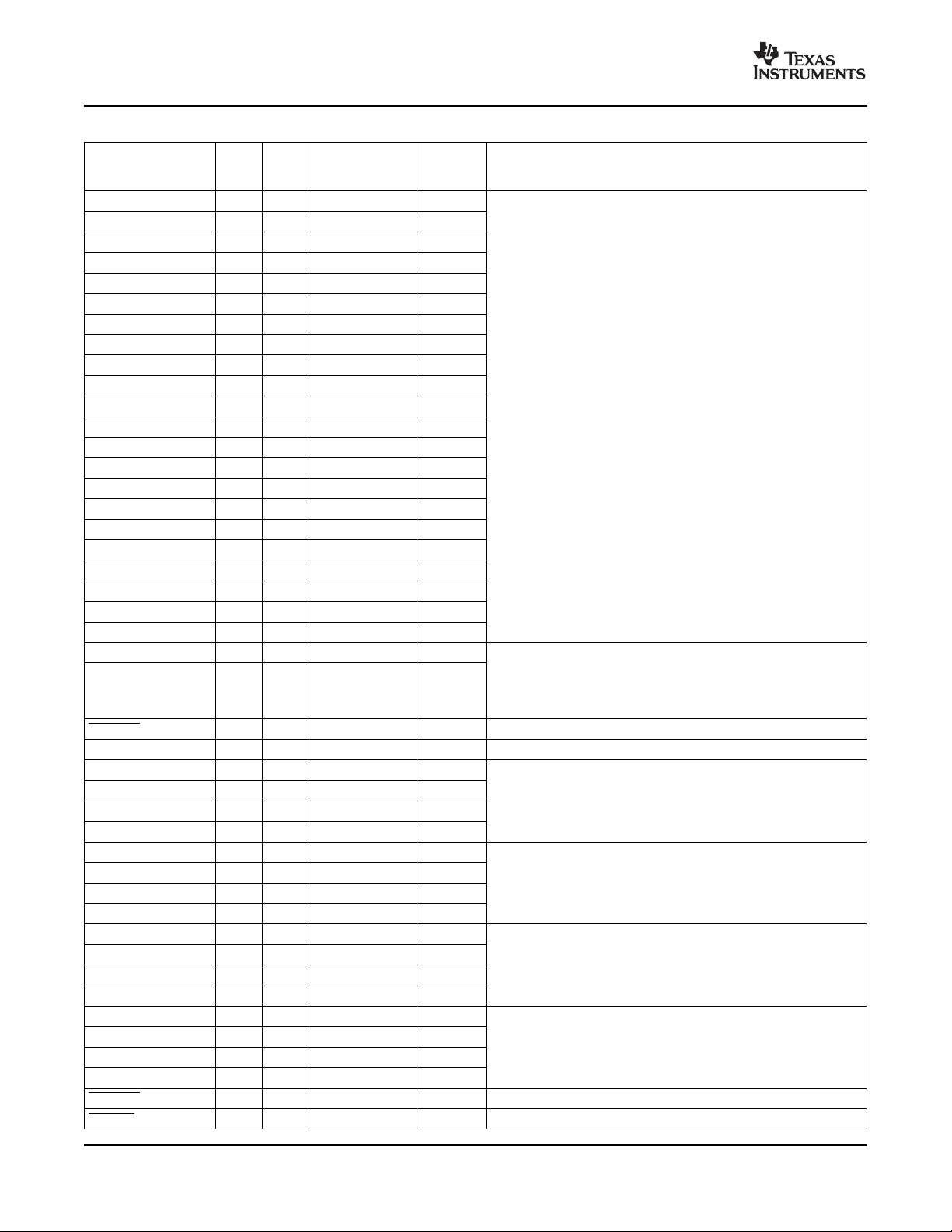

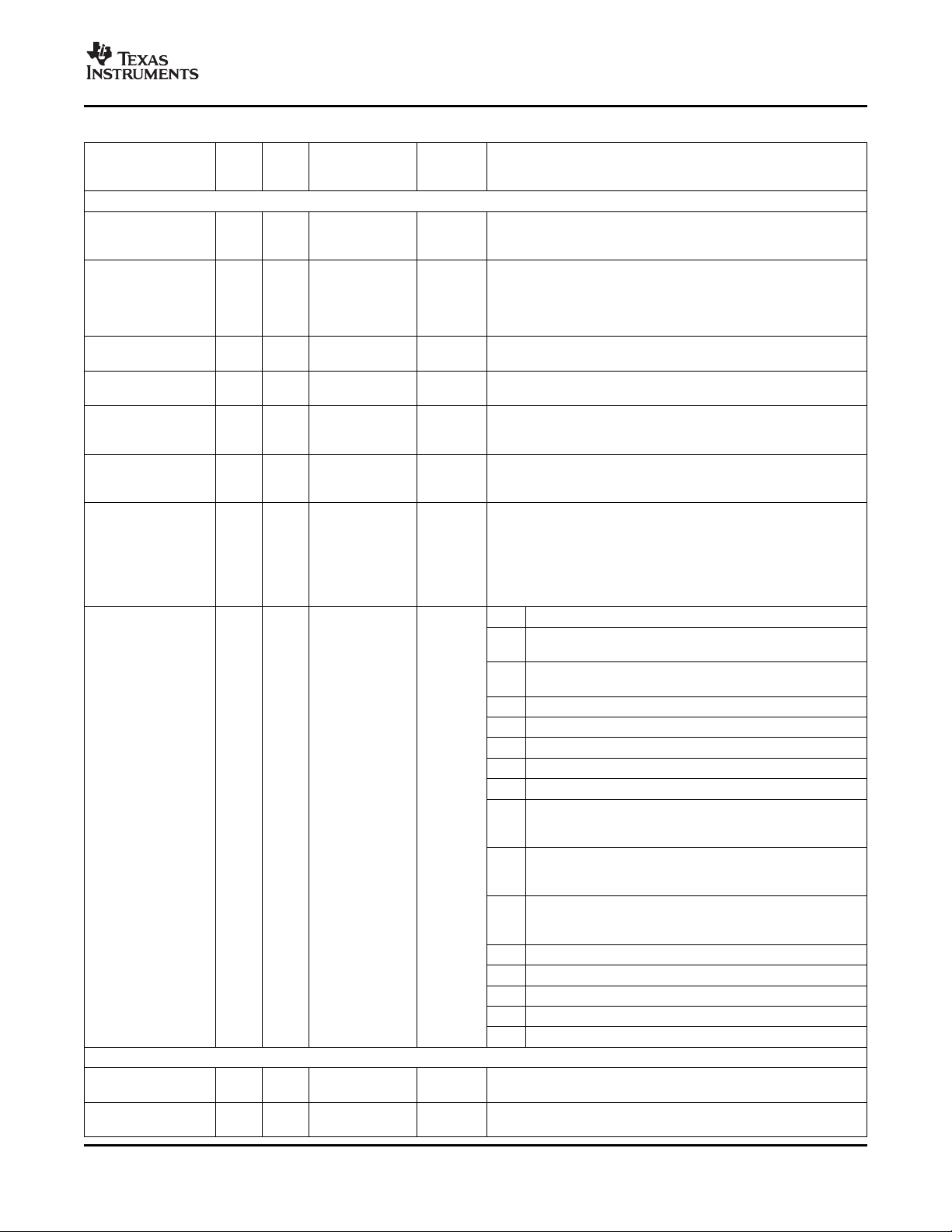

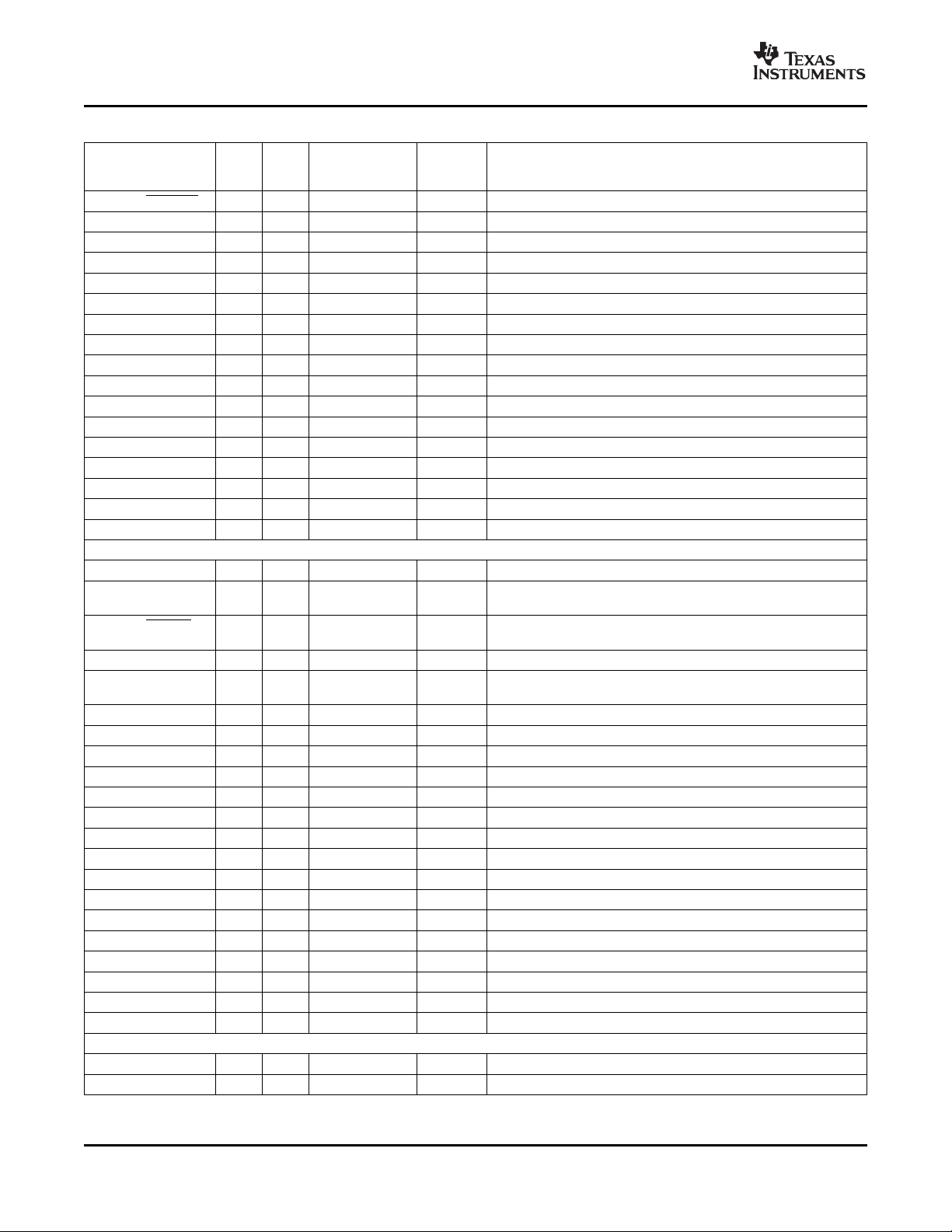

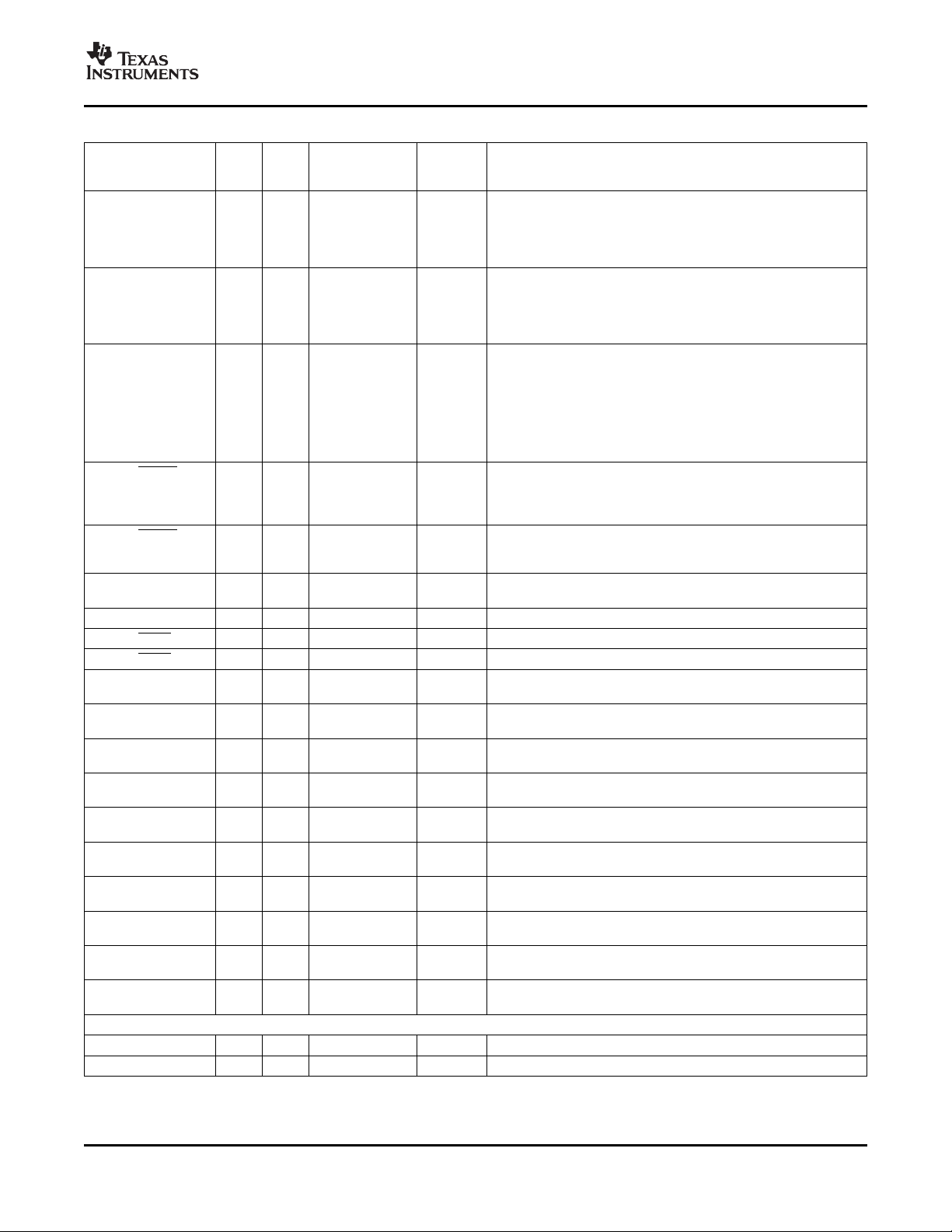

2.5.1 Pin Map (Bottom View)

Figure 2-2 through Figure 2-5 show the bottom view of the ZUT package pin assignments in four

quadrants (A, B, C, and D).

TMS320DM647/TMS320DM648

Digital Media Processor

SPRS372 – MAY 2007

Figure 2-2. ZUT Pin Map [Top Left Quadrant]

Submit Documentation Feedback Device Overview 15

Page 16

www.ti.com

PRODUCT PREVIEW

AD26/

HD26

AD22/

HD22

PCLK/

HHWIL

V

SS

PCBE1

HDS2

/

PIRDY

HRDY

/

AD14/

HD14

PCBE0/

GP04

AD02/

HD02

AD04/

HD04

AD27/

HD27

AD23/

HD23

AD17/

HD17

AD12/

HD12

V

SS

AD08/

HD08

AD05/

HD05

AD01/

HD01

V

SS

AD28/

HD28

PIDSEL/

GP06

GP05

AD18/

HD18

PFRAME

HINT/

PTRDY/

AD15/

HD15

AD13/

HD13

AD09/

HD09

AD06/

HD06

AD00/

HD00

AD03/

HD03

AD29/

HD29

PCBE3/

GP07

AD19/

HD19

AD16/

HD16

PDEVSEL

/HCNTL1

PSTOP

/HCNTL0

AD11/

HD11

AD10/

HD10

AD07/

HD07

VP0CTL0 VP0CLK0

AD30/

HD30

AD24/

HD24

AD20/

HD20

PPERR

HCS

/ PSERR/

HDS1

PPAR/

HAS

VP0D02 VP0D06

V

SS

AD31/

HD31

AD25/

HD25

AD21/

HD21

V

SS

VP0D03

VP0D05 VP0D09

VP0D012/

GP12

VP0CTL1 VP0CLK1

V

SS

V

SS

VP0D04 VP0D08 VP0D16 VP0D18 VP0D17

VP0CTL2

V

SS

V

SS

V

SS

VP0D07

VP0D14/

GP14

VP0D15/

GP15

VP0D13/

GP13

V

SS

V

SS

V

SS

VP0D19

VP1D02/

GP16

VP1D07/

GP21

VP1D06/

GP20

VP1D05/

GP19

VP1CTL0

V

SS

V

SS

V

SS

VP1D04/

GP18

VP1D03/

GP17

VP1D14/

GP26

VP1D13/

GP25

VP1CTL1 VP1CLK0

V

SS

V

SS

VP1D17/

GP29

VP1D12/

GP24

VP1D09/

GP23

VP1D08/

GP22

VP1CTL2 VP1CLK1

V

SS

C

VDD

V

SS

D

VDD33

V

SS

VP1D16/

GP28

VP1D19/

GP31

VP1D15/

GP27

VP1D18/

GP30

V

SS

AC

AB

AA

Y

W

V

U

T

R

P

N

M

13 14 15 16 17 18 19 20 21 22 23

D

VDD33

D

VDD33

D

VDD33

D

VDD33

D

VDD33

D

VDD33

D

VDD33

D

VDD33

D

VDD33

D

VDD33

D

VDD33

PCBE2

HRW

/

PGNT/

GP00

D

VDD33

C

VDD

C

VDD

C

VDD

C

VDD

D

VDD33

C

VDD

C

VDD

TMS320DM647/TMS320DM648

Digital Media Processor

SPRS372 – MAY 2007

Figure 2-3. ZUT Pin Map [Top Right Quadrant]

Device Overview16 Submit Documentation Feedback

Page 17

www.ti.com

VP4CLK0/

AARDY

L

K

J

H

G

F

E

D

C

B

A

1 2 3

4

5

6

7

8 9 10 11

VP4D02/

ABE00

VP4D06/

ACE2

VP4D07/

ACE3

VP4D08/

AEA00

D

VDD33

V

SS

V

SS

V

SS

VP4CLK1

VP4CTL2/

AADS

VP4D09/

AEA01

VP4D12/

AEA02

VP4D14/

AEA04

VP4D13/

AEA03

V

SS

V

SS

VP4CTL1/

ABA1

VP4CTL0/

ABA0

VP4D16/

AEA06

VP4D15/

AEA05

VP4D19/

AEA09

VP4D18/

AEA08

VP4D17/

AEA07

V

SS

C

VDD

V

SS

V

SS

UHPIEN

HPIWIDTH/

AEA16

AEA23

RSV_BOOT/

AEA15

RSV7

C

VDD1

V

SS

EMIB

WIDTH/

AEA22

FASTBOOT

/AEA21

PCI66/

AEA18

V

SS

D

VDD18

V

SS

CLKIN2

DEVICE

ENABLE0/

AEA20

BOOT

MODE3/

AEA14

BOOT

MODE0/

AEA11

BOOT

MODE1/

AEA12

AECLKIN

SEL/

AEA17

BOOT

MODE2/

AEA13

RSV18

V

SS

BBA1

RSV11RSV12

AEA19

D

VDD18

V

SS

BED05

BSDDQM0

BED00

BBA0

BEA12

RSV14

RSV4

BSDDQM1

BSDDQ

GATE1

BED06

BSDDQ

GATE0

V

SS

BSDCAS BSDWE

V

SS

RSV10

V

SS

BED11

BED09

BED07

BED03

BED01

V

REFSSTL

BEA06

BED12

BED15

BED10

BED08

BED04

BED02

RSV15

BSDCKE

BBA2

V

SS

RSV20

BED13

BED14

V

SS

BSDDQS1N BSDDQS1P BSDDQS0N BSDDQS0P

A

VDLL1

BECLKOUTP

BECLKOUTN

12

BEA08

D

VDD18

C

VDD

C

VDD

C

VDD

C

VDD

D

VDD33

V

SS

D

VDD33

V

SS

C

VDD

RSV8

D

VDD33

PLLV2

D

VDD18

D

VDD18

V

SS

D

VDD18

BCE

BEA13

RSV13

BSDRAS

RSV3

RSV6 RSV5

RSV19

D

VDD18

D

VDD18

D

VDD18

V

DD18MON

D

VDD18

TMS320DM647/TMS320DM648

Digital Media Processor

SPRS372 – MAY 2007

Submit Documentation Feedback Device Overview 17

Figure 2-4. ZUT Pin Map [Bottom Left Quadrant]

Page 18

www.ti.com

PRODUCT PREVIEW

V

CCMON

D

VDD18

D

VDD33

L

K

J

H

G

F

E

D

C

B

A

13 14 15 16 17 18 19 20 21 22 23

C

VDD

V

SS

V

SS

EMU4

RSV2 TMS

TRST

V

SS

V

SS

V

SS

EMU11

EMU9

EMU3

EMU2 EMU1 EMU0

C

VDD1

V

SS

V

SS

RESET

EMU6

EMU5

TDI

TDO

V

SS

V

SS

V

SS

V

DD33MON

RESETSTAT

EMU8EMU10

EMU7

TCLK

V

SS

V

SS

V

SS

NMI

POR

V

SS

SPIDI/

UARTRTS

BEODT1

BEA02

V

SS

V

SS

SPICS2/

UARTRX

SPICLK

SPIDO/

UART/

CTS

BEODT0

BEA03

BSDDQM2

BED19

BED23

BSDDQ

GATE2

BED31

SPICS1/

UARTTX

SDA0

V

SS

BEA04 BEA00 BED18

BED22

BED25

BED28

V

SS

SCL0

T1INP12/

GP10

T1OUT12/

GP11

BEA05 BEA01

BED17 BED21 BED24 BED27

BED30

T0INP12/

GP08

T0OUT12/

GP09

BEA09

BED16 BED20 BED26

BED29

BSDDQ

GATE3

RSV16

BEA10

BEA11

BEA07

V

SS

BSDDQS2N

BSDDQS2P

V

SS

BSDDQS3N BSDDQS3P

BSDDQM3

A

VDLL2

V

SS

C

VDD

RSV1

C

VDD

D

VDD33

C

VDD

D

VDD33

D

VDD33

D

VDD33

D

VDD18

D

VDD18

D

VDD18

D

VDD33

D

VDD18

V

SS

D

VDD18

D

VDD18

D

VDD33

D

VDD33

D

VDD18

D

VDD18

D

VDD18

D

VDD18

D

VDD18

TMS320DM647/TMS320DM648

Digital Media Processor

SPRS372 – MAY 2007

18 Device Overview Submit Documentation Feedback

Figure 2-5. ZUT Pin Map [Bottom Right Quadrant]

Page 19

www.ti.com

2.6 Terminal Functions

TMS320DM647/TMS320DM648

Digital Media Processor

SPRS372 – MAY 2007

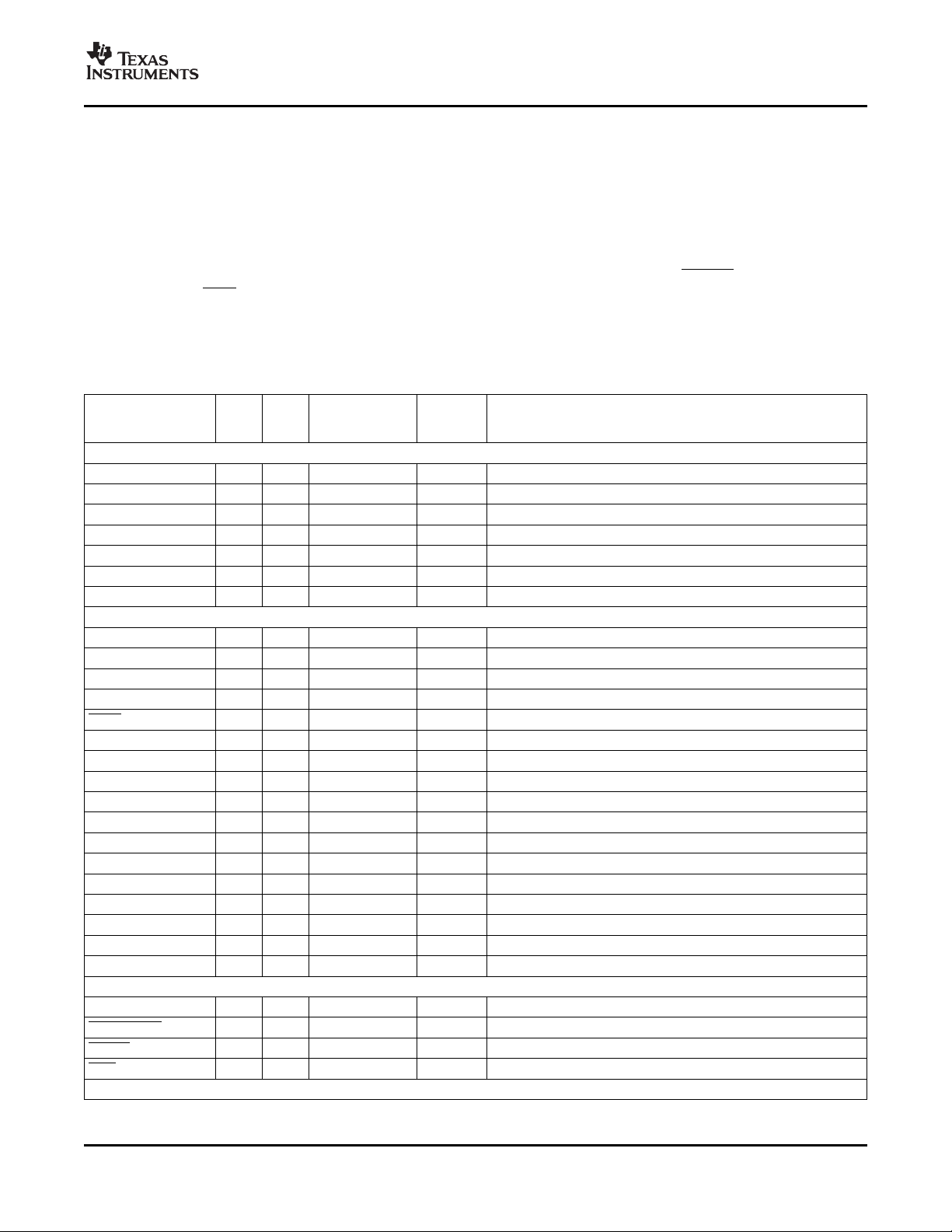

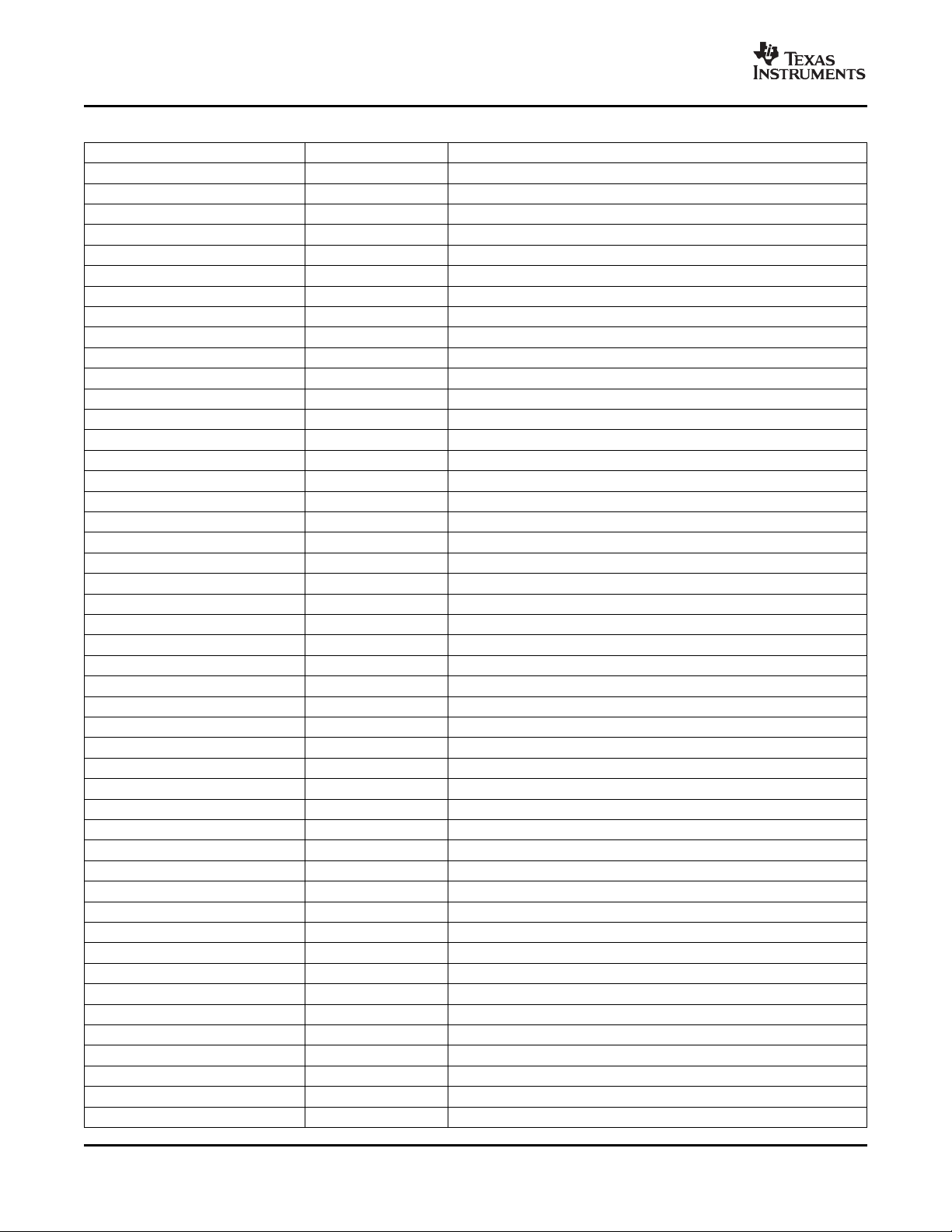

The terminal functions tables (Table 2-4 through Table 2-5 ) identify the external signal names, the

associated pin (ball) numbers along with the mechanical package designator, the pin type, whether the pin

has any internal pullup or pulldown resistors, and a functional pin description. For more detailed

information on device configuration, peripheral selection, multiplexed/shared pin, and debugging

considerations, see Section 3 .

All device boot and configuration pins are multiplexed with functional pins. These pins function as device

boot and configuration pins only during device reset. When both the reset pin ( RESET) and the power-on

reset pin ( POR) are deasserted, the input states of these multiplexed device boot and configuration pins

are sampled and latched into the BOOTCFG register. For proper device operation, these pins must be

pulled up/down to the desired value via an external resistor.

Table 2-4. TERMINAL FUNCTIONS

TERMINAL NAME NO TYPE INTERNAL OPER DESCRIPTION

CLKIN1 M1 I IPD 3.3 V Clock Input for PLL1

CLKIN2 F1 I IPD 3.3 V Clock Input for PLL2

REFCLKN AC11 I Differential Reference Clock input (negative) for SGMII

REFCLKP AB11 I Differential Reference Clock input (positive) for SGMII

PLLV1 N3 A 1.8 V 1.8-V I/O Supply Voltage for PLL1

PLLV2 G7 A 1.8 V 1.8-V I/O Supply Voltage for PLL2

SYSCLK4 M3 I/O/Z IPD 3.3 V Clock out of device speed/4

TCLK H23 I IPU 3.3 V JTAG Test Port Clock

TDI J22 I IPU 3.3 V JTAG Test Port Data In

TDO J23 OZ IPU 3.3 V JTAG Test Port Data Out

TMS L22 I IPU 3.3 V JTAG Test Port Mode Select

TRST L23 I IPD 3.3 V JTAG Test Port Reset

EMU0 K23 I/O/Z IPU 3.3 V JTAG Test Port Emulation 0

EMU1 K22 I/O/Z IPU 3.3 V JTAG Test Port Emulation 1

EMU2 K21 I/O/Z IPU 3.3 V JTAG Test Port Emulation 2

EMU3 K20 I/O/Z IPU 3.3 V JTAG Test Port Emulation 3

EMU4 L18 I/O/Z IPU 3.3 V JTAG Test Port Emulation 4

EMU5 J21 I/O/Z IPU 3.3 V JTAG Test Port Emulation 5

EMU6 K19 I/O/Z IPU 3.3 V JTAG Test Port Emulation 6

EMU7 H21 I/O/Z IPU 3.3 V JTAG Test Port Emulation 7

EMU8 J20 I/O/Z IPU 3.3 V JTAG Test Port Emulation 8

EMU9 H20 I/O/Z IPU 3.3 V JTAG Test Port Emulation 9

EMU10 J19 I/O/Z IPU 3.3 V JTAG Test Port Emulation 10

EMU11 K18 I/O/Z IPU 3.3 V JTAG Test Port Emulation 11

NMI J18 I IPD 3.3 V Non maskable Interrupt

RESETSTAT H19 O 3.3 V Reset Status Pin

RESET G20 I 3.3 V Device Reset

POR H18 I 3.3 V Power On Reset

HOST-PORT INTERFACE (HPI) or PERIPHERAL COMPONENT INTERCONNECT (PCI) or GPIO[0:7]

PULLUP/ VOLT

PULLDOWN

Clock/PLL Configuration

JTAG

RESET/INTERRUPTS

Submit Documentation Feedback Device Overview 19

Page 20

www.ti.com

PRODUCT PREVIEW

TMS320DM647/TMS320DM648

Digital Media Processor

SPRS372 – MAY 2007

TERMINAL NAME NO TYPE INTERNAL OPER DESCRIPTION

AD00/HD00 AA22 I/O/Z IPD 3.3 V Host Port data [15:00] pin or PCI data-address bus [15:00]

AD01/HD01 AB22 I/O/Z IPD 3.3 V

AD02/HD02 AC21 I/O/Z IPD 3.3 V

AD03/HD03 AA23 I/O/Z IPD 3.3 V

AD04/HD04 AC22 I/O/Z IPD 3.3 V

AD05/HD05 AB21 I/O/Z IPD 3.3 V

AD06/HD06 AA21 I/O/Z IPD 3.3 V

AD07/HD07 Y21 I/O/Z IPD 3.3 V

AD08/HD08 AB20 I/O/Z IPD 3.3 V

AD09/HD09 AA20 I/O/Z IPD 3.3 V

AD10/HD10 Y20 I/O/Z IPD 3.3 V

AD11/HD11 Y19 I/O/Z IPD 3.3 V

AD12/HD12 AB18 I/O/Z IPD 3.3 V

AD13/HD13 AA19 I/O/Z IPD 3.3 V

AD14/HD14 AC18 I/O/Z IPD 3.3 V

AD15/HD15 AA18 I/O/Z IPD 3.3 V

AD16/HD16 Y16 I/O/Z IPD 3.3 V Host Port data [31:16] pin or PCI data-address bus [31:16]

AD17/HD17 AB15 I/O/Z IPD 3.3 V

AD18/HD18 AA15 I/O/Z IPD 3.3 V

AD19/HD19 Y15 I/O/Z IPD 3.3 V

AD20/HD20 W15 I/O/Z IPD 3.3 V

AD21/HD21 V15 I/O/Z IPD 3.3 V

AD22/HD22 AC14 I/O/Z IPD 3.3 V

AD23/HD23 AB14 I/O/Z IPD 3.3 V

AD24/HD24 W14 I/O/Z IPD 3.3 V

AD25/HD25 V14 I/O/Z IPD 3.3 V

AD26/HD26 AC13 I/O/Z IPD 3.3 V

AD27/HD27 AB13 I/O/Z IPD 3.3 V

AD28/HD28 AA13 I/O/Z IPD 3.3 V

AD29/HD29 Y13 I/O/Z IPD 3.3 V

AD30/HD30 W13 I/O/Z IPD 3.3 V

AD31/HD31 V13 I/O/Z IPD 3.3 V

PPAR/ HAS W19 I/O/Z IPU 3.3 V Host address strobe (I) or PCI parity [default]

PSTOP/HCNTL0 Y18 I/O/Z IPD 3.3 V Host Control selects between control, address, or data registers (I)

PDEVSEL/HCNTL1 Y17 I/O/Z IPD 3.3 V Host Control selects between control, address, or data registers (I)

PPERR/ HCS W17 I/O/Z IPU 3.3 V Host chip select (I) or PCI parity error [default]

PSERR/ HDS1 W18 I/O/Z IPU 3.3 V Host data strobe 1 (I) or PCI system error [default]

PCBE0/GP04 AC20 I/O/Z IPU 3.3 V PCI command/byte enable 0 or GP[2] [default

PCBE1/ HDS2 AC17 I IPU 3.3 V PCI command/byte enable 1 or host data strobe 2

PCBE2/ HRW W16 I/O/Z IPU 3.3 V PCI command/byte enable 2 or host read or write select (I)

PCBE3/GP07 Y14 I/O/Z IPU 3.3 V PCI command/byte enable 3 or GPIO[7]

PCLK/HHWIL AC15 I/O/Z IPU 3.3 V PCI clock (I) [default] or host half-word select - first or second

PFRAME/ HINT AA16 I/O/Z IPD 3.3 V PCI frame or host interrupt from DSP to host (O/Z)

Table 2-4. TERMINAL FUNCTIONS (continued)

PULLUP/ VOLT

PULLDOWN

[default]

[default]

or PCI Stop [default]

or PCI Device Select [default]

half-word (not necessarily high or low order) [For HPI16 bus width

selection only] (I)

Device Overview20 Submit Documentation Feedback

Page 21

www.ti.com

TMS320DM647/TMS320DM648

Digital Media Processor

SPRS372 – MAY 2007

Table 2-4. TERMINAL FUNCTIONS (continued)

TERMINAL NAME NO TYPE INTERNAL OPER DESCRIPTION

PIRDY/ HRDY AB17 I/O/Z IPD 3.3 V PCI initiator ready [default] or host ready from DSP to host (O/Z)

PGNT/GP00 U13 I/O/Z IPD 3.3 V PCI bus grant (I) or GPIO[0]

PRST/GP01 U12 I/O/Z IPD 3.3 V PCI Reset (I) or GPIO[1]

PINTA/GP02 V12 I/O/Z IPD 3.3 V PCI Interrupt A (O/Z) or GPIO[2]

PREQ/GP03 AA12 I/O/Z IPD 3.3 V PCI bus request (O/Z) or GPIO[3]

PTRDY/GP05 AA17 I/O/Z IPD 3.3 V PCI target ready or GPIO[5]

PIDSEL/GP06 AA14 I/O/Z IPD 3.3 V PCI Initialization device select (I) or GPIO[6]

BBA0 C12 I/O/Z 1.8 V DDR2 Memory Controller Bank Address Control

BBA1 B12 I/O/Z 1.8 V

BBA2 E11 I/O/Z 1.8 V

BCE F9 I/O/Z 1.8 V DDR2 Memory Controller Memory Space Enable

BEA00 D15 I/O/Z 1.8 V DDR2 Memory Controller External Address

BEA01 C15 I/O/Z 1.8 V

BEA02 F13 I/O/Z 1.8 V

BEA03 E14 I/O/Z 1.8 V

BEA04 D14 I/O/Z 1.8 V

BEA05 C14 I/O/Z 1.8 V

BEA06 F11 I/O/Z 1.8 V

BEA07 B14 I/O/Z 1.8 V

BEA08 F12 I/O/Z 1.8 V

BEA09 D13 I/O/Z 1.8 V

BEA10 A13 I/O/Z 1.8 V

BEA11 B13 I/O/Z 1.8 V

BEA12 E12 I/O/Z 1.8 V

BEA13 F10 I/O/Z 1.8 V

BECLKOUTN A12 I/O/Z 1.8 V DDR2 Memory Controller Output Clock (CLKIN2 frequency x 10)

BECLKOUTP A11 I/O/Z 1.8 V Negative DDR2 Memory Controller Output Clock (CLKIN2

BED00 E9 I/O/Z 1.8 V DDR2 Memory Controller External Data

BED01 C9 I/O/Z 1.8 V

BED02 B9 I/O/Z 1.8 V

BED03 C8 I/O/Z 1.8 V

BED04 E8 I/O/Z 1.8 V

BED05 D8 I/O/Z 1.8 V

BED06 C7 I/O/Z 1.8 V

BED07 E7 I/O/Z 1.8 V

BED08 C6 I/O/Z 1.8 V

BED09 B7 I/O/Z 1.8 V

PULLUP/ VOLT

PULLDOWN

DDR2 MEMORY CONTROLLER

frequency x 10)

Submit Documentation Feedback Device Overview 21

Page 22

www.ti.com

PRODUCT PREVIEW

TMS320DM647/TMS320DM648

Digital Media Processor

SPRS372 – MAY 2007

TERMINAL NAME NO TYPE INTERNAL OPER DESCRIPTION

BED10 D6 I/O/Z 1.8 V DDR2 Memory Controller External Data (continued)

BED11 A3 I/O/Z 1.8 V

BED12 B3 I/O/Z 1.8 V

BED13 A4 I/O/Z 1.8 V

BED14 B4 I/O/Z 1.8 V

BED15 C5 I/O/Z 1.8 V

BED16 B16 I/O/Z 1.8 V

BED17 C16 I/O/Z 1.8 V

BED18 D16 I/O/Z 1.8 V

BED19 E16 I/O/Z 1.8 V

BED20 B17 I/O/Z 1.8 V

BED21 C17 I/O/Z 1.8 V

BED22 D17 I/O/Z 1.8 V

BED23 E17 I/O/Z 1.8 V

BED24 C18 I/O/Z 1.8 V

BED25 D18 I/O/Z 1.8 V

BED26 B19 I/O/Z 1.8 V

BED27 C19 I/O/Z 1.8 V

BED28 B20 I/O/Z 1.8 V

BED29 D19 I/O/Z 1.8 V

BED30 C20 I/O/Z 1.8 V

BED31 E19 I/O/Z 1.8 V

BEODT0 E13 I/O/Z 1.8 V On-die termination signals to external DDR2 SDRAM. These pins

BEODT1 A14 I/O/Z 1.8 V

BSDCAS D10 I/O/Z 1.8 V DDR2 Memory Controller SDRAM column address strobe

BSDCKE B11 I/O/Z 1.8 V DDR2 Memory Controller SDRAM clock-enable

BSDDQGATE0 D7 I/O/Z 1.8 V DDR2 Memory Controller data strobe Gate

BSDDQGATE1 B6 I/O/Z 1.8 V

BSDDQGATE2 E18 I/O/Z 1.8 V

BSDDQGATE3 A21 I/O/Z 1.8 V

BSDDQM0 B8 I/O/Z 1.8 V DDR2 Memory Controller byte-enable controls. Decoded from the

BSDDQM1 D5 I/O/Z 1.8 V

BSDDQM2 E15 I/O/Z 1.8 V

BSDDQM3 B21 I/O/Z 1.8 V

BSDDQS0P A9 I/O/Z 1.8 V DDR2 Memory Controller data strobe [3:0]

BSDDQS1P A7 I/O/Z 1.8 V

BSDDQS2P A17 I/O/Z 1.8 V

BSDDQS3P A20 I/O/Z 1.8 V

BSDDQS0N A8 I/O/Z 1.8 V DDR2 Memory Controller data strobe [3:0] negative

BSDDQS1N A6 I/O/Z 1.8 V

BSDDQS2N A16 I/O/Z 1.8 V

BSDDQS3N A19 I/O/Z 1.8 V

BSDRAS E10 I/O/Z 1.8 V DDR2 Memory Controller SDRAM row address strobe

BSDWE D11 I/O/Z 1.8 V DDR2 Memory Controller SDRAM write enable

Table 2-4. TERMINAL FUNCTIONS (continued)

PULLUP/ VOLT

PULLDOWN

are reserved for future use and should not be connected to the

DDR2 SDRAM.

Note: There are no on-die termination resistors implemented on

the DM647/DM648DSP die.

low-order address bits. The number of address bits or byte

enables used depends on the width of external memory. Byte-write

enables for most types of memory. Can be directly connected to

SDRAM read and write mask signal (SDQM).

Device Overview22 Submit Documentation Feedback

Page 23

www.ti.com

TMS320DM647/TMS320DM648

Digital Media Processor

SPRS372 – MAY 2007

Table 2-4. TERMINAL FUNCTIONS (continued)

TERMINAL NAME NO TYPE INTERNAL OPER DESCRIPTION

DEVICEENABLE0/AE F2 I/O/Z IPD 3.3 V EMIFA External Address 20 (word address) (O/Z) For proper

A20 device operation, this pin must be externally pulled up with a 1-k Ω

EMIFAWIDTH/AEA22 G3 I/O/Z IPD 3.3 V EMIFA External Address 22 (word address) (O/Z) EMIFA data bus

FASTBOOT/AEA21 G2 I/O/Z IPD 3.3 V EMIFA External Address 22 (word address) (O/Z) Enables FAST

UHPIEN H2 I IPD 3.3 V UHPI enable pin. This pin controls the selection (enable/disable) of

HPIWIDTH/AEA16 H3 I/O/Z IPD 3.3 V EMIFA External Address 16 (word address) (O/Z) HPI peripheral

RSVBOOT/AEA15 H6 I/O/Z IPU 3.3 V EMIFA External Address 15 (word address) (O/Z) For proper

PCI66/AEA18 G5 I/O/Z IPD 3.3 V PCI Frequency Selection (PCI66). The PCI peripheral must be

BOOTMODE0/AEA11 F3 I/O/Z IPD 3.3 V 0000 Master mode - Emulation Boot

BOOTMODE1/AEA12 F4

BOOTMODE2/AEA13 F5

BOOTMODE3/AEA14 G6

SCL0 D22 I/O/Z 3.3 V I2C clock. When the I2C module is used, use an external pullup

SDA0 C23 I/O/Z 3.3 V I2C data. When I2C is used, make certain there is an external

PULLUP/ VOLT

PULLDOWN

CONFIGURATION AND EMIFA

resistor at device reset

width selection pin state captured at the rising edge of RESET.

0 sets EMIFA CS2 to 8 bit data bus width

1 sets EMIFA CS2 to 16 bit data bus width. For details. see

Section 3 .

BOOT of the device. For details see Section 3 .

the HPI and GPIO[0:7] muxed with PCI. For details see Section 3 .

bus width (HPI_WIDTH) select [Applies only when HPI is enabled;

UHPIEN pin = 1]

device operation, this pin must be externally pulled up with a 1-k Ω

resistor at device reset

enabled (UHPIEN = 0) to use this function.PCI66_AEA18 selects

the PCI operating frequency of 66 MHz or 33 MHz. PCI operating

frequency is selected at reset via the pullup/pulldown resistor on

the PCI66 pin:AEA18:

0 - PCI operates at 33 MHz (default)

1 - PCI operates at 66 MHz.

0001 Slave mode - HPI Boot (if UHPIEN = 1)

or PCI Boot (if UHPIEN = 0) without auto-initialization

0010 Slave mode - HPI Boot (if UHPIEN = 1)

or PCI Boot (if UHPIEN = 0) with auto-initialization

0011 Master mode - UART boot without flow control

0100 Master mode - EMIFA CS2 direct/fast boot

0101 Master mode - I2C boot

0110 Master mode - SPI boot

0111 Reserved

1000 Master mode - 3-port Ethernet Subsystem boot through

SGMII0 for DM647 only

Reserved in DM648

1001 Master mode - 3-port Ethernet Subsystem boot through

SGMII0 for DM648 only

Reserved in DM647

1010 Master mode - 3-port Ethernet Subsystem boot through

SGMII1 for DM648 only

Reserved in DM647

1011 Reserved

1100 Reserved

1101 Reserved

1110 Master mode - UART boot with flow control

1111 Reserved

INTER-INTEGRATED CIRCUIT (I2C)

resistor.

pullup resistor.

Submit Documentation Feedback Device Overview 23

Page 24

www.ti.com

PRODUCT PREVIEW

TMS320DM647/TMS320DM648

Digital Media Processor

SPRS372 – MAY 2007

TERMINAL NAME NO TYPE INTERNAL OPER DESCRIPTION

SGMII0RXN AA10 I 1.2 V Differential SGMII port 0 RX input (negative)

SGMII0RXP AA9 I 1.2 V Differential SGMII port 0 RX input (positive)

SGMII0TXN W11 O 1.2 V Differential SGMII port 0 TX output (negative)

SGMII0TXP Y11 O 1.2 V Differential SGMII port 0 TX output (positive)

SGMII1RXN AC9 I 1.2 V Differential SGMII port 1 RX input (negative)

SGMII1RXP AB9 I 1.2 V Differential SGMII port 1 RX input (positive)

SGMII1TXN W9 O 1.2 V Differential SGMII port 1 TX output (negative)

SGMII1TXP W8 O 1.2 V Differential SGMII port 1 TX output (positive)

MDCLK U9 OZ IPD 3.3 V MDIO serial clock (MDCLK)

MDIO U8 I/O/Z IPU 3.3 V MDIO serial data (MDIO)

SPICLK F22 I/O/Z IPU 3.3 V SPI clock output

SPICS1/UARTTX D23 I/O/Z IPU 3.3 V SPI chip select 1 or UART transmit (O/Z)

SPICS2/UARTRX F23 I/O/Z IPU 3.3 V SPI chip select 2 or UART receive

SPIDI/UARTRTS G23 I/O/Z IPU 3.3 V SPI data input or UART ready to send (O/Z)

SPIDO/UARTCTS F21 I/O/Z IPU 3.3 V SPI data output or UART clear to send

T0INP12/GP08 E20 I/O/Z IPD 3.3 V Timer 0 input pin for lower 32-bit counter (I) or GPIO 8

T0OUT12/GP09 D21 I/O/Z IPD 3.3 V Timer 0 output pin for lower 32-bit counter (O/Z) or GPIO 9

T1INP12/GP10 E21 I/O/Z IPD 3.3 V Timer 1 input pin for lower 32-bit counter (I) or GPIO 10

T1OUT12/GP11 C22 I/O/Z IPD 3.3 V Timer 1 output pin for lower 32-bit counter(O/Z) or GPIO 11

AHCLKR AC4 I/O/Z IPD 3.3 V McASP receive high-frequency master clock

AHCLKX AC3 I/O/Z IPD 3.3 V McASP transmit high-frequency master clock

ACLKR AC6 I/O/Z IPD 3.3 V McASP receive master clock

ACLKX AC7 I/O/Z IPD 3.3 V McASP transmit master clock

AFSR W6 I/O/Z IPD 3.3 V McASP receive frame sync or left/right clock (LRCLK)

AFSX AA7 I/O/Z IPD 3.3 V McASP transmit frame sync or left/right clock (LRCLK)

AXR0 AB6 I/O/Z IPD 3.3 V McASP data pin [0:7]

AXR1 Y6 IPD 3.3 V

AXR2 AA6 IPD 3.3 V

AXR3 AB4 IPD 3.3 V

AXR4 Y5 IPD 3.3 V

AXR5 V7 IPD 3.3 V

AXR6 AA4 IPD 3.3 V

AXR7 V6 IPD 3.3 V

STCLK/AXR8 Y7 I/O/Z IPD 3.3 V The STCLK signal drives the hardware counter for use by the

VDAC/AXR9 AA5 I/O/Z IPD 3.3 V VCXO Interpolated Control Port (VIC) single-bit digital-to-analog

AMUTEIN AB3 I/O/Z IPD 3.3 V McASP mute input

AMUTE U7 I/O/Z IPD 3.3 V McASP mute output (O/Z).

VP0CLK0 Y23 I IPU 3.3 V Video Port 0 Clock 0 (I)

VP0CLK1 V23 I/O/Z IPU 3.3 V Video Port 0 Clock 1

Table 2-4. TERMINAL FUNCTIONS (continued)

PULLUP/ VOLT

PULLDOWN

SGMII0/1 and MDIO

SPI or UART

TIMER 0/1 or GPIO[8:11]

MCASP OR VIDEO PORT OR VIC

video ports (I) or McASP data pin 8.

converter(VDAC) output (O) or McASP data pin 9

VIDEO PORT 0 OR GPIO[12:15]

Device Overview24 Submit Documentation Feedback

Page 25

www.ti.com

TMS320DM647/TMS320DM648

Table 2-4. TERMINAL FUNCTIONS (continued)

TERMINAL NAME NO TYPE INTERNAL OPER DESCRIPTION

PULLUP/ VOLT

PULLDOWN

VP0CTL0 Y22 I/O/Z IPU 3.3 V Video Port 0 Control 0

VP0CTL1 V22 I/O/Z IPU 3.3 V Video Port 0 Control 1

VP0CTL2 U23 I/O/Z IPU 3.3 V Video Port 0 Control 2

VP0D02 W20 I/O/Z IPD 3.3 V Video Port 0 Data 2

VP0D03 V18 I/O/Z IPD 3.3 V Video Port 0 Data 3

VP0D04 U18 I/O/Z IPD 3.3 V Video Port 0 Data 4

VP0D05 V19 I/O/Z IPD 3.3 V Video Port 0 Data 5

VP0D06 W21 I/O/Z IPD 3.3 V Video Port 0 Data 6

VP0D07 T18 I/O/Z IPD 3.3 V Video Port 0 Data 7

VP0D08 U19 I/O/Z IPD 3.3 V Video Port 0 Data 8

VP0D09 V20 I/O/Z IPD 3.3 V Video Port 0 Data 9

VP0D12/GP12 V21 I/O/Z IPD 3.3 V Video Port 0 Data 12 or GPIO 12

VP0D13/GP13 T19 I/O/Z IPD 3.3 V Video Port 0 Data 13 or GPIO 13

VP0D14/GP14 T20 I/O/Z IPD 3.3 V Video Port 0 Data 14 or GPIO 14

VP0D15/GP15 T21 I/O/Z IPD 3.3 V Video Port 0 Data 15 or GPIO 15

VP0D16 U20 I/O/Z IPD 3.3 V Video Port 0 Data 16

VP0D17 U22 I/O/Z IPD 3.3 V Video Port 0 Data 17

VP0D18 U21 I/O/Z IPD 3.3 V Video Port 0 Data 18

VP0D19 R18 I/O/Z IPD 3.3 V Video Port 0 Data 19

VIDEO PORT 1 OR GPIO[16:31]

VP1CLK0 P23 I IPU 3.3 V Video Port 1 Clock 0

VP1CLK1 N23 I/O/Z IPU 3.3 V Video Port 1 Clock 1

VP1CTL0 R23 I/O/Z IPU 3.3 V Video Port 1 Control 0

VP1CTL1 P22 I/O/Z IPU 3.3 V Video Port 1 Control 1

VP1CTL2 N22 I/O/Z IPU 3.3 V Video Port 1 Control 2

VP1D02/GP16 R19 I/O/Z IPD 3.3 V Video Port 1 Data 2 or GPIO 16

VP1D03/GP17 P19 I/O/Z IPD 3.3 V Video Port 1 Data 3 or GPIO 17

VP1D04/GP18 P18 I/O/Z IPD 3.3 V Video Port 1 Data 4 or GPIO 18

VP1D05/GP19 R22 I/O/Z IPD 3.3 V Video Port 1 Data 5 or GPIO 19

VP1D06/GP20 R21 I/O/Z IPD 3.3 V Video Port 1 Data 6 or GPIO 20

VP1D07/GP21 R20 I/O/Z IPD 3.3 V Video Port 1 Data 7 or GPIO 21

VP1D08/GP22 N21 I/O/Z IPD 3.3 V Video Port 1 Data 8 or GPIO 22

VP1D09/GP23 N20 I/O/Z IPD 3.3 V Video Port 1 Data 9 or GPIO 23

VP1D12/GP24 N19 I/O/Z IPD 3.3 V Video Port 1 Data 12 or GPIO 24

VP1D13/GP25 P21 I/O/Z IPD 3.3 V Video Port 1 Data 13 or GPIO 25

VP1D14/GP26 P20 I/O/Z IPD 3.3 V Video Port 1 Data 14 or GPIO 26

VP1D15/GP27 M20 I/O/Z IPD 3.3 V Video Port 1 Data 15 or GPIO 27

VP1D16/GP28 M18 I/O/Z IPD 3.3 V Video Port 1 Data 16 or GPIO 28

VP1D17/GP29 N18 I/O/Z IPD 3.3 V Video Port 1 Data 17 or GPIO 29

VP1D18/GP30 M21 I/O/Z IPD 3.3 V Video Port 1 Data 18 or GPIO 30

VP1D19/GP31 M19 I/O/Z IPD 3.3 V Video Port 1 Data 19 or GPIO 31

VIDEO PORT 2 OR VLYNQ

VP2CLK0 AB1 I IPU 3.3 V Video Port 2 Clock 0 (I)

VP2CLK1/VCLK W1 I/O/Z IPU 3.3 V Video Port 2 Clock 1 or VLYNQ Clock (I/O)

VP2CTL0 AA1 I/O/Z IPU 3.3 V Video Port 2 Control 0

VP2CTL1 AB2 I/O/Z IPU 3.3 V Video Port 2 Control 1

Digital Media Processor

SPRS372 – MAY 2007

Submit Documentation Feedback Device Overview 25

Page 26

www.ti.com

PRODUCT PREVIEW

TMS320DM647/TMS320DM648

Digital Media Processor

SPRS372 – MAY 2007

TERMINAL NAME NO TYPE INTERNAL OPER DESCRIPTION

VP2CTL2/ VSCRUN Y1 I/O/Z IPU 3.3 V Video Port 2 Control 2 or VLYNQ serial clock run request (I/O)

VP2D02 W5 I/O/Z IPD 3.3 V Video Port 2 Data 2

VP2D03 AA2 I/O/Z IPD 3.3 V Video Port 2 Data 3

VP2D04 Y3 I/O/Z IPD 3.3 V Video Port 2 Data 4

VP2D05 U6 I/O/Z IPD 3.3 V Video Port 2 Data 5

VP2D06 Y2 I/O/Z IPD 3.3 V Video Port 2 Data 6

VP2D07 W3 I/O/Z IPD 3.3 V Video Port 2 Data 7

VP2D08 V5 I/O/Z IPD 3.3 V Video Port 2 Data 8

VP2D09 W4 I/O/Z IPD 3.3 V Video Port 2 Data 9

VP2D12/VRXD0 W2 I/O/Z IPD 3.3 V Video Port 2 Data 12 or VLYNQ receive data pin [0] (I)

VP2D13/VRXD1 V3 I/O/Z IPD 3.3 V Video Port 2 Data 13 or VLYNQ receive data pin [1] (I)

VP2D14/VRXD2 V4 I/O/Z IPD 3.3 V Video Port 2 Data 14 or VLYNQ receive data pin [2] (I)

VP2D15/VRXD3 U1 I/O/Z IPD 3.3 V Video Port 2 Data 15 or VLYNQ receive data pin [3] (I)

VP2D16/VTXD0 U3 I/O/Z IPD 3.3 V Video Port 2 Data 16 or VLYNQ transmit data pin [0] (O)

VP2D17/VTXD1 U2 I/O/Z IPD 3.3 V Video Port 2 Data 17 or VLYNQ transmit data pin [1] (O)

VP2D18/VTXD2 U5 I/O/Z IPD 3.3 V Video Port 2 Data 18 or VLYNQ transmit data pin [2] (O)

VP2D19/VTXD3 U4 I/O/Z IPD 3.3 V Video Port 2 Data 19 or VLYNQ transmit data pin [3] (O)

VP3CLK0/AECLKIN T1 I IPD 3.3 V Video Port 3 Clock 0 (I) or EMIFA external input clock (I)

VP3CLK1/AECLKOU P1 I/O/Z IPD 3.3 V Video Port 3 Clock 1 or EMIFA output clock (O/Z)

T

VP3CTL0/ ASDWE T2 I/O/Z IPU 3.3 V Video Port 3 Control 0 or Asynchronous memory write

VP3CTL1/ARNW R1 I/O/Z IPU 3.3 V Video Port 3 Control 1 or Asynchronous memory read/write (O/Z)

VP3CTL2/AOE P2 I/O/Z IPU 3.3 V Video Port 3 Control 2 or Asynchronous/Programmable

VP3D02/AED00 T6 I/O/Z IPU 3.3 V Video Port 3 Data 2 or EMIFA External Data 0

VP3D03/AED01 T5 I/O/Z IPU 3.3 V Video Port 3 Data 3 or EMIFA External Data 1

VP3D04/AED02 T4 I/O/Z IPU 3.3 V Video Port 3 Data 4 or EMIFA External Data 2

VP3D05/AED03 T3 I/O/Z IPU 3.3 V Video Port 3 Data 5 or EMIFA External Data 3

VP3D06/AED04 R6 I/O/Z IPU 3.3 V Video Port 3 Data 6 or EMIFA External Data 4

VP3D07/AED05 R5 I/O/Z IPU 3.3 V Video Port 3 Data 7 or EMIFA External Data 5

VP3D08/AED06 R4 I/O/Z IPU 3.3 V Video Port 3 Data 8 or EMIFA External Data 6

VP3D09/AED07 R3 I/O/Z IPU 3.3 V Video Port 3 Data 9 or EMIFA External Data 7

VP3D12/AED08 R2 I/O/Z IPU 3.3 V Video Port 3 Data 12 or EMIFA External Data 8

VP3D13/AED09 P6 I/O/Z IPU 3.3 V Video Port 3 Data 13 or EMIFA External Data 9

VP3D14/AED10 P5 I/O/Z IPU 3.3 V Video Port 3 Data 14 or EMIFA External Data 10

VP3D15/AED11 P4 I/O/Z IPU 3.3 V Video Port 3 Data 15 or EMIFA External Data 11

VP3D16/AED12 P3 I/O/Z IPU 3.3 V Video Port 3 Data 16 or EMIFA External Data 12

VP3D17/AED13 N4 I/O/Z IPU 3.3 V Video Port 3 Data 17 or EMIFA External Data 13

VP3D18/AED14 N6 I/O/Z IPU 3.3 V Video Port 3 Data 18 or EMIFA External Data 14

VP3D19/AED15 N5 I/O/Z IPU 3.3 V Video Port 3 Data 19 or EMIFA External Data 15

VP4CLK0/AARDY L1 I IPU 3.3 V Video Port 4 Clock 0 (I) or Asynchronous memory ready input (I)

VP4CLK1 K1 I/O/Z IPD 3.3 V Video Port 4 Clock 1

Table 2-4. TERMINAL FUNCTIONS (continued)

PULLUP/ VOLT

PULLDOWN

VIDEO PORT 3 OR EMIFA

enable/Programmable synchronous interface write-enable

synchronous memory output-enable (O/Z)

VIDEO PORT 4 OR EMIFA

Device Overview26 Submit Documentation Feedback

Page 27

www.ti.com

TMS320DM647/TMS320DM648

Digital Media Processor

SPRS372 – MAY 2007

Table 2-4. TERMINAL FUNCTIONS (continued)

TERMINAL NAME NO TYPE INTERNAL OPER DESCRIPTION

VP4CTL0/ABA0 J2 I/O/Z IPD 3.3 V Video Port 4 Control 0 or EMIFA bank address control (ABA[1:0])

VP4CTL1/ABA1 J1 I/O/Z IPD 3.3 V Video Port 4 Control 1 or EMIFA bank address control (ABA[1:0])

VP4CTL2/AADS K2 I/O/Z IPD 3.3 V Video Port 4 Control 2 or Programmable synchronous address

VP4D02/ ABE00 L2 I/O/Z IPU 3.3 V Video Port 4 Data 2 or EMIFA byte-enable control 0. Decoded

VP4D03/ ABE01 M4 I/O/Z IPU 3.3 V Video Port 4 Data 3 or EMIFA byte-enable control 1. Number of

VP4D04/AEA10 M5 I/O/Z IPU 3.3 V Video Port 4 Data 4 or EMIFA External Address 10 (word address)

VP4D05 M6 I/O/Z IPU 3.3 V Video Port 4 Data 5

VP4D06/ ACE2 L3 I/O/Z IPU 3.3 V Video Port 4 Data 6 or EMIFA memory space enable 2

VP4D07/ ACE3 L4 I/O/Z IPU 3.3 V Video Port 4 Data 7 or EMIFA memory space enable 3

VP4D08/AEA00 L5 I/O/Z IPD 3.3 V Video Port 4 Data 8 or EMIFA External Address 0 (word address)

VP4D09/AEA01 K3 I/O/Z IPD 3.3 V Video Port 4 Data 9 or EMIFA External Address 1 (word address)

VP4D12/AEA02 K4 I/O/Z IPD 3.3 V Video Port 4 Data 12 or EMIFA External Address 2 (word address)

VP4D13/AEA03 L6 I/O/Z IPD 3.3 V Video Port 4 Data 13 or EMIFA External Address 3 (word address)

VP4D14/AEA04 K5 I/O/Z IPD 3.3 V Video Port 4 Data 14 or EMIFA External Address 4 (word address)

VP4D15/AEA05 J3 I/O/Z IPD 3.3 V Video Port 4 Data 15 or EMIFA External Address 5 (word address)

VP4D16/AEA06 J4 I/O/Z IPD 3.3 V Video Port 4 Data 16 or EMIFA External Address 6 (word address)

VP4D17/AEA07 J5 I/O/Z IPD 3.3 V Video Port 4 Data 17 or EMIFA External Address 7 (word address)

VP4D18/AEA08 J6 I/O/Z IPD 3.3 V Video Port 4 Data 18 or EMIFA External Address 8 (word address)

VP4D19/AEA09 K6 I/O/Z IPD 3.3 V Video Port 4 Data 19 or EMIFA External Address 9 (word address)

AEA23 H4 OZ IPD 3.3 V EMIFA External Address 23 (word address) (O/Z)

AEA19 H5 I/O/Z IPU 3.3 V EMIFA External Address 19 (word address) (O/Z)

PULLUP/ VOLT

PULLDOWN

(O/Z). Active-low bank selects for the 16-bit EMIFA. When

interfacing to 16-bit asynchronous devices, ABA1 carries bit 1 of

the byte address. For an 8-bit asynchronous interface, ABA[1:0]

are used to carry bits 1 and 0 of the byte address.

(O/Z). Active-low bank selects for the 16-bit EMIFA. WHEN

interfacing to 16-bit asynchronous devices, ABA1 carries bit 1 of

the byte address. For an 8-bit asynchronous interface, ABA[1:0]

are used to carry bits 1 and 0 of the byte address.

strobe or read-enable. For programmable synchronous interface,

the r_enable field in the ChipSelect x Configuration Register

selects between ASADS and ASRE:

– If r_enable = 0, then the ASADS/ASRE signal functions as the

ASADS signal.

– If r_enable = 1, then the ASADS/ASRE signal functions as the

ASRE signal.

from the low-order address bits. The number of address bits or

byte enables used depends on the width of external memory.

Byte-write enables for most types of memory.

address bits or byte enables used depends on the width of

external memory. Byte-write enables for most types of memory.

(O/Z)

(O/Z)

(O/Z)

(O/Z)

(O/Z)

(O/Z)

(O/Z)

(O/Z)

(O/Z)

(O/Z)

(O/Z)

EMIFA

Submit Documentation Feedback Device Overview 27

Page 28

www.ti.com

PRODUCT PREVIEW

TMS320DM647/TMS320DM648

Digital Media Processor

SPRS372 – MAY 2007

Table 2-4. TERMINAL FUNCTIONS (continued)

TERMINAL NAME NO TYPE INTERNAL OPER DESCRIPTION

AECLKINSEL/AEA17 G4 I/O/Z IPD 3.3 V Select EMIFA external clock (I) (The EMIFA input clock AECLKIN

Table 2-5. TERMINAL FUNCTIONS (GROUND and POWER SUPPLY)

PULLUP/ VOLT

PULLDOWN

or SYSCLK4 is selected at reset via the pullup/pulldown resistor

on this pin. Note: AECLKIN is the default for the EMIFA input

clock.)

or EMIFA external address 17 (word address) (O/Z)

TERMINAL NAME NO TYPE INTERNAL OPER VOLT DESCRIPTION

V

SS

V

SS

V

SS

V

SS