TLC320AD57C

Data Manual

Sigma-Delta Stereo Analog-to-Digital Converter

SLAS086A

January 1995

Printed on Recycled Paper

IMPORTANT NOTICE

T exas Instruments (TI) reserves the right to make changes to its products or to discontinue any

semiconductor product or service without notice, and advises its customers to obtain the latest

version of relevant information to verify , before placing orders, that the information being relied

on is current.

TI warrants performance of its semiconductor products and related software to the specifications

applicable at the time of sale in accordance with TI’s standard warranty . T esting and other quality

control techniques are utilized to the extent TI deems necessary to support this warranty.

Specific testing of all parameters of each device is not necessarily performed, except those

mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death,

personal injury , or severe property or environmental damage (“Critical Applications”).

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR

WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES

OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer.

Use of TI products in such applications requires the written approval of an appropriate TI officer .

Questions concerning potential risk applications should be directed to TI through a local SC

sales office.

In order to minimize risks associated with the customer’s applications, adequate design and

operating safeguards should be provided by the customer to minimize inherent or procedural

hazards.

TI assumes no liability for applications assistance, customer product design, software

performance, or infringement of patents or services described herein. Nor does TI warrant or

represent that any license, either express or implied, is granted under any patent right, copyright,

mask work right, or other intellectual property right of TI covering or relating to any combination,

machine, or process in which such semiconductor products or services might be or are used.

Copyright 1995, Texas Instruments Incorporated

Contents

Section Title Page

1 Introduction 1–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1 Features 1–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2 Functional Block Diagram 1–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3 Terminal Assignments 1–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4 Ordering Information 1–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.5 Terminal Functions 1–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2 Detailed Description 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1 Power-Down and Reset Functions 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.1 Power Down 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.2 Reset Function 2–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2 Differential Input 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3 Sigma-Delta Modulator 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4 Decimation Filter 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5 High-Pass Filter 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6 Master-Clock Circuit 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.7 T est 2–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.8 Serial Interface 2–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.8.1 Master Mode 2–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.8.2 Slave Mode 2–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3 Specifications 3–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1 Absolute Maximum Ratings Over Operating Free-Air Temperature Range 3–1. . . . .

3.2 Recommended Operating Conditions 3–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3 Electrical Characteristics 3–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.1 Digital Interface, T

3.3.2 Analog Interface 3–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.3 Channel Characteristics, T

f

= 48 kHz 3–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4 Switching Characteristics 3–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

s

= 25°C, AVDD = DVDD = 5 V 3–2. . . . . . . . . . . . . . . . . . . .

A

= 25°C, AVDD = DVDD = 5 V,

A

4 Parameter Measurement Information 4–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

iii

List of Illustrations

Figure Title Page

2–1 Power-Down Timing Relationships 2–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–2 Differential Analog Input Configuration 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–3 Serial Master Transfer Modes 2–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–4 Serial Slave Transfer Modes 2–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–1 SCLK to Fsync and DOUT – Master Mode 3 4–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–2 SCLK to Fsync, DOUT and LRClk – Master Modes 4 and 6 4–1. . . . . . . . . . . . . . . . . . . .

4–3 SCLK to Fsync, DOUT, and LRClk – Master Mode 5 4–1. . . . . . . . . . . . . . . . . . . . . . . . . . .

4–4 SCLK to Fsync, DOUT, and LRClk – Master Mode 7 4–2. . . . . . . . . . . . . . . . . . . . . . . . . . .

4–5 SCLK to LRClk and DOUT – Slave Mode 0, Fsync High 4–2. . . . . . . . . . . . . . . . . . . . . . .

4–6 SCLK to Fsync, LRClk, and DOUT – Slave Mode 2, Fsync Controlled 4–2. . . . . . . . . . .

List of Tables

Table Title Page

2–1 Master-Clock to Sample-Rate Comparison 2–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

iv

1 Introduction

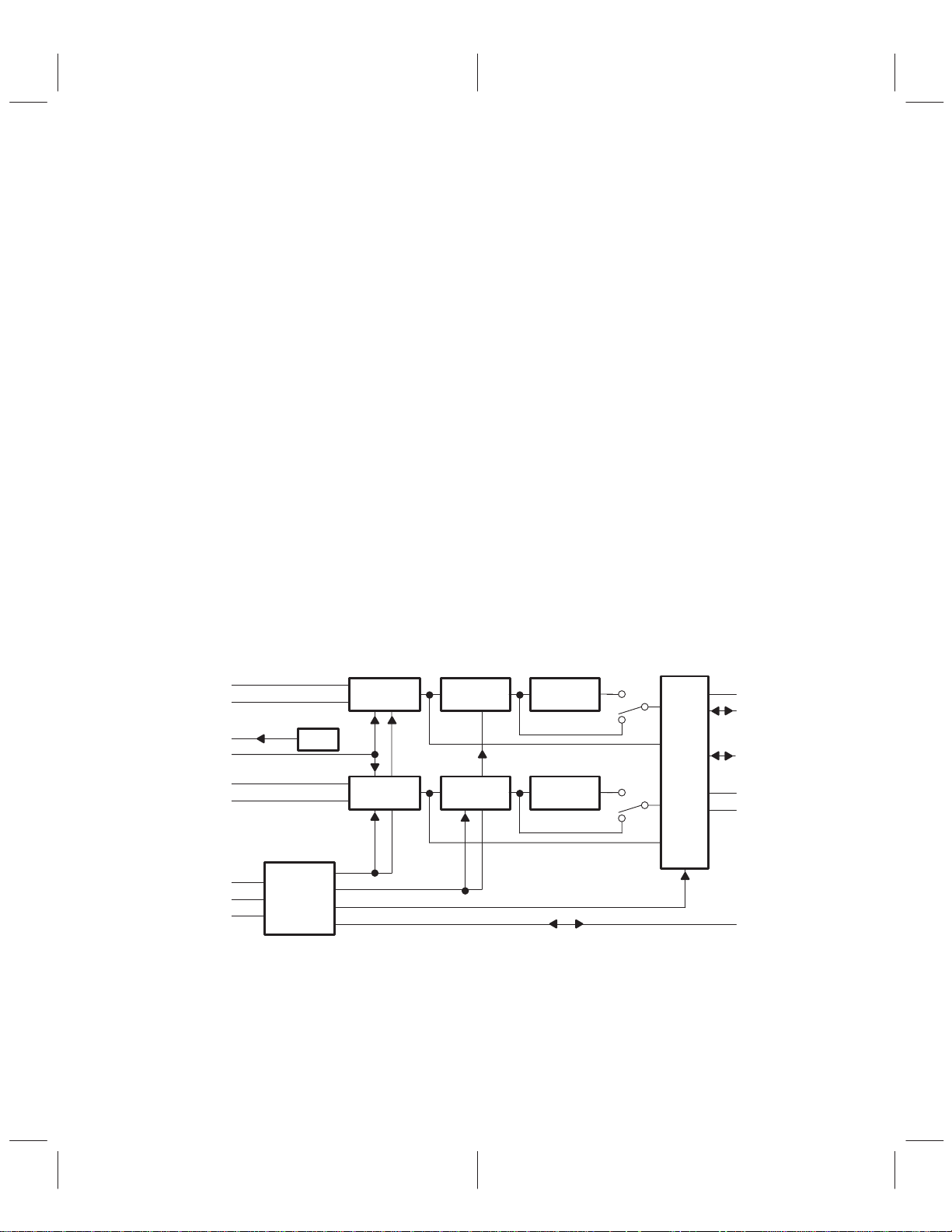

The TLC320AD57C provides high-resolution signal conversion from analog to digital using oversampling

sigma-delta technology. This device consists of two synchronous conversion paths. Also included is a

decimation filter after the modulator as shown in the functional block diagram. Other functions provide

analog filtering and on-chip timing and control.

A functional block diagram of the TLC320AD57C is included in section 1.2. Each block is described in the

Detailed Description section.

1.1 Features

• Single 5-V Power Supply

• Sample Rates (f

• 18-Bit Resolution

• Signal-to-Noise (EIAJ) of 97 dB

• Dynamic Range of 95 dB

• Total Signal-to-Noise+Distortion of 91 dB

• Internal Reference Voltage (V

• Serial Port Interface

• Differential Architecture

• Power Dissipation of 200 mW. Power-Down Mode for Low-Power Applications

• One Micron Advanced LinEPIC1Z Process

1.2 Functional Block Diagram

) up to 48 kHz

s

ref

)

INLP

INLM

REFO

REFI

INRP

INRM

MCLK

CMODE

MODE0–MODE2

Control

VREF

Sigma-Delta

Modulator

Sigma-Delta

Modulator

LinEPIC1Z is a trademark of Texas Instruments Incorporated.

Decimation

Filter

Decimation

Filter

High-Pass

Filter

High-Pass

Filter

I

S

n

e

t

r

e

i

r

a

f

l

a

c

e

DOUT

Fsync

LRClk

OSFR

OSFL

SCLK

1–1

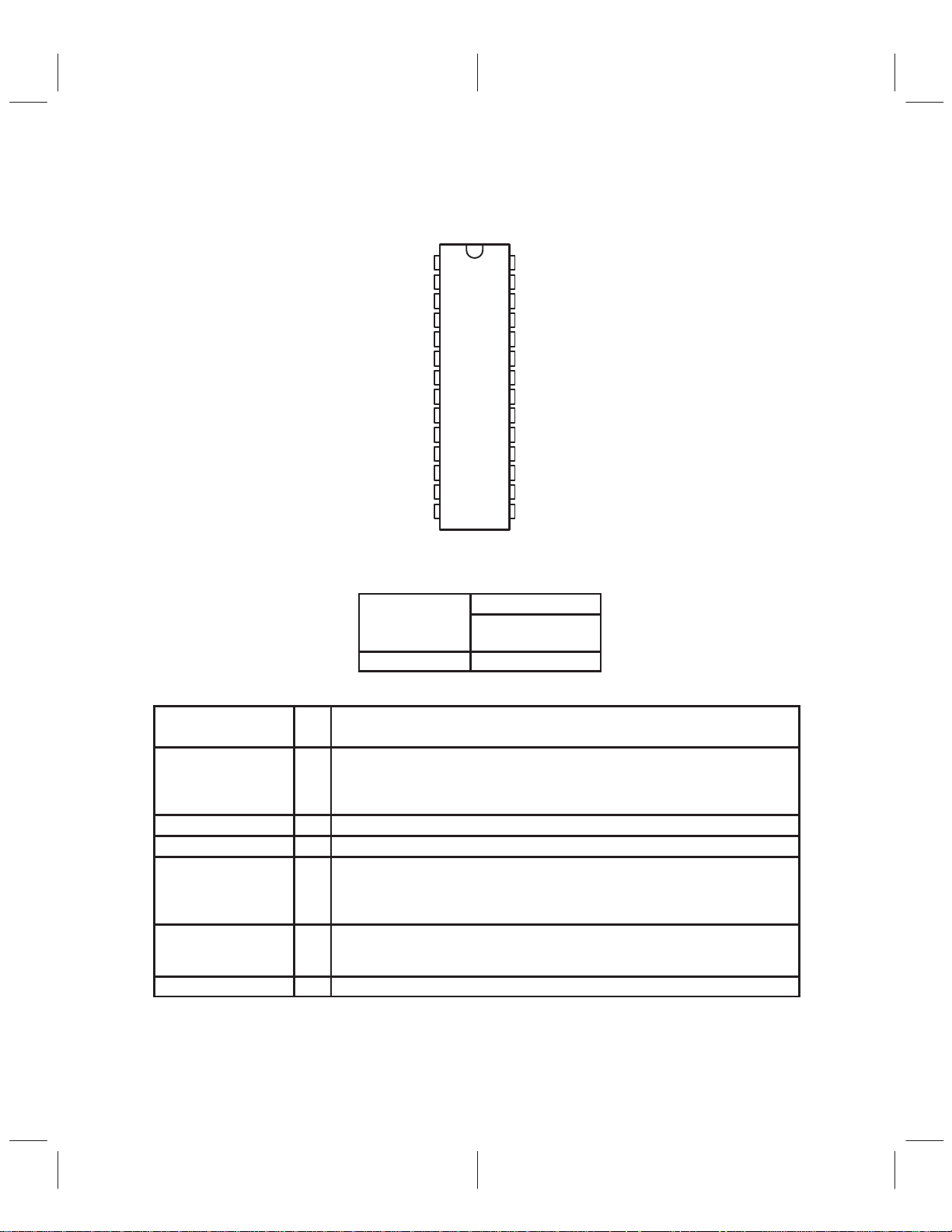

1.3 Terminal Assignments

I/O

DESCRIPTION

DW PACKAGE

(TOP VIEW)

INLP

INLM

REFI

AV

AV

AnaPD

HPByp

MODE2

OSFL

DigPD

TEST

CMODE

MODE0

LRClk

NC – No internal connection

DD

SS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

INRP

INRM

REFO

LGND

Vlogic

NC

MODE1

OSFR

MCLK

DV

SS

DV

DD

Fsync

DOUT

SCLK

1.4 Ordering Information

PACKAGE

T

A

0°C to 70°C TLC320AD57CDW

SMALL OUTLINE

(DW)

1.5 Terminal Functions

TERMINAL

NAME NO.

AnaPD 6 I Analog power-down mode. The analog power-down mode disables the analog

AV

DD

AV

SS

CMODE 12 I Clock mode. CMODE selects between two methods of determining the master clock

DOUT 16 O Data output. DOUT transmits the sigma-delta audio analog-to-digital converter (ADC)

DV

DD

4 I Analog supply voltage

5 I Analog ground

18 I Digital supply voltage

modulators. The single-bit modulator outputs become invalid, which renders the

outputs of the digital filters invalid. When AnaPD is pulled low, normal operation of the

device resumes.

frequency. When CMODE is high, the master clock input is 384× the conversion

frequency. When CMODE is low, the master clock input is 256× the conversion

frequency.

output data to a digital signal processor (DSP) serial port or other compatible serial

interface and is synchronized to SCLK. DOUT is low when DigPD is high.

1–2

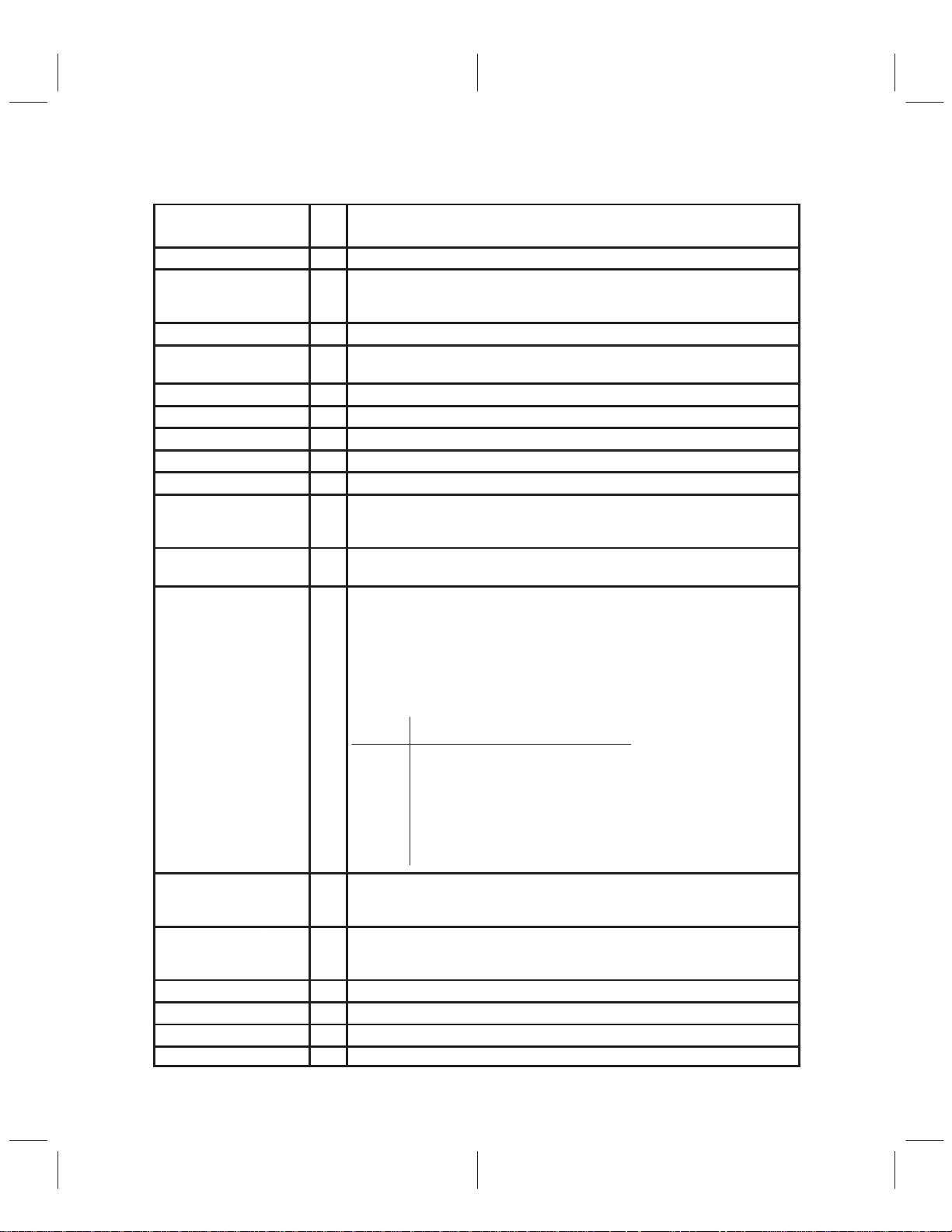

1.5 Terminal Functions (Continued)

I/O

DESCRIPTION

TERMINAL

NAME NO.

DV

SS

DigPD 10 I Digital power-down mode. The digital power-down mode shuts down the digital

Fsync 17 I/O Frame synchronization. Fsync designates valid data from the ADC.

HPByp 7 I High-pass filter bypass. When HPByp is high, the high-pass filter is bypassed. This

INLM 2 I Inverting input to left analog input amplifier

INLP 1 I Noninverting input to left analog input amplifier

INRM 27 I Inverting input to right analog input amplifier

INRP 28 I Noninverting input to right analog input amplifier

LGND 25 I Logic-power-supply ground for analog modulator

LRClk 14 I/O Left/right clock. LRClk signifies whether the serial data is associated with the left

MCLK 20 I Master clock. MCLK derives all of the key logic signals of the sigma-delta audio

MODE0–MODE2 8, 13,22I Serial modes. MODE0–MODE2 configure this device for many different modes of

OSFL, OSFR 9, 21 O Over scale flag left/right. If the left/right channel analog input exceeds the full scale

SCLK 15 I/O Shift clock. If SCLK is confirgured as an input, SCLK clocks serial data out of the

TEST 11 I Test mode. TEST should be low for normal operation.

REFI 3 I Input voltage for modulator reference (normally connected to REFO, terminal 26).

REFO 26 I Internal voltage reference

Vlogic 24 I Logic power supply (5 V) for analog modulator

19 I Digital ground

filters and clock generators. All digital outputs are brought to unasserted levels.

When DigPD is pulled low, normal operation of the device resumes.

allows dc analog signal conversion.

channel ADC (when high) or the right channel ADC (when low). LRClk is low when

DigPD is high.

ADC. The nominal input frequency range is 18.432 MHz to 256 kHz.

operation. The different configurations are:

Master versus slave

16 bit versus 18 bit

MSB first versus LSB first

Slave: Fsync controlled versus Fsync high

Each of these modes is described in the Serial Interface section with timing

diagrams.

MODE MASTER/ MSB/LSB

0 1 2 SLAVE BITS FIRST

0 0 0 slave up to 18 MSB

0 0 1 slave 18 LSB

0 1 0 slave up to 18 MSB

0 1 1 master 16 MSB

1 0 0 master 18 MSB

1 0 1 master 18 LSB

1 1 0 master 16 MSB

1 1 1 master 16 LSB

input range for two consecutive conversions, OSFL and OSFR are set high for 4096

LRClk periods. OSFL and OSFR are low when DigPD is high.

sigma-delta audio ADC. If SCLK is configured as an output, SCLK stops clocking

when DigPD is high.

1–3

Loading...

Loading...