THS1060

10-BIT 60 MSPS IF SAMPLING COMMUNICATIONS

ANALOG-TO-DIGITAL CONVERTER

SLAS212 – MARCH 2000

1

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

features

D

60 MSPS Maximum Sample Rate

D

10-Bit Resolution

D

No Missing Codes

D

On-Chip Sample and Hold

D

73 dB Spurious Free Dynamic Range at

fin = 15.5 MHz

D

5 V Analog and Digital Supply

D

3 V and 5 V CMOS Compatible Digital

Output

D

9.5 Bit ENOB at fIN = 31 MHz

D

60 dB SNR at fIN = 31 MHz

D

82 MHz Bandwidth

D

Internal or External Reference

D

Buffered 900 Ω Differential Analog Input

applications

D

Wireless Local Loop

D

Wireless Internet Access

D

Cable Modem Receivers

D

Medical Ultrasound

D

Magnetic Resonant Imaging

description

The THS1060 is a high speed low noise 10-bit CMOS pipelined analog-to-digital converter. A dif ferential sample

and hold minimizes even order harmonics and allows for a high degree of common mode rejection at the analog

input. A buffered analog input allows for operation with a constant analog input impedance, and prevents

transient voltage spikes from feeding backward to the analog input source. Full temperature DNL performance

allows for industrial application with the assurance of no missing codes. The THS1060 can operate with either

internal or external references. Internal reference usage selection is accomplished simply by externally

connecting reference output terminals to reference input terminals. Packaged in a small 48-pin quad flat-pack,

the THS1060 makes use of Texas Instruments PowerPAD technology. The die of the THS1060 is bonded

directly to a copper alloy plate which is exposed on the bottom of the package. When soldered to a ground land,

the PowerPAD provides superior heat dissipation and thermal performance ideal for industrial applications

in high temperature environments.

Copyright 2000, Texas Instruments Incorporated

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments.

THS1060

10-BIT 60 MSPS IF SAMPLING COMMUNICATIONS

ANALOG-TO-DIGITAL CONVERTER

SLAS212 – MARCH 2000

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

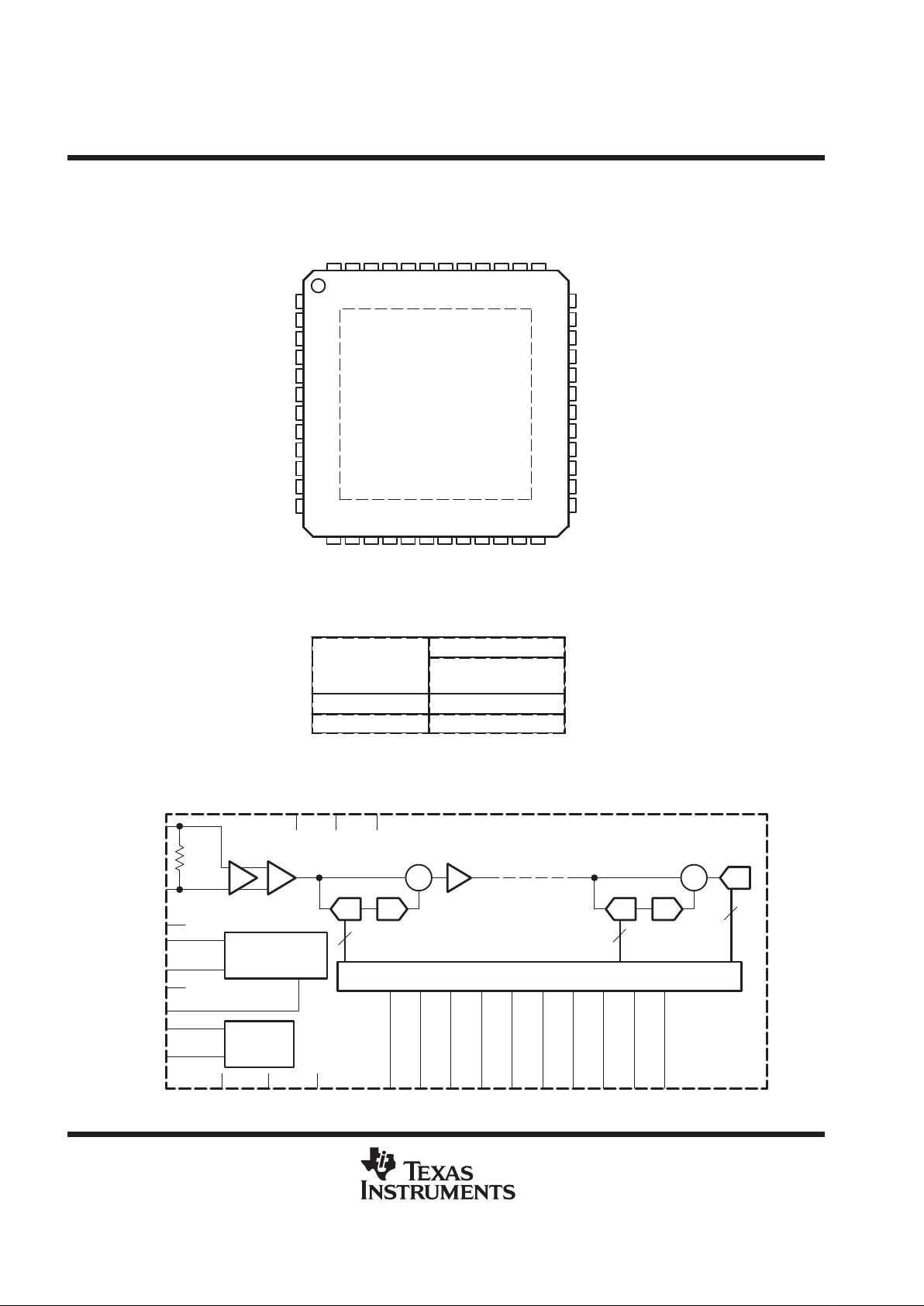

14 15

NC

NC

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

36

35

34

33

32

31

30

29

28

27

26

25

16

1

2

3

4

5

6

7

8

9

10

11

12

AV

SS

AV

DD

V

IN+

V

IN–

AV

DD

V

REFOUT–

V

REFIN

–

V

REFIN

+

V

REFOUT

+

V

BG

AV

SS

AV

DD

17 18 19 20

47 46 45 44 4348 42

V

AV

CLK+

40 39 3841

21

22 23 24

37

13

CLK–

48 PHP PACKAGE

(TOP VIEW)

CM

DD

DVDDDVSSDVSSDVDDDVSSDV

DD

DRV

SS

DRV

DD

AVSSAVSSAVDDAV

SS

DRVSSAVSSDRV

SS

AV

DD

DRVDDDRV

DD

DV

SS

AV

SS

AVAILABLE OPTIONS

PACKAGE

T

A

48-TQFP

(PHP)

–40°C to 85°C THS1060I

0°C to 70°C THS1060C

functional block diagram

Digital Error Correction

S/H

Stage 1 Stage 10

Reference

3.0 V

2.0 V

AV

DD/2

Timing

V

IN–

V

REFOUT+

V

CM

CLK+

DV

SS

D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

AVDDDV

DD

D/A

Σ

A/D

Σ

D/AA/D A/D

V

REFOUT–

V

REFIN+

V

REFIN–

CLK–

1

1

1

Buffer

DRV

DD

AV

SS

DRV

SS

Stages 2 – 9

V

IN+

900 Ω

THS1060

10-BIT 60 MSPS IF SAMPLING COMMUNICATIONS

ANALOG-TO-DIGITAL CONVERTER

SLAS212 – MARCH 2000

3

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

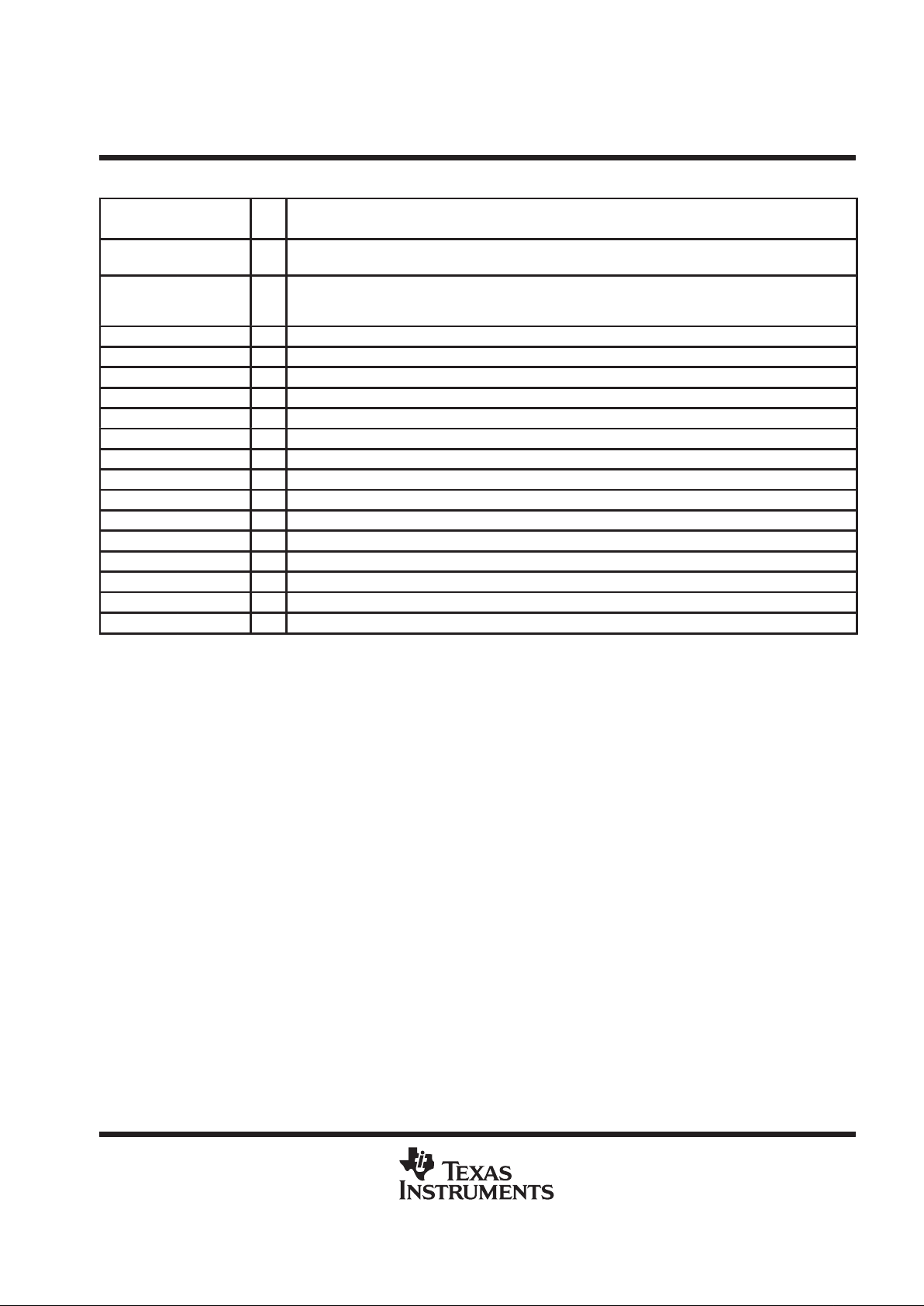

Terminal Functions

TERMINAL

NAME NO.

I/O

DESCRIPTION

AV

DD

2, 5, 12

43, 45, 47

I Analog power supply

AV

SS

1, 11, 13,

41, 42, 44,

46

I Analog ground return for internal analog circuitry

CLK+ 15 I Clock input

CLK– 16 I Complementary clock input

D9–D0 25–34 O Digital data output bits; LSB= D0, MSB = D9 (2s complement output format)

DRV

DD

24, 37, 38 I Digital output driver supply

DRV

SS

23, 39, 40 I Digital output driver ground return

DV

DD

17, 20, 22 I Positive digital supply

DV

SS

18, 19, 21 I Digital ground return

V

BG

10 O Band gap reference. Bypass to ground with a 1 µF and a 0.01 µF chip capacitor.

V

CM

48 O Common mode voltage output. Bypass to ground with a 0.1 µF and a 0.01 µF chip device capacitor.

V

IN+

3 I Analog signal input

V

IN–

4 I Complementary analog signal input

V

REFIN–

7 I External reference input low

V

REFIN+

8 I External reference input high

V

REFOUT+

9 O Internal reference output. Compensate with a 1 µF and a 0.01 µF chip capacitor.

V

REFOUT–

6 O Internal reference output. Compensate with a 1 µF and a 0.01 µF chip capacitor.

detailed description

The THS1060 uses a differential pipeline architecture and assures no missing codes over the full operating

temperature range. The device uses a 1 bit per stage architecture in order to achieve the highest possible

bandwidth. The differential analog inputs are terminated with a 900 Ω resistor . The inputs are then fed to a unity

gain buffer followed by the S/H (sample and hold) stage. This S/H stage is a switched capacitor op-amp based

circuit, see Figure 3. The pipeline is a typical 1 bit per stage pipeline as shown in the functional block diagram.

The digital output of the 10 stages and the last 1 bit flash are sent to a digital correction logic block which then

outputs the final 10 bits.

THS1060

10-BIT 60 MSPS IF SAMPLING COMMUNICATIONS

ANALOG-TO-DIGITAL CONVERTER

SLAS212 – MARCH 2000

4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

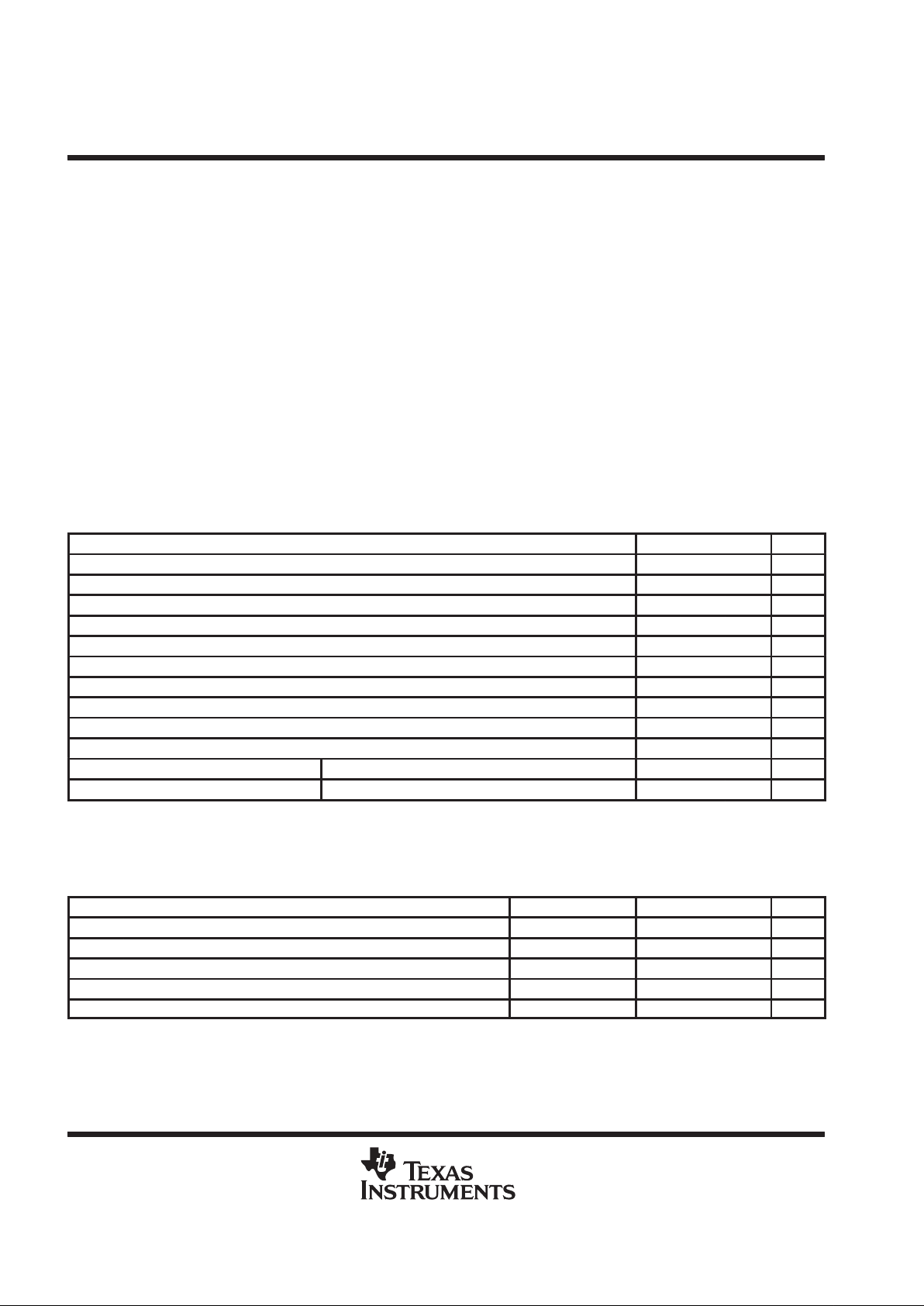

absolute maximum ratings over operating free-air temperature (unless otherwise noted)

†

Supply voltage range: AVDD –0.5 V to 7 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DVDD –0.5 V to 7 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DRVDD –0.5 V to 7 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Voltage between AV

SS

and DVSS –0.3 V to 0.5 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Voltage between DRVDD and DVDD –0.5 V to 5 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Voltage between AVDD and DVDD –0.5 V to 5 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Digital data output –0.3 V to DVDD+0.3 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

CLK peak input current 20 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Peak total input current (all inputs) –30 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operating free-air temperature range, TA: THS1060C 0°C to 70°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

THS1060I –40°C to 85°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature range –65°C to 150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Lead temperature 1,6 mm (1/16 inch) from the case for 10 seconds 260°C. . . . . . . . . . . . . . . . . . . . . . . . . . . .

†

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

recommended operating conditions

PARAMETER MIN NOM MAX UNIT

Sample rate 1 60 MSPS

Analog supply voltage, AV

DD

4.75 5 5.25 V

Digital supply voltage, DV

DD

4.75 5 5.25 V

Digital output driver supply voltage, DRV

DD

3 3.3 5.25 V

CLK + high level input voltage, V

IH

4 5 5.5 V

CLK + low-level input voltage, V

IL

0 1 V

CLK – high-level input voltage, V

IH

4 5 5.5 V

CLK – low-level input voltage, V

IL

0 1 V

CLK pulse-width high, t

p(H)

7.5 8.3 ns

CLK pulse-width low, t

p(L)

7.5 8.3 ns

Operating free-air temperature range, T

A

THS1060C 0 70 °C

Operating free-air temperature range, T

A

THS1060I –40 85 °C

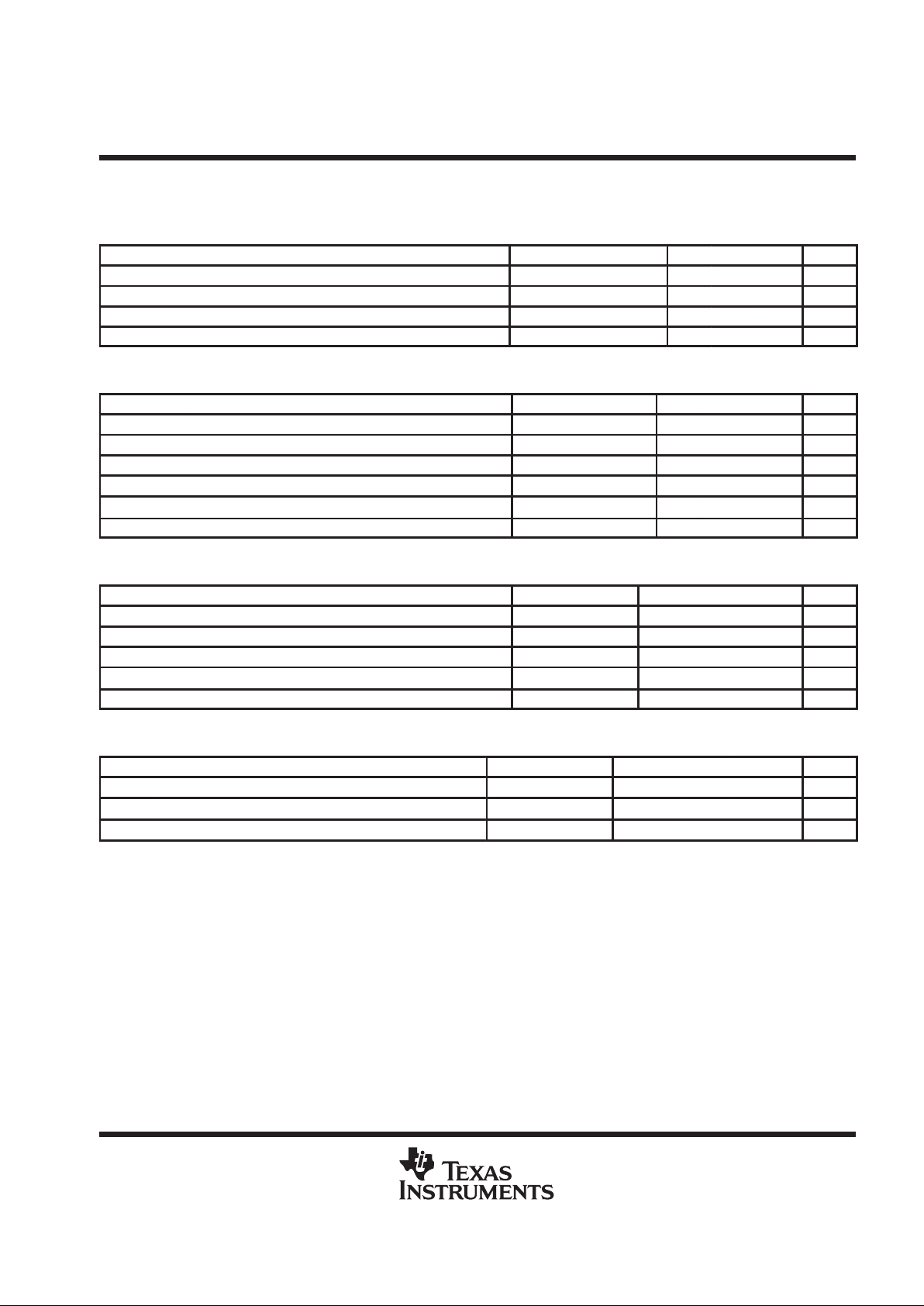

electrical characteristics, over recommended operating free-air temperature range,

AV

DD

= DVDD = 5 V, DRVDD = 3.3 V, internal references, CLK = 60 MHz, (unless otherwise noted)

‡

dc accuracy

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

DNL Dif ferential nonlinearity (see Note 1) ±0.4 ±1 LSB

No missing codes (see Note 2) Assured

INL Integral nonlinearity (see Note 1) ±0.9 ±3 LSB

E

O

Offset error 15 31 mV

E

G

Gain error –7 –10 %FSR

‡

All typical values are at TA = 25°C.

NOTES: 1. Tested without over ranging

2. Tested with over ranging

THS1060

10-BIT 60 MSPS IF SAMPLING COMMUNICATIONS

ANALOG-TO-DIGITAL CONVERTER

SLAS212 – MARCH 2000

5

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

electrical characteristics, over recommended operating free-air temperature range,

AV

DD

= DVDD = 5 V, DRVDD = 3.3 V, internal references, CLK = 60 MHz, (unless otherwise noted)

†

power supply

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

I(AV

DD)

Analog supply current V(VIN) = V(VCM) 120 150 mA

I(DV

DD)

Digital supply current V(VIN) = V(VCM) 2 5 mA

I(DRV

DD)

Output driver supply current V(VIN) = V(VCM) 2 6 mA

P

D

Power dissipation V(VIN) = V(VCM) 0.6 W

†

All typical values are at TA = 25°C.

reference

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

V

REFOUT–

Negative reference output voltage 1.95 2 2.05 V

V

REFOUT+

Positive reference output voltage 2.95 3 3.05 V

V

REFIN–

External reference supplied 2 V

V

REFIN+

External reference supplied 3 V

V(VCM) Common mode output voltage AVDD/2 V

I(VCM) Common mode output current 10 µA

†

All typical values are at TA = 25°C.

analog input

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

RIDifferential input resistance 900 Ω

CIDifferential input capacitance 4 pF

VIAnalog input common mode range VCM ±0.05 V

VIDDifferential input voltage range 2

V p-p

BW Analog input bandwidth (large signal) –3 dB 82 MHz

†

All typical values are at TA = 25°C.

digital outputs

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

V

OH

High-level output voltage IOH = –50 µA 0.8DRV

DD

V

V

OL

Low-level output voltage IOL = 50 µA 0.2DRV

DDVDD

C

L

Output load capacitance 15 pF

†

All typical values are at TA = 25°C.

THS1060

10-BIT 60 MSPS IF SAMPLING COMMUNICATIONS

ANALOG-TO-DIGITAL CONVERTER

SLAS212 – MARCH 2000

6

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

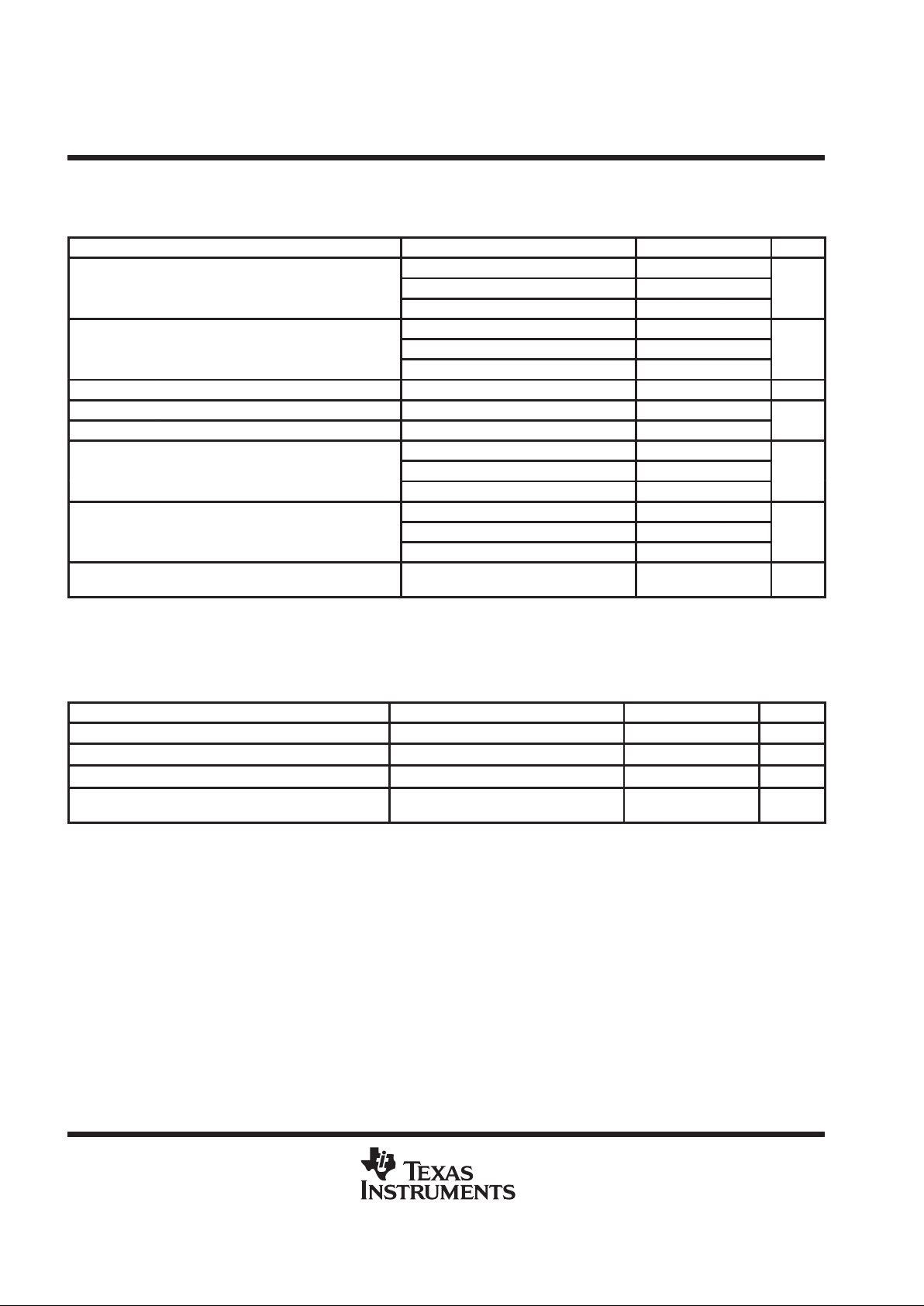

ac specifications, over recommended operating free-air temperature range, AVDD = DVDD = 5 V,

DRV

DD

= 3.3 V, internal references, CLK = 60 MHz, analog input at –2 dBFS(unless otherwise

noted)

†

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

fIN = 2.2 MHz 60

SNR Signal to noise ratio

fIN =15.5 MHz

56 60

dBFS

fIN =31 MHz 60

fIN = 2.2 MHz 59

SINAD Signal to noise and distortion

fIN =15.5 MHz

53 59.6

dBFS

fIN =31 MHz 59

ENOB Effective number of bits fIN =15.5 MHz 8.5 9.6 bits

THD Total harmonic distortion fIN =15.5 MHz –72 –54

SFDR Spurious-free dynamic range fIN =15.5 MHz 57 73

dBc

fIN = 2.2 MHz –80

2

n

d

Harmonic Distortion

fIN =15.5 MHz

–77 –57

dBc

fIN = 31 MHz –79

fIN = 2.2 MHz –68

3

r

d

Harmonic Distortion

fIN =15.5 MHz

–79 –60

dBc

fIN = 31 MHz –68

Two tone SFDR

F1 = 14.9 MHz, F2 = 15.6 MHz,

Analog inputs at – 8 dBFS each

70 dBc

†

All typical values are at TA = 25°C.

operating characteristics over recommended operating conditions, AVDD = DVDD = 5 V,

DRV

DD = 3.3 V

switching specifications

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

Aperture delay, t

d(A)

120 ps

Aperture jitter 1 ps RMS

Output delay t

d(O)

After falling edge of CLK+ 13 ns

Pipeline delay t

d(PIPE)

6.5

CLK

Cycle

THS1060

10-BIT 60 MSPS IF SAMPLING COMMUNICATIONS

ANALOG-TO-DIGITAL CONVERTER

SLAS212 – MARCH 2000

7

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

definitions of specifications

analog bandwidth

The analog input frequency at which the spectral power of the fundamental frequency of a large input signal

is reduced by 3 dB.

aperture delay

The delay between the 50% point of the rising edge of the clock and the instant at which the analog input is

sampled.

aperture uncertainity (jitter)

The sample-to-sample variation in aperture delay

differential nonlinearity

The average deviation of any output code from the ideal width of 1 LSB.

clock pulse width/duty cycle

Pulse width high is the minimum amount of time that the clock pulse should be left in logic 1 state to achieve

rated performance; pulse width low is the minimum time clock pulse should be left in low state. At a given clock

rate, these specs define acceptable clock duty cycles.

offset error

The difference between the analog input voltage at which the analog-to-digital converter output changes from

negative full scale, to one LSB above negative full scale, and the ideal voltage at which this transition should

occur.

gain error

The maximum error in LSBs between a digitized ideal full scale low frequency offset corrected triangle wave

analog input, from the ideal digitized full scale triangle wave, divided by the full scale range, in this case 1024.

harmonic distortion

The ratio of the power of the fundamental to a given harmonic component reported in dBc.

integral nonlinearity

The deviation of the transfer function from an end-point adjusted reference line measured in fractions of 1 LSB.

Also the integral of the DNL curve.

output delay

The delay between the 50% point of the falling edge of the clock and signal and the time when all output data

bits are within valid logic levels (not including pipeline delay).

signal-to-noise-and distortion (SINAD)

When tested with a single tone, the ratio of the signal power to the sum of the power of all other spectral

components, excluding dc, referenced to full scale.

signal-to-noise ratio (SNR)

When tested with a single tone, the ratio of the signal power to the sum of the power of all other power spectral

components, excluding dc and the first 9 harmonics, referenced to full scale.

effective number of bits (ENOB)

For a sine wave, SINAD can be expressed in terms of the number of bits, using the following formula,

ENOB

+

(

SINAD*1.76

)

6.02

spurious-free dynamic range (SFDR)

The ratio of the signal power to the power of the worst spur, excluding dc. The worst spurious component may

or may not be a harmonic. The ratio is reported in dBc (that is, degrades as signal levels are lowered).

THS1060

10-BIT 60 MSPS IF SAMPLING COMMUNICATIONS

ANALOG-TO-DIGITAL CONVERTER

SLAS212 – MARCH 2000

8

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

AIN

CLK+

Digital Output

(D0 – D9)

Data N–7

tp(H) tP(L)

t

d(A)

Sample N

t

c

t

d(O)

t

d(Pipe)

Data N–6 Data N–5 Data N–4 Data N–3 Data N–2 Data N–1 Data N Data N+1 Data N+2

Figure 1. Timing Diagram

equivalent circuits

Figure 2. References

Figure 3. Analog Input Stage

φ1′

φ1′

φ1

φ1

φ2

φ2

V

CM

V

CM

AV

DD

V

CM

AV

SS

R

1

R

2

V

REFOUT+

V

REFOUT–

R2

R2

R1

R1

BAND

GAP

900 Ω

VIN+

VIN–

V

SS

V

DD

10 Ω

D0–D11

Figure 4. Clock Inputs

Figure 5. Digital Outputs

Timing

DV

DD

CLK+

DV

DD

CLK–

DV

SS

DV

SS

THS1060

10-BIT 60 MSPS IF SAMPLING COMMUNICATIONS

ANALOG-TO-DIGITAL CONVERTER

SLAS212 – MARCH 2000

9

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TYPICAL CHARACTERISTICS

†

–110

–100

–90

–80

–70

–60

–50

–40

–30

–20

–10

0

0 5 10 15 20 25 30

OUTPUT POWER SPECTRUM

vs

FREQUENCY

f – Frequency – MHz

Fs = 60 MSPS

fIN = 2.2 MHz, VIN @ –2 dBFS

8K Point Discrete Fourier

Transform

Power – dBFS

Figure 6

–110

–100

–90

–80

–70

–60

–50

–40

–30

–20

–10

0

0 5 10 15 20 25 30

OUTPUT POWER SPECTRUM

vs

FREQUENCY

f – Frequency – MHz

Fs = 60 MSPS

fIN = 15.5 MHz, VIN @ –2 dBFS

8K Point Discrete Fourier

Transform

Power – dBFS

Figure 7

†

AVDD = 5 V, DVDD = 5 V, DRVDD = 3.3 V, TA = 25°C (unless otherwise noted)

THS1060

10-BIT 60 MSPS IF SAMPLING COMMUNICATIONS

ANALOG-TO-DIGITAL CONVERTER

SLAS212 – MARCH 2000

10

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TYPICAL CHARACTERISTICS

–110.00

–100.00

–90.00

–80.00

–70.00

–60.00

–50.00

–40.00

–30.00

–20.00

–10.00

0.00

0 5 10 15 20 25 30

OUTPUT POWER SPECTRUM

vs

FREQUENCY

f – Frequency – MHz

Power – dBFS

Fs = 60 MSPS

fIN = 31 MHz, VIN @ –2 dBFS

8K Point Discrete Fourier

Transform

Figure 8

–110

–100

–90

–80

–70

–60

–50

–40

–30

–20

–10

0

0 5 10 15 20 25 30

OUTPUT POWER SPECTRUM

vs

FREQUENCY

f – Frequency – MHz

Power – dBFS

Fs = 60 MSPS

fIN = 69 MHz, VIN @ –2 dBFS

8K Point Discrete Fourier

Transform

Figure 9

THS1060

10-BIT 60 MSPS IF SAMPLING COMMUNICATIONS

ANALOG-TO-DIGITAL CONVERTER

SLAS212 – MARCH 2000

11

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TYPICAL CHARACTERISTICS

0

10

20

30

40

50

60

70

80

90

100

0 102030405060708090100

NOISE AND DISTORTION

vs

ANALOG INPUT FREQUENCY

f – Analog Input Frequency – MHz

2nd

Harmonic

(dBc)

SFDR (dBc)

SINAD

(dBFS)

SNR (dBFS)

3rd

Harmonic

(dBc)

Fs = 60 MSPS

VIN @ –2 dBFS

Power – dB

Figure 10

–110

–100

–90

–80

–70

–60

–50

–40

–30

–20

–10

0

0 5 10 15 20 25 30

TWO-TONE OUTPUT POWER SPECTRUM

vs

FREQUENCY

f – Frequency – MHz

Fs=60 MSPS, F1=14.9 MHz,

F2 = 15.6 MHz each @ –8 dBFS

8K Point Discrete Fourier

Transform

Power – dBFS

Figure 11

THS1060

10-BIT 60 MSPS IF SAMPLING COMMUNICATIONS

ANALOG-TO-DIGITAL CONVERTER

SLAS212 – MARCH 2000

12

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TYPICAL CHARACTERISTICS

0

10

20

30

40

50

60

70

80

90

100

–50 –45 –40 –35 –30 –25 –20 –15 –10 –5 0

NOISE AND DISTORTION

vs

ANALOG INPUT POWER LEVEL

Input Power – dBFS

Fs = 60 MSPS

fIN = 15.5 MHz

SINAD(dBFS)

SNR(dBFS)

SFDR(dBc)

Power – dB

Figure 12

0

10

20

30

40

50

60

70

80

90

100

5 1015202530354045505560657075

Clock Frequency – MHz

SINAD(dBFS)

SNR(dBFS)

SFDR(dBc)

NOISE AND DISTORTION

vs

CLOCK FREQUENCY

fIN = 15.5 MHz, VIN @ –2 dBFS

Power – dB

Figure 13

THS1060

10-BIT 60 MSPS IF SAMPLING COMMUNICATIONS

ANALOG-TO-DIGITAL CONVERTER

SLAS212 – MARCH 2000

13

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TYPICAL CHARACTERISTICS

0

10

20

30

40

50

60

70

80

90

100

40 45 50 55 60

Duty Cycle – %

SINAD (dBFS)

SNR (dBFS)

SFDR (dBc)

Fs = 60 MSPS

fIN = 15.5 MHz, VIN @ –2 dBFS

PowerPAD not connected, T = 25°C

NOISE AND DISTORTION

vs

DUTY CYCLE

Power – dB

Figure 14

–1

0

1

0 256 512 768 1024

DIFFERENTIAL NONLINEARITY

vs

OUTPUT CODE

Output Code

DNL – (LSBs)

Fs = 60 MSPS

fIN = 15.5 MHz

1023

Figure 15

THS1060

10-BIT 60 MSPS IF SAMPLING COMMUNICATIONS

ANALOG-TO-DIGITAL CONVERTER

SLAS212 – MARCH 2000

14

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TYPICAL CHARACTERISTICS

–2

–1

0

1

2

0 256 512 768

INTEGRAL NONLINEARITY

vs

OUTPUT CODE

Output Code – LSBs

INL – LSBs

Fs = 60 MSPS

fIN = 15.5 MHz

1023

Figure 16

–30

–20

–10

0

0 20406080100

LARGE SIGNAL ANALOG INPUT BANDWIDTH

f – Analog Input Frequency – MHz

Fs = 60 MSPS

–3 dB Point @ 82 MHz

Power – dBFS

Figure 17

0

1

2

3

4

5

6

7

8

9

10

35 40 45 50 55 60 65

PERFORMANCE

vs

DUTY CYCLE WITH PowerPAD

Duty Cycle – %

Fs = 60 MSPS

fIN = 15.5 MHz, VIN @ –2 dBFS

ENOB – bits

ENOB (25°C)

ENOB (85°C)

Figure 18

THS1060

10-BIT 60 MSPS IF SAMPLING COMMUNICATIONS

ANALOG-TO-DIGITAL CONVERTER

SLAS212 – MARCH 2000

15

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

APPLICATION INFORMATION

using the THS1060 references

The option of internal or external reference is provided by allowing for an external connection of the internal

reference to the reference inputs. This type of reference selection offers the lowest noise possible by not relying

on any active switch to make the selection. Compensating each reference output with a 1-µF and 0.01 µF

microwave chip capacitor is required as shown in Figure 19. The differential analog input range is equal to

2 (V

REFOUT+

– V

REFOUT–)

. When using external references, it is best to decouple the reference inputs with a

0.1 µF and 0.01 µF chip capacitor as shown in Figure 20.

0.01 µF 1 µF

0.01 µF 1 µF

V

REFIN+

V

REFOUT+

V

REFIN–

V

REFOUT–

Figure 19. Internal Reference Usage Figure 20. External Reference Usage

0.01 µF 0.1 µF

0.01 µF 0.1 µF

External Reference +

V

REFIN+

V

REFIN–

External Reference –

using the THS1060 clock input

The THS1060 is a high performance A/D converter. In order to obtain the best possible performance, care

should be taken to ensure that the device is clocked appropriately . The optimal clock to the device is a low jitter

square wave with sharp rise times (<2ns) at 50% duty cycle. The two clock inputs (CLK+ and CLK–), should

be driven with complimentary signals that have minimal skew, and nominally swing between 0 V and 5 V. The

device will still operate with a peak to peak swing of 3 V on each clock channel (around the 2.5 V midpoint), but

it could become more duty cycle sensitive under such conditions.

Use of a transformer coupled clock input ensures minimal skew between the CLK+ and CLK– signals. If the

available clock signal swing is not adequate, a step-up transformer can be used in order to deliver the required

levels to the converter’s inputs, see Figure 21. For example if a 3.3 V standard CMOS logic is used for clock

generation, a minicircuits T4–1H transformer can be used for 2x voltage step-up. This provides greater than

6 V differential swing at the secondary of the transformer , which provides greater than 3 V swings to both CLK+

and CLK– terminals of THS1060. The center tap of the transformer secondary is connected to the V

CM

terminal

of the THS1060 for proper dc biasing.

Both the transformer and the clock source should be placed close to THS1060 to avoid transmission line effects.

3.3 V TTL logic is not recommended with T4–1H transformer due to TTLs tendency to have lower output swings.

If the input to the transformer is a square wave (such as one generated by a digital driver), care must be taken

to ensure that the transformer’s bandwidth does not limit the signal’s rise time and effectively alter its shape and

duty cycle characteristics. For a 60 MSPS rate, the transformer’s bandwidth should be at least 300 MHz. A low

phase noise sinewave can also be used to effectively drive the THS1060. In this case, the bandwidth of the

transformer becomes less critical, as long as it can accommodate the frequency of interest (for example, 60

MHz). The turns ratio should be chosen to ensure appropriate levels at the device’s input. If the clock signal

is fed through a transmission line of characteristic impedance Zo , then the secondary of the transformer should

be terminated with a resistor of nZo , where n is the transformer’s impedance ratio (1:n) as shown in Figure 21.

Alternatively a series termination can be used at the clock source.

THS1060

10-BIT 60 MSPS IF SAMPLING COMMUNICATIONS

ANALOG-TO-DIGITAL CONVERTER

SLAS212 – MARCH 2000

16

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

APPLICATION INFORMATION

CLK+

V

CM

THS1060

CLK–

Impedance Ratio = 1:4

3 V – 5 V p-p

0.01 µF 0.1 µF

T4-1H

Z

o

4 Z

o

0.1 µF

Figure 21. Coaxial Clock Source

The clock signals, CLK+ and CLK– should be well matched and must both be driven.

A transformer ensures minimal skew between the two complementary channels. However, skew levels of up

to 500 ps between CLK+ and CLK– can be tolerated with some performance degradation.

The clock input can also be driven differentially with a 5 V TTL signal by using an RF transformer to convert the

TTL signal to a differential signal. The TTL signal is ac coupled to the positive primary terminal with a high pass

circuit. The negative terminal of the transformer is connected to ground (see Figure 22). The transformer

secondary is connected to the CLK inputs.

CLK+

CLK–

V

CM

THS1060

0.01 µF 0.1 µF

5 V TTL CLK

0.1 µF

Impedance Ratio = 1:4

T4 - 1H

Figure 22. TTL Clock Input

THS1060

10-BIT 60 MSPS IF SAMPLING COMMUNICATIONS

ANALOG-TO-DIGITAL CONVERTER

SLAS212 – MARCH 2000

17

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

APPLICATION INFORMATION

using the analog input

The THS1060 obtains optimum performance when the analog signal inputs are driven differentially . The circuit

below shows the optimum configuration, see Figure 23. The signal is fed to the primary of an RF transformer.

Since the input signal must be biased around the common mode voltage of the internal circuitry , the common

mode (VCM) reference from the THS1060 is connected to the center-tap of the secondary. To ensure a steady

low noise V

CM

reference the best performance is obtained when the VCM output is connected to ground with

a 0.1 µF and 0.01 µF low inductance capacitor.

R

VIN+

V

CM

THS1060

0.01 µF 0.1 µF

50 Ω

1:1

VIN–

50 Ω

ac Signal

T1-1T

Figure 23. THS1060 With Coaxial Feed

When it is necessary to buffer or apply a gain to the incoming analog signal, it is also possible to combine a

single-ended amplifier with an RF transformer as shown in Figure 24. For this application, a wide-band current

mode feedback amplifier such as the THS3001 is best. The single ended output allows the use of standard

passive filters between the amplifier output and the primary . In this case, the SFDR of the op amp is not as critical

as that of the A/D converter. While harmonics generated from within the A/D converter fold back into the first

Nyquist zone, harmonics generated externally in the op amps can be filtered out with passive filters.

VIN+

V

IN–

V

CM

THS1060

0.1 µF 0.01 µF

_

+

BPF

10 Ω

1 kΩ1 kΩ

R

T

IF Input

THS3001

Impedance Ratio = 1:n

Figure 24. IF Input Buffered with THS3001 Op Amp

THS1060

10-BIT 60 MSPS IF SAMPLING COMMUNICATIONS

ANALOG-TO-DIGITAL CONVERTER

SLAS212 – MARCH 2000

18

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

APPLICATION INFORMATION

digital outputs

The digital outputs can drive either TTL or 5-V CMOS inputs when DRVDD = 5 V . T o reduce capacitive loading,

each digital output of the THS1060 should drive only one digital input. The CMOS output drivers are capable

of handling up to a 15 pF load. For better SNR performance, use 3.3 V for DRVDD. Resistors of 200-Ω in series

with the digital output can be used for optimizing SNR performance.

power supplies

Best performance is obtained when A VDD is kept separate from DVDD. Regulated or linear supplies, as opposed

to switched power supplies, must be used to minimize supply noise. It is also recommended to partition the

analog and digital components on the board in such a way that the analog supply plane does not overlap with

the digital supply plane in order to limit dielectric coupling between the different supplies.

using the TI PowerPAD

While it is not necessary to use the T exas Instruments PowerP AD to meet the minimum and maximum specs

indicated in this spec sheet, proper use of the PowerPAD will improve the performance of the THS1060

especially at TA = 85°C.

For high speed sampling applications (around 60 MSPS), significant performance enhancement above the

specified values can be achieved by properly applying the PowerPAD. This will maintain the junction

temperature of the device at significantly lower levels and render the device even more insensitive to duty cycle

variations on the clock, as shown in Figure 18.

The THS1060 package makes use of the Texas Instruments PowerPAD which, when soldered to a thermal

land, creates a highly efficient path for heat energy and ground noise currents from the circuit die to the PCB

ground plane. The silicon die in a PowerPAD package is bonded to a copper alloy plate with a thin layer of

thermally and electrically conductive epoxy. The copper alloy plate or PowerPAD is exposed on the bottom

of the device package for a direct solder attachment to a PCB land or conductive pad. The land dimensions

should have minimum dimensions equal to the package dimensions minus 2 mm, see Figure 25.

For a multilayer circuit board, a second land having dimensions equal to or greater than the land to which the

device is soldered should be placed on the back of the circuit board (see Figure 26). A total of 9 thermal vias

or plated through-holes should be used to connect the two lands to a ground plane (buried or otherwise) having

a minimum total area of 3 inches square in 1 oz. copper. For the THS1060 package, the thermal via centers

should be spaced at a minimum of 1 mm. The ground plane need not be directly under or centered around the

device footprint if a wide ground plane thermal run having a width on the order of the device is used to channel

the heat from the vias to the larger portion of the ground plane. The THS1060 package has a standoff of 0.19

mm or 7.5 mils. In order to apply the proper amount of solder paste to the land. a solder paste stencil with a 6

mils thickness is recommended for this device. Too thin a stencil may lead to an inadequate connection to the

land. Too thick a stencil may lead to beading of solder in the vicinity of the pins which may lead to shorts. For

more information, refer to Texas Instruments literature number SLMA002

PowerPAD Thermally Enhanced

Package

.

THS1060

10-BIT 60 MSPS IF SAMPLING COMMUNICATIONS

ANALOG-TO-DIGITAL CONVERTER

SLAS212 – MARCH 2000

19

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

APPLICATION INFORMATION

using the TI PowerPAD (continued)

5 mm

5 mm

2 x 1.25 mm1.25 mm

2 x 1.25 mm

1.25 mm

0.33 mm Diameter

Plated Through Hole

Figure 25. Thermal Land (top view)

Thermal

Land

PWB

PHP (S-PQFP-G48)

Plated Through Hole

Figure 26. Top and Bottom Thermal Lands With Plated Through Holes (side view)

THS1060

10-BIT 60 MSPS IF SAMPLING COMMUNICATIONS

ANALOG-TO-DIGITAL CONVERTER

SLAS212 – MARCH 2000

20

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

MECHANICAL DATA

PHP (S-PQFP-G48) PowerPAD PLASTIC QUAD FLATP ACK

Thermal Pad

(see Note D)

Gage Plane

0,13 NOM

0,25

0,45

0,75

Seating Plane

4146927/A 01/98

0,17

0,27

24

25

13

12

SQ

36

37

7,20

6,80

48

1

5,50 TYP

SQ

8,80

9,20

1,05

0,95

1,20 MAX

0,50

M

0,08

0,08

0°–7°

0,05

0,15

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusions.

D. The package thermal performance may be enhanced by bonding the thermal pad to an external thermal plane. This pad is electrically

and thermally connected to the backside of the die and possibly selected leads.

E. Falls within JEDEC MO-153

IMPORTANT NOTICE

T exas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue

any product or service without notice, and advise customers to obtain the latest version of relevant information

to verify, before placing orders, that information being relied on is current and complete. All products are sold

subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those

pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in

accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent

TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily

performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer’s applications, adequate design and operating

safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent

that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other

intellectual property right of TI covering or relating to any combination, machine, or process in which such

semiconductor products or services might be or are used. TI’s publication of information regarding any third

party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.

Copyright 2000, Texas Instruments Incorporated

Loading...

Loading...