Data Manual

2000 PCIBus Solutions

Printed in U.S.A.

03/00

SCPS045C

PCI1410

PC Card Controllers

Data Manual

Literature Number: SCPS045C

March 2000

Printed on Recycled Paper

IMPORTANT NOTICE

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products

or to discontinue any product or service without notice, and advise customers to obtain the latest

version of relevant information to verify, before placing orders, that information being relied on

is current and complete. All products are sold subject to the terms and conditions of sale supplied

at the time of order acknowledgement, including those pertaining to warranty, patent

infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the

time of sale in accordance with TI’s standard warranty. Testing and other quality control

techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing

of all parameters of each device is not necessarily performed, except those mandated by

government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE

POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR

ENVIRONMENTAL DAMAGE (“CRITICAL APPLICATIONS”). TI SEMICONDUCTOR

PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR

USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY

AT THE CUSTOMER’S RISK.

In order to minimize risks associated with the customer’s applications, adequate design and

operating safeguards must be provided by the customer to minimize inherent or procedural

hazards.

TI assumes no liability for applications assistance or customer product design. TI does not

warrant or represent that any license, either express or implied, is granted under any patent right,

copyright, mask work right, or other intellectual property right of TI covering or relating to any

combination, machine, or process in which such semiconductor products or services might be

or are used. TI’s publication of information regarding any third party’s products or services does

not constitute TI’s approval, warranty or endorsement thereof.

Copyright 2000, Texas Instruments Incorporated

Contents

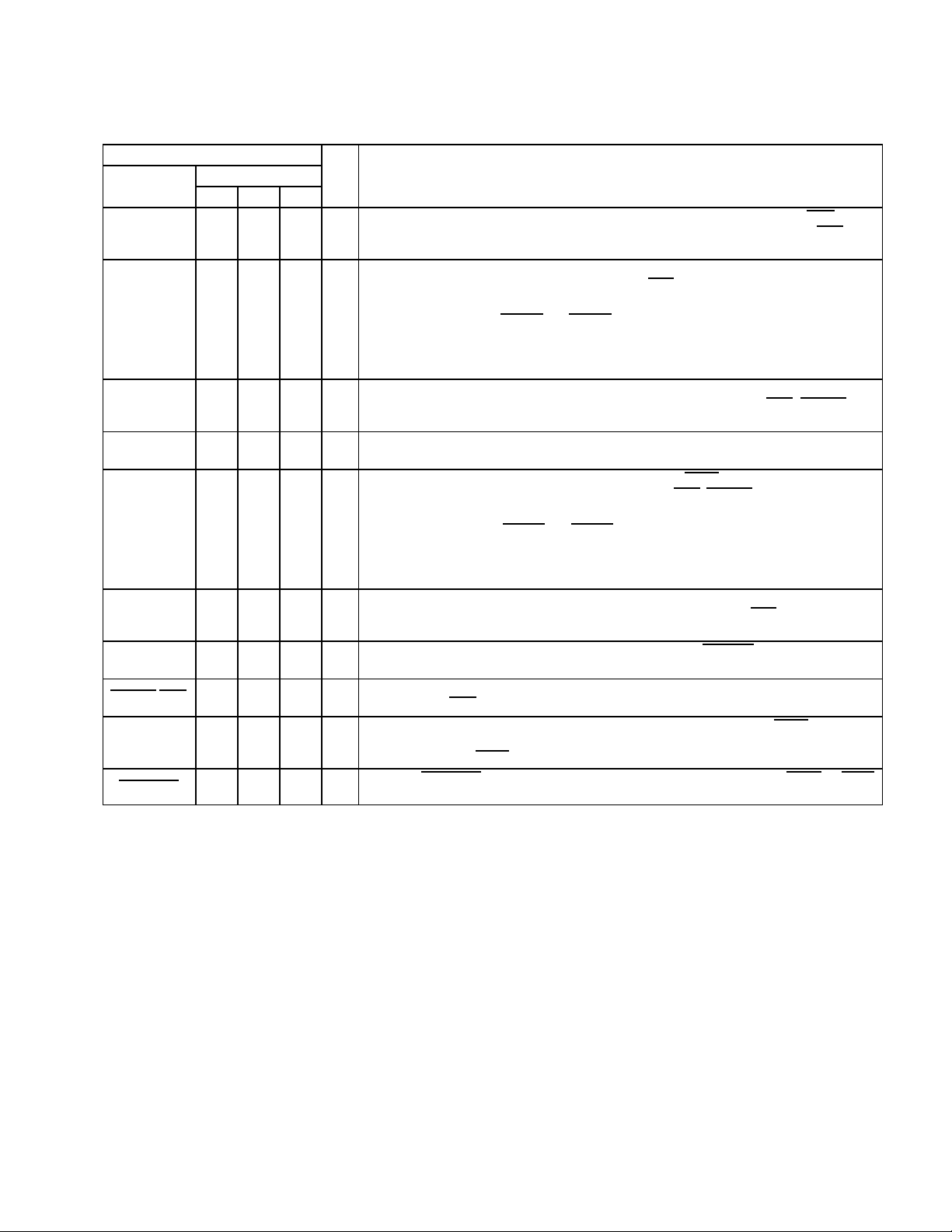

Section Title Page

1 Introduction 1–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1 Description 1–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2 Features 1–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3 Related Documents 1–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4 Ordering Information 1–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2 Terminal Descriptions 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3 Feature/Protocol Descriptions 3–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1 Power Supply Sequencing 3–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2 I/O Characteristics 3–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3 Clamping Voltages 3–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4 Peripheral Component Interconnect (PCI) Interface 3–2. . . . . . . . . . . . . .

3.4.1 PCI Bus Lock (LOCK

3.4.2 Loading Subsystem Identification 3–3. . . . . . . . . . . . . . . . . . . . .

3.5 PC Card Applications 3–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.1 PC Card Insertion/Removal and Recognition 3–3. . . . . . . . . . .

3.5.2 P

3.5.3 Zoomed Video Support 3–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.4 Ultra Zoomed Video 3–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.5 Internal Ring Oscillator 3–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.6 Integrated Pullup Resistors For PC Card Interface 3–7. . . . . .

3.5.7 SPKROUT and CAUDPWM Usage 3–7. . . . . . . . . . . . . . . . . . .

3.5.8 LED Socket Activity Indicators 3–8. . . . . . . . . . . . . . . . . . . . . . . .

3.5.9 PC Card-16 Distributed DMA Support 3–8. . . . . . . . . . . . . . . . .

3.5.10 PC Card-16 PC/PCI DMA 3–10. . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.11 CardBus Socket Registers 3–10. . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6 Serial Bus Interface 3–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.1 Serial Bus Interface Implementation 3–11. . . . . . . . . . . . . . . . . . .

3.6.2 Serial Bus Interface Protocol 3–11. . . . . . . . . . . . . . . . . . . . . . . . .

3.6.3 Serial Bus EEPROM Application 3–13. . . . . . . . . . . . . . . . . . . . . .

3.6.4 Accessing Serial Bus Devices Through Software 3–14. . . . . . . .

3.7 Programmable Interrupt Subsystem 3–15. . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.7.1 PC Card Functional and Card Status Change Interrupts 3–15.

3.7.2 Interrupt Masks and Flags 3–17. . . . . . . . . . . . . . . . . . . . . . . . . . .

3.7.3 Using Parallel IRQ Interrupts 3–17. . . . . . . . . . . . . . . . . . . . . . . . .

3.7.4 Using Parallel PCI Interrupts 3–18. . . . . . . . . . . . . . . . . . . . . . . . .

2

C Power-Switch Interface (TPS2211) 3–4. . . . . . . . . . . . . . .

)3–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

iii

3.7.5 Using Serialized IRQSER Interrupts 3–18. . . . . . . . . . . . . . . . . . .

3.7.6 SMI Support in the PCI1410 3–18. . . . . . . . . . . . . . . . . . . . . . . . . .

3.8 Power Management Overview 3–19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8.1 Clock Run Protocol 3–19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8.2 CardBus PC Card Power Management 3–19. . . . . . . . . . . . . . . .

3.8.3 16-Bit PC Card Power Management 3–19. . . . . . . . . . . . . . . . . . .

3.8.4 Suspend Mode 3–20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8.5 Requirements for Suspend Mode 3–21. . . . . . . . . . . . . . . . . . . . .

3.8.6 Ring Indicate 3–21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8.7 PCI Power Management 3–22. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8.8 CardBus Bridge Power Management 3–23. . . . . . . . . . . . . . . . . .

3.8.9 ACPI Support 3–23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8.10 Master List of PME

Context Bits and

Global Reset Only Bits 3–24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4 PC Card Controller Programming Model 4–1. . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1 PCI Configuration Registers 4–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2 Vendor ID Register 4–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3 Device ID Register 4–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4 Command Register 4–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.5 Status Register 4–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.6 Revision ID Register 4–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.7 PCI Class Code Register 4–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.8 Cache Line Size Register 4–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.9 Latency Timer Register 4–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.10 Header Type Register 4–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.11 BIST Register 4–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.12 CardBus Socket/ExCA Base-Address Register 4–7. . . . . . . . . . . . . . . . . .

4.13 Capability Pointer Register 4–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.14 Secondary Status Register 4–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.15 PCI Bus Number Register 4–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.16 CardBus Bus Number Register 4–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.17 Subordinate Bus Number Register 4–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.18 CardBus Latency Timer Register 4–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.19 Memory Base Registers 0, 1 4–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.20 Memory Limit Registers 0, 1 4–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.21 I/O Base Registers 0, 1 4–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.22 I/O Limit Registers 0, 1 4–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.23 Interrupt Line Register 4–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.24 Interrupt Pin Register 4–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.25 Bridge Control Register 4–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.26 Subsystem Vendor ID Register 4–15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.27 Subsystem ID Register 4–15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.28 PC Card 16-bit I/F Legacy-Mode Base-Address Register 4–15. . . . . . . . .

4.29 System Control Register 4–16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

iv

4.30 Multifunction Routing Register 4–19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.31 Retry Status Register 4–20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.32 Card Control Register 4–21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.33 Device Control Register 4–22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.34 Diagnostic Register 4–23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.35 Socket DMA Register 0 4–24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.36 Socket DMA Register 1 4–25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.37 Capability ID Register 4–26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.38 Next-Item Pointer Register 4–26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.39 Power Management Capabilities Register 4–27. . . . . . . . . . . . . . . . . . . . . .

4.40 Power Management Control/Status Register 4–28. . . . . . . . . . . . . . . . . . . .

4.41 Power Management Control/Status Bridge Support Extensions

Register 4–29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.42 Power Management Data Register 4–29. . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.43 General-Purpose Event Status Register 4–30. . . . . . . . . . . . . . . . . . . . . . . .

4.44 General-Purpose Event Enable Register 4–31. . . . . . . . . . . . . . . . . . . . . . .

4.45 General-Purpose Input Register 4–32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.46 General-Purpose Output Register 4–33. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.47 Serial Bus Data Register 4–33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.48 Serial Bus Index Register 4–34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.49 Serial Bus Slave Address Register 4–34. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.50 Serial Bus Control and Status Register 4–35. . . . . . . . . . . . . . . . . . . . . . . . .

5 ExCA Compatibility Registers 5–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1 ExCA Identification and Revision Register 5–4. . . . . . . . . . . . . . . . . . . . . .

5.2 ExCA Interface Status Register 5–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3 ExCA Power Control Register 5–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.4 ExCA Interrupt and General Control Register 5–8. . . . . . . . . . . . . . . . . . .

5.5 ExCA Card Status-Change Register 5–9. . . . . . . . . . . . . . . . . . . . . . . . . . .

5.6 ExCA Card Status-Change-Interrupt Configuration Register 5–10. . . . . . .

5.7 ExCA Address Window Enable Register 5–11. . . . . . . . . . . . . . . . . . . . . . . .

5.8 ExCA I/O Window Control Register 5–12. . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.9 ExCA I/O Windows 0 and 1 Start-Address Low-Byte Registers 5–13. . . .

5.10 ExCA I/O Windows 0 and 1 Start-Address High-Byte Registers 5–13. . . .

5.11 ExCA I/O Windows 0 and 1 End-Address Low-Byte Registers 5–14. . . . .

5.12 ExCA I/O Windows 0 and 1 End-Address High-Byte Registers 5–14. . . .

5.13 ExCA Memory Windows 0–4 Start-Address Low-Byte Registers 5–15. . .

5.14 ExCA Memory Windows 0–4 Start-Address High-Byte Registers 5–16. . .

5.15 ExCA Memory Windows 0–4 End-Address Low-Byte Registers 5–17. . . .

5.16 ExCA Memory Windows 0–4 End-Address High-Byte Registers 5–18. . .

5.17 ExCA Memory Windows 0–4 Offset-Address Low-Byte Registers 5–19. .

5.18 ExCA Memory Windows 0–4 Offset-Address High-Byte Registers 5–20.

5.19 ExCA Card Detect and General Control Register 5–21. . . . . . . . . . . . . . . .

5.20 ExCA Global Control Register 5–22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.21 ExCA I/O Windows 0 and 1 Offset-Address Low-Byte Registers 5–23. . .

v

5.22 ExCA I/O Windows 0 and 1 Offset-Address High-Byte Registers 5–23. . .

5.23 ExCA Memory Windows 0–4 Page Register 5–24. . . . . . . . . . . . . . . . . . . .

6 CardBus Socket Registers 6–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.1 Socket Event Register 6–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.2 Socket Mask Register 6–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3 Socket Present State Register 6–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.4 Socket Force Event Register 6–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.5 Socket Control Register 6–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.6 Socket Power Management Register 6–9. . . . . . . . . . . . . . . . . . . . . . . . . . .

7 Distributed DMA (DDMA) Registers 7–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.1 DDMA Current Address/Base-Address Register 7–1. . . . . . . . . . . . . . . . .

7.2 DDMA Page Register 7–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.3 DDMA Current Count/Base Count Register 7–2. . . . . . . . . . . . . . . . . . . . .

7.4 DDMA Command Register 7–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.5 DDMA Status Register 7–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.6 DDMA Request Register 7–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.7 DDMA Mode Register 7–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.8 DDMA Master Clear Register 7–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.9 DDMA Multichannel/Mask Register 7–5. . . . . . . . . . . . . . . . . . . . . . . . . . . .

8 Electrical Characteristics 8–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.1 Absolute Maximum Ratings Over Operating

Temperature Ranges 8–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.2 Recommended Operating Conditions 8–2. . . . . . . . . . . . . . . . . . . . . . . . . .

8.3 Electrical Characteristics Over Recommended

Operating Conditions 8–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.4 PCI Clock/Reset Timing Requirements Over Recommended

Ranges of Supply Voltage and Operating Free-Air Temperature 8–4. . .

8.5 PCI Timing Requirements Over Recommended Ranges

of Supply Voltage and Operating Free-Air Temperature 8–4. . . . . . . . . . .

8.6 PC Card Cycle Timing 8–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9 Mechanical Information 9–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

vi

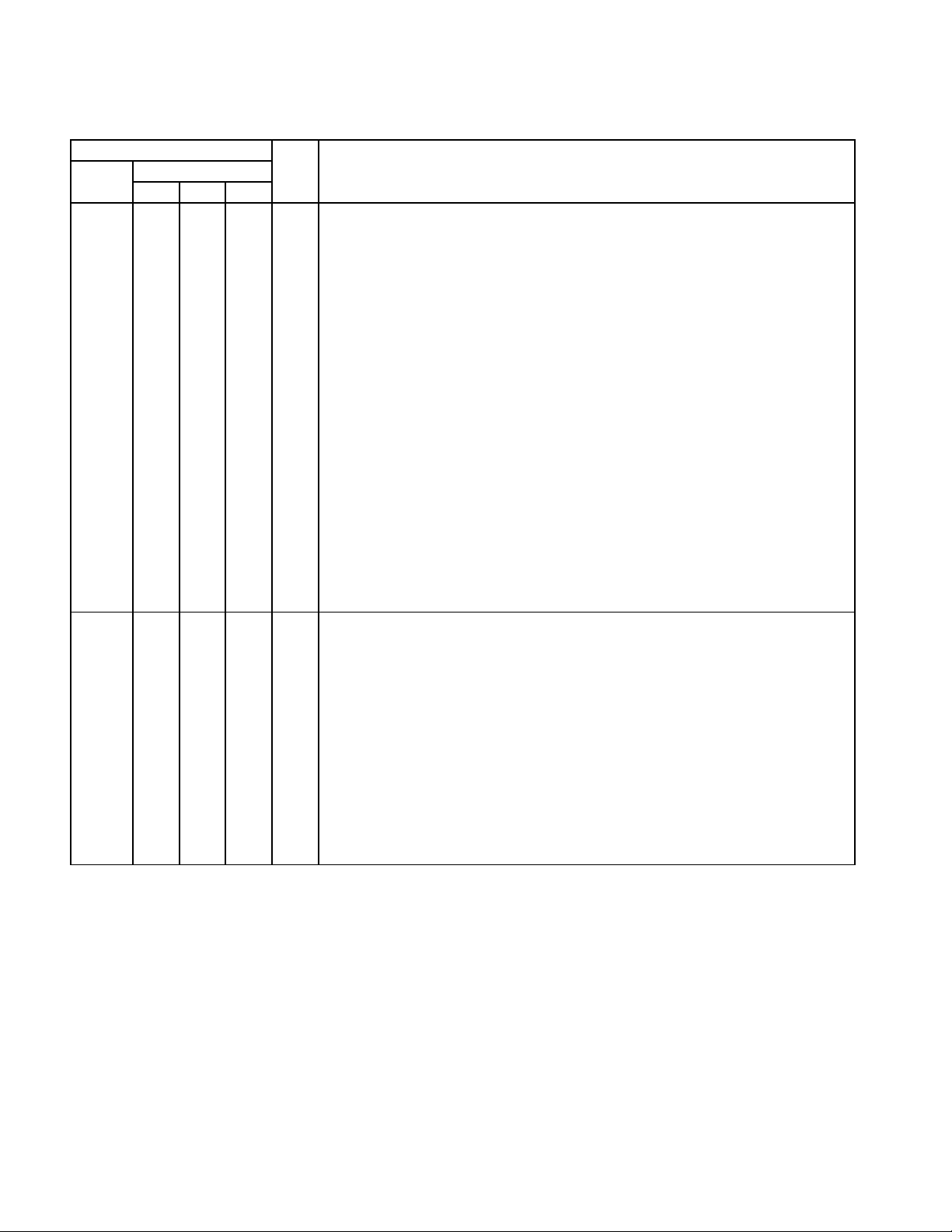

List of Illustrations

Figure Title Page

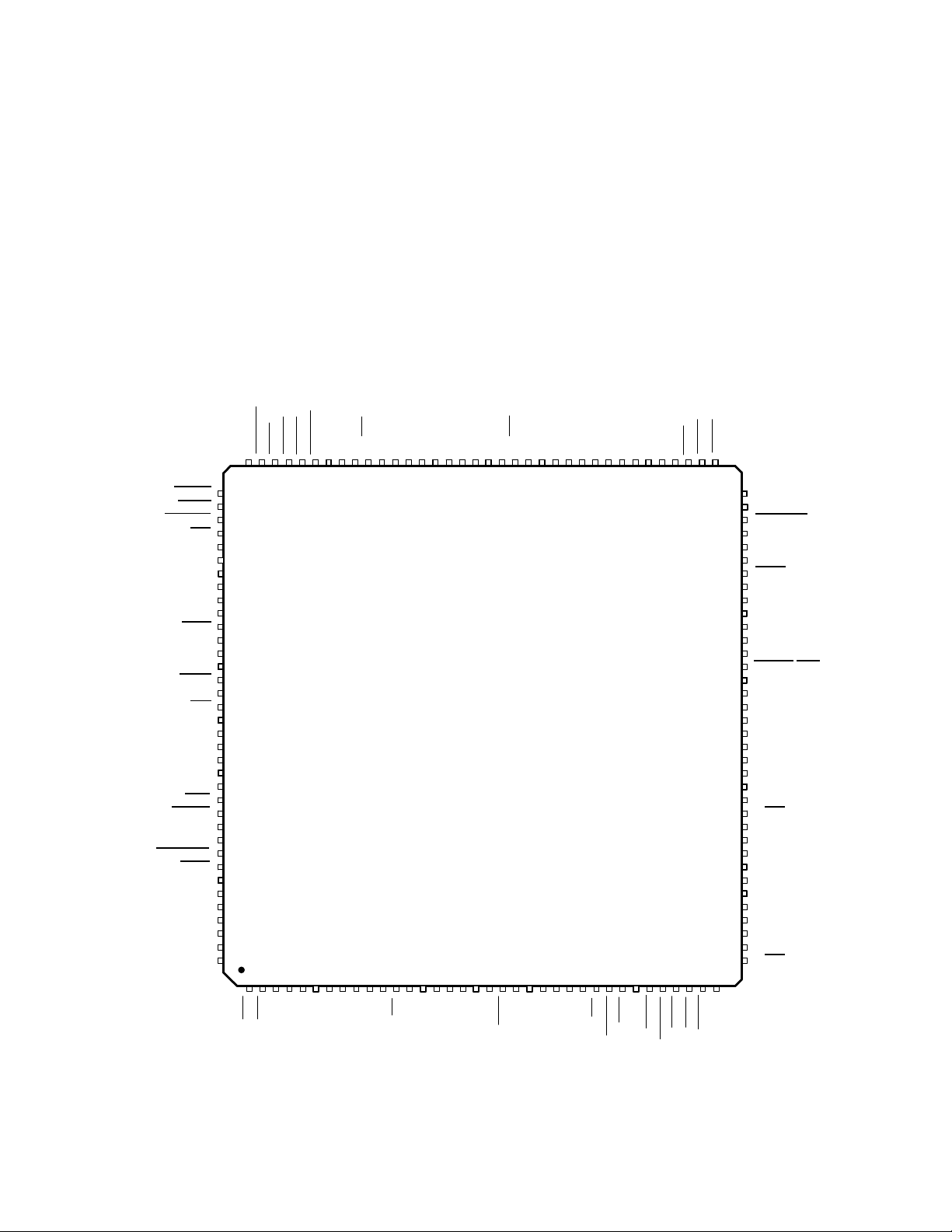

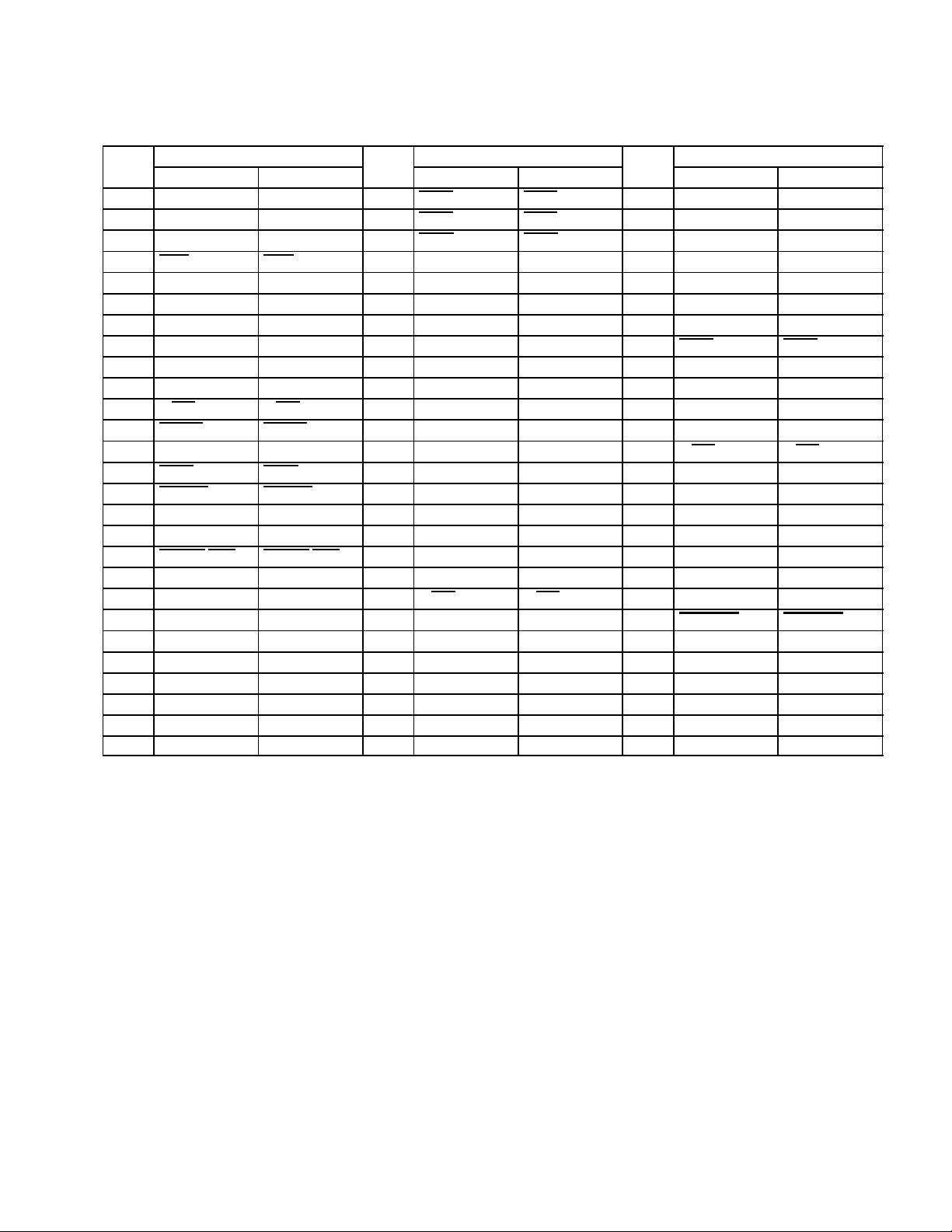

2–1 PCI-to-CardBus Terminal Diagram 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

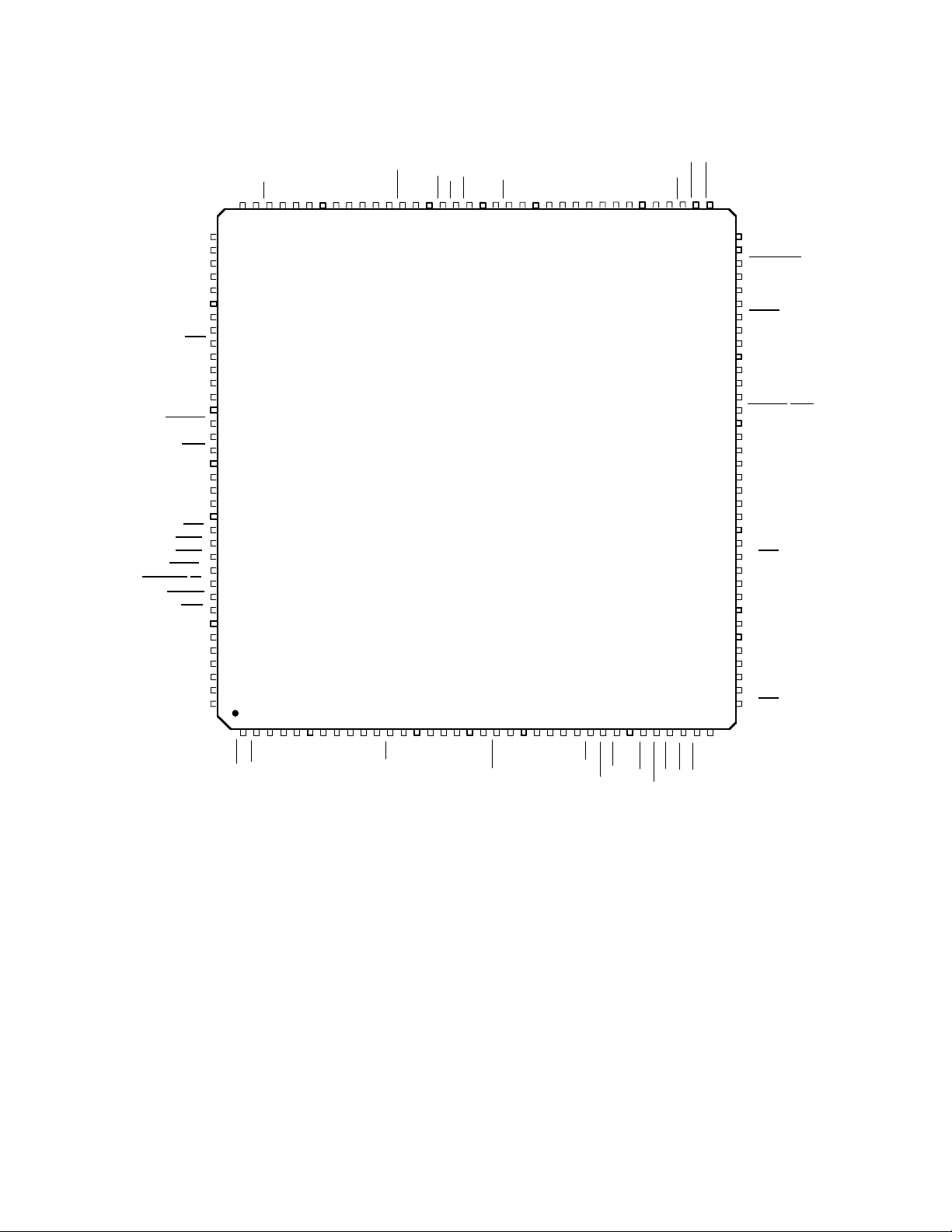

2–2 PCI-to-PC Card (16-Bit) Terminal Diagram 2–2. . . . . . . . . . . . . . . . . . . . . . . . . . .

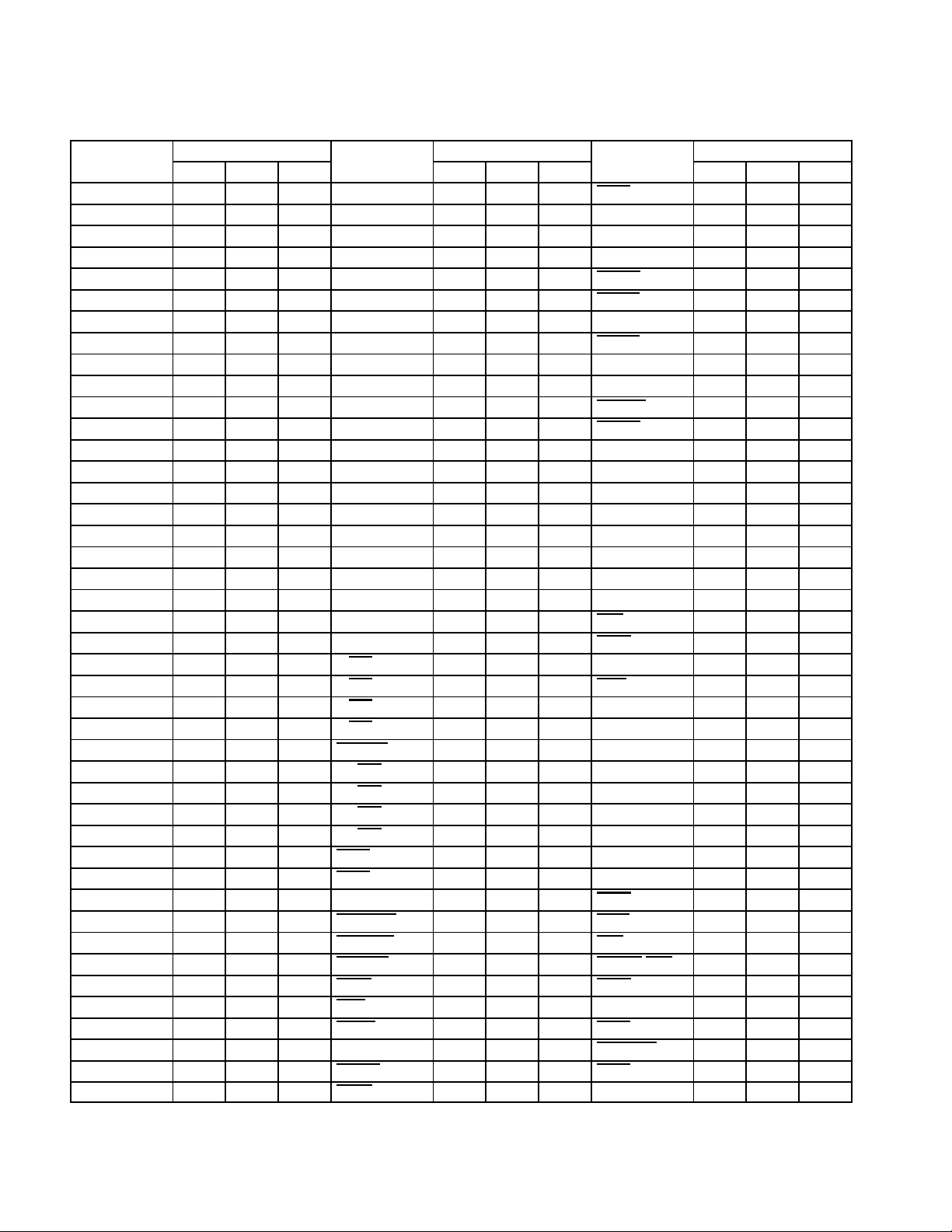

2–3 GGU Package Terminal Diagram 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–4 GHK Package Terminal Diagram 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–1 PCI1410 Simplified Block Diagram 3–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–2 3-State Bidirectional Buffer 3–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–3 TPS2211 Terminal Assignments 3–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–4 TPS2211 Typical Application 3–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–5 Zoomed Video Implementation Using PCI1410 3–5. . . . . . . . . . . . . . . . . . . . . . .

3–6 Zoomed Video Switching Application 3–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–7 Sample Application of SPKROUT and CAUDPWM 3–8. . . . . . . . . . . . . . . . . . . .

3–8 Two Sample LED Circuits 3–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–9 Serial EEPROM Application 3–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–10 Serial Bus Start/Stop Conditions and Bit Transfers 3–12. . . . . . . . . . . . . . . . . . .

3–11 Serial Bus Protocol Acknowledge 3–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–12 Serial Bus Protocol – Byte Write 3–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–13 Serial Bus Protocol – Byte Read 3–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–14 EEPROM Interface Doubleword Data Collection 3–13. . . . . . . . . . . . . . . . . . . . .

3–15 EEPROM Data Format 3–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–16 IRQ Implementation 3–18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–17 Suspend Logic Diagram 3–20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–18 Signal Diagram of Suspend Function 3–21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–19 RI_OUT

3–20 Block Diagram of a Status/Enable Cell 3–24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–1 ExCA Register Access Through I/O 5–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–2 ExCA Register Access Through Memory 5–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–1 Accessing CardBus Socket Registers Through PCI Memory 6–1. . . . . . . . . . . .

Functional Diagram 3–22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

vii

List of Tables

Table Title Page

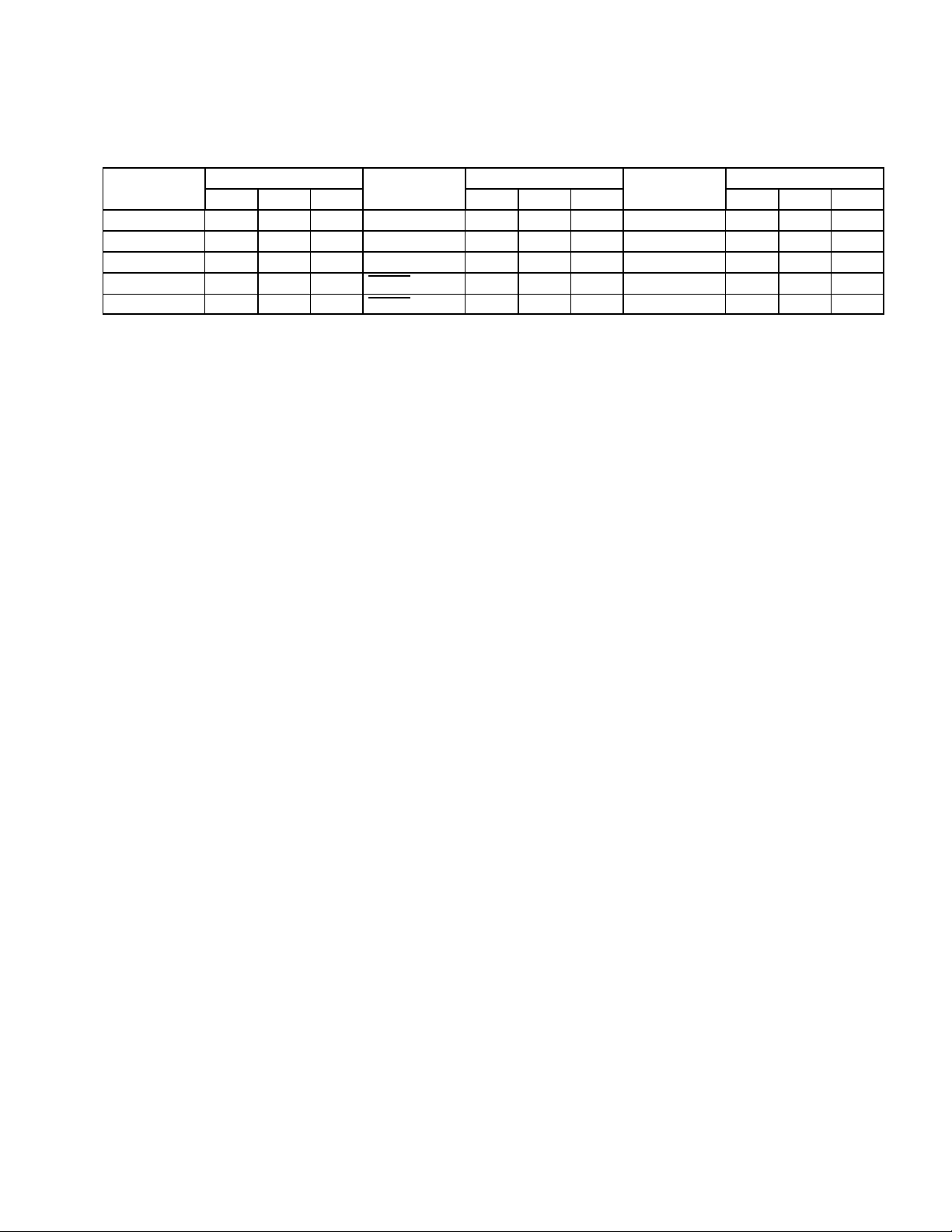

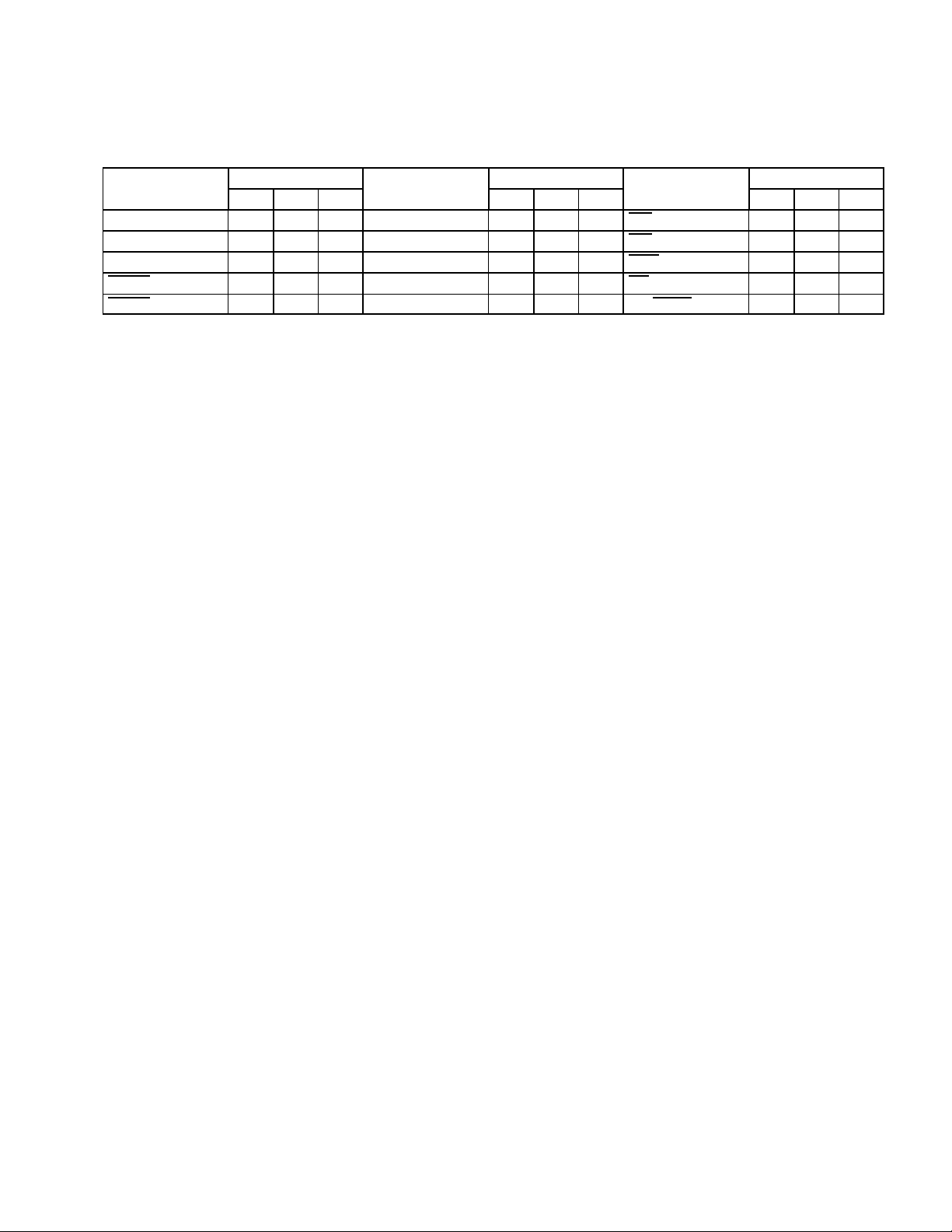

2–1 CardBus and 16-Bit PC Card Signal Names by GGU Terminal Number 2–4. .

2–2 CardBus and 16-Bit PC Card Signal Names by PGE Terminal Number 2–5. . .

2–3 CardBus and 16-Bit PC Card Signal Names by GHK Terminal Number 2–6. . .

2–4 CardBus PC Card Signal Names Sorted Alphabetically to

GGU/PGE/GHK Terminal Number 2–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–5 16-Bit PC Card Signal Names Sorted Alphabetically to

GGU/PGE/GHK Terminal Number 2–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

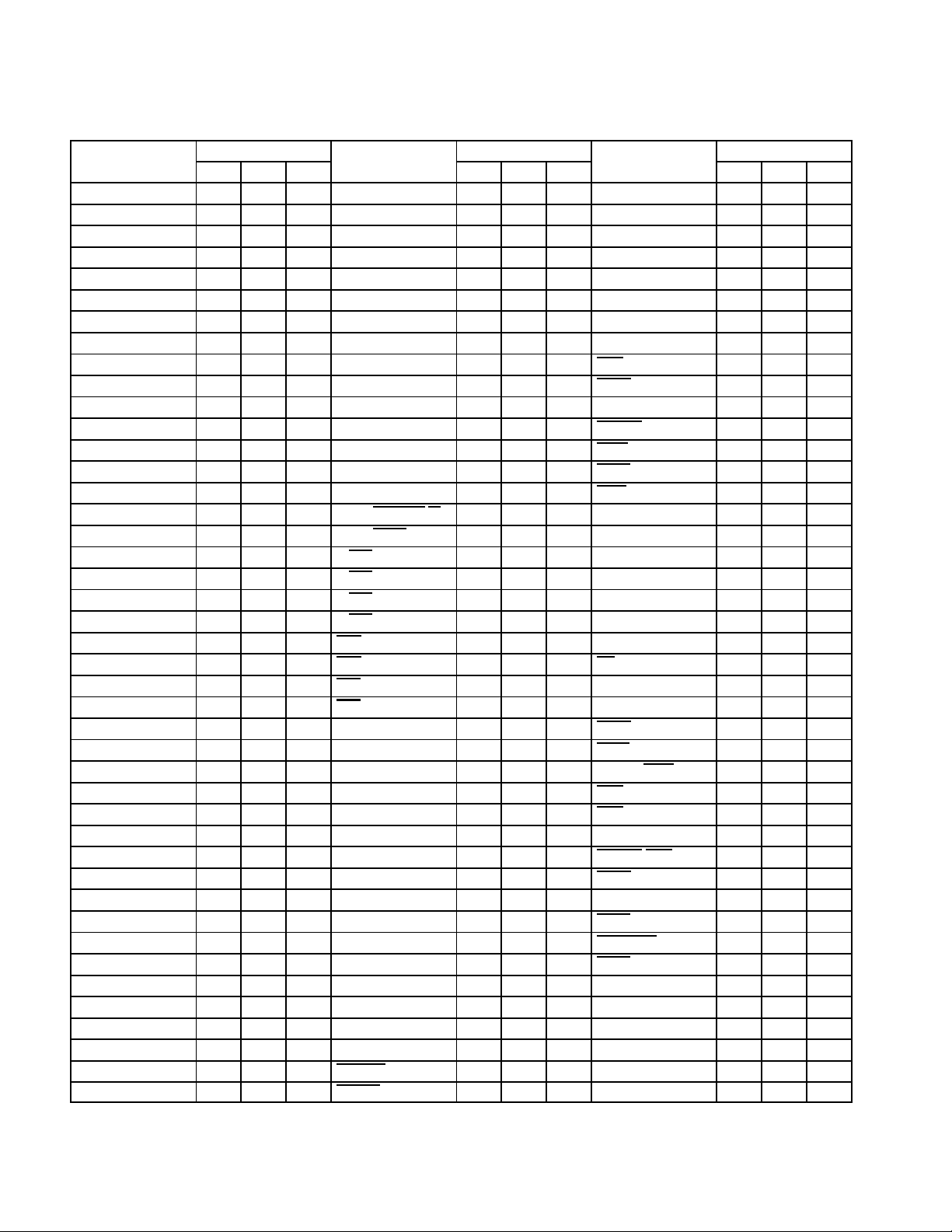

2–6 Power Supply Terminals 2–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–7 PC Card Power Switch Terminals 2–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–8 PCI System Terminals 2–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–9 PCI Address and Data Terminals 2–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–10 PCI Interface Control Terminals 2–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–11 Multifunction and Miscellaneous Terminals 2–15. . . . . . . . . . . . . . . . . . . . . . . . . .

2–12 16-Bit PC Card Address and Data Terminals 2–16. . . . . . . . . . . . . . . . . . . . . . . .

2–13 16-Bit PC Card Interface Control Terminals 2–17. . . . . . . . . . . . . . . . . . . . . . . . . .

2–14 CardBus PC Card Interface System Terminals 2–18. . . . . . . . . . . . . . . . . . . . . . .

2–15 CardBus PC Card Address and Data Terminals 2–19. . . . . . . . . . . . . . . . . . . . . .

2–16 CardBus PC Card Interface Control Terminals 2–20. . . . . . . . . . . . . . . . . . . . . . .

3–1 PC Card Card-Detect and Voltage-Sense Connections 3–4. . . . . . . . . . . . . . . .

3–2 Distributed DMA Registers 3–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–3 PC/PCI Channel Assignments 3–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–4 I/O Addresses Used for PC/PCI DMA 3–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–5 CardBus Socket Registers 3–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–6 Registers and Bits Loadable Through Serial EEPROM 3–13. . . . . . . . . . . . . . . . .

3–7 PCI1410 Registers Used to Program Serial Bus Devices 3–14. . . . . . . . . . . . . . .

3–8 Interrupt Mask and Flag Registers 3–16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–9 PC Card Interrupt Events and Description 3–16. . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–10 SMI Control 3–18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–11 Power Management Registers 3–23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–1 PCI Configuration Registers 4–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–2 Bit Field Access Tag Descriptions 4–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–3 Command Register 4–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–4 Status Register 4–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–5 Secondary Status Register 4–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–6 Bridge Control Register 4–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–7 System Control Register 4–17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–8 Multifunction Routing Register 4–19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–9 Retry Status Register 4–20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

viii

4–10 Card Control Register 4–21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–11 Device Control Register 4–22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–12 Diagnostic Register 4–23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–13 Socket DMA Register 0 4–24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–14 Socket DMA Register 1 4–25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–15 Power Management Capabilities Register 4–27. . . . . . . . . . . . . . . . . . . . . . . . . . .

4–16 Power Management Control/Status Register 4–28. . . . . . . . . . . . . . . . . . . . . . . .

4–17 Power Management Control/Status Bridge Support

Extensions Register 4–29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–18 General-Purpose Event Status Register 4–30. . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–19 General-Purpose Event Enable Register 4–31. . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–20 General-Purpose Input Register 4–32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–21 General-Purpose Output Register 4–33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–22 Serial Bus Data Register 4–33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–23 Serial Bus Index Register 4–34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–24 Serial Bus Slave Address Register 4–34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–25 Serial Bus Control and Status Register 4–35. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–1 ExCA Registers and Offsets 5–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–2 ExCA Identification and Revision Register 5–4. . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–3 ExCA Interface Status Register 5–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–4 ExCA Power Control Register 82365SL Support 5–6. . . . . . . . . . . . . . . . . . . . . .

5–5 ExCA Power Control Register 82365SL-DF Support 5–7. . . . . . . . . . . . . . . . . . .

5–6 ExCA Interrupt and General Control Register 5–8. . . . . . . . . . . . . . . . . . . . . . . . .

5–7 ExCA Card Status-Change Register 5–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–8 ExCA Card Status-Change-Interrupt Configuration Register 5–10. . . . . . . . . . . .

5–9 ExCA Address Window Enable Register 5–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–10 ExCA I/O Window Control Register 5–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–11 ExCA Memory Windows 0–4 Start-Address High-Byte Registers 5–16. . . . . . .

5–12 ExCA Memory Windows 0–4 End-Address High-Byte Registers 5–18. . . . . . . .

5–13 ExCA Memory Windows 0–4 Offset-Address High-Byte Registers 5–20. . . . . .

5–14 ExCA Card Detect and General Control Register 5–21. . . . . . . . . . . . . . . . . . . . .

5–15 ExCA Global Control Register 5–22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–1 CardBus Socket Registers 6–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–2 Socket Event Register 6–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–3 Socket Mask Register 6–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–4 Socket Present State Register 6–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–5 Socket Force Event Register 6–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–6 Socket Control Register 6–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–7 Socket Power Management Register 6–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

ix

7–1 Distributed DMA Registers 7–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–2 DDMA Command Register 7–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–3 DDMA Status Register 7–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–4 DDMA Mode Register 7–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–5 DDMA Multichannel/Mask Register 7–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

x

1 Introduction

1.1 Description

The TI PCI1410 is a high-performance PCI-to-PC Card controller that supports a single PC Card socket compliant

with the 1997 PC Card Standard. The PCI1410 provides features that make it the best choice for bridging between

PCI and PC Cards in both notebook and desktop computers. The 1997 PC Card Standard retains the 16-bit PC Card

specification defined in PCI Local Bus Specification and defines the new 32-bit PC Card, CardBus, capable of full

32-bit data transfers at 33 MHz. The PCI1410 supports both 16-bit and CardBus PC Cards, powered at 5 V or 3.3 V,

as required.

The PCI1410 is compliant with the PCI Local Bus Specification, and its PCI interface can act as either a PCI master

device or a PCI slave device. The PCI bus mastering is initiated during 16-bit PC Card DMA transfers or CardBus

PC Card bridging transactions. The PCI1410 is also compliant with the latest PCI Bus Power Management Interface

Specification and PCI Bus Power Management Interface Specification for PCI to CardBus Bridges.

All card signals are internally buffered to allow hot insertion and removal without external buffering. The PCI1410 is

register compatible with the Intel 82365SL-DF and 82365SL ExCA controllers. The PCI1410 internal data path logic

allows the host to access 8-, 16-, and 32-bit cards using full 32-bit PCI cycles for maximum performance. Independent

buffering and a pipeline architecture provide an unsurpassed performance level with sustained bursting. The

PCI1410 can also be programmed to accept fast posted writes to improve system-bus utilization.

Multiple system-interrupt signaling options are provided, including: parallel PCI, parallel ISA, serialized ISA, and

serialized PCI. Furthermore, general-purpose inputs and outputs are provided for the board designer to implement

sideband functions. Many other features designed into the PCI1410, such as socket activity light-emitting diode (LED)

outputs, are discussed in detail throughout the design specification.

An advanced complementary metal-oxide semiconductor (CMOS) process achieves low system power consumption

while operating at PCI clock rates up to 33 MHz. Several low-power modes enable the host power management

system to further reduce power consumption.

1.2 Features

The PCI1410 supports the following features:

• Ability to wake from D3

• Fully compatible with the Intel 430TX (Mobile Triton II) chipset

• A 144-terminal low-profile QFP (PGE), 144-terminal MicroStar BGA ball grid array (GGU) package, or

209-terminal MicroStar BGA (GHK) package

• 3.3-V core logic with universal PCI interfaces compatible with 3.3-V and 5-V PCI signaling environments

• Mix-and-match 5-V/3.3-V 16-bit PC Cards and 3.3-V CardBus Cards

• Single PC Card or CardBus slot with hot insertion and removal

• Burst transfers to maximize data throughput on the PCI bus and the CardBus bus

• Parallel PCI interrupts, parallel ISA IRQ and parallel PCI interrupts, serial ISA IRQ with parallel PCI

interrupts, and serial ISA IRQ and PCI interrupts

TI is a trademark of Texas Instruments.

MicroStar BGA is a trademark of Texas Instruments.

Intel is a trademark of Intel Corporation.

Other trademarks are the property of their respective owners.

and D3

hot

cold

1–1

• Serial EEPROM interface for loading subsystem ID and subsystem vendor ID

• Pipelined architecture allows greater than 130-Mbps sustained throughput from CardBus to PCI and from

PCI to CardBus

• Interface to parallel single-slot PC Card power interface switches like the TI TPS2211

• Up to five general-purpose I/Os

• Programmable output select for CLKRUN

• Five PCI memory windows and two I/O windows available to the 16-bit PC Card socket

• Two I/O windows and two memory windows available to the CardBus socket

• Exchangeable card architecture (ExCA) compatible registers are mapped in memory and I/O space

• Intel 82365SL-DF and 82365SL register compatible

• Distributed DMA (DDMA) and PC/PCI DMA

• 16-Bit DMA on the PC Card socket

• Ring indicate, SUSPEND

, PCI CLKRUN, and CardBus CCLKRUN

• Socket activity LED pins

• PCI bus lock (LOCK)

• Advanced submicron, low-power CMOS technology

• Internal ring oscillator

1.3 Related Documents

• Advanced Configuration and Power Interface (ACPI) Specification (Revision 2.0)

• PCI Bus Power Management Interface Specification (Revision 1.1)

• PCI Bus Power Management Interface Specification for PCI to CardBus Bridges (Revision 0.6)

• PCI Local Bus Specification (Revision 2.2)

• PCI Mobile Design Guide (Revision 1.0)

• PCI14xx Implementation Guide for D3 Wake-Up

• 1997 PC Card Standard

• PC 98

• PC 99

• Serialized IRQ Support for PCI Systems (Revision 6)

1.4 Ordering Information

ORDERING NUMBER NAME VOLTAGE PACKAGE

PCI1410 PC Card Controller 3.3-V, 5-V tolerant I/Os 144-terminal LQFP

144-terminal PBGA

209-terminal PBGA

1–2

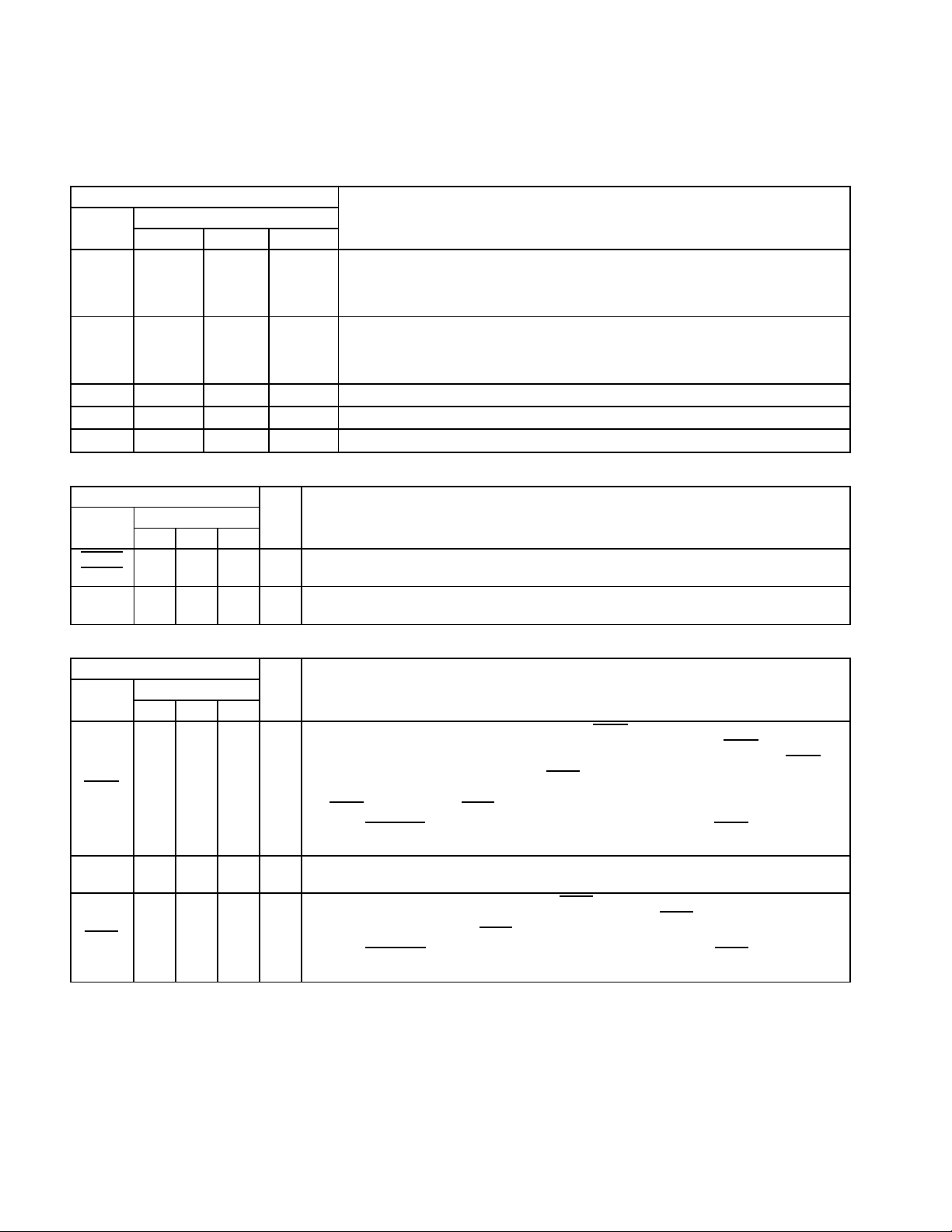

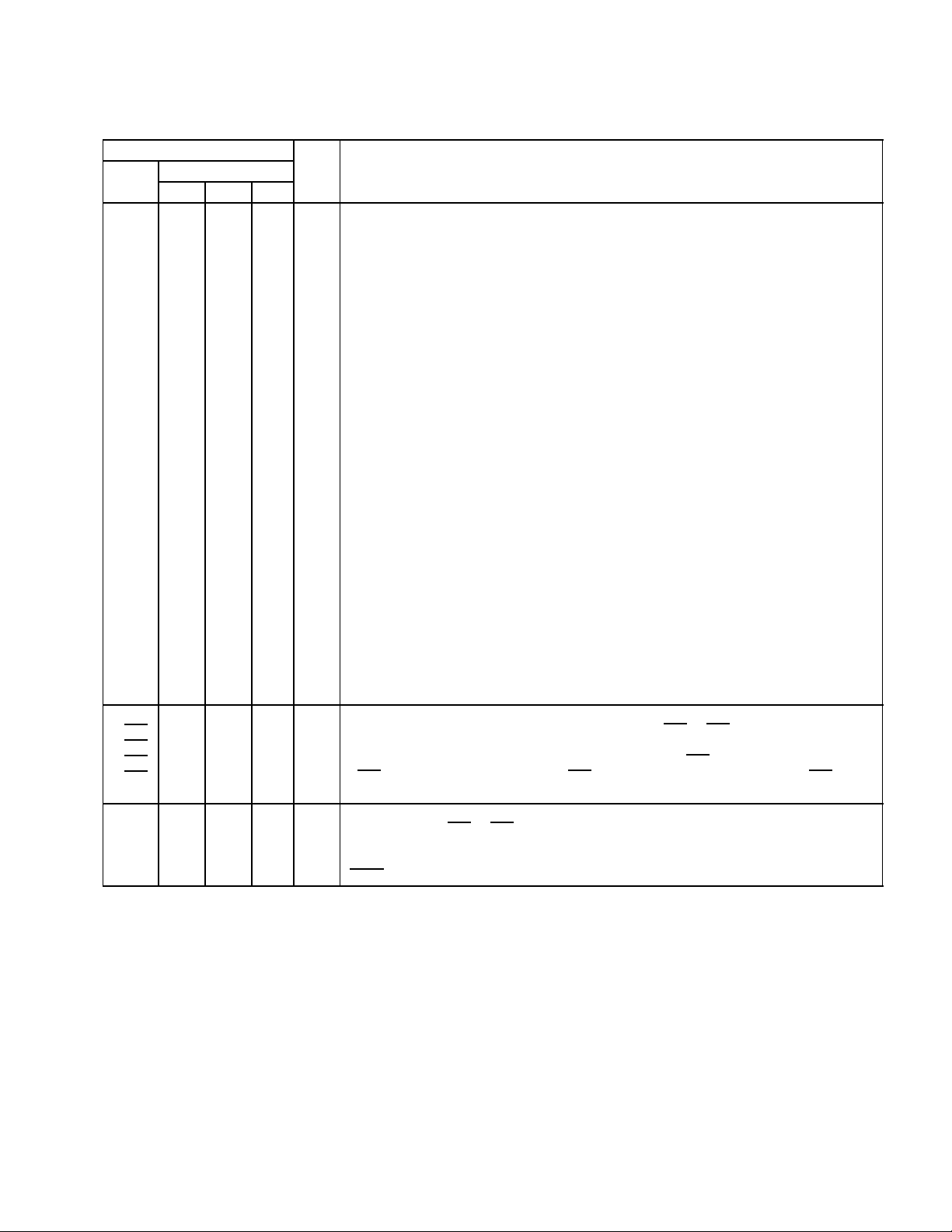

2 Terminal Descriptions

The PCI1410 is packaged in either a 144-terminal GGU MicroStar BGA or a 144-terminal PGE package. It is also

packaged in a 209-terminal GHK MicroStar BGA that is pin compatible with the TI PCI4410. The PCI4410 is a

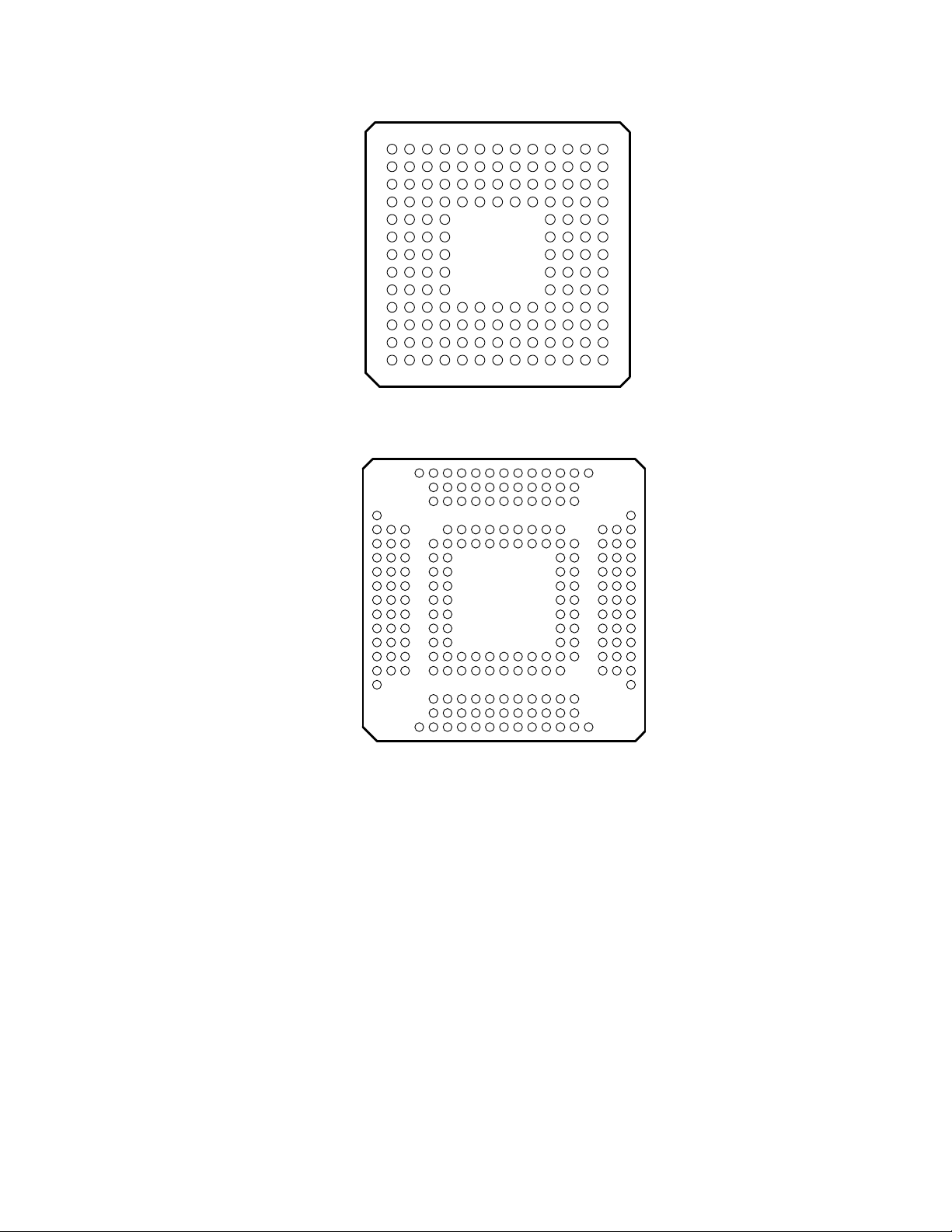

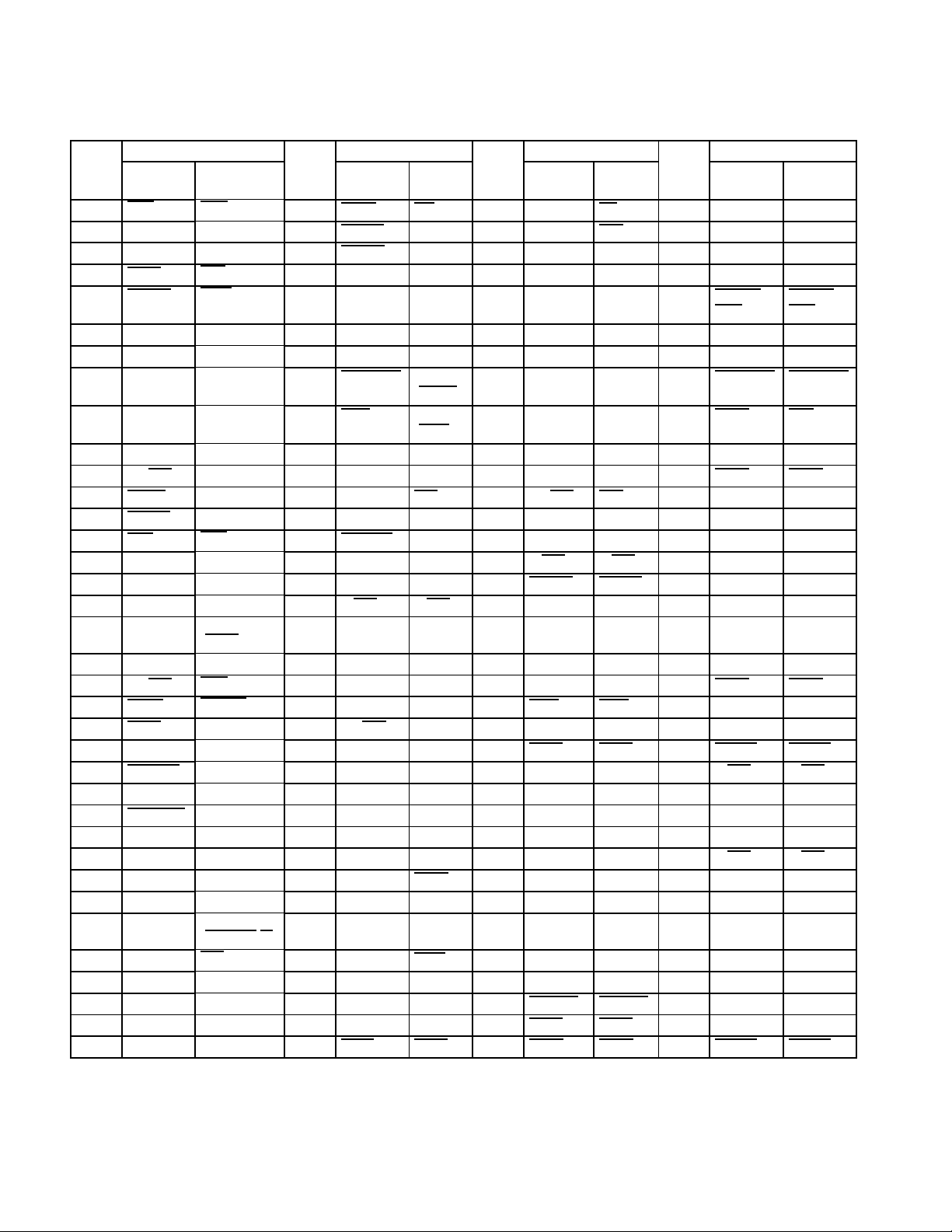

single-socket CardBus bridge with integrated OHCI link. Figure 2–1 is a PGE-package terminal diagram showing

PCI-to-CardBus signal names, and Figure 2–2 is a PGE-package terminal diagram showing PCI-to-PC Card signal

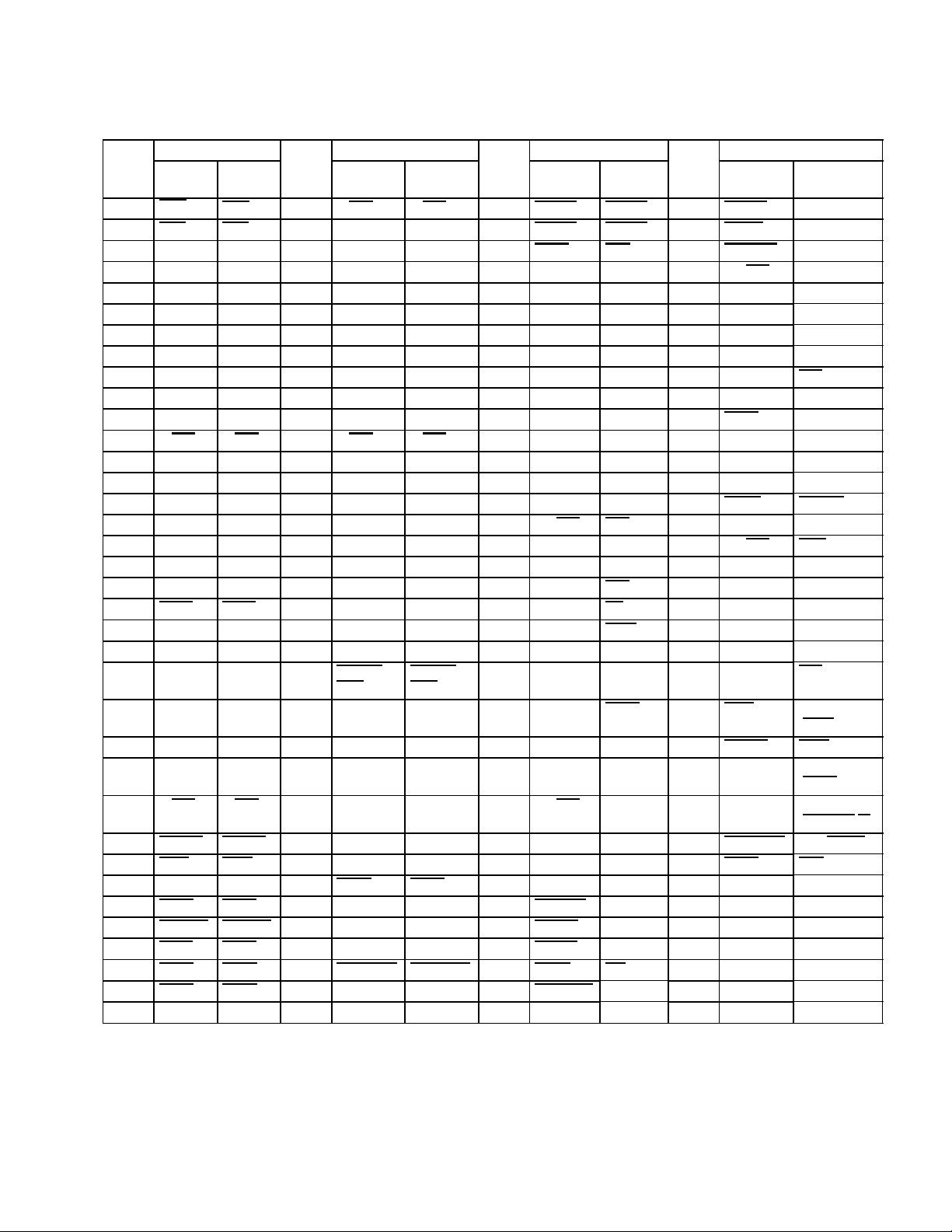

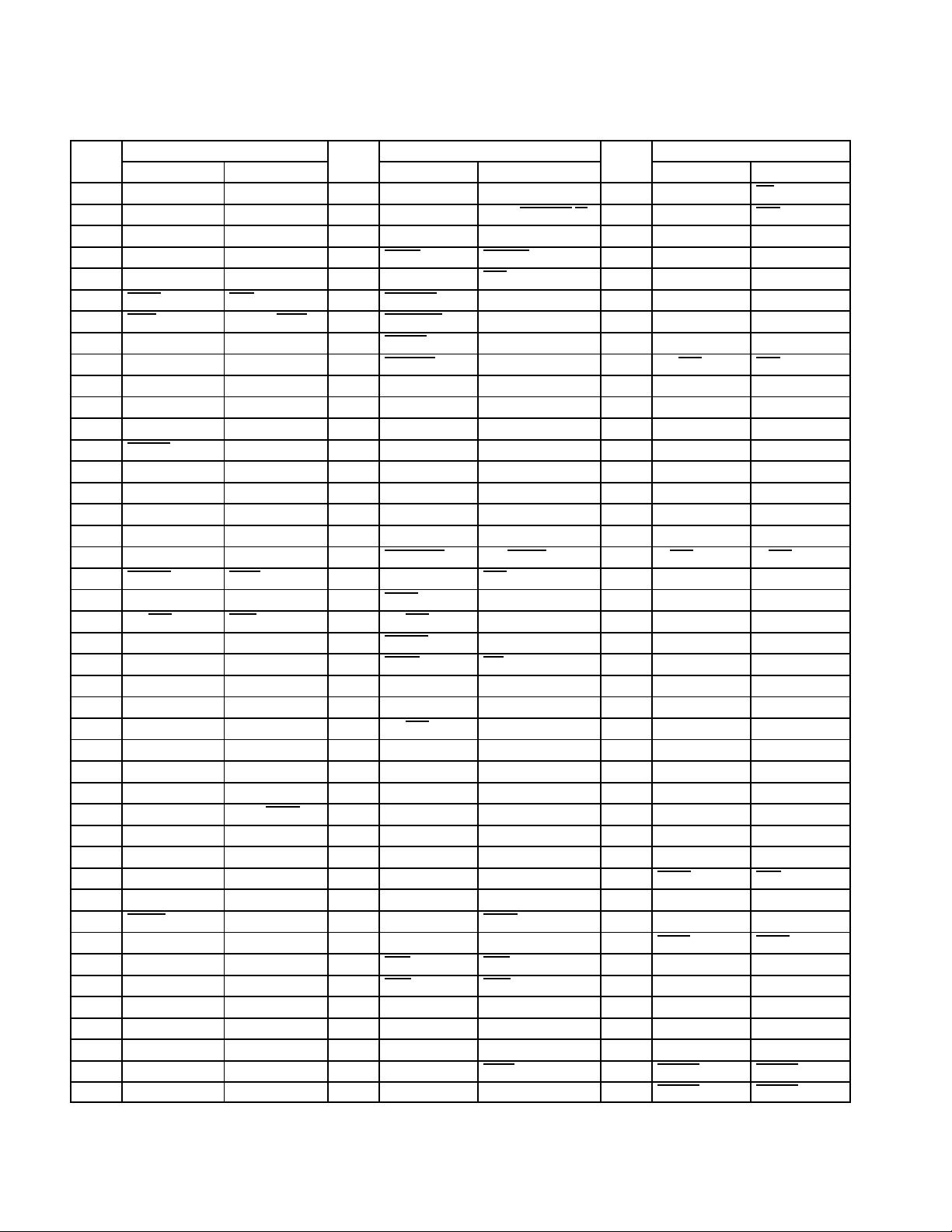

names. Figure 2–3 and Figure 2–4 are terminal diagrams for the GGU and GHK packages, respectively.

CTRDY

CIRDY

CFRAME

CC/BE2

CAD17

GND

CAD18

CAD19

CVS2

CAD20

CRST

CAD21

CAD22

V

CC

CREQ

CAD23

CC/BE3

V

CCCB

CAD24

CAD25

CAD26

GND

CVS1

CINT

CSERR

CAUDIO

CSTSCHG

CCLKRUN

CCD2

V

CC

CAD27

CAD28

CAD29

CAD30

CRSVD

CAD31

PGE LOW-PROFILE QUAD FLAT PACKAGE

(TOP VIEW)

CC

CSTOP

105

104

CBLOCK

CPERR

102

103

V

CPAR

101

CC/BE1

CRSVD

99

100

CAD16

98

CAD15

CAD14

96

97

GND

CAD12

94

95

CCLK

CGNT

CDEVSEL

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

1234567891011121314151617181920212223242526272829303132333435

CAD11

CAD13

92

93

CCCB

V

CAD10

90

91

CAD9

CC/BE0

88

89

CC

V

CAD8

86

87

CRSVD

CAD7

84

85

CAD6

CAD5

82

83

CAD4

CAD3

80

81

GND

CAD1

78

79

CAD2

CAD0

76

77

CCD1

74

75

VCCD0

VCCD1

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

VPPD1

VPPD0

SUSPEND

MFUNC6

MFUNC5

MFUNC4

GRST

MFUNC3

MFUNC2

V

CCI

SPKROUT

MFUNC1

MFUNC0

RI_OUT/PME

GND

AD0

AD1

AD2

AD3

AD4

AD5

AD6AD6

V

CC

AD7

C/BE0

AD8

AD9

AD10

V

CCP

AD11

GND

AD12

AD13

AD14

AD15

C/BE1

REQ

GNT

AD31

AD30

GND

AD29

AD28

AD27

AD26

AD25

AD24

C/BE3

IDSEL

V

CC

AD22

AD23

AD21

V

CCP

AD20

PCLK

PRST

GND

AD19

AD18

Figure 2–1. PCI-to-CardBus Terminal Diagram

AD17

AD16

C/BE2

FRAME

CC

V

IRDY

TRDY

DEVSEL

STOP

PERR

SERR

PAR

2–1

PGE LOW-PROFILE QUAD FLAT PACKAGE

(TOP VIEW)

ADDR22

ADDR15

ADDR23

ADDR12

ADDR24

GND

ADDR7

ADDR25

VS2

ADDR6

RESET

ADDR5

ADDR4

V

CC

INPACK

ADDR3

REG

V

CCCB

ADDR2

ADDR1

ADDR0

GND

VS1

READY(IREQ

WAIT

BVD2(SPKR

BVD1(STSCHG/RI)

WP(IOIS16)

CD2

V

CC

DATA0

DATA8

DATA1

DATA9

DATA2

DATA10

CC

ADDR16

WE

ADDR21

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

)

133

134

)

135

136

137

138

139

140

141

142

143

144

1234567891011121314151617181920212223242526272829303132333435

ADDR19

ADDR20

ADDR14

103

104

105

V

102

101

ADDR8

ADDR18

ADDR13

99

100

ADDR9

ADDR17

96

97

98

ADDR11

IOWR

95

GND

94

IORD

93

92

OE

CE2

91

CCCB

V

90

DATA15

ADDR10

CE1

87

88

89

V

86

CC

DATA7

80

81

82

83

84

85

DATA3

73

74

75

76

77

78

79

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

VPPD1

VPPD0

SUSPEND

MFUNC6

MFUNC5

MFUNC4

GRST

MFUNC3

MFUNC2

V

CCI

SPKROUT

MFUNC1

MFUNC0

RI_OUT/PME

GND

AD0

AD1

AD2

AD3

AD4

AD5

AD6AD6

V

CC

AD7

C/BE0

AD8

AD9

AD10

V

CCP

AD11

GND

AD12

AD13

AD14

AD15

C/BE1

VCCD0

VCCD1

CD1

DATA11

GND

DATA4

DATA12

DATA5

DATA13

DATA6

DATA14

2–2

REQ

GNT

AD31

AD30

GND

AD29

AD28

AD27

AD26

AD25

AD24

C/BE3

CC

V

IDSEL

AD22

AD23

AD21

V

CCP

AD20

PCLK

PRST

GND

AD19

AD18

AD17

AD16

C/BE2

FRAME

Figure 2–2. PCI-to-PC Card (16-Bit) Terminal Diagram

CC

V

IRDY

TRDY

DEVSEL

STOP

PERR

SERR

PAR

N

M

L

K

J

H

G

F

E

D

C

B

A

1

42 3

5

12 1310 118967

Figure 2–3. GGU Package Terminal Diagram

W

V

U

T

R

P

N

M

L

K

J

H

G

F

E

D

C

B

A

12

13141511

9

3

1

2

75

810

6

4

16

18

1917

Figure 2–4. GHK Package Terminal Diagram

Table 2–1 shows the terminal assignments for the 144-terminal GGU CardBus and 16-bit PC Card signal names.

Table 2–2 shows the terminal assignments for the 144-terminal PGE CardBus and 16-bit PC Card signal names.

Table 2–3 shows the terminal assignments for the 209-terminal GHK CardBus and 16-bit PC Card signal names.

Table 2–4 shows the CardBus PC Card signal names sorted alphabetically to the GGU/PGE/GHK terminal numbers.

Table 2–5 shows the 16-bit PC Card signal names sorted alphabetically to the GGU/PGE/GHK terminal numbers.

2–3

Table 2–1. CardBus and 16-Bit PC Card Signal Names by GGU Terminal Number

TERM.

NO.

A1 REQ REQ

A2 CRSVD

A3 CAD28

A4 CCD2

A5 CSERR

A6 CAD26

A7 V

A8 CAD23

A9 CAD21

A10 CAD19

A11 CC/BE2

A12 CIRDY

A13 CTRDY

B1 GNT

B2 CAD31

B3 CAD29

B4 V

B5 CAUDIO

B6 GND

B7 CC/BE3

B8 CREQ

B9 CRST

B10 CAD18

B11 CFRAME

B12 CCLK

B13 CDEVSEL

C1 AD30

C2 AD31

C3 CAD30

C4 CAD27

C5 CSTSCHG

C6 CVS1

C7 CAD24

C8 V

C9 CAD20

C10 GND

SIGNAL NAME

CARD

BUS

CCCB

CC

CC

16-BIT

DATA2

DATA8

CD2

WAIT

ADDR0

V

CCCB

ADDR3

ADDR5

ADDR25

ADDR12

ADDR15

ADDR22

GNT

DATA10

DATA1

V

CC

BVD2

(SPKR

)

GND

REG

INPACK

RESET

ADDR7

ADDR23

ADDR16

ADDR21

AD30

AD31

DATA9

DATA0

BVD1

(STSCHG

VS1

ADDR2

V

CC

ADDR6

GND

TERM.

NO.

C11 CGNT WE G10 CAD11 OE L4 GND GND

C12 CSTOP ADDR20 G11 CAD10 CE2 L5 AD9 AD9

C13 CPERR ADDR14 G12 CAD9 ADDR10 L6 V

D1 AD27 AD27 G13 V

D2 AD28 AD28 H1 PCLK PCLK L8 RI_OUT/

D3 GND GND H2 GND GND L9 V

D4 AD29 AD29 H3 AD19 AD19 L10 MFUNC4 MFUNC4

D5 CCLKRUN WP

D6 CINT READY

D7 CAD25 ADDR1 H11 V

D8 CAD22 ADDR4 H12 CAD8 DATA15 M1 SERR SERR

D9 CVS2 VS2 H13 CC/BE0 CE1 M2 PAR PAR

D10 CAD17 ADDR24 J1 AD17 AD17 M3 AD14 AD14

D11 CBLOCK ADDR19 J2 AD16 AD16 M4 AD11 AD11

D12 V

D13 CPAR ADDR13 J4 FRAME FRAME M6 AD6 AD6

E1 C/BE3 C/BE3 J10 CAD3 DATA5 M7 AD4 AD4

E2 AD24 AD24 J11 CAD6 DATA13 M8 GND GND

E3 AD25 AD25 J12 CAD5 DATA6 M9 SPKROUT SPKROUT

E4 AD26 AD26 J13 CRSVD DATA14 M10 GRST GRST

E10 CRSVD ADDR18 K1 IRDY IRDY M11 MFUNC6 MFUNC6

E11 CC/BE1 ADDR8 K2 V

E12 CAD16 ADDR17 K3 TRDY TRDY M13 VCCD1 VCCD1

E13 CAD14 ADDR9 K4 AD12 AD12 N1 C/BE1 C/BE1

F1 AD22 AD22 K5 AD10 AD10 N2 AD15 AD15

F2 AD23 AD23 K6 AD7 AD7 N3 AD13 AD13

F3 V

F4 IDSEL IDSEL K8 MFUNC0 MFUNC0 N5 C/BE0 C/BE0

F10 CAD15 IOWR K9 MFUNC2 MFUNC2 N6 AD5 AD5

F11 CAD12 ADDR11 K10 CAD2 DATA11 N7 AD3 AD3

F12 GND GND K11 GND GND N8 AD0 AD0

/RI)

F13 CAD13 IORD K12 CAD1 DATA4 N9 MFUNC1 MFUNC1

G1 V

G2 AD21 AD21 L1 DEVSEL DEVSEL N11 MFUNC5 MFUNC5

G3 AD20 AD20 L2 STOP STOP N12 VPPD0 VPPD0

G4 PRST PRST L3 PERR PERR N13 VCCD0 VCCD0

SIGNAL NAME

CARD

BUS

CC

CC

CCP

16-BIT

(IOIS16

(IREQ

V

CC

V

CC

V

CCP

TERM.

NO.

H4 AD18 AD18 L11 SUSPEND SUSPEND

)

H10 CAD7 DATA7 L12 CCD1 CD1

)

J3 C/BE2 C/BE2 M5 AD8 AD8

K7 AD1 AD1 N4 V

K13 CAD4 DATA12 N10 MFUNC3 MFUNC3

SIGNAL NAME

CARD

BUS

CCCB

CC

CC

V

V

V

16-BIT

CCCB

CC

CC

TERM.

NO.

L7 AD2 AD2

L13 CAD0 DATA3

M12 VPPD1 VPPD1

SIGNAL NAME

CARD

BUS

CC

PME

CCI

CCP

16-BIT

V

CC

RI_OUT/

PME

V

CCI

V

CCP

2–4

Table 2–2. CardBus and 16-Bit PC Card Signal Names by PGE Terminal Number

TERM.

NO.

1 REQ

2 GNT GNT 38 AD15 AD15 74 VCCD1 VCCD1 110 CIRDY ADDR15

3 AD31 AD31 39 AD14 AD14 75 CCD1 CD1 111 CFRAME ADDR23

4 AD30 AD30 40 AD13 AD13 76 CAD0 DATA3 112 CC/BE2 ADDR12

5 AD29 AD29 41 AD12 AD12 77 CAD2 DATA11 113 CAD17 ADDR24

6 GND GND 42 GND GND 78 GND GND 114 GND GND

7 AD28 AD28 43 AD11 AD11 79 CAD1 DATA4 115 CAD18 ADDR7

8 AD27 AD27 44 V

9 AD26 AD26 45 AD10 AD10 81 CAD3 DATA5 117 CVS2 VS2

10 AD25 AD25 46 AD9 AD9 82 CAD6 DATA13 118 CAD20 ADDR6

11 AD24 AD24 47 AD8 AD8 83 CAD5 DATA6 119 CRST RESET

12 C/BE3 C/BE3 48 C/BE0 C/BE0 84 CRSVD DATA14 120 CAD21 ADDR5

13 IDSEL IDSEL 49 AD7 AD7 85 CAD7 DATA7 121 CAD22 ADDR4

14 V

15 AD23 AD23 51 AD6 AD6 87 CAD8 DATA15 123 CREQ INPACK

16 AD22 AD22 52 AD5 AD5 88 CC/BE0 CE1 124 CAD23 ADDR3

17 AD21 AD21 53 AD4 AD4 89 CAD9 ADDR10 125 CC/BE3 REG

18 V

19 AD20 AD20 55 AD2 AD2 91 CAD10 CE2 127 CAD24 ADDR2

20 PRST PRST 56 AD1 AD1 92 CAD11 OE 128 CAD25 ADDR1

21 PCLK PCLK 57 AD0 AD0 93 CAD13 IORD 129 CAD26 ADDR0

22 GND GND 58 GND GND 94 GND GND 130 GND GND

23 AD19 AD19 59 RI_OUT/

24 AD18 AD18 60 MFUNC0 MFUNC0 96 CAD15 IOWR 132 CINT READY

25 AD17 AD17 61 MFUNC1 MFUNC1 97 CAD14 ADDR9 133 CSERR WAIT

26 AD16 AD16 62 SPKROUT SPKROUT 98 CAD16 ADDR17 134 CAUDIO BVD2

27 C/BE2 C/BE2 63 V

28 FRAME FRAME 64 MFUNC2 MFUNC2 100 CRSVD ADDR18 136 CCLKRUN WP (IOIS16)

29 IRDY IRDY 65 MFUNC3 MFUNC3 101 CPAR ADDR13 137 CCD2 CD2

30 V

31 TRDY TRDY 67 MFUNC4 MFUNC4 103 CBLOCK ADDR19 139 CAD27 DATA0

32 DEVSEL DEVSEL 68 MFUNC5 MFUNC5 104 CPERR ADDR14 140 CAD28 DATA8

33 STOP STOP 69 MFUNC6 MFUNC6 105 CSTOP ADDR20 141 CAD29 DATA1

34 PERR PERR 70 SUSPEND SUSPEND 106 CGNT WE 142 CAD30 DATA9

35 SERR SERR 71 VPPD0 VPPD0 107 CDEVSEL ADDR21 143 CRSVD DATA2

36 PAR PAR 72 VPPD1 VPPD1 108 CCLK ADDR16 144 CAD31 DATA10

SIGNAL NAME

CARD

BUS

CC

CCP

CC

16-BIT

REQ 37 C/BE1 C/BE1 73 VCCD0 VCCD0 109 CTRDY ADDR22

V

CC

V

CCP

V

CC

TERM.

NO.

50 V

54 AD3 AD3 90 V

66 GRST GRST 102 V

SIGNAL NAME

CARD

BUS

CCP

CC

PME

CCI

16-BIT

V

CCP

V

CC

RI_OUT/

PME

V

CCI

TERM.

NO.

80 CAD4 DATA12 116 CAD19 ADDR25

86 V

95 CAD12 ADDR11 131 CVS1 VS1

99 CC/BE1 ADDR8 135 CSTSCHG BVD1

SIGNAL NAME

CARD

BUS

CC

CCCB

CC

V

V

V

16-BIT

CC

CCCB

CC

TERM.

NO.

122 V

126 V

138 V

SIGNAL NAME

CARD

BUS

CC

CCCB

CC

V

CC

V

CCCB

(IREQ

(SPKR

(STSCHG

V

CC

16-BIT

)

)

/RI)

2–5

Table 2–3. CardBus and 16-Bit PC Card Signal Names by GHK Terminal Number

TERM

TERM

TERM

TERM.

.

NO.

A4 NC NC E9 CAD29 DATA1 H17 CAD11 OE

A5 NC NC E10 CSTSCHG BVD1(STSCHG/RI) H18 CAD10 CE2

A6 NC NC E11 GND GND H19 V

A7 NC NC E12 CREQ INPACK J1 AD31 AD31

A8 CAD30 DATA9 E13 CVS2 VS2 J2 AD30 AD30

A9 CCD2 CD2 E14 CFRAME ADDR23 J3 AD29 AD29

A10 CINT READY(IREQ) E17 CDEVSEL ADDR21 J5 GND GND

A11 CAD24 ADDR2 E18 CSTOP ADDR20 J6 AD28 AD28

A12 V

A13 V

A14 CAD20 ADDR6 F2 NC NC J17 CAD8 DATA15

A15 GND GND F3 NC NC J18 V

A16 CTRDY ADDR22 F5 NC NC J19 CAD7 DATA7

B5 NC NC F6 NC NC K1 AD27 AD27

B6 NC NC F7 NC NC K2 AD26 AD26

B7 NC NC F8 NC NC K3 AD25 AD25

B8 CRSVD DATA2 F9 CAD28 DATA8 K5 AD24 AD24

B9 V

B10 CSERR WAIT F11 CVS1 VS1 K14 CRSVD DATA14

B11 CAD25 ADDR1 F12 CRST RESET K15 CAD5 DATA6

B12 CC/BE3 REG F13 CC/BE2 ADDR12 K17 CAD6 DATA13

B13 CAD22 ADDR4 F14 CPERR ADDR14 K18 CAD3 DATA5

B14 CAD19 ADDR25 F15 CGNT WE K19 CAD4 DATA12

B15 CAD17 ADDR24 F17 V

C5 NC NC F18 CRSVD ADDR18 L2 V

C6 NC NC F19 CC/BE1 ADDR8 L3 AD23 AD23

C7 NC NC G1 NC NC L5 AD21 AD21

C8 CAD31 DATA10 G2 NC NC L6 AD22 AD22

C9 CAD27 DATA0 G3 NC NC L14 CAD1 DATA4

C10 CAUDIO BVD2(SPKR) G5 NC NC L15 GND GND

C11 CAD26 ADDR0 G6 NC NC L17 CAD2 DATA11

C12 CAD23 ADDR3 G14 CAD16 ADDR17 L18 CAD0 DATA3

C13 CAD21 ADDR5 G15 CPAR ADDR13 L19 CCD1 CD1

C14 CAD18 ADDR7 G17 CAD14 ADDR9 M1 V

C15 CIRDY ADDR15 G18 CAD15 IOWR M2 AD20 AD20

D1 NC NC G19 CAD12 ADDR11 M3 PRST PRST

D19 CCLK ADDR16 H1 GNT GNT M5 GND GND

E1 NC NC H2 REQ REQ M6 PCLK PCLK

E2 NC NC H3 NC NC M14 NC NC

E3 NC NC H5 NC NC M15 NC NC

E6 NC NC H6 NC NC M17 NC NC

E7 NC NC H14 CAD13 IORD M18 VCCD0 VCCD0

E8 NC NC H15 GND GND M19 VCCD1 VCCD1

SIGNAL NAME

CARDBUS 16-BIT

CCCB

CC

CC

V

CCCB

V

CC

V

CC

TERM.

.

NO.

E19 CBLOCK ADDR19 J14 CC/BE0 CE1

F1 NC NC J15 CAD9 ADDR10

F10 CCLKRUN WP(IOIS16) K6 C/BE3 C/BE3

CARDBUS 16-BIT

CC

SIGNAL NAME

V

CC

TERM.

.

NO.

L1 IDSEL IDSEL

SIGNAL NAME

CARDBUS 16-BIT

CCCB

CC

CC

CCP

V

CCCB

V

CC

V

CC

V

CCP

2–6

Table 2–3. CardBus and 16-Bit PC Card Signal Names by GHK Terminal Number (Continued)

TERM

TERM

TERM

TERM.

.

NO.

N1 AD19 AD19 R1 TRDY TRDY U15 NC NC

N2 AD18 AD18 R2 STOP STOP V5 AD12 AD12

N3 AD17 AD17 R3 SERR SERR V6 V

N5 IRDY IRDY R6 AD14 AD14 V7 AD7 AD7

N6 AD16 AD16 R7 AD10 AD10 V8 AD4 AD4

N14 NC NC R8 AD6 AD6 V9 AD1 AD1

N15 NC NC R9 GND GND V10 MFUNC1 MFUNC1

N17 NC NC R10 V

N18 NC NC R11 MFUNC6 MFUNC6 V12 VPPD0 VPPD0

N19 NC NC R12 NC NC V13 NC NC

P1 C/BE2 C/BE2 R13 NC NC V14 NC NC

P2 FRAME FRAME R14 NC NC V15 NC NC

P3 V

P5 PERR PERR R18 NC NC W5 GND GND

P6 DEVSEL DEVSEL R19 NC NC W6 AD9 AD9

P7 AD13 AD13 T1 PAR PAR W7 V

P8 AD8 AD8 T19 NC NC W8 AD3 AD3

P9 RI_OUT/PME RI_OUT/PME U5 AD15 AD15 W9 AD2 AD2

P10 MFUNC2 MFUNC2 U6 AD11 AD11 W10 MFUNC0 MFUNC0

P11 MFUNC5 MFUNC5 U7 C/BE0 C/BE0 W11 MFUNC3 MFUNC3

P12 NC NC U8 AD5 AD5 W12 SUSPEND SUSPEND

P13 NC NC U9 AD0 AD0 W13 NC NC

P14 NC NC U10 SPKROUT SPKROUT W14 NC NC

P15 NC NC U11 MFUNC4 MFUNC4 W15 NC NC

P17 NC NC U12 VPPD1 VPPD1 W16 NC NC

P18 NC NC U13 NC NC

P19 NC NC U14 NC NC

SIGNAL NAME

CARDBUS 16-BIT

CC

V

CC

TERM.

.

NO.

CCI

R17 NC NC W4 C/BE1 C/BE1

SIGNAL NAME

CARDBUS 16-BIT

V

CCI

TERM.

.

NO.

V11 GRST GRST

SIGNAL NAME

CARDBUS 16-BIT

CCP

CC

V

V

CCP

CC

2–7

Table 2–4. CardBus PC Card Signal Names Sorted Alphabetically to GGU/PGE/GHK Terminal Number

SIGNAL NAME

AD0 N8 57 U9 CAD11 G10 92 H17 CRST B9 119 F12

AD1 K7 56 V9 CAD12 F11 95 G19 CRSVD A2 143 B8

AD2 L7 55 W9 CAD13 F13 93 H14 CRSVD E10 100 F18

AD3 N7 54 W8 CAD14 E13 97 G17 CRSVD J13 84 K14

AD4 M7 53 V8 CAD15 F10 96 G18 CSERR A5 133 B10

AD5 N6 52 U8 CAD16 E12 98 G14 CSTOP C12 105 E18

AD6 M6 51 R8 CAD17 D10 113 B15 CSTSCHG C5 135 E10

AD7 K6 49 V7 CAD18 B10 115 C14 CTRDY A13 109 A16

AD8 M5 47 P8 CAD19 A10 116 B14 CVS1 C6 131 F11

AD9 L5 46 W6 CAD20 C9 118 A14 CVS2 D9 117 E13

AD10 K5 45 R7 CAD21 A9 120 C13 DEVSEL L1 32 P6

AD11 M4 43 U6 CAD22 D8 121 B13 FRAME J4 28 P2

AD12 K4 41 V5 CAD23 A8 124 C12 GND D3 6 A15

AD13 N3 40 P7 CAD24 C7 127 A11 GND H2 22 E11

AD14 M3 39 R6 CAD25 D7 128 B11 GND L4 42 H15

AD15 N2 38 U5 CAD26 A6 129 C11 GND M8 58 J5

AD16 J2 26 N6 CAD27 C4 139 C9 GND K11 78 L15

AD17 J1 25 N3 CAD28 A3 140 F9 GND F12 94 M5

AD18 H4 24 N2 CAD29 B3 141 E9 GND C10 114 R9

AD19 H3 23 N1 CAD30 C3 142 A8 GND B6 130 W5

AD20 G3 19 M2 CAD31 B2 144 C8 GNT B1 2 H1

AD21 G2 17 L5 CAUDIO B5 134 C10 GRST M10 66 V11

AD22 F1 16 L6 C/BE0 N5 48 U7 IDSEL F4 13 L1

AD23 F2 15 L3 C/BE1 N1 37 W4 IRDY K1 29 N5

AD24 E2 11 K5 C/BE2 J3 27 P1 MFUNC0 K8 60 W10

AD25 E3 10 K3 C/BE3 E1 12 K6 MFUNC1 N9 61 V10

AD26 E4 9 K2 CBLOCK D11 103 E19 MFUNC2 K9 64 P10

AD27 D1 8 K1 CC/BE0 H13 88 J14 MFUNC3 N10 65 W11

AD28 D2 7 J6 CC/BE1 E11 99 F19 MFUNC4 L10 67 U11

AD29 D4 5 J3 CC/BE2 A11 112 F13 MFUNC5 N11 68 P11

AD30 C1 4 J2 CC/BE3 B7 125 B12 MFUNC6 M11 69 R11

AD31 C2 3 J1 CCD1 L12 75 L19 PAR M2 36 T1

CAD0 L13 76 L18 CCD2 A4 137 A9 PCLK H1 21 M6

CAD1 K12 79 L14 CCLK B12 108 D19 PERR L3 34 P5

CAD2 K10 77 L17 CCLKRUN D5 136 F10 PRST G4 20 M3

CAD3 J10 81 K18 CDEVSEL B13 107 E17 REQ A1 1 H2

CAD4 K13 80 K19 CFRAME B11 111 E14 RI_OUT/PME L8 59 P9

CAD5 J12 83 K15 CGNT C11 106 F15 SERR M1 35 R3

CAD6 J11 82 K17 CINT D6 132 A10 SPKROUT M9 62 U10

CAD7 H10 85 J19 CIRDY A12 110 C15 STOP L2 33 R2

CAD8 H12 87 J17 CPAR D13 101 G15 SUSPEND L11 70 W12

CAD9 G12 89 J15 CPERR C13 104 F14 TRDY K3 31 R1

CAD10 G11 91 H18 CREQ B8 123 E12 V

TERM. NO.

GGU PGE GHK

SIGNAL NAME

TERM. NO.

GGU PGE GHK

SIGNAL NAME

CC

TERM. NO.

GGU PGE GHK

F3 14 A13

2–8

Table 2–4. CardBus PC Card Signal Names Sorted Alphabetically to GGU/PGE/GHK

Terminal Number (Continued)

SIGNAL NAME

V

CC

V

CC

V

CC

V

CC

V

CC

TERM. NO.

GGU PGE GHK

K2 30 B9 V

L6 50 F17 V

H11 86 J18 V

D12 102 L2 VCCD0 N13 73 M18 VPPD0 N12 71 V12

C8 122 P3 VCCD1 M13 74 M19 VPPD1 M12 72 U12

SIGNAL NAME

CC

CCCB

CCCB

TERM. NO.

GGU PGE GHK

B4 138 W7 V

G13 90 A12 V

A7 126 H19 V

SIGNAL NAME

CCI

CCP

CCP

TERM. NO.

GGU PGE GHK

L9 63 R10

G1 18 M1

N4 44 V6

2–9

Table 2–5. 16-Bit PC Card Signal Names Sorted Alphabetically to GGU/PGE/GHK Terminal Number

SIGNAL NAME

AD0 N8 57 U9 ADDR11 F11 95 G19 GND D3 6 A15

AD1 K7 56 V9 ADDR12 A11 112 F13 GND H2 22 E11

AD2 L7 55 W9 ADDR13 D13 101 G15 GND L4 42 H15

AD3 N7 54 W8 ADDR14 C13 104 F14 GND M8 58 J5

AD4 M7 53 V8 ADDR15 A12 110 C15 GND K11 78 L15

AD5 N6 52 U8 ADDR16 B12 108 D19 GND F12 94 M5

AD6 M6 51 R8 ADDR17 E12 98 G14 GND C10 114 R9

AD7 K6 49 V7 ADDR18 E10 100 F18 GND B6 130 W5

AD8 M5 47 P8 ADDR19 D11 103 E19 GNT B1 2 H1

AD9 L5 46 W6 ADDR20 C12 105 E18 GRST M10 66 V11

AD10 K5 45 R7 ADDR21 B13 107 E17 IDSEL F4 13 L1

AD11 M4 43 U6 ADDR22 A13 109 A16 INPACK B8 123 E12

AD12 K4 41 V5 ADDR23 B11 111 E14 IORD F13 93 H14

AD13 N3 40 P7 ADDR24 D10 113 B15 IOWR F10 96 G18

AD14 M3 39 R6 ADDR25 A10 116 B14 IRDY K1 29 N5

AD15 N2 38 U5 BVD1(STSCHG/RI) C5 135 E10 MFUNC0 K8 60 W10

AD16 J2 26 N6 BVD2(SPKR) B5 134 C10 MFUNC1 N9 61 V10

AD17 J1 25 N3 C/BE0 N5 48 U7 MFUNC2 K9 64 P10

AD18 H4 24 N2 C/BE1 N1 37 W4 MFUNC3 N10 65 W11

AD19 H3 23 N1 C/BE2 J3 27 P1 MFUNC4 L10 67 U11

AD20 G3 19 M2 C/BE3 E1 12 K6 MFUNC5 N11 68 P11

AD21 G2 17 L5 CD1 L12 75 L19 MFUNC6 M11 69 R11

AD22 F1 16 L6 CD2 A4 137 A9 OE G10 92 H17

AD23 F2 15 L3 CE1 H13 88 J14 PAR M2 36 T1

AD24 E2 11 K5 CE2 G11 91 H18 PCLK H1 21 M6

AD25 E3 10 K3 DATA0 C4 139 C9 PERR L3 34 P5

AD26 E4 9 K2 DATA1 B3 141 E9 PRST G4 20 M3

AD27 D1 8 K1 DATA2 A2 143 B8 READY(IREQ) D6 132 A10

AD28 D2 7 J6 DATA3 L13 76 L18 REG B7 125 B12

AD29 D4 5 J3 DATA4 K12 79 L14 REQ A1 1 H2

AD30 C1 4 J2 DATA5 J10 81 K18 RESET B9 119 F12

AD31 C2 3 J1 DATA6 J12 83 K15 RI_OUT/PME L8 59 P9

ADDR0 A6 129 C11 DATA7 H10 85 J19 SERR M1 35 R3

ADDR1 D7 128 B11 DATA8 A3 140 F9 SPKROUT M9 62 U10

ADDR2 C7 127 A11 DATA9 C3 142 A8 STOP L2 33 R2

ADDR3 A8 124 C12 DATA10 B2 144 C8 SUSPEND L11 70 W12

ADDR4 D8 121 B13 DATA11 K10 77 L17 TRDY K3 31 R1

ADDR5 A9 120 C13 DATA12 K13 80 K19 V

ADDR6 C9 118 A14 DATA13 J11 82 K17 V

ADDR7 B10 115 C14 DATA14 J13 84 K14 V

ADDR8 E11 99 F19 DATA15 H12 87 J17 V

ADDR9 E13 97 G17 DEVSEL L1 32 P6 V

ADDR10 G12 89 J15 FRAME J4 28 P2 V

TERM. NO.

GGU PGE

GHK

SIGNAL NAME

TERM. NO.

GGU PGE

GHK

SIGNAL NAME

CC

CC

CC

CC

CC

CC

TERM. NO.

GGU PGE

F3 14 A13

K2 30 B9

L6 50 F17

H11 86 J18

D12 102 L2

C8 122 P3

GHK

2–10

Table 2–5. 16-Bit PC Card Signal Names Sorted Alphabetically to GGU/PGE/GHK

Terminal Number (Continued)

SIGNAL NAME

V

CC

V

CCCB

V

CCCB

VCCD0 N13 73 M18 VPPD0 N12 71 V12 WE C11 106 F15

VCCD1 M13 74 M19 VPPD1 M12 72 U12 WP(IOIS16) D5 136 F10

TERM. NO.

GGU PGE

B4 138 W7 V

G13 90 A12 V

A7 126 H19 V

GHK

SIGNAL NAME

CCI

CCP

CCP

TERM. NO.

GGU PGE

L9 63 R10 VS1 C6 131 F11

G1 18 M1 VS2 D9 117 E13

N4 44 V6 WAIT A5 133 B10

GHK

SIGNAL NAME

TERM. NO.

GGU PGE

GHK

2–11

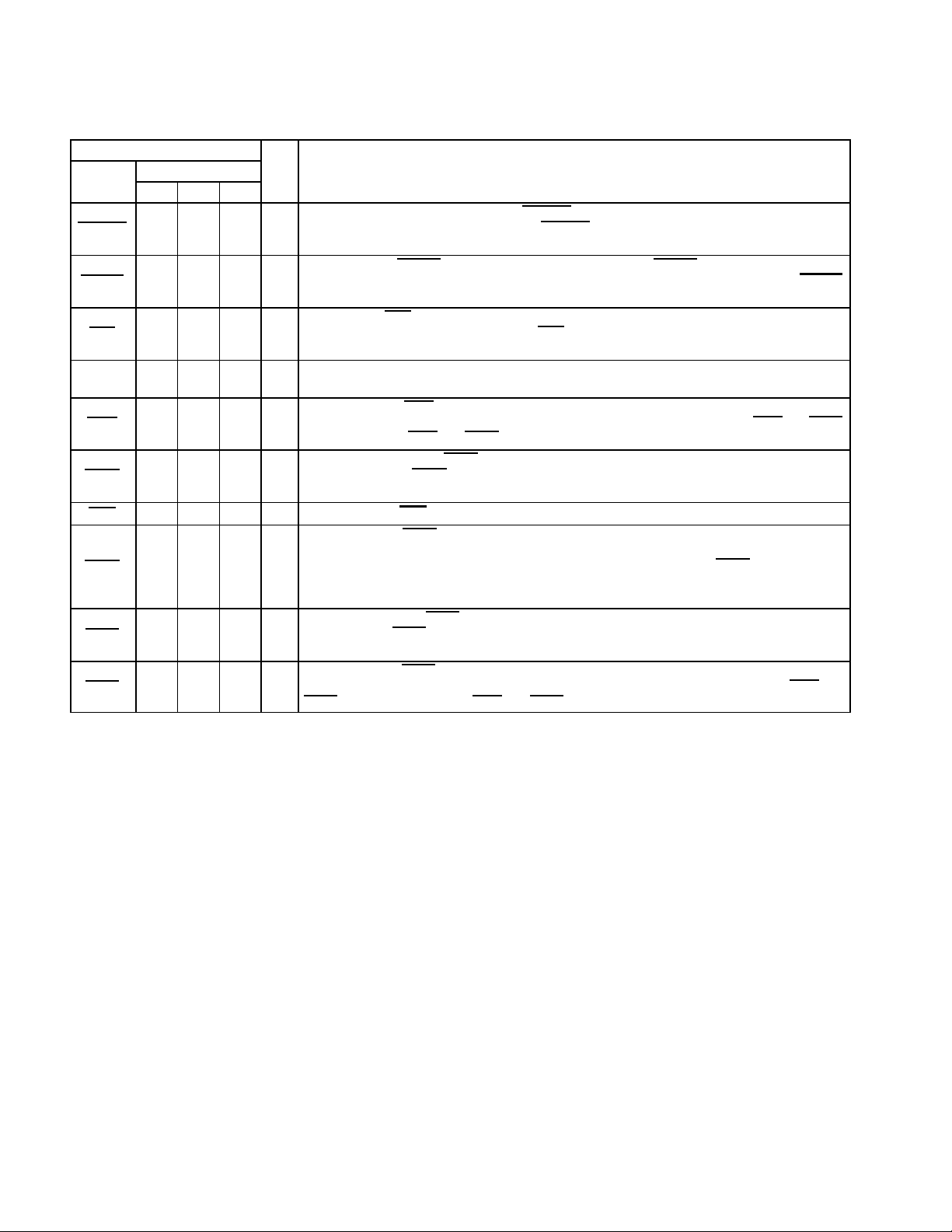

The terminals are grouped in tables by functionality (see Table 2–6 through Table 2–16), such as PCI system function

DESCRIPTION

I/O

DESCRIPTION

and power-supply function. The terminal numbers are also listed for convenient reference.

Table 2–6. Power Supply Terminals

TERMINAL

NAME

GND

V

CC

V

CCCB

V

CCI

V

CCP

NUMBER

GGU PGE GHK

B6, C10,

D3, F12,

H2, K11,

L4, M8

B4, C8,

D12, F3,

H11, K2,

L6

A7, G13 90, 126 A12, H19 Clamp voltage for PC Card interface. Matches card signaling environment, 5 V or 3.3 V.

L9 63 R10 Clamp voltage for interrupt subsystem interface and miscellaneous I/O, 5 V or 3.3 V

G1, N4 18, 44 M1, V6 Clamp voltage for PCI signaling, 5 V or 3.3 V

6, 22, 42,

58, 78,

94, 114,

130

14, 30,

50, 86,

102, 122,

138

A15, E11,

H15, J5,

L15, M5,

R9, W5

A13, B9,

F17, J18,

L2, P3,

W7

Device ground terminals

Power supply terminal for core logic (3.3 V)

DESCRIPTION

Table 2–7. PC Card Power Switch Terminals

TERMINAL

NAME

VCCD0

VCCD1

VPPD0

VPPD1

NUMBER

GGU PGE GHK

N13

M137374

N12

M127172

I/O DESCRIPTION

M18

M19

V12

U12

O Logic controls to the TPS2211 PC Card power interface switch to control AVCC.

O Logic controls to the TPS2211 PC Card power interface switch to control AVPP.

TERMINAL

NAME

GRST M10 66 V11 I

PCLK H1 21 M6 I

PRST

NUMBER

GGU PGE GHK

G4 20 M3 I

Table 2–8. PCI System Terminals

I/O DESCRIPTION

Global reset. When the global reset is asserted, the GRST signal causes the PCI1410 to place all

output buf fers in a high-impedance state and reset all internal registers. When GRST

device is completely in its default state. For systems that require wake-up from D3, GRST

normally be asserted only during initial boot. PRST

context is retained when transitioning from D3 to D0. For systems that do not require wake-up from

D3, GRST

When the SUSPEND

registers are preserved. All outputs are placed in a high-impedance state.

PCI bus clock. PCLK provides timing for all transactions on the PCI bus. All PCI signals are sampled

at the rising edge of PCLK.

PCI reset. When the PCI bus reset is asserted, PRST causes the PCI1410 to place all output buffers

in a high-impedance state and reset internal registers. When PRST

completely nonfunctional. After PRST

When the SUSPEND

registers are preserved. All outputs are placed in a high-impedance state.

should be tied to PRST.

mode is enabled, the device is protected from the GRST, and the internal

is deasserted, the PCI1410 is in a default state.

mode is enabled, the device is protected from the PRST, and the internal

should be used following initial boot so that PME

is asserted, the device is

is asserted, the

will

2–12

TERMINAL

I/O

DESCRIPTION

NAME

AD31

AD30

AD29

AD28

AD27

AD26

AD25

AD24

AD23

AD22

AD21

AD20

AD19

AD18

AD17

AD16

AD15

AD14

AD13

AD12

AD11

AD10

AD9

AD8

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AD0

C/BE3

C/BE2

C/BE1

C/BE0

PAR M2 36 T1 I/O

NUMBER

GGU PGE GHK

C2

C1

D4

D2

D1

E4

E3

E2

F2

F1

G2

G3

H3

H4

J1

J2

N2

M3

N3

K4

M4

K5

L5

M5

K6

M6

N6

M7

N7

L7

K7

N8

E1

J3

N1

N5

10

15

16

17

19

23

24

25

26

38

39

40

41

43

45

46

47

49

51

52

53

54

55

56

57

12

27

37

48

3

J1

4

J2

5

J3

7

J6

8

K1

9

K2

K3

11

K5

L3

L6

L5

M2

N1

N2

N3

N6

U5

R6

P7

V5

U6

R7

W6

P8

V7

R8

U8

V8

W8

W9

V9

U9

K6

P1

W4

U7

Table 2–9. PCI Address and Data Terminals

I/O DESCRIPTION

PCI address/data bus. These signals make up the multiplexed PCI address and data bus on the

primary interface. During the address phase of a primary bus PCI cycle, AD31–AD0 contain a 32-bit

I/O

address or other destination information. During the data phase, AD31–AD0 contain data.

PCI bus commands and byte enables. These signals are multiplexed on the same PCI terminals.

During the address phase of a primary bus PCI cycle, C/BE3

During the data phase, this 4-bit bus is used as byte enables. The byte enables determine which

I/O

byte paths of the full 32-bit data bus carry meaningful data. C/BE0

C/BE1

applies to byte 1 (AD15–AD8), C/BE2 applies to byte 2 (AD23–AD16), and C/BE3 applies

to byte 3 (AD31–AD24).

PCI bus parity. In all PCI bus read and write cycles, the PCI1410 calculates even parity across the

AD31–AD0 and C/BE3

parity indicator with a one-PCLK delay. As a target during PCI cycles, the calculated parity is

compared to the initiator parity indicator. A compare error results in the assertion of a parity error

(PERR

).

–C/BE0 buses. As an initiator during PCI cycles, the PCI1410 outputs this

–C/BE0 define the bus command.

applies to byte 0 (AD7–AD0),

2–13

TERMINAL

I/O

DESCRIPTION

NAME

DEVSEL

FRAME

GNT

IDSEL F4 13 L1 I

IRDY

PERR

REQ

SERR

STOP

TRDY

NUMBER

GGU PGE GHK

L1 32 P6 I/O

J4 28 P2 I/O

B1 2 H1 I

K1 29 N5 I/O

L3 34 P5 I/O

A1 1 H2 O PCI bus request. REQ is asserted by the PCI1410 to request access to the PCI bus as an initiator.

M1 35 R3 O

L2 33 R2 I/O

K3 31 R1 I/O

Table 2–10. PCI Interface Control Terminals

I/O DESCRIPTION

PCI device select. The PCI1410 asserts DEVSEL to claim a PCI cycle as the target device. As a PCI

initiator on the bus, the PCI1410 monitors DEVSEL

before timeout occurs, then the PCI1410 terminates the cycle with an initiator abort.

PCI cycle frame. FRAME is driven by the initiator of a bus cycle. FRAME is asserted to indicate that

a bus transaction is beginning, and data transfers continue while this signal is asserted. When FRAME

is deasserted, the PCI bus transaction is in the final data phase.

PCI bus grant. GNT is driven by the PCI bus arbiter to grant the PCI1410 access to the PCI bus after

the current data transaction has completed. GNT

on the PCI bus parking algorithm.

Initialization device select. IDSEL selects the PCI1410 during configuration space accesses. IDSEL

can be connected to one of the upper 24 PCI address lines on the PCI bus.

PCI initiator ready. IRDY indicates the ability of the PCI bus initiator to complete the current data phase

of the transaction. A data phase is completed on a rising edge of PCLK where both IRDY

are asserted. Until IRDY and TRDY are both sampled asserted, wait states are inserted.

PCI parity error indicator. PERR is driven by a PCI device to indicate that calculated parity does not

match PAR when PERR

Section 4.4).

PCI system error. SERR is an output that is pulsed from the PCI1410 when enabled through bit 8 of

the command register (offset 04h, see Section 4.4) indicating a system error has occurred. The

PCI1410 need not be the target of the PCI cycle to assert this signal. When SERR

command register, this signal also pulses, indicating that an address parity error has occurred on a

CardBus interface.

PCI cycle stop signal. STOP is driven by a PCI target to request the initiator to stop the current PCI

bus transaction. STOP

do not support burst data transfers.

PCI target ready. TRDY indicates the ability of the primary bus target to complete the current data

phase of the transaction. A data phase is completed on a rising edge of PCLK when both IRDY

are asserted. Until both IRDY and TRDY are asserted, wait states are inserted.

TRDY

is enabled through bit 6 of the command register (offset 04h, see

is used for target disconnects and is commonly asserted by target devices that

until a target responds. If no target responds

may or may not follow a PCI bus request, depending

is enabled in the

and TRDY

and

2–14

Table 2–11. Multifunction and Miscellaneous Terminals

I/O

DESCRIPTION

TERMINAL

NAME

MFUNC0 K8 60 W10 I/O

MFUNC1 N9 61 V10 I/O

MFUNC2 K9 64 P10 I/O

MFUNC3 N10 65 W11 I/O

MFUNC4 L10 67 U11 I/O

MFUNC5 N11 68 P11 I/O

MFUNC6 M11 69 R11 I/O

RI_OUT/PME L8 59 P9 O

SPKROUT

SUSPEND L11 70 W12 I

NUMBER

GGU PGE GHK

M9 62 U10 O

I/O DESCRIPTION

Multifunction terminal 0. MFUNC0 can be configured as parallel PCI interrupt INTA, GPI0,

GPO0, socket activity LED output, ZV switching outputs, CardBus audio PWM, GPE

parallel IRQ. See Section 4.30, Multifunction Routing Register, for configuration details.

Multifunction terminal 1. MFUNC1 can be configured as GPI1, GPO1, socket activity LED

output, ZV switching outputs, CardBus audio PWM, GPE

Multifunction Routing Register, for configuration details.

Serial data (SDA). When VCCD0

provides the SDA signaling for the serial bus interface. The two-terminal serial interface loads

the subsystem identification and other register defaults from an EEPROM after a PCI reset. See

Section 3.6.1, Serial Bus Interface Implementation, for details on other serial bus applications.

Multifunction terminal 2. MFUNC2 can be configured as PC/PCI DMA request, GPI2, GPO2,

socket activity LED output, ZV switching outputs, CardBus audio PWM, GPE

parallel IRQ. See Section 4.30, Multifunction Routing Register, for configuration details.

Multifunction term i n a l 3 . MFUNC3 can be configured as a parallel IRQ or the serialized interrupt

signal IRQSER. See Section 4.30, Multifunction Routing Register, for configuration details.

Multifunction terminal 4. MFUNC4 can be configured as PCI LOCK, GPI3, GPO3, socket activity

LED output, ZV switching outputs, CardBus audio PWM, GPE

Section 4.30, Multifunction Routing Register, for configuration details.

Serial clock (SCL). When VCCD0

provides the SCL signaling for the serial bus interface. The two-terminal serial interface loads

the subsystem identification and other register defaults from an EEPROM after a PCI reset. See

Section 3.6.1, Serial Bus Interface Implementation, for details on other serial bus applications.

Multifunction terminal 5. MFUNC5 can be configured as PC/PCI DMA grant, GPI4, GPO4,

socket activity LED output, ZV switching outputs, CardBus audio PWM, GPE

See Section 4.30, Multifunction Routing Register, for configuration details.

Multifunction terminal 6. MFUNC6 can be configured as a PCI CLKRUN or a parallel IRQ. See

Section 4.30, Multifunction Routing Register, for configuration details.

Ring indicate out and power management event output. Terminal provides an output for

ring-indicate or PME

Speaker output. SPKROUT is the output to the host system that can carry SPKR or CAUDIO

through the PCI1410 from the PC Card interface. SPKROUT is driven as the exclusive-OR

combination of card SPKR//CAUDIO inputs.

Suspend. SUSPEND protects the internal registers from clearing when the GRST or PRST

signal is asserted. See Section 3.8.4, Suspend Mode, for details.

signals.

and VCCD1 are high after a PCI reset, the MFUNC1 terminal

and VCCD1 are high after a PCI reset, the MFUNC4 terminal

, or a parallel IRQ. See Section 4.30,

, RI_OUT, or a

, RI_OUT, or a parallel IRQ. See

, or a parallel IRQ.

, or a

2–15

NAME

I/O

DESCRIPTION

ADDR25

ADDR24

ADDR23

ADDR22

ADDR21

ADDR20

ADDR19

ADDR18

ADDR17

ADDR16

ADDR15

ADDR14

ADDR13

ADDR12

ADDR11

ADDR10

ADDR9

ADDR8

ADDR7

ADDR6

ADDR5

ADDR4

ADDR3

ADDR2

ADDR1

ADDR0

DATA15

DATA14

DATA13

DATA12

DATA11

DATA10

DATA9

DATA8

DATA7

DATA6

DATA5

DATA4

DATA3

DATA2

DATA1

DATA0

TERMINAL

NUMBER

GGU

PGE GHK

A10

D10

B11

A13

B13

C12

D11

E10

E12

B12

A12

C13

D13

A11

F11

G12

E13

E11

B10

C9

A9

D8

A8

C7

D7

A6

H12

J13

J11

K13

K10

B2

C3

A3

H10

J12

J10

K12

L13

A2

B3

C4

116

113

111

109

107

105

103

100

98

108

110

104

101

112

95

89

97

99

115

118

120

121

124

127

128

129

87

84

82

80

77

144

142

140

85

83

81

79

76

143

141

139

Table 2–12. 16-Bit PC Card Address and Data Terminals

I/O DESCRIPTION

B14

B15

E14

A16

E17

E18

E19

F18

G14

D19

C15

F14

G15

F13

G19

J15

G17

F19

C14

A14

C13

B13

C12

A11

B11

C11

J17

K14

K17

K19

L17

C8

A8

F9

J19

K15

K18

L14

L18

B8

E9

C9

O PC Card address. 16-bit PC Card address lines. ADDR25 is the most significant bit.

I/O PC Card data. 16-bit PC Card data lines. DATA15 is the most significant bit.

2–16

Table 2–13. 16-Bit PC Card Interface Control Terminals

I/O

DESCRIPTION

TERMINAL

NAME

BVD1

(STSCHG

/RI)

BVD2

(SPKR

)

CD1

CD2

CE1

CE2

INPACK B8 123 E12 I

IORD

IOWR

OE G10 92 H17 O

NUMBER

GGU PGE GHK

C5 135 E10 I

B5 134 C10 I

L12A475

137

H13

G118891

F13 93 H14 O

F10 96 G18 O

L19

A9

J14

H18

I/O DESCRIPTION

Battery voltage detect 1. BVD1 is generated by 16-bit memory PC Cards that include

batteries. BVD1 is used with BVD2 as an indication of the condition of the batteries on a

memory PC Card. Both BVD1 and BVD2 are high when the battery is good. When BVD2

is low and BVD1 is high, the battery is weak and should be replaced. When BVD1 is low,

the battery is no longer serviceable and the data in the memory PC Card is lost. See

Section 5.6, ExCA Card Status-Change-Interrupt Configuration Register, for enable bits.

See Section 5.5, ExCA Card Status-Change Register, and Section 5.2, ExCA Interface

Status Register, for the status bits for this signal.

Status change. STSCHG

or battery voltage dead condition of a 16-bit I/O PC Card.

Ring indicate. RI

Battery voltage detect 2. BVD2 is generated by 16-bit memory PC Cards that include

batteries. BVD2 is used with BVD1 as an indication of the condition of the batteries on a

memory PC Card. Both BVD1 and BVD2 are high when the battery is good. When BVD2

is low and BVD1 is high, the battery is weak and should be replaced. When BVD1 is low,

the battery is no longer serviceable and the data in the memory PC Card is lost. See

Section 5.6, ExCA Card Status-Change-Interrupt Configuration Register, for enable bits.

See Section 5.5, ExCA Card Status-Change Register, and Section 5.2, ExCA Interface

Status Register, for the status bits for this signal.

Speaker. SPKR

have been configured for the 16-bit I/O interface. The audio signals from cards A and B are

combined by the PCI1410 and are output on SPKROUT.

DMA request. BVD2 can be used as the DMA request signal during DMA operations to a

16-bit PC Card that supports DMA. The PC Card asserts BVD2 to indicate a request for a

DMA operation.

Card detect 1 and card detect 2. CD1 and CD2 are internally connected to ground on the

PC Card. When a PC Card is inserted into a socket, CD1

I

status, see Section 5.2, ExCA Interface Status Register.

Card enable 1 and card enable 2. CE1 and CE2 enable even- and odd-numbered address

bytes. CE1

O

address bytes.

Input acknowledge. INPACK is asserted by the PC Card when it can respond to an I/O read

cycle at the current address.

DMA request. INPACK

a 16-bit PC Card that supports DMA. If it is used as a strobe, then the PC Card asserts this

signal to indicate a request for a DMA operation.

I/O read. IORD is asserted by the PCI1410 to enable 16-bit I/O PC Card data output during

host I/O read cycles.

DMA write. IORD

Card that supports DMA. The PCI1410 asserts IORD

Card to host memory.