Sony CDXC-8050-X Service manual

CDX-C8050X

SERVICE MANUAL

Ver 1.2 2001.06

• The tuner and CD sections have no adjustments.

SPECIFICATIONS

AUDIO POWER SPECIFICATIONS

POWER OUTPUT AND TOTAL HARMONIC DISTORTION

19 watts per channel minimum continuous average power into

4 ohms, 4 channels driven from 10 Hz to 20 kHz with no more

than 1% total harmonic distortion.

Other Specifications

CD player section

System Compact disc digital audio

Signal-to-noise ratio 90 dB

Frequency response 10 – 20,000 Hz

Wow and flutter Below measurable limit

Laser Diode Properties

Material GaAlAs

Wavelength 780 nm

Emission Duration Continuous

Laser output power Less than 44.6 µW*

* This output is the value measured at a distance

of 200 mm from the objective lens surface on the

Optical Pick-up Block.

Tuner section

FM

Tuning range 87.5 – 107.9 MHz

Antenna terminal External antenna connector

Intermediate frequency 10.7 MHz/450 kHz

Usable sensitivity 8 dBf

Selectivity 75 dB at 400 kHz

Signal-to-noise ratio 66 dB (stereo),

Harmonic distortion at 1 kHz

Separation 35 dB at 1 kHz

Frequency response 30 – 15,000 Hz

AM

Tuning range 530 – 1,710 kHz

Antenna terminal External antenna connector

Intermediate frequency 10.7 MHz/450 kHz

Sensitivity 30 µV

system

72 dB (mono)

0.6% (stereo),

0.3% (mono)

US Model

Model Name Using Similar Mechanism NEW

CD Drive Mechanism Type MG-383V-121//Q

Optical Pick-up Name KSS-720A

Power amplifier section

Outputs Speaker outputs

(sure seal connectors)

Speaker impedance 4 – 8 ohms

Maximum power output 50 W × 4 (at 4 ohms)

General

Outputs Audio outputs

Power antenna relay

control lead

Power amplifier control

lead

Telephone ATT control

lead

Power requirements 12 V DC car battery

(negative ground)

Dimensions Approx. 178 × 50 × 183 mm

(7 1/8 × 2 × 7 1/4 in.)

(w/h/d)

Mounting dimensions Approx. 182 × 53 × 162 mm

(7 1/4 × 2 1/8 × 6 1/2 in.)

(w/h/d)

Mass Approx. 1.3 kg (2 lb. 14 oz.)

Supplied accessories Card remote commander RM-X91

Parts for installation and

connections (1 set)

Front panel case (1)

Design and specifications are subject to change without

notice.

FM/AM COMPACT DISC PLAYER

9-870-128-12

2001F0400-1

© 2001.6

Sony Corporation

e Vehicle Company

Shinagawa Tec Service Manual Production Group

1

Ver 1.1 2000. 08

k

SERVICE NOTES

CAUTION

Use of controls or adjustments or performance of procedures

other than those specified herein may result in hazardous

radiation exposure.

If the optical pick-up block is defective, please replace the whole

optical pick-up block.

Never turn the semi-fixed resistor located at the side of optical

pick-up block.

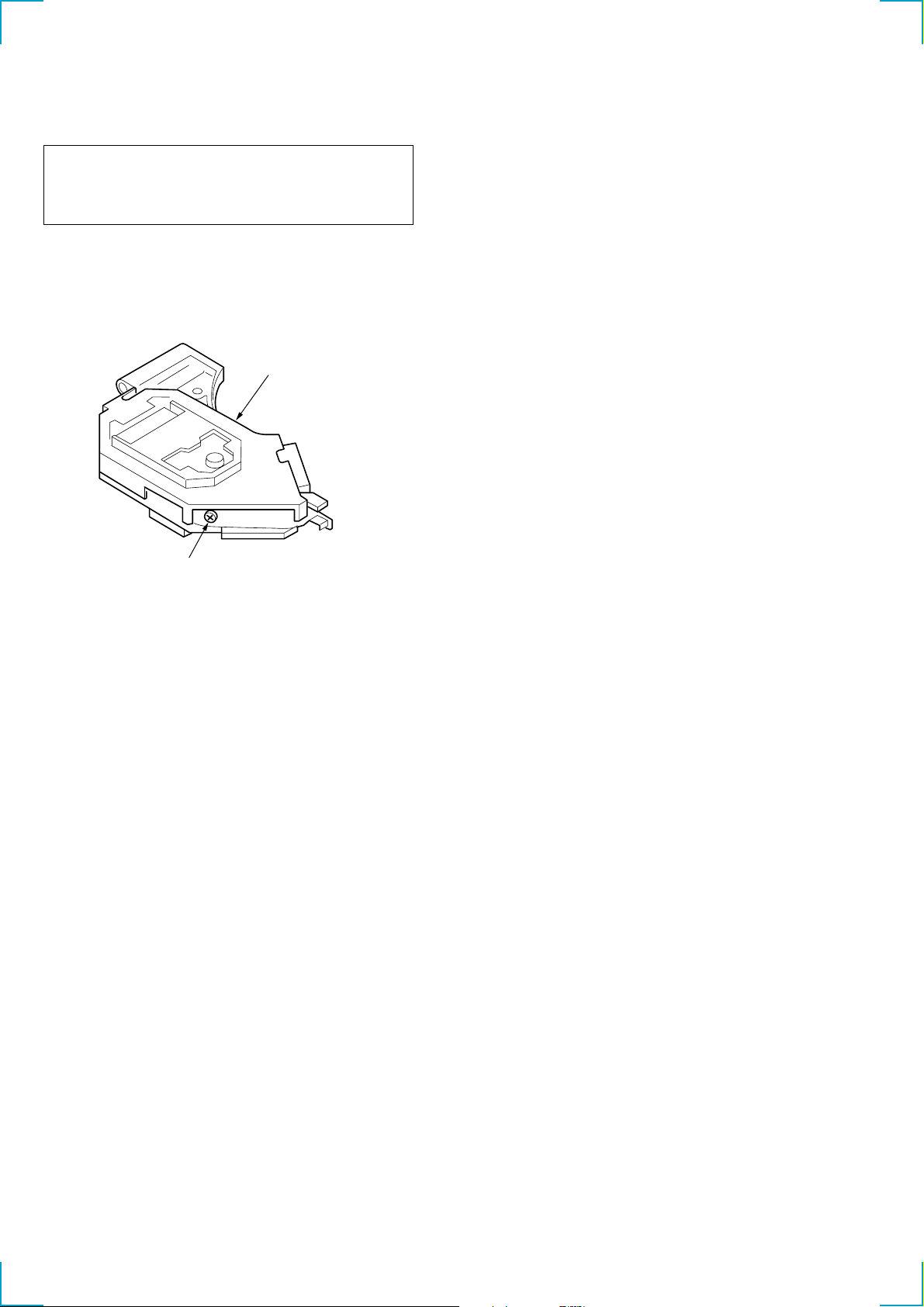

optical pick-up bloc

semi-fixed resistor

NOTES ON HANDLING THE OPTICAL PICK-UP BLOCK

OR BASE UNIT

The laser diode in the optical pick-up block may suffer electrostatic

breakdown because of the potential difference generated by the

charged electrostatic load, etc. on clothing and the human body.

During repair, pay attention to electrostatic breakdown and also use

the procedure in the printed matter which is included in the repair

parts.

The flexible board is easily damaged and should be handled with

care.

NOTES ON LASER DIODE EMISSION CHECK

The laser beam on this model is concentrated so as to be focused on

the disc reflective surface by the objective lens in the optical pickup block. Therefore, when checking the laser diode emission, observe from more than 30 cm away from the objective lens.

Notes on Chip Component Replacement

• Never reuse a disconnected chip component.

• Notice that the minus side of a tantalum capacitor may be dam-

aged by heat.

TABLE OF CONTENTS

1. GENERAL

Location of controls ................................................................. 3

Getting Started ......................................................................... 3

Setting the clock ...................................................................... 3

CD/MD .................................................................................... 4

Radio ....................................................................................... 5

DSP .......................................................................................... 6

Other Functions ....................................................................... 7

TV/Video ................................................................................. 8

Additional Information ............................................................ 9

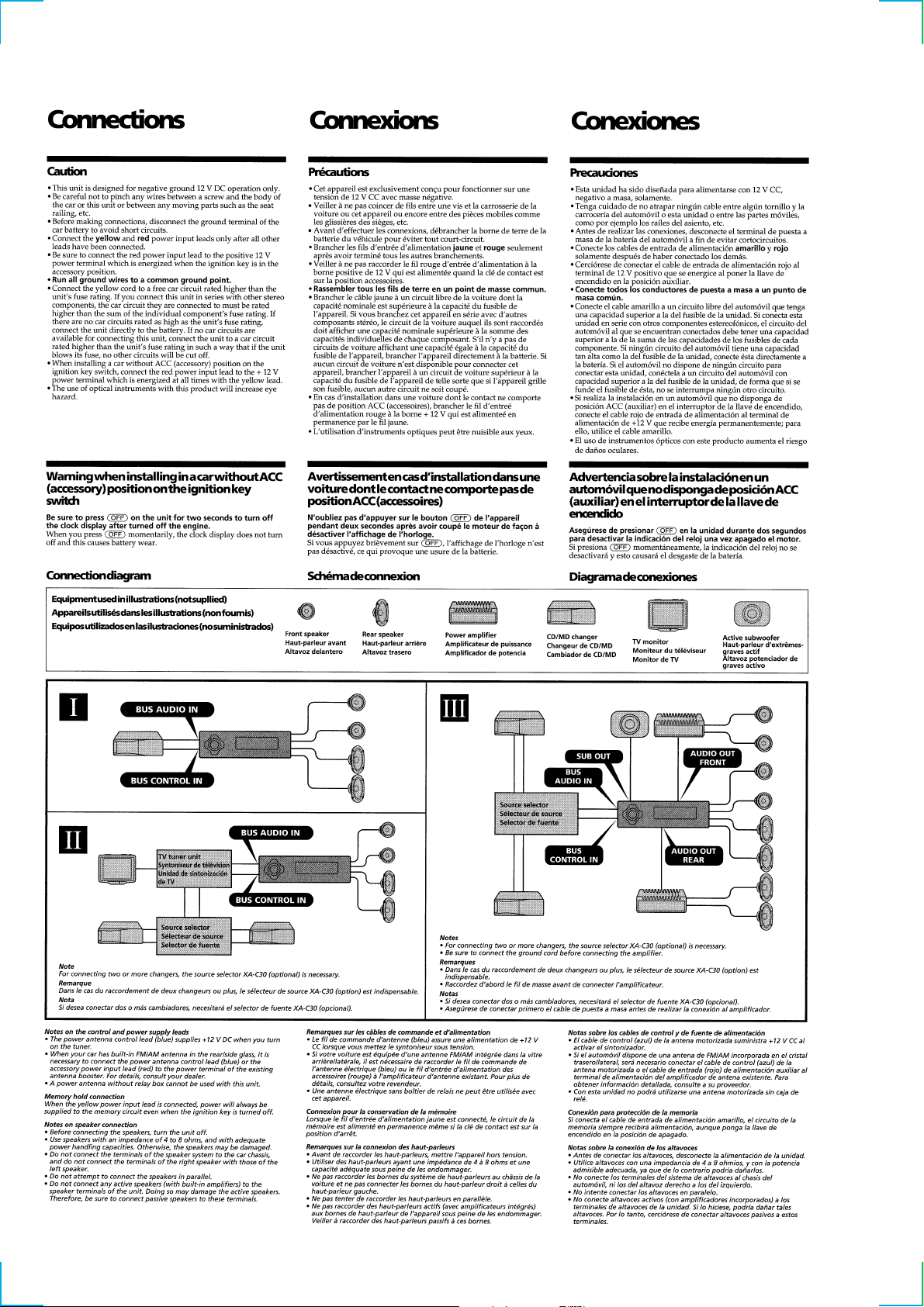

Connections ........................................................................... 10

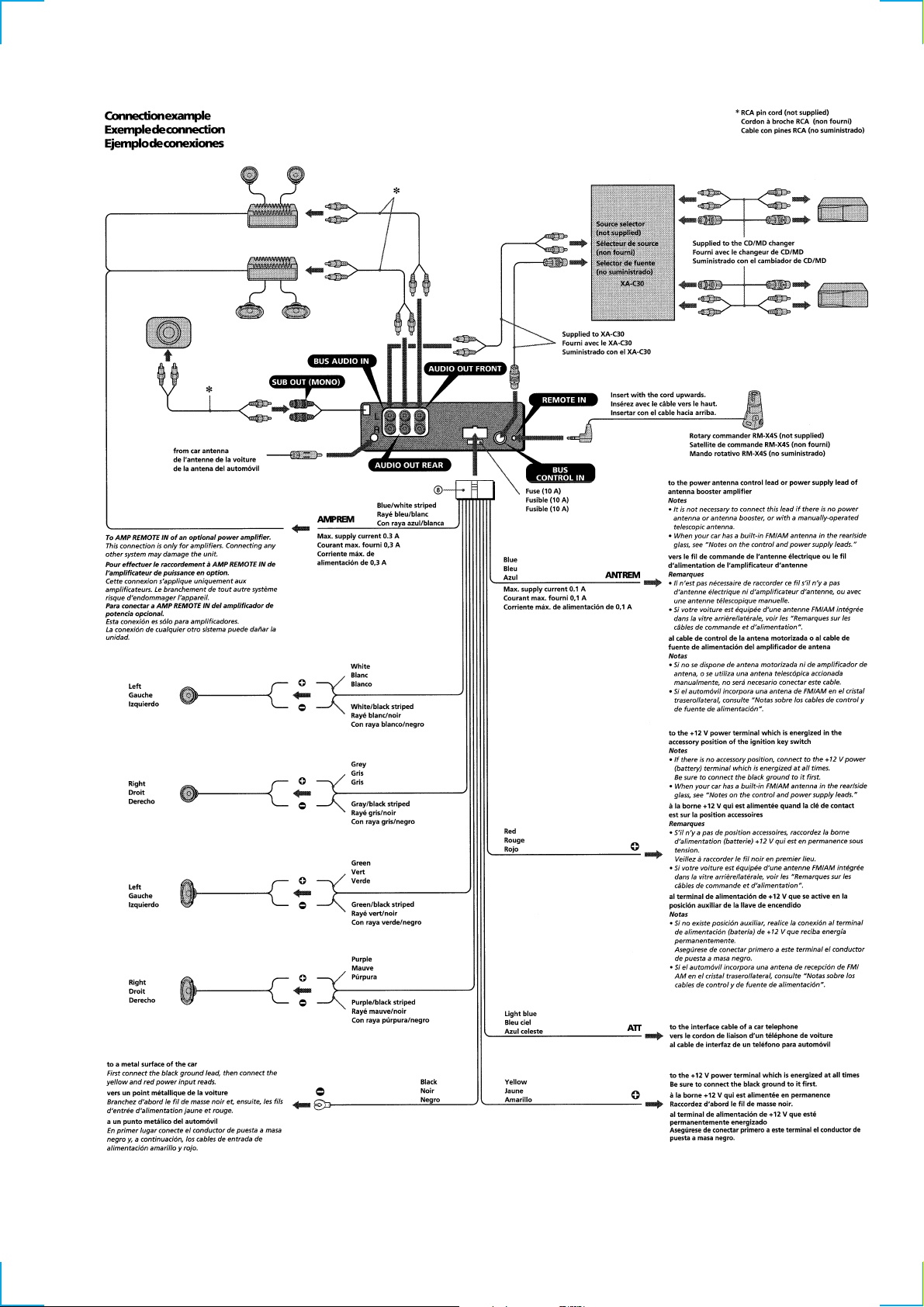

2. DISASSEMBLY

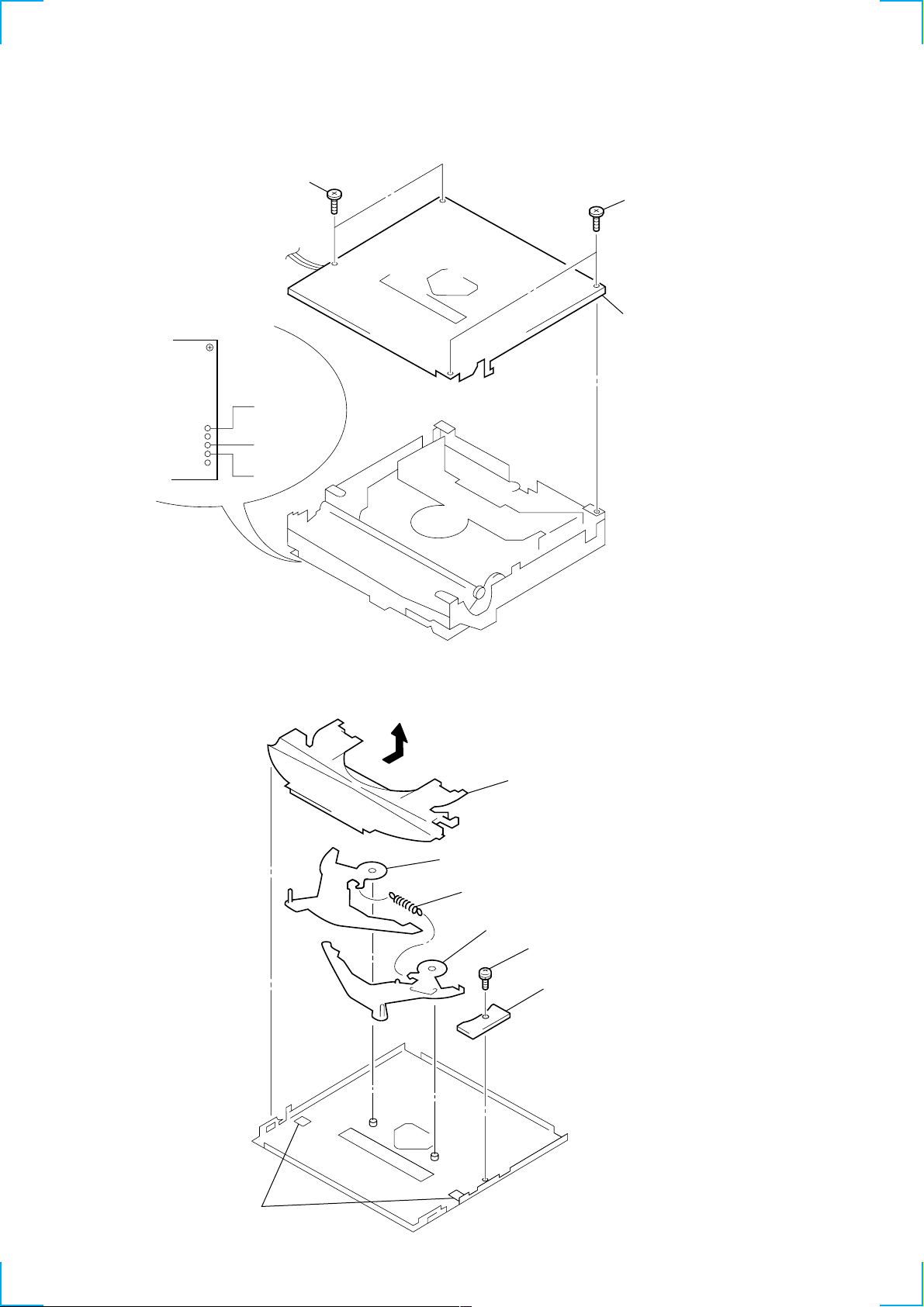

2-1. Sub Panel Assy .................................................................. 12

2-2. CD Mechanism Block ....................................................... 12

2-3. Main Board ....................................................................... 13

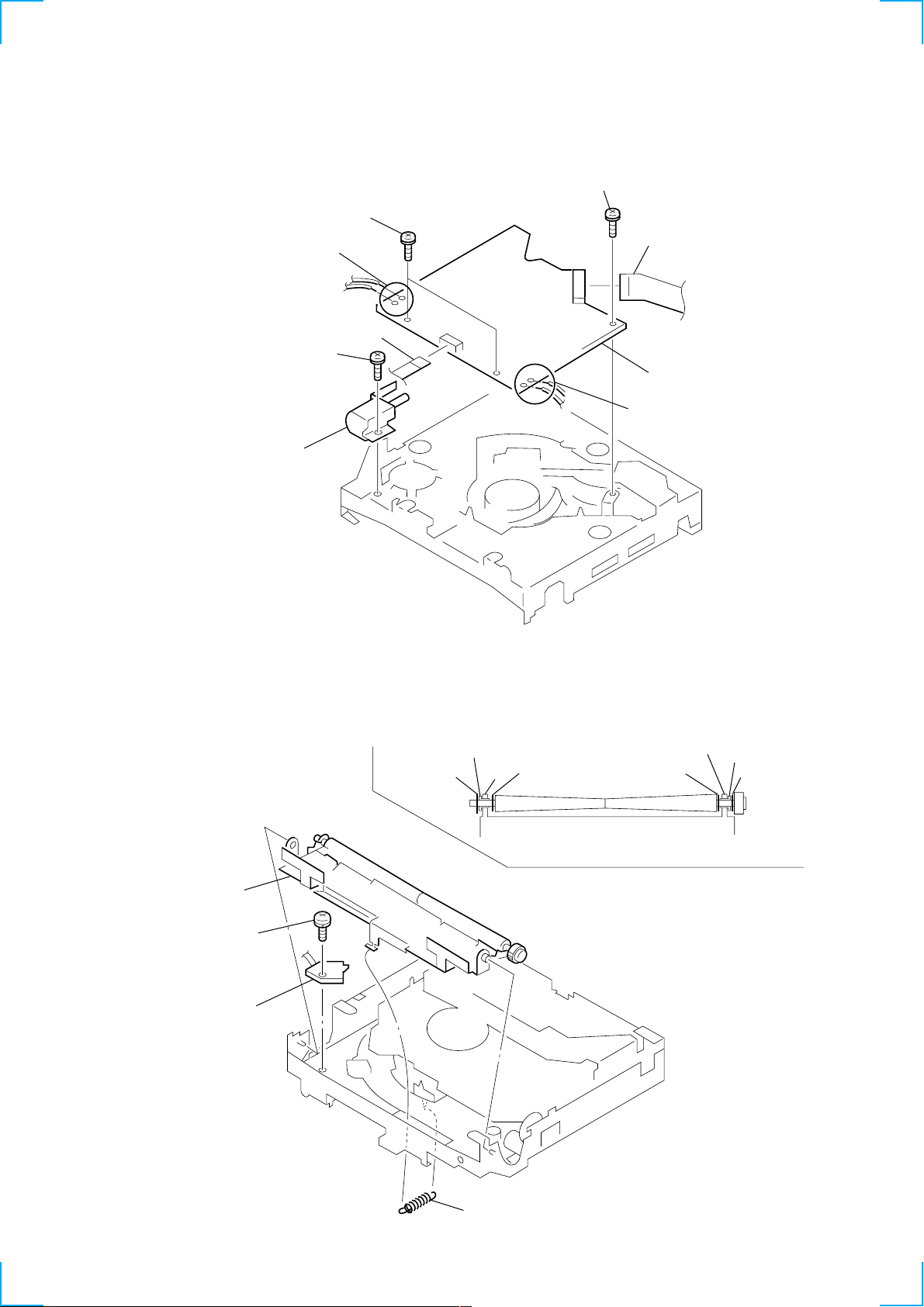

2-4. Heat Sink ........................................................................... 13

2-5. Chassis (T) Assy................................................................ 14

2-6. Lever Assy ......................................................................... 14

2-7. Servo Board ....................................................................... 15

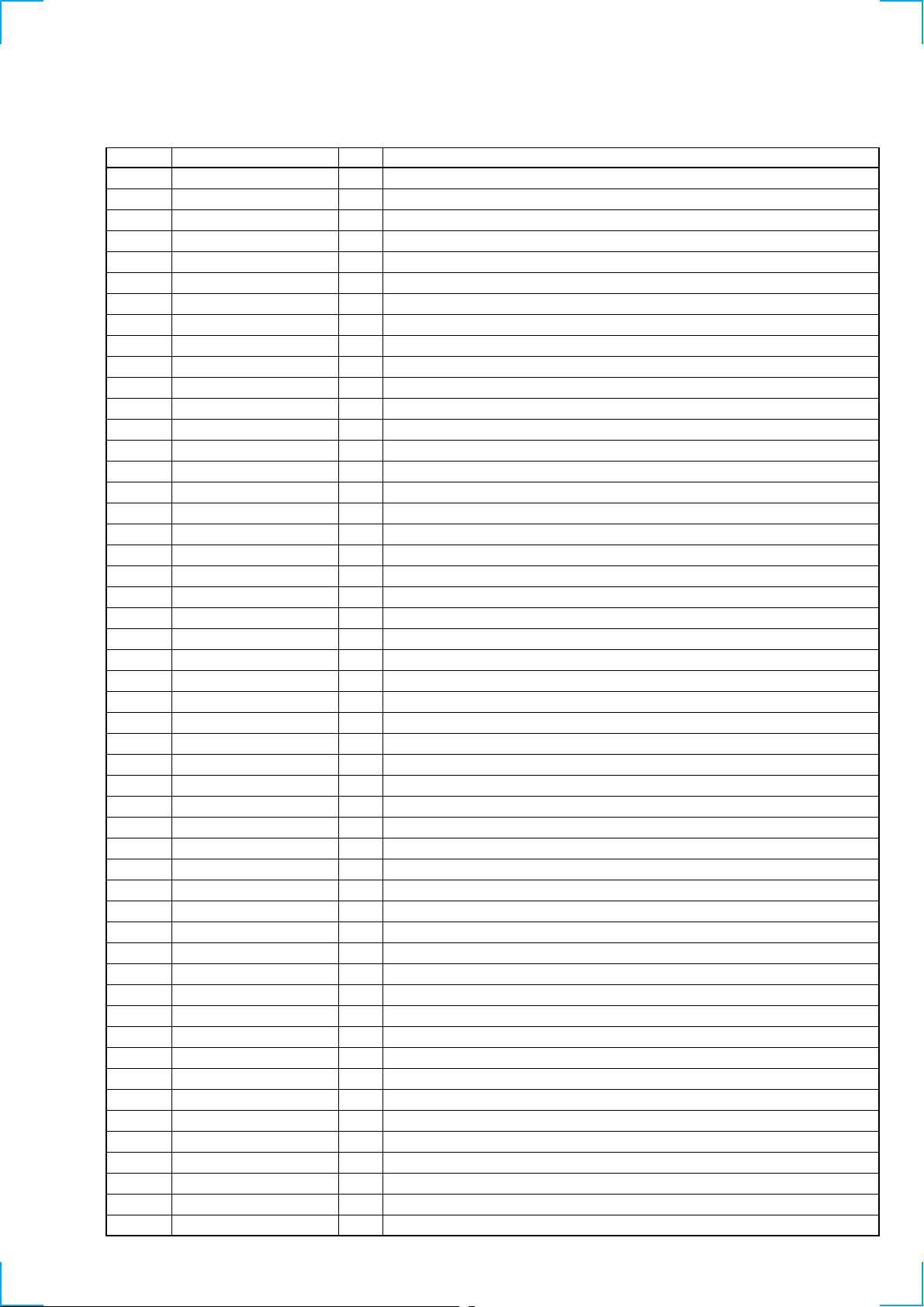

2-8. ARM Roller Assy .............................................................. 15

2-9. Chassis (OP) Assy ............................................................. 16

2-10. Optical Pick-up Block ....................................................... 16

3. DIAGRAMS

3-1. IC Pin Descriptions ........................................................... 17

3-2. Block Diagram –CD Section– ........................................... 26

3-3. Block Diagram –Tuner Section– ....................................... 27

3-4. Block Diagram –Display Section– .................................... 28

3-5. Circuit Boards Location .................................................... 29

3-6. Printed Wiring Boards –CD Mechanism Section–............ 30

3-7. Schematic Diagram –CD Mechanism Section (1/2)– ....... 32

3-8. Schematic Diagram –CD Mechanism Section (2/2)– ....... 33

3-9. Printed Wiring Board –Main Section– .............................. 34

3-10. Schematic Diagram –Main Section (1/4)– ........................ 36

3-11. Schematic Diagram –Main Section (2/4)– ........................ 37

3-12. Schematic Diagram –Main Section (3/4)– ........................ 38

3-13. Schematic Diagram –Main Section (4/4)– ........................ 39

3-14. Printed Wiring Board –DSO Section– .............................. 40

3-15. Schematic Diagram –DSO Section– ................................. 41

3-16. Printed Wiring Board –Sub (CD) Section– ....................... 42

3-17. Schematic Diagram –Sub (CD) Section– .......................... 43

3-18. Printed Wiring Board –Key Section– ................................ 44

3-19. Schematic Diagram –Key Section– .................................. 45

4. EXPLODED VIEWS

4-1. Chassis Section ................................................................. 48

4-2. Front Panel Section ........................................................... 49

4-3. CD Mechanism Section (1) ............................................... 50

4-4. CD Mechanism Section (2) ............................................... 51

4-5. CD Mechanism Section (3) ............................................... 52

SAFETY-RELATED COMPONENT WARNING!!

COMPONENTS IDENTIFIED BY MARK 0 OR DOTTED LINE

WITH MARK 0 ON THE SCHEMATIC DIAGRAMS AND IN

THE PARTS LIST ARE CRITICAL TO SAFE OPERATION.

REPLACE THESE COMPONENTS WITH SONY PARTS WHOSE

PART NUMBERS APPEAR AS SHOWN IN THIS MANUAL OR

IN SUPPLEMENTS PUBLISHED BY SONY.

2

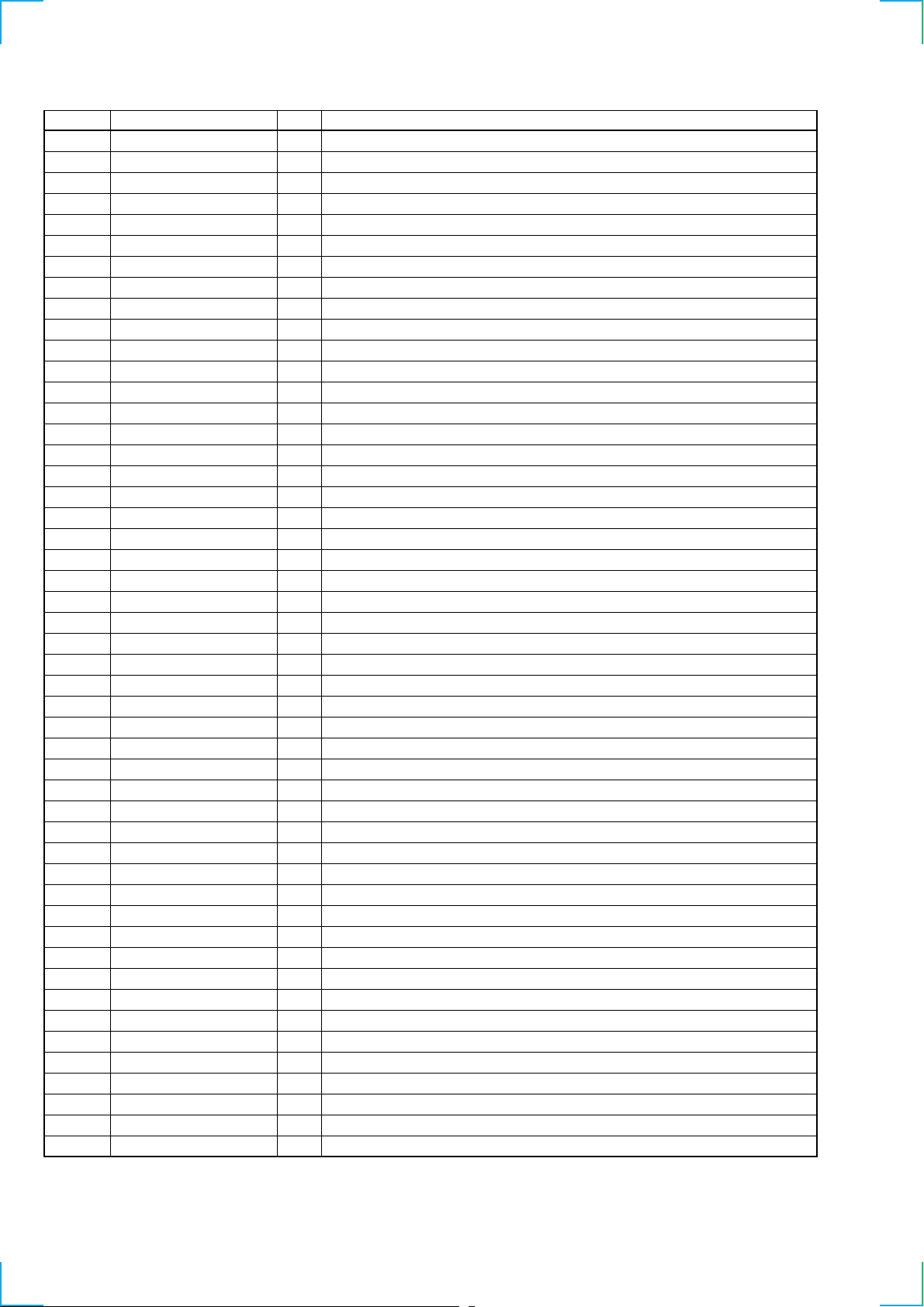

5. ELECTRICAL PARTS LIST ........................................ 53

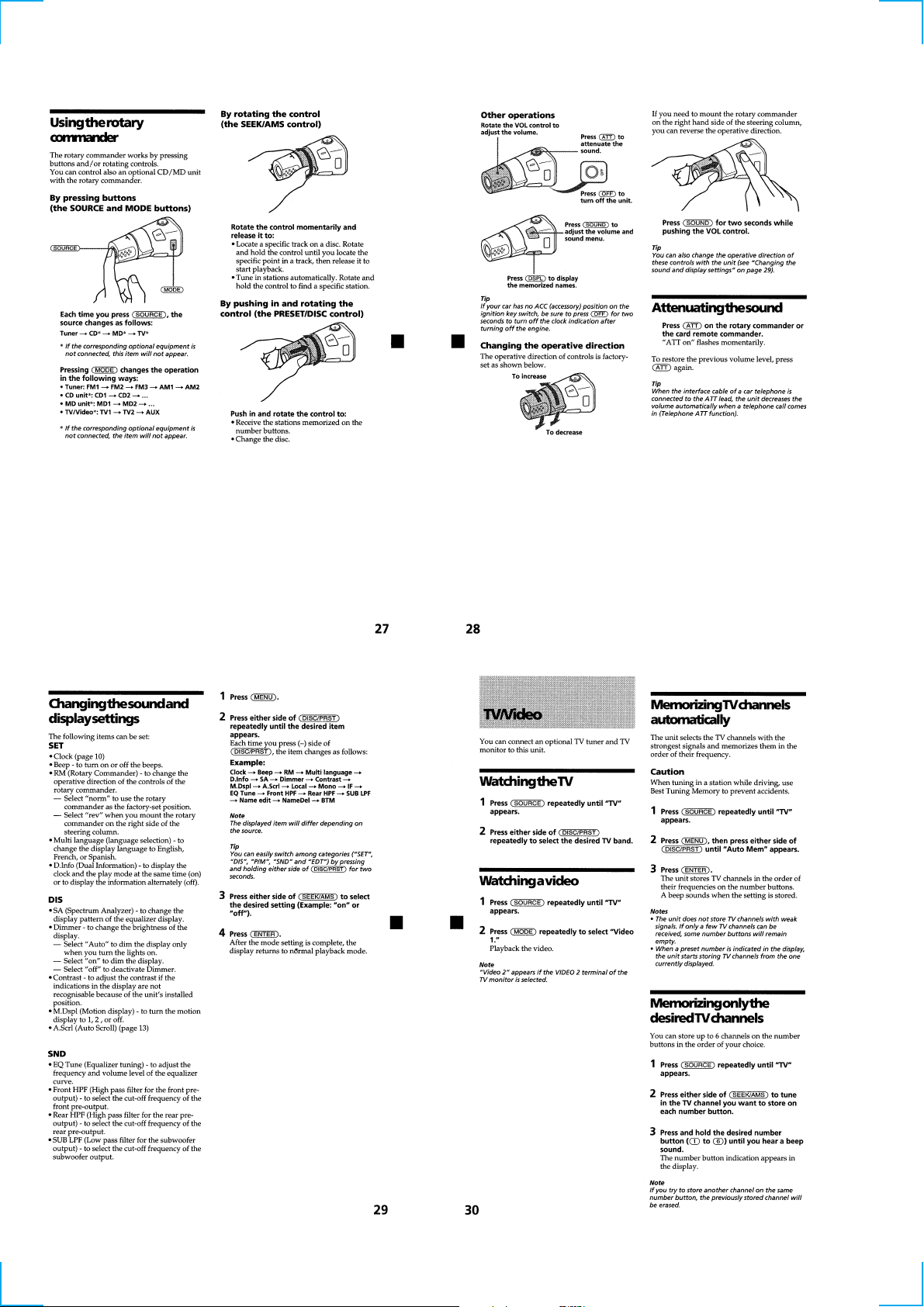

SECTION 1

GENERAL

This section is extracted

from instruction manual.

3

45678910

11

SECTION 2

DISASSEMBLY

Note : Follow the disassembly procedure in the numerical order given.

2-1. SUB PANEL ASSY

4 two claws

6 sub panel assy

2 PTT 2.6x8

2-2. CD MECHANISM BLOCK

5 CD mechanism block

2 PTT 2.6x5

3 claw

5 CN701

1 PTT 2.6x8

7 bracket (CD)

6 PTT 2.6x5

12

3

1 PTT 2.6x5

4 CN401

7 heat sink

1 PTT 2.6x8

2 PTT 2.6x8

4 PTT 2.6x8

5 PTT 2.6x8

6 PTT 2.6x8

3 PTT 2.6x12

2-3. MAIN BOARD

7 ground point screws

(PTT 2.6x6)

1 CN301

8 MAIN board

6 ground point screw

(PTT 2.6x6)

5 PTT 2.6x10

4 PTT 2.6x10

3 cord (connector)

2 PTT 2.6x10

2-4. HEAT SINK

13

2-5. CHASSIS (T) ASSY

2 P 2x3

3 P 2x3

2-6. LEVER ASSY

1 Unsolder the

lead wires.

4 chassis (T) assy

black

red

white

4 claws

5 guide (disc)

6 lever (R) assy

3 tension spring (LR)

7 lever (L) assy

1 PS 2x4

2 DISC IN SW board

14

2-7. SERVO BOARD

7 PS 2x4

8 PS 2x4

3 Removal the solders.

5 P 2x3

6 loading motor assy

(M903)

2-8. ARM R OLLER ASSY

• When installing, take note of the positions

arm (roller) and washers. (Fig. 1)

2 CN2

1 CN3

9 SERVO board

4 Removal the solders.

2 arm roller assy

3 PS 2x3

4 LOAD SW board

shaft retainer

washer (RA)

arm

washer

Fig. 1

washer

arm

shaft retainer

washer (RA)

1 tension spring (RA)

15

2-9. CHASSIS (OP) ASSY

8 compression spring (FL)

1 tension spring (KF1)

7 chassis (OP) assy

9 compression spring (FL)

2 tension spring (KR1)

5 Fit lever (D) in the

direction of the arrow.

6 Turn loading ring in the

direction of the arrow.

4 damper (T)

2-10. OPTICAL PICK-UP BLOCK

1 P 2x3

2 sled motor assy

(M902)

3 damper (T)

3 optical pick-up block

16

SECTION 3

DIAGRAMS

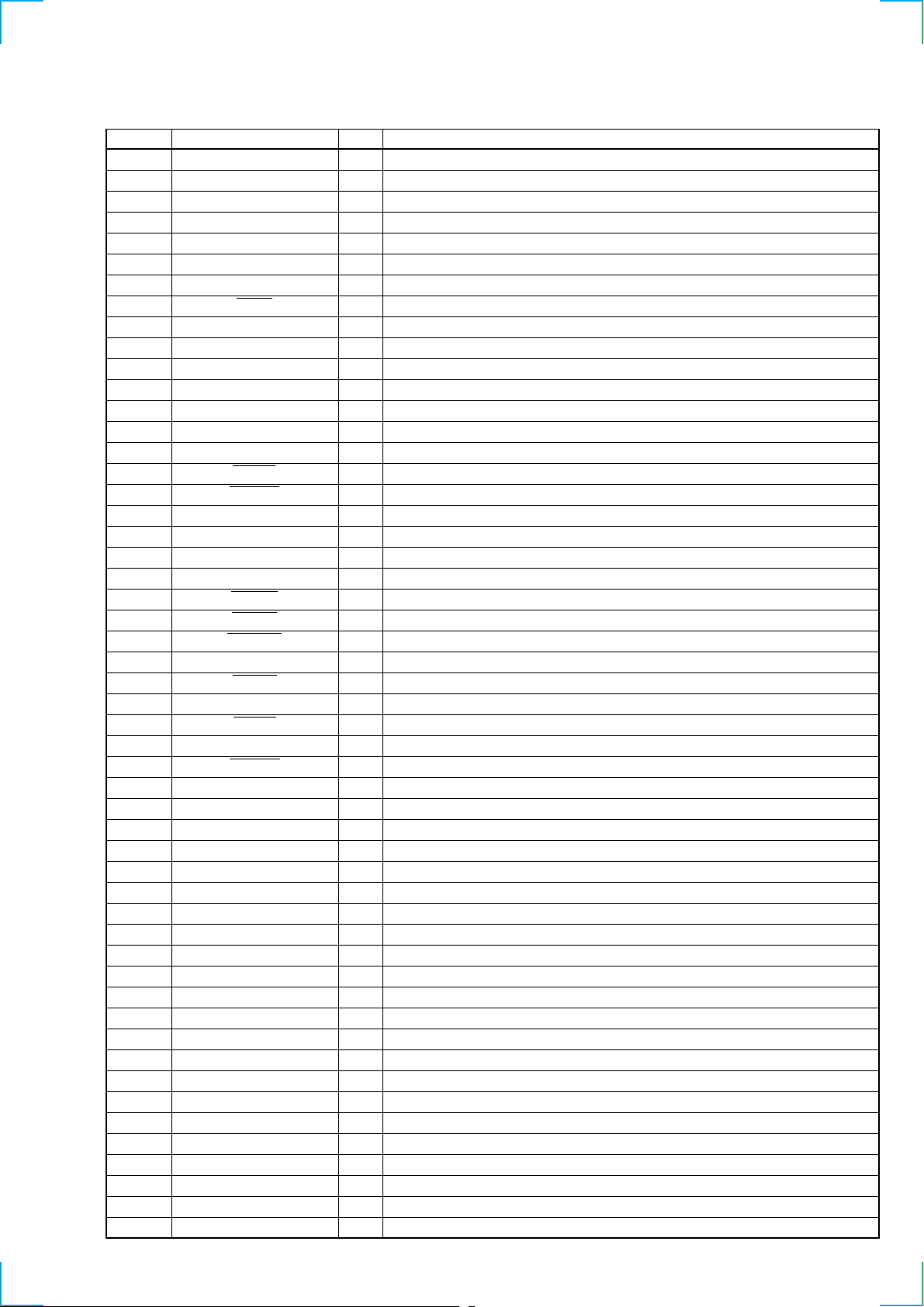

3-1. IC PIN DESCRIPTIONS

• IC501 CXD2598Q (DIGITAL SERVO, DIGITAL SIGNAL PROCESSOR) (SERVO BOARD)

Pin No. Pin Name I/O Pin Description

1 DVDD — Digital power supply pin

2 DVSS — Digital ground

3 SOUT O Servo brock serial data output (Not used.)

4 SOCK O Servo brock serial data read clock output (Not used.)

5 XOLT O Servo brock serial data latch output (Not used.)

6 SQSO O Sub Q 80 bit, PCM peak and level data output. CD TEXT data output

7 SQCK I Clock input from SQSO read output.

8 SCSY I Fixed at “L”.

9 SBSO O Serial output of sub-P to W. (Not used.)

10 EXCK I Clock input from SBSO read output. (Fixed at “L”)

11 XRST I System reset (“L”: Reset)

12 STSM I System mute input (Fixed at “L”)

13 DATA I Serial data input from CPU.

14 XLAT I Latch input from CPU. Latch serial data at the falling edge.

15 CLOK I Serial data transfer clock input from CPU.

16 SENS O SENS output for CPU.

17 SCLK I Clock input from SENS serial data read.

18 ATSK I/O Input/output for anti-shock.

19 WFCK O WFCK (Write Flame Clock) output (Not used.)

20 XUGF O XUGF output (Not used.)

21 XPCK O XPCK output (Not used.)

22 GFS O GFS output

23 C2PO O C2PO output (Not used.)

24 SCOR O “H” output at either detection, sub code sync S0 or S1.

25 C4M O 4.2336 MHz output (Not used.)

26 WDCK O Word clock input f=2Fs (Not used.)

27 COUT I/O Track number count signal input/output (Not used.)

28 MIRR I/O Mirror signal input/output (Not used.)

29 DVSS — Digital ground

30 DVDD — Digital power supply pin

31 DFCT I/O Diffect signal input/output (Not used.)

32 FOK I/O Focus OK signal output

33 PWM1 I External control input of spindle motor.

34 LOCK I/O Lock signal input/output

35 MDP O Servo control output of spindle motor.

36 SSTP I Disc most inner track detection signal input

37 FSTIO I/O 2/3 frequency division output of pins ih and ij. (Not used.)

38 SFDR O Sled drive output

39 SRDR O Sled drive output

40 TFDR O Tracking drive output

41 TRDR O Tracking drive output

42 FFDR O Focus drive output

43 FRDR O Focus drive output

44 DVDD — Digital power supply pin

45 DVSS — Digital ground

46 TEST I Test pin (Fixed at “L”)

47 TES1 I Test pin (Fixed at “L”)

48 XTSL I X’tal select input (“L”: 16.9344 MHz, “H”: 33.8688 MHz)

49 VC I Center voltage input

50 FE I Focus error signal input

51 SE I Sled error signal input

17

Pin No. Pin Name I/O Pin Description

52 TE I Tracking error signal input

53 CE I Center servo analog input

54 RFDC I RF signal input

55 ADIO O Test pin (Not used.)

56 AVSSO — Analog ground

57 IGEN I Constant current input from OP amplifier.

58 AVDDO — Analog ground

59 ASYO O EFM full-swing output (“L”: VSS, “H”: VDD)

60 ASYI I Asymmetry comparate voltage input

61 RFAC I EFM signal input

62 AVSS3 — Analog ground

63 CLTV I VCO control voltage input from master.

64 FILO O Filter output for master PLL (slave=digital PLL)

65 FILI I Filter input from master PLL.

66 PCO O Charge pump output for master PLL.

67 AVDD3 — Analog power supply pin

68 BIAS I Asymmetry circuit constant current input

69 VCTL I VCO2 control input from wideband EFM PLL. (Not used.)

70 V16M O VCO2 oscillator output for wideband EFM PLL. (Not used.)

71 VPCO O Charge pump output for wideband EFM PLL. (Not used.)

72 DVSS — Digital ground

73 MD2 I Digital out ON/OFF control input (“L”: OFF, “H”: ON)

74 DOUT O Digital out output

75 ASYE I Asymmetry circuit ON/OFF input (“L”: OFF, “H”: ON)

76 DVDD — Digital power supply pin

77 LRCK O D/A interface LR clock output (f=Fs)

78 LRCKI I D/A interface LR clock input

79 PCMD O D/A interface serial data output (2’s COMP, MSB fast)

80 PCMD I D/A interface serial data input (2’s COMP, MSB fast)

81 BCK O D/A interface bit clock output

82 BCKI I D/A interface bit clock input

83 EMPH O Emphasis ON/OFF signal output

84 EMPHI I Emphasis ON/OFF signal input (“H”: ON, “L”: OFF)

85 XVDD — Power supply for master clock.

86 XTAI I X’tal oscillator input from master clock (16.9344 MHz).

87 XTAO O X’tal oscillator output for master clock (16.9344 MHz) (Not used.)

88 XVSS — Ground pin for master clock.

89 AVDD1 — Analog power supply pin

90 AOUT1 O Lch analog output (Not used.)

91 AIN1 I Lch OPAMP input (Not used.)

92 LOUT1 O Lch LINE output (Not used.)

93 AVSS1 — Analog ground

94 AVSS2 — Analog ground

95 LOUT2 O Rch LINE output (Not used.)

96 AIN2 I Rch OPAMP input (Not used.)

97 AOUT2 O Rch analog output (Not used.)

98 AVDD2 — Analog power supply pin

99 RMUT O Rch “0” detect Flug (Not used.)

100 LMUT O Lch “0” detect Flug (Not used.)

18

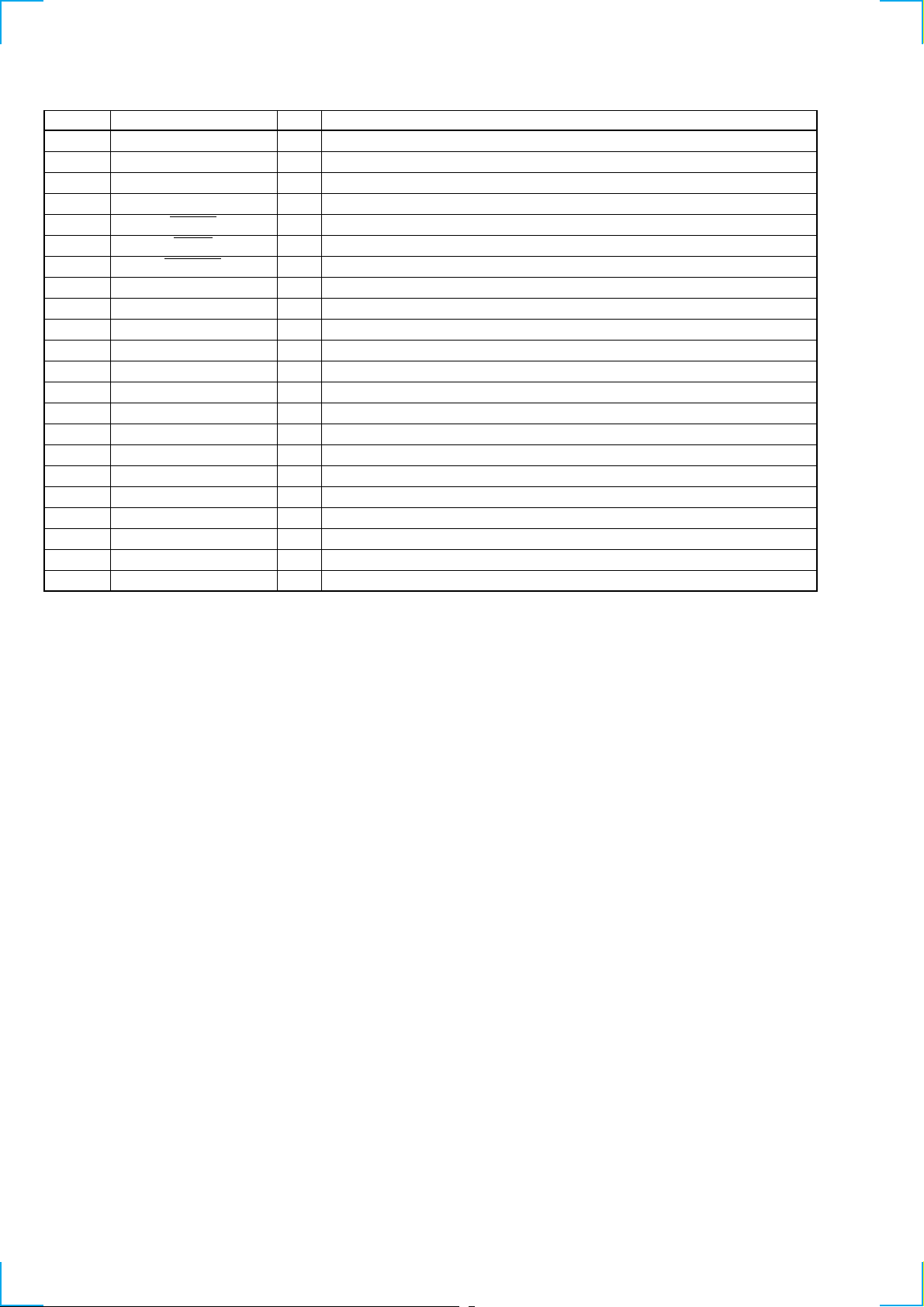

• IC5 CXP84640-072Q (CD SYSTEM CONTROL) (SERVO BOARD)

Pin No. Pin Name I/O Pin Description

1 ITRPT — Not used in this set.

2, 3 ——Not used in this set.

4, 5 NCO — Not used in this set.

6 OPEN I Front panel open detection input

7 CLOSE O Front panel close control output

8 LINKOFF I Bus interface link input

9 NCO — Not used in this set.

10 D SW I Down switch input (SW4)

11 SSTP I Limit switch input (SW3)

12, 13 NCO — Not used in this set.

14, 15 ——Not used in this set.

16 EMPH O O De-emphasis ON/OFF control output

17 CDMON O CD mechanism deck power control output

18 CD ON O CD power control output

19 A MUT O System attenuate control output

20 LD ON O Laser power ON/OFF control output

21 CD RST O CD system reset output

22 HOLD O Hold switch output

23 AGC CONT O AGC control output

24 ——Not used in this set.

25 PH3 I Not used in this set.

26 TSTIN0 I Not used in this set.

27 TSTIN1 I Not used in this set.

28 TST.CLV I Not used in this set.

29 NCO — Not used in this set.

30 RESET I System reset input (“L”=Reset)

31 X IN I X’tal oscillator input from system clock. (10 MHz)

32 X OUT O X’tal oscillator output for system clock. (10 MHz)

33 GND — Analog ground

34 XT OUT O Not used in this set.

35 XT IN I Not used in this set.

36 AVSS — A/D converter ground

37 AVREF I A/D converter reference voltage input

38 TEP L I Not used in this set.

39 TEP H I Not used in this set.

40 SLED– I Sled drive input

41 PH2 I Not used in this set.

42 SEK/SMET I Fixed at “H” in this set.

43 GFS/MNT2 SEL I Fixed at “H” in this set.

44 SC-JIG ON/OFF I Fixed at “H” in this set.

45 SCLK O CD-TEXT data read clock output

46 LOCK I/O Lock signal input/output

47 ——Not used in this set.

48 SCK2 O Sub Q read clock output

49 SI2 I Sub Q 80 bit, PCM peak and level data 16 bit input.

50 ——Not used in this set.

51 BUS CLK I/O Bus system serial clock input/output

52 BUS SI I Bus system serial interface input

53 BUS SO O Bus system serial interface output

54 F OK I Focus OK signal input

55 GFS I GFS signal detection input

56 TEST MODE I Fixed at “H” in this set.

19

Pin No. Pin Name I/O Pin Description

57 SENS I SENS signal input

58 ——Not used in this set.

59 ——Not used in this set.

60 BU.IN I Back-up power detection input

61 BUSON I Bus on control input

62 IN SW I Disc in switch input (SW1)

63 SELF SW I Self switch input (SW2)

64 SCOR O Sub-code sync output

65 CD-CKO O CD signal process serial clock input

66 LM LOD O Loading motor control output

67 CD DATA O CD signal process serial data output

68 CD-XLAT O CD signal process serial data latch output

69 LM-EJ O Loading motor control output

70 DRV-OE O Focus/tracking coil/sled motor control output

71 MD2 O Digital out ON/OFF control output (“L”: OFF, “H”: ON)

72 VDD — Power supply pin

73 NIH I Fixed at “H” in this set.

74 V/Z I Fixed at “H” in this set.

75 PH1 I Not used in this set.

76 ——Not used in this set.

77 DOUT-SEL I Fixed at “H” in this set.

78 – 80 ——Not used in this set.

20

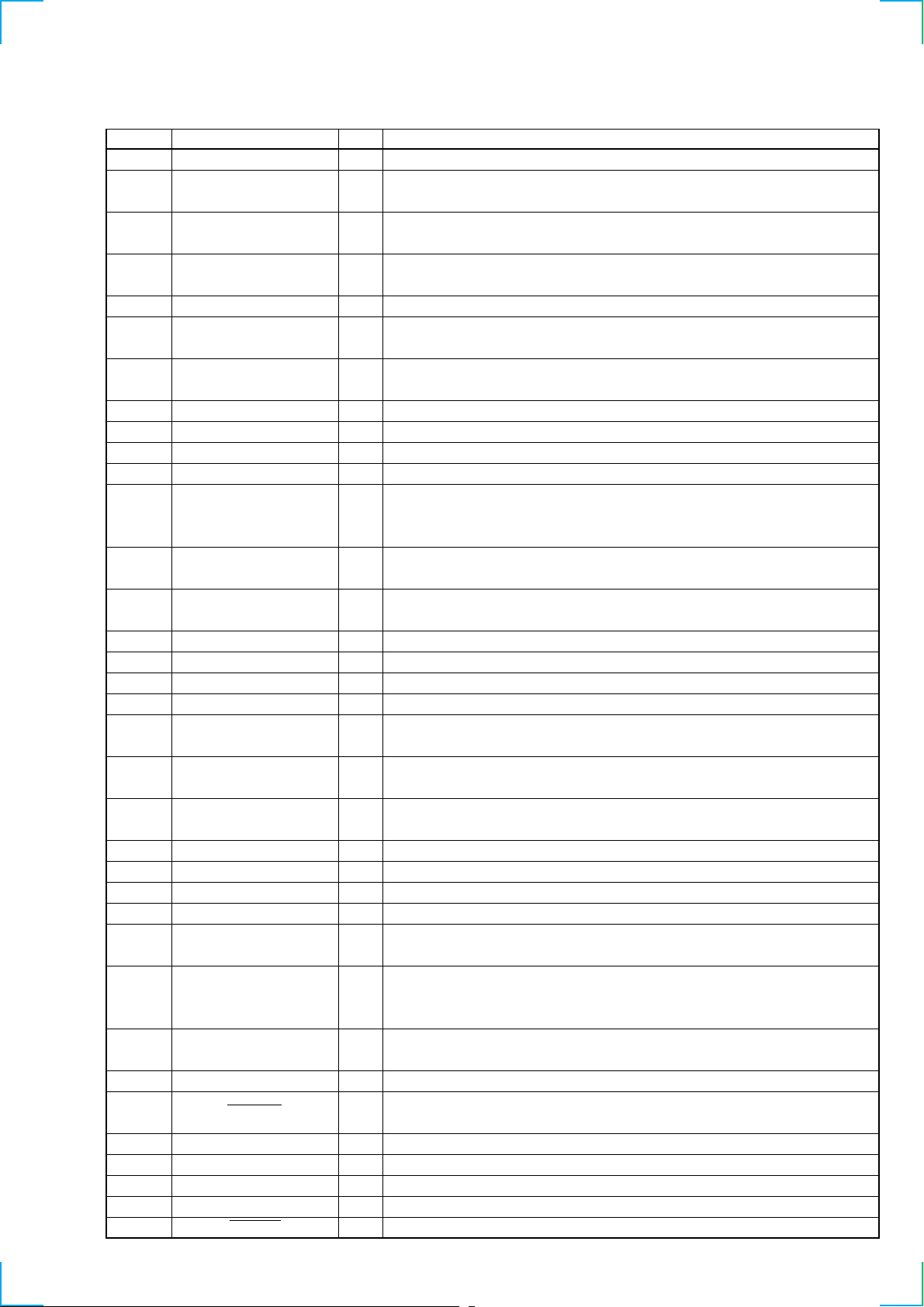

• IC502 MB90574PMT-G-263-BND (SYSTEM CONTROL) (MAIN BOARD)

Pin No. Pin Name I/O Pin Description

1 NIL I Not used (fixed at “L”)

2 AMSIN I

3 AMSON O

4 SP LAT O

5 ATT O Audio line muting on/off control signal output terminal “L”: muting on

6 SYSRST O

7 F/R O

8 VCC — Power supply terminal (+5 V)

9 MTLIN I Auto metal detection signal input terminal Not used (fixed at “L”)

10 E2PSIO I/O Two-way data bus for tuner EEPROM with the FM/AM tuner unit (TUX201)

11 E2PCKO O Tuner EEPROM bus clock signal output to the FM/AM tuner unit (TUX201)

12 FLS SI I

13 FLS SO O

14 BUS-ON O

15 BEEP O Beep sound drive signal output terminal

16 NCO O Not used (open)

17 UNISI I Serial data input from the SONY bus interface (IC601)

18 UNISO O Serial data output to the SONY bus interface (IC601)

19 UNICKO O

20 IFWIDTH I

21 SWSHIFT O

22, 23 NCO O Not used (open)

24 SIRCS I Sircs remote control signal input from the remote control receiver (IC951)

25 DSPSI I Serial data input from the CXD2726Q (IC805)

26 DSPSO O Serial data output to the CXD2726Q (IC805)

27 DSPCKO O

28 DSPPLL O

29 DSPMST O

30 NCO O Not used (open)

31 VOLATT O

32 TU ATT O Muting on/off control signal output of the FM/AM tuner signal “L”: muting on

33 VSS — Ground terminal

34 C — Connected to coupling capacitor for the power supply

35 DSPLAT O Serial data latch pulse output to the CXD2726Q (IC805)

36 DSPRST O Reset signal output to the CXD2726Q (IC805) “L”: reset

Input terminal of whether a music is present or not is detected at auto music sensor

“L”: music is not present, “H”: music is present Not used (fixed at “L”)

Tape auto music sensor control ssignal output terminal

“L” is output to lower the gain for audio level at FF/REW mode Not used (open)

Serial data latch pulse output for spectrum analyzer section to the liquid crystal

display drive controller (IC701)

System reset signal output to the MD mechanism controller (IC501), liquid crystal

display drive controller (IC701) and SONY bus interface (IC601) “L”: reset

Tape detection signal output terminal “L”: reverse side, “H”: forward side

Not used (open)

Input terminal at the flash memory data write mode

Front panel open/close detection signal input terminal

“L” is input when the front panel is closed

Output terminal at the flash memory data write mode

Display serial data output to the liquid crystal display driver (IC901)

Bus on/off control signal output to the CD mechanism controller (IC5), liquid crystal

display drive controller (IC701) and SONY bus interface (IC601) “L”: bus on

Serial clock signal output to the CD mechanism controller (IC5), liquid crystal

display drive controller (IC701) and SONY bus interface (IC601)

Tuner wide/narrow select signal input terminal “L”: wide, “H”: narrow

Not used (fixed at “L”)

When the radio is tuned at the frequency to produce beats, shift the frequency of the

signal from the D/D converter so as to produce no beats.

Serial data transfer clock signal output to the CXD2726Q (IC805) and liquid crystal

display drive controller (IC701)

PLL clock control signal output to the CXD2726Q (IC805)

At “L” is output: fixed at “L” is PLCLK (pin ia of IC805 CXD2726Q )

At “H” is output: PLL clock signal output to the PLCLK (pin ia of IC805 CXD2726Q)

Bit clock (BCK) and L/R sampling (LRCK) signal master/slave mode selection signal

output to the CXD2726Q (IC805) “L”: master mode, “H”: slave mode

Pre amplifier muting on/off control signal output to the electrical volume (IC301)

“L”: muting on

21

Pin No. Pin Name I/O Pin Description

37 ANT CUT O

38 DVCC — Power supply terminal (+5 V) (for D/A converter)

39 DVSS — Ground terminal (for D/A converter)

40, 41 NCO O Not used (open)

42 AVCC — Power supply terminal (+5 V) (for analog system)

43 AVRH I Reference voltage (+5 V) input terminal (for A/D converter)

44 AVRL I Reference voltage (0 V) input terminal (for A/D converter)

45 AVSS — Ground terminal (for analog system)

46 KEYIN0 I Key0 input terminal (A/D input )

47 KEYIN1 I Key1 input terminal (A/D input )

48 RCIN0 I Rotary remote commander key input terminal (A/D input)

49 DSTSEL I Destination setting terminal (A/D input) (fixed at “L”)

50 QUALITY I Noise level detection signal input at SEEK mode (A/D input)

51 FM AGC I FM AGC detection signal input from the FM/AM tuner unit (TUX201) (A/D input)

52 MPTH I

53 VSM I

54 VCC — Power supply terminal (+5 V)

55 AMPON O

56 NS MASK O Discharge control signal output for the noise detection circuit “H”: discharge

57 MTLOUT O METAL output terminal (METAL on at “L” output) Not used (open)

58 REEL I Rotation detect signal input terminal Not used (fixed at “L”)

59 POS0 I

60 POS1 I

61 POS2 I

62 POS3 I

63 VSS — Ground terminal

64 NCO I Not used (fixed at “L”)

65 FSW IN I Frequency count terminal from power control (IC302)

66 LMLOD O

67 CMON O Capstan/reel motor control signal output terminal “H”: motor on Not used (open)

68 TAPE ON O

69 FLASH W I Internal flash memory data write mode detection signal input terminal

70 I2CSIO I/O

71 I2CCKO O

72 RCIN1 I Rotary remote commander shift key input terminal

73 X1A O Sub system clock output terminal (32.768 kHz)

74 X0A I Sub system clock input terminal (32.768 kHz)

75 DAVN I

76 DISCON_IN I CD/MD on/off control signal input from the CD mechanism controller (IC5)

77 BUIN I

Tuner system power supply on/off control signal output terminal

“H” tuner power on Not used (open)

Multi-path detection signal input from the RDS decoder (IC201) (A/D input)

Not used (open)

FM and AM signal meter voltage detection input from the FM/AM tuner unit

(TUX201) (A/D input)

Standby on/off control signal output terminal

“L”: standby mode, “H”: amplifier on

Tape position (EJECT/FF/REW/REV/FWD mode) detect input from the tape

operation switch on the deck mechanism Not used this function (fixed at “L”)

POS0: “L”: EJECT mode, “H”:others mode

POS1: “L”: FF and FWD mode, “H”: others mode

POS2: “L”: REW mode,“H”: others mode

POS3: “L”: REV and EJECT mode, “H”: others mode

Loading motor control signal output terminal “H” active

(For the loading direction and forward side operation) Not used (open)

Tape system power supply on/off control signal output terminal “H”: tape on

Not used (open)

Two-way data I2C bus with the FM/AM tuner unit (TUX201), RDS decoder (IC201)

and electrical volume (IC301)

I2C bus clock signal output to the FM/AM tuner unit (TUX201), RDS decoder

(IC201) and electrical volume (IC301)

Data transmit completed detection signal input from the RDS decoder (IC201)

“L” active Not used (open)

Battery detection signal input from the SONY bus interface (IC601) and battery detect

circuit “L” is input at low voltage

22

Pin No. Pin Name I/O Pin Description

78 DSPRADY I

79 KEYACK I

80 ADON O

81 ACCIN I Accessory detection signal input terminal “L”: Accessory on

82 FLASH ON O

83 PWON O Main system power supply on/off control signal output terminal “H”: power on

84 TESTIN I Setting terminal for the test mode “L”: test mode, Normally: fixed at “H”

85 RAMBU I

86 HSTX I Hardware standby input terminal “L” hardware standby mode Reset signal input inset

87 MD2 I Setting terminal for the CPU operational mode (fixed at “L” in this set)

88 MD1 I Setting terminal for the CPU operational mode (fixed at “H” in this set)

89 MD0 I Setting terminal for the CPU operational mode (fixed at “H” in this set)

90 RSTX I

91 VSS — Ground terminal

92 X0 I Main system clock input terminal (3.68 MHz)

93 X1 O Main system clock output terminal (3.68 MHz)

94 VCC — Power supply terminal (+5 V)

95 ILLIN I

96 TELATT I

97 EMPH I Emphasis control signal input from the CD Mechanism controller (IC5)

98 F CH O Frequency changing terminal from the power control (IC302) “H”: frequency change

99 – 102 NCO O Not used (open)

103 4V SEL I

104 COL SEL I

105 AMPATT O

106 BOOT O Serial data output to the liquid crystal display drive controller (IC701)

107 DSPGAIN O Not used (open)

108 NCO O Not used (open)

109 MODELSEL0 I

110 DSPON O Power supply on/off control signal output for the CXD2726Q (IC805) “H”: DSP on

111 MODELSEL1 I

112 BAND I Not used (fixed at “L”)

113 TUNON O

114 DOORSW I Not used (fixed at “L”)

115 REIN1 I

Transfer enable signal input from the CXD2726Q (IC805)

“L”: transfer prohibition, “H”: transfer permission

Input of acknowledge signal for the key entry Acknowledge signal is input to

accept function and eject keys in the power off status On at input of “H”

A/D converter power control signal output terminal

When the KEYACK (pin ul) that controls reference voltage power for key A/D

conversion input is active, “L” is output from this terminal to enable the input

Power on/off control signal output of the illumination LED and liquid crystal display

driver (IC901) “H”: power on

Internal RAM reset detection signal input from the RN5VD33AA (IC504)

Input terminal to check that RAM data are not destroyed due to low voltage

This checking is made within 100 msec after reset

System reset signal input from the reset signal generator (IC503) and reset swich (S101)

“L”: reset “L” is input for several 100 msec after power on, then it changes to “H”

Auto dimmer control illumination line detection signal input terminal

“L” is input at dimmer detection

Telephone detection signaal input terminal At input of “H”, the signal is attenuated

by –20 dB

Input terminal of whether line driver is mounted or not is detected

“L”: line driver is not mounted, “H”: line driver is mounted

Setting terminal for the illumination color

“L”: 2 color, “H”: 1 (red) color

Power amplifier muting on/off control signal output terminal “H”: muting on

Not used (open)

Setting terminal for the internal mechanism tape or CD/MD

“L”: tape, “H”: CD/MD (fixed at “H” in this set)

Setting terminal for the internal mechanism CD or MD

“L”: CD, “H”: MD (fixed at “H” in this set)

Tuner system power supply on/off control signal output terminal

“H”: tuner power on

Dial pulse input of the rotary encoder (RE901) (A phase input)

(for VOLUME/B ASS/TREBLE/B ALANCE/F ADER control)

23

Pin No. Pin Name I/O Pin Description

116 REIN0 I

117 NOSESW I

118 DOORIND O

119 VSS — Ground terminal

120 DOLBY O Dolby control terminal “H”: dolby on Not used (open)

Dial pulse input of the rotary encoder (RE901) (B phase input)

(for VOLUME/B ASS/TREBLE/BALANCE/FADER control)

Front panel block remove/attach detection signal input from the nose detection swich

(S102) “L”: front panel is attached

LED drive signal output of the CD disc slot illumination and Z indicator (LED771 –

773, LSW771) “H”: LED on “H”is output to turn on LED when front panel is opened

24

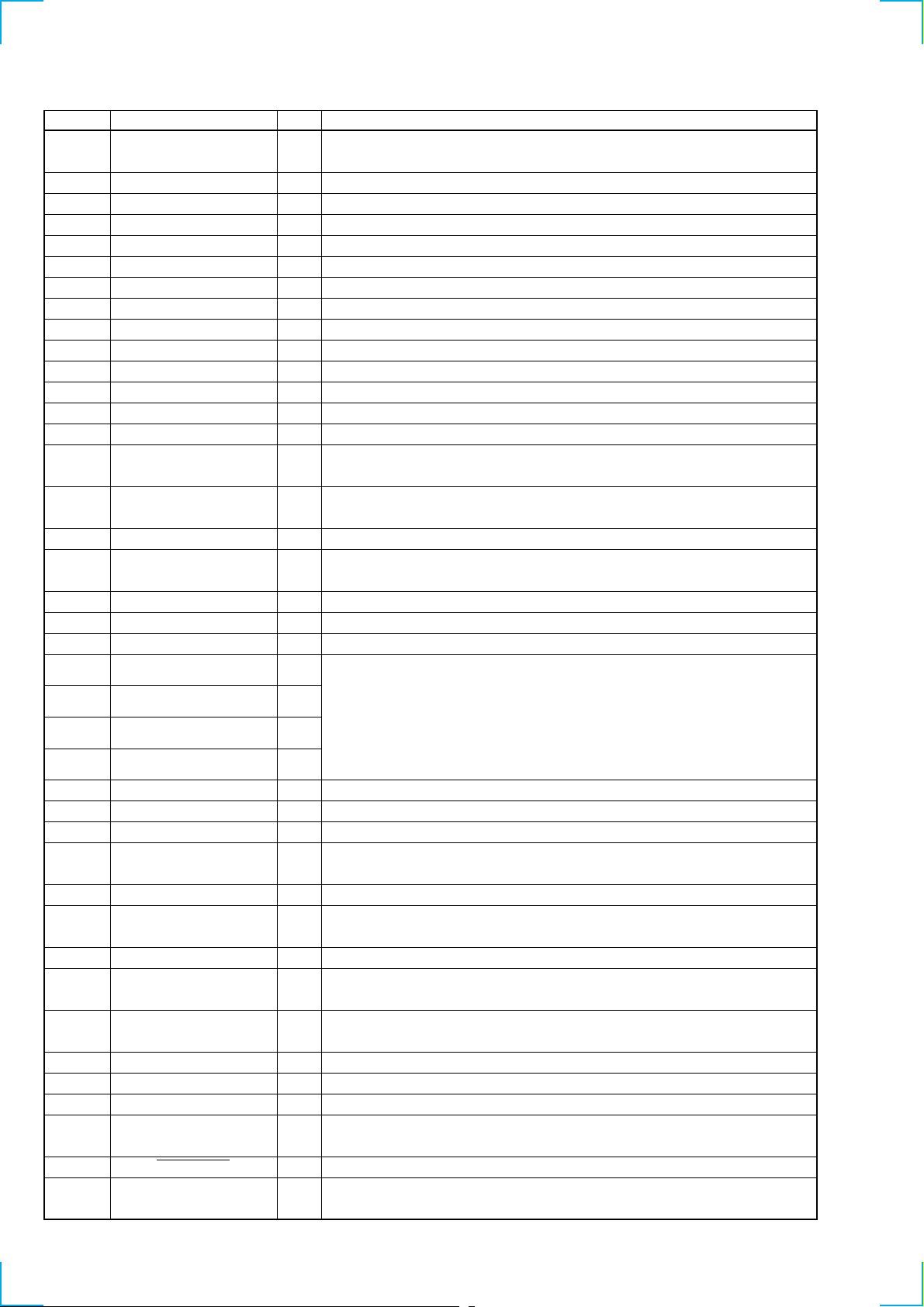

• IC805 CXD2726Q-4 (DIGITAL SIGNAL PROCESSOR, DIGITAL FILTER, D/A CONVERTER) (DSO BOARD)

Pin No. Pin Name I/O Pin Description

1 DGND — Ground terminal (digital system)

2 – 15 T.P I Input terminal for the test (fixed at “L”)

16 – 21 TST0 – TST5 I Input terminal for the test (fixed at “L”)

22 – 24 JPE1 – JPE3 I External condition jump terminal “H”: condition jump (fixed at “L”)

25 DVDD — Power supply terminal (+3.3 V) (digital system)

26 DA1GND — Ground terminal (for D/A converter 1) (analog system)

27 DA1LO O

28 DA1VDD — Power supply terminal (+3.3 V) (for D/A converter 1) (analog system)

29 DA1RO O

30 DA1VDD — Power supply terminal (+3.3 V) (for D/A converter 1) (analog system)

31 DA1GND — Ground terminal (for D/A converter 1) (analog system)

32 ADLVDD — Power supply terminal (+3.3 V) (for L-ch side A/D converter) (analog system)

33 ADLGND — Ground terminal (for L-ch side A/D converter) (analog system)

34 ADLREF O Connected to the bus control for A/D converter (for L-ch side)

35 ADLIN I

36 DA2GND — Ground terminal (for D/A converter 2) (analog system)

37 DA2VDD — Power supply terminal (+3.3 V) (for D/A converter 2) (analog system)

38 DA2LO O D/A converter 2 (L-ch side) output terminal (Not used.)

39 MCKVDD — Power supply terminal (+3.3 V) (for master clock) (analog system)

40 MCKO O System clock output terminal (16.9344 MHz)

41 MCKI I System clock input terminal (16.9344 MHz)

42 MCKGND — Ground terminal (for master clock) (analog system)

43 DA2RO O

44 DA2VDD — Power supply terminal (+3.3 V) (for D/A converter 2) (analog system)

45 DA2GND — Ground terminal (for D/A converter 2) (analog system)

46 ADRIN I

47 ADRREF O Connected to the bus control for A/D converter (for R-ch side)

48 ADRGND — Ground terminal (for R-ch side A/D converter) (analog system)

49 ADRVDD — Power supply terminal (+3.3 V) (for R-ch side A/D converter) (analog system)

50 DA3GND — Ground terminal (for D/A converter 3) (analog system)

51 DA3VDD — Power supply terminal (+3.3 V) (for D/A converter 3) (analog system)

52 DA3LO O

53 DA3GND — Power supply terminal (+3.3 V) (for D/A converter 3) (analog system)

54 DA3RO O

55 DA3GND — Ground terminal (for D/A converter 3) (analog system)

56 DGND — Ground terminal (digital system)

57 SYSRST I System reset signal input from the master controller (IC502) “L”: reset

58 BFOT O Master clock signal output terminal

59 SCK I

60 REDY O

61 TRDT O

62 XLAT I Serial data latch pulse input from the master controller (IC502)

D/A converter 1 (L-ch side) output terminal

Analog signal output for front side (L-ch side) output in this set

D/A converter 1 (R-ch side) output terminal

Analog signal output for rear side (L-ch side) output in this set

A/D converter (L-ch side) analog input terminal

Tuner and bus audio input signal (L-ch side) in this set

D/A converter 2 (R-ch side) output terminal

Analog signal output for sub woofer output in this set

A/D converter (R-ch side) analog input terminal

Tuner and bus audio input signal (R-ch side) in this set

D/A converter 3 (L-ch side) output terminal

Analog signal output for rear side (R-ch side) output in this set

D/A converter 3 (R-ch side) output terminal

Analog signal output for front side (R-ch side) output in this set

Serial data transfer clock signal input from the master controller (IC502) and liquid

crystal display drive controller (IC701)

Transfer enable signal output to the master controller (IC502)

“L”: transfer prohibition

Serial data output to the master controller (IC502) and liquid crystal display drive

controller (IC701)

Pin No. Pin Name I/O Pin Description

63 RVDT I Serial data input from the master controller (IC502)

64 24/23BIT I

65 DVDD — Power supply terminal (+3.3 V) (digital system)

66 DVSS — Ground terminal (digital system)

67 – 69 SO1 – SO3 O Serial data output terminal (Not used.)

70 SOUT O Serial data output terminal (Not used.)

71 SI1 I Serial data input terminal

72, 73 SI2, SI3 I Serial data input terminal Not used (fixed at “L”)

74 SIN I Serial data input terminal Not used (fixed at “L”)

75 BCK I Bit clock signal (2.8224 MHz) input terminal

76 LRCK I L/R sampling clock signal (44.1 kHz) input terminal

77 MST/SLV I

78 DVDD — Power supply terminal (+3.3 V) (digital system)

79 PLLGND — Ground terminal (PLL system)

80 PLLENA I PLL enable signal input terminal Normally: fixed at “L”

81 22 MHz O PLL clock signal output terminal (22.5792 MHz) (Not used.)

82 PLLCNT I

83 PLLVDD — Power supply terminal (+3.3 V) (PLL system)

84 DGND — Ground terminal (digital system)

85 – 94 T.P I Input terminal for the test Normally: fixed at “L”

95 DVDD — Power supply terminal (+3.3 V) (digital system)

96 DRAMGND — Ground terminal (for D-RAM)

97 – 99 T.P I Input terminal for the test Normally: fixed at “L”

100 DRAMVDD — Power supply terminal (+3.3 V) (for D-RAM)

Serial data 24/32 bit slot selection signal input terminal

“L”: 24 bit slot, “H”: 32 bit slot (validity at slave mode) (fixed at “L” in this set)

Bit clock (BCK) and L/R sampling clock (LRCK) signal master/slave mode selection

signal input from the master controller (IC502) “L”: master mode, “H”: slave mode

PLL clock output control signal input from the master controller (IC502)

At “L” is input: fixed at “L” is PLCLK (pin ia)

At “H” is input: PLL clock signal output from the PLCLK (pin ia)

25 25

CDX-C8050X

3-2. BLOCK DIAGRAM — CD SECTION —

OPTICAL PICKUP

KSS-720A

A

C

B

D

E

F

PD

LD

FOCUS

COIL

TRACKING

COIL

I-V

CONV.

M902

SLED

MOTOR

M901

SPINDLE

MOTOR

M903

LOADING

MOTOR

A

5

C

7

B

6

D

8

FOCUS

ERROR

E

11

TRACKING

F

ERROR

10

PD

4

LD

LD

DRIVE

Q101

TRACKING/FOCUS COIL DRIVE

SLED/SPINDLE/LOADING MOTOR DRIVE

10

11

12

13

AMP

LD

3

IC7

FOCUS

COIL

DRIVE

TRACKING

8

COIL

DRIVE

9

SLED

6

MOTOR

7

DRIVE

SPINDLE

MOTOR

DRIVE

LOADING

5

MOTOR

4

DRIVE

RF AMP, LD APC,

ERROR AMP

IC1

22

21

25

24

31

32

18

1

2

MUTE 1

34

MUTE 2

35

RFO RFAC

RF

EQ

FE

TE

LD ON

HOLD SW

AGC CONT

16

14

13

22

21

20

A MUT

EMPH

MDON

CDON

BUS SI

BUS ON

RESET

BU IN

BUS SO

BATT

CHECK

Q352

19

16

17

18

51

52

61

30

60

53

MDON

CDON

ATT

TO DISPLAY

5

TO TUNER

SECTION

(Page 27)

SECTION

S101

(RESET)

4

(Page 28)

10 3

13 2

12

9

8

11

Q601

SYSTEM CONTROL

IC502 (1/3)

ATT

5

EMPH

97

UNI CKO

19

UNI SI

17

UNI SO

18

BUS ON

14

SYS RST

6

BU IN

77

SIRCS

RSTX

90

HSTX

86

IC503

1 2

RESET

BATT (H)

CHECK

Q604

BUS INTERFACE

IC601

BATT (L)

CHECK

RESET

BUS ON

CONT

DATA

CLK

• Signal path

:CD

IR

RECEIVE

IC951

24

BU 5V

Q605

BATT

BATT

Q603

1

8

6

6

4

3

5

2

4

1

7

CN601

BUS

CONTROL IN

BATT

DIGITAL SERVO,

DIGITAL SIGNAL PROCESSOR

IC501

XTAI

86

BCK

81

LRCK

77

SUB

CODE

PCMD

LOCK

SQSO

SQCK

SCOR

XRST

DATA

XLAT

SCLK

CLOK

SENS

MD2

GFS

FOK

79

34

6

7

24

73

11

13

14

17

15

16

22

32

RFDC

FE

TE

SE

FFDR

FRDR

TFDR

TRDR

SFDR

SRDR

MDP

EFM

DEM

SERVO

CTL

61

54

50

52

51

42

43

40

41

38

39

35

D/A

I/F

DIGITAL

CLV

PROCESS

1

TO DISPLAY

SECTION

16M

BCK

LRCK

DATA

SW3

(LIMIT)

SW1

(DISC IN)

SW4

(DOWN)

SW2

(SELF)

(Page

(KEY BOARD)

X1

10MHz

CD SYSTEM CONTROL

28)

LOCK

46

OPEN

6

SI2

49

SCK2

48

SCOR

64

MD2

71

CD RST

21

CD DATA

67

CD XLAT

68

SCLK

45

CD CKO

65

SENS

57

GFS

55

FOK

54

31

XIN

32

XOUT

SSTP

11

IN SW

62

D SW

10

SELF SW

63

LM EJ

69

LM LOD

66

SLED –

40

DRIVE OE

70

LD ON

20

HOLD

22

AGC CONT

23

IC5

BUS CLK

SRST

2

TO DISPLAY

SECTION

(Page 28)

04

BUS CLK

BUS SI

BUS ON

BUS CHECK

UNI SO

LINK OFF

Q602

2626

3-3. BLOCK DIAGRAM — TUNER SECTION —

TUNER UNIT

TUX201

ANT1

(ANTENNA)

04

AM ANT MPX

1 10

2

AM IF

AMDETFM ANT

SW SHIFT SW SHIFT

S METER VSM

SDA IIC

SCL IIC

FM AGC

SDA EEPROM

SCL EEPROM

19

8

7

14

12

13

4

17

18

Q202 Q205

MUTE

CONTROL

Q206,207

TU8V

3

TO DISPLAY

SECTION

(Page 28)

REG

Q201

TU5V

ADL

CDX-C8050X

CN302

–1

L

BUS AUDIO IN

CN301

CN101

–2

–5

–6

–3

–4

–1

–2

1

9

2

10

4

12

3

11

13

14

7

15

5

6

16

R

L

R

L

R

L

R

FL+

FL–

RL+

RL–

FR+

FR–

RR+

RR–

TEL MUTE

ILL

ACC

TEST

AMP REM

ANT REM

BATT

AUDIO OUT

FRONT

AUDIO OUT

REAR

SUB OUT

POWER

CONT.

BATT

L-CH LINE DRIVER

IC303

2 3

7 12

SUB LINE DRIVER

IC304

7 12

ATT

Q353

ACC

DET

Q112

POWER

CONT

Q107-109

POWER

CONT

Q203,204

MUTE

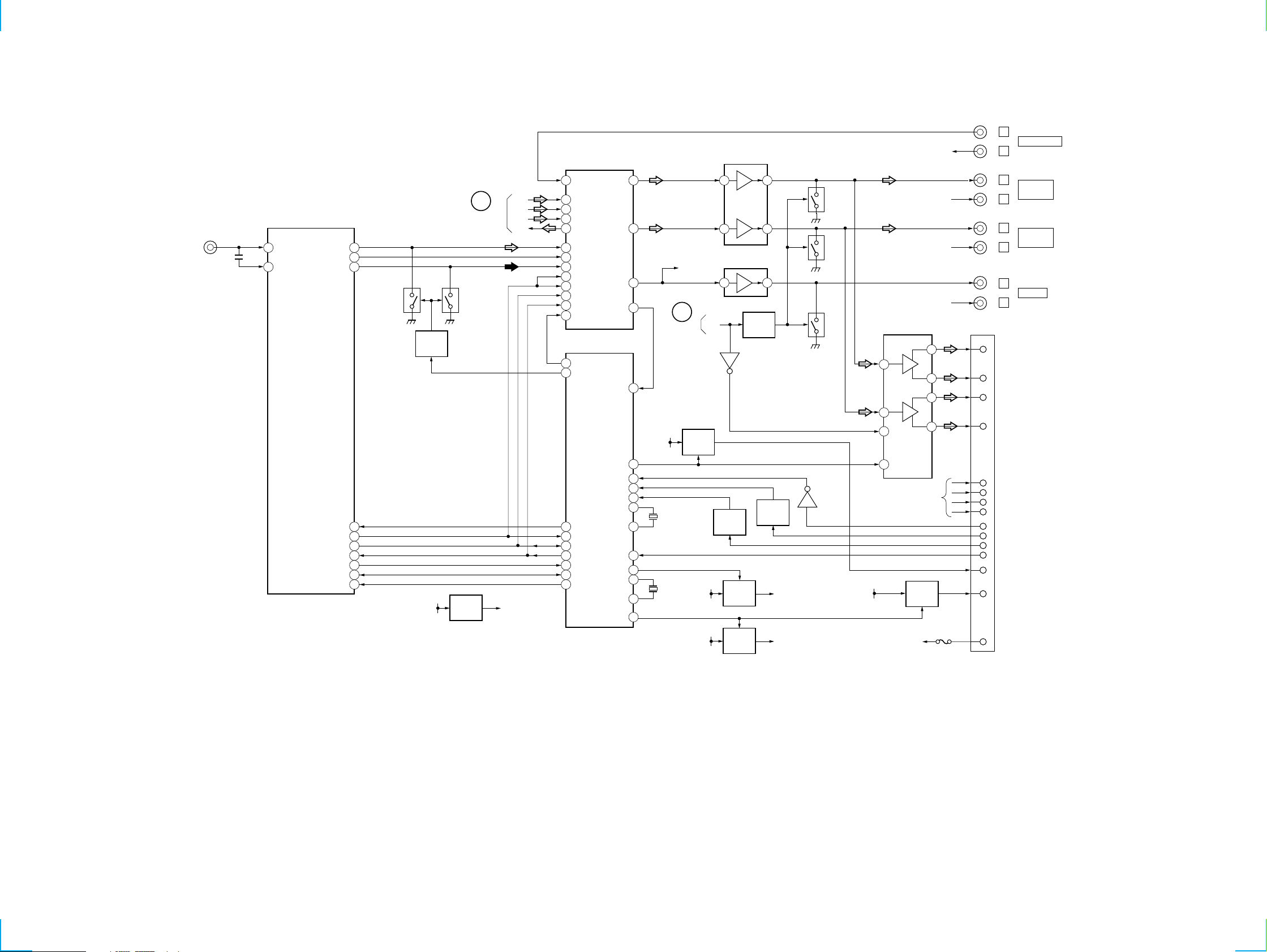

CONTROL

Q354, 355

ILL

DET

Q113

COM 8V

TU 8V

Q111

Q356

Q358

Q360

BATT

POWER AMP

12

11

22

MUTE

4

STBY

IC351

ELECTRONIC VOLUME

IC301

1 30

SEL OUT FL

FL

RL

SR

34

33

35

38

13

12

11

15

14

20

21

18

ACINLF

AC INLR

SWINR

ACOUTL

MPX

AM IF

AM

MP IV

S METER

SDA

SCL

EXTATT

OUT RL

OUTSWR

QUAL

29

R-CH

25

17

4

TO CD

SYSTEM CONTROL

IC502 (2/3)

31

VOL ATT

32

TU ATT

21

53

I2CSIO

70

I2CCKO

71

FM AGC

51

E2PSIO

10

E2PCKO

11

QUALITY

AMP ON

TEL ATT

ILL IN

ACC IN

XDA

TEST

PW ON

TU ON

XIA

50

55

96

95

81

73

74

84

83

92

XO

93

XI

113

SECTION

(Page 26)

BATT

X103

32.768kHz

X104

3.68MHz

Q363,365

COM8V

POWER

CONT.

Q364,366

BATT

R-CH

R-CH

R-CH

R-CH

5

3

9

7

R-CH

27 27

CDX-C8050X

3-4. BLOCK DIAGRAM — DISPLAY SECTION —

04

2

TO CD

SECTION

(Page 26)

LCD901

BUS SI

UNI SO

BUS CLK

BUS ON

BUS CHECK

LINK OFF

S RST

LCD+B

LCD DRIVER

IC901

DATA

DIMMER

86

Q903

REG

Q110

CLK

BUF

IC702

CE

100

76

99

98

BU5VBATT

SUB SYSTEM CONTROL

IC701

UNI SI

98 61

97

UNI SO

UNI SCK

101

BUS ON

38

BUS IN

49

NMI

82

LINK OFF

50

RES

81

LCD DATA

60

CLK

64

CEI

66

SP SI

SP SCK

XTAL

EXTAL

BOOT

SP LAT

ILL ON

+6V

63

85

86

57

33

52

X105

18.43MHz

BATT

REG

IC801,Q801

REG

Q802

IC802

REG

1 3

POWER

CONT.

Q703-705

BU 5V

BU 5V

J651

(REMOTE IN)

A 3.3V

DSP5V

D3.3V

LCD+B

AD ON

CONT.

Q702

KEY

ACTIVE

Q701

KEY IN

MATRIX

LED771-773

BU5V

AD ON

S102

(NOSE DET)

IC504

RAM

2 1

BACKUP

ENCODER

LED

DRIVE

Q771,772

RE901

ROTALY

SYSTEM CONTROL

115

RE IN1

116

REIN0

80

ADON

79

KEY ACK

72

RC IN1

48

RC IN0

46

KEY IN0

47

KEY IN1

106

BOOT

4

SP LATCH

82

FLASH ON

DOOR IND

118

NOSESW

117

RAMBU

85

IC502 (3/3)

DSP

DISC ON IN

CKO

RST

LAT

READY

MST

DSPPLL

BEEP

FSW IN

DSP ON

F CH

26

SO

25

SI

27

36

35

78

29

(Page 26)

28

15

65

110

98

76

1

TO CD

SECTION

BATT

Q101

DATA

LRCK

16M

BEEP

DRIVE

Q351

+6V

BCK

BUFFER

IC803

9 8

2 3

5 6

4

BZ101

POWER

CONT.

Q102,104

POWER

CONT.

Q406,407

AND

IC804

1

2

IC804

REG

Q402,403

63

RVDT

61

TRDT

59

SCK

57

SYS RST

62

XLAT

60

REDY

77

MST/SLV

71

SI1

76

LRCK

75

BCK

58

BFOT

82

PLL CNT

Q103,105,

VCC INP

2

ON/OFF

DRIVE

Q106

1

OUT

RT

7

DSP

IC805

DAILO

DA3RO

DA1RO

DA3LO

DA2RO

ADL IN

ADR IN

MCK0

MCK1

4

DC/DC

CONV.CONT.

IC302

CD5V

MD6V

IC807

+6V

5

TO CD

FL

RL

SR

ADL

3

TO TUNER

SECTION

(Page 27)

27

R-CH

54

29

52

43

35

46

40

41

R-CH

R-CH

X801

16.9MHz

MD ON

CD ON

IC807

IC809

SECTION

(Page 26)

2828

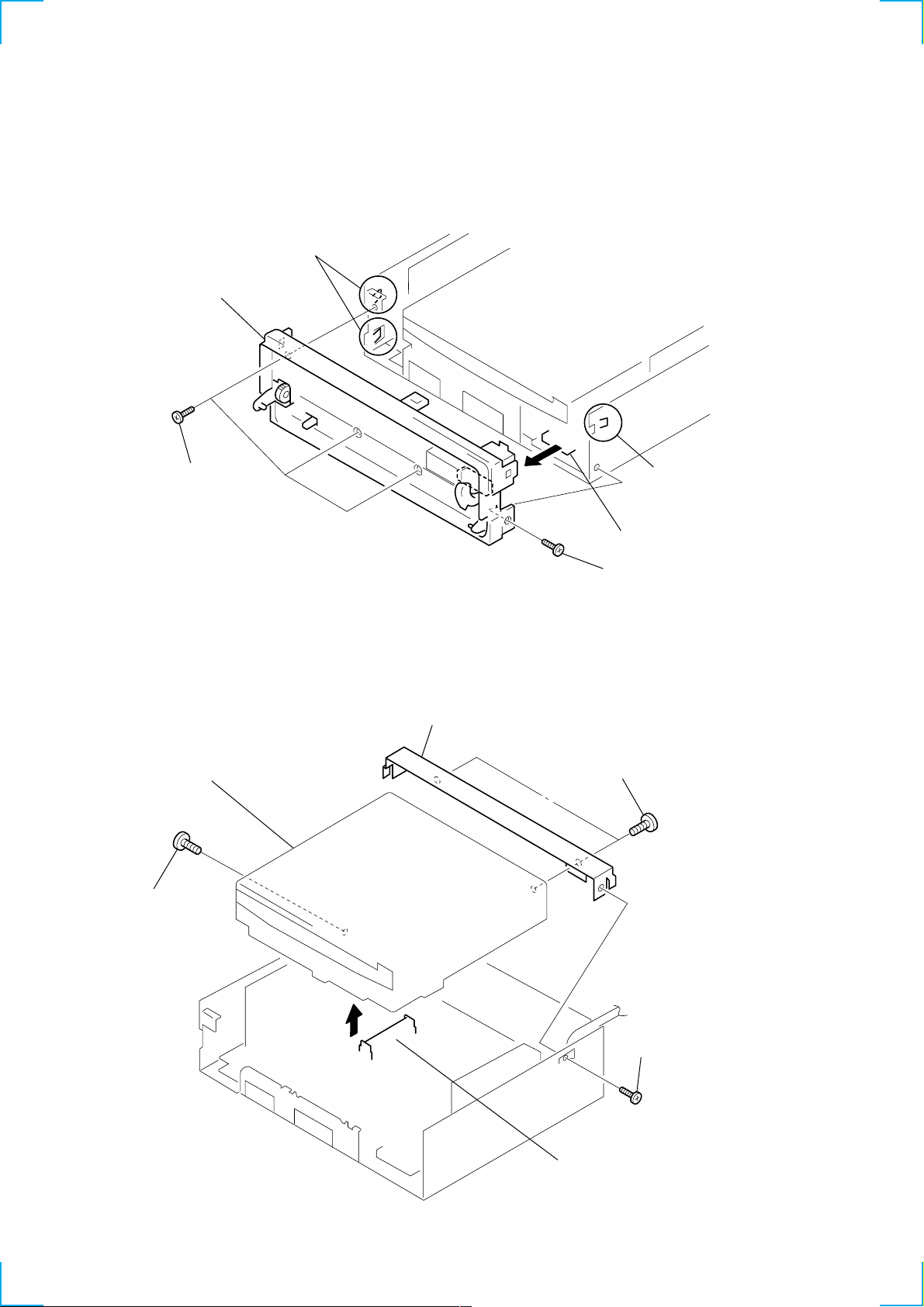

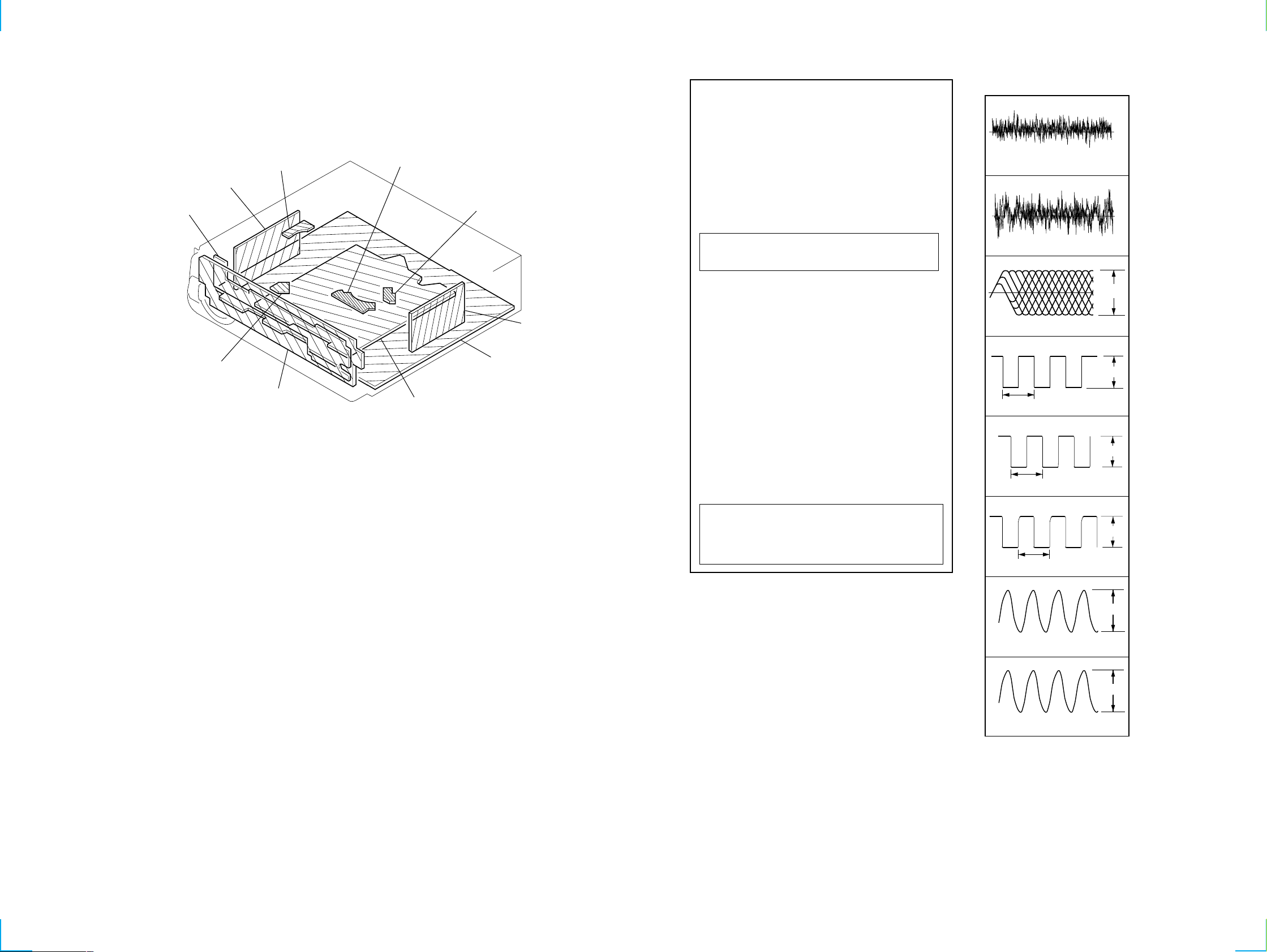

3-5. CIRCUIT BOARDS LOCATION

DISC IN SW board

DSO board

SUB (CD) board

LOAD SW board

KEY board

SUB board

SERVO board

LIMIT SW board

MAIN board

tuner unit

(TUX201)

THIS NOTE IS COMMON FOR PRINTED WIRING

BOARDS AND SCHEMATIC DIAGRAMS.

(In addition to this, the necessary note is

printed in each block.)

for schematic diagram:

• All capacitors are in µF unless otherwise noted. pF: µµF

50 WV or less are not indicated except for electrolytics

and tantalums.

• All resistors are in Ω and 1/

specified.

• % : indicates tolerance.

f

•

• C : panel designation.

Note: The components identified by mark 0 or dotted line

• U : B+ Line.

• Power voltage is dc 14.4V and fed with regulated dc power

• Voltages are tak en with a V OM (Input impedance 10 MΩ).

• Wavefor ms are taken with a oscilloscope.

• Circled numbers refer to waveforms.

• Signal path.

for printed wiring boards:

• X : parts extracted from the component side.

• Y : parts extracted from the conductor side.

•

• b : Pattern from the side which enables seeing.

Caution:

Pattern face side: Parts on the pattern face side seen from the

(Side B) pattern face are indicated.

Parts face side: Parts on the parts face side seen from the

(Side A) parts face are indicated.

: internal component.

with mark 0 are critical for safety.

Replace only with part number specified.

supply from ACC and BATT cords.

Voltage variations may be noted due to normal produc-

tion tolerances.

Voltage variations may be noted due to normal produc-

tion tolerances.

F : FM

f : AM

J : CD

a

: Through hole.

(The other layer’s patterns are not indicated.)

4

W or less unless otherwise

• Waveforms (MODE:PLAY)

1

0V

Approx. 200mVp-p

qd

(TE)

IC1

2

0V

Approx. 620mVp-p

qf

(FE)

IC1

3

1.2Vp-p

qh

(RFO)

IC1

4

5Vp-p

22.7µsec

IC501

(LRCK)

uj

5

5Vp-p

474nsec

IC501

(PCMO)

ul

6

5.7Vp-p

474nsec

ia

(BCK)

IC501

7

8

16.89MHz

IC501

IC5

ih

10MHz

(X IN)

ea

3.8Vp-p

(XTAI)

2Vp-p

29 29

Loading...

Loading...