Page 1

C509-L

8-Bit CMOS Microcontroller

User's Manual 10.97

http://www.siemens.de/

Semiconductor/

Page 2

C509-L Data Sheet

Revision History : 10.97

Previous Releases : 06.96 (Original Version)

Page (new

version)

1-6

1-11

3-1

3-12

4-12

6-6

6-28

6-78

6-85

6-88

6-93

7-13

7-16

11-1

11-3, 11-4

11-1, 11-5,

11-7

11-7 to11-9

Chapter 12

Page (prev.

version)

1-6

1-11

3-1

3-12

4-12

6-6

6-28

6-78

6-85

6-88

6-93

7-13

7-16

11-1

11-3

11-1, 11-5,

11-7

11-6 to11-8

Chapter 12

Subjects (changes since last revision)

Duty cycle for XTAL2 corrected

RESET : correction in text “for the duration of two machine cycles“

Correction in text : XRAM is internal

1st paragraph: sentence “Bit Swap is ...” added;

Table 3-2: Text in right column corrected

Figure 3-7; corrected and improved

Last paragraph og 4.4.2 : last sentence deleted

Correction in figure 6-4 and text : “Delay = 1 state“

Correction in text 2nd paragraph : “consists of three ...“

Abbreviations below table 6-10 added

Name of bit T1P2 corrected to T2P0

Formula for mode 1,3 baud rate corrected; last sentence added

Formula for mode A,B baud rate corrected

Several references in the text corrected from IRCON to IRCON0

Description of ICR and ICS added

V

modified

IL2

Improved and extended ICC specification

V

min. changed from 5V - 15% to 5V - 5%

CC

AC characteristics : 16 MHz clock oscillator duty cycle (DC) for

external clock changed to 0.45 to 0.55

Improved index; bold page numbers for main definition reference

Edition 10.97

Published by Siemens AG,

Bereich Halbleiter, MarketingKommunikation, Balanstraße 73,

81541 München

© Siemens AG 1997

All Rights Reserved.

Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for

applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

For questions on technology, delivery and prices please contact the Semiconductor Group Offices in Germany or

the Siemens Companies and Representatives worldwide (see address list).

Due to technical requirements components may contain dangerous substances. For information on the types in

question please contact your nearest Siemens Office, Semiconductor Group.

Siemens AG is an approved CECC manufacturer.

Packing

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales

office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall haveto invoice

you for any costs incurred.

Components used in life-support devices or systems must be expressly authorized for such purpose!

Critical components

systems

1 A critical component is a component used in a life-support device or system whose failure can reasonably be

2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or

2

with the express written approval of the Semiconductor Group of Siemens AG.

expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that

device or system.

maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.

1

of the Semiconductor Group of Siemens AG, may only be used in life-support devices or

Page 3

General Information

C509-L

Table of Contents Page

1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

1.1 Pin Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

1.2 Pin Definitions and Functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

2 Fundamental Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

2.1 CPU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

2.2 CPU Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5

3 Memory Organization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

3.1 Program Memory, “Code Space” . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

3.2 Data Memory, “Data Space”. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

3.3 General Purpose Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

3.4 Program and Data Memory Organization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

3.4.1 Interface of External FLASH/ROM/EPROM and External SRAM Memory. . . . . . . . 3-4

3.4.2 Normal Mode Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5

3.4.3 XRAM Mode Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6

3.4.4 Bootstrap Mode Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

3.4.5 Programming Mode Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8

3.4.6 Special Function Register SYSCON1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-10

3.4.7 Operating Mode (Chipmode) Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-12

3.4.7.1 Special Software Unlock Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-13

3.4.7.2 Control Signals of the Chipmodes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-14

3.4.7.3 Switching of the SWAP-Bit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-15

3.4.8 Watchdog Timer - Behaviour in the Different Operating Modes. . . . . . . . . . . . . . . 3-16

3.5 Special Function Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-17

4 External Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

4.1 Accessing External Memory. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

4.1.1 Role of P0 and P2 as Data/Address Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

4.1.2 Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

4.1.3 External Program Memory Access. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

4.1.4 PSEN

4.1.5 Overlapping External Data and Program Memory Spaces. . . . . . . . . . . . . . . . . . . . 4-2

4.1.6 ALE, Address Latch Enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-4

4.2 Enhanced Hooks Emulation Concept. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-5

4.3 Eight Datapointers for Faster External Bus Access . . . . . . . . . . . . . . . . . . . . . . . . . 4-6

4.3.1 The Importance of Additional Datapointers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-6

4.3.2 How the Eight Datapointers of the C509-L are Realized . . . . . . . . . . . . . . . . . . . . . 4-6

4.3.3 Advantages of Multiple Datapointers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-7

4.3.4 Application Example and Performance Analysis . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-7

4.4 XRAM Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-10

4.4.1 XRAM Access Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-10

4.4.2 Accesses to XRAM using the DPTR (16-bit Addressing Mode). . . . . . . . . . . . . . . 4-12

4.4.3 Accesses to XRAM using the Registers R0/R1 . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-12

4.4.4 Reset Operation of the XRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-16

4.4.5 Behaviour of Port0 and Port2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-16

, Program Store Enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

Semiconductor Group 1-1 1997-10-01

Page 4

General Information

C509-L

Table of Contents Page

5 Reset and System Clock Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

5.1 Reset Function and Circuitries . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

5.2 Hardware Reset Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

5.3 Fast Internal Reset after Power-On . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

5.4 Reset Output Pin (RO

5.5 Oscillator and Clock Circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6

5.6 System Clock Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-8

6 On-Chip Peripheral Components . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

6.1 Parallel I/O . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

6.1.1 Port Structures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

6.1.1.1 Port Structure Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

6.1.1.2 Quasi-Bidirectional Port Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5

6.1.1.2.1 Basic Port Circuitry of Port 1 to 6 and 9 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5

6.1.1.2.2 Port 0 Circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-8

6.1.1.2.3 Port 0 and Port 2 used as Address/Data Bus. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-9

6.1.1.3 Bidirectional (CMOS) Port Structure. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-10

6.1.1.3.1 Input Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-10

6.1.1.3.2 Output Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-11

6.1.1.3.3 Hardware Power Down Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-13

6.1.2 Alternate Functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-14

6.1.3 Port Handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-16

6.1.3.1 Port Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-16

6.1.3.2 Port Loading and Interfacing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-17

6.1.3.3 Read-Modify-Write Feature of Ports 1 to 6 and 9. . . . . . . . . . . . . . . . . . . . . . . . . . 6-17

6.2 Timer/Counter 0 and 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-19

6.2.1 Timer/Counter 0 / 1 Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-20

6.2.2 Mode 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-24

6.2.3 Mode 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-25

6.2.4 Mode 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-26

6.2.5 Mode 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-27

6.3 The Compare/Capture Unit (CCU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-28

6.3.1 Timer 2 Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-33

6.3.1.1 Timer 2 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-33

6.3.1.2 Timer 2 Operating Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-36

6.3.1.2.1 Gated Timer Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-37

6.3.1.2.2 Event Counter Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-37

6.3.1.2.3 Reload of Timer 2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-37

6.3.2 Operation of the Compare Timers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-39

6.3.2.1 Compare Timer and Compare Timer 1 Registers. . . . . . . . . . . . . . . . . . . . . . . . . . 6-39

6.3.2.2 Operating Modes of the Compare Timers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-42

6.3.3 Compare Functions of the CCU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-44

6.3.3.1 Compare Mode 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-45

6.3.3.2 Compare Mode 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-47

6.3.3.3 Compare Mode 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-48

6.3.4 Timer- and Compare-Register Configurations of the CCU. . . . . . . . . . . . . . . . . . . 6-49

) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6

Semiconductor Group 1-2 1997-10-01

Page 5

General Information

C509-L

Table of Contents Page

6.3.4.1 Timer 2 - Compare Function with Registers CRC, CC1 to CC3. . . . . . . . . . . . . . . 6-50

6.3.4.2 Timer 2 - Capture Function with Registers CRC, CC1 to CC4. . . . . . . . . . . . . . . . 6-53

6.3.4.3 Compare Function of Register CC4; “Concurrent Compare” . . . . . . . . . . . . . . . . . 6-55

6.3.4.4 Compare Function of Registers CM0 to CM7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-59

6.3.4.4.1 CMx Registers Assigned to the Compare Timer . . . . . . . . . . . . . . . . . . . . . . . . . . 6-60

6.3.4.4.2 CMx Registers Assigned to the Timer 2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-63

6.3.4.5 Timer 2 Operating in Compare Mode 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-64

6.3.4.6 Compare / Capture Operation with Compare Timer 1 . . . . . . . . . . . . . . . . . . . . . . 6-65

6.3.4.6.1 Compare Function of Registers CC10 to CC17 . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-66

6.3.4.6.2 Capture Function of Registers CC10 to CC17 . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-68

6.3.5 Modulation Range in Compare Mode 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-69

6.3.6 Using Interrupts in Combination with the Compare Function . . . . . . . . . . . . . . . . . 6-71

6.3.6.1 Some advantages in using compare interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-71

6.3.6.2 Interrupt Enable Bits of the Compare/Capture Unit . . . . . . . . . . . . . . . . . . . . . . . . 6-73

6.3.6.3 Interrupt Flags of the Compare/Capture Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-74

6.4 Arithmetic Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-75

6.4.1 MDU Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-75

6.4.2 Operation of the MDU. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-77

6.4.3 Multiplication/Division . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-78

6.4.4 Normalize and Shift . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-79

6.4.5 The Overflow Flag . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-80

6.4.6 The Error Flag. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-80

6.5 Serial Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-82

6.5.1 Serial Interface 0. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-82

6.5.1.1 Operating Modes of Serial Interface 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-82

6.5.1.2 Multiprocessor Communication Feature. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-83

6.5.1.3 Baud Rates of Serial Channel 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-85

6.5.2 Serial Interface 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-90

6.5.2.1 Operating Modes of Serial Interface 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-90

6.5.2.2 Multiprocessor Communication Feature. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-92

6.5.2.3 Baud Rates of Serial Channel 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-92

6.5.3 Detailed Description of the Operating Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-94

6.5.3.1 Mode 0, Synchronous Mode (Serial Interface 0) . . . . . . . . . . . . . . . . . . . . . . . . . . 6-94

6.5.3.2 Mode 1/Mode B, 8-Bit UART (Serial Interfaces 0 and 1) . . . . . . . . . . . . . . . . . . . . 6-97

6.5.3.3 Mode 2, 9-Bit UART (Serial Interface 0). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-100

6.5.3.4 Mode 3 / Mode A, 9-Bit UART (Serial Interfaces 0 and 1) . . . . . . . . . . . . . . . . . . 6-100

6.6 A/D Converter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-104

6.6.1 A/D Converter Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-104

6.6.2 A/D Converter Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-107

6.6.3 A/D Converter Clock Selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-111

6.6.4 A/D Conversion Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-112

6.6.5 Adjustment of the Sample Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-116

6.6.6 A/D Converter Calibration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-118

Semiconductor Group 1-3 1997-10-01

Page 6

General Information

C509-L

Table of Contents Page

7 Interrupt System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-1

7.1 Structure of the Interrupt System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-1

7.2 Interrupt Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-6

7.2.1 Interrupt Enable Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-6

7.2.2 Interrupt Priority Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-10

7.2.3 Interrupt Request Flags . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-11

7.3 Interrupt Priority Level Structure. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-17

7.4 How Interrupts are Handled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-19

7.5 External Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-21

7.6 Interrupt Response Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-22

8 Fail Save Mechanisms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-1

8.1 Programmable Watchdog Timer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-1

8.1.1 Input Clock Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-2

8.1.2 Watchdog Timer Control Flags. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-3

8.1.3 Starting the Watchdog Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-4

8.1.3.1 The First Possibility of Starting the Watchdog Timer . . . . . . . . . . . . . . . . . . . . . . . . 8-4

8.1.3.2 The Second Possibility of Starting the Watchdog Timer. . . . . . . . . . . . . . . . . . . . . . 8-4

8.1.4 Refreshing the Watchdog Timer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-5

8.1.5 Watchdog Reset and Watchdog Status Flag . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-5

8.2 Oscillator Watchdog . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-6

9 Power Saving Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-1

9.1 Hardware Enable for the Use of the Power Saving Modes . . . . . . . . . . . . . . . . . . . 9-2

9.2 Power Saving Mode Control Register PCON. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-3

9.3 Idle Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-4

9.4 Software Power Down Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-6

9.5 Slow Down Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-7

9.6 Hardware Power Down Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-8

9.7 Hardware Power Down Mode Reset Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-10

10 The Bootstrap Loader . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-1

10.1 General Functions of the Bootstrap Loader . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-1

10.2 Phase I: Check for Existing Custom Software in the External FLASH Memory . . 10-3

10.2.1 Custom Software Check by the Info Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-3

10.2.2 Checksum Calculation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-7

10.3 Phase II: Automatic Serial Synchronization with the Host. . . . . . . . . . . . . . . . . . . 10-8

10.3.1 Automatic Synchronization Procedure. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-9

10.3.2 Baud Rates for Correct Synchronization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-12

10.4 Phase III: Serial Communication with the Host . . . . . . . . . . . . . . . . . . . . . . . . . . 10-13

10.4.1 Block Transfer Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-13

10.4.1.1 Header Block Definition. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-15

10.4.1.2 Data and EOT Block Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-16

10.4.2 Operating Mode Selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-17

10.4.2.1 Selection of Operating Mode 0. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-19

10.4.2.2 Selection of Operating Mode 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-23

10.4.2.3 Selection of Operating Mode 2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-24

Semiconductor Group 1-4 1997-10-01

Page 7

General Information

C509-L

Table of Contents Page

10.4.2.4 Selection of Operating Mode 3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-27

10.5 Description of the Bootstrap Loader Subroutines. . . . . . . . . . . . . . . . . . . . . . . . . 10-29

11 Device Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-1

11.1 Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-1

11.2 DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-1

11.3 A/D Converter Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-5

11.4 AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-7

12 Index . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-1

Semiconductor Group 1-5 1997-10-01

Page 8

Introduction

C509-L

1Introduction

The C509-L is a high-end microcontroller in the Siemens SAB-C500 8-bit microcontroller family. lt

is based on the well-known industry standard 8051 architecture; a great number of enhancements

and new peripheral features extend its capabilities to meet the extensive requirements of new

applications. Further, the C509-L is a superset of the Siemens SAB 80C517/80C517A 8-bit

microcontroller thus offering an easy upgrade path for SAB 80C517/80C517A users.

The high performance of the C509-L microcontroller is achieved by the C500-Core with a maximum

operating frequency of 16 MHz internal (and external) CPU clock. While maintaining all the features

of the SAB 80C517A, the C509-L is expanded by one I/O port, in its compare/capture capabilities,

by A/D converter functions, by additional 1 KByte of on-chip RAM (now 3 KByte XRAM) and by an

additional user-selectable CMOS port structure. The C509-L is mounted in a P-MQFP-100-2

package.

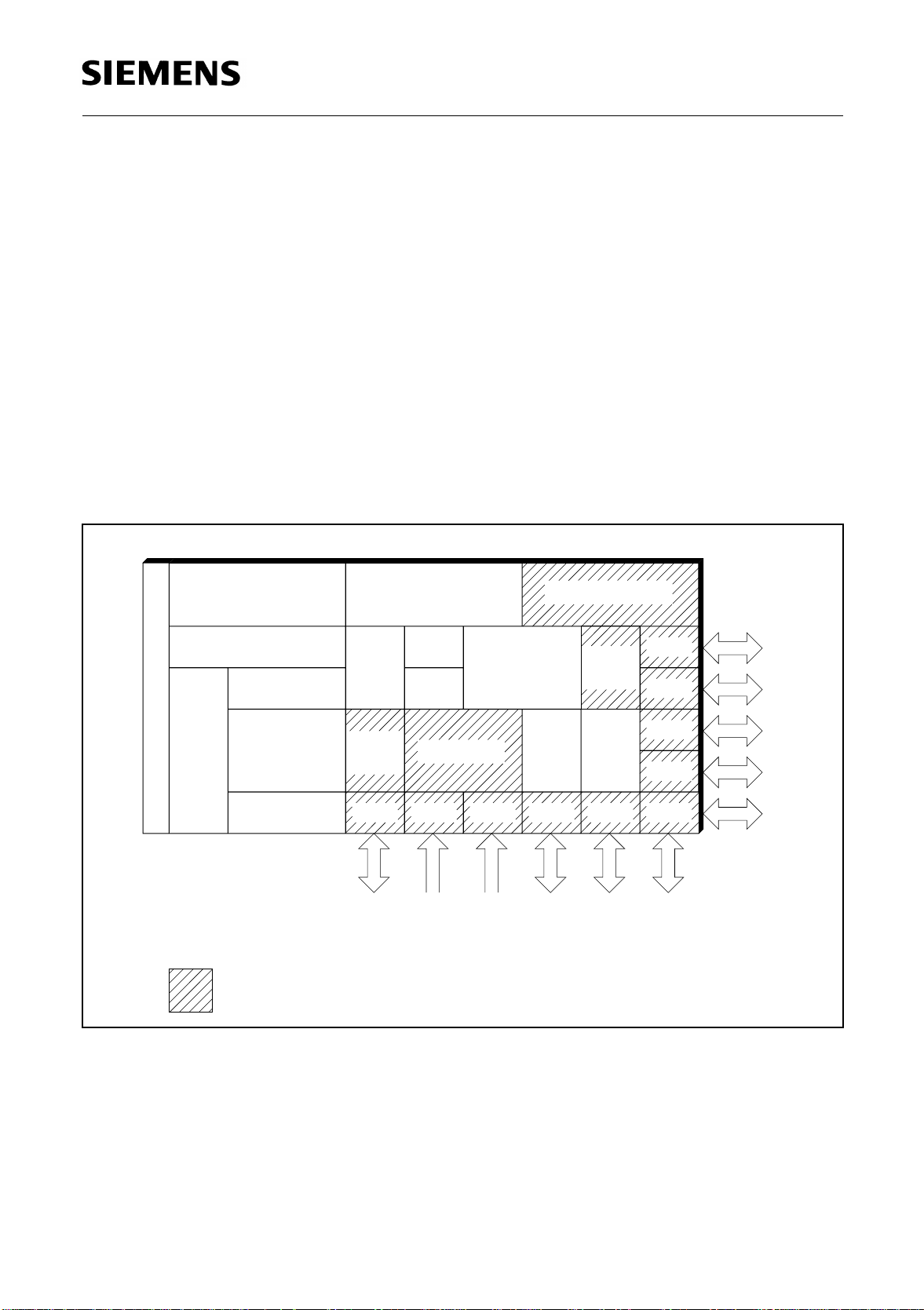

Figure 1-1 shows the different functional units of the C509-L and figure 1-2 shows the simplified

logic symbol of the C509-L.

C509

Watchdog

Oscillator

Watchdog

8-Bit UART

HW/SW

Power

Down

Modes

On-Chip Emulation Support Module

MDU

8-Bit USART

T 2

Comp.

Timer 1

Port 9 Port 8

I/O I/O I/O I/O

RAM

256 x 8

T 0

T 1

10-Bit ADC

analog/

digit.

input

CPU

C500-Core

(8-Dataptr)

Port 7

analog/

digit.

input

Boot ROM 512 x 8

XRAM

3 K x 8

CCU

Port 6

Comp.

Timer 1

Port 5

Port 4

Port 4

Port 4

Port 4

Port 4

I/O

I/O

I/O

I/O

I/O

Improved functionality in

comparison to the SAB 80C517A.

MCB02493

Figure 1-1

C509-L Functional Units

Semiconductor Group 1-1 1997-10-01

Page 9

Introduction

C509-L

Listed below is a summary of the main features of the C509-L:

l

Full upward compatibility with SAB 80C517/80C517A

l

256 byte on-chip RAM

l

3K byte of on-chip XRAM

l

256 directly addressable bits

l

375 ns instruction cycle at 16-MHz oscillator frequency

l

64 of 111 instructions are executed in one instruction cycle

l

External program and data memory expandable up to 64 Kbyte each

l

On-chip emulation support logic (Enhanced Hooks Technology

l

10-bit A/D converter

– 15 multiplexed inputs

– Built-in self calibration

l

Two 16-bit timers/counters (8051 compatible)

l

Three 16-bit timers/counters (can be used in combination with the compare/capture unit)

l

Powerful compare/capture unit (CCU) with up to 29 high-speed or PWM output channels or 13

capture inputs

l

Arithmetic unit for division, multiplication, shift and normalize operations

l

Eight datapointers instead of one for indirect addressing of program and external data memory

l

Extended watchdog facilities

– 15-bit programmable watchdog timer

– Oscillator watchdog

l

Ten I/O ports

– Eight bidirectional 8-bit I/O ports with selectable port structure

quasi-bidirectional port structure (8051 compatible)

bidirectional port structure with CMOS voltage levels

– One 8-bit and one 7-bit input port for analog and digital input signals

l

Two full-duplex serial interfaces with own baud rate generators

l

Four priority level interrupt systems, 19 interrupt vectors

l

Three power saving modes

– Slow-down mode

– Idle mode

– Power-down mode

l

Siemens high-performance ACMOS technology

l

M-QFP-100 rectangular quad flat package

l

Temperature Ranges : SAB-C509-L

SAF-C509-L

= 0 to 70 ° C

T

A

= -40 to 85 ° C

T

A

TM

)

Semiconductor Group 1-2 1997-10-01

Page 10

Introduction

C509-L

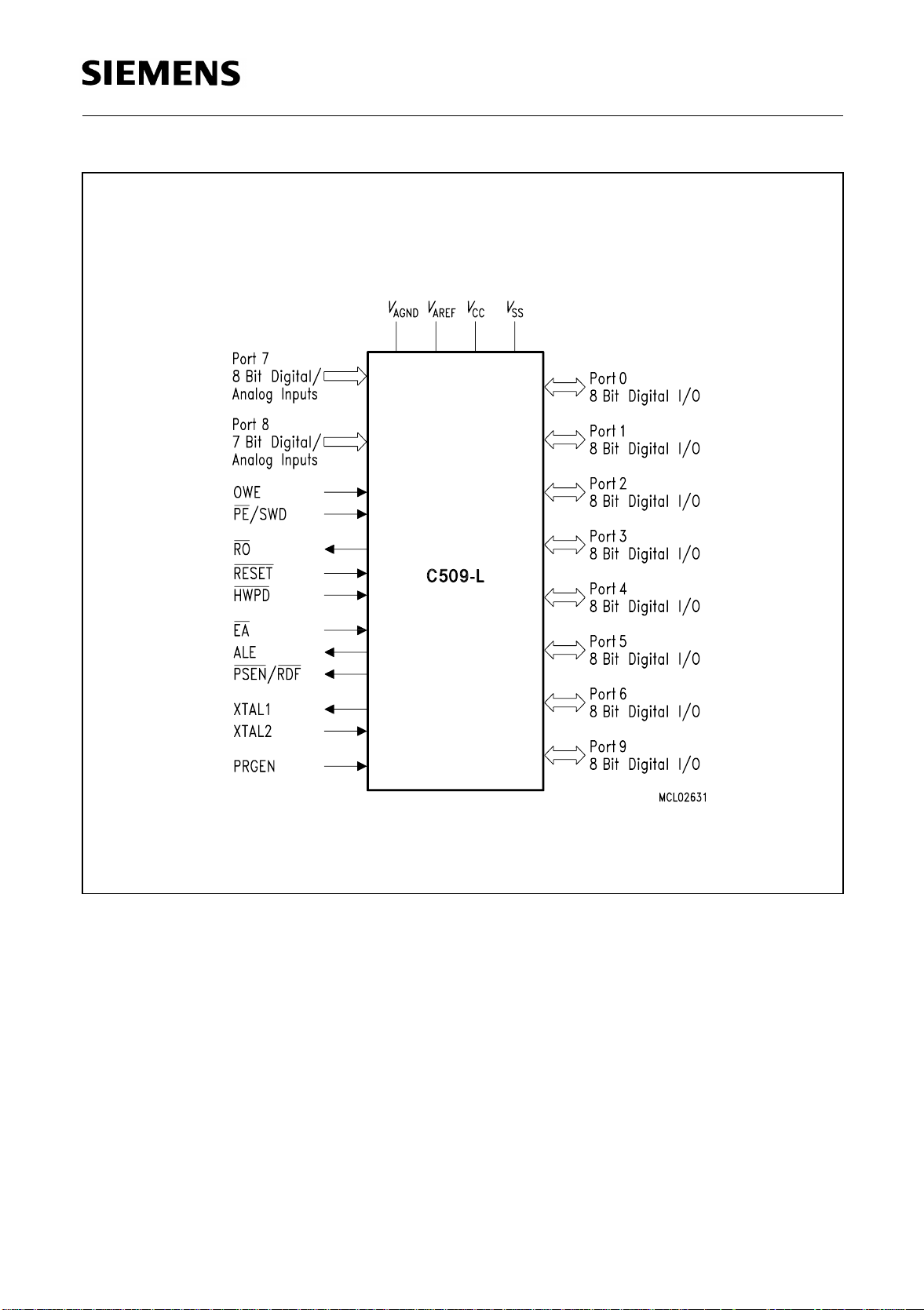

Figure 1-2

C509-L Logic Symbol

Semiconductor Group 1-3 1997-10-01

Page 11

Introduction

1.1 Pin Configuration

This section describes the pin configuration of the C509-L in the P-MQFP-100-2 package.

C509-L

Figure 1-3

C509-L Pin Configuration (P-MQFP-100-2, top view)

Semiconductor Group 1-4 1997-10-01

Page 12

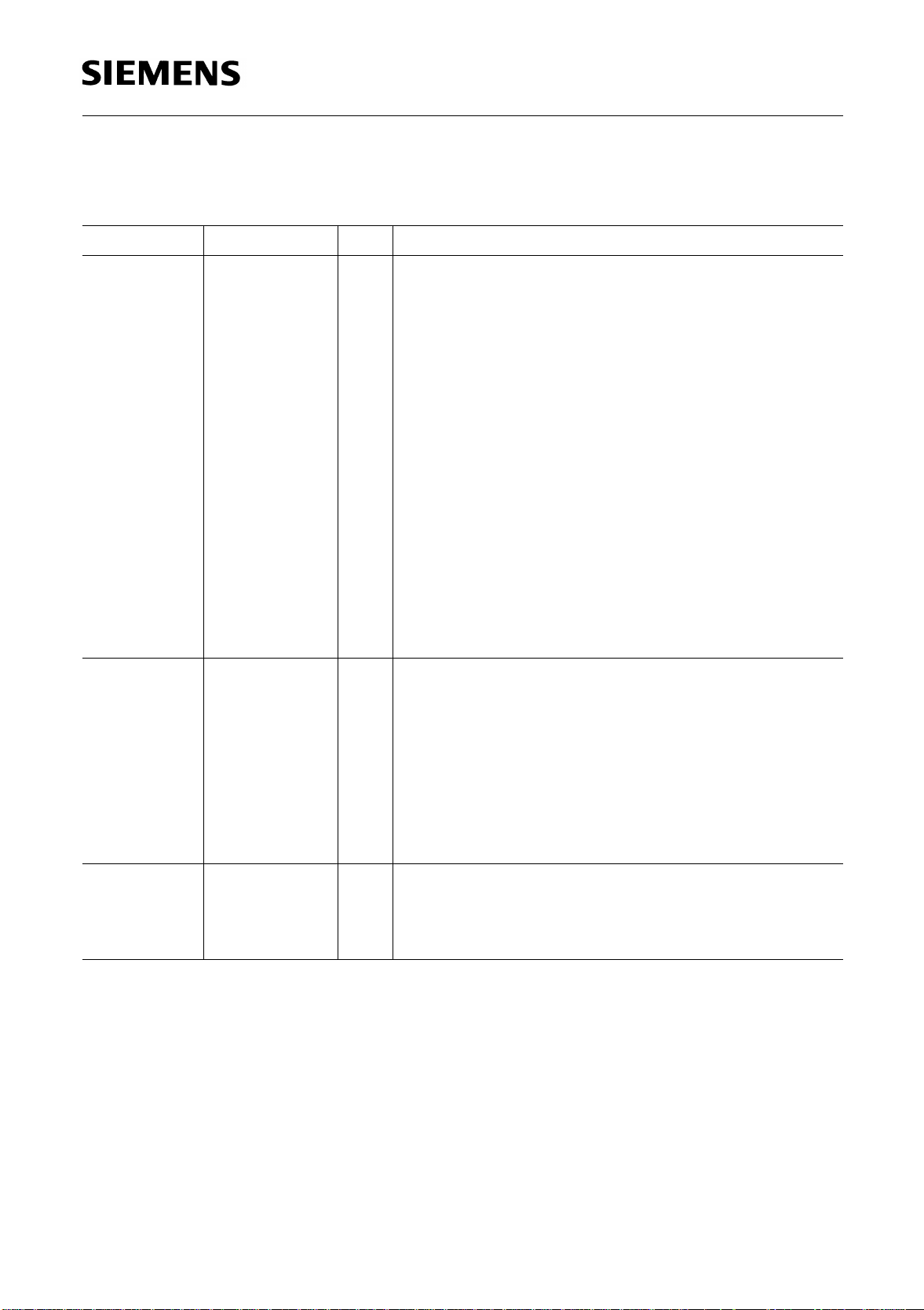

1.2 Pin Definitions and Functions

This section describes all external signals of the C509-L with its function.

Table 1-1

Pin Definitions and Functions

Symbol Pin Number I/O*) Function

Introduction

C509-L

P1.0 - P1.7 9-6, 1,

100-98

9

8

7

6

1

100

99

98

I/O

Port 1

is an 8-bit bidirectional I/O port with internal pullup

resistors. Port 1 pins that have 1's written to them are

pulled high by the internal pullup resistors, and in that

state can be used as inputs. As inputs, port 1 pins being

externally pulled low will source current ( I

, in the DC

IL

characteristics) because of the internal pullup resistors.

Port 1 can also be switched into a bidirectional mode, in

which CMOS levels are provided. In this bidirectional

mode, each port 1 pin can be programmed individually

as input or output.

Port 1 also contains the interrupt, timer, clock, capture

and compare pins that are used by various options. The

output latch corresponding to a secondary function must

be programmed to a one (1) for that function to operate

(except when used for the compare functions).

The secondary functions are assigned to the pins of

port 1 as follows :

P1.0 INT3

CC0 Interrupt 3 input / compare 0 output /

capture 0 input

P1.1 INT4 CC1 Interrupt 4 input / compare 1 output /

capture 1 input

P1.2 INT5 CC2 Interrupt 5 input / compare 2 output /

capture 2 input

P1.3 INT6 CC3 Interrupt 6 input / compare 3 output /

capture 3 input

P1.4 INT2

CC4 Interrupt 2 input / compare 4 output /

capture 4 input

P1.5 T2EX Timer 2 external reload trigger input

P1.6 CLKOUT System clock output

P1.7 T2 Counter 2 input

*) I = Input

O = Output

Semiconductor Group 1-5 1997-10-01

Page 13

Table 1-1

Pin Definitions and Functions (cont’d)

Symbol Pin Number I/O*) Function

Introduction

C509-L

P9.0 - P9.7 74-77,

5-2

XTAL2 12 –

I/O

Port 9

is an 8-bit bidirectional I/O port with internal pullup resistors. Port 9 pins that have 1's written to them are pulled

high by the internal pullup resistors, and in that state can

be used as inputs. As inputs, port 9 pins being externally

pulled low will source current ( I

, in the DC characteri-

IL

stics) because of the internal pullup resistors.

Port 9 can also be switched into a bidirectional mode, in

which CMOS levels are provided. In this bidirectional

mode, each port 1 pin can be programmed individually

as input or output.

Port 9 also serves alternate compare functions. The output latch corresponding to a secondary function must be

programmed to a one (1) for that function to operate.

The secondary functions are assigned to the pins of

port 9 as follows :

P9.0-P9.7 CC10-CC17 Compare/capture channel 0-7

output/input

XTAL2

is the input to the inverting oscillator amplifier and input

to the internal clock generator circuits.

When supplying the C509-L with an external clock

source, XTAL2 should be driven, while XTAL1 is left

unconnected. A duty cycle of 0.45 to 0.55 of the clock

signal is required. Minimum and maximum high and low

times as well as rise/fall times specified in the AC

characteristics must be observed.

XTAL1 13 –

XTAL1

Output of the inverting oscillator amplifier. This pin is

used for the oscillator operation with crystal or ceramic

resonartor

*) I = Input

O = Output

Semiconductor Group 1-6 1997-10-01

Page 14

Table 1-1

Pin Definitions and Functions (cont’d)

Symbol Pin Number I/O*) Function

Introduction

C509-L

P2.0 – P2.7 14-21 I/O

PSEN

/ RDF 22 O

Port 2

is a 8-bit I/O port. Port 2 emits the high-order address

byte during fetches from external program memory and

during accesses to external data memory that use 16-bit

addresses (MOVX @DPTR). In this application it uses

strong internal pullup resistors when issuing 1s. During

accesses to external data memory that use 8-bit

addresses (MOVX @Ri), port 2 issues the contents of the

P2 special function register.

P2.0 - P2.7 A8 - A15 Address lines 8 - 15

Program Store Enable / Read FLASH

The PSEN

external program memory to the bus during external

code fetch operations. It is activated every third

oscillator period. PSEN is not activated during external

data memory accesses caused by MOVX instructions.

PSEN is not activated when instructions are executed

from the internal Boot ROM or from the XRAM.

In external programming mode RDF becomes active

when executing external data memory read (MOVX)

instructions.

output is a control signal that enables the

ALE 23 O

EA

PRGEN 25 I External Flash-EPROM Program Enable

*) I = Input

O = Output

24 I External Access Enable

Address Latch Enable

This output is used for latching the low byte of the

address into external memory during normal operation.

It is activated every third oscillator period except during

an external data memory access caused by MOVX

instructions.

The status of this pin is latched at the end of a reset.

When held at low level, the C509-L fetches all

instructions from the external program memory. For the

C509-L this pin must be tied low.

A low level at this pin disables the programming of an

external Flash-EPROM. To enable the programming of

an external Flash-EPROM, the pin PRGEN must be held

at high level and bit PRGEN1 in SFR SYSCON1 has to

be set. There is no internal pullup resistor connected to

this pin.

Semiconductor Group 1-7 1997-10-01

Page 15

Table 1-1

Pin Definitions and Functions (cont’d)

Symbol Pin Number I/O*) Function

Introduction

C509-L

P0.0 – P0.7 26, 27,

30-35

I/O Port 0

is an 8-bit open-drain bidirectional I/O port. Port 0 pins

that have 1s written to them float, and in that state can be

used as high-impendance inputs. Port 0 is also the

multiplexed low-order address and data bus during

accesses to external program or data memory. In this

operating mode it uses strong internal pullup resistors

when issuing 1 s.

P0.0 - P0.7 AD0-AD7 Address/data lines 0 - 7

HWPD

36 I Hardware Power Down

A low level on this pin for the duration of one machine

cycle while the oscillator is running resets the C509-L.

A low level for a longer period will force the part to power

down mode with the pins floating. There is no internal

pullup resistor connected to this pin.

P5.0 - P5.7 44-37 I/O Port 5

is an 8-bit bidirectional I/O port with internal pullup

resistors. Port 5 pins that have 1's written to them are

pulled high by the internal pullup resistors, and in that

state can be used as inputs. As inputs, port 5 pins being

externally pulled low will source current (I

characteristics) because of the internal pullup resistors.

Port 5 can also be switched into a bidirectional mode, in

which CMOS levels are provided. In this bidirectional

mode, each port 5 pin can be programmed individually

as input or output.

Port 5 also serves as alternate function for “Concurrent

Compare” and "Set/Reset compare” functions. The

output latch corresponding to a secondary function must

be programmed to a one (1) for that function to operate.

The secondary functions are assigned to the pins of port

5 as follows :

P5.0 - P5.7 CCM0-CCM7 Concurrent Compare

, in the DC

IL

or Set/Reset lines 0 - 7

*) I = Input

O = Output

Semiconductor Group 1-8 1997-10-01

Page 16

Table 1-1

Pin Definitions and Functions (cont’d)

Symbol Pin Number I/O*) Function

OWE 45 I Oscillator Watchdog Enable

A high level on this pin enables the oscillator watchdog.

When left unconnected, this pin is pulled high by a weak

internal pullup resistor. The logic level at OWE should

not be changed during normal operation. When held at

low level the oscillator watchdog function is turned off.

During hardware power down the pullup resistor is

switched off.

Introduction

C509-L

P6.0 - P6.7 46-50,

54-56

46

47

48

49

I/O Port 6

is an 8-bit bidirectional I/O port with internal pullup

resistors. Port 6 pins that have 1's written to them are

pulled high by the internal pullup resistors, and in that

state can be used as inputs. As inputs, port 6 pins being

externally pulled low will source current (I

characteristics) because of the internal pullup resistors.

Port 6 can also be switched into a bidirectional mode, in

which CMOS levels are provided. In this bidirectional

mode, each port 6 pin can be programmed individually

as input or output.

Port 6 also contains the external A/D converter control

pin, the receive and transmission lines for the serial

port 1, and the write-FLASH control signal. The output

latch corresponding to a secondary function must be

programmed to a one (1) for that function to operate.

The secondary functions are assigned to the pins of

port 6 as follows :

P6.0 ADST

P6.1 R×D1 Receiver data input of serial interface 1

P6.2 T×D1 Transmitter data output of serial

P6.3 WRF The WRF (write Flash) signal is active

, in the DC

IL

External A/D converter start pin

interface 1

when the programming mode is

selected. In this mode WRF becomes

active when executing external data

memory write (MOVX) instructions.

*) I = Input

O = Output

Semiconductor Group 1-9 1997-10-01

Page 17

Table 1-1

Pin Definitions and Functions (cont’d)

Symbol Pin Number I/O*) Function

Introduction

C509-L

P8.0 - P8.6 57-60,

51-53

RO

61 O Reset Output

P4.0 – P4.7 64-66,

68-72

I Port 8

is a 7-bit unidirectional input port. Port pins can be used

for digital input if voltage levels meet the specified input

high/low voltages, and for the higher 7-bit of the

multiplexed analog inputs of the A/D converter

simultaneously.

P8.0 - P8.6 AIN8 - AIN14 Analog input 8 - 14

This pin outputs the internally synchronized reset

request signal. This signal may be generated by an

external hardware reset, a watchdog timer reset or an

oscillator watchdog reset. The RO output is active low.

I/O Port 4

is an 8-bit bidirectional I/O port with internal pull-up

resistors. Port 4 pins that have 1’s written to them are

pulled high by the internal pull-up resistors, and in that

state can be used as inputs. As inputs, port 4 pins being

externally pulled low will source current (I

characteristics) because of the internal pull-up resistors.

Port 4 also erves as alternate compare functions. The

output latch corresponding to a secondary functionmust

be programmed to a one (1) for that function to operate.

The secondary functions are assigned to the pins of port

4 as follows :

P4.0 - P4.7 CM0 - CM7 Compare channel 0 - 7

, in the DC

IL

PE

/ SWD 67 I Power Saving Modes Enable / Start Watchdog Timer

A low level on this pin allows the software to enter the

power down mode, idle and slow down mode. If the low

level is also seen during reset, the watchdog timer

function is off on default.

Usage of the software controlled power saving modes is

blocked, when this pin is held on high level. A high level

during reset performs an automatic start of the watchdog

timer immediately after reset.

When left unconnected this pin is pulled high by a weak

internal pullup resistor. During hardware power down the

pullup resistor is switched off.

*) I = Input

O = Output

Semiconductor Group 1-10 1997-10-01

Page 18

Table 1-1

Pin Definitions and Functions (cont’d)

Symbol Pin Number I/O*) Function

RESET 73 I RESET

A low level on this pin for the duration of two machine

cycles while the oscillator is running resets the C509-L.

A small internal pullup resistor permits power-on reset

using only a capacitor connected to VSS.

Introduction

C509-L

V

V

AREF

AGND

78 – Reference voltage for the A/D converter

79 – Reference ground for the A/D converter

P7.0 - P7.7 87-80 I Port 7

Port 7 is an 8-bit unidirectional input port. Port pins can

be used for digital input if voltage levels meet the

specified input high/low voltages, and for the lower 8-bit

of the multiplexed analog inputs of the A/D converter

simultaneously.

P7.0 - P7.7 AIN0 - AIN7 Analog input 0 - 7

*) I = Input

O = Output

Semiconductor Group 1-11 1997-10-01

Page 19

Table 1-1

Pin Definitions and Functions (cont’d)

Symbol Pin Number I/O*) Function

Introduction

C509-L

P3.0 – P3.7 90-97

90

91

92

93

94

95

96

97

I/O Port 3

is an 8-bit bidirectional I/O port with internal pullup

resistors. Port 3 pins that have 1's written to them are

pulled high by the internal pullup resistors, and in that

state can be used as inputs. As inputs, port 3 pins being

externally pulled low will source current (I

characteristics) because of the internal pullup resistors.

Port 3 also contains two external interrupt inputs, the

timer 0/1 inputs, the serial port 0 receive/transmit line

and the external memory strobe pins. The output latch

corresponding to a secondary function must be

programmed to a one (1) for that function to operate.

The secondary functions are assigned to the port pins of

port 3 as follows

P3.0 R×D0 Receiver data input (asynchronous) or

P3.1 T×D0 Transmitter data output (asynchronous)

P3.2 INT0 Interrupt 0 input / timer 0 gate control

P3.3 INT1 Interrupt 1 input / timer 1 gate control

P3.4 T0 Counter 0 input

P3.5 T1 Counter 1 input

P3.6 WR

P3.7 RD / The read control signal enables the

, in the DC

IL

data input/output (synchronous) of serial

interface 0

or clock output (synchronous) of the

serial interface 0

The write control signal latches the data

byte from port 0 into the external data

memory

external data memory to port 0

PSENX PSENX (external program store enable)

enables the external code memory

when the external / internal XRAM

mode or external / internal programming

mode is selected.

V

SS

V

CC

*) I = Input

O = Output

10, 28, 62, 88 – Circuit ground potential

11, 29, 63, 89 – Supply terminal for all operating modes

Semiconductor Group 1-12 1997-10-01

Page 20

Fundamental Structure

C509-L

2 Fundamental Structure

The C509-L is the high-end 8051-compatible microcontroller of the C500 microcontroller family with

a significantly increased performance of CPU and peripheral units. It includes the complete

SAB 80C517A functionality, providing 100% upward compatibility. This means that all existing

80517A programs or user’s program libraries can be used further on without restriction and may be

easily extended to the C509-L.

Some of the various on-chip peripherals of the C509-L support the 8-bit core in case of stringent

real-time requirements. The 32-bit/16-bit arithmetic unit, the improved 4-level interrupt structure and

eight 16-bit datapointers are meant to give such a CPU support. But strict compatibility to the 8051

architecture is a principle of the C509-L design.

Furthermore, the C509-L contains eight 8-bit I/O ports and fifteen general input lines. The second

serial channel is compatible to the 8051-UART and provided with an independent and freely

programmable baud rate generator. An 10-bit resolution A/D-converter with built-in self calibration

has been integrated to allow analog signal processing. The C509-L further includes a powerful

compare/capture unit with two 16-bit compare timers for all kinds of digital signal processing. The

controller has been completed with well considered provisions for “fail-safe” reaction in critical

applications and offers all CMOS features like low power consumption as well as an idle, powerdown and slow-down mode.

Figure 2-1 shows the block diagram of the C509-L.

Semiconductor Group 2-1 1997-10-01

Page 21

Fundamental Structure

C509-L

Figure 2-1

Block Diagram of the C509-L

Semiconductor Group 2-2 1997-10-01

Page 22

Fundamental Structure

C509-L

2.1 CPU

The CPU is designed to operate on bits and bytes. The instructions, which consist of up to 3 bytes,

are performed in one, two or four machine cycles. One machine cycle requires six oscillator cycles

(this number of oscillator cycles differs from other members of the C500 microcontroller family). The

instruction set has extensive facilities for data transfer, logic and arithmetic instructions. The

Boolean processor has its own full-featured and bit-based instructions within the instruction set. The

C509-L uses five addressing modes: direct access, immediate, register, register indirect access,

and for accessing the external data or program memory portions a base register plus index-register

indirect addressing.Efficient use of program memory results from an instruction set consisting of

44 % one-byte, 41 % two-byte, and 15 % three-byte instructions. With a 16 MHz clock, 58 % of the

instructions execute in 375 ns.

The CPU (Central Processing Unit) of the C509-L consists of the instruction decoder, the arithmetic

section and the program control section. Each program instruction is decoded by the instruction

decoder. This unit generates the internal signals controlling the functions of the individual units

within the CPU. They have an effect on the source and destination of data transfers, and control the

ALU processing.

The arithmetic section of the processor performs extensive data manipulation and is comprised of

the arithmetic/logic unit (ALU), an A register, B register and PSW register.

The ALU accepts 8-bit data words from one or two sources and generates an 8-bit result under the

control of the instruction decoder. The ALU performs the arithmetic operations add, substract,

multiply, divide, increment, decrement, BDC-decimal-add-adjust and compare, and the logic

operations AND, OR, Exclusive OR, complement and rotate (right, left or swap nibble (left four)).

Also included is a Boolean processor performing the bit operations as set, clear, completement,

jump-if-not-set, jump-if-set-and-clear and move to/from carry. Between any addressable bit (or its

complement) and the carry flag, it can perform the bit operations of logical AND or logical OR with

the result returned to the carry flag.

The program control section controls the sequence in which the instructions stored in program

memory are executed. The 16-bit program counter (PC) holds the address of the next instruction to

be executed. The conditional branch logic enables internal and external events to the processor to

cause a change in the program execution sequence.

Accumulator

ACC is the symbol for the accumulator register. The mnemonics for accumulator-specific

instructions, however, refer to the accumulator simply as A.

Program Status Word

The Program Status Word (PSW) contains several status bits that reflect the current state of the

CPU.

Semiconductor Group 2-3 1997-10-01

Page 23

Fundamental Structure

C509-L

Special Function Register PSW (Address D0H) Reset Value : 00

Bit No. D7

D0

H

MSB

H

D6

H

D5

H

D4

CY AC F0 RS1

H

D3

H

D2

H

RS0 OV F1 P

D1

H

LSB

D0

H

PSW

Bit Function

CY Carry Flag

Used by arithmetic instructions.

AC Auxiliary Carry Flag

Used by instructions which execute BCD operations)

F0 General Purpose Flag

RS1

RS0

Register Bank select control bits

These bits are used to select one of the four register banks.

RS1 RS0 Function

H

0 0 Bank 0 selected, data address 00H-07

0 1 Bank 1 selected, data address 08H-0F

1 0 Bank 2 selected, data address 10H-17

1 1 Bank 3 selected, data address 18H-1F

H

H

H

H

OV Overflow Flag

F1 General Purpose Flag

Used by arithmetic instructions.

P Parity Flag

Set/cleared by hardware after each instruction cycle to indicate an odd/even

number of “one” bits in the accumulator, i.e. even parity.

B Register

The B register is used by 8-bit multiply and divide instructions and serves as both source and

destination. For other instructions it can be treated as another scratch pad register.

Stack Pointer

The stack pointer (SP) register is 8 bits wide. It is incremented before data is stored during PUSH

and CALL executions and decremented after data is popped during a POP and RET (RETI)

execution, i.e. it always points to the last valid stack byte. While the stack may reside anywhere in

the on-chip RAM, the stack pointer is initialized to 07H after a reset. This causes the stack to begin

a location = 08H above register bank zero. The SP can be read or written under software control.

Semiconductor Group 2-4 1997-10-01

Page 24

Fundamental Structure

C509-L

2.2 CPU Timing

A machine cycle consists of 6 states (6 oscillator periods). Each state is divided into a phase 1 half,

during OSC is high, and a phase 2 half, during which OSC is low. Thus, a machine cycle consists

of 6 oscillator periods, numbered S1P1 (state 1, phase 1) through S6P2 (state 6, phase 2). Each

state lasts for one oscillator period. Typically, arithmetic and logical operations take place during

phase 1 and internal register-to-register transfers take place during phase 2.

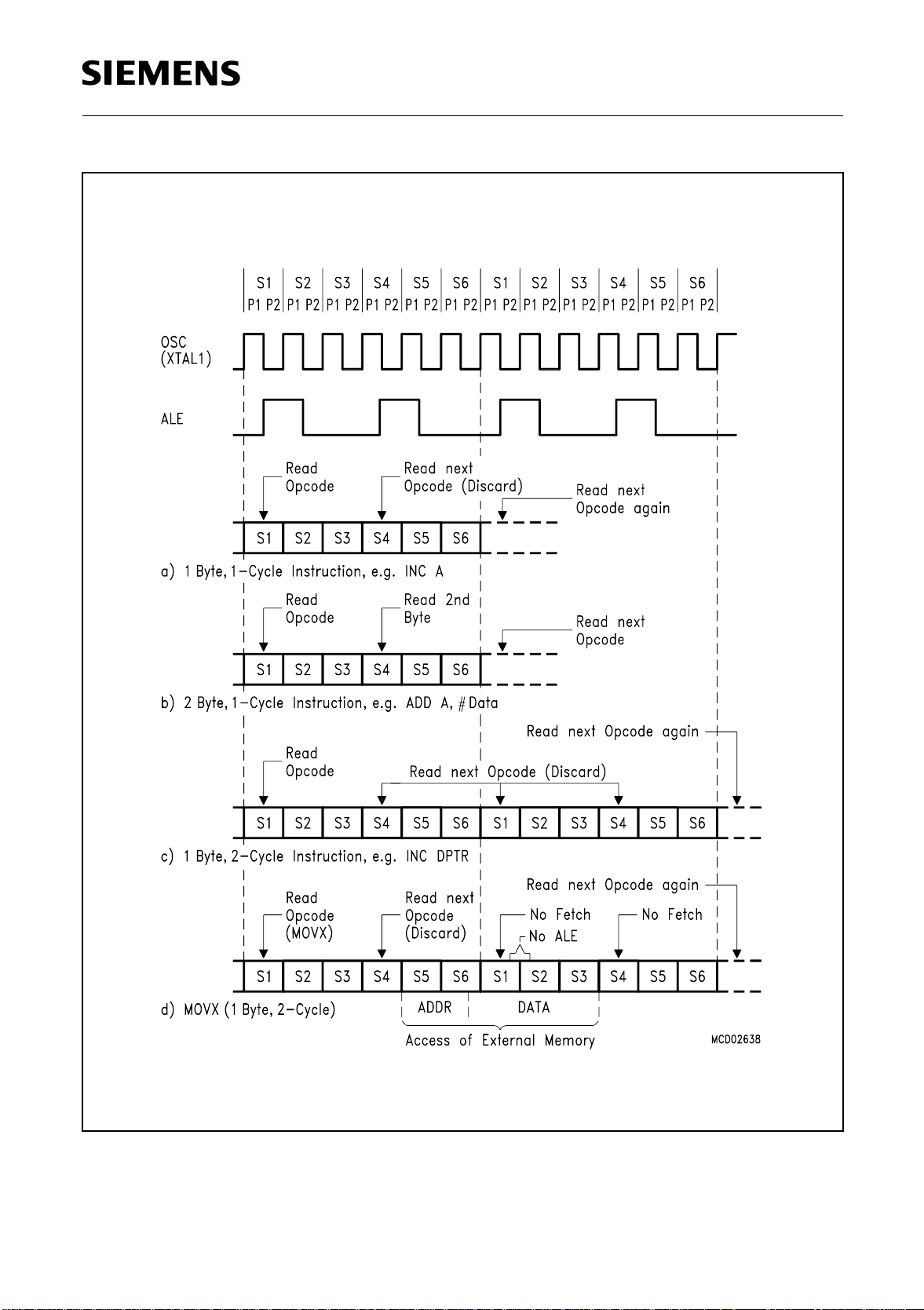

The diagrams in figure 2-2 show the fetch/execute timing related to the internal states and phases.

Since these internal clock signals are not user-accessible, the XTAL1 oscillator signals and the ALE

(address latch enable) signal are shown for external reference. ALE is normally activated twice

during each machine cycle: once during S1P2 and S2P1, and again during S4P2 and S5P1.

Executing of a one-cycle instruction begins at S1P2, when the op-code is latched into the instruction

register. If it is a two-byte instruction, the second reading takes place during S4 of the same

machine cycle. If it is a one-byte instruction, there is still a fetch at S4, but the byte read (which would

be the next op-code) is ignored (discarded fetch), and the program counter is not incremented. In

any case, execution is completed at the end of S6P2.

Figures 2-2 a) and b) show the timing of a 1-byte, 1-cycle instruction and for a 2-byte, 1-cycle

instruction.

Most C509-L instructions are executed in one cycle. MUL (multiply) and DIV (divide) are the only

instructions that take more than two cycles to complete; they take four cycles. Normally two code

bytes are fetched from the program memory during every machine cycle. The only exception to this

is when a MOVX instruction is executed. MOVX is a one-byte, 2-cycle instruction that accesses

external data memory. During a MOVX, the two fetches in the second cycle are skipped while the

external data memory is being addressed and strobed. Figure 2-2 c) and d) show the timing for a

normal 1-byte, 2-cycle instruction and for a MOVX instruction.

Semiconductor Group 2-5 1997-10-01

Page 25

Fundamental Structure

C509-L

Figure 2-2

Fetch and Execute Sequences

Semiconductor Group 2-6 1997-10-01

Page 26

Memory Organization

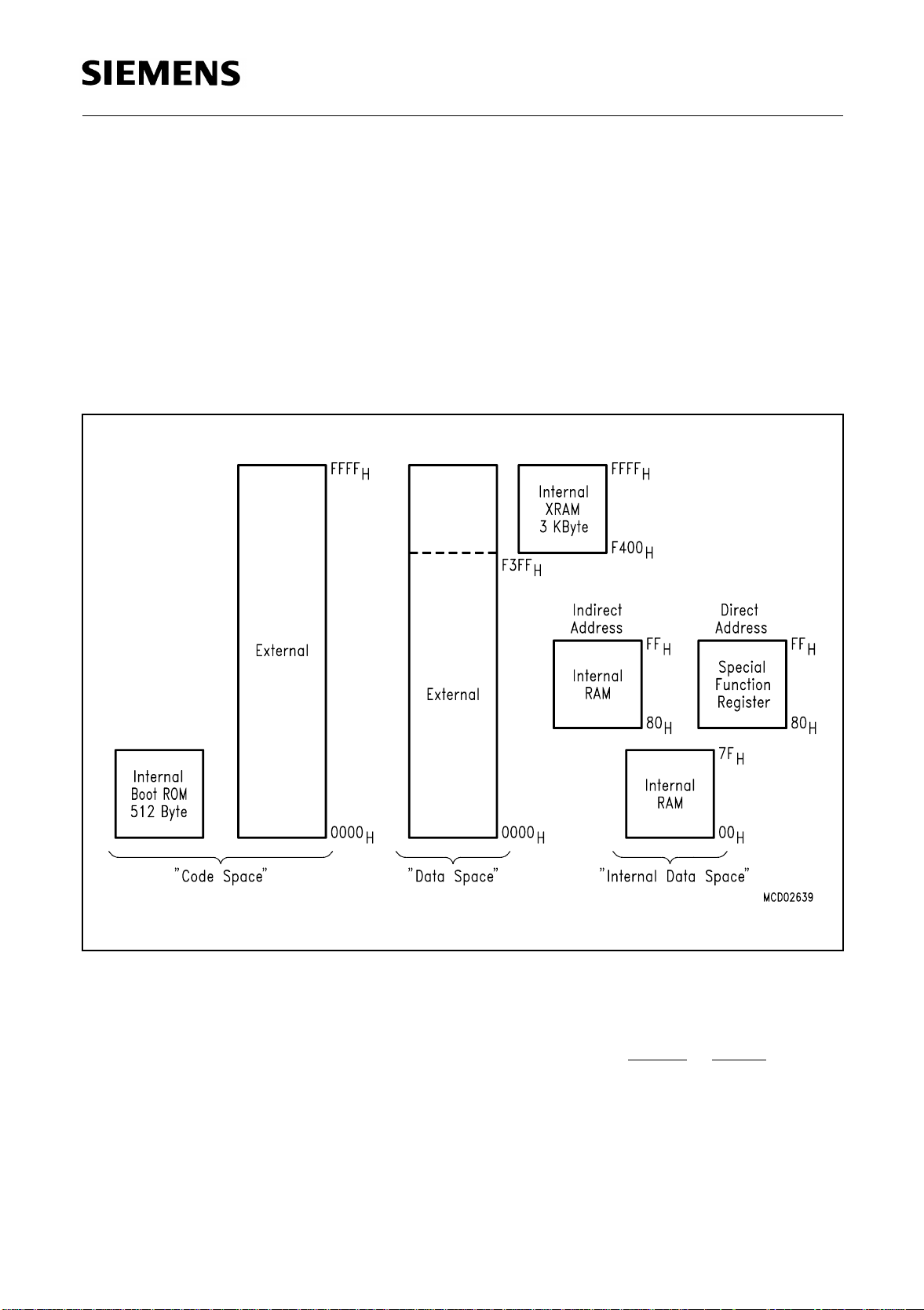

3 Memory Organization

The C509-L CPU manipulates data and operands in the following five address spaces:

– up to 64 Kbyte of external program memory

– up to 64 Kbyte of external data memory

– 512 byte of internal Boot ROM (program memory)

– 256 bytes of internal data memory

– 3 Kbyte of internal XRAM data memory

– a 128 byte special function register area

Figure 3-1 illustrates the memory address spaces of the C509-L.

C509-L

Figure 3-1

C509-L Memory Map

The internal XRAM data memory overlaps with the external data memory in the address range from

F400H to FFFFH. In this address range, either external or internal data RAM can be used. If the

internal XRAM has been enabled, it only can be disabled by an active RESET or HWPD signal.

The internal Boot ROM also overlaps with the external code memory in the address range from

0000H to 01FFH. Depending on the selected operating mode (chipmode), either external code

memory or the internal Boot ROM is accessed in this address range.

Semiconductor Group 3-1 1997-10-01

Page 27

Memory Organization

C509-L

3.1 Program Memory, “Code Space”

Besides the internal Boot ROM, the C509-L has no internal program memory (ROM). In normal

mode the program memory of the C509-L is located externally and can be expanded up to 64 Kbyte.

In the normal mode the C509-L fetches all instructions from the external program memory.

Therefore, the pin EA of the C509-L must be always tied to low level.

The Boot ROM includes a bootstrap loader program for the bootstrap mode of the C509-L. The

software routines of the bootstrap loader program allow the easy and quick programming or loading

of the internal XRAM (F400H to FFFFH) via the serial interface while the MCU is in-circuit. This

allows to transfer custom routines to the XRAM, which will program an external 64 KByte FLASH

memory. The routines of the bootstrap loader program may be executed or even can be blocked to

prevent unauthorized persons from reading out or writing to the external FLASH memory.

Therefore, the bootstrap loader checks an external FLASH memory for existing custom software

and executes it. The bootstrap loader program is described in detail in chapter 10.

3.2 Data Memory, “Data Space”

The data memory address space consists of an internal and an external memory space. The

internal data memory is divided into three physically separate and distinct blocks: the lower 128

bytes of RAM, the upper 128 bytes of RAM, and the 128 byte special function register (SFR) area.

While the upper 128 bytes of data memory and the SFR area share the same address locations,

they are accessed through different addressing modes. The lower 128 bytes of data memory can

be accessed through direct or register indirect addressing; the upper 128 bytes of RAM can be

accessed through register indirect addressing; the special function registers are accessible through

direct addressing. Four 8-register banks, each bank consisting of eight 8-bit multi-purpose registers,

occupy locations 0 through 1FH in the lower RAM area. The next 16 bytes, locations 20H through

2FH, contain 128 directly addressable bit locations. The stack can be located anywhere in the

internal data memory address space, and the stack depth can be expanded up to 256 bytes.

The external data memory can be expanded up to 64 Kbytes and can be accessed by instructions

that use a 16-bit or an 8-bit address. The internal XRAM is also located in the external data memory

area and must be accessed by external data memory instructions (MOVX). The XRAM can also

serve as code memory in the XRAM mode and in the FLASH programming mode. In these modes

program code which has been prior loaded via the bootstrap loader program, is executed in the

XRAM.

3.3 General Purpose Registers

The lower 32 locations of the internal RAM are assigned to four banks with eight general purpose

registers (GPRs) each. Only one of these banks may be enabled at a time. Two bits in the program

status word, RS0 (PSW.3) and RS1 (PSW.4), select the active register bank (see description of the

PSW in chapter 2). This allows fast context switching, which is useful when entering subroutines

or interrupt service routines.

The 8 general purpose registers of the selected register bank may be accessed by register

addressing. With register addressing the instruction op code indicates which register is to be used.

For indirect addressing R0 and R1 are used as pointer or index register to address internal or

external memory (e.g. MOV @R0).

Semiconductor Group 3-2 1997-10-01

Page 28

Memory Organization

C509-L

Reset initializes the stack pointer to location 07H and increments it once to start from location 08

H

which is also the first register (R0) of register bank 1. Thus, if one is going to use more than one

register bank, the SP should be initialized to a different location of the RAM which is not used for

data storage.

3.4 Program and Data Memory Organization

The C509-L can operate in four different operating modes (chipmodes) with different program and

data memory organizations:

– Normal Mode

– XRAM Mode

– Bootstrap Mode

– Programming Mode

Table 3-1 describes the program and data memory areas which are available in the different

chipmodes of the C509-L. It also shows the control bits of SFR SYSCON1, which are used for the

software selection of the chipmodes.

Table 3-1

Overview of Program and Data Memory Organization

Operating Mode

(Chipmode)

Program Memory Data Memory SYSCON1 Bits

Ext. Int. Ext. Int. PRGEN1SWAP

Normal Mode 0000

FFFF

H

H

XRAM Mode 0200H -

F3FF

H

Bootstrap Mode 0200H -

F3FF

H

Programming Mode 0200H -

FFFF

H

-

–

0000H 01FFH =

Boot ROM;

F400

H

-

FFFFH =

(XRAM)

0000H 01FFH =

Boot ROM

0000H 01FFH =

Boot ROM;

F400

H

-

FFFFH =

XRAM

0000H F3FF

H

0000

FFFF

H

H

-

(read only)

0000H F3FF

H

0000

FFFF

H

H

-

(read and

write)

F400

H

FFFF

H

(XRAM)

–

F400

H

FFFF

H

(XRAM)

–

-

00

01

-

10

11

Semiconductor Group 3-3 1997-10-01

Page 29

Memory Organization

C509-L

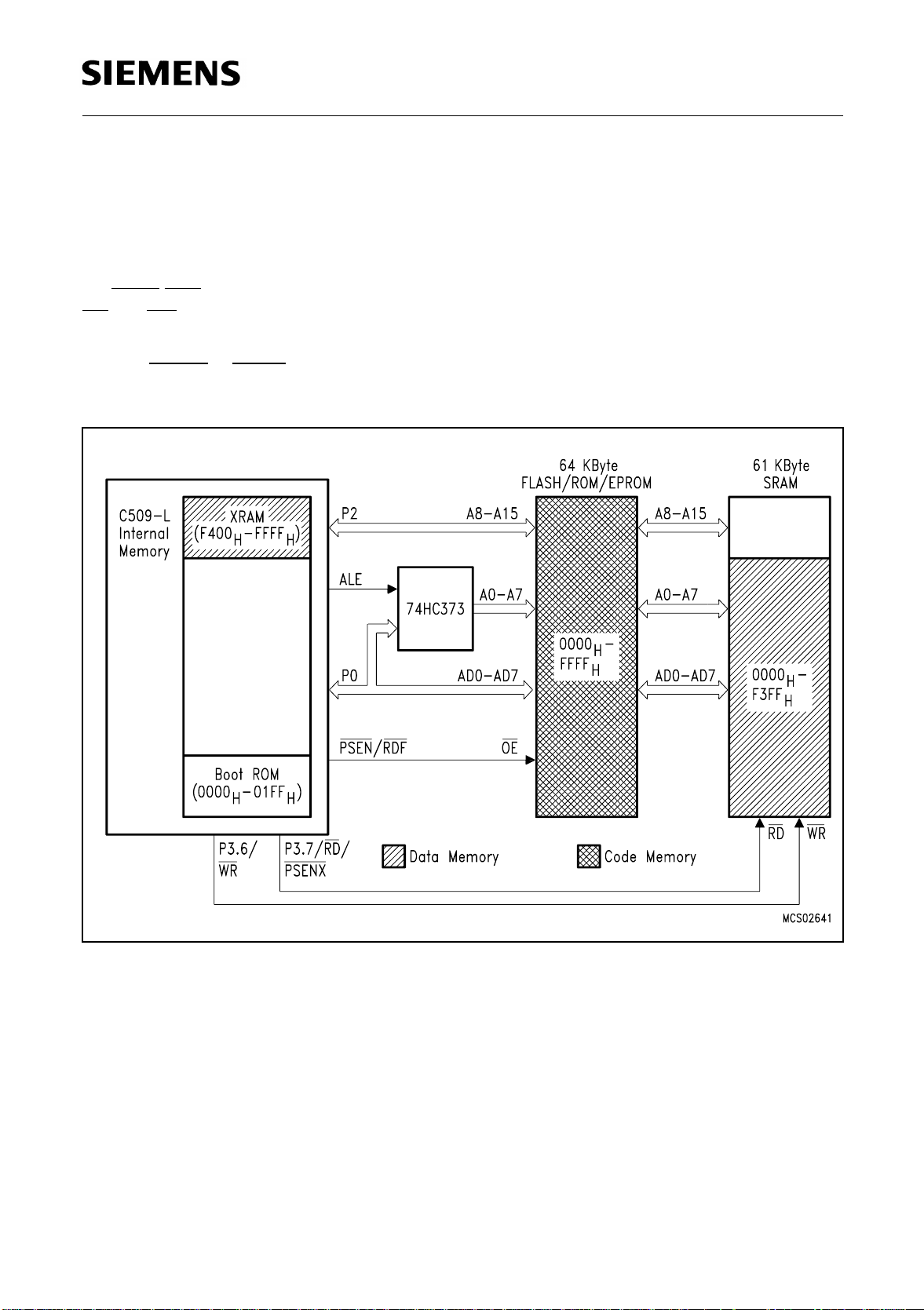

3.4.1 Interface of External FLASH/ROM/EPROM and External SRAM Memory

The external FLASH/ROM/EPROM memory and the external SRAM memory can be used in the

chipmodes either as code memory or as data memory. The basic memory configuration is shown

in figure 3-2.

The following alternate function pins control the read/write accesses for code/data memories:

PSEN / RDF Read control signal for the FLASH/ROM/EPROM memory

P6.3 / WRF Write control signal for the FLASH/ROM/EPROM memory

P3.6 / WR Write control signal for the SRAM memory

P3.7 / RD / PSENX Read control signal for the SRAM memory

Figure 3-2

Interface of External FLASH/ROM/EPROM and External SRAM Memory

Semiconductor Group 3-4 1997-10-01

Page 30

Memory Organization

C509-L

3.4.2 Normal Mode Configuration

The Normal Mode is the standard 8051 compatible operating mode of the C509-L. In this mode 64K

byte external code memory and 61K byte external SRAM as well as 3K byte internal data memory

(XRAM) are provided. If the XRAM is disabled (default after reset), totally 64K byte external data

memory are available. The Boot ROM is disabled. The external program memory is controlled by

the PSEN/RDF signal. Read and write accesses to the external data memory are controlled by the

RD and WR pins of port 3.

The Normal Mode is entered by keeping the pin PRGEN at a logic low during the rising edge of the

external RESET or HWPD signal. The locations of the code- and data-memory in Normal Mode are

shown in figure 3-4.

Figure 3-3

Locations of Code- and Data Memory in Normal Mode

Semiconductor Group 3-5 1997-10-01

Page 31

Memory Organization

C509-L

3.4.3 XRAM Mode Configuration

The XRAM Mode is implemented in the C509-L for executing e.g. up to 3K byte diagnostic software

which has been loaded into the XRAM in the Bootstrap Mode via the serial interface. In this

operating mode the Boot ROM, the XRAM, and the external data memory are mapped into the code

memory area, while the external ROM/EPROM is mapped into the external data memory area.

External program memory fetches from the SRAM are controlled by the P3.7/RD/PSENX pin.

External data memory read accesses from the ROM/EPROM are controlled by the PSEN/RDF pin.

In XRAM mode, the external data memory can only be read but not written.

The XRAM mode is entered by setting the SWAP bit, while the PRGEN pin (PRGEN1 bit) is kept

low. The locations of the code- and data-memory in the XRAM mode are shown in figure 3-4.

Figure 3-4

Locations of Code- and Data Memory in XRAM Mode

Notes: In the XRAM mode, programming of the external FLASH EPROM is not possible because

the PRGEN pin (PRGEN1 bit) is at logic low level (HW-protection).

The internal XRAM is selected automatically in the code memory, if the SWAP bit is set.

When leaving the XRAM Mode, the XRAM is disabled (only if the XMAP0 bit was not

cleared by software before).

Semiconductor Group 3-6 1997-10-01

Page 32

Memory Organization

C509-L

3.4.4 Bootstrap Mode Configuration

In the Bootstrap Mode the Boot ROM and the external FLASH/ROM/EPROM are mapped into the

code memory area. 61K byte external SRAM as well as 3K byte internal data memory (XRAM) are

provided in the external data memory area. The external program memory is controlled by the

PSEN/RDF signal. Read and write accesses to the external data memory are controlled by the RD

and WR pins of port 3.

The Bootstrap Mode is entered by keeping the pin PRGEN at a logic high level during the rising

edge of the external RESET or HWPD signal (→ PRGEN1=1). The locations of the code- and data

memory in the external boot-strap mode are shown in figure 3-5.

Figure 3-5

Locations of Code- and Data Memory in Bootstrap Mode

In Bootstrap Mode the internal XRAM is selected automatically as data memory. When leaving the

Bootstrap Mode, the XRAM is disabled (only if the XMAP0 bit was not cleared by software before).

Semiconductor Group 3-7 1997-10-01

Page 33

Memory Organization

C509-L

3.4.5 Programming Mode Configuration

The External Programming Mode is implemented for the in-circuit programming of external 5V-only

FLASH EPROMs. Similar as in the XRAM mode, the Boot ROM, the XRAM, and the external data

memory (SRAM) are mapped into the code memory area, while the external FLASH memory is

mapped into the external data memory area. Additionally to the XRAM mode, the FLASH memory

can also be written through external data memory accesses (MOVX instructions). External program

memory fetches from the SRAM are controlled by the P3.7/RD/PSENX pin. External data memory

read/write accesses from/to the ROM/EPROM are controlled by the PSEN/RDF and P6.3/WRF pin.

The Programming Mode is entered by setting the bits PRGEN1 and SWAP in SFR SYSCON1. The

locations of the code- and data memory in the Programming Mode are shown in figure 3-6.

Figure 3-6

Locations of Code- and Data Memory in Programming Mode

Prior to the usage of the Programming Mode, the XRAM has to be loaded by the FLASH specific

programming software algorithms (see also chapter 10 “The Bootstrap Loader”). This XRAM load

operation can be done using the Bootstrap Mode.

Semiconductor Group 3-8 1997-10-01

Page 34

Memory Organization

C509-L

Notes: The internal XRAM is enabled automatically in the code memory area if the SWAP bit is

set. When leaving the Programming Mode, the XRAM is disabled (only if the XMAP0 bit

was not cleared by software before).

Leaving the Programming Mode can be accomplished by:

– Clearing the bits PRGEN1 and SWAP prior to executing the special software unlock

sequence followed by a LJMP to “startaddress” in the FLASH memory returns the C509-L

into normal mode (program execution will start at “startaddress”).

– Activating the RESET or HWPD signal with the PRGEN pin at logic low level will clear the

bits PRGEN1 and SWAP.

Notes: Switching the PRGEN pin to logic low level during programming of an external FLASH will

reset the PRGEN1 bit. As a result the XRAM mode is entered and this inhibits any write

access to the external FLASH EPROM.

Clearing the SWAP bit during Programming Mode and executing the special software

unlock sequence will force the C509-L into the Bootstrap Mode.

Semiconductor Group 3-9 1997-10-01

Page 35

Memory Organization

C509-L

3.4.6 Special Function Register SYSCON1

There are five control bits located in SFR SYSCON1 (B2H) which control the code and data memory

organization of the C509-L. Two of these bits (PRGEN1 and SWAP) cannot be programmed as

normal bits but with a special software unlock sequence. The special software unlock sequence

was implemented to prevent unintentional changing of these bits and consists of consecutive

followed instructions which have to set two dedicated enable bits.

Special Function Register SYSCON1 (Address B2H) Reset Value : 00XXXEE0

B

1)

MSB

Bit No. 76543210

B2

ESWC SWC – EA1

H

1) “E” means that the value of the bit is defined through the external logic level at

pin PRGEN at the rising edge of the external RESET

EA0

PRGEN1PRGEN0 SWAP

or HWPD signals.

Bit Function

ESWC Enable Switch Chipmode

When selecting the chipmode with the bits SWAP and PRGEN1, the ESWC bit has

to be set simultaneously as the first instruction in the special software unlock

sequence. The bit ESWC will be cleared by hardware after 2 instruction cycles.

SWC Switch Chip Mode

The SWC bit has to be set as the second instruction in a special software unlock

sequence directly after having set bit ESWC. The new chipmode becomes active

after the second instruction cycle which follows the special software unlock

sequence. These two instruction cycles are used for initializing of the program

counter (LJMP instruction)

SWC is a write only bit. Reading SWC will always return a ‘0’.

LSB

SYSCON1

–, EA1, EA0 Reserved bits; at read operations these bits are undefined; at write operations to

SYSCON1 these bits can be written with “0” or “1”.

PRGEN1 Program Enable Bit 1

The PRGEN1 bit enables/disables the write accesses to an external FLASH

EPROM. The PRGEN1 bit contains the logic value of the external PRGEN pin

which is latched at the rising edge of the external RESET

or HWPD signal. When

the logic low level appears at the PRGEN pin, the PRGEN1 bit will be cleared in the

next instruction cycle without the need of a special software unlock sequence.

PRGEN1 = 0: Write access (programming) of external FLASH EPROM is

disabled

PRGEN1 = 1: Write access (programming) of external FLASH EPROM is

enabled

Any changing the PRGEN1 bit without using a special software unlock sequence

with the ESWC and SWC bits will have no effect and the former selected status will

be kept.

Semiconductor Group 3-10 1997-10-01

Page 36

Bit Function

PRGEN0 Program Enable Bit 0

The PRGEN0 bit is a read-only bit and represents the logic level of the external

PRGEN pin.

PRGEN0 = 1: The PRGEN1 bit can be set or cleared under software control.

PRGEN0 = 0: The PRGEN1 bit is held at logic low level and cannot be set under

software control.

Notes: Clearing the PRGEN0 bit by changing the logic level at the PRGEN pin in

the Normal Mode disables write accesses to the external FLASH EPROM.

Enable/disable write accesses to external FLASH EPROM can be done by

changing the PRGEN1 bit with a special software unlock sequence.

SWAP Swap Code- and Data Memory

SWAP = 0: The data memory and the code memory remain in their predefined

locations.

SWAP = 1: The following address areas and memory locations are assigned to

code memory:

0000H - 01FF

0200H - F3FF

F400H - FFFF

The following address areas and memory locations ar assigned to

data memory:

0000H - FFFF

H

H

H

H

Memory Organization

C509-L

→ Boot ROM

→ External data memory is swapped to external

code memory

→ The XRAM is enabled and automatically

mapped into code memory space.

(independent of bit XMAP0 in SFR SYSCON)

→ External FLASH /ROM/EPROM

The former code memory is assigned as data

memory and is now addressable by using

MOVX instructions.

Semiconductor Group 3-11 1997-10-01

Page 37

Memory Organization

C509-L

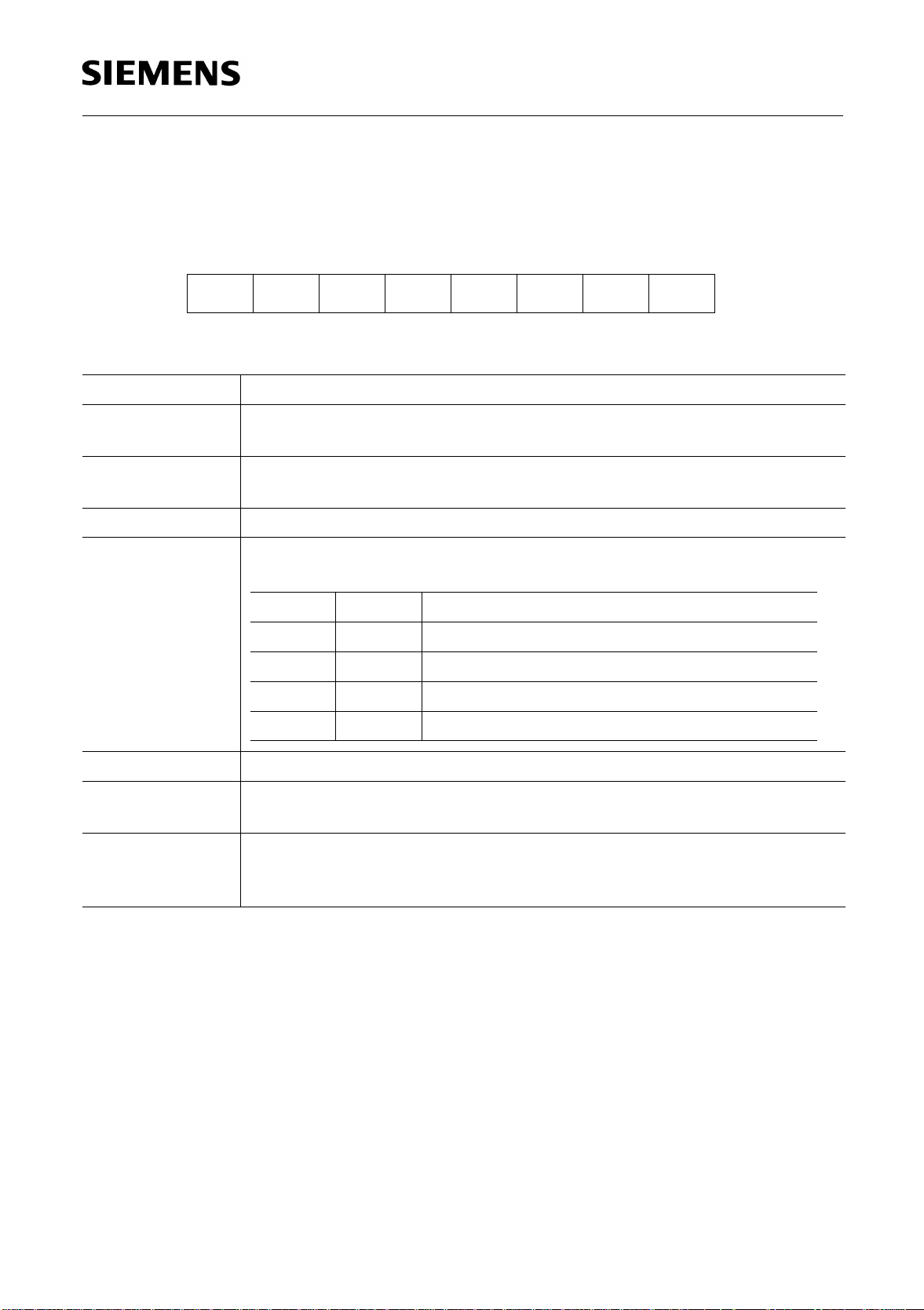

3.4.7 Operating Mode (Chipmode) Selection

The chipmode selection can be done by hardware after an active RESET or HWPD signal. Further,

the logic state of pin PRGEN is used for hardware selection. Bit Swap is not affected by hardware

selection. The chipmodes can also be selected by software. Software selection is achieved by

programming specific bits of SFR SYSCON1.

The following table 3-2 shows the hardware and software selection capabilities of the chipmodes.

Table 3-2

Hardware and Software Selection of Chipmodes

Operating Mode

Hardware Selection Software Selection

(Chipmode)

Normal Mode PRGEN pin = low

RESET or HWPD: edge

PRGEN pin = don’t care;

1 4

setting bits PRGEN1,SWAP = 0,0;

executing unlock sequence

XRAM Mode from Programming Mode:

setting PRGEN pin = low

PRGEN pin = don’t care;

2 5

setting bits PRGEN1,SWAP = 0,1;

executing unlock sequence

Bootstrap Mode PRGEN pin = high

RESET or HWPD: edge

PRGEN pin = high;

3 6

setting bits PRGEN1,SWAP =1,0;

executing unlock sequence

Programming Mode not possible PRGEN pin = high;

7

setting bits PRGEN1,SWAP = 1,1;

executing unlock sequence

Figure 3-7 below shows the information of table 3-2 as a state diagram (reference number in the

circle).

1

Normal Mode

PRGEN1, SWAP = 0,0

4

7

XRAM Mode

PRGEN1, SWAP = 0,1

5

6

5

2

5

3

4

7

6

Bootstrap Mode

PRGEN1, SWAP = 1,0

4

Programming Mode

PRGEN1, SWAP = 1,1

7

6

Hardware Selection

Software Selection

MCD02645

Figure 3-7

State Diagram of Chipmode Selection

Semiconductor Group 3-12 1997-10-01

Page 38

Memory Organization

C509-L

3.4.7.1 Special Software Unlock Sequence

The bits ESWC and SWC in SFR SYSCON1 are implemented in a way to prevent unintentional

changing of the bits SWAP or PRGEN1. Any changing the bits SWAP or PRGEN1 without using

the ESWC and SWC bits in a special software unlock sequence will have no effect and the above

bits will get back their old values two instruction cycles after being changed.

The following programming steps must be executed at the ESWC/SWC unlock sequence:

1.) First instruction:

Changing the value of the bits SWAP or PRGEN1 with one or more consecutive instructions

simultaneously with setting of bit ESWC:

ANL SYSCON1, #11111X1YB ; clearing of bits PRGEN1 (X=0) and/or SWAP (Y=0)

ORL SYSCON1, #10000X0YB ; setting of ESWC bit with setting of PRGEN1 or SWAP

; e.g. clearing of the SWAP bit:

ANL SYSCON1,#11111110B

ORL SYSCON1,#10000000B

or:

ORL SYSCON1, #10000X0YB ; setting of the bits PRGEN1 (X=1) and/or SWAP (Y=1) and

; setting the ESWC bit simultaneously

; e.g. setting of the SWAP bit:

ORL SYSCON1,#10000001B

2.) Second instruction:

Setting of bit SWC immediately after 1.) with

ORL SYSCON1, #40H ;

The new chipmode becomes active two instruction cycles after the instruction which sets the bit

SWC (see 2.). These two instruction cycle delay should normally be used for initialization of the

program counter to the 16 bit start-address of the new code memory resource, e.g. with:

LJMP 0XXXXH ; XXXX = 16-bit hex address in new code memory

If the code memory resource is not changed by the new chipmode there is no need of a new

initialization of the program counter. However the new Chipmode becomes active two instruction

cycles after 2.).

The special software unlock instruction sequence cannot be interrupted by an interrupt request. Any