Page 1

C501

8-Bit Single-Chip Microcontroller

User’s Manual 04.97

http://www.siemens.de/

Semiconductor/

Page 2

Edition 04.97

This edition was realized using the software

system FrameMaker

.

Published by Siemens AG,

Bereich Halbleiter, Marketing-

Kommunikation, Balanstraße 73,

81541 München

©

Siemens AG 1997.

All Rights Reserved.

Attention please!

As far as patents or other rights of third parties are concerned, liability is only assum ed

for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured

characteristics.

Terms of delivery and rights to change design

reserved .

For questions on technology, delivery and

prices please contact the Semico nduct or

Group Offices in Germany or the Siemens

Companies and Representatives wor ldwide

(see address list).

Due to technical requirements components

may contain dangerous substances. For information on the types in question please

contact your nearest Siemens Office, Sem iconductor Group.

Siemens AG is an approved CECC manufacturer.

Packing

Please use the recycling operators known to

you. We can also help you – get in touch with

your nearest sales office. By agree m ent we

will take packing material back, if it is sorted.

You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept,

we shall have to invoice you for any costs incurred.

Components used in life-support devices

or systems must be expressly authorized

for such purpose!

Critical components

Group of Siemens AG, may only be used in

life-support devices or system s

1

of the Semiconductor

2

with the express written approval of the Semiconductor

Group of Siemens AG.

1 A critical component is a component used

in a life-support device or system whose

failure can reasonably be expected to

cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

2 Life support devices or systems are in-

tended (a) to be implanted in the human

body, or (b) to support and/or maintain

and sustain human life. If they fail, it is

reasonable to assume that the health of

the user may be endangered.

Page 3

C501 User’s Manual

Revision History : 04.97

Previous Releases : 02.96, 08.94, 08.93 (Original Version)

Page

(previous

version)

general C501G-1E OTP version included (new chapter 9, AC/DC characteri stics

Chapter 1

1-2

3-4 to 3-6

4-2

6-10

6-15 follo.

6-23 follo.

6-30 follo.

chapter 7

8-2

chapter 9

9-6, 9-9

9-12

9-17

9-18

-

-

Page

(new

version)

Chapter 1

1-2

3-2 to 3-7

4-4

4-5

6-10

6-15, 6-16

6-22, 6-23

6-29

chapter 7

8-4

chapter 9

chapter 10

10-3

10-6,10-8

10-10

10-13

10-15/16

10-18

10-21

chapter 11

Subjects (changes since last revision)

now in chapter 10)

Several figures: update with C501-1E signal names and definitions;

P-MQFP-44 package (pin configuration and pin numbers) added

Feature list is updated

Actualized design of the SFR tables

Figure 4-1 moved

Description of enhanced hooks emulation concept added

Figure 6-6 corrected

Improved timer 0/1 register description

Improved timer 2 register description

Improved serial port register description

Improved description of the interrupt related functions: all enable,

control, and request register bits now included

Table 8-1 moved into chapter 8.4

New chapter 9 “OTP Memory Operation of the C501-1E” included

Old chapter 9 (“Device Specifications”) is now chapter 10

“DC Characteristics for C501-1E” included

Characteristics for “External Clock Drive” on three pages moved below

“Ext. Data Memory Characteristics”

Old figure 7 moved to figure 10-4

New chapter 10.8 “OTP Programming and Verification Characteristics”

Figure 10-9: M-QFP-44 pin numbers for XTAL1/XTAL2 added

M-QFP-44 package outline added

Manual index information added

Page 4

C501

Table of Contents Page

1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

1.1 Pin Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

1.2 Pin Definitions and Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

2 Fundamental Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

2.1 CPU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-2

2.2 CPU Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4

3 Memory Organization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

3.1 Program Memory, “Code Space” . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

3.2 Data Memory, “Data Space” . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

3.3 General Purpose Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

3.4 Special Function Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

4 External Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

4.1 Accessing External Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

4.1.1 Role of P0 and P2 as Data/Address Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

4.1.2 Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

4.1.3 External Program Memory Access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

4.2 PSEN, Program Store Enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-4

4.3 ALE, Address Latch Enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-4

4.4 Overlapping External Data and Program Memory Spaces . . . . . . . . . . . . . 4-4

4.5 Enhanced Hooks Emulation Concept . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-5

5 System Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

5.1 Hardware Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

5.2 Hardware Reset Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

6 On-Chip Peripheral Components . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

6.1 Parallel I/O . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

6.1.1 Port Structures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

6.1.1.1 Port 0 and Port 2 used as Address/Data Bus . . . . . . . . . . . . . . . . . . . . . . . 6-7

6.1.2 Alternate Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-8

6.1.3 Port Handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-10

6.1.3.1 Port Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-10

6.1.3.2 Port Loading and Interfacing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-11

6.1.3.3 Read-Modify-Write Feature of Ports 1,2 and 3 . . . . . . . . . . . . . . . . . . . . . 6-11

6.2 Timers/Counters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-13

6.2.1 Timer/Counter 0 and 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-14

6.2.1.1 Timer/Counter 0 and 1 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-15

6.2.1.2 Mode 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-18

6.2.1.3 Mode 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-19

6.2.1.4 Mode 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-20

6.2.1.5 Mode 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-21

Semiconductor Group I-1

Page 5

C501

Table of Contents Page

6.2.2 Timer/Counter 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-22

6.2.2.1 Timer 2 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-23

6.2.2.2 Auto-Reload (Up or Down Counter) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-26

6.2.2.3 Capture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-28

6.3 Serial Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-29

6.3.1 Multiprocessor Communications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-30

6.3.2 Serial Port Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-30

6.3.3 Baud Rates Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-32

6.3.3.1 Using Timer 1 to Generate Baud Rates . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-33

6.3.3.2 Using Timer 2 to Generate Baud Rates . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-34

6.3.4 Details about Mode 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-36

6.3.5 Details about Mode 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-39

6.3.6 Details about Modes 2 and 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-42

7 Interrupt System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-1

7.1 Interrupt Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-2

7.1.1 Interrupt Enable Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-2

7.1.2 Interrupt Request / Control Flags . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-4

7.1.3 Interrupt Priority Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-6

7.2 Interrupt Priority Level Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-7

7.3 How Interrupts are Handled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-8

7.4 External Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-10

7.5 Interrupt Response Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-11

8 Power Saving Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-1

8.1 Power Saving Mode Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-1

8.2 Idle Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-2

8.3 Power Down Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-3

8.4 State of Pins in Software Initiated Power Saving Modes . . . . . . . . . . . . . . . 8-4

9 OTP Memory Operation of the C501-1E . . . . . . . . . . . . . . . . . . . . . . . . . . 9-1

9.1 Programming Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-1

9.2 Quick-Pulse Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-2

9.3 Encryption Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-3

9.4 Security Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-3

9.5 OTP Memory Verification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-4

Semiconductor Group I-2

Page 6

C501

Table of Contents Page

10 Device Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-1

10.1 Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-1

10.2 DC Characteristics for C501-L / C501-1R . . . . . . . . . . . . . . . . . . . . . . . . . 10-2

10.3 DC Characteristics for C501-1E . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-3

10.4 AC Characteristics for C501-L / C501-1R / C501-1E . . . . . . . . . . . . . . . . 10-5

10.5 AC Characteristics for C501-L24 / C501-1R24 / C501-1E24 . . . . . . . . . . . 10-7

10.6 AC Characteristics for C501-L40 / C501-1R40 . . . . . . . . . . . . . . . . . . . . . 10-9

10.7 ROM Verification Characteristics for C501-1R . . . . . . . . . . . . . . . . . . . . . 10-14

10.8 OTP Programming and Verification Characteristics for C501-1E . . . . . . 10-15

10.9 Package Outlines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-19

11 Index . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-1

Semiconductor Group I-3

Page 7

Introduction

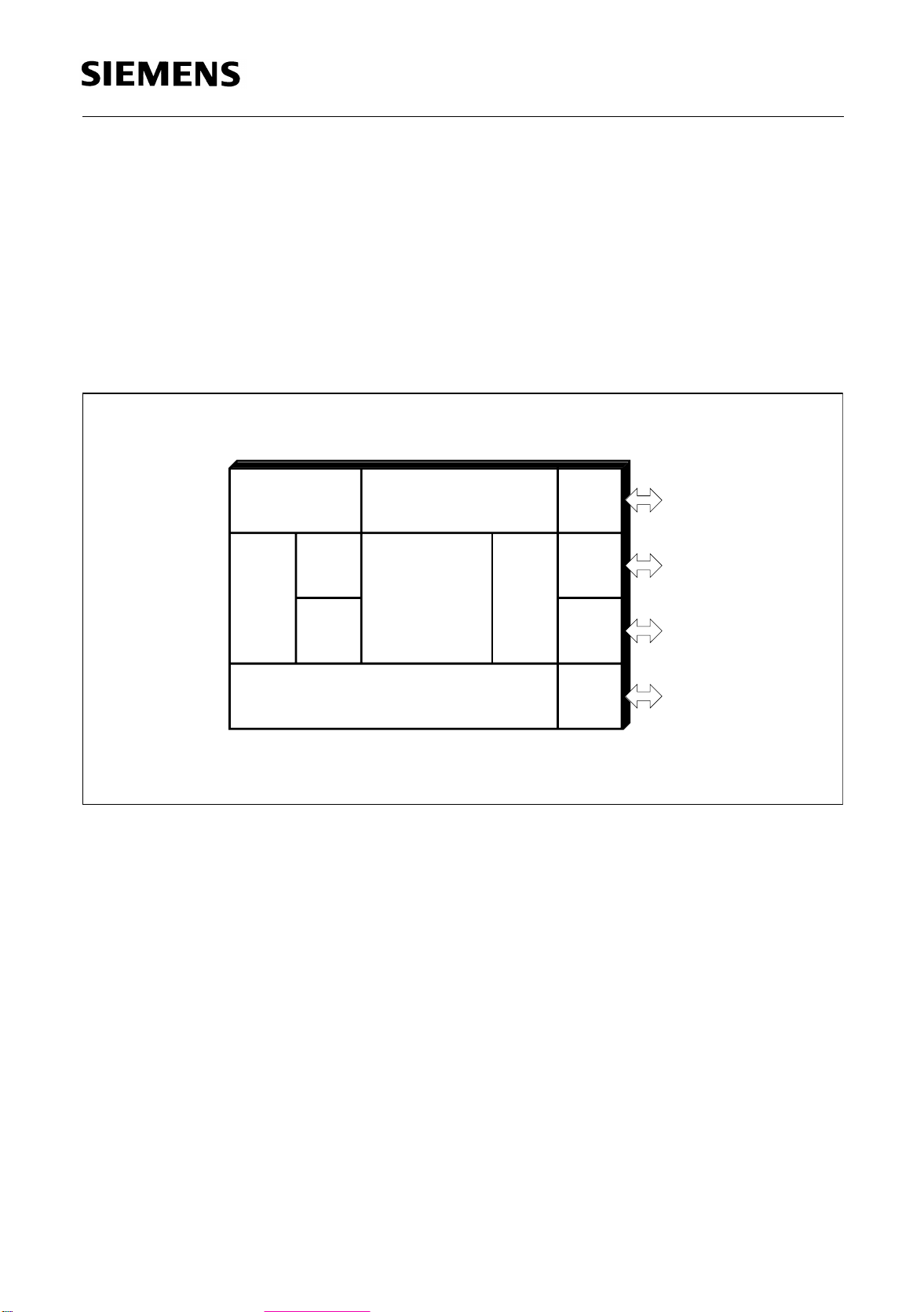

C501

1 Introduction

The C501-L, C501-1R, and C501-1E described in this document are compatible (also pincompatible) with the 80C52 and can be used in typical 80C52 applications.

The C501-1R contains a non-volatile 8K×8 read-only program memory, a volatile 256×8 read/write

data memory, four ports, three 16-bit timers/counters, a seven source, two priority level interrupt

structure and a serial port. The C501-L is identical, except that it lacks the program memory on

chip. The C501-1E contains a one-time programmable (OTP) program memory on chip. The term

C501 refers to all versions within this specification unless otherwise noted.

Power

Saving

Modes

T2

Figure 1-1

C501G Functional Units

RAM

256 x 8

T0

CPU

T1

8K x 8 ROM (C501-1R)

8K x 8 OTP (C501-1E)

USART

Port 0

Port 1

Port 2

Port 3

Ι

/O

Ι

/O

Ι

/O

Ι

/O

MCA03238

Semiconductor Group 1-1

Page 8

Listed below is a summary of the main features of the C501:

• Fully compatible to standard 8051 microcontroller

• Versions for 12/24/40 MHz operating frequency

• Program memory : completely external (C501-L)

8K × 8 ROM (C501-1R)

8K × 8 OTP memory (C501-1E)

• 256 × 8 RAM

• Four 8-bit ports

• Three 16-bit timers / counters (timer 2 with up/down counter feature)

• USART

• Six interrupt sources, two priority levels

• Power saving modes

• Quick Pulse programming algorithm (C501-1E only)

• 2-Level program memory lock (C501-1E only)

• P-DIP-40, P-LCC-44, and P-MQFP-44 package

• Temperature ranges : SAB-C501 T

SAF-C501 TA : – 40 ˚C to 85 ˚C

: 0 ˚C to 70˚C

A

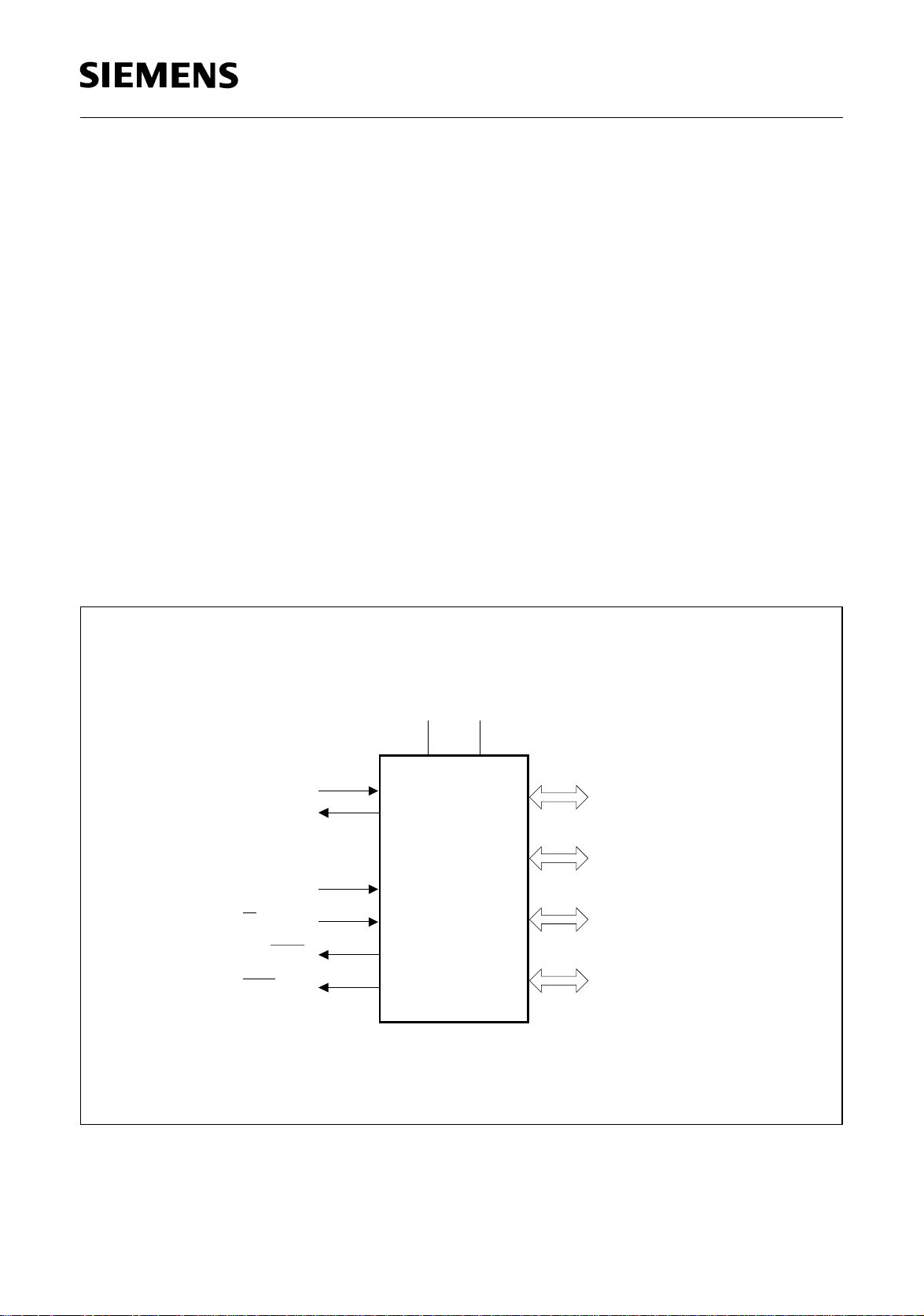

Introduction

C501

Figure 1-2

Logic Symbol

XTAL1

XTAL2

RESET

EA

/

V

PP

ALE/PROG

PSEN

VV

CC

SS

C501

MCL03217

Port 0

8-Bit Digital

Port 1

Port 2

Port 3

Ι/O

/OΙ8-Bit Digital

/OΙ8-Bit Digital

/OΙ8-Bit Digital

Semiconductor Group 1-2

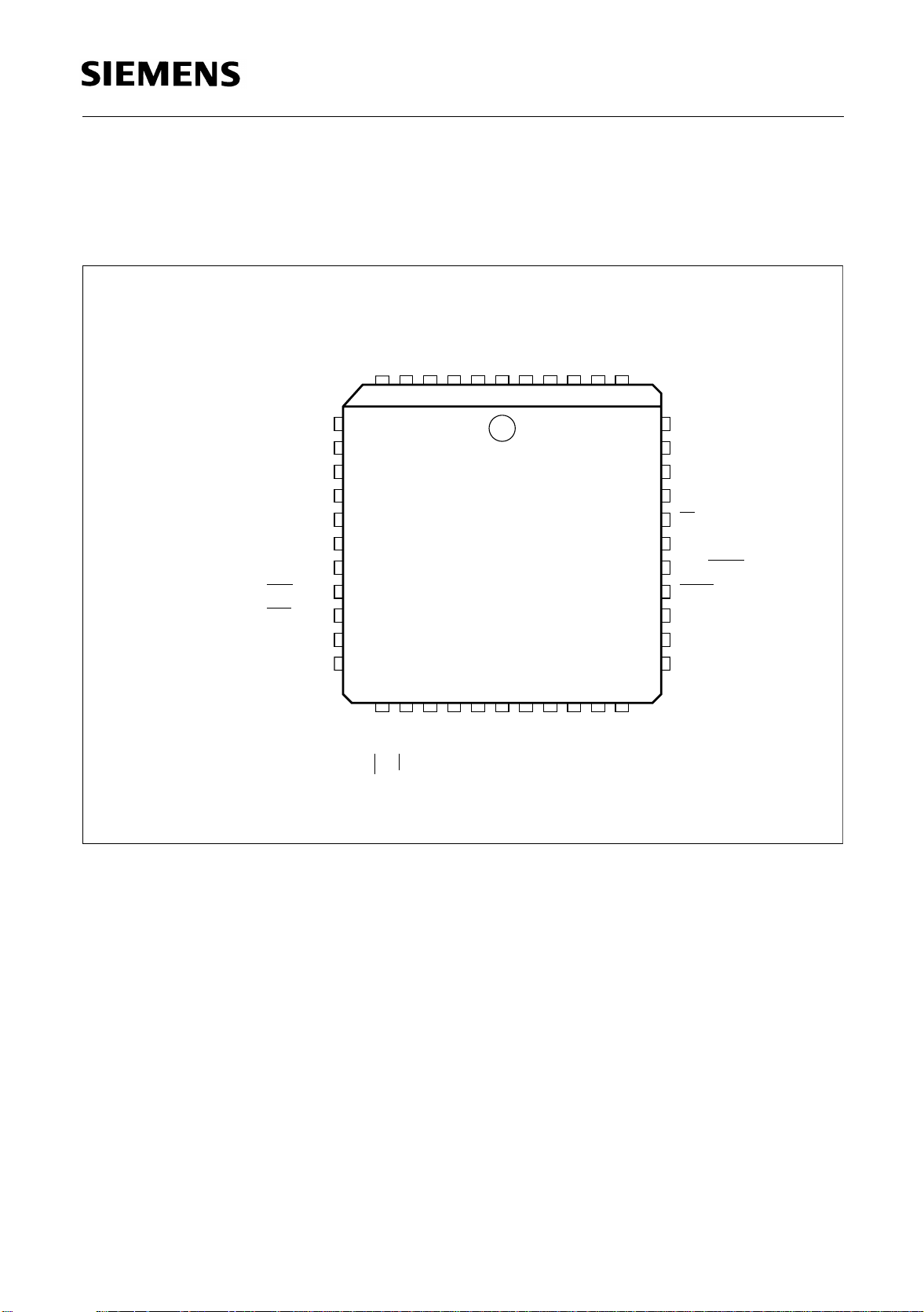

Page 9

Introduction

C501

1.1 Pin Configuration

This section shows the pin configuration of the C501 in the P-LCC-44, P-DIP-40, and P-MQFP-44

packages.

CC

P0.1/AD1

P1.3

P1.4

6 5 4 3 2 1 44 43 42 41 40

P1.5

P1.6

P1.7

RESET P0.7/AD7

RxD/P3.0

N.C.

TxD/P3.1

INT0/P3.2

INT1/P3.3

T0/P3.4

T1/P3.5

8

9

10

11

12

13

14

15

16

17

WR/P3.6

P1.2

P1.1/T2EX

XTAL1

XTAL2

RD/P3.7

N.C

P1.0/T2

C501

SS

V

N.C.

P0.0/AD0

V

P2.1/A9

P2.0/A8

P2.2/A10

P0.3/AD3

P0.2/AD2

397

38

37

36

35

34

33

32

31

30

29

2827262524232221201918

P2.3/A11

P2.4/A12

P0.4/AD4

P0.5/AD5

P0.6/AD6

EA/

V

N.C.

ALE/PROG

PSEN

P2.7/A15

P2.6/A14

P2.5/A13

MCP03214

PP

Figure 1-3

Pin Configuration P-LCC-44 Package (top view)

Semiconductor Group 1-3

Page 10

Introduction

C501

T2/P1.0

T2EX/P1.1

P1.2

P1.3

P1.4

P1.5

P1.6

P1.7

RxD/P3.0

TxD/P3.1

INT0/P3.2

1

2

3

4

5

6

7

8

9

10

11

12

C501

40

39

38

37

36

35

34

33

32

31

30

29

V

CC

P0.0/AD0

P0.1/AD1

P0.2/AD2

P0.3/AD3

P0.4/AD4

P0.5/AD5

P0.6/AD6

P0.7/AD7RESET

EA/

V

PP

ALE/PROG

PSEN

INT1/P3.3

13

14

T1/P3.5

15

16

RD/P3.7

XTAL2

XTAL1

17

18

19

20

V

SS

Figure 1-4

Pin Configuration P-DIP-40 Package (top view)

28

27

26

25

24

23

22

21

MCP03215

P2.7/A15

P2.6/A14T0/P3.4

P2.5/A13

P2.4/A12WR/P3.6

P2.3/A11

P2.2/A10

P2.1/A9

P2.0/A8

Semiconductor Group 1-4

Page 11

P0.6/AD6

P0.5/AD5

P0.4/AD4

PP

V

EA/

N.C.

P2.6/A14

P2.7/A15

PSEN

ALE/PROG

Introduction

C501

P0.3/AD3

33

P0.2/AD2

P0.1/AD1

P0.0/AD0

V

CC

N.C.

C501

P1.0/T2

P1.1/T2EX

P1.2

P1.3

P1.4 WR/P3.6

44 12

P1.5

P1.6

P1.7

RESET P0.7/AD7

RxD/P3.0

Figure 1-5

Pin Configuration P-MQFP-44 Package (top view)

N.C.

TxD/P3.1

23242526272829303132

2234

2036

1937

1838

1739

1640

1541

1442

1343

11

10987654321

T0/P3.4

INT0/P3.2

T1/P3.5 P2.5/A13

INT1/P3.3

P2.4/A12

2135

P2.3/A11

P2.2/A10

P2.1/A9

P2.0/A8

N.C.

V

SS

XTAL1

XTAL2

RD/P3.7

MCP03216

Semiconductor Group 1-5

Page 12

1.2 Pin Definitions and Functions

This section describes all external signals of the C501 with its function.

Table 1-1

Pin Definitions and Functions

Symbol Pin Number I/O*) Function

P-LCC-44 P-DIP-40 P-MQFP-44

Introduction

C501

P1.0 – P1.7 2–9

2

3

*) I = Input

O = Output

1–8

1

2

40–44,

1–3,

40

41

I/O Port 1

is a quasi-bidirectional I/O port with

internal pull-up resistors. Port 1 pins that

have 1s written to them are pulled hig h by

the internal pullup resistors, and in that

state can be used as inputs. As inputs,

port 1 pins being externally pulled l ow will

source current (

istics) because of the internal pull-up

resistors. Port 1 also contains the timer 2

pins as secondary function. The output

latch corresponding to a secondary

function must be pro-grammed to a one

(1) for that function to operate.

The secondary functions are assigned to

the pins of port 1, as follows:

P1.0 T2 Input to counter 2

P1.1 T2EX Capture - Reload trigger of

I

, in the DC character-

IL

timer 2 / Up-Down count

Semiconductor Group 1-6

Page 13

Table 1-1

Pin Definitions and Functions (cont’d)

Symbol Pin Number I/O*) Function

P-LCC-44 P-DIP-40 P-MQFP-44

Introduction

C501

P3.0 – P3.7 11,

13–19

11

13

14

15

16

17

18

19

10–17

10

11

12

13

14

15

16

17

5, 7–13

5

7

8

9

10

11

12

13

I/O Port 3

is a quasi-bidirectional I/O port with

internal pull-up resistors. Port 3 pins that

have 1s written to them are pulled hig h by

the internal pull-up resistors, and in that

state they can be used as inputs. As

inputs, port 3 pins being ext ernally pulled

low will source current (

characteristics) because of the internal

pull-up resistors. Port 3 al so contains the

interrupt, timer, serial port 0 and external

memory strobe pins which are used by

various options. The output latch

corresponding to a secondary function

must be programmed to a one (1) for that

function to operate.

The secondary functions are assigned to

the pins of port 3, as follows:

P3.0 R×D receiver data input (asyn-

P3.1 T×D transmitter data output

P3.2 INT

P3.3 INT1

P3.4 T0 counter 0 input

P3.5 T1 counter 1 input

P3.6 WR

P3.7 RD

I

, in the DC

IL

chronous) or data input

output (synchronous) of

serial interface 0

(asynchronous) or clock

output (synchronous) of

the serial interface 0

0 interrupt 0 input/timer 0

gate control

interrupt 1 input/timer 1

gate control

the write control signal latches the data byte from

port 0 into the external

data memory

the read control signal

enables the external data

memory to port 0

*) I = Input

O = Output

Semiconductor Group 1-7

Page 14

Table 1-1

Pin Definitions and Functions (cont’d)

Symbol Pin Number I/O*) Function

P-LCC-44 P-DIP-40 P-MQFP-44

XTAL2 20 18 14 – XTAL2

Output of the inverting oscillator

amplifier.

XTAL1 21 19 15 – XTAL1

Input to the inverting oscillator amplifier

and input to the internal clock generator

circuits.

To drive the device from an external

clock source, XTAL1 should be driven,

while XTAL2 is left unconnected. There

are no requirements on the duty cy cle of

the external clock signal, since the input

to the internal clocking ci rcuitry is divided

down by a divide-by-two flip-flop.

Minimum and maximum high and low

times as well as rise fall times specified

in the AC characteristics must be

observed.

Introduction

C501

P2.0 – P2.7 24–31 21–28 18–25 I/O Port 2

is a quasi-bidirectional I/O port with

internal pull-up resistors. Port 2 pins that

have 1s written to them are pulled high

by the internal pull-up resistors, and in

that state they can be used as inputs. As

inputs, port 2 pins being ext ernally pulled

low will source current (

characteristics) because of the internal

pull-up resistors. Port 2 emits the highorder address byte during fetches from

external program memory and during

accesses to external data memory that

use 16-bit addresses (MOVX @DPTR).

In this application it uses strong internal

pull-up resistors when issuing 1s. During

accesses to external data memory that

use 8-bit addresses (MOVX @Ri),

port 2 issues the contents of the P2

special function register.

*) I = Input

O = Output

I

, in the DC

IL

Semiconductor Group 1-8

Page 15

Introduction

Table 1-1

Pin Definitions and Functions (cont’d)

Symbol Pin Number I/O*) Function

P-LCC-44 P-DIP-40 P-MQFP-44

PSEN 32 29 26 O The Program Store Enable

output is a control signal that enables the

external program memory to the bus

during external fetch operations. It is

activated every six oscillator periods

except during external data memory

accesses. Remains high during internal

program execution.

RESET 10 9 4 I RESET

A high level on this pin for two machine

cycles while the oscillator is running

resets the device. An internal diffused

ALE/PROG

resistor to

using only an external capacitor to

33 30 27 I/O The Address Latch Enable

output is used for latching the low-byt e of

the address into external memory durin g

normal operation. It is activa ted every six

oscillator periods except during an

external data memory access.

For the C501-1E this pin is also the

program pulse input (PROG

memory programming.

V

permits power-on reset

SS

C501

V

.

CC

) during OTP

EA

/V

PP

*) I = Input

O = Output

35 31 29 I External Access Enable

Semiconductor Group 1-9

When held at high level, instructions are

fetched from the internal ROM (C501-1R

and C501-1E) when the PC is less than

2000H. When held at low level, the C501

fetches all instructions from external

program memory. For the C501-L this

pin must be tied low.

This pin also receives the programming

supply voltage

V

during OTP memory

PP

programming (C501-1E) only).

Page 16

Table 1-1

Pin Definitions and Functions (cont’d)

Symbol Pin Number I/O*) Function

P-LCC-44 P-DIP-40 P-MQFP-44

P0.0 – P0.7 43–36 39–32 37–30 I/O Port 0

is an 8-bit open-drain bidirectional I/O

port. Port 0 pins that have 1s written to

them float, and in that state can be used

as high-impedance inputs. Port 0 is also

the multiplexed low-order address and

data bus during accesses to external

program or data memory. In this

application it uses strong internal pull-up

resistors when issuing 1s.

Port 0 also outputs the code by tes during

program verification in the C501-1R and

C501-1E. External pull-up resistors are

required during program verification.

Introduction

C501

V

SS

V

CC

22 20 16 – Circuit ground potential

44 40 38 – Supply terminal for all operating modes

N.C. 1, 12,

23, 34

*) I = Input

O = Output

– 6, 17,

28, 39

– No connection

Semiconductor Group 1-10

Page 17

Fundamental Structure

C501

2 Fundamental Structure

The C501 is fully compatible to the standard 8051 microcontroller family.

It is compatible with the 80C32/52/82C52. While maintaining all architectural and operational

characteristics of the 8051 micr ocontroller family, the C501 incorporates some enhancements in the

timer 2 and fail save mechanism unit.

Figure 2-6 shows a block diagram of the C501.

V

CC

V

SS

XTAL1

XTAL2

RESET

ALE/PROG

PSEN

EA/

V

PP

C501

OSC & Timing

Serial Channel

CPU

Timer 0

Timer 1

Timer 2

Interrupt Unit

(USART)

RAM

256 x 8

C501-1R : ROM

C501-1E : OTP

8K x 8

Port 0

Port 1

Port 2

Port 3

Port 0

8-Bit Digit.

Port 1

8-Bit Digit.

Port 2

8-Bit Digit.

Port 3

8-Bit Digit.

Ι/O

Ι/O

Ι/O

/OΙ

Figure 2-6

Block Diagram of the C501

Semiconductor Group 2-1

MCB03219

Page 18

Fundamental Structure

C501

2.1 CPU

The C501 is efficient both as a controller and as an arithmetic processor. It has extensive facilities

for binary and BCD arithmetic and excels in its bit-handling capabilities. Efficient use of program

memory results from an instruction set consisting of 44% one-byte, 41% two-byte, and 15% threebyte instructions. With a 12 MHz crystal, 58% of the in structions execute in 1.0 µs (24 MHz : 500 ns,

40 MHz : 300 ns).

The CPU (Central Processing Unit) of the C501 consists of the instruction decoder, the arithmetic

section and the program control section. Each program instruction is decoded by the instruction

decoder. Th is unit generate s the internal si gnals controllin g the functions of the individual units

within the CPU. They have an effect on the source and destination of data transfers and control the

ALU processing.

The arithmetic section of the processor performs extensive data manipulation and is comprised of

the arithmetic/logic unit (ALU), an A register, B register and PSW register.

The ALU accepts 8-bit data words from one or two sources and generates an 8-bit result under the

control of the instruction decoder. The ALU performs the arithmetic operations add, substract,

multiply, divide, increment, decrement, BDC-decimal-add-adjust and compare, and the logic

operations AND, OR, Exclusive OR, complement and rotate (right, left or swap nibble (left four)).

Also included is a Boolean processor performing the bit operations as se t, clear, complement, jumpif-not-set, jump-if-set-and-clear and move to/from carry. Between any addressable bit (or its

complement) and the carry flag, it can perform the bit operations of logical AND or logical OR with

the result returned to the carry flag.

The program control section controls the sequence in which the instructions stored in program

memory are executed. The 16-bit program counter (PC) holds the a ddress of the next inst ruction to

be executed. The conditional branch logic enables internal and external eve nts to the pr ocess or to

cause a change in the program execution sequence.

Accumulator

ACC is the symbol for the accumulator register. The mnemonics for accumulator-specific

instructions, however, refer to the accumulator simply as A.

Program Status Word

The Program Status Word (PSW) contains several status bits that reflect the current state of the

CPU.

Semiconductor Group 2-2

Page 19

Fundamental Structure

C501

Special Function Register PSW (Address D0H) Reset Value : 00H

Bit No. MSB LSB

H

D7

CY AC

H

D6

H

D5

F0

H

D4

RS1 RS0 OV F1 PD0

Bit Function

CY Carry Flag

Used by arithmetic instruction.

AC Auxiliary Carry Flag

Used by instructions which execute BCD operations.

F0 General Purpose Flag

RS1

RS0

Register Bank select control bits

These bits are used to select one of the four register banks.

RS1 RS0 Function

0 0 Bank 0 selected, data address 00H-07

0 1 Bank 1 selected, data address 08H-0F

1 0 Bank 2 selected, data address 10H-17

1 1 Bank 3 selected, data address 18H-1F

H

D3

H

D2

H

D1

H

D0

H

PSW

H

H

H

H

OV Overflow Flag

Used by arithmetic instruction.

F1 General Purpose Flag

P Parity Flag

Set/cleared by hardware after each instruction to indicate an odd/even

number of “one” bits in the accumulator, i.e. even parity.

B Register

The B register is used during multiply and divide and serves as both source and destination. For

other instructions it can be treated as another scratch pad register.

Stack Pointer

The stack pointer (SP) register is 8 bits wide. It is incremented before data is stored during PUSH

and CALL executions and decremented after data is popped during a POP and RET (RETI)

execution, i.e. it always points to the last valid stack byte. While the stack may reside anywhere in

the on-chip RAM, the stack pointer is i nitia lize d to 07H after a reset. This causes the stack to begin

a location = 08H above register bank zero. The SP can be read or written under software control.

Semiconductor Group 2-3

Page 20

Fundamental Structure

C501

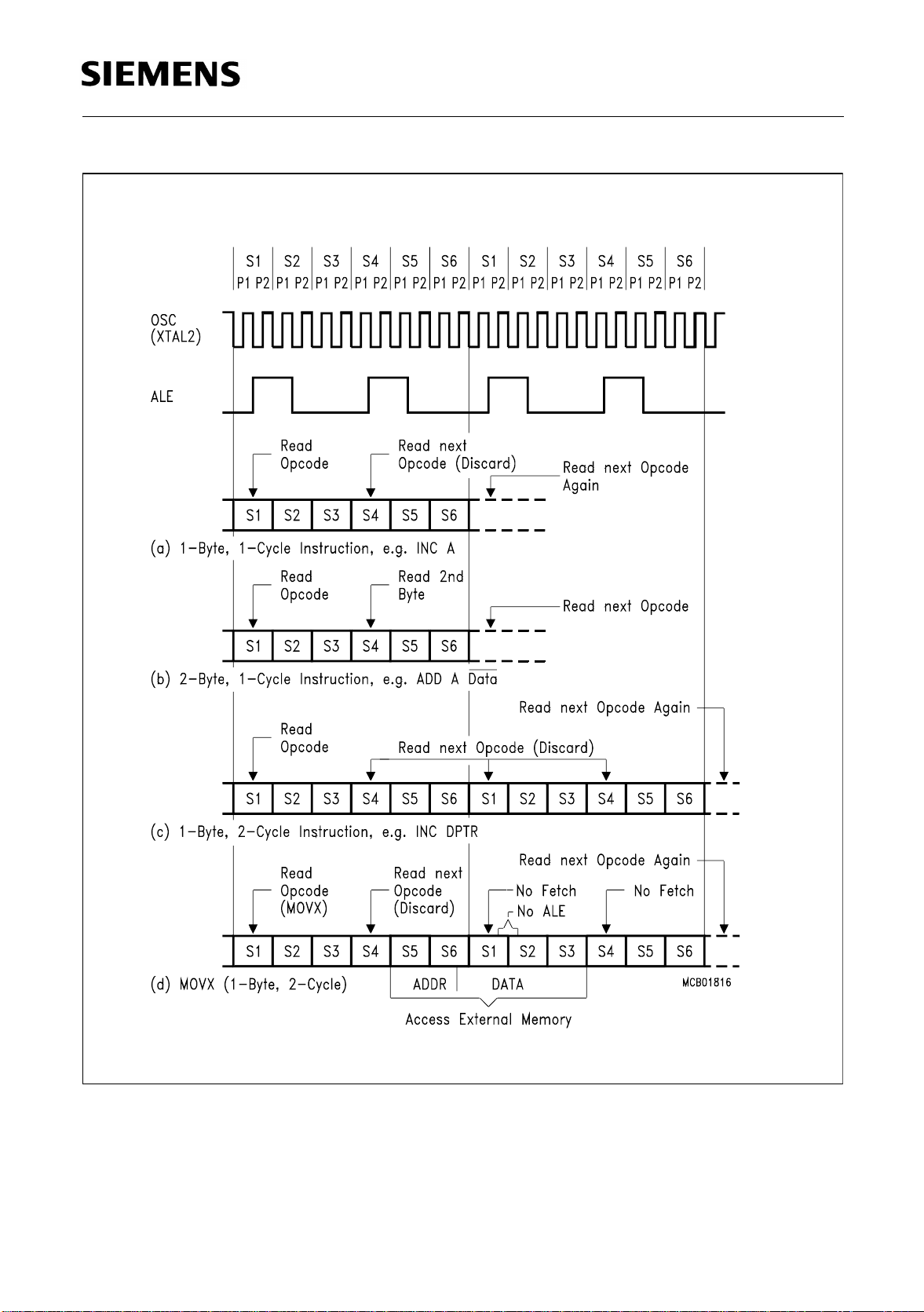

2.2 CPU Timing

A machine cycle of the C501 consists of 6 states (12 oscillator periods). Each state is devided into

a phase 1 half, during which the phase 1 clock is a ctive, and a phas e 2 half, d uring which the phase

2 clock is active. Thus, a machine cy cle cons ists of 12 osci llator peri ods, numbe rerd S1P1 (state 1,

phase 1) through S6P 2 (state 6, phase 2). Each sta te lasts for two oscillator period s. Typically,

arithmetic and logically operations take place during phase 1 and internal register-to-register

transfers take place during phase 2.

The diagrams in figure 2-7 show the fetch/execute timing related to the intern al states and phases .

Since these internal clock signals are not us er-accessible, the XTAL2 oscillato r signals and the ALE

(address latch enable) signal are s hown for external re ference. ALE is nor mally activated twice

during each machine cycle: once during S1P2 and S2P1, and again during S4P2 and S5P1.

Execution of a one-cycle instruction begins at S1P2, when the op-code is latched into the instruction

register. If it is a two-byte instruction, the second reading takes place during S4 of the same

machine cycle. If it is a one-byte instruction, there is still a fetch at S4, but the byte read (which would

be the next op-code) is ignored (discarded fetch), and the program counter is not incremented. In

any case, execution is completed at the end of S6P2.

Figures 2-7 (a) and (b) show the timing of a 1-byte, 1-cycle instruction and for a 2-byte, 1-cycle

instruction.

Most C501 instructions ar e executed in one cycle. MUL (multipl y) and DIV (divide) are the only

instructions that take more than two cycles to complete; they take four cycles. Normally two code

bytes are fetched from the program me mory during every machine cycle. The only except ion to this

is when a MOVX instruction is executed. MOVX is a one-byte, 2-cycle instruction that accesses

external data memory. During a MOVX, the two fetches in the second cycle are skipped while the

external data memory is being addressed and strobed. Figure 2-7 c) and d) show the timing for a

normal 1-byte, 2-cycle instruction and for a MOVX instruction.

Semiconductor Group 2-4

Page 21

Fundamental Structure

C501

Figure 2-7

Fetch Execute Sequence

Semiconductor Group 2-5

Page 22

Memory Organization

3 Memory Organization

The C501 CPU manipulates operands in the following four address spaces:

– up to 64 Kbyte of internal/external program memory

– up to 64 Kbyte of external data memory

– 256 bytes of internal data memory

– a 128 byte special function register area

Figure 3-1 illustrates the memory address spaces of the C501.

C501

External

Internal

"Code Space"

FFFF

2000

External

(EA = 0)(EA = 1)

H

H

1FFF

0000

FFFF

H

External

Indirect

Address

FF

H

Internal

RAM

80

H

H

0000

H

"Data Space" "Internal Data Space"

H

Internal

RAM

Direct

Address

Special

Function

Register

7F

H

00

H

MCD03224

FF

80

H

H

Figure 3-1

C501 Memory Map

Semiconductor Group 3-1

Page 23

Memory Organization

C501

3.1 Program Memory, “Code Space”

The C501-1R/-1E h as 8 Kbytes of read-only/OTP program memory, while the C501-L has no

internal program memory. The program memory can be externally expande d up to 64 Kbytes. If the

EA

pin is held high, the C501 executes out of internal program memory unl ess the address exceeds

1FFFH. Locations 2000H through FFFFH are then fetched from the external program memory. If

the EA

3.2 Data Memory, “Data Space”

The data memor y address space consists of an internal and an ext ernal memory space. The

internal data memory is divided into three physically separate and distinct blocks : the lower

128 bytes of RAM, the upper 128 bytes of RAM, and the 128 byte special function register (SFR)

area.

While the upper 128 bytes of data memory and the SFR area share the same address locations,

they are accessed through different addressing modes. The lower 128 bytes of data memory can

be accessed through direct or register indirec t addressing; the upper 128 bytes of RAM can be

accessed through register indirect addressing; the special function regis ters are accessible throug h

direct addressing. Four 8-register banks , each bank consisting of eight 8-bi t multi-purpose registers,

occupy locations 0 through 1FH in the lower RAM area. The next 16 bytes, locations 20H through

2FH, contain 128 directly addressable bit locations. The stack can be located anywhere in the

internal data memory address space, and the stack depth can be expanded up to 256 bytes.

pin is held low, the C501 fetches all instructions from the external program memory.

The external data memory can be expanded up to 64 Kbyte and can be accessed by instructions

that use a 16-bit or an 8-bit address.

3.3 General Purpose Registers

The lower 32 locations of the internal RAM are assigned to four banks with eight general purpose

registers (GPRs) each. Only one of these banks may be enabled at a time. Two bits i n the program

status word, RS0 and RS1, select the active register bank (see description of the PSW in

chapter 2). This allows fast context switching, which is useful when entering subroutines or

interrupt service routines.

The 8 general purpose regist ers of the selected register bank may be accessed by register

addressing. With register addressing the instruction op code indicates which register is to be used.

For indirect addressing R0 and R1 are used as pointer or index register to address internal or

external memory (e.g. MOV @R0).

Reset initializes the stack pointer to location 07H and increments it once to start from location 08

which is also the first register (R0) of register bank 1. Thus, if one is going to use more than one

register bank, the SP should be initialized to a different location of the RAM which is not used for

data storage.

H

Semiconductor Group 3-2

Page 24

Memory Organization

C501

3.4 Special Function Registers

All registers, except the p rogram counter an d the fou r general purpose regi ster bank s, resid e in th e

special function register area.

The 27 special function register (SFR) include pointers and registers that provide an interface

between the CPU and the other on-chip peripherals. There are also 128 directly addressable bits

within the SFR area.

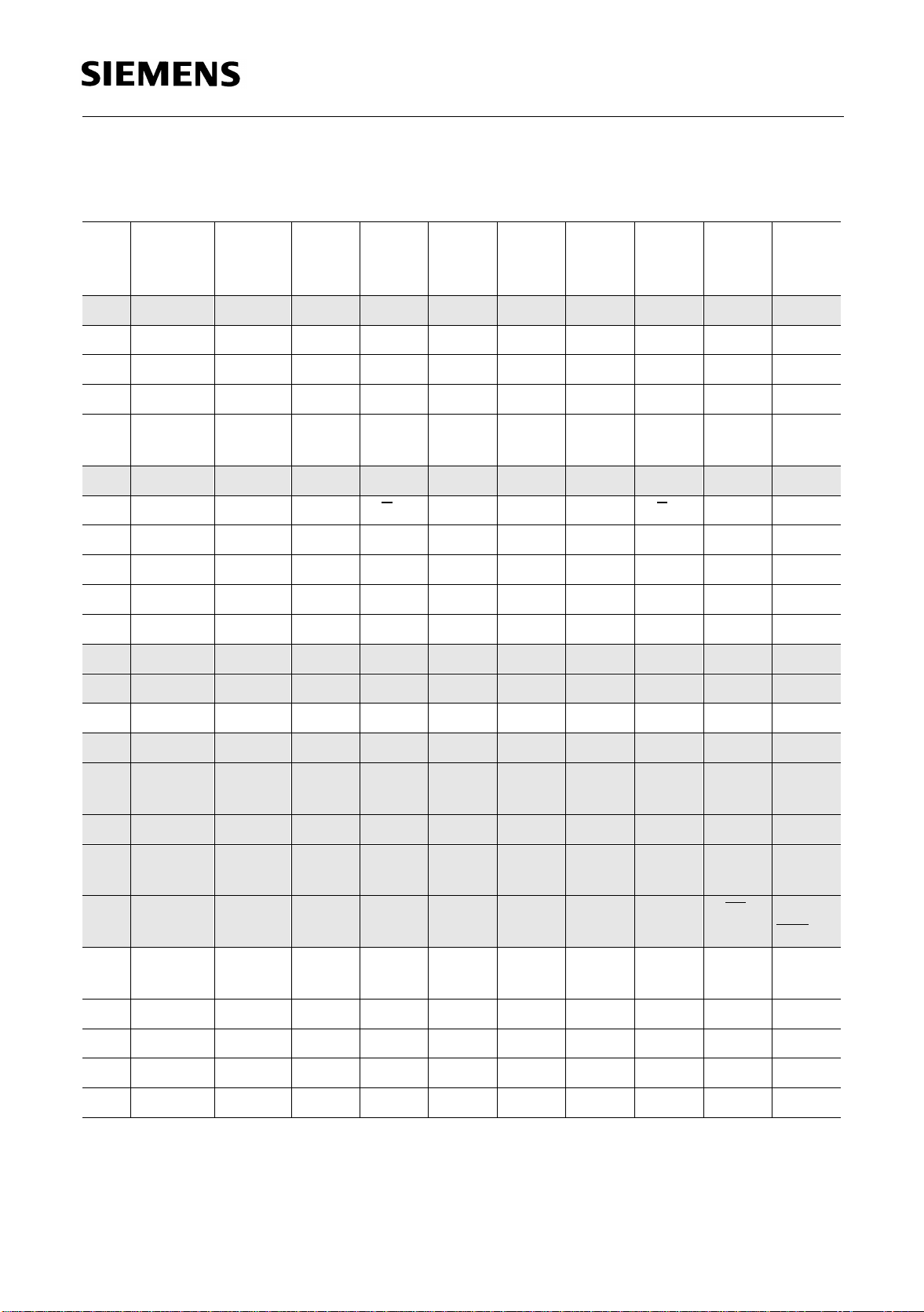

All SFRs are listed in table 3-1 and table 3-2.

In table 3-2 they are organized in groups which refer to the functional blocks of the C50 1. Table 3-3

illustrates the contents (bits) of the SFRs.

Semiconductor Group 3-3

Page 25

Memory Organization

C501

Table 3-2

Special Function Registers - Functional Blocks

Block Symbol Name Address Contents after

Reset

1)

CPU ACC

B

DPH

DPL

PSW

SP

Interrupt

System

IE

IP

Ports P0

P1

P2

P3

Serial

Channel

PCON

SBUF

SCON

Timer 0 /

Timer 1

TCON

TH0

TH1

TL0

TL1

TMOD

Timer 2 T2CON

T2MOD

RC2H

RC2L

TH2

TL2

Pow. Sav.

PCON

Modes

Accumulator

B-Register

Data Pointer, High Byte

Data Pointer, Low Byte

Program Status Word Register

Stack Pointer

Interrupt Enable Register

Interrupt Priority Register

Port 0

Port 1

Port 2

Port 3

2)

Power Control Register

Serial Channel Buffer Register

Serial Channel Control Register

Timer 0/1 Control Register

Timer 0, High Byte

Timer 1, High Byte

Timer 0, Low Byte

Timer 1, Low Byte

Timer Mode Register

Timer 2 Control Register

Timer 2 Mode Register

Timer 2 Reload/Capture Register, High Byte

Timer 2 Reload/Capture Register, Low Byt

Timer 2 High Byte

Timer 2 Low Byte

2)

Power Control Register 87

E0

F0

83

82

D0

81

A8

B8

80

90

A0

B0

87

99

98

88

8C

8D

8A

8B

89

C8

C9

CB

CA

CD

CC

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

1)

1)

1)

1)

1)

1)

1)

1)

1)

1)

1)

00

H

00

H

00

H

00

H

00

H

07

H

0X000000

XX000000

FF

H

FF

H

FF

H

FF

H

0XXX0000

3)

XX

H

00

H

00

H

00

H

00

H

00

H

00

H

00

H

00

H

XXXXXXX0

00

H

00

H

00

H

00

H

0XXX0000

3)

B

3)

B

3)

B

3)

B

3)

B

1) Bit-addressable special f unc t ion registers

2) This special function register is listed repeatedly since some bits of it also belong to other functional blocks.

3) “X“ means that the value is undef ined and the location is reserved

Semiconductor Group 3-4

Page 26

Table 3-3

Contents of the SFRs, SFRs in numeric order of their addresses

Memory Organization

C501

Addr Register Content

after

Reset

2)

80

81

82

83

87

P0 FF

H

SP 07

H

DPL 00

H

DPH 00

H

PCON 0XXX-

H

0000

2)

88

89

TCON 00

H

TMOD 00

H

8AHTL0 00

8BHTL1 00

8CHTH0 00

8DHTH1 00

2)

90

98

99

A0

A8

P1 FF

H

2)

SCON 00

H

SBUF XX

H

2)

P2 FF

H

2)

IE 0X00-

H

0000

2)

B0

B8

P3 FF

H

2)

IP XX00-

H

0000

2)

C8

T2CON 00

H

1)

H

H

H

H

B

H

H

H

H

H

H

H

H

H

H

B

H

B

H

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

.7 .6 .5 .4 .3 .2 .1 .0

.7 .6 .5 .4 .3 .2 .1 .0

.7 .6 .5 .4 .3 .2 .1 .0

.7 .6 .5 .4 .3 .2 .1 .0

SMOD – – – GF1 GF0 PDE IDLE

TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0

GATE C/T

M1 M0 GATE C/T M1 M0

.7 .6 .5 .4 .3 .2 .1 .0

.7 .6 .5 .4 .3 .2 .1 .0

.7 .6 .5 .4 .3 .2 .1 .0

.7 .6 .5 .4 .3 .2 .1 .0

.7 .6 .5 .4 .3 .2 .1 .0

SM0 SM1 SM2 REN TB8 RB8 TI RI

.7 .6 .5 .4 .3 .2 .1 .0

.7 .6 .5 .4 .3 .2 .1 .0

EA – ET2 ES ET1 EX1 ET0 EX0

RD WR T1 T0 INT1 INT0 TxD RxD

– – PT2 PS PT1 PX1 PT0 PX0

TF2 EXF2 RCLK TCLK EXEN2 TR2 C/T2 CP/

RL2

C9HT2MOD XXXX-

XXX0

CAHRC2L 00

CBHRC2H 00

CCHTL2 00

CDHTH2 00

1) X means that the value is undefine d and the location is reserved

2) Bit-addressable special fun ction registers

H

H

H

H

–––––––DCEN

B

.7 .6 .5 .4 .3 .2 .1 .0

.7 .6 .5 .4 .3 .2 .1 .0

.7 .6 .5 .4 .3 .2 .1 .0

.7 .6 .5 .4 .3 .2 .1 .0

Semiconductor Group 3-5

Page 27

Memory Organization

Table 3-3

Contents of the SFRs, SFRs in numeric order of their addresses (cont’d)

C501

Addr Register Content

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

after

H

H

H

1)

CY AC F0 RS1 RS0 OV F1 P

.7 .6 .5 .4 .3 .2 .1 .0

.7 .6 .5 .4 .3 .2 .1 .0

Reset

2)

D0

E0

F0

1) X means that the value is undefine d and the location is reserved

2) Bit-addressable special fun ction registers

PSW 00

H

2)

ACC 00

H

2)

B 00

H

Semiconductor Group 3-6

Page 28

External Bus Interface

C501

4 External Bus Interface

The C501 allows for external memory expansion. To accomplish this, the external bus interface

common to most 8051-based controllers is employed.

4.1 Accessing External Memory

It is possible to distinguish between accesses to external program memory and external data

memory or other peripheral components respectively. This distinction is made by hardware:

accesses to external program memory use the signal PSEN

strobe. Accesses to external data memory use RD

functions of P3.7 and P3.6). Port 0 and port 2 (with exceptions) are used to provide data and

address signals. In this section only the port 0 and port 2 functions relevant to external memory

accesses are described.

Fetches from external program memory always use a 16-bit address. Accesses to external data

memory can use either a 16-bit address (MOVX @DPTR) or an 8-bit address (MOVX @Ri).

and WR to strobe the memory (alternate

(program store enable) as a read

4.1.1 Role of P0 and P2 as Data/Address Bus

When used for accessing external mem ory, p ort 0 p rovide s the data byte time-m ultip lexed with th e

low byte of the address. In this state, port 0 i s disconnected from its own port l atch, and the address/

data signal drives both FETs in the port 0 output buffers. Thus, in this appli cation, the port 0 pins are

not open-drain outputs and do not require external pullup resistors.

During any access to external me mory, the CPU wri tes FFH to the port 0 latch (the speci al functio n

register), thus obliterating whatever information the port 0 SFR may have been holding.

Whenever a 16-bit address is used, the high byte of the address comes out on port 2, where it is

held for the duration of the read or write cycle. During this time, the port 2 lines are disconnected

from the port 2 latch (the special function register).

Thus the port 2 latch does not have to contain 1s, and the contents of the port 2 SFR are not

modified.

If an 8-bit address is used (MOVX @Ri), the contents of the port 2 SFR remain at the port 2 pins

throughout the external memory cycle. This will facilitate paging. It should be noted that, if a port 2

pin outputs an address bit that is a 1, strong pullups will be used for the entire read/write cy cle and

not only for two oscillator periods.

Semiconductor Group 4-1

Page 29

External Bus Interface

C501

a)

ALE

PSEN

RD

P2

P0

b)

One Machine Cycle One Machine Cycle

S1 S2 S3 S4 S5 S6 S1 S2 S3 S4 S5 S6

INST.

IN

PCL

OUT

PCL OUT

valid

PCH

OUT

INST. INST. INST. INST.

IN OUT

PCL OUT

PCH PCH

OUT

PCL PCL

PCL OUT

valid

PCH

OUTIN IN OUT

valid

One Machine CycleOne Machine Cycle

PCL OUT

(A)

without

MOVX

OUTOUT

PCL

IN

valid

ALE

PSEN

RD

PCL

OUT

PCH

OUT

ININ

DPL or Ri

valid

P2

P0

INST. INST. INST.

PCL OUT

valid

Figure 4-1

External Program Memory Execution

DPH OUT OR

P2 OUT

DATA

IN

PCH

OUT

PCL

OUT

PCL OUT

valid

S6S5S4S3S2S1S6S5S4S3S2S1

(B)

with

MOVX

IN

MCT03220

Semiconductor Group 4-2

Page 30

External Bus Interface

C501

4.1.2 Timing

The timing of the external bus interface, in particular the relationship between the control signals

ALE, PSEN

, RD, WR and information on port 0 and port 2, is illustated in figure 4-1 a) and b).

Data memory

Program memory

4.1.3 External Program Memory Access

The external program memory is accessed under two conditions:

– whenever signal EA

– whenever the program counter (PC) contains a number that is larger than 1FFFH.

This requires the ROM-less version C501-L to have EA

bytes to be fetched from external memory.

When the CPU is executing out of exte rnal pro gram memory, all 8 bits of port 2 a re dedi cated to a n

output function and may not be used for general-purpose I/O. The contents of the port 2 SFR

however is not affected. During external program memory fetches port 2 lines output the high byte

of the PC, and during accesses to external data memory they output either DPH or the port 2 SFR

(depending on whether the external data memory access is a MOVX @DPTR or a MOVX @Ri).

When the C501 executes instructions from external program memory, port 2 is at all times

dedicated to output the high-order address byte. This means t hat port 0 and port 2 of the C501 ca n

never be used as general-purpose I/O. This means that port 0 and port 2 of the C501-L can never

be used as general-purpose I/O. This also applies to the C501-1R/1E when they are operating with

external program memory only.

: in a write cycle, the data byte to be written appears on port 0 just before WR is

activated and remains there until after WR

incoming byte is accepted at port 0 before the read strobe is deactivated.

: Signal PSEN functions as a read strobe.

is active (low) or

wired low to allow the lower 8 K program

is deactivated. In a read cycle, the

Semiconductor Group 4-3

Page 31

4.2 PSEN, Program Store Enable

External Bus Interface

C501

The read strobe for external fetches is PSEN

CPU is accessing external program memory, PSEN

MOVX instruction) no matter whether or not the byte fetched is actually needed for the current

instruction. When PSEN

including activation and deactivation of ALE and RD

cycle, including activation and deactivation of ALE and PSEN takes 3 oscillator periods. The

execution sequence for these two types of read cycles is shown in figure 4-1 a) and b).

4.3 ALE, Address Latch Enable

The main function of ALE is to provide a properly timed signal to latch the low byte of an address

from P0 into an external latch during fetches from external memory. The ad dress byte is valid at the

negative transition of ALE. For that purpose, ALE is activated twice every machine cycle. This

activation takes place even if the cycle involves no external fetch. The only time no ALE pulse

comes out is during an access to external data memory when RD

ALE of the second cycle of a MOVX instruction is missing (see figure 4-1 b). Consequently, in any

system that does not use data memory, ALE is activated at a constant rate of 1/6 of the oscillator

frequency and can be used for external clocking or timing purposes.

4.4 Overlapping External Data and Program Memory Spaces

In some applications it is desirable to execute a program from the same physical memory that is

used for storing data. In the C501 the e xternal p rogram and data memory spaces can be co mbined

by AND-ing PSEN

strobe that can be used for the combined physical memory. Since the PSEN

RD

cycle, the external memory needs to be fast enough to adapt to the PSEN cycle.

and RD. A positive logic AND of these two signals produces an active low read

is activated its timing is not the same as for RD. A complete RD cycle,

. PSEN is not activated for internal fetches. When the

is activated twice every cycle (except during a

, takes 6 oscillator periods. A complete PSEN

/WR signals are active. The first

cycle is faster than th e

Semiconductor Group 4-4

Page 32

External Bus Interface

C501

4.5 Enhanced Hooks Emulation Concept

The Enhanced Hooks Emulation Concept of the C500 microcontroller family is a new, innovative

way to control the execution of C500 MCUs and to gain extensive information on the internal

operation of the controllers. Emulation of on-chip ROM base d programs is possible, too (not true for

the C509-l, because it lacks internal program memory).

Each production chip has built-in logic for the supprt of the Enhanced Hooks Emulation Concept.

Therefore, no costly bond-out chips are necessary for emulation. This also ensure that emulation

and production chips are identical.

1)

The Enhanced Hooks Technology

together with an EH-IC to function similar to a bond-o ut chip. This simplifies th e design and reduces

costs of an ICE-system. ICE-systems using an EH-IC and a compatible C500 are able to emulate

all operating modes of the different versions of the C500 microcontrollers. This includes emulation

of ROM, ROM with code rollover and ROMless modes of operation. It is also able to operate in

single step mode and to read the SFRs after a break.

TM

, which requires embedded logic in the C500 allows the C500

SYSCON

PCON

TCON

RESET

EA

ALE

PSEN

RSYSCON

RPCON

RTCON

C500

MCU Interface Circuit

Optional

I/O Ports

Figure 4-2

Basic C500 MCU Enhanced Hooks Concept Configuration

Port 3 Port 1

Port 0

Port 2

Target System Interface

ICE-System Interface

to Emulation Hardware

EH-IC

Enhanced Hooks

RPort 0RPort 2

TEA TALE TPSEN

MCS02647

Port 0, port 2 and some of the control lines of the C500 based MCU are used by Enhanced Hooks

Emulation Concept to control the operation of the device during emulation and to transfer

informations about the programm execution and data transfer between the external emulation

hardware (ICE-system) and the C500 MCU.

1

“Enhanced Hooks Techno logy ” is a tra dem ark and patent of Metalink Corporation licensed to Siemens.

Semiconductor Group 4-5

Page 33

System Reset

C501

5 System Reset

5.1 Hardware Reset

The hardware reset function incorporated in the C501 allows for an easy automatic start-up at a

minimum of additional hardware and forces the controller to a predefined default state. The

hardware reset function can also be used during no rmal operation in order to restart the device. This

is particularly done when the power-down mode is to be terminated.

The RESET input is an active high input. An internal Schmitt trigger is used at the input for noise

rejection. Since the reset is synchronized internally, the RESET pin must be held high for at least

two machine cycles (24 osci llator perio ds) while th e oscil lator is running. With the osci llator runnin g

the internal reset is executed during the second machine cycle and is repeated every cycle until

RESET goes low again.

During reset, pins ALE and PSEN

are configured as inputs and should not be stimulated exte rnally.

An external stimulation at these lines during reset activates several test modes which are reserved

for test purposes. This in turn may cause unpredictable output operations at several port pins.

A pullup resistor is internally connected to

only. An automatic reset can be obtained when

V

to allow a power-up reset with an external capacitor

CC

V

is applied by connecting the RESET pin to V

CC

SS

via a capacitor. After VCC has been turned on, the capacitor must hold the voltage level at the

RESET pin for a specific time to effect a complete reset.

A correct reset leaves the processor in a defined state. The program execution starts at location

0000H. After reset is internally accomplished the port latches of ports 0, 1, 2 and 3 default in FFH.

This leaves port 0 floating, since it is an open drain port when not used as data/address bus. All

other I/O port lines (ports 1, 2 and 3) output at one (1).

The content of the internal RAM of the C501 is not affected by a reset. After power-up the content

is undefined, while it remains unchanged during a reset if the power supply is not turned off.

Semiconductor Group 5-1

Page 34

System Reset

C501

5.2 Hardware Reset Timing

This section describes the timing of the hardware reset signal.

The input pin RESET is sampled once during each machine c ycle. This happens in state 5 phase 2.

Thus, the external reset signal is synchronized to the internal CPU timing. When the reset is found

active (high level) the internal reset procedure is started. It needs two complete machine cycles to

put the complete device to its correct reset state, i.e. all special function registers contain their

default values, the port latches contain 1’s etc. The RESET signal must be active for at least two

machine cycles; after this time the C501 remains in its reset state as long as the signal is active.

When the signal goes inactive this transition is recognized in the following state 5 phase 2 of the

machine cycle. Then the proc essor sta rts its a ddress outp ut (when confi gured for ext ernal ROM) i n

the following state 5 phase 1. One phase later (state 5 phase 2) the first falling edge at pin ALE

occurs.

Figure 5-3 shows this timing for a configuration with EA = 0 (external program memory). Thus,

between the release of the RESET signal and the first falling edge at ALE there is a time period of

at least one machine cycle but less than two machine cycles.

S4 S5 S6 S1 S2 S3 S4 S5 S6 S1 S2 S3 S4 S5 S6 S1 S2

P1 P2

RESET

P0

P2

ALE

Figure 5-3

CPU Timing after Reset

One Machine Cycle

PCL

OUT

PCH

OUT

Inst.

PCL

in OUT

MCT02092

PCH

OUT

Semiconductor Group 5-2

Page 35

On-Chip Peripheral Components

C501

6 On-Chip Peripheral Components

I/O Ports

The C501 has four 8-bit I/O portst. Port 0 is an open-drain bidirectional I/O port, while ports 1 to 3

are quasi-bidirectional I/O ports with internal pullup resistors. That means, when configured as

inputs, ports 1 to 3 will be pulled high and wil l s ource current when extern ally pull ed l ow. Po rt 0 will

float when configured as input.

The output drivers of port 0 and 2 and the input buffers of po rt 0 are also used for acc essing external

memory. In this application, port 0 outputs the low byte of the external memory address, time

multiplexed with the byte being written or read. Port 2 outputs the hi gh byte of the e xternal memory

address when the address is 16 bits wide. Otherwis e, th e port 2 pins continue emitting the P2 SFR

contents. In this function, port 0 is not an open-drain port, but uses a strong internal pullup FET.

6.1 Parallel I/O

6.1.1 Port Structures

Digital I/O

The C501 allows for digital I/O on 32 lines grouped into 4 bidirectional 8-bit por ts. Each port bit

consists of a latch, an output driver and an input buffer. Read and write accesses to the I/O ports

P0 through P3 are performed via their corresponding special function registers P0 to P3.

Semiconductor Group 6-1

Page 36

On-Chip Peripheral Components

C501

Figure 6-1 shows a functional diagram of a ty pical bit latch and I/O buffer, which i s the core of eac h

of the 4 I/O-ports. The bit latch (one bit in the port’s SFR) is represented as a ty pe-D flip-flop, which

will clock in a value from the internal bus in res pons e to a “write-to-la tch” si gnal f rom the CPU. Th e

Q output of the flip-flop is placed on the internal bus in response to a “read-latch” signal from the

CPU. The level of the port pin itself is placed on the internal bus in response to a “read-pin” signal

from the CPU. Some instructions that read from a port (i.e. from the corresponding port SFR P0 to

P3) activate the “read-latch” signal, while others activate the “read-pin” signal.

Read

Latch

Int. Bus

Write

to

Latch

Read

Pin

Figure 6-4

Basic Structure of a Port Circuitry

D

CLK

Port

Latch

Q

Port

Q

Driver

Circuit

MCS01822

Port

Pin

Semiconductor Group 6-2

Page 37

On-Chip Peripheral Components

C501

Port 1, 2 and 3 output drivers have internal pullup FET’s (see figure 6-5). Each I/O line ca n be used

independently as an input or output. To be used as an input, the port bit stored in the bit latch must

contain a one (1) (that means for figure 6-5: Q=0), which turns off the output driver FET n1. Then,

for ports 1, 2 and 3, the pin is pulled hig h by the internal pul lups, but can be pul led low by an external

source. When externally pulled low the port pins source current (

ports are sometimes called “quasi-bidirectional”.

I

or ITL). For this reason these

IL

Read

Latch

Int. Bus

Write

to

Latch

Read

Pin

D

Bit

Latch

CLK

Figure 6-5

Basic Output Driver Circuit of Ports 1, 2, and 3

V

CC

Internal

Pull Up

Arrangement

Q

Q

n1

MCS01823

Pin

Semiconductor Group 6-3

Page 38

On-Chip Peripheral Components

C501

In fact, the pullups mentioned before and inclu ded in figure 6-5 are pullup arrangemen ts as shown

in figure 6-6. One n-channel pulldown FET and three pullup FETs are used:

V

CC

Port

Pin

MCS03230

Q

Input Data

(Read Pin)

=1

Delay = 1 State

_

<

1

p1 p2 p3

n1

V

SS

=1=1

Figure 6-6

Output Driver Circuit of Ports 1 to 5 and 7

–The pulldown FET n1 is of n-channel type. It is a very stron g driver transistor which is capabl e

of sinking high currents (

circuit to

V

must be avoided if the transisto r is turned on, since the high current might destroy

CC

I

); it is only activated if a “0” i s progra mmed to the port pin. A short

OL

the FET. This also means that no ”0“ must be programmed into the latch of a pin that is used

as input.

–The pullup FET p1 is of p-channel type. It is activated for two oscillator periods (S1P1 and

S1P2) if a 0-to-1 transition is programmed to the port pin, i.e. a “1” is programmed to the port

latch which contained a “0”. The extra pullup can drive a similar current as the pulldown FET

n1. This provides a fast transition of the logic levels at the pin.

–The pullup FET p2 is of p-channel type. It is always activated when a “1” is in the port latch,

thus providing the logic high outpu t lev el. Thi s p ullup FET sourc es a muc h lower c urrent tha n

p1; therefore the pin may also be tied to ground, e.g. when used as input with logic low input

level.

– The pullup FET p3 is of p-channel type. It is only activated if the voltage at the port pin is

higher than approximately 1.0 to 1.5 V. This provides an additional pullup current if a logic

high level shall be output at the pin (and the voltage is not forced lower than approximately

1.0 to 1.5 V). However, this transistor is turned off if the pin is driven to a logic low level, e.g

when used as input. In this configuration only the weak pullup FET p2 i s active, which s ources

the curr ent

(

I

). Thus, an additional power consumption can be avoided if port pins are used as inputs

TL

I

. If, in addition, the pullup FET p3 is activated, a higher current can be sourced

IL

with a low level applied. However, the driving capability is stronger if a logic high level is

output.

Semiconductor Group 6-4

Page 39

On-Chip Peripheral Components

C501

The described activating and deactivating of t he four different transistors results i n four states which

can be:

– input low state (IL), p2 active only

– input high state (IH) = steady output high state (SOH), p2 and p3 active

– forced output high state (FOH), p1, p2 and p3 active

– output low state (OL), n1 active

If a pin is used as input and a low level is applied, it will be in IL state, if a high level is applied, it

will switch to IH state. If the latch is loaded with “0”, the pin will be in OL state. If the latch holds a

“0” and is loaded with “1”, the pin will enter FOH state for two cycles a nd then s witch to SOH state.

If the latch holds a “1” and is reloaded with a “1” no state change will occur.

At the beginning of power-on reset the pins will be in IL state (latch is set to “1”, voltage level on

pin is below of the trip point of p3). Depending on the volta ge level and load applied to the pin, it will

remain in this state or will switch to IH (=SOH) state.

If it is is used as output, the weak pul l-up p2 will pull the voltage level at t he pin above p3’s tri p point

after some time and p3 will turn on and provide a strong “1”. Note, however, that if the load exceeds

the drive capability of p2 (

first 0-to-1 transition on the latch occurs. Until this the output level might stay below the trip point of

the external circuitry.

I

), the pin might remain in the IL state and provide a week “1” until the

IL

The same is true if a pin is used as bidirectional line a nd the external

circuitry is switched from

output to input when the pin is held at “0” and the load then exceeds the p2 drive capabilities.

I

If the load exceeds

the pin can be forced to “1” by writing a “0” followed by a “1” to the port pin.

IL

Semiconductor Group 6-5

Page 40

On-Chip Peripheral Components

C501

Port 0, in contrast to ports 1, 2 and 3, is considered as “true” bidirectional, because the port 0 pins

float when configured as inputs. Thus, this port differs in not having internal pullups. The pullup FET

in the P0 output driver (see figure 6-7) is used only when the port is emitting 1 s during the external

memory accesses. Otherwise, the pullup is always off. Consequently, P0 lines that are used as

output port lines are open drain lines. Writing a “1” to the port latch leaves both output FETs off and

the pin floats. In that condition it can be used as high-impedance input. If port 0 is configured as

general I/O port and has to emit logic high-level (1), external pullups are required.

Read

Latch

Int. Bus

Write

to

Latch

Read

Pin

Figure 6-7

Port 0 Circuitry

D

CLK

Bit

Latch

Addr./Data

Control

&

=1

Q

Q

MUX

V

CC

MCS02122

Port

Pin

Semiconductor Group 6-6

Page 41

On-Chip Peripheral Components

C501

6.1.1.1 Port 0 and Port 2 used as Address/Data Bus

As shown in figure 6-7 and below in figure 6-8, the output drivers of ports 0 and 2 can be switched

to an internal address or address/data bus for use in ex ternal memory acce sses. In this applicatio n

they cannot be used as general purpose I/O, even if not all address lines are used externally. The

switching is done by an internal control sign al dependent on the input level at the EA

contents of the program counter. If the ports are configured as an address/data bus, the port latches

are disconnected from the driver circuit. During this tim e, the P2 SFR remains unchanged while th e

P0 SFR has 1’s written to it . Being an address/data bus, port 0 uses a pullup FET as shown in

figure 6-7. When a 16-bit address is used, port 2 uses the additional strong pullups p1 to emit 1’s

for the entire external memory cycle instead of the weak ones (p2 and p 3) used during normal port

activity.

Read

Latch

Addr.

Control

V

CC

pin and/or the

Int. Bus

Write to

Latch

Read

Pin

Figure 6-8

Port 2 Circuitry

D

CLK

Bit

Latch

Internal

Pull Up

Arrangement

Q

MUX

Q

=1

MCS02123

Port

Pin

Semiconductor Group 6-7

Page 42

On-Chip Peripheral Components

C501

6.1.2 Alternate Functions

The pins of ports 1 and 3 are multifunction al. They are port pins and also serv e to implement special

features as listed in table 6-4.

Figure 6-9 shows a functional diagram of a port latch with alternate function. To pass the alternate

function to the output pin and vice versa, however, the gate between the latch and driver circuit must

be open. Thus, to use the alternate input or o utput fun ction s, the corresp onding bit l atch i n the p ort

SFR has to contain a one (1); otherwise the pulldown FET is on and the port pin is stuck at 0 . After

reset all port latches contain ones (1).

Read

Latch

Int. Bus

Write

to

Latch

Read

Pin

D

CLK

Bit

Latch

Q

Q

Alternate

Input

Function

Alternate

Output

Function

V

CC

Internal

Pull Up

Arrangement

Pin

&

MCS01827

Figure 6-9

Circuitry of Ports 1 and 3

Semiconductor Group 6-8

Page 43

On-Chip Peripheral Components

Ports 1 and 3 are provided for several alternate functions, as listed in table 6-4:

Table 6-4

Alternate Functions of Port 1 and 3

Port Pin Alternate Function

C501

P1.0

P1.1

P3.0

P3.1

P3.2

P3.3

P3.4

P3.5

P3.6

P3.7

T2

T2EX

RxD

TxD

INT0

INT1

T0

T1

WR

RD

Input to counter 2

Capture-reload trigger of timer 2 / up down count

Serial port’s receiver data input (asynchronous) or data input/output

(synchronous)

Serial port’s transmitter data output (asynchronous) or data clock output

(synchronous)

External interrupt 0 input, timer 0 gate control

External interrupt 1 input, timer 1 gate control

Timer 0 external counter input

Timer 1 external counter input

External data memory write strobe

External data momory read strobe

Semiconductor Group 6-9

Page 44

On-Chip Peripheral Components

C501

6.1.3 Port Handling

6.1.3.1 Port Timing

When executing an instruction that changes the value of a port latch, the new value arrives at the

latch during S6P2 of the final cycle of the instruction. However, port latches are only sampled by

their output buffers during phase 1 of any clock period (during phase 2 the output buffer holds the

value it noticed during the previous phase 1). Consequently, the new value in the port latch will n ot

appear at the output pin until the next phase 1, which will be at S1P1 of the next machine cycle.

When an instruction reads a val ue from a p ort pin (e.g. MOV A, P1 ) the port pi n is actuall y sample d

in state 5 phase 1 or phase 2 depending on port and alternate functions. Figure 6-10 illustrates this

port timing. lt must be noted that this mechanism of sampling once per machine cycle is also used

if a port pin is to detect an “edge”, e.g. when us ed as counter input. In this case an “edg e” is detected

when the sampled value differs from the value that was sampled the cycle before. Therefore, there

must be met certain requirements on the pulse le ngth of signals in order to a void signal “edges” not

being detected. The minimum time period of high and low level is one machine cycle, which

guarantees that this logic level is noticed by the port at least once.

Figure 6-10

Port Timing

XTAL2

Input sampled:

e.g. MOV A, P1

Port

S4 S5

P1 P2

Old Data

S6

P2P1

P2P1

S1

S2

P2P1

P2P1

P1 active for 1 State

(driver transistor)

New Data

S3

P2P1

MCT03231

Semiconductor Group 6-10

Page 45

On-Chip Peripheral Components

C501

6.1.3.2 Port Loading and Interfacing

The output buffers of ports 1, 2 and 3 can drive TTL inputs directly. The maximum port load which

still guarantees correct logic output levels can be looked up in the C501 DC characteristics in

chapter 10. The corresponding parameters are

The same applies to port 0 output buffers. They do, however, require external pullups to drive

floating inputs, except when being used as the address/data bus.

When used as inputs it must be noted that the ports 1, 2 and 3 are not floating but have internal

pullup transistors. The driving devices must be capable of sinking a sufficient current if a logic low

level shall be applied to the port pin (the parameters

specify these currents). Port 0 has floating inputs when used for digital input.

6.1.3.3 Read-Modify-Write Feature of Ports 1,2 and 3

Some port-reading instructions read the latch and othe rs read the pin. The i nstruc tions reading the

latch rather than the pin read a val ue, pos sib ly change it, and then rewrite it to the latch. These are

called “read-modify-write”- instructions, which are lis ted i n table 6-5. If t he de stinat ion is a port or a

port pin, these instructions read the latch rather than the pin. Note that all other instructions which

can be used to read a port, exclusively read the port pin. In any case, reading from latch or pin,

respectively, is performed by reading the SFR P0, P1, P2 and P3; for example, “MOV A, P3” reads

the value from port 3 pins, while “ANL P3, #0AAH” reads from the latch, modifies the value and

writes it back to the latch.

V

and VOH.

OL

I

and IIL in the C501 DC characteristics

TL

It is not obvious that the last three instructions in table 6-5 are read-modify-write instructions, but

they are. The reason is that they read the port byte, all 8 bits, modify the addressed bit, then write

the complete byte back to the latch.

Semiconductor Group 6-11

Page 46

On-Chip Peripheral Components

Table 6-5

Read-Modify-Write"- Instructions

Instruction Function

ANL Logic AND; e.g. ANL P1, A

ORL Logic OR; e.g. ORL P2, A

XRL Logic exclusive OR; e.g. XRL P3, A

JBC Jump if bit is set and clear bit; e.g. JBC P1.1, LABEL

CPL Complement bit; e.g. CPL P3.0

INC Increment byte; e.g. INC P1

DEC Decrement byte; e.g. DEC P1

DJNZ Decrement and jump if not zero; e.g. DJNZ P3, LABEL

MOV Px.y,C Move carry bit to bit y of port x

C501

CLR Px.y Clear bit y of port x

SETB Px.y Set bit y of port x

The reason why read-modify-write instructions a re directed to the latch rather than the pin is to avoid

a possible misinterpretation of the voltage level at the pin. For exam ple, a port bit might be use d to

drive the base of a transistor. When a “1” is written to the bi t, the transi stor is turned on. If th e CPU

then reads the same por t bit at the pin rather than the la tch, it will read the base voltage of the

transistor (approx. 0.7 V, i.e. a logic low level!) and interpret it as “0”. For example, when modi fying