C167Derivatives

16-Bit CMOS Single-Chip Microcontrollers

User's Manual 03.96 Version 2.0

http://www.siemens.de/

Semiconductor/

C167

Revision History: Version 2.0 (03.96)

Previous Version: Version 1.0 (08.94)

Preliminary User’s Manual Revision 1.0 (07.92)

Page

(in previous

Version)

Page

Subjects (major changes since last revision)

(in current

Version)

– Extension of document scope to C167CR, C167SR, C167S

– Correction of the items published in the paper "Corrections C167"

Edition 03.96

This edition was realized using the software system FrameMaker

Published by Siemens AG,

Bereich Halbleiter, Marketing-

Kommunikation, Balanstraße 73,

81541 München

©

Siemens AG 1996.

All Rights Reserved.

Attention please!

As far as patents or other rights of third parties are conc erned, liability is only assumed for components, not for app lic ations, processes

and circuits implemented within components or assemblies.

The information describes the type of component and shall not be conside red as as sured characteristics.

Terms of delivery and rights to change design res erved.

For questions on technology, delivery and prices please contact the Semiconductor Group Offices in Germany or the Siemens Companies

and Representatives worldwide (see address list).

Due to technical requirements components m ay contain dangerous substances. For information on the types in question please contact

your nearest Siemens Office, Sem iconductor Group.

Siemens AG is an approved CECC manufacturer.

Packing

Please use the recycling operators know n to you. We can also help you – get in touch with your near est sales office. By agreement we

will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

Components used in life-support devices or systems must be expressly authorized for such purpose!

Critical components

written approval of the Semiconductor Group of Siemens AG.

1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the

failure of that life-support device or system, or to affect its safet y or ef fectiv eness of that device or system.

2 Life support devices or systems are intended (a) to be implante d in the human body, or (b) to su pport and/o r maintain a nd sustain hu-

man life. If they fail, it is reasonable to assume that the health of the user may be endangered.

1

of the Semiconductor Group of Siemens AG, may only be used in life-support devices or systems2 with the express

.

C167

Table of Contents Page

1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

1.1 The Members of the 16-bit Microcontroller Family . . . . . . . . . . . . . . . . . . . . 1-2

1.2 Summary of Basic Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

1.3 Abbreviations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-7

2 Architectural Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

2.1 Basic CPU Concepts and Optimizations . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-2

2.1.1 High Instruction Bandwidth / Fast Execution . . . . . . . . . . . . . . . . . . . . . . . . 2-3

2.1.2 Programmable Multiple Priority Interrupt System . . . . . . . . . . . . . . . . . . . . . 2-6

2.2 The On-chip System Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

2.3 The On-chip Peripheral Blocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-11

2.4 Protected Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-17

3 Memory Organization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

3.1 Internal ROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

3.2 Internal RAM and SFR Area . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-4

3.3 The On-Chip XRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-9

3.4 External Memory Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-11

3.5 Crossing Memory Boundaries . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-12

4 The Central Processing Unit (CPU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

4.1 Instruction Pipelining . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

4.1.1 Particular Pipeline Effects . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-6

4.2 Bit-Handling and Bit-Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-9

4.3 Instruction State Times . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-10

4.4 CPU Special Function Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-11

5 Interrupt and Trap Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

5.1 Interrupt System Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

5.1.1 Interrupt Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6

5.2 Operation of the PEC Channels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-11

5.3 Prioritization of Interrupt and PEC Service Requests . . . . . . . . . . . . . . . . 5-14

5.4 Saving the Status during Interrupt Service . . . . . . . . . . . . . . . . . . . . . . . . . 5-15

5.5 Interrupt Response Times . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-17

5.5.1 PEC Response Times . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-19

5.6 External Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-21

5.7 Trap Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-24

6 Parallel Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

6.1 PORT0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5

6.1.1 Alternate Functions of PORT0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-6

6.2 PORT1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-8

6.2.1 Alternate Functions of PORT1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-9

6.3 Port 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-11

6.3.1 Alternate Functions of Port 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-12

Semiconductor Group I-1

C167

Table of Contents Page

6.4 Port 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-15

6.4.1 Alternate Functions of Port 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-16

6.5 Port 4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-20

6.5.1 Alternate Functions of Port 4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-20

6.6 Port 5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-23

6.6.1 Alternate Functions of Port 5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-23

6.7 Port 6 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-25

6.7.1 Alternate Functions of Port 6 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-26

6.8 Port 7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-30

6.8.1 Alternate Functions of Port 7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-31

6.9 Port 8 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-34

6.9.1 Alternate Functions of Port 8 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-35

7 Dedicated Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-1

8 The External Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-1

8.1 External Bus Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-2

8.2 Programmable Bus Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-10

8.3 READY Controlled Bus Cycles . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-15

8.4 Controlling the External Bus Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-16

8.5 EBC Idle State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-24

8.6 External Bus Arbitration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-25

8.7 The XBUS Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-29

9 The General Purpose Timer Units . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-1

9.1 Timer Block GPT1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-1

9.1.1 GPT1 Core Timer T3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-3

9.1.2 GPT1 Auxiliary Timers T2 and T4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-8

9.1.3 Interrupt Control for GPT1 Timers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-15

9.2 Timer Block GPT2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-16

9.2.1 GPT2 Core Timer T6 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-18

9.2.2 GPT2 Auxiliary Timer T5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-23

9.2.3 Interrupt Control for GPT2 Timers and CAPREL . . . . . . . . . . . . . . . . . . . . 9-31

10 The Asynchronous/Synchronous Serial Interface . . . . . . . . . . . . . . . . 10-1

10.1 Asynchronous Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-4

10.2 Synchronous Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-8

10.3 Hardware Error Detection Capabilities . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-10

10.4 ASC0 Baud Rate Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-10

10.5 ASC0 Interrupt Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-12

11 The High-Speed Synchronous Serial Interface . . . . . . . . . . . . . . . . . . . 11-1

11.1 Full-Duplex Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-6

11.2 Half Duplex Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-8

11.3 Baud Rate Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-10

Semiconductor Group I-2

C167

Table of Contents Page

11.4 Error Detection Mechanisms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-12

11.5 SSC Interrupt Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-14

12 The Watchdog Timer (WDT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-1

12.0.1 Operation of the Watchdog Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-2

13 The Bootstrap Loader . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-1

14 The Capture / Compare Units . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14-1

14.1 The CAPCOM Timers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14-4

14.2 CAPCOM Unit Timer Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14-8

14.3 Capture/Compare Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14-9

14.3.1 Selection of Capture Modes and Compare Modes . . . . . . . . . . . . . . . . . 14-11

14.4 Capture Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14-12

14.5 Compare Modes, . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14-13

14.5.1 Double-Register Compare Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14-18

14.6 Capture/Compare Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14-20

15 The Pulse Width Modulation Module . . . . . . . . . . . . . . . . . . . . . . . . . . . 15-1

15.1 Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15-2

15.2 PWM Module Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15-7

15.3 Interrupt Request Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15-11

15.4 PWM Output Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15-12

16 The Analog / Digital Converter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-1

16.1 Mode Selection and Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-3

16.2 Conversion Timing Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-10

16.3 A/D Converter Interrupt Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-11

17 System Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17-1

17.0.1 System Startup Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17-7

18 Power Reduction Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18-1

18.1 Idle Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18-1

18.2 Power Down Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18-3

18.3 Status of Output Pins during Idle and Power Down Mode . . . . . . . . . . . . . 18-4

19 System Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19-1

19.1 Stack Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19-4

19.2 Register Banking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19-8

19.3 Procedure Call Entry and Exit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19-8

19.4 Table Searching . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19-11

19.5 Peripheral Control and Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19-11

19.6 Floating Point Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19-12

19.7 Trap/Interrupt Entry and Exit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19-12

19.8 Unseparable Instruction Sequences . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19-12

Semiconductor Group I-3

C167

Table of Contents Page

19.9 Overriding the DPP Addressing Mechanism . . . . . . . . . . . . . . . . . . . . . . 19-13

19.10 Handling the Internal ROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19-14

19.11 Pits, Traps and Mines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19-15

20 The Register Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20-1

20.0.1 Register Description Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20-1

20.1 CPU General Purpose Registers (GPRs) . . . . . . . . . . . . . . . . . . . . . . . . . 20-2

20.2 Special Function Registers ordered by Name . . . . . . . . . . . . . . . . . . . . . . 20-4

20.3 Registers ordered by Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20-12

20.4 Special Notes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20-19

21 Instruction Set Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-1

22 Device Specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22-1

23 The On-Chip CAN Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23-1

24 Keyword Index . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24-1

Semiconductor Group I-4

Introduction / C167

1 Introduction

The rapidly growing area of embedded control applications is representing one of the most timecritical operating environments for today’s microcontrollers. Compl ex co ntrol al gorithm s hav e to be

processed based on a large number of digital as well as analog input signals, and the appropriate

output signals must be generated within a defined maximum response time. Embedded control

applications also are often sensitive to board space, power consumption, and overall system cost.

Embedded control applications therefore require microcontrollers, which...

• offer a high level of system integration

• eliminate the need for additional peripheral devices and the associated software overhead

• provide system security and fail-safe mechanisms.

With the increasing complexity of embedded control applications, a significant increase in CPU

performance and peripheral functionality over conventional 8-bit controllers is required from

microcontrollers for high-end embedded control systems. In order to achieve this high performance

goal Siemens has decided to develop its family of 16-bit CMOS microcontrollers without the

constraints of backward compatibility.

Of course the architecture of the 16-bit microcontroller family pursues successfull hardware and

software concepts, which have been established in Siemens's popular 8-bit controller families.

About this Manual

This manual describes the func tionality of a number of 16-bit microc ontrollers of the Siemens C166family, the socalled C167-class.

As these microcontrollers provide a great extent of i dentical functionali ty it makes sense to describe

a superset of the provided features. For this reason some sections o f this manual do not refer to all

the C167 derivatives that are offered (eg. devices without a CAN interface). These section s contain

respective notes wherever possible.

The descriptions in this manual refer to the following derivatives of the C167-class:

● C167CR-LM Version with PLL, 2 KByte XRAM, CAN module

● C167CR-4RM Version with PLL, 2 KByte XRAM, 32 KByte ROM, CAN module

● C167CR-16RM Version with PLL, 2 KByte XRAM, 128 KByte ROM, CAN module

● C167CR-16FM Version with PLL, 2 KByte XRAM, 128 KByte Flash memory, CAN module

● C167SR-LM Version with PLL, 2 KByte XRAM

● C167S-4RM Version with PLL, 32 KByte ROM

● C167-LM Basic version

This manual is valid for the versions with on-chip ROM or Flash memory of the mentioned

derivatives as well as for the romless versions. Of course it refers to all devices of the different

available temperature ranges and packages.

For simplicity all these various versions are referred to by the term C167 throughout this manual.

The complete pro-electron comform designations are listed in the respective data sheets.

Semiconductor Group 1-1

Introduction / C167

1.1 The Members of the 16-bit Microcontroller Family

The microcontrollers of the Siemens 16-bit family have been designed to meet the high

performance requirements of real-time embedded control applications. The architecture of this

family has been optimized for high instruction throughput and minimum response time to external

stimuli (interrupts). Intelligent peripheral subsystems have been integrated to reduce the need for

CPU intervention to a minimum extent. This also minimizes the need for communication via the

external bus interface. The high flexibility of this architecture allows to serve the diverse and varyi ng

needs of different application areas such as au tomotive, industrial control , or data communications.

The core of the 16-bit family has been developped with a modular family conc ept in mind. All family

members execute an efficie nt control-optimiz ed instru ction se t (additional instruc tions for members

of the second generation). This allows an easy and quick implementation of new family members

with different internal memory sizes and technologies, different sets of on-chip peripherals and/or

different numbers of IO pins.

The XBUS concept opens a straight forward path for the integration of application specific

peripheral modules in addition to the standard on-chip peripherals in order to build application

specific derivatives.

As programs for embedded control applications become larger,

by programmers, because high level language programs are easier to write, to debug and to

maintain.

high level languages are favoured

Semiconductor Group 1-2

Introduction / C167

The 80C166-type microcontrollers were the first generation of the 16-bit controller family. These

devices have established the C16x architecture.

The C165-type and C167-type devices are members of the second generation of this family. This

second generation is even more powerful due to additional instructions for HLL support, an

increased address space, increased internal RAM and highly efficient management of various

resources on the external bus.

Enhanced derivatives of this second generation provide additional features like additio nal internal

high-speed RAM, an integrated CAN-Module, an on-chip PLL, etc.

Utilizing integration to design efficient systems may require the integration of application specific

peripherals to boost system performance, while minimizing the part count. These efforts are

supported by the so-called XBUS, defined for the Siemens 16-bit microcontrollers (second

generation). This XBUS is an internal representation of the external bus interface that opens and

simplifies the integration of peripherals by standardizing the required interfa ce. O ne re present ative

taking advantage of this technology is the integrated CAN module that is offered by so me devices.

The C165-type devices are reduced versions of the C167 which provide a smaller package and

reduced power consumption at the expe nse of the A/D converter, the CAPCOM un its and the PWM

module.

A variety of different versions is provided which offer mask-programmable ROM, Flash memory or

no non-volatile memory at all. Also there are devices with specific functional units.

The devices may be offered in different packages, temperature ranges and speed classes.

More standard and application-specific derivatives are planned and in development.

Information about specific versions and derivatives will be made available with the devices

themselves. Contact your Siemens representative for up-to-date material.

Note: As the architecture and the basic feature s (ie. CPU core and built in p eripherals) are identical

for most of the currently offered v ersions of the C167, the descrip tions within this manual that

refer to the “C167” also apply to the other variations, unless otherwise noted.

Semiconductor Group 1-3

Introduction / C167

1.2 Summary of Basic Features

The C167 is an improved representative of the Siemens family of full featured 16-bit single-chip

CMOS microcontrollers. It combines high CPU performance (up to 10 million instructions per

second) with high peripheral functionality.

Several key features contribute to the high performance of the C167 (the indicated timings refer to

a CPU clock of 20 MH z).

High Performance 16-Bit CPU With Four-Stage Pipeline

• 100 ns minimum instruction cycle time, with most instructions executed in 1 cycle

• 500 ns multiplication (16-bit *16-bit), 1 µs division (32-bit/16-bit)

• Multiple high bandwidth internal data buses

• Register based design with multiple variable register banks

• Single cycle context switching support

• 16 MBytes linear address space for code and data (von Neumann architecture)

• System stack cache support with automatic stack overflow/underflow detection

Control Oriented Instruction Set with High Efficiency

• Bit, byte, and word data types

• Flexible and efficient addressing modes for high code density

• Enhanced boolean bit manipulation with direct addressability of 6 Kbits

for peripheral control and user defined flags

• Hardware traps to identify exception conditions during runtime

• HLL support for semaphore operations and efficient data access

Integrated On-chip Memory

• 2 KByte internal RAM for variables, register banks, system stack and code

• 2 KByte on-chip high-speed XRAM for variables, user stack and code (not on all derivatives)

• Internal Mask ROM or Flash memory (not for romless devices)

External Bus Interface

• Multiplexed or demultiplexed bus configurations

• Segmentation capability and chip select signal generation

• 8-bit or 16-bit data bus

• Bus cycle characteristics selectable for five programmable address areas

16-Priority-Level Interrupt System

• 56 interrupt nodes with separate interrupt vectors

• 300/500 ns typical/maximum interrupt latency in case of internal program execution

• Fast external interrupts

Semiconductor Group 1-4

Introduction / C167

8-Channel Peripheral Event Controller (PEC)

• Interrupt driven single cycle data transfer

• Transfer count option (standard CPU interrupt after a programmable

number of PEC transfers)

• Eliminates overhead of saving and restoring system state for interrupt requests

Intelligent On-chip Peripheral Subsystems

• 16-Channel 10-bit A/D Converter with programmable conversion time

(9.7 µs minimum), auto scan modes, channel injection mode

• Two 16-Channel Capture/Compare Units with 2 independent time bases each,

very flexible PWM unit/event recording unit with 5 different operating modes,

includes four 16-bit timers/counters with 400 ns maximum resolution

• 4-Channel PWM Unit

• 2 Multifunctional General Purpose Timer Units

GPT1: three 16-bit timers/ counters, 400 ns maximum resolution

GPT2: two 16-bit timers/counters, 200 ns maximum resolution

• Asynchronous/Synchronous Serial Channel (USART)

with baud rate generator, parity, framing, and overrun error detection

• High Speed Synchronous Serial Channel

programmable data length and shift direction

• Watchdog Timer with programmable time intervals

• Bootstrap Loader for flexible system initialization

• O n-chip CAN-Module (not on all derivatives)

111 IO Lines With Individual Bit Addressability

• Tri-stated in input mode

• Push/pull or open drain output mode

• Selectable input thresholds (not on all derivatives)

Different Temperature Ranges

• 0 to +70 °C, – 40 to +85 °C, – 40 to +110 °C

Siemens CMOS Process

• Low Power CMOS Technology, including power saving Idle and Power Down modes

144-Pin Plastic Quad Flat Pack (PQFP) Package

• EIAJ standard, 0.65 mm (25.6 mil) lead spacing, surface mount technology

Semiconductor Group 1-5

Introduction / C167

Complete Development Support

A variety of software and hardware development tools for the Siemens family of 16-bit

microcontrollers is available from experienced international tool suppliers. The high quality and

reliability of these tools is already proven in many applications and by many users. The tool

environment for the Siemens 16-bit microcontrollers includes the following tools:

• Compilers (C, MODULA2, FORTH)

• Macro-Assemblers, Linkers, Locaters, Library Managers, Format-Converters

• Architectural Simulators

• HLL debuggers

• Real-Time operating systems

• VHDL chip models

• In-Circuit Emulators (based on bondout or standard chips)

• Plug-In emulators

• Emulation and Clip-Over adapters, production sockets

• Logic Analyzer disassemblers

• Evaluation Boards with monitor programs

• Industrial boards (also for CAN, FUZZY, PROFIBUS, FORTH applications)

• Network driver software (CAN, PROFIBUS)

Semiconductor Group 1-6

1.3 Abbreviations

The following acronyms and termini are used within this document:

ADC . . . . . . . . . Analog Digital Converter

ALE. . . . . . . . . . Address Latch Enable

ALU. . . . . . . . . . Arithmetic and Logic Unit

ASC. . . . . . . . . . Asynchronous/synchronous Serial Controller

CAN . . . . . . . . . Controller Area Network (License Bosch)

CAPCOM . . . . . CAPture and COMpare unit

CISC . . . . . . . . . Complex Instruction Set Computing

CMOS. . . . . . . . Complementary Metal Oxide Silicon

CPU . . . . . . . . . Central Processing Unit

Introduction / C167

EBC. . . . . . . . . . External Bus Controller

ESFR . . . . . . . . Extended Special Function Register

Flash. . . . . . . . . Non-volatile memory that may be electrically erased

GPR . . . . . . . . . General Purpose Register

GPT. . . . . . . . . . General Purpose Timer unit

HLL . . . . . . . . . . High Level Language

IO . . . . . . . . . . . Input / Output

PEC. . . . . . . . . . Peripheral Event Controller

PLA. . . . . . . . . . Programmable Logic Array

PLL . . . . . . . . . . Phase Locked Loop

PWM. . . . . . . . . Pulse Width Modulation

RAM . . . . . . . . . Random Access Memory

RISC . . . . . . . . . Reduced Instruction Set Computing

ROM . . . . . . . . . Read Only Memory

SFR . . . . . . . . . . Special Function Register

SSC. . . . . . . . . . Synchronous Serial Controller

XBUS . . . . . . . . Internal representation of the External Bus

XRAM . . . . . . . . On-chip extension RAM

Semiconductor Group 1-7

Architectural Overview / C167

2 Architectural Overview

The architecture of the C167 combines the advantages of both RISC and CISC processors in a very

well-balanced way. The sum of the features which are combined result in a high performance

microcontroller, which is the right choice not only for today’s applications, but also for future

engineering challenges. The C167 not only integrates a powerful CPU core an d a set o f periphe ral

units into one chip, but also connects the units in a very efficient way. One of the four buses used

concurrently on the C167 is t he XBUS, an internal repres entation of the external bus interfac e. This

bus provides a standardized method of integrating application-specific peripherals to produce

derivates of the standard C167.

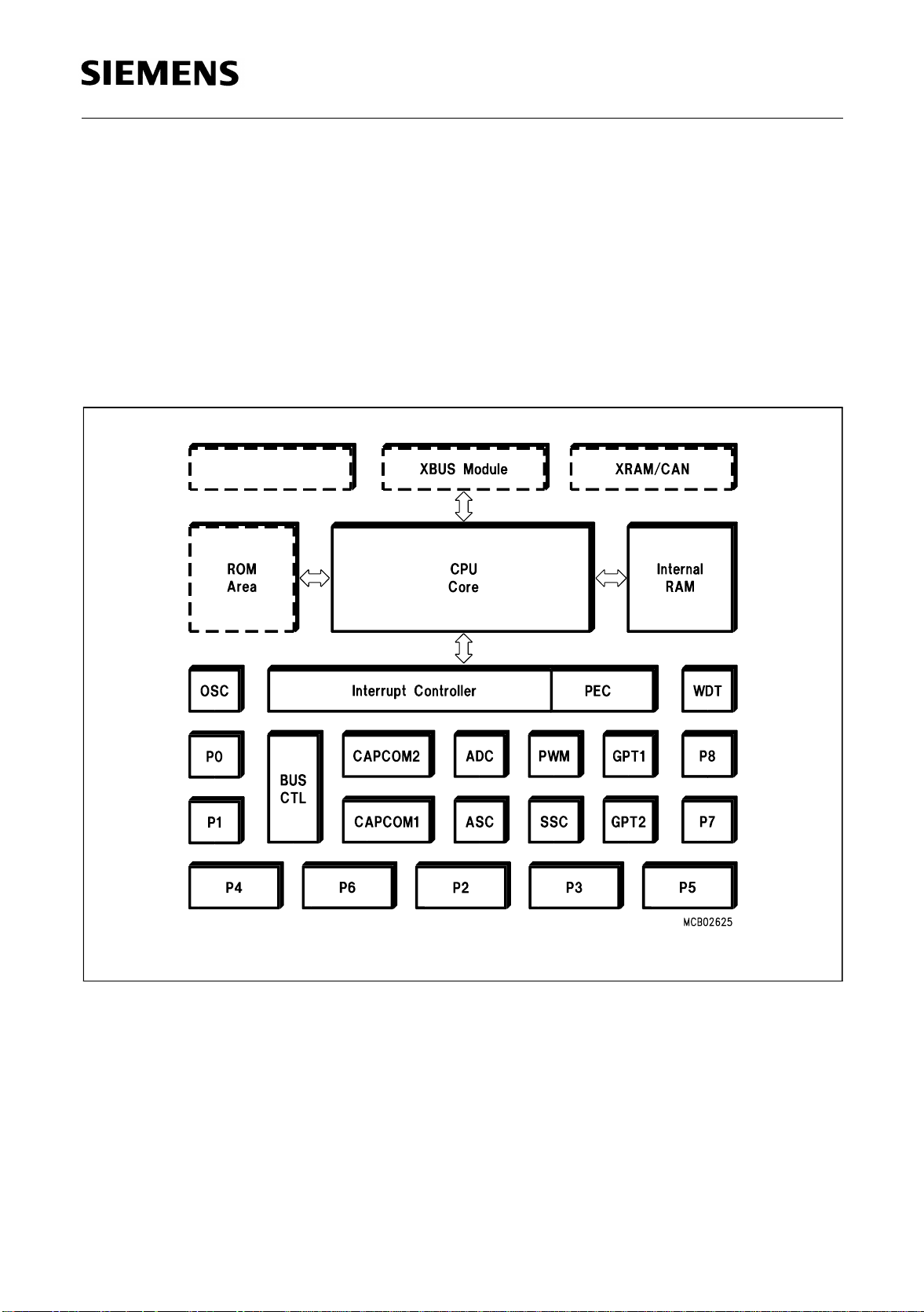

Figure 2-1

C167 Functional Block Diagram

Semiconductor Group 2-1

Architectural Overview / C167

2.1 Basic CPU Concepts and Optimizations

The main core of the CPU cons ists of a 4-stage ins truction pipeline, a 16-bi t arithmetic and logic unit

(ALU) and dedicated SFRs. Additional hardware is provided for a separate multiply and divide unit,

a bit-mask generator and a barrel shifter.

Figure 2-2

CPU Block Diagram

To meet the demand for greater performance and flexibility, a number of areas has been optimized

in the processor core. Functional blocks in the CPU core are controlled by signals from the

instruction decode logic. These are summarized below, and described in detail in the following

sections:

1) High Instruction Bandwidth / Fast Execution

2) High Function 8-bit and 16-bit Arithmetic and Logic Unit

3) Extended Bit Processing and Peripheral Control

4) High Performance Branch-, Call-, and Loop Processing

5) Consistent and Optimized Instruction Formats

6) Programmable Multiple Priority Interrupt Structure

Semiconductor Group 2-2

Architectural Overview / C167

High Instruction Bandwidth / Fast Execution

Based on the hardware provisions, most of the C167’s instructions can be executed in just one

machine cycle, which requires 100 ns at 20 MHz CPU clock. For example, shift and rotate

instructions are always processed within one machine cycle, independent of the number of bits to

be shifted.

Branch-, multiply- and divide instructions normally take more than one machine cycle. These

instructions, however, have also been optimized. For example, branch instructions only require an

additional machine cycle, when a branch is taken, and most branches taken in loops require no

additional machine cycles at all, due to the so-called ‘Jump Cache’.

A 32-bit / 16-bit division takes 1µs, a 16-bit

The instruction cycle time has been dramatically reduced through the use of instruction pipelining.

This technique allows the core CPU to process portions of multiple sequential ins tructi on stages in

parallel. The following four stage pipeline provides the optimum balancing for the CPU core:

FETCH: In this stage, an instruction is fetched from the internal ROM or RAM or from the external

memory, based on the current IP value.

16-bit multiplication takes 0.5 µs.

*

DECODE: In this stage, the previously fetched instruction is decoded and the required operands

are fetched.

EXECUTE: In this stage, the specified operation is performed on the previously fetched operands.

WRITE BACK: In this stage, the result is written to the specified location.

If this technique were not used, each instruction would require four machine c ycles. Th is increas ed

performance allows a greater number of tasks and interrupts to be processed.

Instruction Decoder

Instruction decoding is primarily generated from PLA outputs based on the selected opcode. No

microcode is used and each pi peline stag e receives contro l signals sta ged in control regis ters from

the decode stage PLAs. Pipeline holds are primarily caused by wait states for external memory

accesses and cause the holding of signals in the control registers. Multiple-cycle instructions are

performed through instruction injection and simple internal state machines which modify required

control signals.

High Function 8-bit and 16-bit Arithmetic and Logic Unit

All standard arithmetic and logical operations are performed in a 16-bit ALU. In addition, for byte

operations, signals are provided from bits six and seven of the ALU result to correctly set the

condition flags. Multiple precision arithmetic is provided through a 'CARRY-IN' signal to the ALU

from previously calculated portions of the desired operation. Most internal execution blocks have

been optimized to perform operations on either 8-bit or 16-bit quanti ties. Once the pipeline has been

filled, one instruction is completed per machine cycle, except for multiply and divide. An advanced

Booth algorithm has been incorporated to allow four bits to be multiplied and two bits to be divided

per machine cycle. Thus, these operations use two coupled 16-bit registers, MDL and MDH, and

require four and nine machine cycles, respective ly, to perform a 16-bit by 16-bit (or 32-bit by 16-bit)

calculation plus one machine cycle to setup and adjust the operands and the result. Even these

Semiconductor Group 2-3

Architectural Overview / C167

longer multiply and divide instructions can be interrupted during their executi on to allow for very fast

interrupt response. Instructions have also been provided to allow byte packing in memory while

providing sign extension of bytes for word wide arithmetic operations. The internal bus structure

also allows transfers of bytes or words to or from peripherals based on the p eripheral requirements.

A set of consistent flags is automati call y upda ted in the PSW after each arithmetic, logical, shift, or

movement operation. These flags allow branching on specific conditions. Support for both signed

and unsigned arithmetic is provided through user-specifiable branch tests. These flags are also

preserved automatically by the CPU upon entry into an interrupt or trap routine.

All targets for branch calculations are also computed in the central ALU.

A 16-bit barrel shifter provides multiple bit shifts in a single cycle. Rotates and arithmetic shifts are

also supported.

Extended Bit Processing and Peripheral Control

A large number of instructions has been dedicated to bit processing. These instructions provide

efficient control and testing of peripherals while enhancing data manipulation. Unlike other

microcontrollers, these instructions provide direct access to two operands in the bit-addressable

space without requiring to move them into temporary flags.

The same logical instruc tions ava ilabl e for words and bytes are also supported for bi ts. This allows

the user to compare and modify a control bit for a peripheral in one instruction. Multiple bit shift

instructions have been included to avoid long instruction streams of single bit shift operations.

These are also performed in a single machine cycle.

In addition, bit field instructions have been provided, which allow the modification of multiple bits

from one operand in a single instruction.

High Performance Branch-, Call-, and Loop Processing

Due to the high percentage of branching in controller applications, branch instructions have been

optimized to require one extra machine cycle only when a branch is taken. This is implemented by

precalculating the target address while decoding the instruction. To decrease loop execution

overhead, three enhancements have been provided:

• The first solution provides single cycl e branch execution after the first iteration of a loop. Thus , only

one machine cycle is lost during the execution of the entire loop. In loops which fall through upon

completion, no machine cycles are lost when exiting the loop. No special instructions are required

to perform loops, and loops are automatically detected during execution of branch instructions.

• The second loop enhancement allows the detection of the end of a table and avoids the use of two

compare instructions embedded in loops. One simply places the lowest negati ve number at the end

of the specific table, and s pecifies branching i f neither this value nor the compared value have been

found. Otherwise the loop is terminated if either conditi on has been met. The terminating condition

can then be tested.

• The third loop enhancement provides a more flexible solution than the Decrement and Skip on

Zero instruction which is found in other microcontrollers. Through the use of Compare and

Increment or Decrement instructions, the user can make comparisons to any v alue. This allows loop

counters to cover any range. This is particularly advantageous in table searching.

Semiconductor Group 2-4

Architectural Overview / C167

Saving of system state is automatically performed on the internal system stack avoiding the use of

instructions to preserve state upon entry and exit of interrupt or trap routi nes. Call instructions push

the value of the IP on the system s tack, and require the same executi on time as branch instru ctions.

Instructions have also be en p rovide d to su pport indirec t b ra nch and cal l i nstruct ions. Thi s suppo rts

implementation of multiple CASE statement branching in assembler macros and high level

languages.

Consistent and Optimized Instruction Formats

To obtain optimum performance in a pipelined design, an instruction set has been designed which

incorporates concepts from Reduced Instruction Set Computing (RISC). These concepts primarily

allow fast decoding of the instructi ons and operands while reducing pi peline holds. These concepts,

however, do not preclude the use of complex instructions, which are required by microcontroller

users. The following goals were used to design the instruction set:

1) Provide powerful instructions to perform operations which currently require sequences of

instructions and are frequently used. Avoid transfer into and out of temporary registers such

as accumulators and carry bits. Perform tasks in parallel such as saving state upon entry into

interrupt routines or subroutines.

2) Avoid complex encoding schemes by placing operands in consistent fields for each instruction. Also avoid complex addressing modes which are not frequently used. This decreases

the instruction decode time while also simplifying the development of compilers and assemblers.

3) Provide most frequently used instructions with one-word instruc tion formats . All other ins tructions are placed into two-word formats. This allows all instructions to be placed on word

boundaries, which alleviates the need for complex alignment hardware. It also has the benefit of increasing the range for relative branching instructions.

The high performance offered by the hardware implementation of the CPU can efficie ntly be utilized

by a programmer via the highly functional C167 instruction set which includes the following

instruction classes:

• Arithmetic Instructions

• Logical Instructions

• Boolean Bit Manipulation Instructions

• Compare and Loop Control Instructions

• Shift and Rotate Instructions

• Prioritize Instruction

• Data Movement Instructions

• System Stack Instructions

• Jump and Call Instructions

• Return Instructions

• System Control Instructions

• Miscellaneous Instructions

Possible operand types are bits, bytes and words. Specific instruction support the conversion

(extension) of bytes to words. A variety of direct, indirect or immediate addressing modes are

provided to specify the required operands.

Semiconductor Group 2-5

Architectural Overview / C167

Programmable Multiple Priority Interrupt System

The following enhancements have been included to allow processing of a large number of interrupt

sources:

1) Peripheral Event Controller (PEC): This processor is used to off-loa d many interrupt requests

from the CPU. It avoids the overhead of entering and exiting interrupt or trap routi nes by pe rforming single-cycle interrupt-driven byt e or word data transfers between any two locations in

segment 0 with an optional increment of either the PEC source or the destination pointer.

Just one cycle is ’stolen’ from the current CPU activity to perform a PEC service.

2) Multiple Priority Interrupt Controller: This controller allows all interrupts to be placed at any

specified priority. Interrupts may also be grouped, which provides the user with the ability to

prevent similar priority tasks from interrupting each other. For each of the possible interrupt

sources there is a separate control register, which contains an interrupt request flag, an interrupt enable flag and an interrupt priority bitfi eld. O nce havi ng been acc epted by the CPU, an

interrupt service can only be interrupt ed by a h igher prioritized service request. For standard

interrupt processing, each of the possible interrupt sources has a dedicated vector location.

3) Multiple Register Banks: This feature allows the user to specify up to sixteen general pur-

pose registers located anywhere i n the inte rnal RAM. A sin gle one-machine-cycl e instruct ion

allows to switch register banks from one task to another.

4) Interruptable Multiple Cycle Instructions: Reduced interrupt latency is provided by allowing

multiple-cycle instructions (multiply, divide) to be interruptable.

With an interrupt response time within a range from just 250 ns to 500 ns (in case of internal

program execution), the C167 is capable of reacting very fast on non-deterministic events.

Its fast external interrupt inputs are sampled every 50 ns and allow to recognize even very short

external signals.

The C167 also provides an excellent mechanism to identify and to process exceptions or error

conditions that arise during run-time, so called ’Hardware Traps’. Hardware traps cause an

immediate non-maskable system reaction which is similiar to a standard interrupt service

(branching to a dedicated vector table location). The occurrence of a hardware trap is additionally

signified by an individual bit in the trap flag register (TFR). Except for another higher prioritize d trap

service being in progress, a hardware trap will interrupt any current program execution. In turn,

hardware trap services can normally not be interrupted by standard or PEC interrupts.

Software interrupts are supported by means of the ’TRAP’ instruction in combination with an

individual trap (interrupt) number.

Semiconductor Group 2-6

Architectural Overview / C167

2.2 The On-chip System Resources

The C167 controllers provide a number of powerful system resources designed around the CPU.

The combination of CPU and these resources results in the high performance of the members of

this controller family.

Peripheral Event Controller (PEC) and Interrupt Control

The Peripheral Event Controller allows to respond to an interrupt request with a single da ta transfer

(word or byte) which only consumes one instruction cycle and do es not require to sa ve and restore

the machine status. Each interrupt source is prioritized every mac hine cy cle in the interrupt con trol

block. If PEC service is selected, a PEC transfer is started. If CPU interrupt service is requested, the

current CPU priority level stored in the PSW register is tested to determine whether a higher priority

interrupt is currently being serviced. When an interrupt is acknowledged, the current state of the

machine is saved on the inte rnal syst em stack and the CPU branches to the sy stem spec ific vec tor

for the peripheral.

The PEC contains a set of SFRs which store the count value a nd control bits for eight data trans fer

channels. In addition, the PEC uses a dedicated area of RAM which contains the source and

destination addresses. The PEC is controlled similar to any other peripheral through SFRs

containing the desired configuration of each channel.

An individual PEC transfer counter is implicitly decremented for each PEC service except forming

in the continuous transfer mode. When this counter reaches zero, a standard interrupt is performed

to the vector location related to the corresponding source. PEC services are very well suited, for

example, to move register contents to/from a memory table. The C167 has 8 PEC channels each

of which offers such fast interrupt-driven data transfer capabilities.

Memory Areas

The memory space of the C167 is configured in a Von Neumann architecture which means that

code memory, data memory, registers and IO ports are organized within the same linear address

space which covers up to 16 MBytes. The entire memory space can be accessed bytewise or

wordwise. Particular portions of the on-chip memory have additionally been made directly bit

addressable.

A 2 KByte 16-bit wide internal RAM provides fast access to General Purpose Registers (GPRs),

user data (variables) and system stack. The internal RAM may also be used for code. A unique

decoding scheme provides flexible user register banks in the internal memory while optimizing the

remaining RAM for user data.

The CPU disposes of an actual register context consisting of up to 16 wordwide and/or bytewide

GPRs, which are physically located within the on-chip RAM area. A Context Pointer (CP) register

determines the base address of the active register bank to be acces sed by the CPU at a time. The

number of register banks is only re stricted by the available internal RAM s pace. For easy parameter

passing, a register bank may overlap others.

A system stack of up to 1024 words is provi ded as a s torage fo r temporary data. The sy stem stack

is also located within the on-chip RAM area, and it is accessed by the CPU via the stack p ointer (SP)

register. Two separate SFRs, STKOV and STKUN, are implicitly compared against the stack

pointer value upon each stack access for the detection of a stack overflow or underflow.

Semiconductor Group 2-7

Architectural Overview / C167

Hardware detection of the selected memory space is placed at the internal memory decoders and

allows the user to specify any address directly or ind irectly and obtain the desired data without using

temporary registers or special instructions.

A 2 KByte 16-bit wide on-chip XRAM provides fast access to user data (variables), user stacks

and code. The on-chip XRAM is realized as an X-Peripheral and appears to the software as an

external RAM. Therefore it cannot store register banks and is not bitaddressable. The XRAM allows

16-bit accesses with maximum speed.

An optional internal ROM provides for both code and consta nt dat a storage. Th is memory area is

connected to the CPU via a 32-bit-wide bus. Thus, an entire do uble-word instruction can be f etched

in just one machine cycle. Program execution from the on-chip ROM is the fastest of all possible

alternatives.

For Special Function Registers 1024 Bytes of the address space are reserved. The standard

Special Function Register area (SFR) uses 512 bytes, while the Extended Special Function

Register area (ESFR) uses the other 512 bytes. (E)SFRs are wordwide registers which are used for

controlling and monitoring functions of the different on-chip units. Unused (E)SFR addresses are

reserved for future members of the C167 family with enhanced functionality.

External Bus Interface

In order to meet the needs of designs where more memory is required than is provided on ch ip, up

to 16 MBytes of external RAM and/or ROM can be connected to the microcontrol ler v ia i ts ex ternal

bus interface. The integrated External Bus Contro ller (EBC) allows to access external memory and/

or peripheral resources in a very flexible way. For up to five address areas the bus mode

(multiplexed / demultiplexed), the data bus width (8-bit / 16-bit) and even the length of a bus cycle

(waitstates, signal delays) can be selected independently. This allows to access a variety of

memory and peripheral components directly and with maximum efficiency. If the device does not

run in Single Chip Mode, where no external memory is required, the EBC can control external

accesses in one of the following four different external access modes:

• 16-/18-/20-/24-bit Addresses, 16-bit Data, Demultiplexed

• 16-/18-/20-/24-bit Addresses, 8-bit Data, Demultiplexed

• 16-/18-/20-/24-bit Addresses, 16-bit Data, Multiplexed

• 16-/18-/20-/24-bit Addresses, 8-bit Data, Multiplexed

The demultiplexed bus modes use PORT1 for addresses and PORT0 for data input/output. The

multiplexed bus modes use PORT0 for both addresses and data input/ou tput. All modes u se Port 4

for the upper address lines (A16...) if selected.

Important timing characteristics of the external bus interface (waitstates, ALE length and Read/

Write Delay) have been made programmable to allow the user the adaption of a wide range of

different types of memories and/or peripherals. Access to very slow memories or peripherals is

supported via a particular 'Ready' function.

For applications which require less than 64 KBytes of address space, a non-segmented memory

model can be selected, where all locations can be addressed by 16 bits, and thus Port 4 is not

needed as an output for the upper address bits (A23/A19/A17...A16), as is the case when using the

segmented memory model.

Semiconductor Group 2-8

Architectural Overview / C167

The on-chip XBUS is an internal representation of the external bus and allows to access

integrated application-specific peripherals/modules in the same way as external components. It

provides a defined interface for these customized peripherals.

The on-chip XRAM and the on-chip CAN-Module are examples for these X-Peripherals.

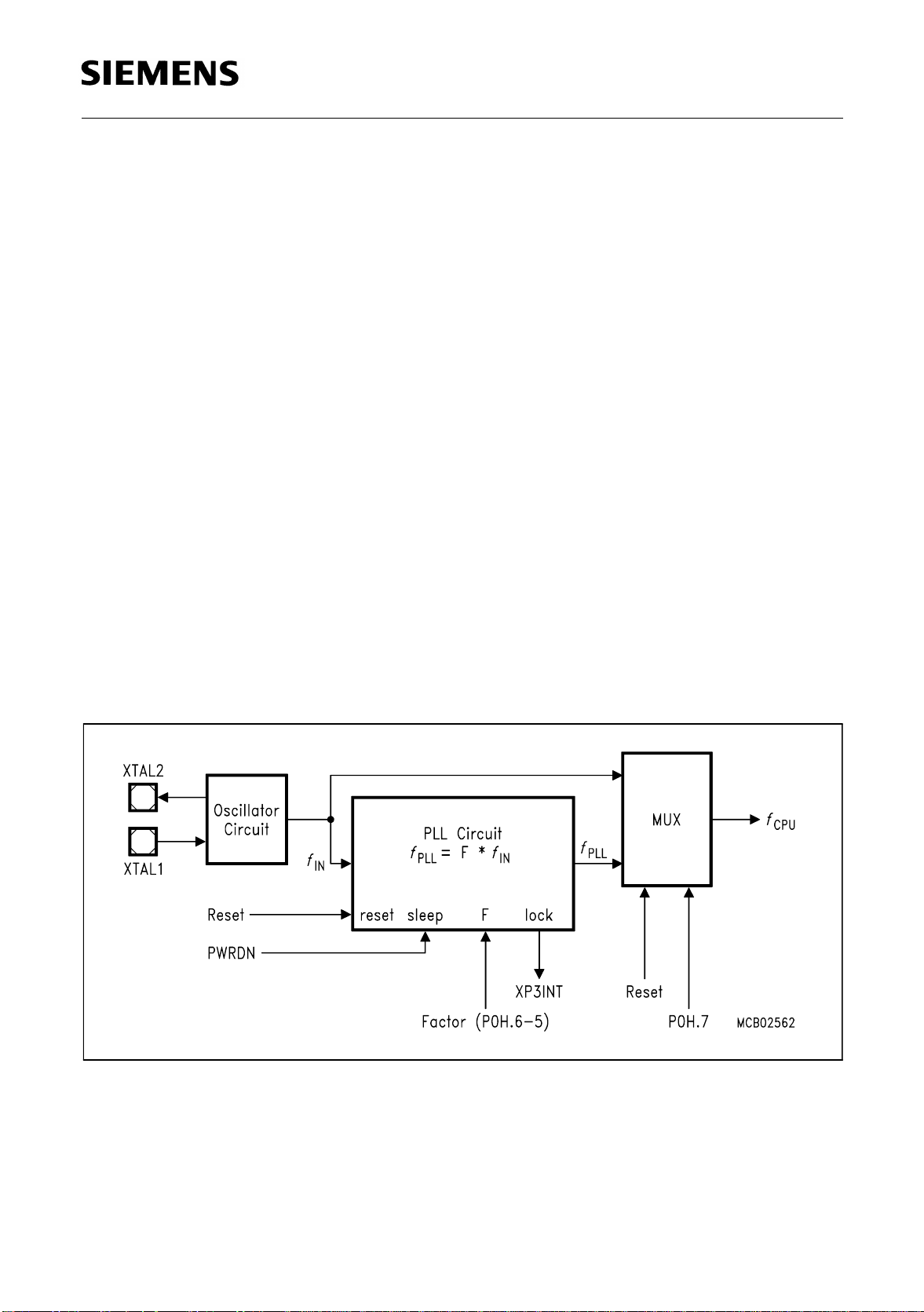

Clock Generator

The on-chip clock generator provides the C167 with its basic clock signal that controls all activities

of the controller hardware. Its oscillator can either run with an external crystal and appropriate

oscillator circuitry (see also recommendations in chapter „Dedicated Pins“) or it can be driven by an

external oscillator. The oscillator either directly feeds the external clock signal to the controller

hardware (through buffers, of course), divides the external cl ock frequency by 2, or feeds an on-chip

phase locked loop (PLL) which multiplies the input frequency by a selectable factor F (depending on

the device mode and/or type). This resulting internal clock signal is also referred to as “CPU clock”.

Two separated clock signals are generated for the CPU itself and the peripheral part of the chip.

While the CPU clock is stopped during the idle mode, the peripheral clock keeps running. Both

clocks are switched off, when the power down mode is entered.

The on-chip PLL circuit allows operation of the C167 on a low frequency external clock while still

providing maximum performance. The PLL multiplies the external clock frequency by a selectable

factor of 1:F and generates a CPU clock signal with 50% duty cycle. The PLL als o provides fail safe

mechanisms which allow the detection of frequency deviations and the execution of emergency

actions in case of an external clock failure.

Figure 2-3

PLL Block Diagram

Semiconductor Group 2-9

Architectural Overview / C167

PLL Operation

The PLL is enabled when pin P0H.7 is latched high during reset. On power-up the PLL provides a

stable clock signal within ca. 1 ms after V

signal (in this case the PLL will run on its basic frequency of 2...5 MHz). The PLL starts

synchronizing with the external clock signal as soon as it is available. Within ca. 1 ms after stable

oscillations of the external clock within the specified frequency range the PLL will be synchronous

with this clock at a frequency of F *f

OSC

Note: If the C167 is required to operate on the desired CPU clock directly after reset make sure that

RSTIN

remains active until the PLL has locked (ca. 1 ms).

When PLL operation is selected the CPU clock is a selectable multiple of the oscillator frequency,

ie. the input frequency. The table below lists the possible selections.

has reached 5V±10%, even if there is no external clock

CC

, ie. the PLL locks to the external clock.

P0.15-13

(P0H.7-5)

111

110

101

100

0XX

1)

The external clock input range refers to a CPU clock range of 10...25 MHz.

2)

The maximum depends on the duty cycle of the external clock signal.

CPU

Frequency f

= f

* F

XTAL

f

* 4 2.5 to 6.25 MHz Default configuration

XTAL

f

* 3 3.33 to 8.33 MHz

XTAL

f

* 2 5 to 12.5 MHz

XTAL

f

* 5 2 to 5 MHz

XTAL

f

* 1 1 to 25 MHz Direct drive

XTAL

CPU

External Clock Input

Range

1)

Notes

2)

In emulation mode direct drive is selected with P0.15 (P0H.7) = ’1’.

The PLL constantly synchronizes to the external clock signal. Due to the fact that the external

frequency is 1/F’th of the PLL output frequency the outpu t frequency may be slightly higher or lower

than the desired frequency. This jitter is irrelevant for longer time periods. For short periods (1...4

CPU clock cycles) it remains below 4%.

When the PLL detects a missing input clock signal it generates an interrupt request. This warning

interrupt indicates that the PLL frequency is no more locked, ie. no more stable. This occurs when

the input clock is unstabl e and es pecially when the i nput cloc k fails complete ly, eg. due to a broken

crystal. In this case the synchronization mechanism will reduce the PLL output frequency down to

the PLL’s basic frequency (2...5 MHz). The basic frequency is still gene rated and allows the CPU to

execute emergency actions in case of a loss of the external clock.

Operation without PLL

The PLL is disabled when pin P0H.7 is latched low during reset. In this case the C167’s clock

system is directly fed from the external clock input, ie. f

OSC

= f

. The maximum input clock

CPU

frequency depends on the clock signal’s duty cycle, because the minimum values for the clock

phases (TCLs) must be respected.

Semiconductor Group 2-10

Architectural Overview / C167

2.3 The On-chip Peripheral Blocks

The C167 family clearly separates peripherals from the core. This structure permits the maximum

number of operations to be performed in p arallel and allows peripherals to be added or deleted from

family members without modifications to the core. Each functional block processes data

independently and communicates information over common buses. Peripherals are controlled by

data written to the respective Special Function Registers (SFRs). These SFRs are located either

within the standard SFR area (00’FE00

(00’F000

...00’F1FFH).

H

These built in peripherals either allow the CPU to interface with the external world, or provide

functions on-chip that otherwise were to be added externally in the respective system.

The C167 generic peripherals are:

• Two General Purpose Timer Blocks (GPT1 and GPT2)

• Two Serial Interfaces (ASC0 and SSC)

• A Watchdog Timer

• Two 16-channel Capture / Compare units (CAPCOM1 and CAPCOM2)

• A 4-channel Pulse Width Modulation unit

• A 10-bit Analog / Digital Converter

• Nine IO ports with a total of 111 IO lines

...00’FFFFH) or within the extended ESFR area

H

Each peripheral also contains a set of Special Function Registers (SFRs), which control the

functionality of the peripheral and temporarily store intermediate data results. Each peripheral has

an associated set of status flags. Individually selected clock signals are generated for each

peripheral from binary multiples of the CPU clock.

Peripheral Interfaces

The on-chip peripherals generally have two different types of interfaces, an interface to the CPU

and an interface to external hardware. Communica tion between CPU and peripherals i s performed

through Special Function Registers (SFRs) and interrupts. The SFRs serve as control/status and

data registers for the peripherals. Interrupt requests are generated by the peripherals based on

specific events which occur during their operation (eg. operation complete, error, etc.).

For interfacing with external hardware, speci fic pins of the paral lel ports a re used, when an input or

output function has been selected for a peripheral. During this time, the port pins are controlled by

the peripheral (when used as outputs) or by the external hardware which controls the peripheral

(when used as inputs). This is called the 'alternate (input or output) function' of a port pin, in contrast

to its function as a general purpose IO pin.

Peripheral Timing

Internal operation of CPU and peripherals is based on the CPU clock (f

). The on-chip oscillator

CPU

derives the CPU clock from the crystal or from the external clock signal. The clock signal which is

gated to the peripherals is independent from the clock signal which feeds the CPU. During Idle

mode the CPU’s clock is stopped while the peripherals continue their operation. Peripheral SFRs

may be accessed by the CPU once per state. When an SFR is written to by software in the same

state where it is also to be modified by the peripheral, the software write operation has priority.

Further details on peripheral timing are included in the specific sections about each peripheral.

Semiconductor Group 2-11

Architectural Overview / C167

Programming Hints

Access to SFRs

All SFRs reside in data page 3 of the memory space. The following addressing mechanisms allow

to access the SFRs:

• indirect or direct addressing with 16-bit (mem) addresses it must be guaranteed that the used

data page pointer (DPP0...DPP3) selects data page 3.

• accesses via the Peripheral Event Controller (PEC) use the SRCPx and DSTPx pointers instead

of the data page pointers.

• short 8-bit (reg) addresses to the standard SFR area do not use the data page pointers but

directly access the registers within this 512 Byte area.

• short 8-bit (reg) addresses to the extended ESFR area require switching to the 512 Byte

extended SFR area. This is done via the EXTension instructions EXTR, EXTP(R), EXTS(R).

Byte write operations to word wide SFRs via indirect or direct 16-bit (mem) addressing or byte

transfers via the PEC force zeros in the non-addressed byte. Byte write operations via short 8-bit

(reg) addressing can only access the low byte of an SFR and force zeros in the high byte. It is

therefore recommended, to use the bit field instructions (BFLDL and BFLDH) to write to any number

of bits in either byte of an SFR without disturbing the non-addressed byte and the unselected bits.

Reserved Bits

Some of the bits which are contained in the C167's SFRs are marked as 'Reserved'. User so ftware

should never write '1's to reserved bits. These bits are c urrently not impl emented and may be used

in future products to invoke new functions. In this case, the active state for these functions will be

'1', and the inactive state will be '0'. Therefore writing only ‘0’s to reserved locations provides

portability of the current software to future devices. Read accesses to reserved bits return ‘0’s.

Parallel Ports

The C167 provides up to 111 IO lines which are organized into eight input/output ports and one

input port. All port lines are bit-addressable, and all input/output lines are individually (bit-wise)

programmable as inputs or outputs via direction registers. The IO ports are true bidirectional ports

which are switched to high impedance state when configured as inp uts. The output drivers of three

IO ports can be configured (pin by pin) for push/pull operation or open-drain operation via control

registers. During the internal reset, all port pins are configured as inputs.

All port lines have programmable alternate input or output functions associated with them. PORT0

and PORT1 may be used as address and data lines when accessing ex ternal memory, while Port 4

outputs the additional segment address bits A23/19/17...A16 in systems where segmentation is

used to access more than 64 KBytes of memory. Port 6 provides optional bus arbitration signals

(BREQ

provides inputs/outputs for the CAPCOM1 unit. Port 3 includes alternate functions of timers, serial

interfaces, the optional bus control signal BHE

used for timer control signals and for the analog inputs to the A/D Converter. Port 7 provides the

output signals from the PWM unit and inputs/outputs for the CAPCOM2 unit. Port 8 provides inputs/

outputs for the CAPCOM2 unit. Fo ur pins o f PORT1 may also be used as inputs f or the CAPCOM2

unit. All port lines that are not used for these alternate functions may be used as general purpose

IO lines.

, HLDA, HOLD) and chip select signals. Port 2 accepts the fas t external int errupt inputs and

and the system clock output (CLKOUT). Port 5 is

Semiconductor Group 2-12

Architectural Overview / C167

Serial Channels

Serial communication with other microcontrollers, processors, terminals or external peripheral

components is provided by two serial interfaces with different functionality, an Asynchronous/

Synchronous Serial Channel (ASC0) and a High-Speed Synchronous Serial Channel (SSC).

They are upward compatible with the serial ports of the Siemens 8-bit microcontroller families and

support full-duplex asynchronous communica tion at up to 625 KBaud and half-duplex sy nchronous

communication at up to 5 MBaud (2.5 MBaud on the ASC0) @ 20 MHz CPU clock. The SSC may

be configured so it interfaces with serially linked peripheral components.

Two dedicated baud rate generators allow to set up a ll standard baud rates with out oscillator tuning.

For transmission, reception and error handling 3 separate interrupt vecto rs are provided on channel

SSC, 4 vectors are provided on channel ASC0.

In asynchronous mode, 8- or 9-bit data frames are transmitted or received, preceded by a start bit

and terminated by one or two stop bits. For multiprocessor communication, a mechanism to

distinguish address from data bytes has been included (8-bit data plus wake up bit mode).

In synchronous mode, the ASC0 transmits or receives bytes (8 bits) synchronously to a shift clock

which is generated by the ASC0. The SSC transmits or receives characters of 2...16 bits length

synchronously to a shift clock which can be generated by the SSC (master mode) or by an extern al

master (slave mode). The SSC can start shifting with the LSB or with the MSB, while the ASC0

always shifts the LSB first.

A loop back option is available for testing purposes.

A number of optional hardware error detection capabilities has been included to increase the

reliability of data transfers. A parity bit can automatically be generated on transmission or be

checked on reception. Framing error detection allows to recognize data frames with missing stop

bits. An overrun error will be generated, if the last character received has not been read out of the

receive buffer register at the time the reception of a new character is complete.

The On-chip CAN Module

The integrated CAN Module handles the completely autonomous transmission and reception of

CAN frames in accordance with the CAN specification V2.0 part B (active), ie. the on-chip

CAN M odule can receive and transmit standard frames with 11-bit identifiers as well as extended

frames with 29-bit identifiers.

The module provides Full CAN functionality on up to 15 message objects. Messag e object 15 may

be configured for Basic CAN functionality. Both modes provide separate masks for acceptance

filtering which allows to accept a number of identifiers in Ful l CAN mode and also allows to disregard

a number of identifiers in Basic CAN mode. All message objects can be updated independe nt from

the other objects and are equipped for the maximum message length of 8 bytes.

The bit timing is derived from the XCLK and is programmable up to a data rate of 1 MBaud. The

CAN Module uses two pins to interface to a bus transceiver.

Note: The CAN Module is not part of all C167 derivatives. This description, of course, refers to

those devices only which incorporate a CAN Module.

Semiconductor Group 2-13

Architectural Overview / C167

General Purpose Timer (GPT) Unit

The GPT units represent a very flexible multifunctional timer/counter structure which may be used

for many different time related tasks such as event timing and co unting, pulse width and duty cy cle

measurements, pulse generation, or pulse multiplication.

The five 16-bit timers are organiz ed in two separate m odules, GPT1 and G PT2. Each ti mer in each

module may operate independently in a number of different modes, or may be concatenated with

another timer of the same module.

Each timer can be configured individually for one of three basic modes of operation, which are

Timer, Gated Timer, and Counter Mode. In Timer Mode the input clock for a timer is derived from

the internal CPU clock divided by a programmable p resca ler, while Counter Mode a llows a timer to

be clocked in reference to external events (via TxIN).

Pulse width or duty cycle measurement is supported in Gated Timer Mode where the operation of

a timer is controlled by the ‘gate’ level on its external input pin TxIN.

The count direction (up/down) for each timer is programmable by software or may additionally be

altered dynamically by an external signal (TxEUD) to facilitate eg. position tracking.

The core timers T3 and T6 have output toggle latches (TxOTL) which change their state on each

timer over-flow/underflow. The state o f these latches may be output on port pins (TxOUT) or may be

used internally to concat enate the core timers with the respective a uxiliary timers resultin g in 32/33bit timers/counters for measuring long time periods with high resolution.

Various reload or capture functions can be selected to reload timers or capture a timer’s contents

triggered by an external signal or a selectable transition of toggle latch TxOTL.

The maximum resolution of the timers in module GPT1 is 400 ns (@ 20 MHz CPU clock). With its

maximum resolution of 200 ns (@ 20 MHz CPU clock) the GPT2 timers provide precise event

control and time measurement.

Watchdog Timer

The Watchdog Timer represents one of the fail-safe mechani sms which have been implemented to

prevent the controller from malfunctioning for longer periods of time.

The Watchdog Timer is always en abled after a reset of the chip, and can only be disabled in the time

interval until the EINIT (en d of initial ization) ins truction has been executed. Thus , the chip’ s start-up

procedure is always monitored. The software has to be designed to service the Watchdog Timer

before it overflows. If, due to hardware or software related failures, the software fails to do so, the

Watchdog Timer overflows and generates an internal ha rdware reset and pulls the RSTOUT

in order to allow external hardware components to reset.

pin low

The Watchdog Timer is a 16-bit timer, clocked with the CPU clock divided either by 2 or by 128. The

high byte of the Watchdog Timer register can be set to a prespecified reload value (stored in

WDTREL) in order to allow further variation of the monitored time interval. Each time it is serviced

by the application software, the high byte of the Watchdog Timer is reloaded. Thus, time intervals

between 25 µs and 420 ms can be monitored (@ 20 MHz). The default Watchdog Timer interval

after reset is 6.55 ms (@ 20 MHz).

Semiconductor Group 2-14

Architectural Overview / C167

Capture/Compare (CAPCOM) Units

The two CAPCOM units support generation and control of timing sequences on up to 32 channels

with a maximum resolution of 400 ns. The CAPCOM units are typically used to handle high speed

IO tasks such as pulse and wa veform generati on, pulse widt h modulation (PWM), Digital to Anal og

(D/A) conversion, software timing, or time recording relative to external events.

Four 16-bit timers (T0/T1, T7/T8) with reload registers provide two independent time bases for the

capture/compare register array.

The input clock for the timers is programmable to several prescaled values of the internal CPU

clock, or may be derived from an overflow/underflow of timer T6 in module GPT2. This provides a

wide range of variation for the timer period and resolution and allows precise adjustments to the

application specific requiremen ts. In additi on, ex ternal c ount i nputs for CAPCOM time rs T0 an d T7

allow event scheduling for the capture/compare registers relative to external events.

Both of the two capture/compare register arrays contain 16 dual purpose capture/compare

registers, each of which may be individually allocated to either CAPCOM timer T0 or T1 (T7 or T8,

respectively), and programmed for capture or compare function. Each register has one port pin

associated with it which serves as an i nput pin for triggering the capture function, or as an output pin

(except for CC24...CC27) to indicate the occurence of a compare event.

When a capture/compare register has been selected for capture mode, the current contents of the

allocated timer will be latched (captured) into the capture/compare register in response to an

external event at the port pin which is associated with this register. In addition, a specific interrupt

request for this capture/compare register is generated. Either a positive, a negative, or both a

positive and a negative external sign al trans ition at the pi n can be selected as the triggering event.

The contents of all registers which have been selected for one of the five compare modes are

continuously compared with the contents of the allocated timers. When a match occurs between the

timer value and the value in a capt ure/compare regi ster, specific acti ons wil l be take n based on the

selected compare mode.

Pulse Width Modulation Unit

The PWM Unit supports the generation of up to four independent high-spee d PWM signals. It allows

to generate standard (edge aligned) PWM signals as well as symmetrical (center aligned) PWM

signals. In Burst Mode two chann els may be comb ined wi th their out put signal s ANDed, where one

channel gates the output signal of the other channel. Single Shot Mode allows to generate single

output pulses (retriggerable) under software control. Each PWM channel is controlled by an up/

down counter with associated reload and compare regis ters. The polarity of the PWM output signals

may be controlled via the respective port output latch (combination via EXOR).

Semiconductor Group 2-15

Architectural Overview / C167

A/D Converter

For analog signal measurement, a 10-bit A/D converter with 16 multiplexed input channels and a

sample and hold circuit has been integrated on-chip. It uses the method of successive

approximation. The sample time (for loading the capacitors) and the conversion time is

programmable and can so be adjusted to the external circuitry.

Overrun error detection/protection is provided for the conversion result register (ADDAT): either an

interrupt request will be generated when the result of a previous conversion has not b een read from

the result register at the time the next conversion is complete, or the next conversi on is suspended

in such a case until the previous result has been read.

For applications which require l ess than 16 analog input channel s, the remaining channel inputs can

be used as digital input port pins.

The A/D converter of the C167 supports four different conversion modes. In the standard Single

Channel conversion mode, the analog level on a specified channel is sampled onc e and converted

to a digital result. In the Single Channel Continuous mode, the analog level on a specified channel

is repeatedly sampled and converted without software intervention. In the Auto Scan mode, the

analog levels on a prespecified number of channels are seque ntially sampled and converted. In the

Auto Scan Continuous mode, the number of prespecified channels is repeatedly sampled and

converted. In addition, the conversion of a specific channel can be inserted (injected) into a running

sequence without disturbing this sequence. This is called Channel Injection Mode.

The Peripheral Event Controller (PEC) may be used to automatically store the conversion results

into a table in memory for later evaluation, without requiring the overhead of entering and exiting

interrupt routines for each data transfer.

Semiconductor Group 2-16

Architectural Overview / C167

2.4 Protected Bits

The C167 provides a special mechanism to protect bits which can be modified by the on-chip

hardware from being changed unintentionally by software accesses to related bit s (see also chapter

“The Central Processing Unit”).

The following bits are protected:

Register Bit Name Notes