Page 1

q

SERVICE MANUAL

CODE : 00Z

XEA403USME

ELECTRONIC

CASH REGISTER

MODEL

CONTENTS

CHAPTER 1. SPECIFICATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

XE-A403

(U version)

CHAPTER 2. OPTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

CHAPTER 3. MASTER RESET AND PROGRAM RESET. . . . . . . . . 4

CHAPTER 4. HARDWARE DESCRIPTION. . . . . . . . . . . . . . . . . . . . 5

CHAPTER 5. DIAGNOSTIC PROGRAM . . . . . . . . . . . . . . . . . . . . . 10

CHAPTER 6. CIRCUIT DIAGRAM AND PWB LAYOUT . . . . . . . . . 14

Parts mark ed w ith "!" are important for maintaining the safety of the set. Be sure to replace these parts with specified

ones for maintaining the safety and performance of the set.

SHARP CORPORATION

This document has been pub lished to be used

for after sales service only.

The contents are subject to change without notice.

Page 2

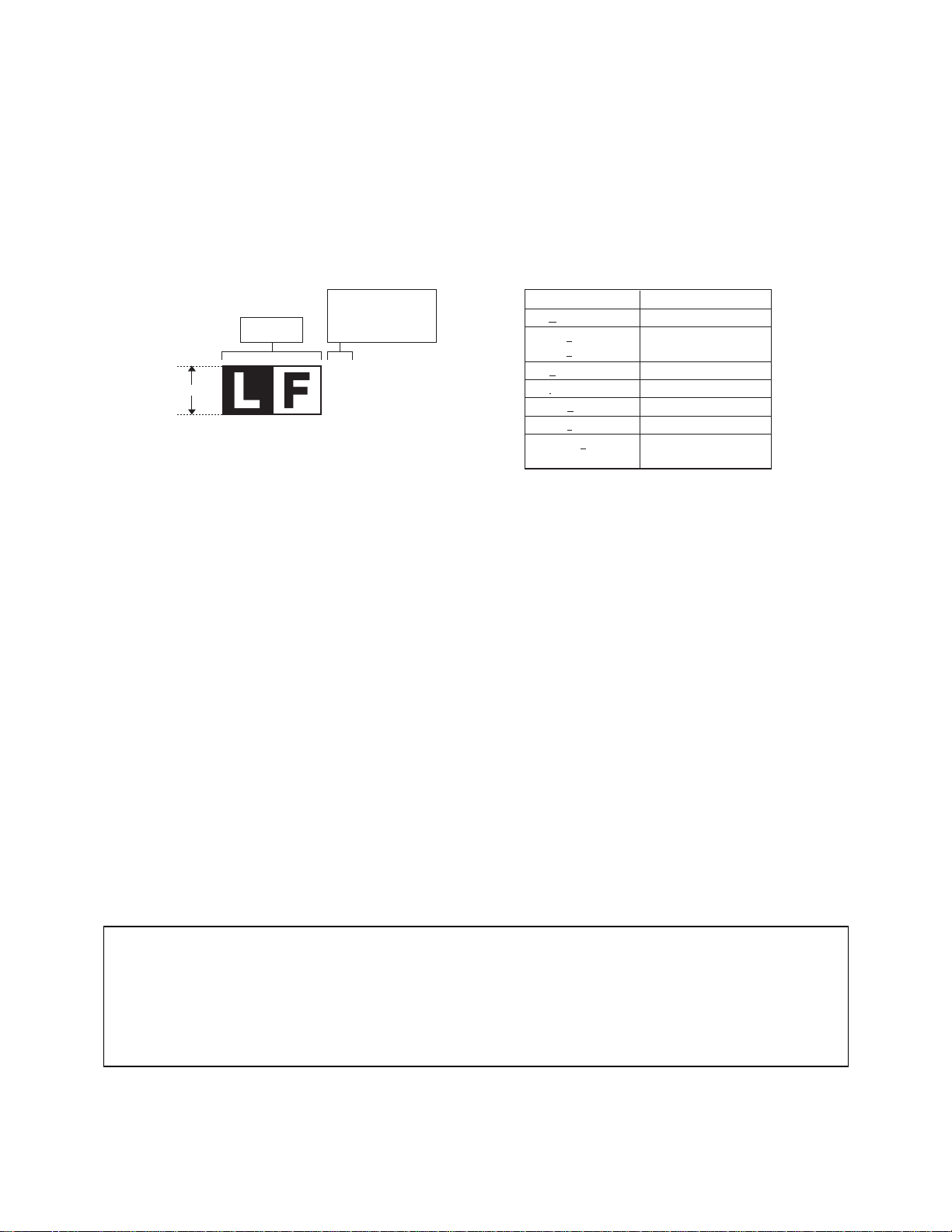

LEAD-FREE SOLDER

The PWB’s of this model employs lead-free solder. The “LF” marks indicated on the PWB’s and the Service Manual mean “Lead-Free” solder.

The alphabet following the LF mark shows the kind of lead-free solder.

Example:

<Solder composition code of lead-free solder>

Solder composition

Sn-Ag-Cu

Sn-Ag-Bi

Sn-Ag-Bi-Cu

Sn-Zn-Bi

Sn-In-Ag-Bi

Sn-Cu-Ni

Sn-Ag-Sb

Bi-Sn-Ag-P

Bi-Sn-Ag

5mm

Lead-Free

Solder composition

code (Refer to the

table at the right.)

a

(1) NOTE FOR THE USE OF LEAD-FREE SOLDER THREAD

When repairing a lead-free solder PWB, use lead-free solder thread. Never use conventional lead solder thread, which may cause a

breakdown or an accident.

Since the melting point of lead-free solder thread is about 40°C higher than that of conventional lead solder thread, the use of the exclusive-use soldering iron is recommendable.

Solder composition code

a

b

z

i

n

s

p

(2) NOTE FOR SOLDERING WORK

Since the melting point of lead-free solder is about 220°C, which is about 40°C higher than that of conventional lead solder, and its soldering capacity is inferior to conventional one, it is apt to keep the soldering iron in contact with the PWB for longer time. This may cause land

separation or may exceed the heat-resistive temperature of components. Use enough care to separate the soldering iron f rom the PWB

when completion of soldering is confirmed.

Since lead-free solder includes a greater quantity of tin, the iron tip may corrode easily. Turn ON/OFF the soldering iron power frequently.

If different-kind solder remains on the soldering iron tip, it is melted together with lead-free solder. To avoid this, clean the soldering iron tip

after completion of soldering work.

If the soldering iron tip is discolored black during soldering work, clean and file the tip with steel wool or a fine filer.

CAUTIONS

THERE IS A RISK OF EXPLOSION IF THE BATTERY

IS REPLACED BY AN INCORRECT TYPE.

PROPERLY DISPOSE OF USED BATTERIES ACCORDING

TO THE INSTRUCTIONS.

XE-A403 LEAD-FREE SOLDER

Page 3

PC-UM10M

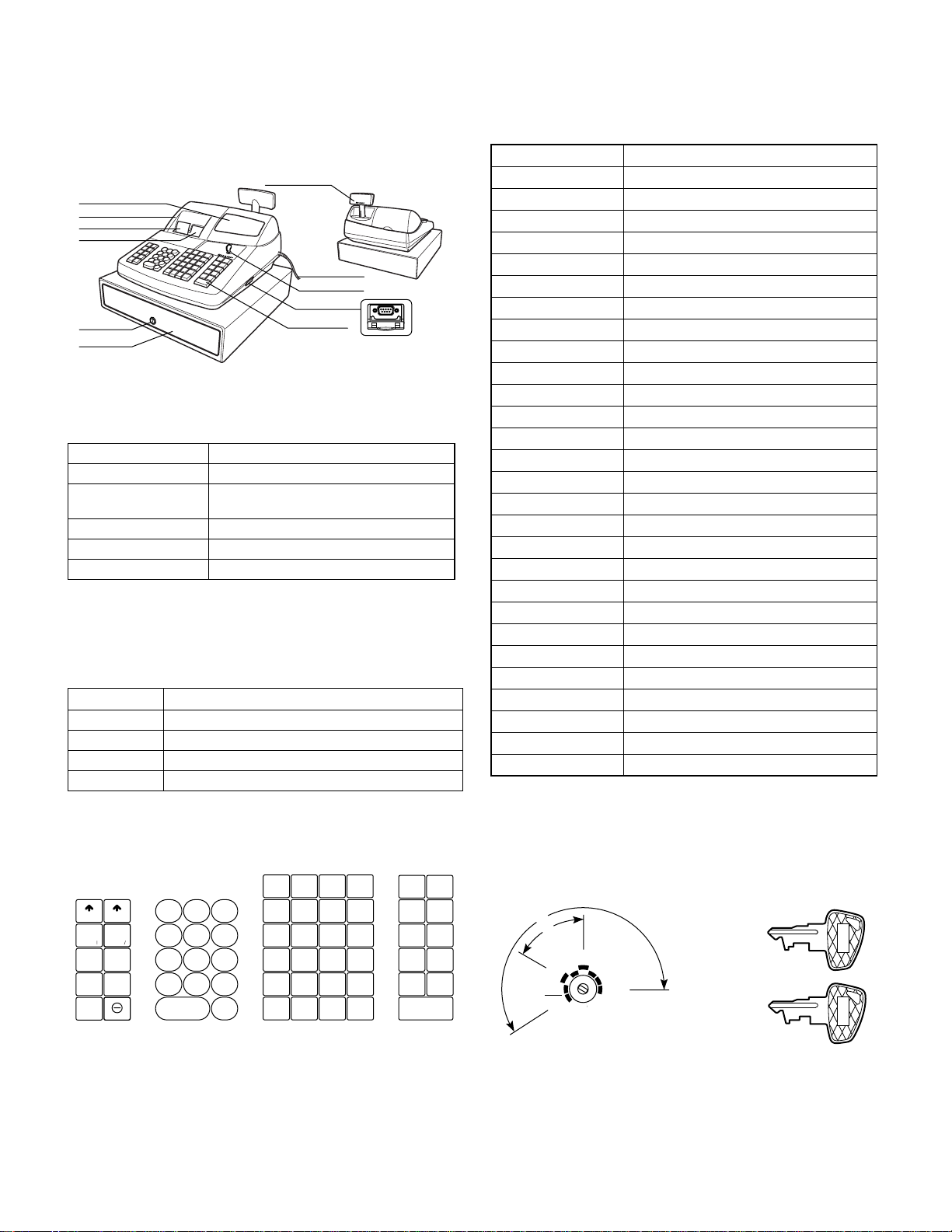

CHAPTER 1. SPECIFICATIONS

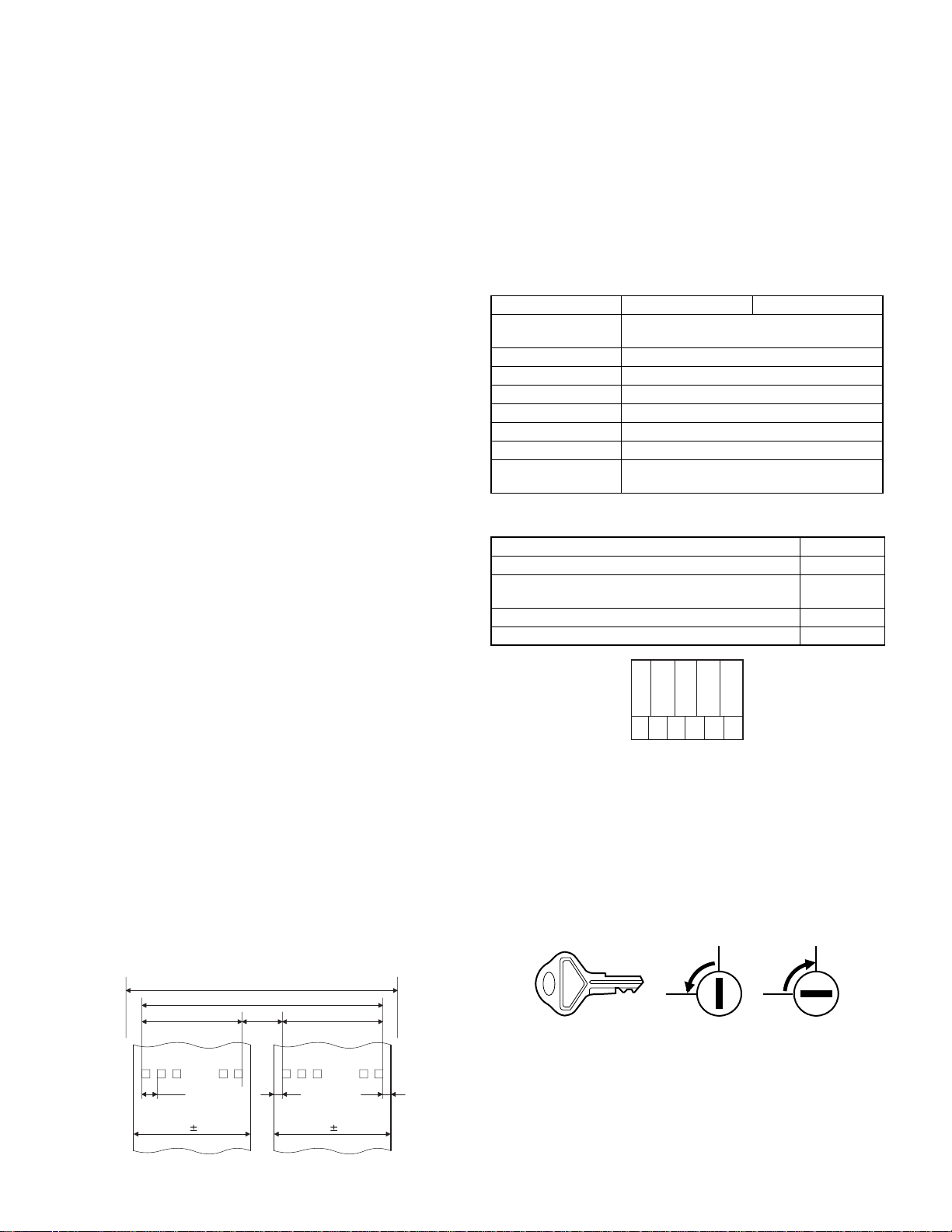

1. APPEARANCE

nFront view nRear view

Customer display

(Pop-up type)

Operator display

Printer cover

Receipt paper

Journal window

AC power cord

Mode switch

Drawer lock

Drawer

Keyboard

RS-232C connector

2. RATING

XE-A403

Weight 28.0lb (12.7kg)

Dimensions 420 (W) x 429 (D) x 297 (H) mm

16.6 (W) x 16.9 (D) x 11.7 (H) inches

Power source AC 120V (

10%), 60Hz

m

Power consumption Stand-by 9W, Operating 49W (max.)

Working temperature 0°C~40°C (32°F to 104°F)

3. KEYBOARD

3-1. KEYBOARD LAYOUT

XE-A401/A403

Type Normal keyboard

Key position STD/MAX 59

Key pitch 19 (W) x 19 (H) mm

Key layout Fixed type

Q Key names

KEY TOP DESCRIPTION

(RECEIPT) Receipt paper feed key

2

(JOURNAL)

2

RA Received-on account key

RCPT/PO Receipt print/Receipt on/off & Paid-out key

VOID Void key

ESC Escape key

%1, %2 Percent 1and 2 key

RFND Refund key

-

@/FOR Multiplication key

n

CL Clear key

0-9,00 Numeric Keys

PLU/SUB PLU/Subdepartment code entry key

DEPT# Department code entry key

DEPT SHIFT Department code entry shift key

CLK# Clerk code entry key

Dept1-40 Depar tment 1 to 40 keys

TAX Manual tax entry key

TAX 1 SHIFT Tax 1 shift key

TAX 2 SHIFT Tax 2 shift key

AUTO Automatic ally entry key

CONV Currency Conversion key

CHK Check Menu key #1

CH1, CH2 Charge 1 and 2 keys

MDSE SBTL Merchandise subtotal key

#/TM/SBTL Non-add code/Time display/Subtotal key

CA/AT/NS Total/Amount tender/Non Sale key

Journal paper feed key

Discount key

Decimal point key

3-2. KEY LIST

Keyboard layout

Q

PLU

/SUB

@/

RECEIPT JOURNAL

%1RA

RCPT

%2

/PO

NUMBER

–

VOID

RFND

SHIFT

DC

ESC

BS

SPACE

FOR

789

456

123

CL

•

0

00

5 F3010 K3515 P4020

4

3

2

1

Note: The small characters on the bottom or lower right in each key

indicates functions or characters which can be used for character

entries for text programming.

DEPT

DEPT

#

25

A

24

B

9

23

C

8

22

D

7

21

E

6

CLK

#

SHIFT

29

34

G

28

H

27

I

26

J

39

L

14

Q

19

33

38

M

13

R

18

32

37

N

12

S

17

31

36

O

11

T

16

AUTO

TAX

X

U

TAX2

TAX1

SHIFT

SHIFT

Y

V

CONVCH1

ZW

CHK CH

2

MDSE

#/TM

SBTL

SBTL

CA/AT/NS

XE-A403 SPECIFICATIONS

4. MODE SWITCH

4-1. LAYOUT

• Rotary type

MA

OP

REG

OP

MGR

X/Z

X

OFF

VOID

PGM

1/Z1

X2/Z2

The mode switch can be operated by inserting one of the two supplied

mode keys - manager (MA) and operator (OP) keys. These keys can be

inserted or removed only in the “REG” or “OFF” position.

– 1 –

Manager key (MA)

Operator key (OP)

MA

OP

Page 4

PC-UM10M

The mode switch has these settings:

OFF: This mode locks all register operations. (AC power turns off.)

No change occurs to register data.

OP X/Z: To take individual clerk X or Z reports, and to take flash

reports.

It can be used to toggle receipt state “ON” and “OFF” by press-

ing he [RCP/PO] key.

REG: For entering sales.

PGM: To program various items.

VOID

: Enters into the void mode. This mode allows correction after

finalizing a transaction.

MGR: For manager’s entries. The manager can use this mode for an

override entry.

X1/Z1: To take the X/Z report for various daily totals.

X2/Z2: To take the X/Z report for periodic (weekly or monthly) consoli-

dation.

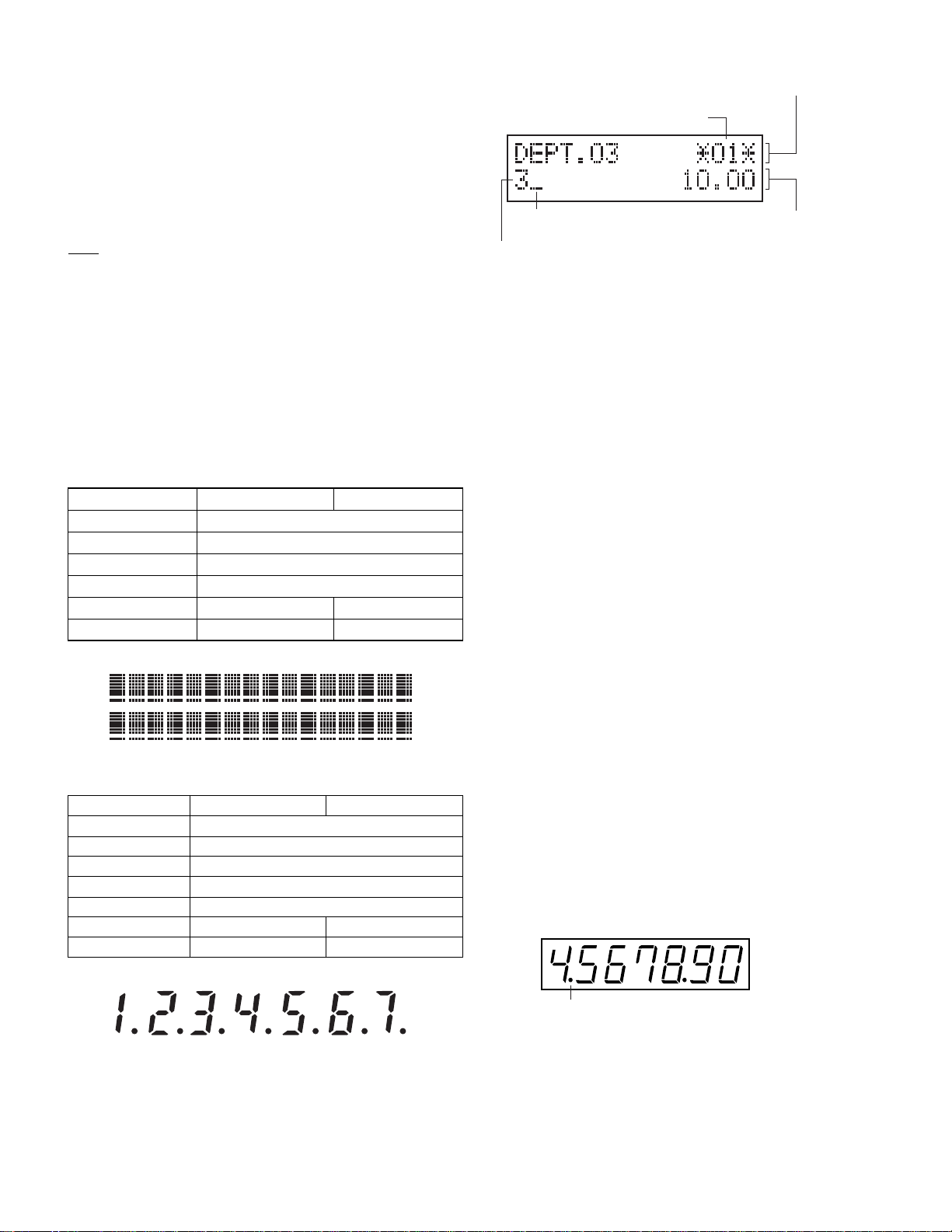

5. DISPLAY

5-1. OPERATOR DISPLAY

XE-A401 XE-A403

Display device LCD

Number of line 2 line

Number of positions 16 digits/line

Color of display Yellow / Green

Character form 7 segment + Dp 5 x 7Dot matrix

Character size 14.2 (H) x 7.9 (W) mm 8.0 (H) x 4.8 (W) mm

Layout:

5-2. CUSTOMER DISPLAY

XE-A401 XE-A403

Display device LED

Number of line 1 line

Number of positions 7 positions

Color of display Yellow / Green

Style Pop up type

Character form 7 segment + Dp 5 x 7Dot matrix

Character size

14.2 (H) x 7.9 (W) mm 14.2 (H) x 7.8 (W) mm

QOperator display

Function message display area

Clerk code or mode name

Receipt OFF indicator

Repeat / Sentinel mark / Power save mark

• Clerk code or Mode name

The mode you are in is displayed. When a clerk is ass igned, the

clerk code is displayed in the REG or OP X/Z mode. For example,

“

” is displayed when clerk 01 is assigned.

*01*

• Repeat

The number of repeats is displayed, start ing at “2” and incremental

with each repeat. When you have registered ten times, the display

will show “0” (2

• Sentinel mark

When amount in the drawer reaches the amount you prepro-

grammed, the sentinel mark “X” is displayed to advise you to remove

the money and put it in a safe place.

• Power save mark

When the cash register goes into the power save mode, the power

save mark (decimal point) lights up.

• Function message display area

Item labels of departments and PLU/subdepartments and function

texts you use, such as %1, (-) and CASH are displayed.

When an amount is to be entered or entered, “AMOUNT” is dis-

played: When an amount is to be entered, ------- is displayed at the

numeric entry area with “AMOUNT”. When a preset price has been

set, the price is displayed at the numeric entry area with “AMOUNT”.

• Numeric entry display area

Numbers entered using numeric keys are displayed here.

Date and time display

Date and time appear on the display in the OP X/Z, REG, or MGR

mode. In the REG or MGR mode, press the [#/TM/SBTL] key to display the date and time.

Error message

When an error occurs, the corresponding error message is displayed

in the function message display area.

3......9 3 0 3 1 3 2...)

3

Numeric entry display area

QCustomer display (Pop-up type)

Layout:

Power save mark

(Lighting the mark only under the power save mode)

XE-A403 SPECIFICATIONS

– 2 –

Page 5

PC-UM10M

6. PRINTER

6-1. PRINTER

• Part number : PR-45M II

• NO. of station : 2 (Receipt and journal)

• Valida tion : No

• Printing system : Line thermal

• No. of dot : Receipt: 288 dots

• Dot pitch : Horizontal: 0.125mm

• Font : 10 dots (W)

• Printing capacity : Receipt max. 24 characters

• Character size : 1.25mm (W)

• Print pitch : Column distance 1.5mm

• Print speed : Approximate 50mm/s (13.3 lines/sec)

• Paper feed speed

(Manual feed)

• Reliability : Mechanism MCBF 5 million lines

• Paper end sensor : journal side: Yes

• Cutter : Manual

• Near end sensor : No

6-2. PAPER

• Paper roll dimension: 44.5 m 0.5mm in width

Journal: 288 dots

Vertical: 0.125mm

24 dots (H)

u

Journal max. 24 characters

3.0mm (H) at 10 u 24

dots

Row distance 3.75mm

: Approximate 40mm/s

Head life 12.5 million characters

(at 4 dots/1 character/1 element)

Receipt side: Yes

Max. 80mm in diameter

u

7. DRAWER

[OUTLINE]

• Standard equipment: Yes

• Max. number of additional drawers: 0

• The drawer consists of:

1) Drawer box (outer case) and drawer

2) Coin case (for SEC)

3) Money case

4) Lock (attached to the drawer)

[SPECIFICATION]

7-1. DRAWER BOX AND DRAWER

XE-A401 XE-A403

Model name of the

drawer box

Size

color Gray (PB-N8.0)

Material Metal

Release lever Standard equipment: situated at the bottom

Bell –

Drawer open sensor –

Separation from the

main unit

7-2. MONEY CASE

Separation from the drawer Allowed

Separation of the bill compartments from the coin

compartments

Bill separator Disallowed

Number of compartments 5B/6C

SK423

420 (W) x 426 (D) x 114 (H) mm

–

SEC

Allowed

• Paper quality : (Journal/Receipt)

High-quality paper

paper thickness: 0.06 to 0.08mm

Nihon seisi thermal paper : TF50KS-E

Oji thermal paper : P D150R,

6-3. LOGO STAMP

• No

6-4. CUTTER

• Method : Manual

6-5. PRINTING AREA

Receipt & Journal

Number of themal head heater elements 864 dots

36

(288dots)

0.125

44.5 0.5

Receipt

(688dots)

(112dots)

4

3614

(288dots)

44.5 0.5

Journal

PD160R

4.5

(units;mm)

7-3. LOCK (LOCK KEY : LKGIM7331BHZZ)

• Location of the lock: Front

• Method of locking and unlocking:

•Key No: SK1-1

8. BATTERY

8-1. MEMORY BACK UP BATTERY

Built-in battery: Rechargeable batteries, memory holding time about 1

XE-A403 SPECIFICATIONS

– 3 –

5B/6C

To lock, insert the drawer lock key into the lock

and turn it 90 degrees counter clockwise.

To unlock, insert the drawer lock key and turn it

90 degrees clockwise.

k

c

o

SK1-1

month (with fully charged built-in batteries, at room temperature)

L

k

c

o

l

n

u

Page 6

CHAPTER 2. OPTIONS

1. OPTIONS (NONE)

2. SERVICE OPTIONS (NONE)

3. SUPPLIES

PC-UM10M

NO NAME PARTS CODE

1 Thermal roll paper

TPAPR6645RC05

PRICE

RANK

BA 5 ROLLS/PACK

4. SPECIAL SERVICE TOOLS

NO NAME PARTS CODE

1 RS-232 Loop-back connector

UKOG-6705RCZZ

PRICE

RANK

BU

CHAPTER 3. MASTER RESET AND PROGRAM RESET

1. MASTER RESETTING

Master resetting clears the entire memory and resumes initial values.

Master resetting can be accomplished by using the following procedure:

Procedure A: 1) Unplug the AC cord from the wall outlet.

2) Set the mode switch to the PGM position.

3) While holding down both the JOURNAL FEED key

and [CL] key, plugin the AC cord to the wall outlet.

The master reset can also be accomplished in the following case.

In case power failure occurs when the machine has no battery

attached to it, the master reset operation is automatically performed

after the power has been restored.

(This is because if power failure occurs with no battery attached to

the machine, all the memories are lost and the machine does not

work properly after power recovery; this requires the master res et

operation.)

2. PROGRAM RESETTING (INITIALIZATION)

This resetting resumes the initial program without clearing memory.

This resetting can be operated at below sequence in PGM mode.

Procedure: 1) Unplug the AC cord from the wall outlet.

2) Set the mode switch to the PGM position.

3) While holding down both JOURNAL FEED key and

RECEIPT FEED key, plugin the AC cord to the wall

outlet.

Note: In case power failure occurs when the machine has no battery

attached to it, the master reset operation is automatically performed after the power has been restored.

DESCRIPTION

DESCRIPTION

XE-A403 OPTIONS

– 4 –

Page 7

PC-UM10M

D

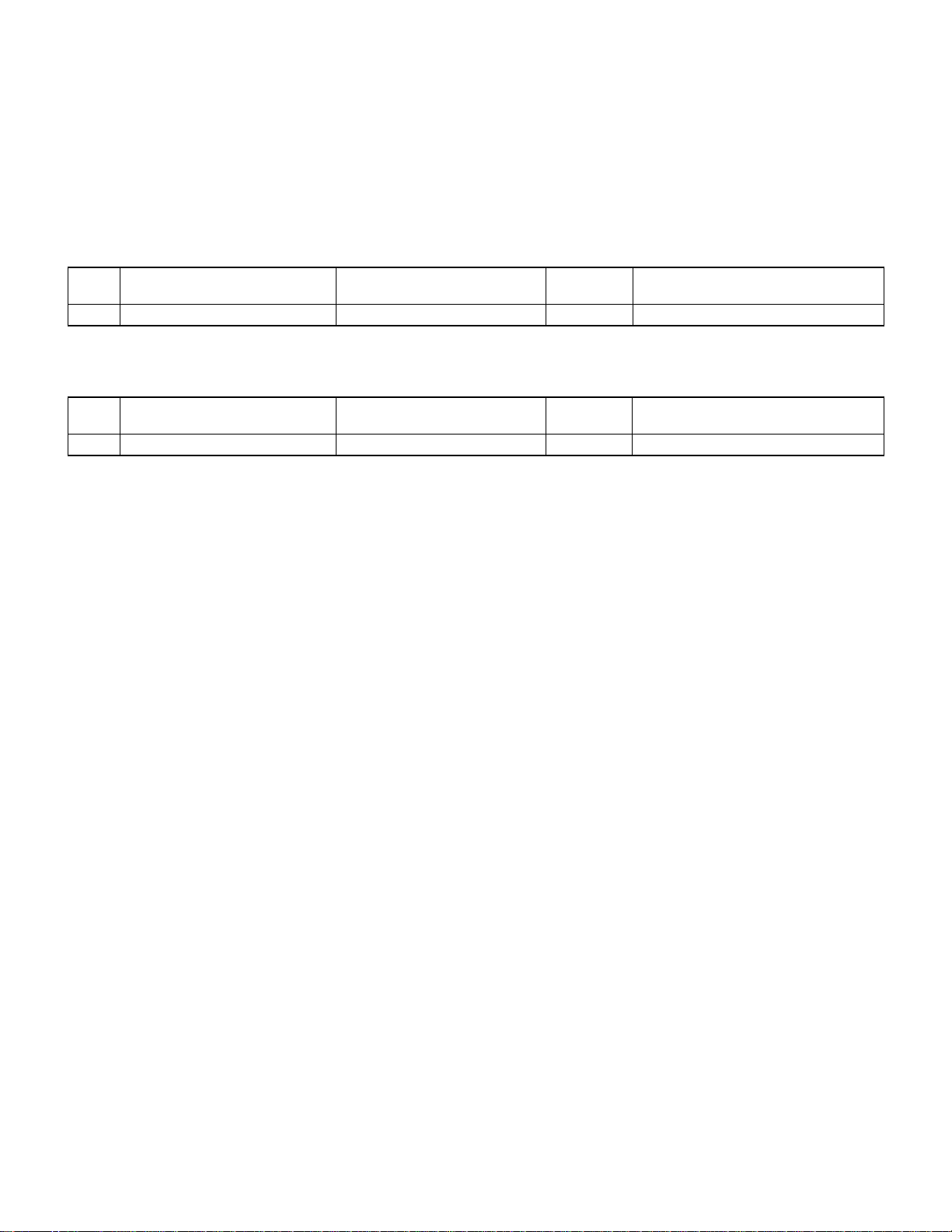

CHAPTER 4. HARDWARE DESCRIPTION

1. BLOCK DIAGRAM

XE-A403

POWER

SUPPLY

CPU

RAM 10KB

DRIVER, SENSOR

PRINTER

CPU

MITSUBISHI M30620SAFP

(INTERNAL RAM 10KB)

EXTERNAL MEMORY

RAM 256KB

FLASH ROM 512KB

SHARP LH28F004BVT

PRINTER

PR45MII

4 to 16

ECODER

KEY RETURN

RS232C

256KB

DIG DRIVER

DRAWER

RAM

SEG

LCD

16 DIGITS

POPUP

7 DIGITS

KEY & SW

2. MEMORY MAP

2-1. ADDRESS MAP

/CS0 0 0 0 0

BR0 0 1 0 1

BR1 0 0 1 1

00000h

00400h

02C00h

04000h

08000h

28000h

30000h

40000h 128KB 128KB 64KB 64KB

50000h /CS 0

80000h

C0000h

FFFFFh

Only the /CS0 area (30000h ~ FFFFFh) in the bank is valid.

2-2. EXTERNAL BUS

External BUS ACCESS SPEED

SRAM /CS2 area

FLASH ROM /CS0 area BANK 0

I/O

BANK 0 BANK 1 BANK 2 BANK 3

Internal RAM area

10KB

Internal rserved area

External I/O

External SRAM 1

128KB

External I/O

External SRAM 2External SRAM 2 External SRAM 2 External SRAM 2

IPL SW IPL SW

OFF:Flash ROM OFF: EP ROM

ON:EP RPM ON: Flash RPM

Even if the bank is changed, the same address

can be accessed.

(Cutter)

FLASH ROM FLASH ROM

256KB 256KB

SRAM/EPROM/FLASH ROM ; 2 BCLK

External I/O ; 1 BCLK *1BCLK = 83.3ns (at 12MHz)

address 08000h ~ 27FFFh 128KB

Same as ER-A235P

/CS0 area BANK 0

address 30000h ~ 4FFFFh 128KB

address 80000h ~ FFFFFh 256KB

(Moves to Bank 1 when rewritten using EPROM)

/CS3

/CS2

/CS 1

XE-A403 HARDWARE DESCRIPTION

– 5 –

Page 8

3. PRINTER CONTROL

PC-UM10M

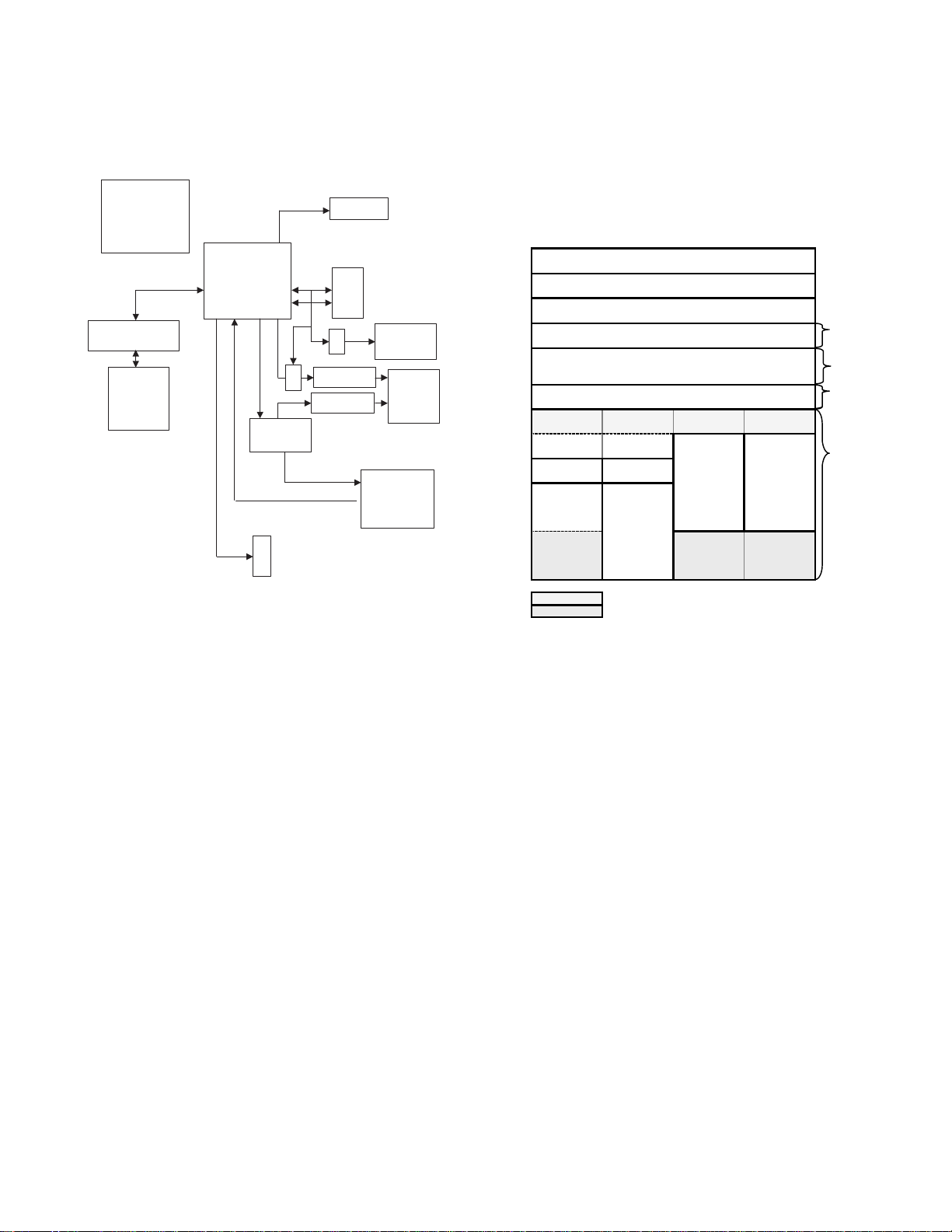

3-1. STEPPING MOTOR CONTROL

The stepping motor is driven at a constant voltage by Sanken STA471A.

1step: 0.125mm, A1dot: 1step

Printing speed 50mm/s

< CPU’s PORT >

No. CPU PORT Signal to be used

80 P10 RAS

79 P11 RBS

78 P12 RCS

77 P13 RDS

76 P14 JAS

75 P15 JBS

74 P16 JCS

73 P17 JDS

< Driving steps >

RECEIPT MOTOR

Driver IC input (CPU output) Motor driving signal

STEP RAS RBS RCS RDS /RPFA /RPFB /RPFC /RPFD

1HLLHL H H L

2LHLHHLH L

3LHHLH L L H

4HLHL L H L H

Driver IC input (CPU output) Motor driving signal

STEP JAS JBS JCS JDS /JPFA /JPFB /JPFC /JPFD

1LHHLH L L H

2LHLHHLH L

3HLLHL H H L

4HLHL L H L H

When the motor is at rest, the same phase as the final excitation

*

phase is RUSH energize for 10 ms t o turn off all phases.

RAS ~ RDS and JAS ~ JDS into L.

No energizing should be allowed at lease 30 ms after s topping the

motor before restarting.

When starting the motor, the first excitation phase is RUSH energized for 10 ms to start the motor.

Turn all

3

3-2. HEAD CONTROL

HEAD:832 dots in all. Printable range: 384 dots at receipt side; 384 dots

at journal side

Related PORT

No. CPU PORT Signal to be used

30 TXD2 SO

29 RXD2 SI

28 CLK2 PCLK

93 P103 /STRB1

92 P104 /STRB2

91 P105 /STRB3

90 P106 /STRB4

89 P107 LATCH

21 P81 VHCOM

/STB1: 1 ~ 288dot: 288 dots in all

/STB2: 289 ~ 432dot: 144 dots in all

/STB3: 433 ~ 576dot: 144 dots in all

/STB4: 577 ~ 864dot: 288 dots in all

When turning on or off the printer power s upply, make sure t o turn /

*

STB1, 2, 3, 4 to “H”.

Do not turn on without paper.

*

THERMAL HEAD power supply control : Turns ON when P81= “H”;

*

turns OFF when “L”. (The power supply for HEAD and STEPPING

MOTOR is shared). When printing is finished (when the motor is

stopped) Athe power should be turned OFF.

Before printing or feeding paper, perform A/D conversion in ** ms

*

after the printer head is turned ON and make sure the voltage is stable.

(The power supply of the printer head should be turned ON and OFF

by using the regulator IC.)

Total 864 dots

XE-A403 HARDWARE DESCRIPTION

– 6 –

Page 9

PC-UM10M

4. I/O

M16C/24 PORT MEMORY SPACE: NORMAL MODE

PROCESSOR MODE: MICRO PROCESSOR MODE

It is used by (SEPARATE BUS 8bit Width)

PIN

PORT

No.

P00 88 I/O D0 Out L P54 42 O /HLDA (NU) Out L

P01 87 I/O D1 D1 Out L P55 41 I /HOLD /HOLD In

P02 86 I/O D2 D2 Out L P56 40 O ALE (NU) Out L

P03 85 I/O D3 D3 Out L P5 7 39 I /RDY /RDY In

P04 84 I/O D4 D4 Out L P60 38 O P60 DR1 L Out L DRAWER 1 DRIVE

P05 83 I/O D5 D5 Out L P61 37 O CLK0 FSCK(NU) L Out L FMC FSCK

P06 82 I/O D6 D6 Out L P62 36 I RXD0 FRD(NU) L Out L FMC FRD

P07 81 I/O D7 D7 Out L P63 35 O TXD0 FSD (NU) L Out L FMC FSD

P10 80 O P10 RAS L Out L RECEIPT PAPER

P11 79 O P11 RBS L Out L RECEIPT PAPER

P12 78 O P12 RCS L Out L RECEIPT PAPER

P13 77 O P13 RDS L Out L RECEIPT PAPER

P14 76 O P14 JAS L Out L JOURNAL PAPER

P15 75 O P15 JBS L Out L JOURNAL PAPER

P16 74 O P16 JCS L Out L JOURNAL PAPER

P17 73 O P17 JDS L Out L JOURNAL PAPER

P20 72 O A0 A0 Out L P74 26 O P74 /ER H Out L RS-232 /ER

P21 71 O A1 A1 Out L P75 25 I P7 5 /CD In RS-232 /CD

P22 70 O A2 A2 Out L P76 24 I P7 6 /CS In RS- 232 /CS

P23 69 O A3 A3 Out L P77 23 I P7 7 /DR In RS-232 /DR

P24 68 O A4 A4 Out L P80 22 O P80 BUZZER L Out L

P25 67 O A5 A5 Out L P81 21 O P81 VHCOM L In PRINTER HEAD

P26 66 O A6 A6 Out L P 8 2 20 I /INT0 POFF In

P27 65 O A7 A7 Out L P83 19 I /INT1 /FRDY(NU) L Out L FMC /FRDY

P30 63 O A8 A8 Out L P8 4 18 O P84 /BUSY(NU) L Out L FMC #BUSY

P31 61 O A9 A9 Out L P8 5 17 I /NMI /NMI(NU) In

P32 60 O A10 A10 Out L P86 11 O

P33 59 O A11 A11 Out L P87 10 I XCIN XCIN 32.768kHz

P34 58 O A12 A12 Out L P90 7 I P90 MODE In MODE KEY SENSE

P35 57 O A13 A13 Out L P91 6 I P91 MSENS In MISCELLANEOUS

P36 56 O A14 A14 Out L P92 5 O P92 BA1 L Out L BANK signal 1

P37 55 O A15 A15 Out L P93 4 O P93 BA0 L Out L BANK signal 0

P40 54 O A16 A 16 Out L P94 3 O P94 DATA /CE L Out L LCD DATA LATCH

P41 53 O A17 A17 Out L P95 2 O P95 BLON L Out L BACK LIGHT ON

P42 52 O A18 A18 Out L P96 1 O P96 LCDON L Out L LCD POWER ON

P43 51 O A19 A19 Out L P97 100 I P9 7 IPLON In IPL ON signal

P44 50 O /CS0 /CS0 Out H P100 97 I AN0 TM In HEAD temperature

P45 49 O /CS1 /CS1 Out L P101 95 I AN1 VPTEST In HEAD voltage

P46 48 O /CS2 /CS2 Out H P102 94 I AN2 VREF In Referance voltage

P47 47 O /CS3 /CS3 Out L P103 93

P50 46 O /WR /WR Out L P104 92 O AN4 /STRB2 H In PRINTER STORE

P51 45 O /BHE (NU) Out L P10 5 91 O P105 /STRB3 H In PRINTER STORE

P52 44 O /RD /RD Out L P106 90 O P106 /STRB4 H In PRINTER STORE

P53 43 O BCLK BCLK Out L P107 89 O P107 LATCH L In PRINTER LATCH

I/O

Pin

name

Signal

name

Initial

value

OFF

MODE

Function PORT

FEED A

FEED B

FEED C

FEED D

FEED A

FEED B

FEED C

FEED D

PIN

No.

P64 34 O /RTS1 /RS H Out L RS-232 /RS

P65 33 O P65 /FRES(NU) L Out L FMC /FRES

P66 32 I RXD1 RD In RS-232 RD

P67 31 O TXD1 SD H Out L RS-232 SD

P70 30 O TXD2 SO L Out L PRINTER DATA

P71 29 I RXD2 SI In PRINTER DATA IN

P72 28 O CLK2 PCLK L Out L PRINTER CLOCK

P73 27 O P73 DR2 L Out L DRAWER 2 DRIVE

Pin

I/O

name

XCOUT

AN3 /STRB1 H In PRINTER STORE

O

Signal

name

XCOUT 32.768kHz

Initial

value

OFF

MODE

SIGNAL

OUT

SIGNAL

CONTROL

SENSE

signal

monitor

monitor

SIGNAL 1

SIGNAL 2

SIGNAL 3

SIGNAL 4

SIGNAL

Function

XE-A403 HARDWARE DESCRIPTION

– 7 –

Page 10

Power supply/CONTROL pins

PIN

PORT

BYTE 8 I BYTE Connected to VCC Vcc 62 Vcc Connected to VCC

CNVss 9 I CNVss Connected to GND Vss 64 Vss connected to GND

/RESET 12 I /RESET AVss 96 AVss Connected to GND

Xout 13 O Xout OPEN Vref 98 Vref Connected to VCC

Vss 14 Vss Connected to GND AVcc 99 AVcc Connected to VCC

Xin 15 I Xin connected to Spectram diffusion IC

Vcc 16 Vcc Connected to VCC

I/O Pin name Fu nctio n PORT

No.

PIN

I/O Pin name Function

No.

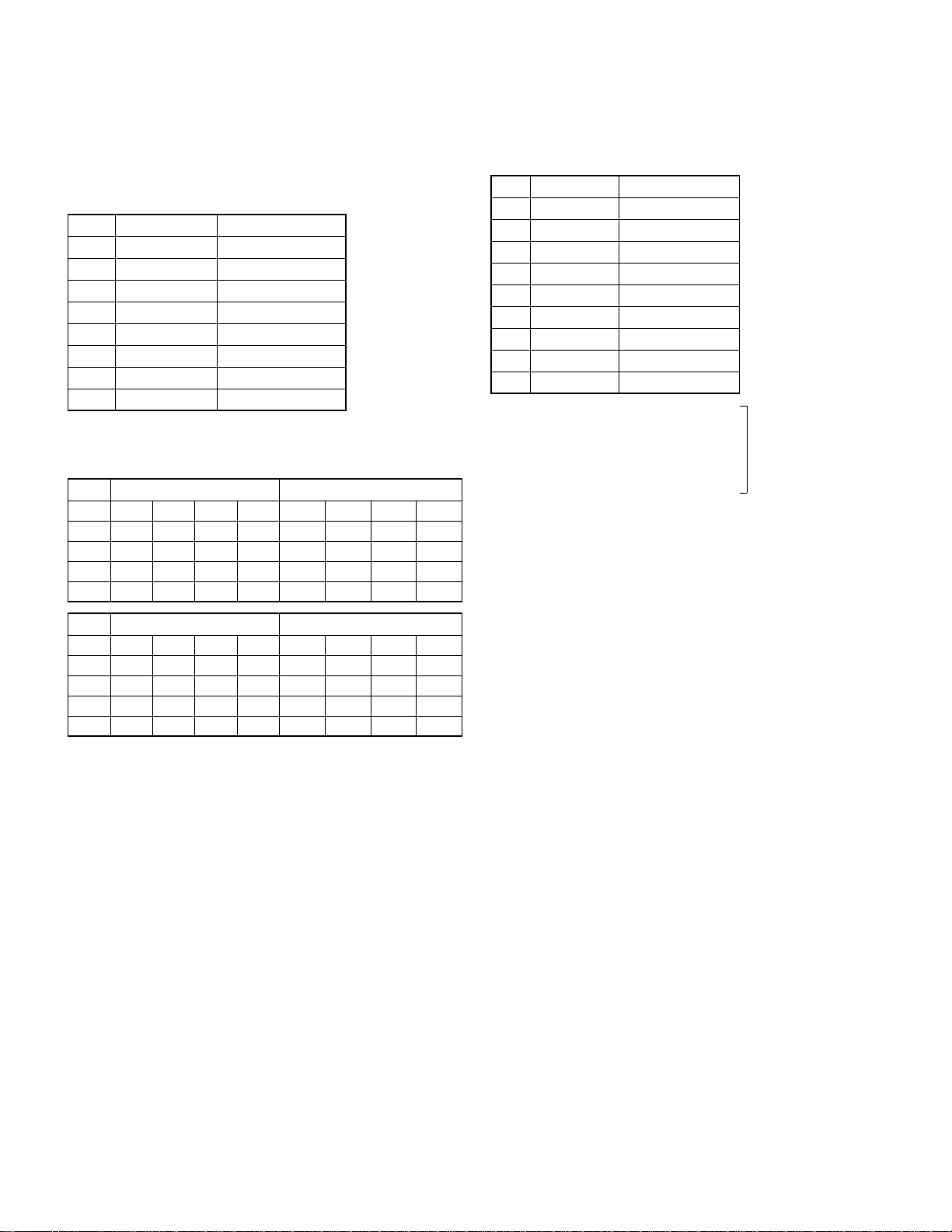

5. KEY-DISPLAY

PC-UM10M

5-1. LCD CONTROL

Basically the same as the ER-A275P.

LCD-related registers

Function Address R/W

LCD Write Data 04001h W

LCD Read Data 04002h R

LCD Control Signal / Key Strobe Signal 04003h W

Data Latch Signal CPU port P94 W

< LCD Control Signal / Key Strobe Signal >

Address Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

04003h – E R/W RS KS3 KS2 KS1 KS0

Bit7 : Not used

Bit6 : E

Enable Signal Enable

Bit5 : R/W

H : Data read L : Data Write

Bit4 : RS

H : Data input L : Instruction Input

< Data Latch Signal >

L : LCD write data latch

5-2. KEY/DISPLAY SCAN

On the A403, the key and display scan signal is common.

KEY/display SCAN and key read should be performed at the following

timing.

KEY/display SCAN cycle: 10ms

1

Blanking time: 50us

2

KEY DATA READ timing: More than 10 ms from the fall of the SCAN

3

signal

Key / Display-related registers

Function Address R/W

LED Segment Signal 04000h W

LCD Control Signal / Key Strobe Signal 04003h W

Key Return Signal 04003h R

< LED Segment Signal >

Address Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

04000h dp g f e d c b a

< LCD Control Signal / Key Strobe Signal >

Address Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

04003h - E R/W RS KS3 KS2 KS1 KS0

Bit3 ~ 0 : KS3 ~ 0

Strobe signals for keys and POP UP Display are generated at KS3 - 0.

< Key Return Signal >

Address Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

04003h KR7 KR6 KR5 KR4 KR3 KR2 KR1 KR0

XE-A403 HARDWARE DESCRIPTION

– 8 –

Page 11

PC-UM10M

5-3. KEYSCAN MATRIX

Others

CPU STO ST1 ST2 ST3 ST4 ST5 ST6 ST7 ST8 ST9

MODE P90 SRV PGM Time REG MGR X1/Z1 X2/Z2

Others P91 P F-R PF-J RPE HEAD

UP

JPE DRAWER

OPEN

MRS RS/CI

5-4. DISPLAY

The A403 has an LCD display, 5 x 7 dots, 2 lines, at the front side and a

7-digit LED at the pop-up side.

FRONT:

POP UP:

• Display DIG IT signal

The above ST0 ~ ST6 are display digit signals.

ST0: 1st digit ~ ST6: 7th digit

• Display SEGMENT signal

The LED segment signal is outputted by writing SEGMEN T data in

the /CS3 space.

Correspondence of DATA ~ SEGMENT

D0 ~ D6

D7

3

DP

3

A ~ g

7. REWRITIN G FLASH MEMORY

IPL from COM: Data from the PC is written to flash ROM through

the COM port. (Max. 38.4 kbps)

8. DRAWER

The A403 has a 1 channel of drawer port. (+ 1 channel is reserved for

the CPU PORT) O R No open sensor is provided.

The driving time for the DRAWER solenoid are as follows: 50ms (max)

45ms (min)

9. PRINT RATE

384 dots/1 line

10. A/D CONVERSION

The printer power supply voltage should be measured at more than 10

ms after the printer is turned ON.

11. BUZZER

6. POWER SUPPLY

Measures should be taken to restore within 10 ms after a

power failure occurs..

TRANS.

/POFF detection

point

LM2574 +

PQ1CG2032

24V

ON/OFF CONTROL

(MODE SW)

BATTERY

PIEZO type BUZZER

The oscillating frequency is 4.0kHz

12. RESET

The RESET signal is generated when:

1) The mode key switch is turned from SRV to a position other than

SRV’(excluding OFF).

2) The power is turned ON more than 10 seconds after the power is

turned OFF. (The reset signal may not be is sued if the POWEROFF time is short.)

3) The mode key switch is turned from OFF to a position other than OF

(excluding the SRV position). (If the power-off time is less than 5

seconds, the reset signal may not be issued.)

0.5kHz

m

XE-A403 HARDWARE DESCRIPTION

– 9 –

Page 12

CHAPTER 5. DIAGNOSTIC PROGRAM

PC-UM10M

1. TEST ITEMS

The test items are as follows:

Code Description

1) 100 Display buzzer test

2) 101 Key code

3) 102 Printer test

4) 104 Keyboard test

5) 105 Mode switch test

6) 106 Printer sensor test

7) 107 Clock display test

8) 110 Drawer 1 open & sensor test

9) 120 External RAM test

10) 121 CPU internal RAM test

11) 130 FLASH ROM test

12) 160 AD conversion port test

13) 500 RS232C test

Starting DIAG.

*

Mode switch: PGM

Key operation: Above code + “PO” key

2.

DESCRIPTION OF EACH DIAG PROG R AM

1) DISPLAY BUZZER TEST

1

Key operation

100

3

RCPT/PO

2

Test procedure

OP display

DISP

BUZZER

PGM

0123456789ABCDEF

Rear display

The decimal point on the LED and the cursor on the LCD will shift

from the lower digit to the upper digit in steps of 1 digit (every 200

msec)

After that, all segments will turn on (about 1 sec)

These two modes are repeated.

At the same time, the buzzer sounds continuously.

3

Check that:

A) Each position is correctly displayed.

B) The brightness of each number is uniform.

4.5.6.7.8.9.0.

C) The buzzer sound is normal.

4

End of testing

You can exit the test mode by pressing any key. The following is

printed.

100

2) KEY CODE

1

Key operation

101

3

RCPT/PO

2

Test procedure

OP display

3

Check that:

KEY code :

KEY

Every time a key is pressed, the hard code of that key

is displayed as a decimal number.

When a key is pressed twice or pressed in an incorrect manner, --- will be displayed.

CODE

PGM

KEY CODE

4

End of testing

You can exit the test mode by turning the mode s witch to a pos ition

other than the PGM mode. The printer prints as follows:

XE-A403 DIAGNOSTIC PROGRAM

– 10 –

101

Page 13

PC-UM10M

3) PRINTER TEST

1

Key operation

102

3

RCPT/PO

2

Test procedure

OP display

At the receipt side, the logo is also printed and the receipt is issued.

Check that:

3

The print is free from contamination, blur, and uneven density.

End of testing

4

The test will end automatically.

R/J

5 lines of 24 digits are printed.

PRINTER

PGM

Enlargement

4) KEYBOARD TEST

Key operation

1

_ _ _ _104

2

KEY check sum code

Test procedure

2

The keyboard is checked using the sum check code of the key code.

If the sum check code is not entered, the check is made using the

sum check code of the default keyboard arrangement

The sum check data for each model is entered to the front 4 digits of

the DIAG code, and that data is compared with the key data added

until the final key (CA/AT) is pressed.

Both data are the same, the test ends, printing the number given

below.

If both data are different, the printer prints the error message.

OP display

3

RCPT/PO

KEY

BOARD

PGM

104

5) MODE SWITCH TEST

1

Key operation

3

105

2

Test procedure

OP display

MODE: PGM_VOID_OFF_OP X/Z_REG_MGR_X1/Z1_X2/Z2__PGM

X :

The above X must be rea d in the correct order. (If the contact is

open, 9 will be displayed.)

3

Check:

The display during testing and the content of the completion print.

4

End of testing

When the test ends normally

When an error occurs: E – ~ –

RCPT/PO

MODE

SW

105

129 34567 1

PGM

X

105

105

6) PRINTER SENSOR TEST

1

Key operation

3

106

2

Test procedure

Check the status of the paper end sensor and head up sensor.

OP display

3

Check the following.

X:

Y:

4

End of testing

You can exit the test mode by pressing any key and the printer prints

the following.

RCPT/PO

R/J

SENSOR

106

1 - Paper present at the receipt side

O - No paper at the receipt side

1 - Paper present at the journal side

O - No paper at the journal side

PGM

XY

106

Check:

3

A) The content of completion print

End of testing

4

When the test ends normally:

When an error occurs: E – ~ –

Note: Calculation of key sum check data

Hard codes (hexadecimal number) at the position (excluding feed

key) where there is an input data contact are added.

However, the end key (TL) is not added.

This data to which hard codes have been added is converted into

a decimal number value, which will become the sum check data

that will be entered when DIAG is started.

KEY CODE

104

104

XE-A403 DIAGNOSTIC PROGRAM

– 11 –

7) CLOCK TEST

1

Key operation

107

3

RCPT/PO

2

Test procedure

OP display

TIM

ER

104

3

Check that:

“–“ blinks and the clock counts up.

CHECK

Hour

Blinks at an interval of 0.5 sec.

PGM

Min. Sec.

Page 14

PC-UM10M

4

End of testing

When any key is pressed, the date and time are printed and the test

mode will be terminated.

107 XXXXXX XXXXXX

day

hour

min.

sec.

year

month

8) DRAWER 1 OPEN & SENSOR TEST

1

Key operation

110

3

RCPT/PO

2

Test procedure

OP display

3

Check that:

A) The drawer 1 opens normally.

B) The sensor correctly indicates the status of the drawer 1.

On the XE-A403, “C” (CLOSED) is always displayed.

*

4

End of testing

You can exit the test mode by pressing any key. The printer prints

the following.

DRAWER

X : O = DRAWER OPENED

C = DRAWER CLOSED

1

PGM

110

9) EXTERNAL RAM TEST

1

Key operation

3

120

2

Test procedure

The standard 256 Kbyte RAM is checked.

The contents of memory must be stored before and after this test.

RAM (08000H27FFFH area and 40000H5FFFFH area) is

tested in the following procedure:

a) Store data in the test areas

b) Write “00H”

c) Read and compare “00H” and then write”55H”

d) Read and compare “55H” and then write “AAH”

e) Read and compare “AAH”

f) Restore stored data

If an error occurs at a step, the error is printed.

If any error does not occur, the following addresses are checked in

turns.

Addresses to be checked:

RCPT/PO

10000H , 10001H , 10002H , 10004H , 10008H ,

10010H , 10020H , 10040H , 10080H ,

10100H , 10200H , 10400H , 10800H ,

11000H , 12000H , 14000H , 18000H ,

20000H

40000H , 40001H , 40002H , 40004H , 40008H ,

40010H , 40020H , 40040H , 40080H ,

40100H , 40200H , 40400H , 40800H ,

XE-A403 DIAGNOSTIC PROGRAM

41000H , 42000H , 44000H , 48000H ,

50000H

OP display

RAM

PGM

120

3

Check:

A) The completion print.

4

End of testing

The program ends after printing as follows:

When the test ends normally: 120

When the test end abnormally: Ex – ~ – 120

*****

x = 1:Data error

x = 2:Address error

X

When an error occurs, the printer outputs the error message and the

address where the error has occurred in the area

*****

.

10) CPU INTERNAL RAM TEST

1

Key operation

121

3

RCPT/PO

2

Test procedure

The test program tests internal RAM (10 Kbytes) of the CPU.

The contents of memory must be stored before and after this test.

RAM (00400H ~ 02BFFH area) is tested in the following procedure.

a) Store data in the test area.

b) Write “00H”

c) Read and compare “00H” and then write “55H”

d) Read and compare “55H” and then write “AAH”

e) Read and compare “AAH”

f) Restore stored data

If an error occurs at a step, the error is printed.

If any error does not occur, the following addresses are checked

in turns.

Addresses to be checked:

01000H , 01001H , 01002H , 01004H , 01008H

01010H , 01020H , 01040H , 01080H ,

01100H , 01200H , 01400H , 01800H ,

02000H

OP display

RAMCPU

PGM

121

3

Check:

The completion print.

4

End of testing

The test program ends after printing.

When the test ends normally: 121

When the test ends abnormally: Ex – ~ – 121

*****

x = 1:Data error

x = 2:Address error

If an error occurs, the printer outputs the error message and the

address where the error has occurred in the area

– 12 –

*****

.

Page 15

PC-UM10M

11) FLASH ROM TEST

1

Key operation

130

3

RCPT/PO

Test procedure

2

The test program checks that the checksum of the flash ROM

(BANK0F80000H ~ FFFFFH).

The lower two digits of the checksum should be 10H.

OP display

ROMFLASH

PGM

130

Check:

3

The completion print.

End of testing

4

The test will automatically be terminated and the printer prints as follows:

When the test ends normally: 130

When the test ends

abnormally:

ROM

E

– – ~ – –

ROM

********

********

********

********

(Model name)

(Version)

(Model name)

(Version)

130

Data communication check

A loopback test of 256-byte data between is performed.

DATA: $00 - $FF BAUD RATE :9600 BPS

OP display

232

RS TEST

C

500

Check:

3

The completion print.

End of testing

4

Completion print RS TEST OK

Error print RS TEST **NG**ERxx

xx Contents of error

01 ER DR error

02 ER CI error

03 RS CD error

04 RS CD error

05 SD RD error DATA error

06 SD RD error DATA error/framing error

3. KEY CODE TABLE

XE

A403

PGM

12)AD CONVERSION PORT TEST

1

Key operation

3

160

Test procedure

2

The test program displays the voltage of each AD conversion port.

OP display

Display

RCPT/PO

TM

=

PGM

160

OP display

VRF

=

PGM

160

OP display

VPTEST

=

PGM

160

End of testing

13) RS232C TEST

Install the RS232C loopback connector.

1

Key operation

500

3

RCPT/PO

Test procedure

2

The test program checks the control signals.

RF

JF

037

033

048

032

054

038

055

039

CHECK SUM :

052

050

053

128

132

130

133

129

118

4075

116

114

117

113

112

083

084

082

085

081

102

067

068

066

069

080

103

147

146

149

065

086

087

148

018

145

064

070

071

003

002

017

016

022

004

005

001

000

006

007

OUTPUT INPUT

/ER /RS /DR /CI /CD /CS

OFFOFFOFFOFFOFFOFF

OFF ON OFF OFF ON ON

ON OFF ON ON OFF OFF

ON ON ON ON ON ON

XE-A403 DIAGNOSTIC PROGRAM

– 13 –

Page 16

PC-UM10M

Vcc:20pin

GND:10pin

FSCK

FRD

FSD

/FRES

/FRDY

150pF*10(C19-C28)

/BUSY

150pF*8(C1-C8)

100pF*8(C9-C16)

D0 a

D1 b

D2 c

D3

d

D4 e

D5

f

D6 g

D7

dp

/CS3

A16 A15

A14

A12

A7

A13

A6

A8

A5A9A4 A11

A3

A2

A10A1D7

D0

D6

D1

D5

D2 D4

D3

A16

A15

A14

A12

A7 A13

A6 A8

A5 A9

A4

A11

A3

A2 A10

A1

D7

D0 D6

D1 D5

D2 D4

D3

D[0..7]

A[0..19]

A0

A0

P64

P66

P67

P74

P75

P76

P77

P95

P96

A0A1A2A3A4A5A6

A7

JAS

JBS

A8A9A10

A11

A12

A13

A14

A15

A16

A17

VHCOM

/POFF

D0

D1D2D3

D4D5D6

D7

cde

f

g

dp

DR1

A19

a

b

DR2

/RESET

/CS0

/CS2

/WR

/RD

BCLK

/RDY

/WR

/RD

/CS2

RAS

RBS

RCS

RDS

JCS

JDS

A18

/CS3

SI

SO

PCLK

TM

VPT

EST

/RAMCS

P94

/LE0W

/STRB4

/STRB3

/STRB1

P91

P90

/CS1

BA0

BA1

/LATCH

/RES

VREF

IPLON

/POFF

/RES

/STRB2

VDD

VCC

VCC

VDD

VDD

VDD

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VDD

VCC

VDD

VDD

VCC

VCC

VDD

VCC

VCC

VDD

VDD

C55

0.1uF

IC34

KIA7045F

1

2

3

C23

C39

0.1uF

R1

10K

R21 100

+

C56

(10uF/50V)

R53

100

R36

10K

R2

10K

R7

10K

C12

R54

100

R30

10K

R8

10K

R43

47K

R9

10K

R57 2.2K

C7

R151

33K

R20 100

R47

10K

C16

C29

30pF

R66

10K

R63

10K

R143

10K

C19

C24

R3

10K

R64

10K

IC4

1MSRAM LP621024D-T 70ns

1

2

3

456

7

8

9

10

111213

14

15

16

171819202122232425262728293031

32

NC

A16

A14

A12A7A6

A5

A4A3A2

A1

A0

I/O0

I/O1

I/O2

VSS I/O3

I/O4

I/O5

I/O6

T/O7

CS1

A10OEA11

A9

A8

A13

WE

CS2

A15

VCC

C25

D17

1SS355

R48

10K

R58 2.2K

C11

+

C43

(10uF/50V)

C10

R31

10K

R67

10K

R141

1K

R26

10K

C53

R10

10K

C8

R11

10K

R19

100

C26

C42

150pF

X2

CST12.

0

M

TW

2

3

1

R16

10K

R17

100

R59 2.2K

C50

150pF

Q18

C3198

C62

100pF

C30

100pF

C15

C20

R52

470

R4

10K

C49

0.1uF

C54

330pFx3

C9

R22

100

R46

10K

R38

10K

IC1

M30624FGFP

8180828384858687888990

919293949596979899

100

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

424140

393837

363534

333231

D7D8D6D5D4D3D2D1D0

AN7

AN6

AN5

AN4

AN3

AN2

AN1

AVSS

AN0

VREF

AVCC

SIN4

SO

U

T4

CLK

4

TB4

IN

TB

3IN

SOUT3

SI

N

3

CLK3

BYTE

C

N

VSS

XC

I

N

XC

OUT

RESE

T

XO

U

T

VSS

XI

N

VC

C

NM

I

INT2

INT

1

INT

0

TA4IN/U

TA

4

OUT/

U

TB

3IN

TB

EOU

T

TA

2

INW

TA2OUTW

TA1IN/V

TA

1

OUT/

V

TB5I

N

TB5OU

T

D9

D10

D11

D12

D13

D14

D15

A0

A1

A2

A3

A4

A5

A6

A7

VSS

A8

VC

C

A9

A1

0

A11

A1

2

A1

3

A14

A1

5

A16

A17

A1

8

A1

9

CS0

CS1

CS2

CS3

WR

BHE

RD

CBCLK

HLDA

HOLD

ALE

CLKOUT

RTS0

CLK0

RXD0

TXD0

CLKS1

CLK1

RXD1

TXD1

R12

10K

R18

100

C40

(30pF)

C2

R32

10K

R41

47K

C27

R60 2.2K

C60

R27

10K

R39

47K

D18

1SS355

C57

C21

R5

10K

C1

C14

C58

R51

10K

C59

R65 2.2K

R61 2.2K

R68

R37

10K

R69

R13

10K

R71

R153

330

R70

IC6

1MSRAM LP621024D-T 70ns

1

2345678

9

10

11

12

131415

16 17

1819202122

23

24

25

26272829303132

NC

A16

A14

A12A7A6A5A4A3A2A1A0

I/O0

I/O1

I/O2

VSS I/O3

I/O4

I/O5

I/O6

T/O7

CS1

A10

OE

A9

A8

A13

WE

CS2

A15

VCC

R73

10K

R72

10Kx5

C3

C61

330pFx5

R33

10K

C28

C22

R42

47K

B

+

BZ1

PIEZO BZ

R28

10K

C13

R62

2.2K

C18

27pF

+

C31

10uF/10V,OS

C41

(30pF)

D19

1SS355

R23

330

R24

0

X1

32.768KHz

R55 2.2K

C17

18pF

R14

10K

C130

1uF

C51

150pF

C4

R34

10K

C5

R152

33K

R40

10k

IC2

74HC273

347

8

13

141718

11

1

2

569

12

15

16

19

D1

D2

D3

D4D5D6

D7D8CLK

CLR

Q1

Q2Q3Q4Q5Q6Q7Q8

R45

1K

R6

10K

R29

10K

C32

0.1uF

C52

R15

10K

C6

R44

10K

R56 2.2K

C38

0.1uF

R35

10K

D

1/7

1

2

3

87654

CHAPTER 6. CIRCUIT DIAGRAM AND PWB LAYOUT

CPU

CIRCUIT DIAGRAM

D

/RAMCS

VCC

D5

D6

D3

171819202122232425262728293031

CS1

I/O4

I/O5

I/O6

T/O7

I/O2

A1

I/O1

A0

I/O0

A0

D0

D2 D4

D1

R44

10K

R66

10K

R67

10K

VCC

R43

R42

R41

C62

100pF

C30

100pF

TB5OU

30

TB5I

29

TA1OUT/

28

TA1IN/V

27

TA2OUTW

26

TA2INW

25

TBEOUT

24

TB

23

TA

22

TA4IN/U

21

INT

20

INT

19

INT2

18

NM

17

VC

16

N

XI

15

VSS

14

XOUT

13

RESE

12

XCOU

11

XCIN

10

NVSS

C

9

BYTE

8

CLK3

7

SIN3

6

SOUT3

5

TB

4

TB4

3

CLK

2

SOUT4

1

VDD

/STRB4

/STRB3

/STRB2

/LATCH

B

/RD

C41

(30pF)

R47

10K

VDD

VSS I/O3

1MSRAM LP621024D-T 70ns

PCLK

SI

SO

C53

C52

C54

DR2

47K

47K

47K

/FRDY

/BUSY

R51

10K

R52

C60

C57

C58

330pFx5

C59

C61

/STRB1

VCC

VCC

B

IC6

P74

P96

/RES

/RESET

R153

VCC

NC

1

P75

P95

470

330

VDD

A15

2829303132

WE

A15

CS2

A14

A16

A12A7A6A5A4A3A2A1A0

456

2

3

A12

A16

A14

330pFx3

P77

P76

P94

BA0

BA1

C49

0.1uF

Q18

C3198

C130

3

IC34

2

1

/CS2

10K

R48

C42

150pF

D3

D7

A11

20

2122232425

17

18

27

19

26

A9

A8

A10OEA11

A13

7

A5 A9

A7 A13

A6 A8

VHCOM

2.2K

R65

P91

P90

R141

D17

1uF

KIA7045F

8

A4

1K

1SS355

I/O3

I/O4

I/O5

I/O6

CS1

T/O7

I/O2

VSS

I/O0

I/O1

9

12

13

15

11

14

10

16

1MSRAM LP621024D-T 70ns

D2 D4

D1 D5

A1

A3

A0

D0 D6

A2 A10

+

B

BZ1

PIEZO BZ

1K

R45

/POFF

VDD

C32

0.1uF

+

C31

10uF/10V,OS

3

2

1

0

R24

X2

330

R23

C18

27pF

X1

R152

33K

R151

33K

C17

18pF

C

VCC

R46

VDD

/RES

1SS355

IC4

30pF

/WR

BCLK

/RD

VDD

RD

WR

BHE

HLDA

HOLD

CBCLK

AN7

AN6

88

8990919293949596979899

87

100

R22

R21 100

R20 100

C16

C15

C14

C13

C12

C11

C10

C9

D0

D1D2D3

100pF*8(C9-C16)

– 14 –

/WR

C40

10K

A13

A8

32

A8

WE

A13

A15

CS2

VCC

A12A7A6

NC

A16

A14

123456789

A14

A16 A15

A5A9A4 A11

A12

A7

A6

DR1

/RDY

FSCK

FSD

FRD

ALE

CLK0

TXD0

RTS0

RXD0

CLKOUT

AN5

AN4

AN3

AN2

AN1

AVSS

EST

VREF

VPT

R71

VCC

R70

R69

R68

R72

A9

A5

P64

CLKS1

AN0

TM

(30pF)

A11

A4A3A2

/FRES

CLK1

VREF

VDD

A3

V

U

10Kx5

A10A1D7

OE

A10

10111213141516

A2

VCC

P67

P66

TXD1

RXD1

T

N

3IN

OUT/

4

0

1

I

C

T

T

3IN

IN

4

AVCC

SIN4

100

IPLON

+

VDD

C56

(10uF/50V)

C55

0.1uF

10K

R35

10K

R34

R33

10K

10K

R32

R31

10K

10K

R30

R29

10K

10K

R28

R27

10K

VCC

10K

R26

R8

10K

R7

10K

10K

R6

R5

10K

10K

R4

10K

R3

R2

10K

VCC

R1

10K

A7

A8A9A10

0.1uF

C38

VCC

A11

A12

A13

A0A1A2A3A4A5A6

D[0..7]

A[0..19]

VCC

A14

A15

A16

A17

C28

C27

C26

C25

C24

C23

C22

C21

C20

C19

2.2K

2.2K

R56

R59

R55 2.2K

R60 2.2K

R58 2.2K

R61 2.2K

R57 2.2K

JAS

JBS

JCS

JDS

RCS

RDS

b

a

aD1b

5

2

Q2Q3Q4Q5Q6Q7Q8

Q1

IC2

D2

D1

3

478

D0

R64

10K

10K

R63

150pF*10(C19-C28)

C8

C7

C6

C5

C4

C3

C2

C1

2.2K

150pF*8(C1-C8)

R62

RAS

RBS

6

D2cD3

c

d

9

D3

A18

d

e

e

121516

D4D5D6

13

D4

A19

f

f

141718

D5

VCC

VDD

C51

C50

C

g

dp

dp

GND:10pin

Vcc:20pin

19

74HC273

D7D8CLK

CLR

1

11

D18

D6gD7

R143

VCC

/LE0W

R40

VCC

/CS0

47K

R39

R38

10K

R37

10K

R73

10K

R36

10K

150pF

50

49484746454443424140393837363534333231

150pF

CS0

9

A1

51

A1

8

52

A17

53

A16

54

A1

5

55

A14

56

3

A1

57

A1

2

58

A11

59

A1

0

60

A9

61

C

VC

62

A8

63

VSS

64

A7

65

A6

66

A5

67

A4

68

A3

69

A2

70

A1

71

A0

72

D15

73

D14

74

D13

75

D12

76

D11

77

D10

78

D9

79

D8

80

D7

IC1

81

82

M30624FGFP

100

100

R53

R54

R16

10K

R15

10K

R14

10K

R13

10K

R12

10K

R11

10K

R10

10K

VCC

R9

10K

D7

/POFF

1SS355

D19

10K

/CS3

10k

C29

/CS3

/CS1

/CS2

CS2

CS3

CS1

D6D5D4D3D2D1D0

83

848586

100

100

100

R18

R17

R19

D4D5D6

XE-A403 CIRCUIT DIAGRAM AND PWB LAYOUT

VDD

TW

M

0

CST12.

32.768KHz

A

+

C43

(10uF/50V)

C39

0.1uF

1

432

765

8

A

Page 17

PC-UM10M

D

C

B

E

DRAWER1

CN2

STRAIGHT

3

2

CON

1

DR CN(3Pin)5045-03A

CN3

FB2

1SR154-400

D21

C97

0.1uF

CON

RIGHT-ANGL

123

<DR CN(3Pin)5046-03A>

JUMPER

Q12

2SD2170

A

1

2

3

FB1 JUMPER

F2

V

24

+

T400mA/250V

C132

R107

+

DR1

1.8K

D22

10uF/50V

5

1SS35

4

CIM31J601NE

CIM31J601NE

CIM31J601NE

FB33

FB32

FB34

CIM31J601NE

FB35

54321

/JPFB

/JPFC

VCC

VLED

VCC

CN6

40

VH

39

40

CUTM+

CUTM-

37

38

C96

CUTS

0.1uF

a

VJCOM

b

a

bcd

/JPFA

c

/JPES

/JPFD

313233343536373839

d

efg

dp

f

e

g

dp

TM1

KS3

KS2

/STRB4

KS1

VH

/STRB3SOSI

KR1

P91

/RESET

KR0

P90

KS0

1

P90P9

KR1

/RESET

KR0

KR2

KR2

KR3

PCLK

KR3

KR4

876

2

DRIVER 2/7

3

1

456

123

7891011

45678

9

10

F

FOR KEY I/

CN5

D

1213141516

111213

14

C

17

181920212223242526

18

192021222324252627282930313233343536373839

151617

CIM31J601NE

FB36 CIM31J601NE

FB37

/LATCH

/STRB2

/STRB1

KR4

KR5

KR6

KR7

KR5

KR6

KR7

2728293031

/RPES

101112131415161718192021222324252627282930313233343536

8

9

9

101112131415161718192021222324252627282930

/VON

/S9

/S9

/VON

32333435363738

VRCOM

6

7

/S2

/S2

/S3

/RPFA

5

/S3

/S4

/RPFB

/RPFC

4

/S4

/S5

/S5

/S6

PHUPS

/RPFD

2345678

/S6

/S7

/S7

39

B

R111

16KF

R112

3.6KF

5

D8

1SS35

VCC

65

123

1

PRINT CN(40Pin)6229 640 003 800+

EST

VPT

7

8

40

40

KEY I/F RELAY CN(40Pin)40FE-BT-VK-N

A

XE-A403 CIRCUIT DIAGRAM AND PWB LAYOUT

– 15 –

Page 18

PC-UM10M

D

C65

IC11

A16 A17

+

C64

A0

47

464544

48

A16

GND

BYTE#

A13

A15

A14

1

2

3

4

A15

A14

A13

VCC

VCC

21

3

D[0..7]

A[0..19]

4

VCC

/RAMCS

0.1uF

10uF/50V

D7

D6

434241

DQ7

DQ14

DQ15/A-1

A11

A12

A10A9A8

678

5

A10

A12

A11

D5

4039383736

DQ6

DQ13

9

A9

C

D4

DQ4

DQ5

DQ12

WE#

NC

NC

1011121314

/WR

VCC

RP#

/RES

35

DQ11

VPP

34

DQ3

DQ10

RY/BY#

WP#

15

D2

33

16

32

DQ9

DQ2

A17

NC

171819

A18

B

/RD

/RD

D6D3D3

D7

A11

A10

21

22

20

232425

A9

CE

OE

A10

A11

A4

A3

A0D0D1D2GND D3

A2

A1

9

8

121314

10

11

A2

A1

A0

D0

A3

DQ1

A7

A1

D0

VCC

28

27

30

29

25

26

CE#

OE#

DQ8

DQ0

GND

C63

0.1uF

A6

A5

A4A3A2

A1 A0

20

212223

24

4M FLASH ROM LH28F400BVE-BL85

VCC

A7

A6

A4A3A2

A5

IC12

32

VCC

VPP

1

31

30

A17

A18/PGM

A16

A15

2

3

A16 A18

A15 A17

A8

26

29

27

28

A8

A13

A14

A12

A7A6A5

4

567

A5A9A4

A12 A14

A7 A13

A6

D1

31

A8

D5

D4

18

19

D4

D5D6D7

15

16 17

D2

D1

A

1

2

IC SOCKET(4M ROM)

3

4

R144

10K

C127

VDD

IC9A

R150

10K

VCC

R149

10K

VDD

8765

150pF

13

VDD

IC9B

74LV11A

3

IC13

IC33D

6

4

16

VCC

A

123

BA0

12

5

11

12

1

2

BAJ

74LV11A

15

BCG2A

4

A19

13

IC9C

VDD

11

121314

Y4Y3Y2Y1Y0

G2B

G1

5

6

BA1

/CS0

(74LV00A)

9

7

10

Y5

Y7

8

10

9

8

11

Y6

GND

*IC33

74LV11A

*IC9

74LV138A

14Pin:GND

7Pin:VCC

14Pin:GND

7Pin:VDD

VDD

VCC

R142

C66

10K

0.1uF

S1

1 ROM

2

3

COPY

IPLON

C126

IPL SW SSS312

0.1uF

+24V

VCC VLED

R123

R122

3.9K

9.1KF

R127

2.7K

R126

56K

R124

+

C118

/POFF

1

84

-

+

3

2

7

8

-

+

6

5

10KF

(1uF/50V)

C119

1000pF

BA10393F

IC32A

4

IC32B

BA10393F

R125

6.2KF

P-OFF

ZD1

UDZ5.1B

65

7

8

FLASH ROM 3/7

D

C

B

A

XE-A403 CIRCUIT DIAGRAM AND PWB LAYOUT

– 16 –

Page 19

PC-UM10M

D

21

IC23

3

VLED

DB[0..7]

4

DB7

DB6

DB5

4

5

BA00ASFP

2

1

P95

R100

P95

5.6K

R145

C

22uF/10V,OS

C87

+

3

10K

DB1D3DB2

DB0

DB3

R102

B

A

1

2.4KF

VCC

C89

22uF/16V

+

CN1

2

34567

8910111213141516

1

K

GND

VCCV0RS

R/WEDB0

E

RS

R/W

DB2

DB1

DB3

DB4

DB5

LCD CN(16Pin)B16B-XF-A-E

DB7

DB6

D6

/S6

R105

/S6

22K

Q11

KRC111S

1SS355

2

R103

12K

P96

P96

R106

(4.7K)

P91

P91

3

4

KR7

KR1

KR2

KR3

KR4

KR6

KR0

E

R/W

RS

DB5

DB7

DB4

KR5

KR1

KR4D6KR5D7KR6

KR7

KR0

KR2

KR3

D5

D6

VCC

C83

10uF/50V

+

D[0..7]

C88

0.1uF

D[0..7]

VCC

C86

+

765

/LE0W

20

IC25

123

10uF/50V

C93

0.1uF

D4

17

15

16

18

141312

11

19

D6

D4

D5

D7

Q5

Q7

Q6

Q4

VCC

Q1

Q2

D1

QE

Q0

Q3

D3

D0

D2

4

5

9108

7

6

D2

D3

D0D7D1

P94

DB3 DB4

DB0

DB1

DB2

VCC

10K

R101

/LE0W

/LE1W

16

15

14

13

Y0

VCC

A

G2A

B

C

IC24

3

2

4

1

A1

A0

A0

A1

/WR

VCC

LE

GND

/LE3W

5

74HC374

C90

VCC

101112

Y4

Y3Y2Y1

G1

G2B

6

7

100pF

9

Y5

Y7

8

Y6

GND

R99

10K

74HC138

/CS3

/LE1

/LE2

VCC

11

191817

151614

13

20

12

B1B2B4B3B5B6B7

B8

1G

VCC

C82

10uF/50V

+

IC26

DIRA1A2

234

1

C85

0.1uF

D0 /LE2W

D1

C91

100pF

74HC245

A4

A7

A5

A3

A6A8GND

5

679108

D2

D4

D5

D6

D7 DB6

VCC

10uF/50V

C81

+

C84

0.1uF

R/WD2D5

D4

D6

E

RS

18

19

VCC

QEQ0D0

11

1516141312

17

LE

D7

D6

D5

D4

Q5

Q6

Q7

Q4

74HC374

D1

Q1

Q2

D2

GND

Q3

D3

9

4

5

8

7

6

10

D3

D0 D7

D1

20

IC27

123

VCC

VCC

10K

R98

C92

100pF

/LE3R

13

18

171516

14

11

19

12

20

B1

B2

B7

B8

B4B3B5

B6

1G

VCC

IC28

A1A2A3A4A5A6A8

DIR

2

3

4

1

C94

D0

D1

D2

0.1uF

567

D3

74HC245

A7

GND

9

8

10

D4

D5

R104

10K

VCC

C95

100pF

765

KS0

KS2

KS1

KS3

KS0

KS1

KS2

KS3

/CS3

8

8

LCD I/F 4/7

D

C

B

A

XE-A403 CIRCUIT DIAGRAM AND PWB LAYOUT

– 17 –

Page 20

PC-UM10M

5/7

D

+24V

VH +24V

R132

22KF

L2

180uH

with FUSE

R118

10(FUSER)

Q16

KTD998

Q16:HEAT SINK

TP1

VO

1

1

IC30

D20

1SR159-200

C122

D15

+

+

7

5

C111

C

2200uF/50V

R133

1.2KF

RB160L-60

R128

6,8pin:N.C

LM2574NADJ

3

2

4

C129

+

4700uF/50V

(5.6K)

L:ON

0.1uF

R129

H:OFF

18K

VOUT=1.23X(1+R2/R1)

NOT INSTALL

R131

18K

C128

100uF/50V

/VON

R130

ZD3

UDZ5.1B

33

+

C112

220uF/50V

B

VDD

VCC

TP2

VBAT

R120

180

1

VCC +5VVCC +5V

VLEDVLED

VLED +5.8V

D12

L1

180uH

IPEAK>2.2A

1SR159-200

D13

C115

1SR159-200

R134

ZD2

C113

1000uF

+

D11

+

+

3KF

C114

/16V

R119

150

/16V

47uF

/16V

330uF

1KF

R135

PTZ6.2A

RB060L40

A

1

2

CN9

BT CN(2Pin)B2B-XH-A-E(BLUE)

C116

0.1uF

F6

T2.0A/250V

+

BD1

CP301

-

C117

MYLOR

F4

UL,CSA T3.15AL/125V

POWER TRANS

120V

0.033uF

WITH HOLDER

1

2

CN8

PS CN(2Pin)B2P-VH

87654321

USA

+20% INPUT & NO LOAD: VOUT<=40V

POWER SUPPLY

for EUROPE

D

C

XE-A403 CIRCUIT DIAGRAM AND PWB LAYOUT

– 18 –

IC31:HEAT

SINK

B

PQ1CG2032FZ

142

IC31

)

F5

+24V

T1.0A/250V(LT-5

53

C120

0.01uF

+

C121

220uF/50V

7654321

8

A

Page 21

PC-UM10M

6/7

100ohm*5

C110

VCC

B

/CI

5V

SHORT PIN

SP1

F3

T500mA/250V

D

C

123456789

CN7

RS232C CN(D-SUB 9Pin)

/CD

/SD

/RS

/RS

/ER

/SD

RD RD

/CD /ER

/DR /CS

/CS

/CI /DR

FB11

FB9

R114

FB10

R115

R116

FB12

R117

FB8

FB6

FB7

FB5

EFCB322513TS X 8

R113

A

C104

10uF/50V

+

VCC

C103

0.1uF

C105

0.1uF

C1-C2+

0.1uF

R148

R147

R146

17

V

16

C102

C

231289

T1OUT

T2OUT

T3OUT

-

C2

T1IN

T2IN

T3IN

7

6

20

21

0.1uF

10K

10K

10K

P64

P74

P67

P74

P67

P64

T4OUT

T4IN

8

P66

R1IN

R1OUT

P66

13

V+

VCC

VCC

1110

0.1uF

C1+

121415

C101

VCC

C100

87654321

RS232C DRIVER

D

4

R2IN

R2OUT

5

P75

P75

272318

R3IN

R4IN

R3OUT

R4OUT

262219

P77

P77

R5IN

R5OUT

P76

P76

D9

25

24

/SHDN

10

/EN

/S9

/S9

C109

C107

C106 C108

IC29

HIN211

1SS355

B

1000pF*5

Q15

KRC111S

P91

P91

7654321

8

A

XE-A403 CIRCUIT DIAGRAM AND PWB LAYOUT

– 19 –

Page 22

PC-UM10M

D

C

B

VH

S

T

A

7/ 7

VCC

R92

1K

R91

Q6

FB25

1K

KRC111S

P91

PHUPS

C79

D5

FB26

EFCB322513

R77

20K

C69

10uF/50V

EFCB322513TS

F1

1000pF

55

1SS3

/S3

C73

2200uF/35V

T1.6A/250V

Q7

R82

NTD2955

10K

31

5.6K

Q2

2SK27

R83

+24V

VJCOM

FB27

EFCB322513TS

24V

+

VRCOM

FB28

EFCB322513TS

[0 SHORT]

JP1

/RPFA

/RPFB

/RPFC

IC18

0.1uF

100pF

357

246

RAS

RBS

RCS

9

8

/RPFD

RDS

FB18

ST A 471A

FB19

1

10

FB20

FB21

EFCB322513TS(FB14-FB21)

-

8

+2 4V

R79

4.7K

VCC

Q3

/JPFA

/JPFB

/JPFC

/JPFD

FB15

FB16

FB17

FB14

357

9

10

JCS

8

VCC

JDS

R75

ST A 471A

18KF

1

TM

C68

R76

4.7K

C67

FB13

TS

IC17

246

JAS

JBS

87654321

PRINTER DRIVER

EFCB322513

TM1

D

C

P91

VREF

2

1

KRC111S

FB22

3

+

/JPES

C77

D2

S

T

3

EFCB32251

C75

R88

4

IC16A

330pF

/S4

0.1uF

100 K

BA10393F

1SS355

VCC

(47K)

/RES

VCC

FB23

6

-

8

+2 4V

7

R78

4.7K

Q4

KRC111S

5

+

/RPES

R89

C71

R154

S

T

EFCB322513

C76

IC16B

330pF

D24

1K

D23

M

VHCO

0.1uF

100 K

4

BA10393F

1SS35 5

1SS355

D25

STRB1STR B 3

IC15

R80

VCC

+

D26

1SS355

1SS355

2

KIA431F

1

3

C70

1000pF

240

7654321

C131

22uF/16V

15K

R93

R136

8

D3

1SS355

P91

/S2

B

A

XE-A403 CIRCUIT DIAGRAM AND PWB LAYOUT

– 20 –

Page 23

PC-UM10M

D

C

B

A

1/1

12345678

21

/VON

69 70 71 72 73 74 75 76 77 78 79 80

KEYBOARD&MODE SW

123456789101112

J

R

14 15 16 17 18 19 20 21 22 23 24 25 26

28 29 30 31 32 33 34 35 36 37 38 39 40

42 43 44 45 46 47 48 49 50 51 5352 54

56 57 58 59 60 61 62 63 64 65 66 67 68

13

27

41

55

56

55

425150 64

30

14 41

27634

70

69 1

XE-A401 KEYBOARD

R

12

CN3

D1

/S0

162120 74

29

13 15

272837

J

9

10

11

1SS133D21SS133D31SS133D41SS133D51SS133D61SS133D71SS133

/S1

/S2

/S3

65

35

75

36

49 48

7

8

/S4

/S5

MODE SW

57

58

63

5943525354 68

31

32

33 62

4

3

71

72

73 5

18178911 79

45

46

47 19

6160443839

4

5

6

1SS133D91SS133

D8

D10

/S7

/S8

/S6

67

66

24

22

771080 12

78

76

25

23

2

3

1SS133

D11

/S1

/S9

40 26

1

1SS133

D12

/S0

KEY_CN12 52045-1245

1SS133

2

2

2

1

2

0

1

9

1

8

1

7

1

6

1

5

1

4

1

3

1

2

1

1

1

0

123456789

CN4

KEY_CN22 52044-2245

/S0

/S1

/S2

MDR

/S3

/S4

/S5

/S6

/S7

KR7

KR6

KR5

KR4

KR3

KR2

KR1

KR0

P91

VCC

/VON

VCC

47K*9(R16-R24)

/RESET

/RESET

VLED

P90

P90

47K

R15

R24

R23

R21

R20 R22

R19

R18

R17

R16

VLED

C6

100pF

R7

12K

R6

12K

R5

12K

R4

12K

Q3 Q4 Q5 Q6 Q7

R3

12K

Q2

R2

12K

Q1

KR[0..7]

P91

KR[0..7]

R1

12K

R14

R13

R12

R11

R10

R9

R8

KTA1271*7(Q1-Q7)

Q8Q9Q10Q11Q12

120

120

120

120

120

Q13

120

Q14KRA101M*7(Q8-Q14)

120

/S[0..6]

/S[0..6]

G1'

G2'

G3'

G4'

G5'

G6'

G7'

IC3H

1

1

A

'

8

IC3G

1

2

B

'

7

IC3F

1

3

C

'

6

IC3E

1

4

D

'

5

IC3D

1

5

E

'

4

IC3C

1

6

F

'

3

IC3B

1

7

G

'

2

IC3A

1

8

DP'

1

3

bcda

efg

d

p

C2

10uF/16V

VCC

VCC

C1

0.1uF

/S0

/S1

/S2

/S3

/S4

/S6

16

15

VCC

A

G2A

G2B

IC1

1B 2C 3

4

5G1 6Y7 7

VCC

8

/S7 /S5

KS0

KS1

KS2

KS3

D

C3

0.1uF

/S8

/S9

16

15

Y6 9Y510Y411Y312Y213Y114Y0

GND

74HC138

Y6 9Y510Y411Y312Y213Y114Y0

VCC

A

G2A

G2B

GND

IC2

1B 2C 3

74HC138

4

5G1 6Y7 7

8

C

FROM MAIN

VLED

VLED

C5

C4

PLACE NEAR CONNECTER

VCC

CN1

0.1uF

100uF/16V

a

a

b

b

cdefg

cdefg

POP UP

KR4

KR5

KR6

KR7

/S2

/S7

/RESET

P90

P91

KR0

KR1

KR2

KS3

KS2

dp

dp

KR3

KS1

KS0

KR4

KR5

P90

P91

KR0

KR1

KR2

KR3

KR6

/RESET

P97

B

/S6

/S9

/VON

/S3

/S4

/S5

/S2

/S7

/VON

/S3

/S4

/S5

/S6

/S9

91010111112121313141415151616171718181919202021212222232324242525262627272828292930303131323233333434353536363737383839394040

11223344556677889

CN2

KEY I/F CN(40Pin)

40FE-BT-VK-N

15

G1'

G2'

G1'

G3'

G4'

G2'

G3'

G5'

G6'

G7'A'B'C'D'E'F'G'DP'

G4'

G5'

G6'

G7'A'B'C'D'E'F'G'DP' 1

A

234567891011121314

9 PIN :GND

10PIN : NC

IC3

POP UP CN(15Pin)

15FMN-BTK-A

KID65083AP

87654

XE-A403 CIRCUIT DIAGRAM AND PWB LAYOUT

– 21 –

Page 24

PWB LAYOUT

Q A SIDE

PC-UM10M

Q B SIDE