Page 1

FO-5800U/C

SERVICE MANUAL

No. 00ZFO5800USME

FACSIMILE

MODEL FO-5800

Illustration: FO-5800

In this Service Manual for FO-5800U/C which is provided with 3rd. cassette and memory PWB (FO-1MK), only the

information which differs from that for FO-5700U/C already issed is contained. For the information not contained, refer

to the Service Manual for FO-5700U (00ZFO5700USME) or FO-5700C (00ZFO5700CSME), FO-4700U/FO-47UC

(00ZFO4700USME) or FO-4700C/FO-47UC (00ZFO4700CSME) and FO-1MK (00ZFO1MKCUSME).

Difference between FO-5700U/C and FO-5800U/C

FO-5700U/C FO-5800U/C

3rd. cassette

Control PWB unit

Printer PWB unit DCEKC470BXH01 DCEKC470BXH02

CAUTION

This laser facsimile is a class 1 laser product that complies with 21CFR 1040.10 and 1040.11 of the CDRH or IEC60825-1 standard.

This means that this machine does not produce a hazardous laser radiation. The use of controls, adjustments or performance of

procedures other than those specified herein may result in hazardous radiation exposure.

This laser radiation is not a danger to the skin, but when an exact focusing of the laser beam is achieved on the eyes retina, there is

danger of spot damage to the retina.

The following cautions must be observed to avoid exposure of the laser beam to your eyes at the time of servicing.

1) When a problem in the laser optical unit has occurred, the whole optical unit must be exchanged as a unit, not an individual part.

2) Do not look into the machine with the main switch turned on after removing the toner/developer unit and drum cartridge.

3) Do not look into the laser beam exposure slit of the laser optical unit with the connector connected when removing and installing

the optical system.

4) The cover of Laser Printer Unit contains the safety interlock switch.

Do not defeat the safety interlock by inserting wedges or other items into the switch slot.

Laser Wave Length : 770-810 mm

Laser Pulse Times

Laser Output Power : 0.37 mW

: 49.2 µs

–––––––––––

U: DCEKC489MXHZZ U: DCEKC282NXHZZ

C: DCEKC283NXHZZ C: DCEKC688NXHZZ

STANDARD EQUIPMENT

Parts marked with " " is important for maintaining the safety of the set. Be sure to replace these parts with specified ones for maintaining the safety and performance of the set.

This document has been published to be used

SHARP CORPORATION

for after sales service only.

The contents are subject to change without notice.

Page 2

FO-5800U/C

CAUTION FOR BATTERY REPLACEMENT

(Danish) ADVARSEL !

Lithiumbatteri-Eksplosionsfare ved fejlagtig håndtering.

Udskiftning må kun ske med batteri

af samme fabrikat og type.

Levér det brugte batteri tilbage til leverandoren.

(English) Caution !

Danger of explosion if battery is incorrectly replaced.

Replace only with the same or equivalent type

recommended by the equipment manufacturer.

Discard used batteries according to manufacturer’s instructions.

(Finnish) VAROITUS

Paristo voi räjähtää, jos se on virheellisesti asennettu.

Vaihda paristo ainoastaan laitevalmistajan suosittelemaan

tyyppiin. Hävitä käytetty paristo valmistajan ohjeiden

mukaisesti.

(French) ATTENTION

Il y a danger d’explosion s’ il y a remplacement incorrect

de la batterie. Remplacer uniquement avec une batterie du

même type ou d’un type recommandé par le constructeur.

Mettre au rébut les batteries usagées conformément aux

instructions du fabricant.

(Swedish) VARNING

Explosionsfare vid felaktigt batteribyte.

Använd samma batterityp eller en ekvivalent

typ som rekommenderas av apparattillverkaren.

Kassera använt batteri enligt fabrikantens

instruktion.

(German) Achtung

Explosionsgefahr bei Verwendung inkorrekter Batterien.

Als Ersatzbatterien dürfen nur Batterien vom gleichen Typ oder

vom Hersteller empfohlene Batterien verwendet werden.

Entsorgung der gebrauchten Batterien nur nach den vom

Hersteller angegebenen Anweisungen.

Page 3

FO-5800U/C

CONTENTS

CHAPTER 1. GENERAL DESCRIPTION

[1] Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

[2] Refer to the service manual of FO-4700U/FO-47UC or FO-4700C/FO-47UC

[3] Refer to the service manual of FO-4700U/FO-47UC or FO-4700C/FO-47UC

[4] Refer to the service manual of FO-4700U/FO-47UC or FO-4700C/FO-47UC

[5] Refer to the service manual of FO-4700U/FO-47UC or FO-4700C/FO-47UC

CHAPTER 2. ADJUSTMENTS

[1] Adjustments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

[2] Diagnostics and service soft switches . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-2

[3] Troubleshooting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-35

[4] Error code table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-36

CHAPTER 3. MECHANICAL DESCRIPTION

[1] Refer to the service manual of FO-4700U/FO-47UC or FO-4700C/FO-47UC

[2] Refer to the service manual of FO-4700U/FO-47UC or FO-4700C/FO-47UC

[3] Refer to the service manual of FO-4700U/FO-47UC or FO-4700C/FO-47UC

[4] How to install the verification stamp (FO-45VS) refer to the service manual supplement of

FO-4700U/FO-47UC or the service manual of FO-4700C/FO47UC

CHAPTER 4. DIAGRAMS

[1] Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

[2] Wiring diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

[3] Point-to-point diagram and connector signal name . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

CHAPTER 5. CIRCUIT DESCRIPTION

[1] Circuit description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

[2] Circuit description of control PWB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

[2-1] Circuit description of memory PWB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-19

[2-2] Circuit description of 3rd. cassette PWB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-20

[3] Refer to the service manual of FO-4700U/FO-47UC or FO-4700C/FO-47UC

[4] Refer to the service manual of FO-4700U/FO-47UC or FO-4700C/FO-47UC

[5] Refer to the service manual of FO-4700U/FO-47UC or FO-4700C/FO-47UC

[6] Refer to the service manual of FO-4700U/FO-47UC or FO-4700C/FO-47UC

CHAPTER 6. CIRCUIT SCHEMATICS AND PARTS LAYOUT

[1] Control PWB circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

[2] LIU PWB circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-19

[3] Printer PWB circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-21

[4] Power supply PWB circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-25

[5] Operation panel PWB circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-27

[6] High voltage PWB circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-29

[7] Toner empty PWB circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-31

[8] 2nd. cassette PWB circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-32

[9] 3rd. cassette PWB circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-34

[10] Memory PWB circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-36

CHAPTER 7. OPERATION FLOWCHART

[1] Refer to the service manual of FO-4700U/FO-47UC or FO-4700C/FO-47UC

[2] Refer to the service manual of FO-4700U/FO-47UC or FO-4700C/FO-47UC

CHAPTER 8. OTHERS

[1] Refer to the service manual of FO-4700U/FO-47UC or FO-4700C/FO-47UC

[2] Refer to the service manual of FO-4700U/FO-47UC or FO-4700C/FO-47UC

P ARTS GUIDE

Page 4

FO-5800U/C

CHAPTER 1. GENERAL DESCRIPTION

[1] Specifications

• GENERAL

Automat ic dialing Rapid Key Dialing: 48 numbers

Speed Dialing: 100 numbers

Memo ry siz e* 2 MB (approx. 116 pages)

Mode m speed 33,600 bps (max.)

Automatic fallback to lower speeds.

Transmission time* Approx. 2 seconds

Toner ca rtridge yield Initial starter cartridge (included with

(4% page coverage,letter fax machine): Approx. 3000 pages

paper) Replacement cartridge (FO-47ND):

Approx. 6000 pages

Drum car tridge yield Initial starter cartridge (included with

fax machine): 20,000 pages (avg.)

Replacement cartridge (FO-47DR):

20,000 pages (avg.)

Resolution Horizontal: 203 pels/inch (8 pels/mm)

Vertical:

Standard: 98 lines/inch (3.85 lines/mm)

Fine /Halftone:

196 lines/inch (7.7 lines/mm)

Super fine:

391 lines/inch (15.4 lines mm)

Automatic do cument 50 pages max. (20 lb letter paper)

feeder

Effective Scanning width 10.1" (256 mm) max.

Effectiv e Printing width 8.0" (203 mm) max.

Recepti on mo de s Auto/Manual

Instascan speed 30 ppm (letter paper)

Full Dual Access Yes

Copy function Single/Multi/Sort (99 copies/page)

Power requirements 120 V AC, 60 Hz

Operating temperature 50 - 86°F (10 - 30°C)

Humidity 20 to 85% RH

Power consumption Standby: 13.5 W

Maximum: 580 W

Dimensions Width: 18.1" (460 mm)

Depth: 15.2" (385 mm)

Height: 20.1" (510 mm)

Weight Approx. 54.2 Ibs.(24.6kg)

* Based on ITU-T (CCITT) T est Chart #1 at standard resolution in Sharp

special mode, excluding time for protocol signals (i.e., ITU-T phase C

time only).

Paper capacity 1250 sheets (one 250 sheet tray and

two 500 sheet cassettes)

Compression scheme MMR, MR, MH, Sharp (H2)

Halftone (grayscale) 64 levels

Applicable telephone line Public switched telephone network

Compatibility ITU-T (CCITT) G3 mode

Printing resolution Horizontal: 406 lines/inch

(16 lines/mm)

Vertical: 391 lines/inch

(15.4 lines/mm)

PC Printing: 600 dpi

Input document size Automatic feeding:

Width: 5.8 to 10.1" (148 to 256 mm)

Length: 5.0 to 14.3" (128 to 364 mm)

Manual feeding:

Width: 5.8 to 11.0" (148 to 279 mm)

Length: 5.0 to 17.0" (128 to 432 mm)

Note: This facsimile machine is Year 2000 compliant.

Option

Toner cartridge

Drum cartridge

PC interface

Option memory

Verification stamp

: FO-47ND

: FO-47DR

: FO-47IF

: FO-3MK

: FO-45VS

<IMPORTANT PLEASE READ FIRST>

To avoid problems with supplies, please don’t use supplies from other units. Please use new supplies, when supply changes are required.

1 – 1

Page 5

FO-5800U/C

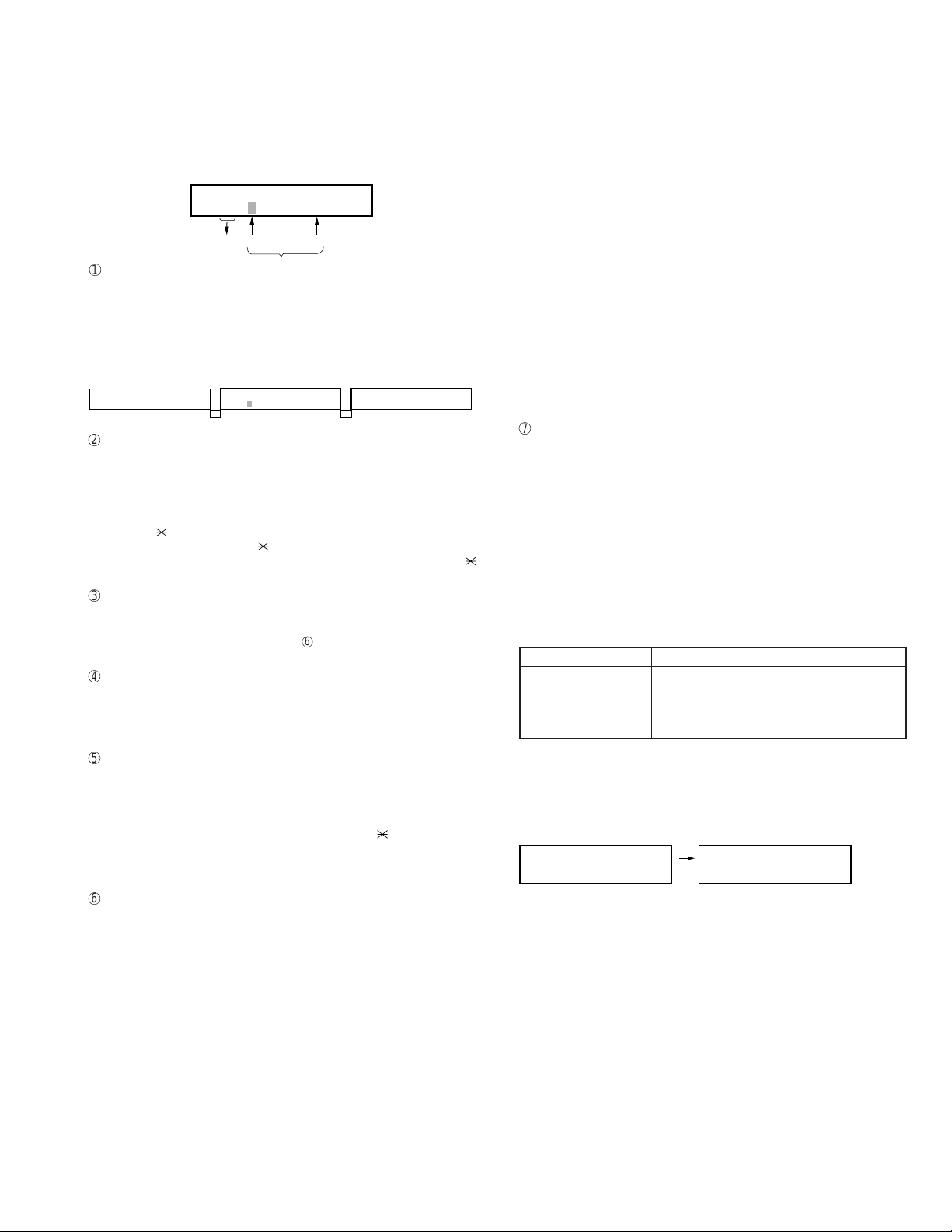

TOP VOID LABEL

CHAPTER 2. ADJUSTMENTS

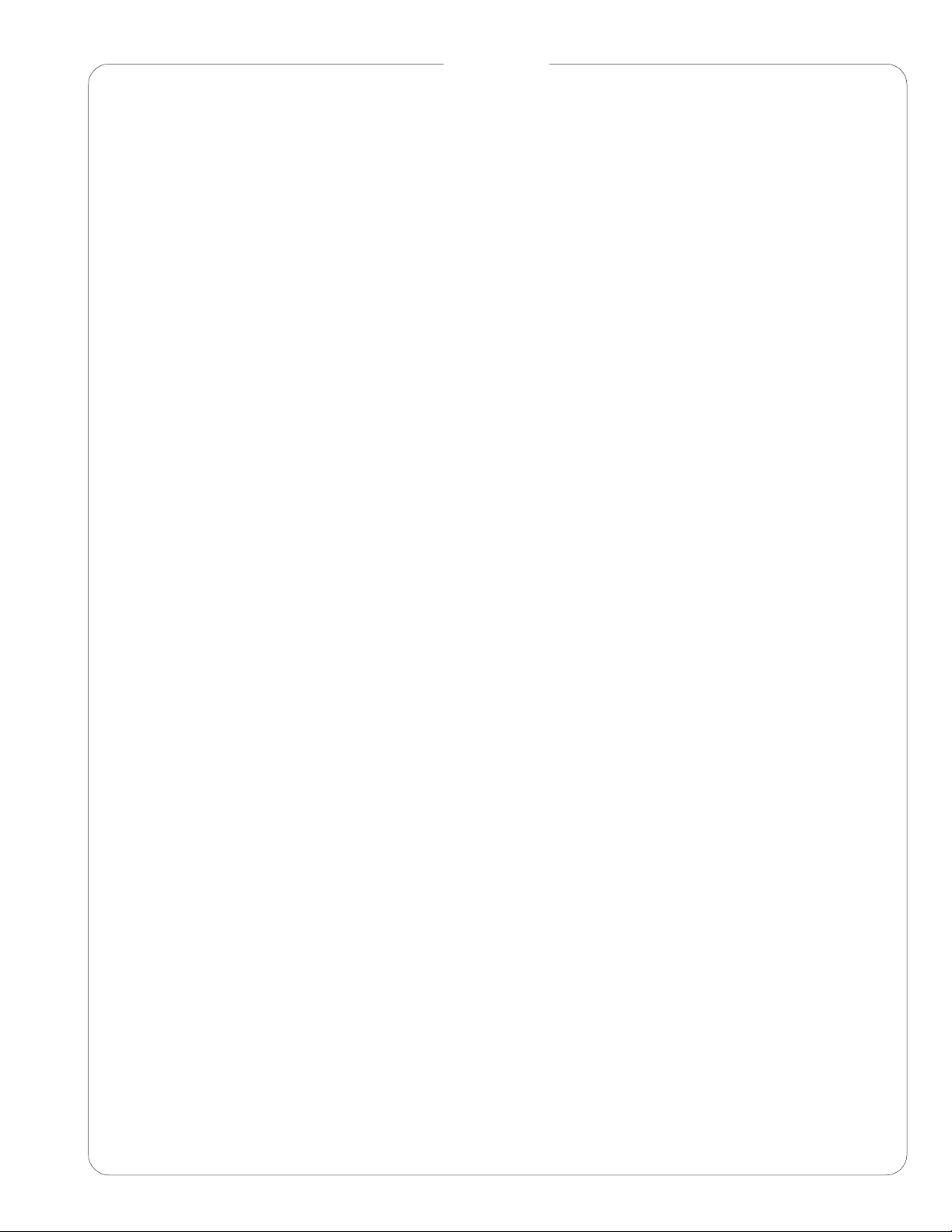

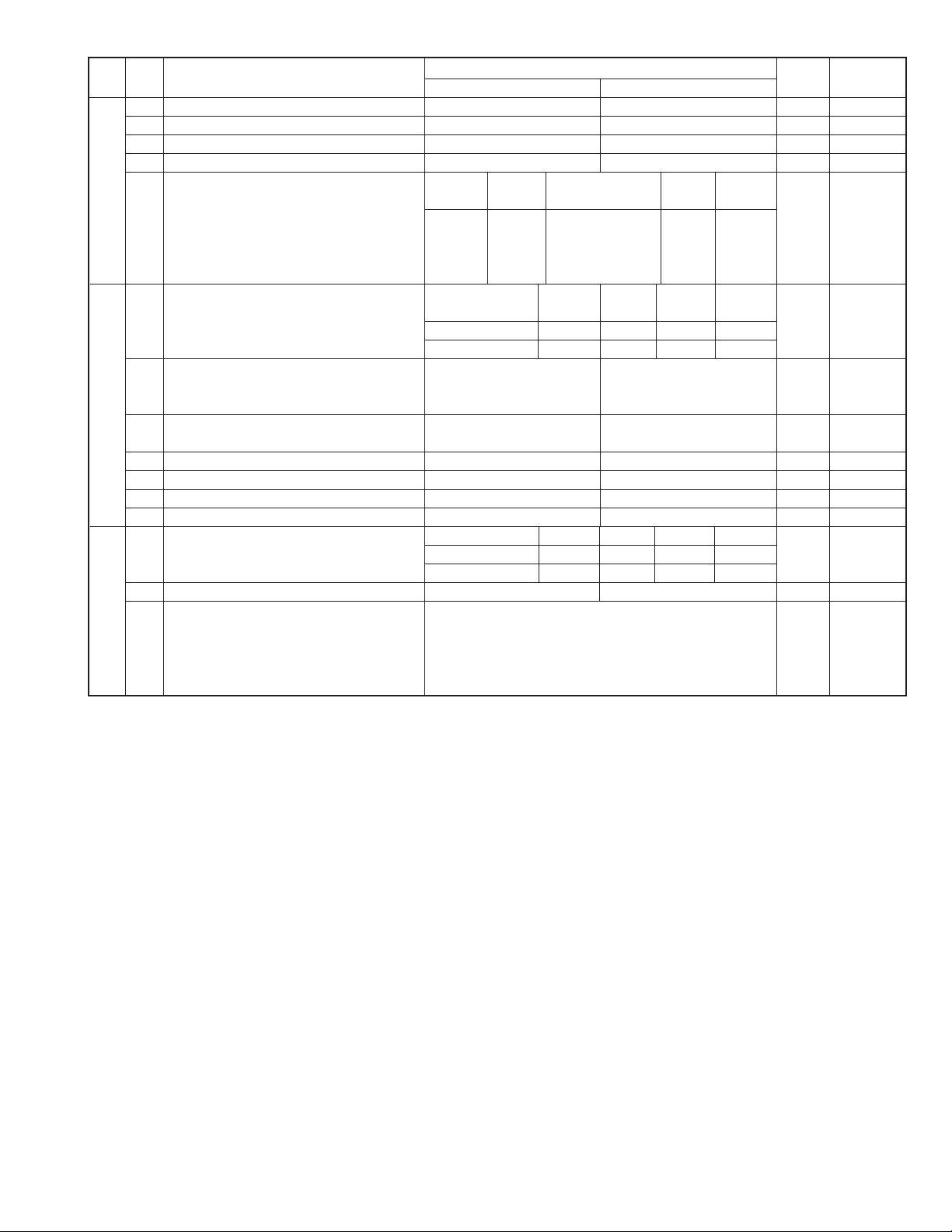

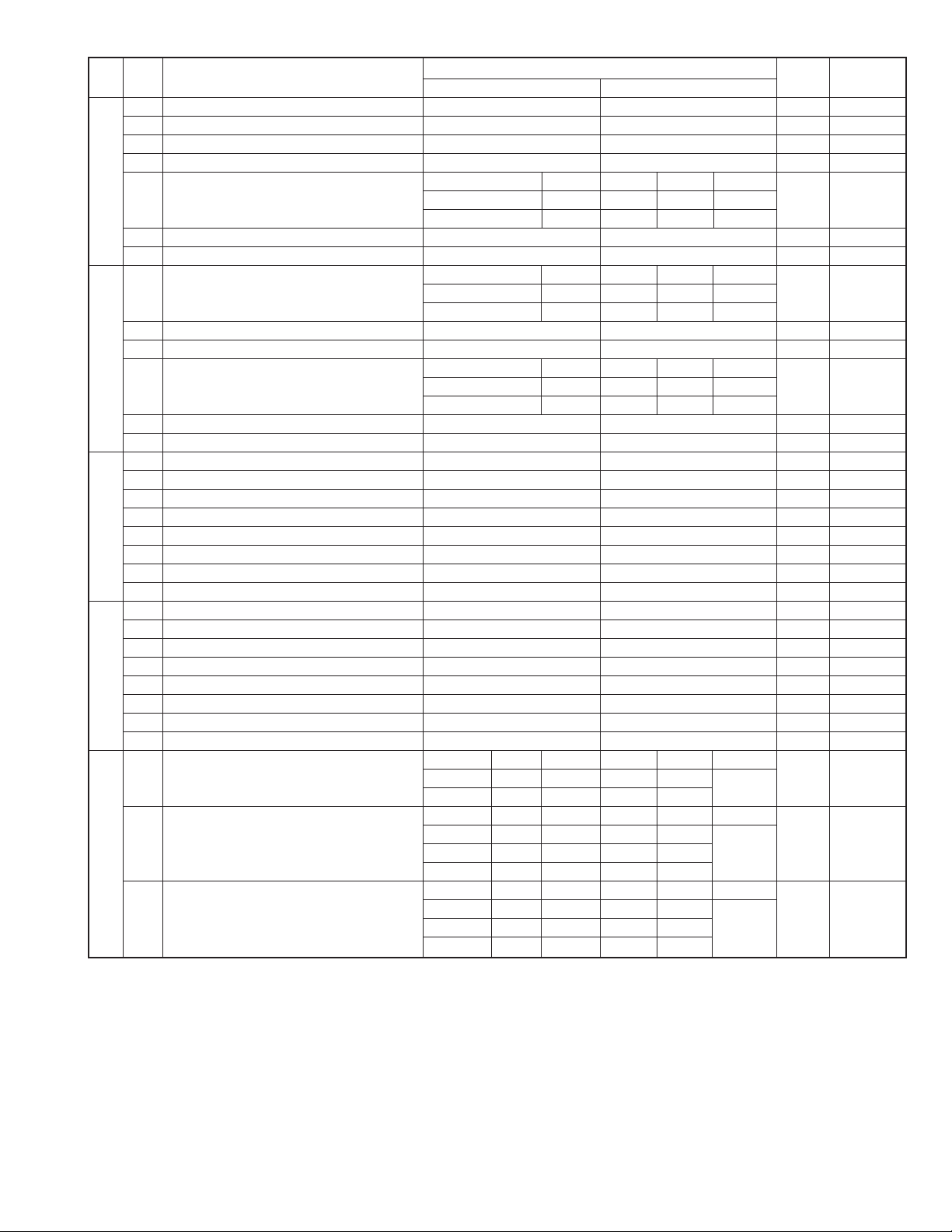

[1] Adjustments

General

Since the following adjustments and settings are provided for this model,

make adjustments and/or setup as necessary.

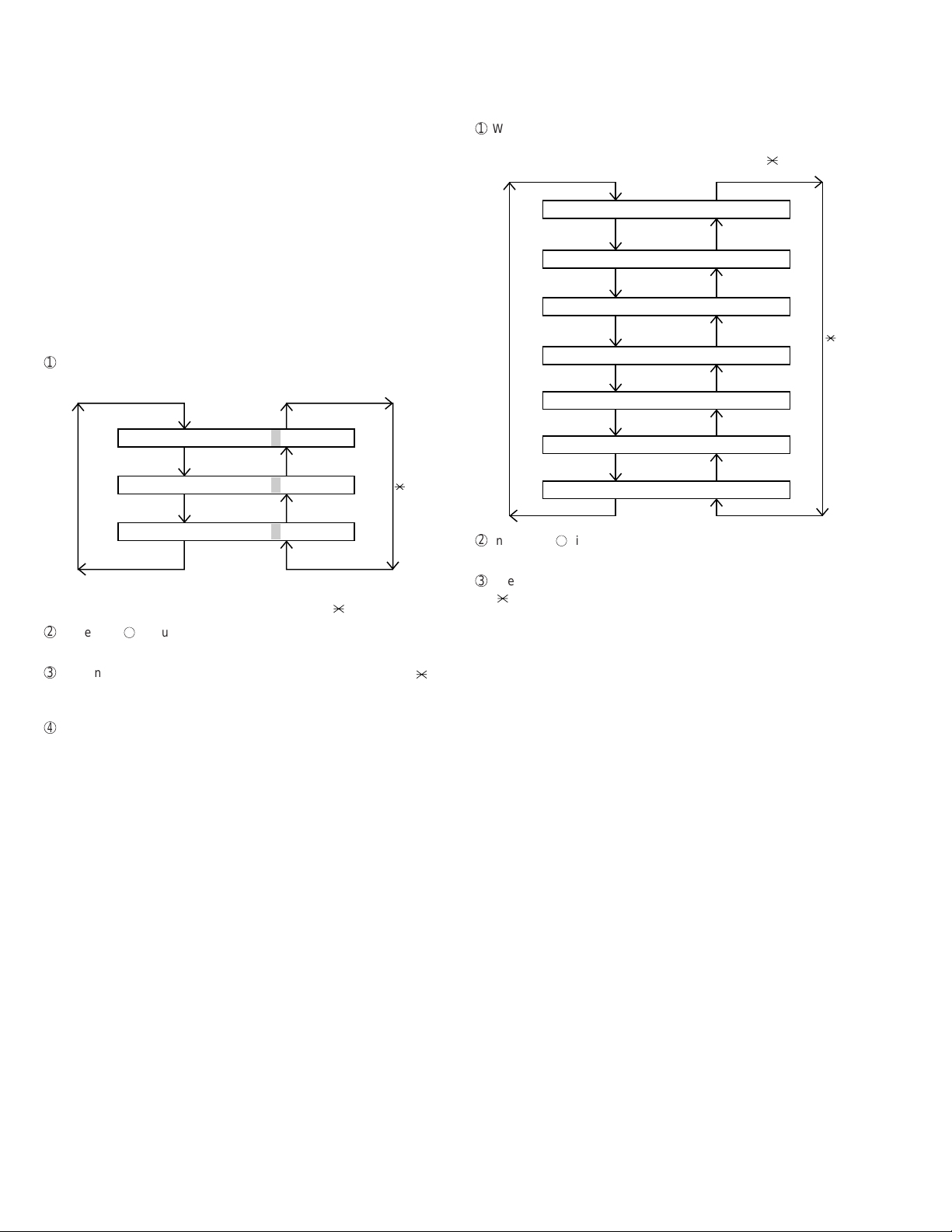

1. Adjustments

Adjustments of output voltage (FACTORY ONLY)

1. Install the power supply unit in the machine.

2. Set the recording paper and document.

3. When the document is loaded, power is supplied to the output lines.

Confirm that outputs are within the limits below.

Output voltage settings

CONTROL

PWB

CN5

12

POWER SUPPLY

PWB

Output Voltage limits

+5V MAIN 4.845V~5.355V

+5V SUB 4.845V~5.355V

+24V MAIN 23.04V~24.96V

+24V SUB 23.04V~24.96V

Connector CN4

No.

Pin No. CN1

1 11 +5V

2 10 HV C HL

39T VR

4 8 T REM

5 7 T MON

6 6 B MON

7 5 B VR

8 4 C REM

9 3 C MON

10 2 MG

11 1 +24

1

8

1

CN1

12

1

CNPW

1

CNPRT

30

1

11

1

30

CN1

1

CN4

PRINTER

PWB

–

1

8

CN7

11

CN1

HI VOLTAGE

PWB

IC2

Voltage for adjust

IC2

VR1

VD

+ Check point for voltage

+–

Digital multi meter

Fig. 1

Connector CN5

No.

Pin No. CNPW

1 +24V SUB

2MG

3MG

4MG

5 +24V MAIN

6 +24V MAIN

7 +5V SUB

8DG

9DG

10 DG

11 +5V MAIN

12 +5V MAIN

Connector CN1

No.

Pin No. CN7

1 24 MAIN

2MG

3DG

4 5V MAIN

5 HEATER ON

6FAN

7 FAN LOCK

8 H RELAY OFF

ADJUST VOLT AGE LIST

Top Void Printer Adjust V oltage

Label (mm.) Fig. 2 VR1 Fig. 1

5.5~6.9 4.42V

7.0~8.9 3.87V

9.0~10.9 3.14V

11.0~12.9 2.50V

Fig. 2

13.0~14.9 1.86V

15.0~17.0 1.22V

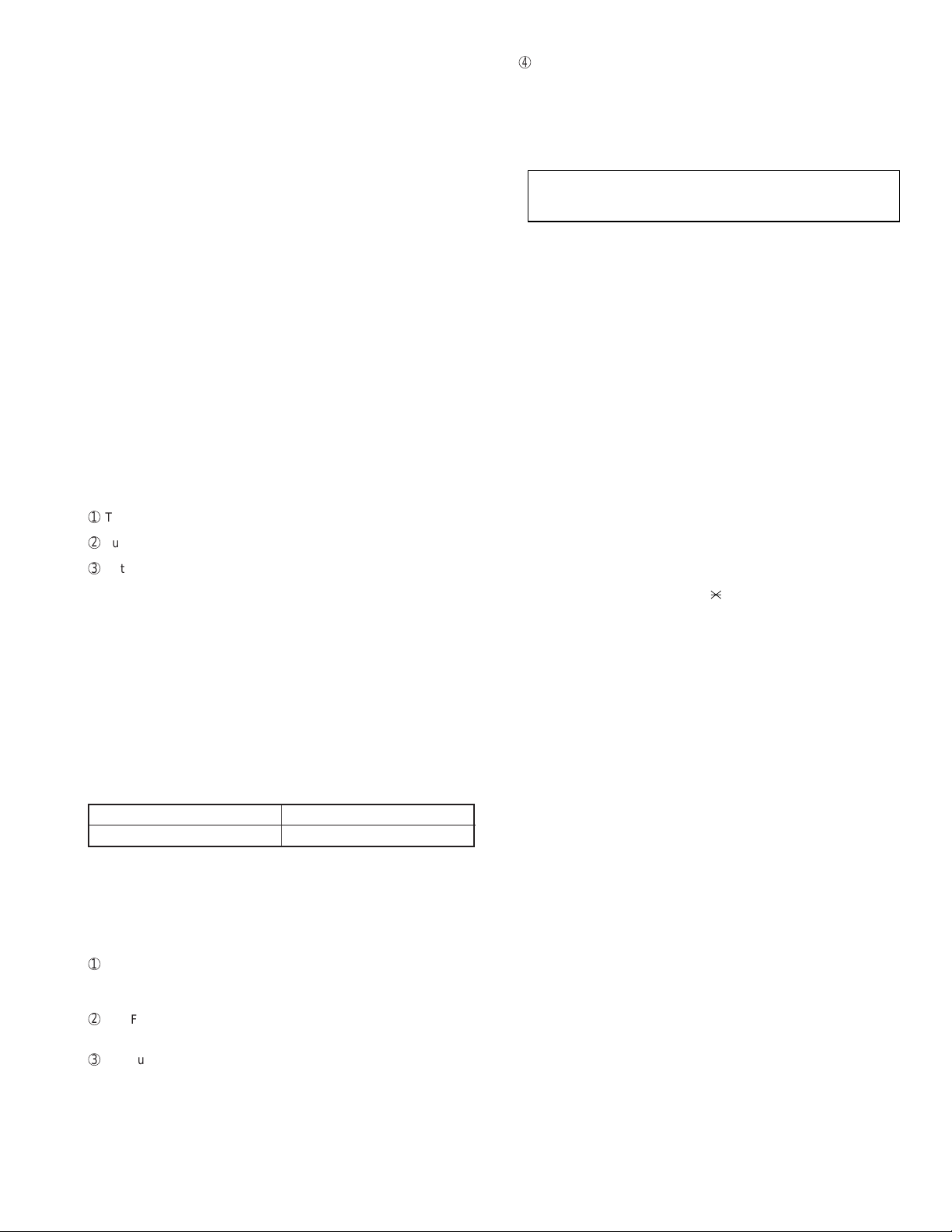

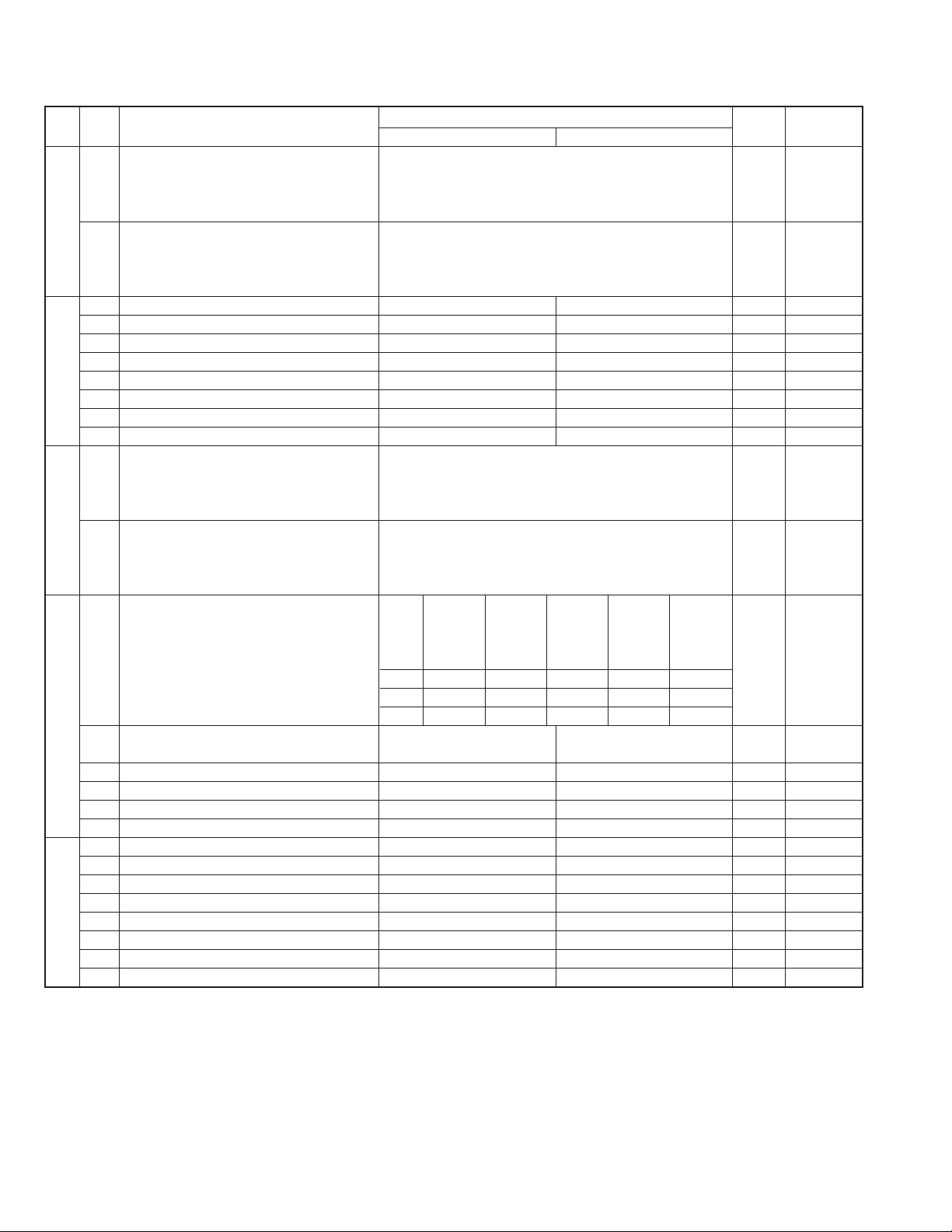

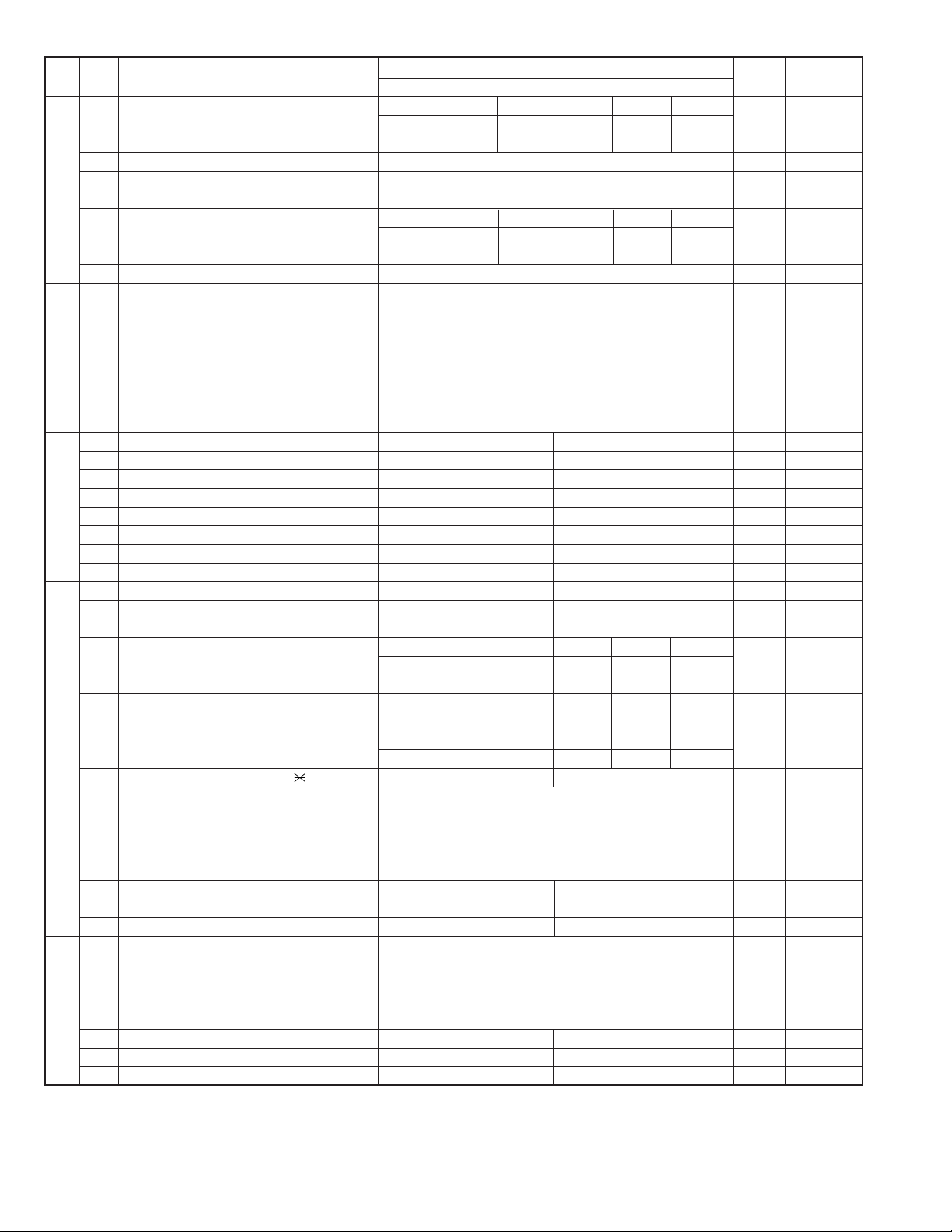

2. IC protectors replacement

ICPs (IC Protectors) are installed to protect the TX motor drive circuit

and verification stamp drive circuit. ICPs protect various ICs and electronic circuits from an overcurrent condition.

The location of ICPs are shown below:

12

1

27 25

CNPW

CNOP

150

130

CNPRT

IC7

F101

CNTXM

CNSTP

11

42

F100

1

1

CNLIU

CONTROL PWB

(BOTTOM SIDE)

CNPN

24

CNCIS

9

CNSP

CNSEN

101

1

2

1

8

Fig. 3

(1) F100 (ICPS10) is installed in order to protect IC’s from and

overcurrent generated in the verification stamp drive circuit. If F100

is open, replace it with a new one.

(2) F101 (ICPS18) is installed in order to protect IC’s from an overcurrent

generated in the TX motor drive circuit. If F101 is open, replace it

with a new one.

In addition to the replacement of F101 and F100, the factor causing

F101 and F100 to open must also be repaired. If not, F101 and

F100 will open again.

Replacement parts

ICPS10 (Sharp code: VHViCPS10//-1)

ICPS18 (Sharp code: VHViCPS18//-1)

3. Settings

(1) Dial mode selector

OPTION SETTING: DIAL MODE (Soft Switch No. SW2 DATA No. 1)

Use this to set the fax machine to the type of telephone line you are on.

• The factory setting is "TONE".

(step 1) Select "OPTION SETTING".

KEY:

DISPLAY:

(step 2) Select "DIAL MODE".

KEY:

DISPLAY:

(step 3) Select, using "1" or "2".

KEY:

DISPLAY: TONE SELECTED

KEY:

DISPLAY:

(step 4) End, using the "STOP" key.

KEY:

FUNCTION 4

4:OPTIONAL SETTING

ENTER #(01-34, ,#)

2

2

DIAL MODE

1

2

PULSE SELECTED

STOP

Cursor

When initially registering,

the mode shows 1=TONE.

When registering again, the

mode which was registered

formerly is shown.

1=TONE, 2=PULSE

2 – 1

Page 6

FO-5800U/C

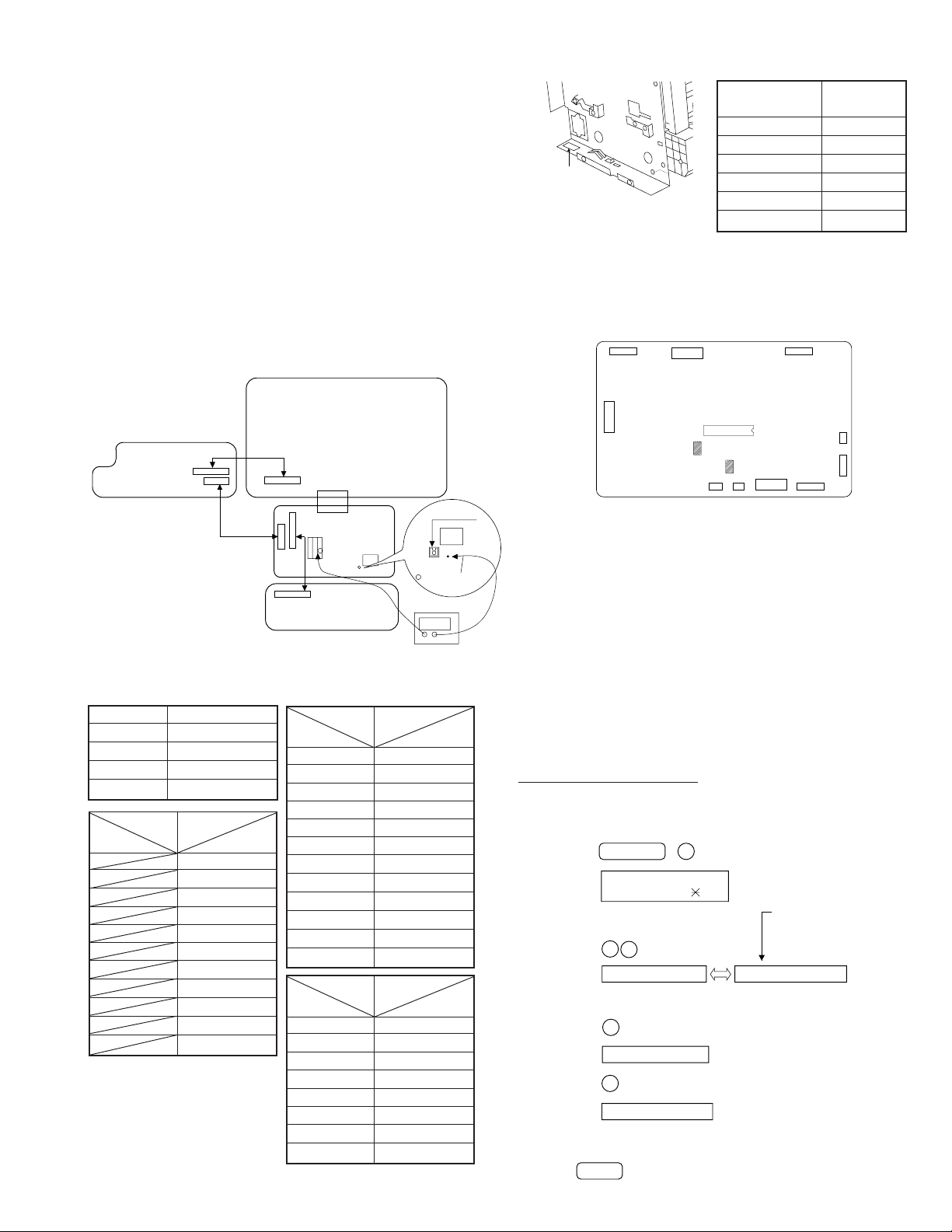

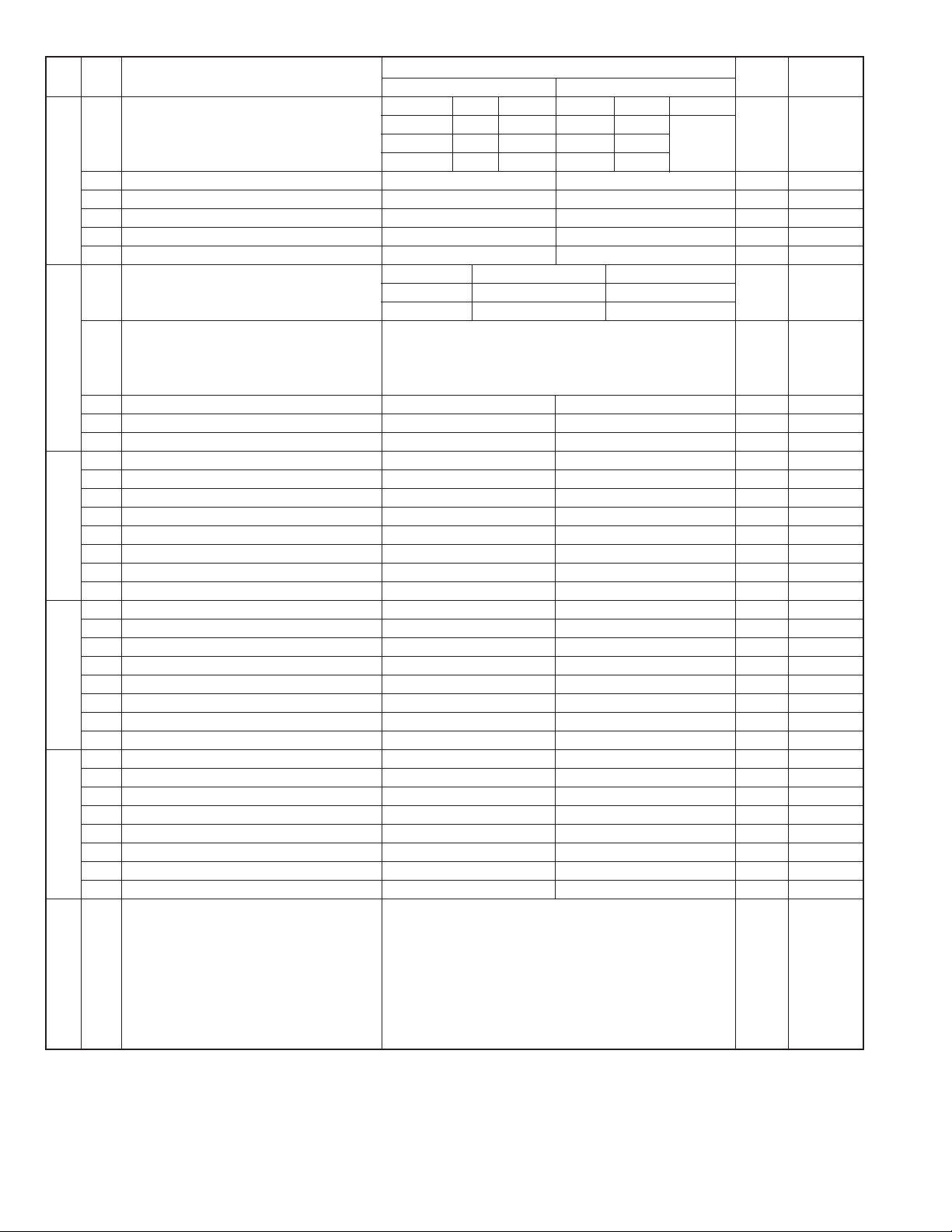

[2] Diagnostics and service soft switches

1. Operating procedure

Two kinds of diagnoses are supported.

1-1. Fax diagnosis

This diagnosis is concerned with the main body of fax which is used

for production and service support.

Entering the diagnostic mode

FUNC

Press

display will appear.

U: ROM: FBN0

C: ROM: FBP0

FBN0

FBP0

Then press the

and the key or select with the rapid key.

Enter the mode with the

(Diag

•

specifications)

FUNC

02 PRINT AREA

03 ROM & RAM CHECK

04 AUTO FEEDER MODE

05 AGING MODE

06 PANEL CHECK MODE

07 OPTICAL ADJUST MODE

08 PRODUCT CHECK

09

10

9 8

START

key. Select the desired item with the

START

key.

9 8 7

START01 SOFT SWITCH MODE

START

START

START

START

START

START

START

START

START

U: ROM:

C: ROM:

START

SIGNAL SEND MODE

COMM. CHECK MODE

FBN0

FBP0

7

, and

the

following

key

1-2. Print diagnosis

This diagnosis is concerned with the print which is used for

production and service support.

Entering the diagnostic mode

FUNC

Press

display will appear.

PCU ROM Ver.:

Then press the

key andthe key orselect withthe rapid key.

Enterthe modewith the key.

(Diag•specifications)

FUNC

01

02

03

08

09

9 8

START

9 8 6

START

START

START

START04

START05

START06

START07

START

START

START10

START11

6

, and

key. Select the desired item with the

START

PCU ROM Ver.:

START

AREA PRINT MODE

CHECK PATTERN 1

CHECK PATTERN 2

CHECK PATTERN 3

PAPER FEED AGING

BIAS ADJUST MODE

LIFE SET MODE

LIFE ALL CLEAR

LIFE ENTRY MODE

TOP ADJUST MODE

LIFE CLEAR MODE

the

following

11

12

13

14

15 CONF. PASSCODE

16

17

18

19

20

21

22

START

START

START

START

START

START

START

START

START

START

START

START

MEMORY CLEAR

FLASH MEMORY

ALL FAX/TEL. ENTRY MODE

DEPT. PASSCODE

PRINT HOLD CODE

MEMORY SET MODE

STAMP AGING

DIAL TEST MODE

COPY DIAG MODE

SIGNAL SEND MODE2

JBIG TEST MODE

Memory clear when power is turned on

Pressing the START and STOP keys, turn on the main power, and the

following message will be displayed.

MEMORY CLEAR

EXECUTE ? 1 = YES , 2 = NO

Here, when 1: YES is selected, the memory will be cleared to be ready

for operation.

If 2: NO is selected, it will continue ready for operation as it is.

2 – 2

Page 7

FO-5800U/C

2. Diagnostic items description

2-1. Fax diagnosis

1) Soft switch mode

In this mode, the soft switch are set and the soft switch list is printed.

Soft switch mode screen

S O F T S W I T C H M O D E

S W 0 1 = 0 0 0 0 0 0 0 0

8

Data

1

Switch number selection

1 2 3 4 5 6 7 :DATA No.

Switch

No.

• Press START key for setting of the next soft switch. If the soft

switch number is the final, pressing START key will exit the soft

switch mode.

• Enter two digits of a soft switch number to set the switch number.

If a switch number of unexisting soft switch is entered, key error

buzzer sounds to reject the input.

S O F T S W I T C H M O D E

S W 0 1 = 0 0 0 0 0 0 0 0

2

Data number selection

E N T E R L A S T D I G I T

S W 1

1 6

S O F T S W I T C H M O D E

S W 1 6 = 0 0 0 1 0 1 1 0

The cursor position shows the data to be set.

Pressing # key moves the cursor to the right. If, however, the cursor is

on data number 8, pressing # key shifts the cursor to data number 1

of the next switch number. If the switch number is the final, pressing

# key will exit the soft switch mode.

Pressing key moves the cursor to the left. If, however, the cursor is

on data number 1, pressing key shifts the cursor to data number 1

of the former switch number. If the switch number is 1, pressing

key will not move the cursor and the error buzzer will sound.

3

Data setting method

Press the FUNCTION key, and the data at the position of the cursor

will be reversed to 0 when it is 1, or to 1 when it is 0. (If the soft switch

can be changed at the bit (Refer to 6.), the error buzzer will sound

with the process not received.)

4

Outputting method of soft switch list

In the soft switch mode, press the REPORT key, and the soft switch

list will be output.

If the recording paper runs out or is clogged, the key error buzzer will

sound with the process not received.

5

Storage of data

In the following case, the data of the soft switches set will be stored.

• It is shifted to set the next soft switch by pressing the START

switch.

• It is shifted to set the next soft switch with the [#] key.

• It is shifted to set the last soft switch with the [ ] key.

• It is shifted to set another soft switch by inputting two digits as the

switch number. (When 2 digits are completely input.)

• Output of the soft switch list is started.

6

Inhibition of data change

(This is also applicable for the optional setting.)

In the following case, it is inhibited to change the data with the key

error buzzer.

• Switching ON/OFF of ECM during the use of image memory.

• Switching OFF to ON of the print hold function when the print

hold pass code has not yet been registered.

• Clearing the print hold pass code when print hold function is ON.

• Switching ON/OFF of the print hold function during the use of

memory such as in the case of substitute receiving.

• OFF to ON of telephone billing function which is using the image

memory is used (Note: In the existing set, the telephone billing

code function is specified from OFF to ON when the timer system

communication (including the batch communication) is set.)

Here, the memory is usable when the telephone billing code function is on. It can be set from ON to OFF while the memory is

used. However, if setting is practically changed even once, it can

not be returned from OFF to ON.

• Switching ON/OFF of PC interface function during the use of im-

age memory.

• OFF to ON of department control function during use of image

memory.

(Note: In the existing set, the department control function is set

from OFF to ON when the timer communication (including the

batch sending) or the memory hold is set.)

• ON to OFF of continuous serial polling function when the con-

tinuous serial polling is started.

(Note: In the existing set, "ON to OFF of the continuous serial

polling function when the continuous serial polling is registered"

has been applied, but the conditions are now moderated. However, registration is impossible to the program of the new continuous serial polling when the continuous serial polling function is

OFF.)

• In addition, change of all soft switches during communication

7

Linked change of data (This is the same even in the optional setting.)

• When the department control function is off, the multi TTI func-

tion and telephone billing code function are turned off.

2) Print area

According to the size of the specified sheet, the effective printing area is

printed.

3) ROM & RAM check

The sum value of ROM, the work and the back-up RAM are checked.

The RS232C interface is also checked. If any error occurs, the buzzer

will inform it. (Refer to the following table). Finally, the result will be printed.

This diagnosis does not check the flash memory. The flash memory is

checked with the flash memory test.

Number of buzzer sounds Device checked Remarks

1 time <Short sound> ROM Main

2 times <Short sounds> Integrated ROM Main

3 times <Short sounds> SRAM Main

4 times <Short sounds> DRAM Main

For the short and long sounds, one pattern is as follows.

Main system: 0.5 seconds ON/0.5 seconds OFF

Sub system: 1.00 second ON/0.5 seconds OFF

The execution state of checking is as follows. Moreover, the list of the

check result is output after checking is ended.

Display during check

ROM CPU SRM DRM

• • • •

Display after check

ROM CPU SRM DRM

P P P E

P=PASS E=ERROR

ROM/RAM

check list

output

2 – 3

Page 8

FO-5800U/C

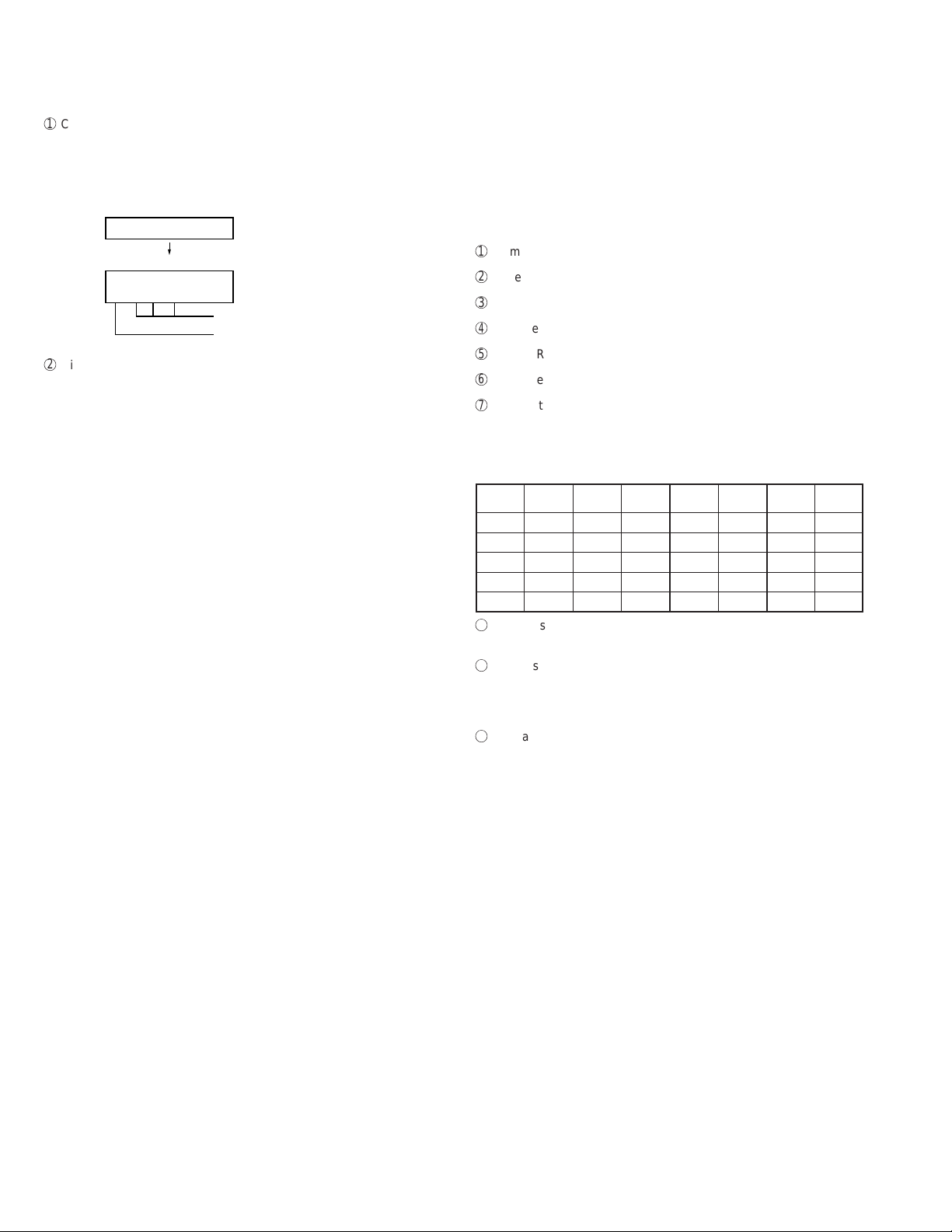

4) Auto feeder mode

The auto feed function can be checked by inserting and discharging the

document. (The distance between pages can be displayed during operation of the scanner.)

1

Check of auto feed function

After this mode is activated, set up the document, and press the

STAR T key , and it will be automatically fed. (Before the ST ART key is

pressed, the document sensor alone is activated.) Moreover, the

document size (A4/B4) and sensor information (A4/B4/ORG) are displayed when the document sensor is turned.

04 : AUTO FEEDER MODE

After setup of the document

04 : AUTO FEEDER MODE

B4 (A4 B4 ORG)

Only the sensor which is

activated (fallen down) is displayed.)

The paper sheet size (A4/B4) is

displayed.

2

Display of distance between pages during operation of the scanner

• Soon after this mode is activated, press the FUNCTION key for 5

seconds or more, and the display mode of the distance between

pages will be activated. Then, set up the sending paper and select

the image quality, and then press the START key, and operation

will be started.

Be sure to press the FUNCTION key prior to the START key. If

the FUNCTION key is not pressed but the STAR T key is pressed,

it will operate in the same matter as in the existing auto feeder

mode.

If the START key is pressed, the FUNCTION key will be invalid

hereafter. Therefore, the display mode of the distance between

pages and the existing mode can not be changed.

• While the sending paper is read, the image quality key can be

input. STD/FINE/S-FINE modes are usable. However, the same

operation of FINE will be selected if the intermediate tone is set.

• The image quality, the length of the sending page read, the page

distance to the next sending paper and the total of the sending

papers read are shown on the display.

• When the stop key is pressed or 100 sending papers are read,

the content shown on the display will be totally output as the list

after the remaining sending papers are discharged.

5) Aging mode

If any document is set up in the first state (when started), copying will be

executed. If it is not set up, "check pattern 1" of the print diagnosis is

output at the intervals of 1 time/60 minutes. (A total of 10 sheets are

output.)

7) Optical adjust mode

Set documents and press the START key for ordinary copying.

According to key operation, copying can be temporarily stopped.

STOP key: To temporarily stop reading documents.

START key: To start reading documents again.

When any document is not set, print area printing is performed.

8) Product check

The diagnosis is used in the production process.

After shift to the mode, the following operations are sequentially executed. At this time, the sensor of read-error can be checked by feeding

the B4 document. Set up one short document of B4 size.

1

Memory clear (Same as Diagnosis 11)

2

Panel test (Same as Diagnosis 06)

3

Dial test (Same as Diagnosis 24)

4

Document auto feed

5

ROM & RAM test check (Same as the Diagnosis 03)

6

Flash memory test mode (Same as Diagnosis 12)

7

Registration of fixed data

Registration of rapid key No. and other data necessary for produc-

tion.

The registered data are shown in the following table. The chain dial

is not set for any destination.

Rapid FAX Rapid FAX Rapid FAX Rapid FAX

No. No. No. No. No. No. No. No.

01 20 06 25 11 1 21 01

02 21 07 26 12 2 22 02

03 22 08 27 13 3 23 03

04 23 09 28 14 4 24 04

05 24 10 29 15 5 25 05

8

Transmission check (Same as Diagnosis 10)

The soft switches necessary for production are set.

9

Test result print (one sheet)

Memory clear printing

Panel test result printing

ROM & RAM test result printing

F

Print area printing (one sheet)

6) Panel check mode

This is used to check whether each key is normally operated or not.

According to the key input, LCD is displayed. Moreover, during execution,

the document reading lamp is turned on.

T est results are printed. (The maximum 100 input keys can be printed .)

LED repeats lighting at regular intervals in sequence. (Lighting speed

is specified separately.)

In case of inputting all keys, key input OK is displayed when finishing

the STOP key.

When pressing the NUMERIC key during panel check, output of DTMF

corresponding with the key is started.

When pressing other keys, output is stopped.

2 – 4

Page 9

9) Signal send mode

Rapid key RXX XX : Rapid number

SPEED key SXXX XXX

: Speed key number

After shift to the mode, press the START key, and the signals will be

transmitted in the following sequence.

It can be used to check the modem and so on.

[ 1] No signals

[ 2] 4800BPS (V27ter)

[ 3] 14400BPS (V . 33)

[ 4] 12000BPS (V . 33)

[ 5] 14400BPS (V . 17)

[ 6] 12000BPS (V . 17)

[ 7] 9600BPS (V. 17)

[ 8] 7200BPS (V. 17)

[ 9] 9600BPS (V. 29)

[10] 7200BPS (V . 29)

[11] 4800BPS (V27ter)

[12] 2400BPS (V27ter)

[13] 300BPS (FLAG)

[14] 2100Hz (CED)

[15] 1100Hz (CNG)

10) Comm. check mode

Turn on the line monitor .

1

2

Turn off the COVER SHEET FUNCTION.

3

Set line equivalence at 0 km.

After the check, it is necessary to be sure to return the aforementioned

soft switches into the initial state.

(Clear the memory with the diagnosis.)

11) Memory clear

Clear the back-up memory to initialize the soft switches.

The flash memory will be initialized. Then, the initialized list be output.

12) Flash memory

The flash memory is checked.

The ordinary memories (ROM, SRAM, DRAM) are checked in the ROM

& RAM check process. The write/read test is taken every block to print

the result.

When an error occurs, the following error buzzer will sound.

Number of buzzer sounds Check device

9 times <Short sounds> Flash memory (Option)

During operation of this diagnosis, dual operation is not possible at all.

If this is excessively repeated, it will shorten the life of the flash memory.

13) All FAX/TEL. entry mode

The function is used to simplify the registration of FAX/TEL No. during

aging.

1

The diagnosis mode is activated. If anything is not registered in the

Rapid number 01 or any program or group is not registered, it will

pass the diagnosis without doing anything.

2

The FAX/TEL number (including the substitutive destination) of the

Rapid number 01 is copied to the Rapid numbers 02 thru 48.

3

FAX number of the Rapid number 01 is copied to SPEED key numbers

001 thru 200.

FO-5800U/C

4

If any chain dial is not in the Rapid number, the Rapid numbers 02

thru 48 and SPEED key numbers 001 thru 200 are registered in the

group number 01.

If any chain dial is set, the group will be not produced but the chain

dial setting alone of the Rapid number 01 will be reset.

(In all others except the Rapid number 01, the chain dials will be

continuously set as they are.)

(16th and subsequential letters of the destination name registered in the

Rapid number 01 will be discarded.)

14) Dept. passcode

The department passcode list is printed.

15) Conf. passcode

The confidential passcode list is printed.

Differing from printing of one box alone soon after registration, the confidential passcodes of all boxes are printed.

16) Print hold code

The print lockout passcode No. is printed.

17) Memory set mode

The set and dump list of the memory content is output.

• The address (8 digits (P) generally including the bank information is

input, and the data of 2 digits is continuously input.

Inputting is done in the hexadecimal mode. The ten-key is used for 0

thru 9, and the alphabetic keys A (RAPID 01 thru 06) are used for A

thru F.

• During data inputting, the address can be moved forward and back-

ward one byte by one byte with " " and "#". (The address prior to the

address 0 is looped as the maximum address.)

• The V alidity of the address is not checked. Accordingly, writing/ read-

ing operations are possible in the address of the memory not as-

signed, the address of ROM and so on.

(However, as practical, writing is not done, and the data content runs

short each reading.)

Though writing is possible in the flash memory, a little time is re-

quired.

It is also necessary to take care that the life of the flash memory is

excessively shortened if much data is written in the flash memory.

Since it may run away depending the written content, take minute

care for the writing address.

• When the REPORT key is input, the memory dump list is produced

from the displayed address (here, it is limited at the 16-byte bound-

ary address (address with end 0) which does not exceed the speci-

fied address and is just in front.). The dump list is output to a maxi-

mum of 99 pages. If any data of one page can be repeatedly devel-

oped and printed, the list is sufficient. But it is not desired that the

content of plural pages are developed in the memory once and are

then printed. If the STOP key is pressed, it will pass to the diagnosis

after the page which is now being printed is completed printed.

If the address exceeds the maximum address, it will return to the

address 0 and printing will be continued.

18) Stamp aging

Diag mode is left though it doesn’t have this function.

2 – 5

Page 10

FO-5800U/C

19) Dial test mode

The mode is used to inspect whether dialing is accurate in two kinds of

dial modes . All data which can be dialed in this mode are automatically

called up in both PB mode and DP mode.

When this mode is activated, the following operations will be automatically executed . Whether the dialed content is right or not is judged with

the external instrument which is connected to the line cable.

1

After shift to the FAX diagnosis mode, press RAPID 24.

(Also switch the display with the [ ] and [#] keys.)

2

Press the START key.

3

Turn on CML, and dial the following in the PB mode.

1, 2, 3, 4, 5, 6, 7, 8, 9, , 0, #

4

Turn off CML 500 mS alone.

5

Dial the following in the DP mode.

1, 5, 9, 0

6

After dialing, turn off CML.

This mode uses the ordinary auto dial. (Accordingly, the signal sending

time and minimum pause are all the same as ordinary.

The measurement result in this mode is completely all the same as in

the ordinary dial mode.

Moreover, the same process as above is also done in the dial test mode

which is executed in the product check mode.

20) Copy diag mode

In order to shorten the process time during production, this mode is

used to automatically switch the copy mode. Three menus are provided.

1. 1Set up two documents. (In case of two documents or more,

there is no problem.

2

Press the STAR T key.

3

Copy 1st document in the fine mode/density AUTO. (One sheet

is printed in the ordinary copy mode.)

4

Copy 2nd (subsequential) document in the intermediate tone

mode/density DARK. (In the ordinary copying mode, one sheet

is printed when the RESOLUTION key is pressed three times.)

When copy test is tried during production or is checked in two modes

(fine and intermediate tones), this mode is provided to reduce the troublesome work which makes the operator stand aside to change the mode.

Accordingly, the fine and intermediate tones are merely switched, and

the mode is not switched to another mode. (Input of the image quality/

density key is invalid.)

2. Try the copy in the mode fixed at COPY REDUCE 95% and fine

mode/density AUTO. At this time, don’t change the soft key of

COPY REDUCE. (Input of the image quality/density key is invalid.)

3. Continuously try the above items 1 and 2.

21) Signal Send Mode2

The signals concerned with V.34 & V.8 are checked.

After this mode is activated, press the START key, and the signals will

be sent in the following sequence.

It can be used to check the modem.

[ 1] No signal

[ 2] 33600BPS

[ 3] 31200BPS

[ 4] 28800BPS

[ 5] 26400BPS

[ 6] 24000BPS

[ 7] 21600BPS

[ 8] 19200BPS

[ 9] 16800BPS

[10] 14400BPS

[11] 12000BPS

[12] 9600BPS

[13] 7200BPS

[14] 4800BPS

[15] 2400BPS

22) JBIG Test Mode

Enter the diagnostic mode.

1

2

Press the RAPID22 button. ("22: JBIG TEST MODE" appears.)

3

Press the START key to begin the JBIG test operation.

When both tests are completed normally, the buzzer sounds and "JBIG

TEST NORMAL END" appears at the same time.

If the decoding test terminates abnormally, the buzzer sounds and

"ERROR: JBIG DECODE" appears at the same time.

If the encoding test terminates abnormally, the buzzer sounds and

"ERROR: JBIG ENCODE" appears at the same time.

2 – 6

Page 11

FO-5800U/C

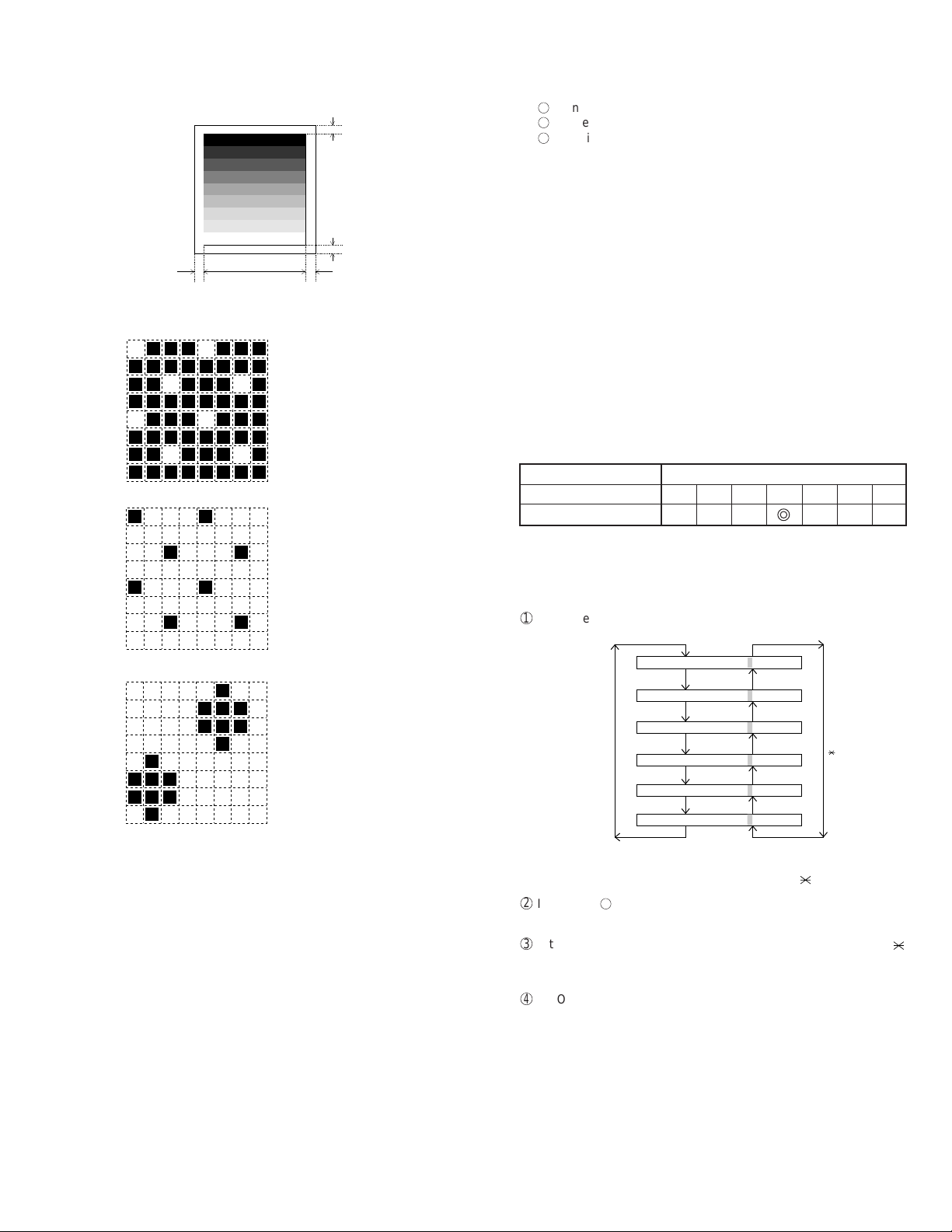

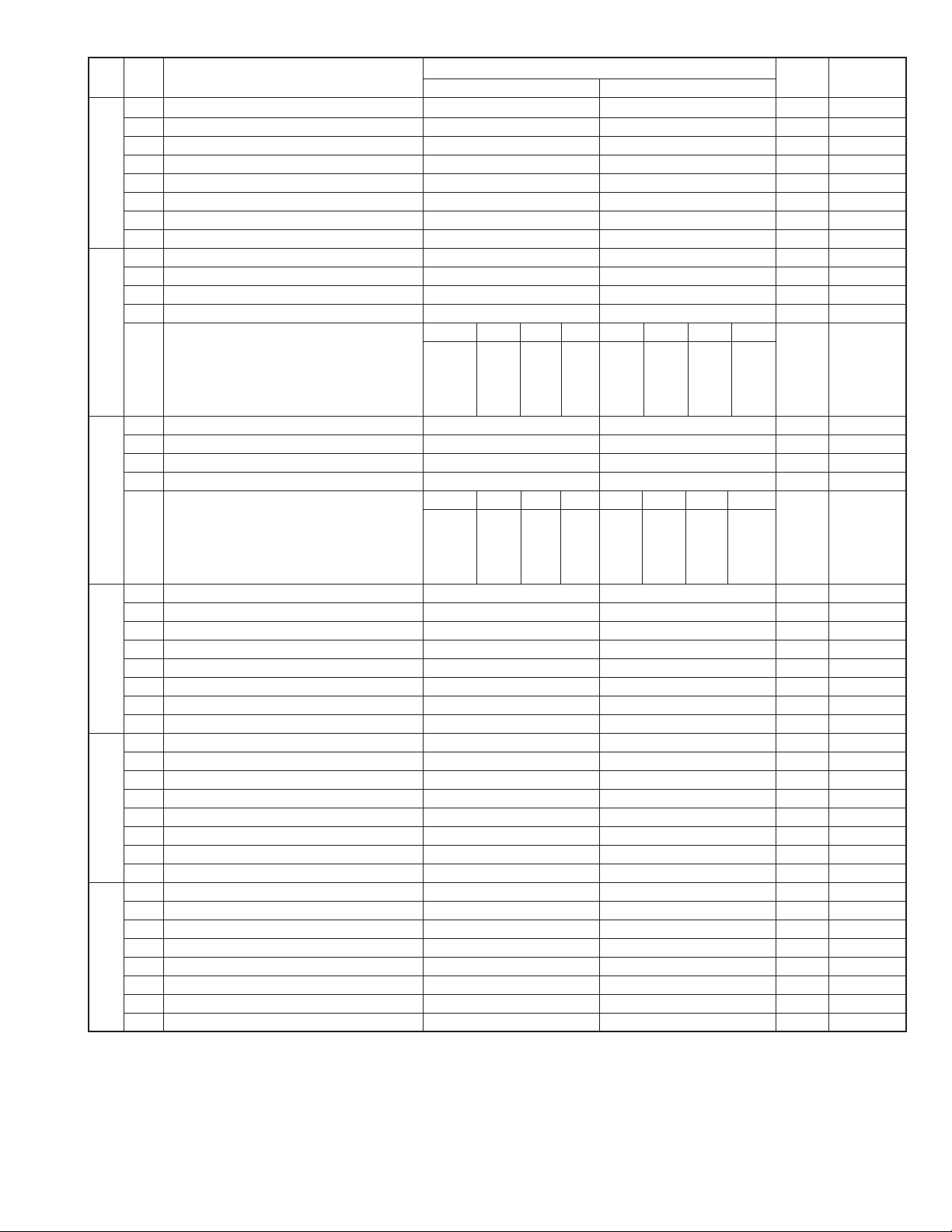

2-2. Print diagnosis

Rapid key 01: Area print mode

The effective printing area frame is printed in the specified sheet size.

1

2

3

4

5

6

7

8

9

4mm ± 2

208mm

1. [Full black pattern]

2. [Intermediate tone 2 pattern]

3. [Intermediate tone 1 pattern]

4mm ± 2.5

4mm

4mm

The left pattern is repeated.

The left pattern is repeated.

Rapid key 05: Paper feed aging

The mode is used for aging related to the printing. In this mode, the

following modes are provided.

1

Blank paper aging mode (ALL WHITE AGING)

2

Whole black print aging mode (ALL BLACK AGING)

3

4% printing aging mode (4% AGING)

After selecting the paper-pass aging mode in the print diagnosis mode,

input the number of each mode above with the ten-key, and the mode

will be executed. The detailed specifications of each mode are described

as follows. Here, the operation in each mode is stopped only when the

STOP key is pressed by the operator or a printing-impossible error occurs.

• Blank paper aging mode

In the mode, printing is continued in the whole white (white paper)

printing pattern until the STOP key is pressed by the operator . (In the

printing area)

• Whole black printing aging mode

In the mode, printing is continued in the whole black (whole black)

printing pattern until the STOP key is pressed by the operator . (In the

printing area)

Rapid key 06: Bias adjust mode

The mode is used to adjust the printing density of the printed image. The

image printing density is adjustable in seven steps of 1 to 7.

For details, refer to the following table. (For selection, use the keys 1

thru 7.)

Image printing density Thin ←→Thick

1234567

Default value

4. [Mesh point pattern]

The left pattern is repeated.

5. [Longitudinal strip 2 pattern]

Black 2 dot and white 2 dot are repeated in line.

6. [Lateral strip 2 pattern]

Black 2 line and white 2 line are repeated.

7. [Longitudinal strip 1 pattern]

Black 1 dot and white 1 dot are repeated in line.

8. [Lateral strip 1 pattern]

Black 1 line and white 1 line are repeated.

9. [Full White pattern]

Rapid key 02: Check pattern 1

The lateral stripe 2 pattern is printed on one sheet.

(Black 2 line and white 2 line are repeated.)

Rapid key 03: Check pattern 2

The lateral stripe 2 pattern is printed on multiple pages.

Press the STOP key to end the printing.

Rapid key 04: Check pattern 3

The intermediate tone 1 is printed on one sheet.

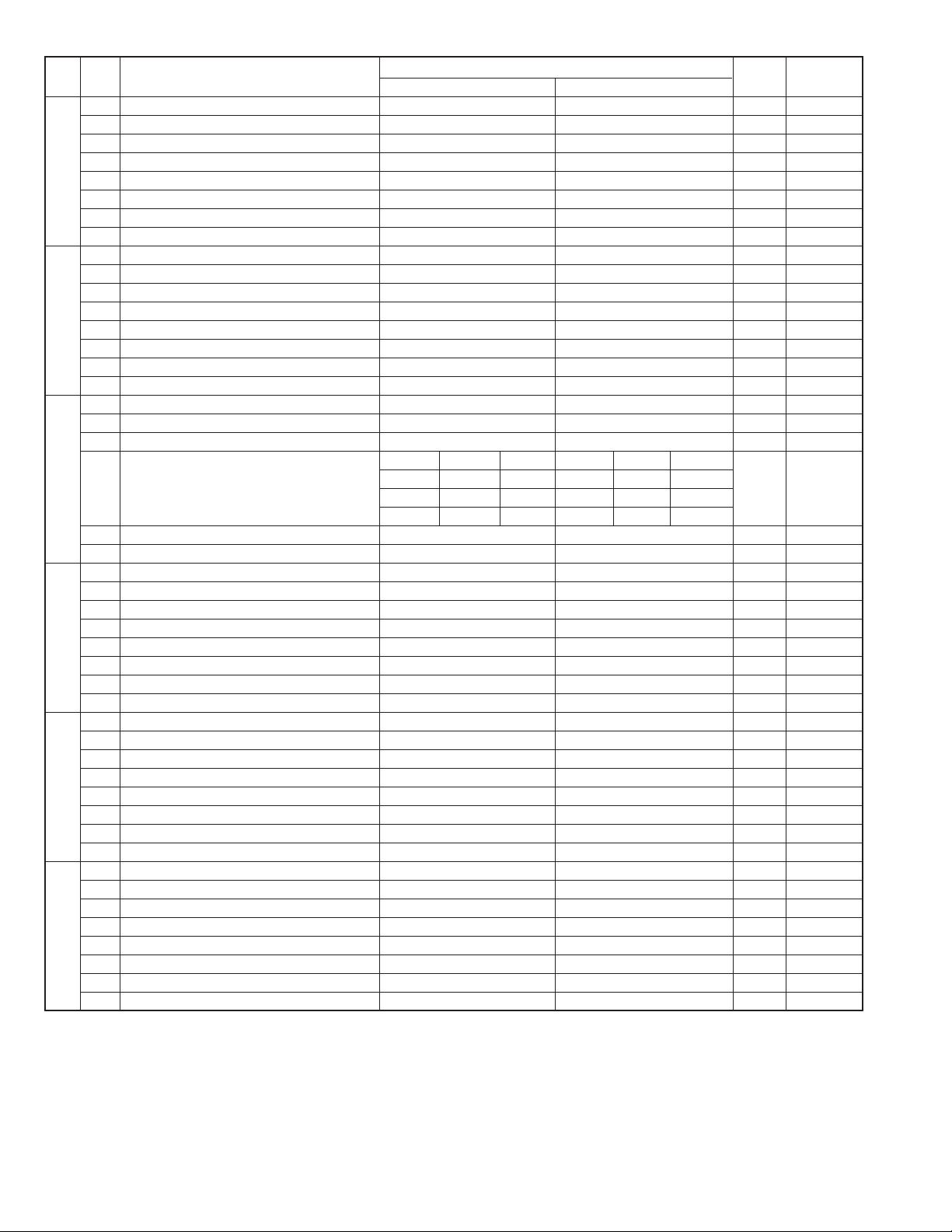

Rapid key 07: Life set mode

The mode is used to set the life counter of the printer and the counter of

the auto feeder at desired values. For setting, proceed with the following

procedure.

1

When the life counter setting mode is selected, the following will be is

displayed.

= 00123

DRUM

LIFE

LIFE

IFE1

L

LIFE2

LIFE3

0

= 00123

0

= 00123

0

= 00123

0

= 00123

0

0

key

MACHINE

# key

FEEDER LI FE = 00123

The cursor blinks at the top data.

Five counters can be selected with the "#" and " " keys.

2

In the state 1, input a desired setting number of 6 digits with the tenkey.

3

After input of 6 digits, shift to another counter with the "#" and " "

keys as necessary. When all necessary counters are completely input, press the START key.

4

"STORED" will be displayed with the set values stored into the memory.

For checking, retry this mode.

Note:

This counter indicates the printer use conditions such as numbers of

printed pages from the beginning of use. In the normal memory clear

condition, the counter will not be reset.

In conditions including damaged memory contents caused by repairing

the panel, this counter should be reset or cleared in addition to the ordinary memory clear.

2 – 7

Page 12

FO-5800U/C

Rapid key 08: Life all clear

The mode is used to clear the life counter of the printer of the counter

of the auto feeder.

Note: The counter shows the operational state of the printer (e.g. how

many sheets have been printed since start of use?). The ordinary memory does not reset the counter. Accordingly, it is necessary to reset this counter in addition to the ordinary memory

clear if the content in the memory on the control PWB is broken

because of PWB repair, etc. (In the production stage, it is necessary to execute this in the last process.)

Rapid key 09: Life entry mode

(For Serviceman temporary counter)

The mode is used to set a desired value for the judgment value (alarm

judgment counter value) of the general purpose life counters 1 thru 3 of

the printer. If the life of a consumable part (developer, imprinter, etc) is

set, the model which has the error display and RMS function will inform

RMS when the counter reaches the set value. For setting, proceed with

the following procedure.

1

When the life counter setting mode is selected, the following will be

displayed.

# key

LI FE1= 00000

LI FE2= 00000

0

0

key

Rapid key 11: Life clear mode

The mode is used to respectively clear the life counter of the printer and

the counter of the auto feeder. For setting, proceed with the following

procedure.

1

When the life counter clearing mode is selected, the following will be

is displayed.

Seven counters can be selected with the "#" and " " keys.

# key

MACHINE

DRUM

FEEDER L I FE LEAR

TONER L I FE LEAR

LIFE

LIFE

L

IFE1

LIFE2

LIFE3

LEAR

C

LEAR

C

LEAR

C

LEAR

C

LEAR

C

C

C

key

LI FE3= 00000

0

The cursor blinks at the top data.

Three counters can be selected with the "#" and " " keys.

2

In the state 1 , input a desired setting number of 6 digits with the ten-

key.

3

After input of 6 digits, shift to another counter with the "#" and " "

keys as necessary. When all necessary counters are completely input, press the START key.

4

"STORED" will be displayed with the set values stored into the

memory. For checking, retry this mode.

Note: The counter shows the operational state of the printer (how many

sheets have been printed since start of use? and others). The

ordinary memory does not reset the counter. Accordingly, it is

necessary to reset the counter or do the clear process in addition to the ordinary memory clear if the content in the memory

on the control PWB is broken because of PWB repair, etc. (In

the production stage, it is necessary to execute this in the last

process.)

Rapid key 10: Top adjust mode

As the method to adjust the top margin for printing, adjust top margin

adjusting VR on the PWB. If this mode is used at this time, adjustment is

possible without the printing test every time when VR is turned.

For the practical use, determine the adjusting value on the basis of the

old data, and adjust to the determined value in this mode. Then, check it

with the printing test.

2

In the state 1, input the CLEAR key, and the counter will be respectively cleared.

3

After one clear, move the cursor to another counter with the "#" and

" " keys as necessary, and then press the CLEAR key. When the

necessary counters are completely cleared, press the STOP key.

2 – 8

Page 13

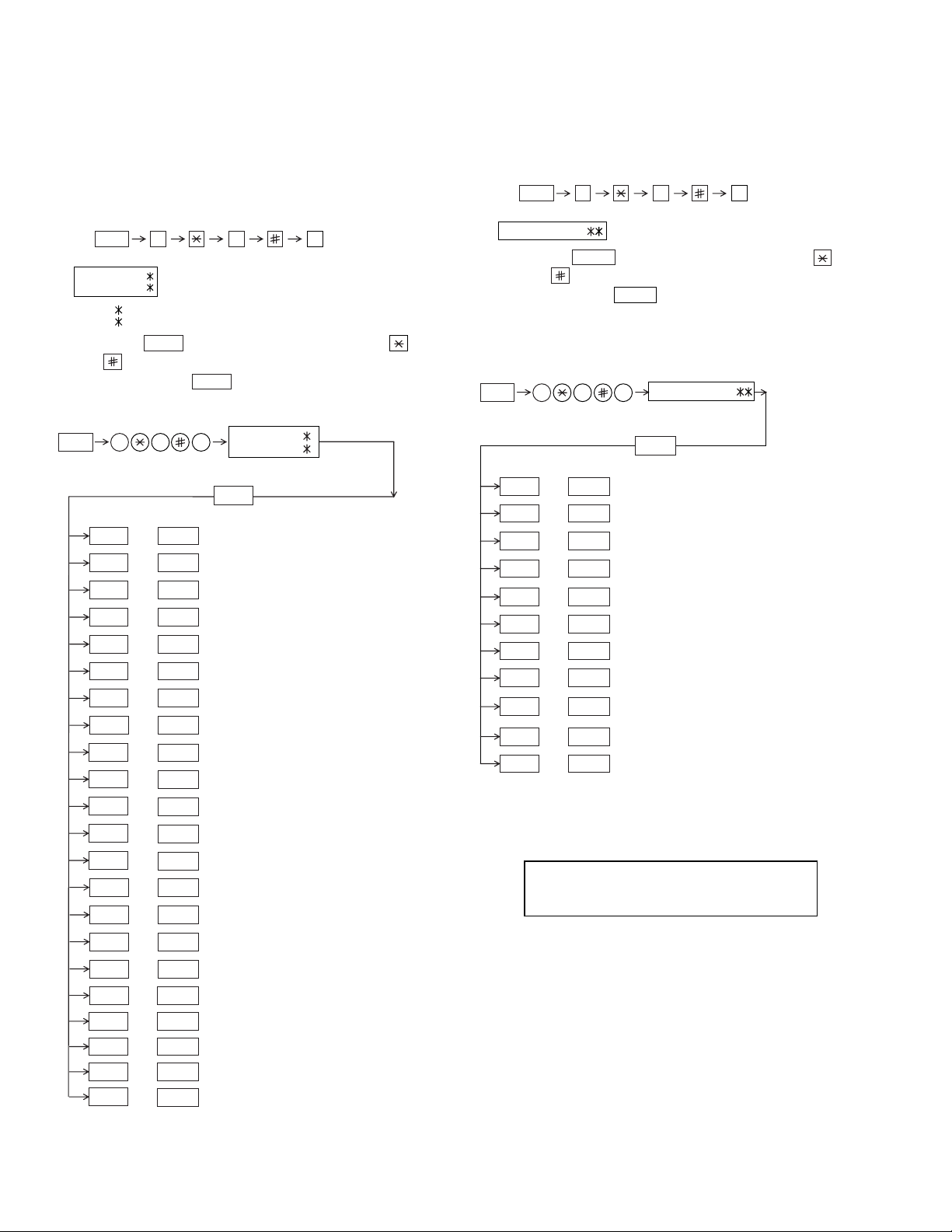

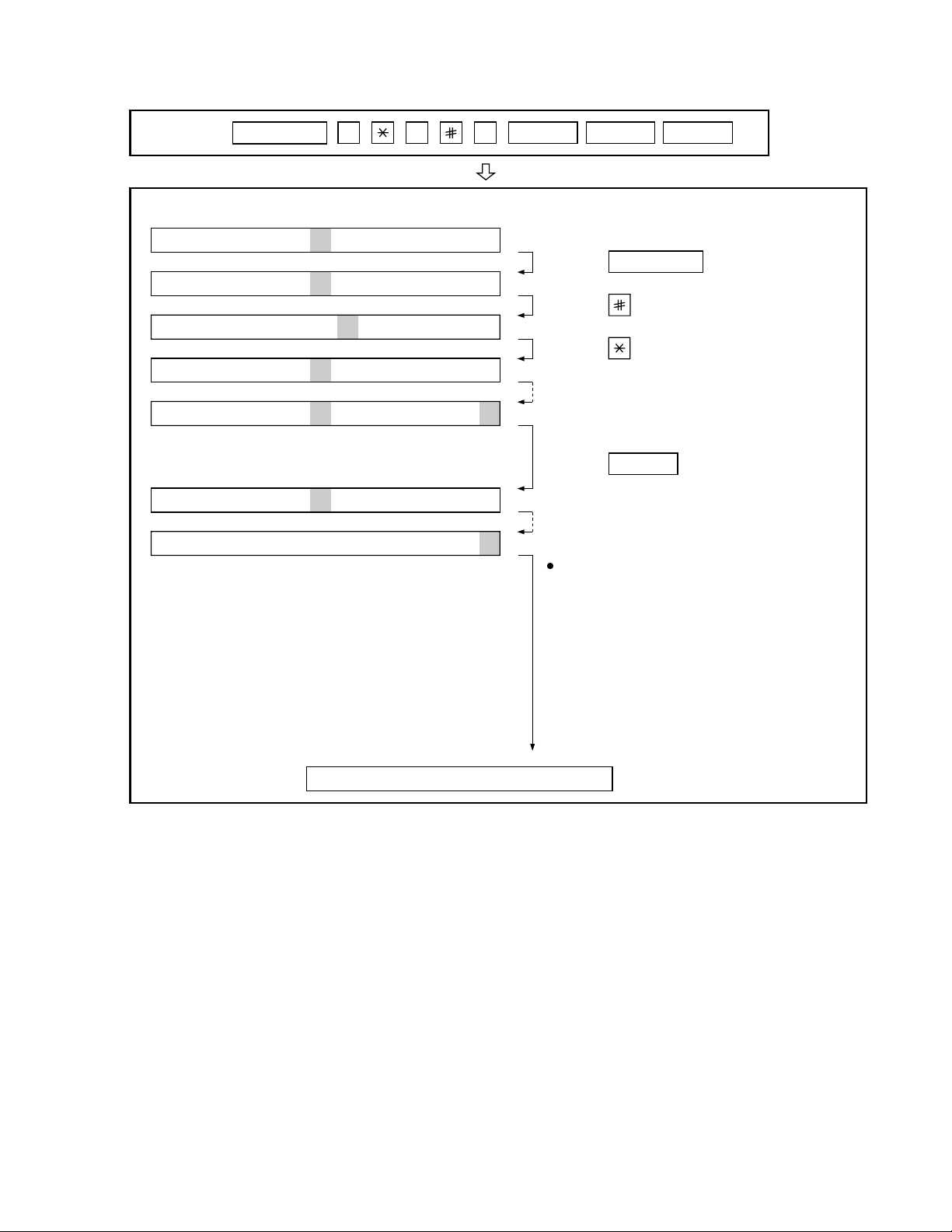

3. How to make soft switch setting

To enter the soft switch mode, make the following key entries in sequence.

FO-5800U/C

Press

FUNCTION

9 8 7 START 0 1START

S F T S W 1 = 0 0 0 0 0 0 0 0

S F T S W 1 = 1 0 0 0 0 0 0 0

S F T S W 1 = 1 0 0 0 0 0 0 0

S F T S W 1 = 1 0 0 0 0 0 0 0

S F T S W 1 = 1 0 0 0 0 0 0 0

S F T S W 2 = 0 0 0 0 0 0 0 0

S F T S W 99 = 0 0 0 0 0 0 0 0

Press FUNCTION key.

Press key.

Press key.

Bit1 - 8 are set.

Press key during setting.

START

Soft SW2 - 99 are set.

To finish the settings halfway between

SW 1 and SW99, press the STOP key.

In this case, the setting being done to

the SW No. on display will be nullified

while settings done to the preceding

SW Nos. remain in effect.

The soft switch mode is terminated.

2 – 9

Page 14

FO-5800U/C

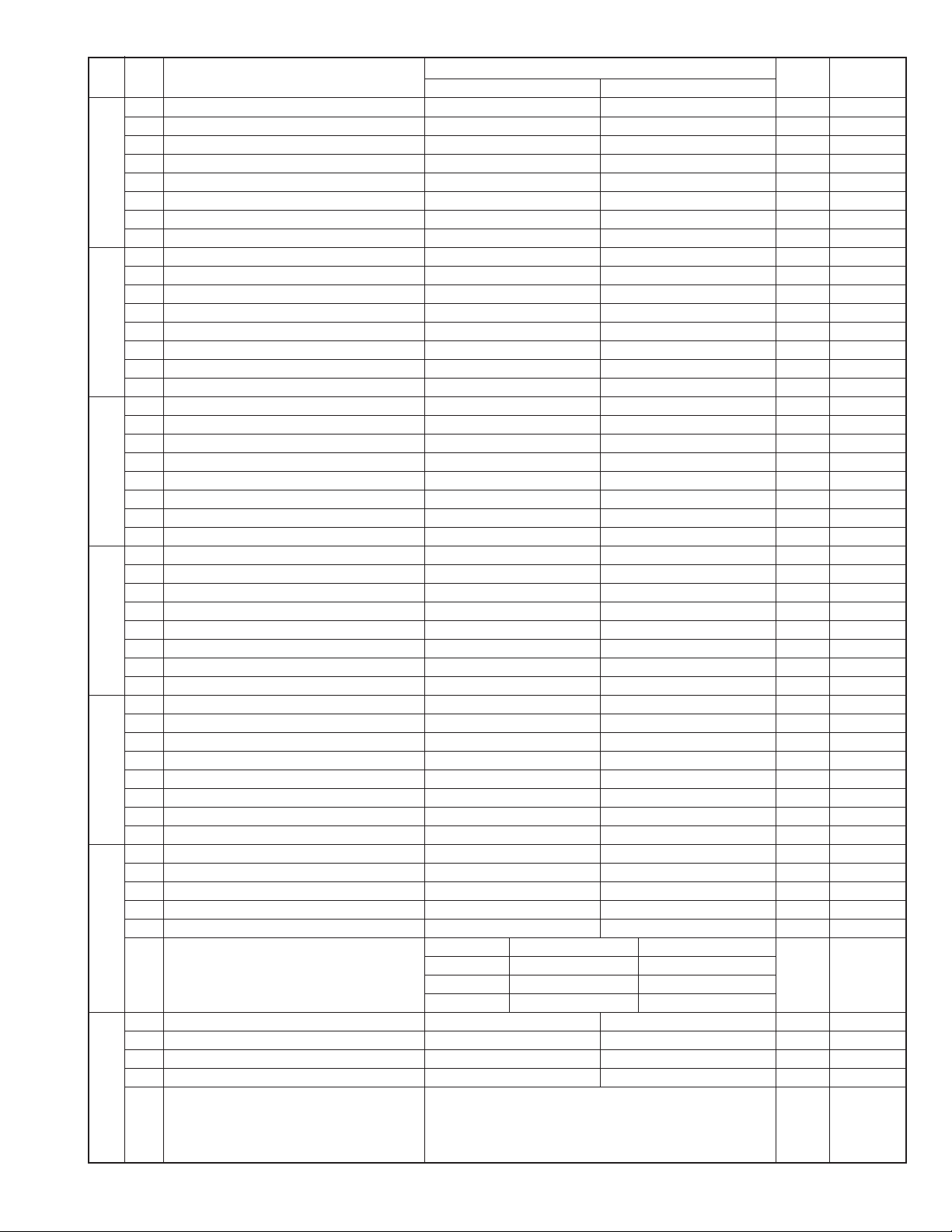

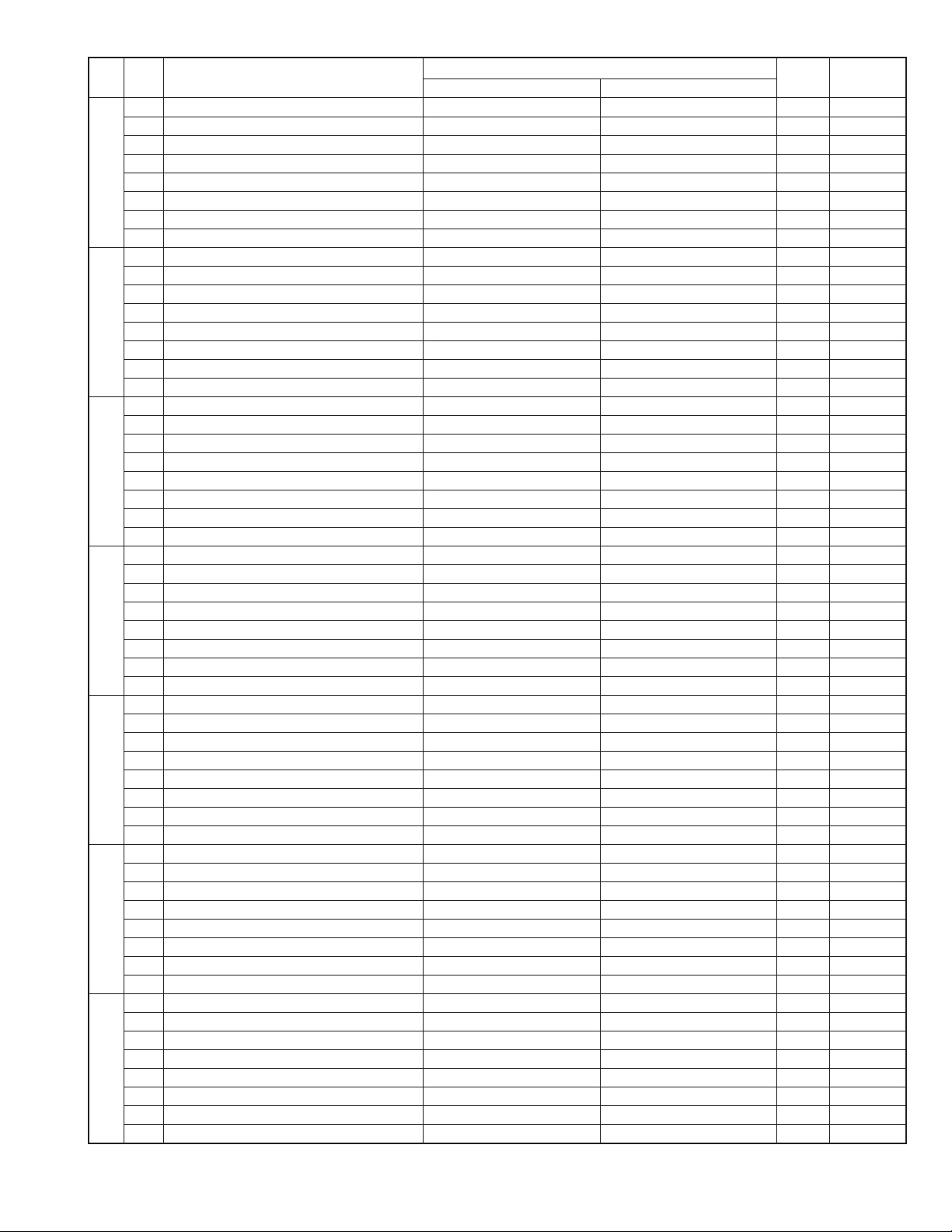

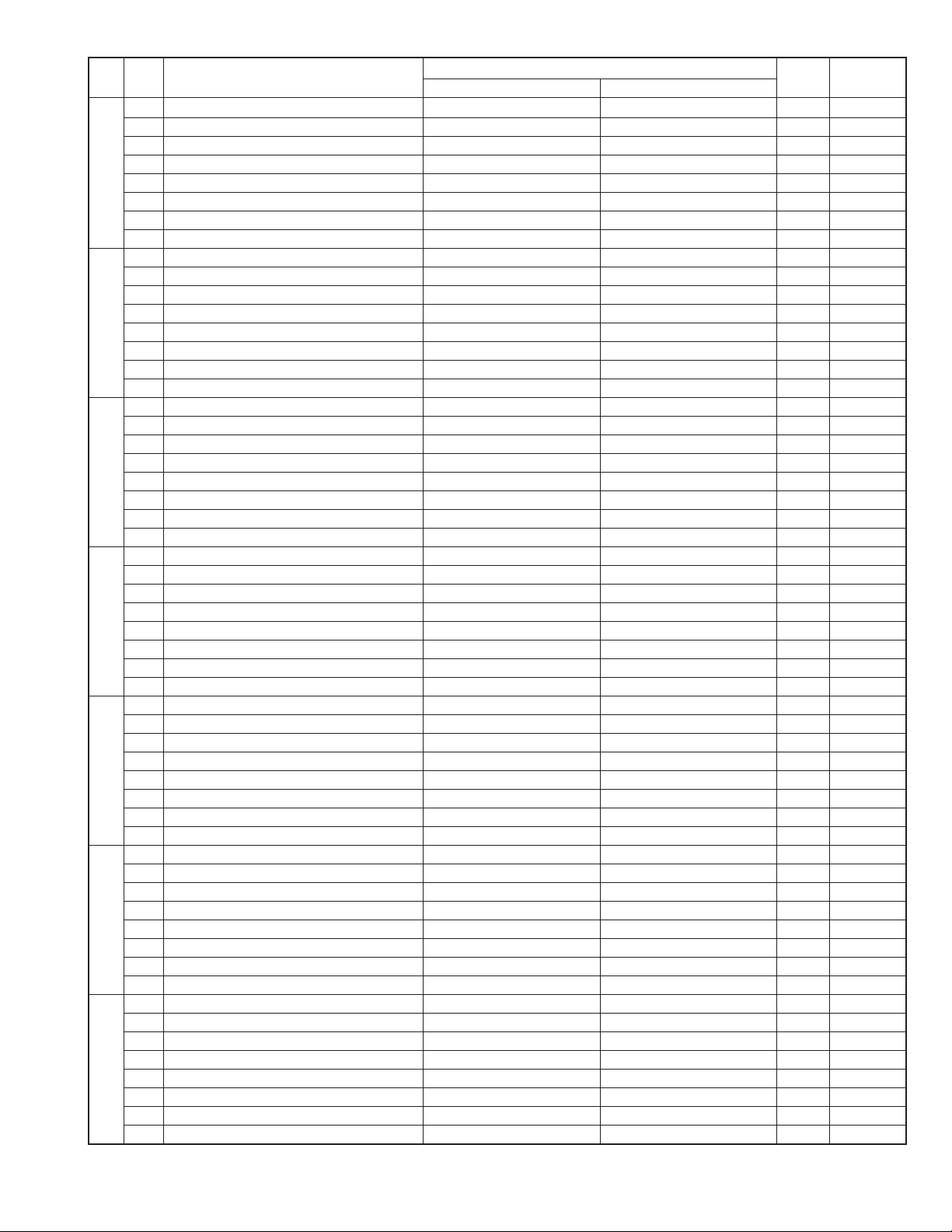

4. Soft switch description

• Soft switch

DATA

SW

NO.

NO.

1 Recall interval Binary input 8421 0 OPTION

2 No. = 1234(Data No.) 1 Set to 1~15

3 EX 0101 0

SW1

SW2

SW3

SW4 3 No. 3 1 00001

SW5

4 eg. Recall interval is set to 5 min. 1

5 Recall times Binary input 8421 0 OPTION

6 No. = 5678(Data No.) 0 Set to 0~14

7 EX 0010 1

8 eg. Recall times is set to 2 times. 0

1 Dial mode PULSE TONE 0

2 Receive mode AUTO MANUAL 1

3 ECM mode Off On 0 OPTION

4 Reserved 0

5 Polling security On Off 1 OPTION

6 Auto cover sheet No Yes 1 OPTION

7 JUNK-FAX function in manual reception Yes No 0

8 JUNK-FAX function Yes No 0 OPTION

1 Number of rings for auto-receive Binary input 8421 0 OPTION

2 (0: No ring receive) No. = 1234(Data No.) 0 Set to 0~9

3 EX 0001 0

4 eg. Number of rings for auto receive is set to 1 time. 1

5 Switch to auto-receive from manual receive Binary input 8421 0 OPTION

6 (0: No switch) No. = 5678(Data No.) 0 Set to 0~9

7 EX 0000 0

8 eg. Switch to auto receive is set to disable. 0

Communication results printout Printed at Printed at Printed at

1 No. 1 0 00110

2 No. 2 0 01010

4 Image addition function to the communication On Off 1 OPTION

result table (for memory transmission only)

5 Reserved 0

6 TEL billing code function On Off 0 OPTION

7 Billing code position Before After 1 OPTION

8 Multi-TTI feature On Off 0 OPTION

1 Time display format 24 hours 12 hours-AM/PM 0

2 Date display format Month-Day-Year Day-Month-Year 1

3 Header print Off On 0

4 Footer print On Off 0

5 Relay data output No Yes 0

6 Substitute reception Off On 0

7 Substitute reception conditions Reception disable without TSI Reception enable without TSI 0

8 CSI transmission Off On 0

ITEM

error only

Switch setting and function

1

error/timer/

memory sion mode

only only

transmis- every time

0

Not printed

Printed OPTION

Initial

setting

Remarks

2 – 10

Page 15

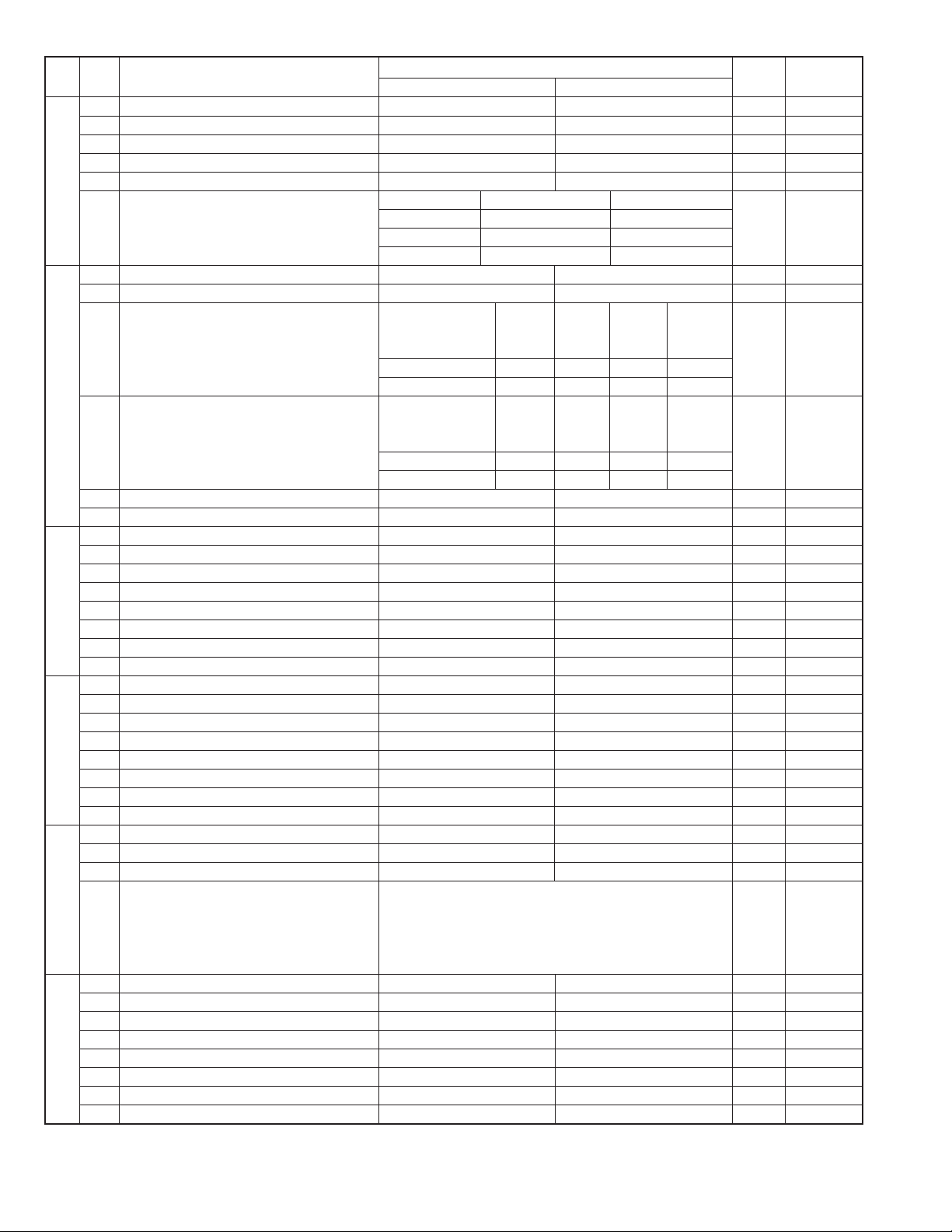

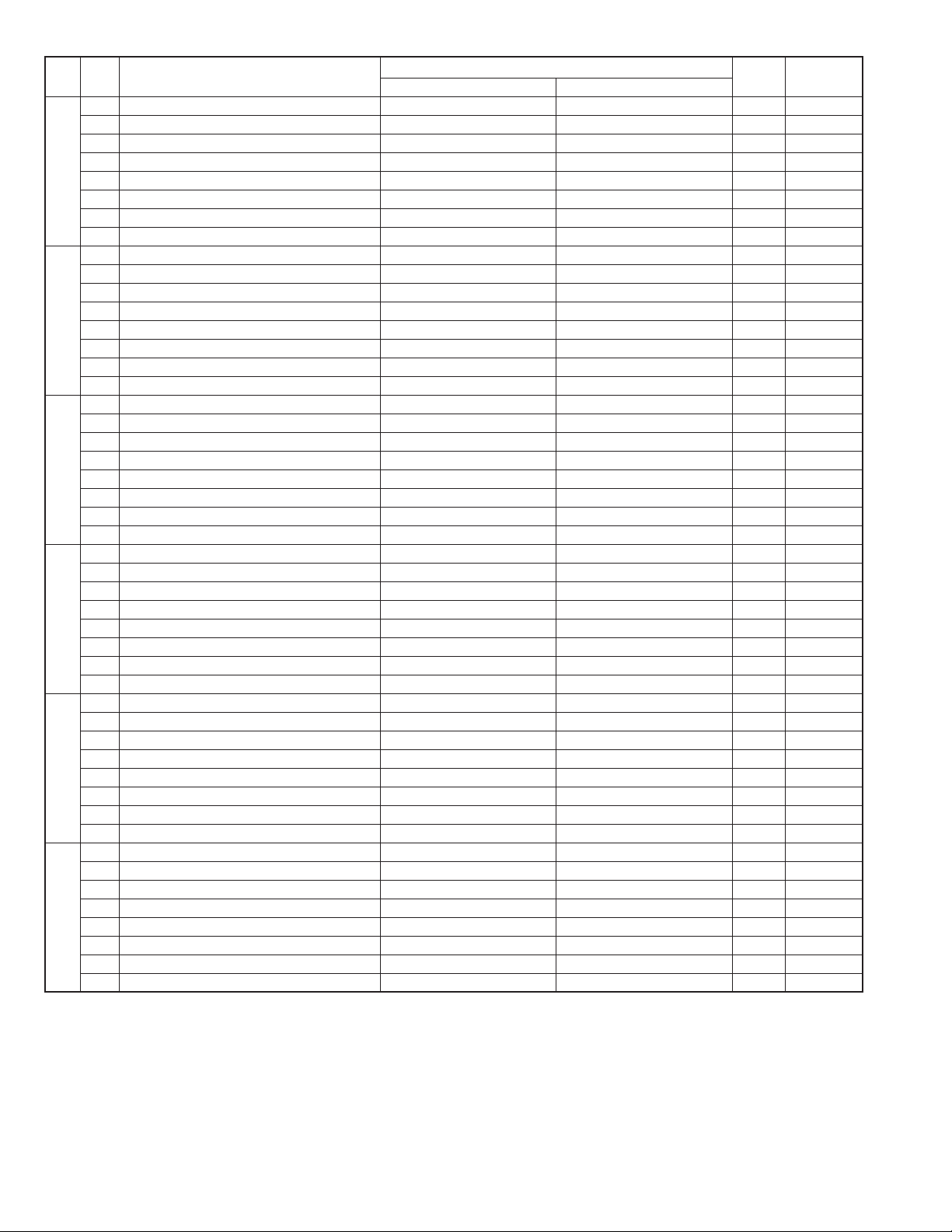

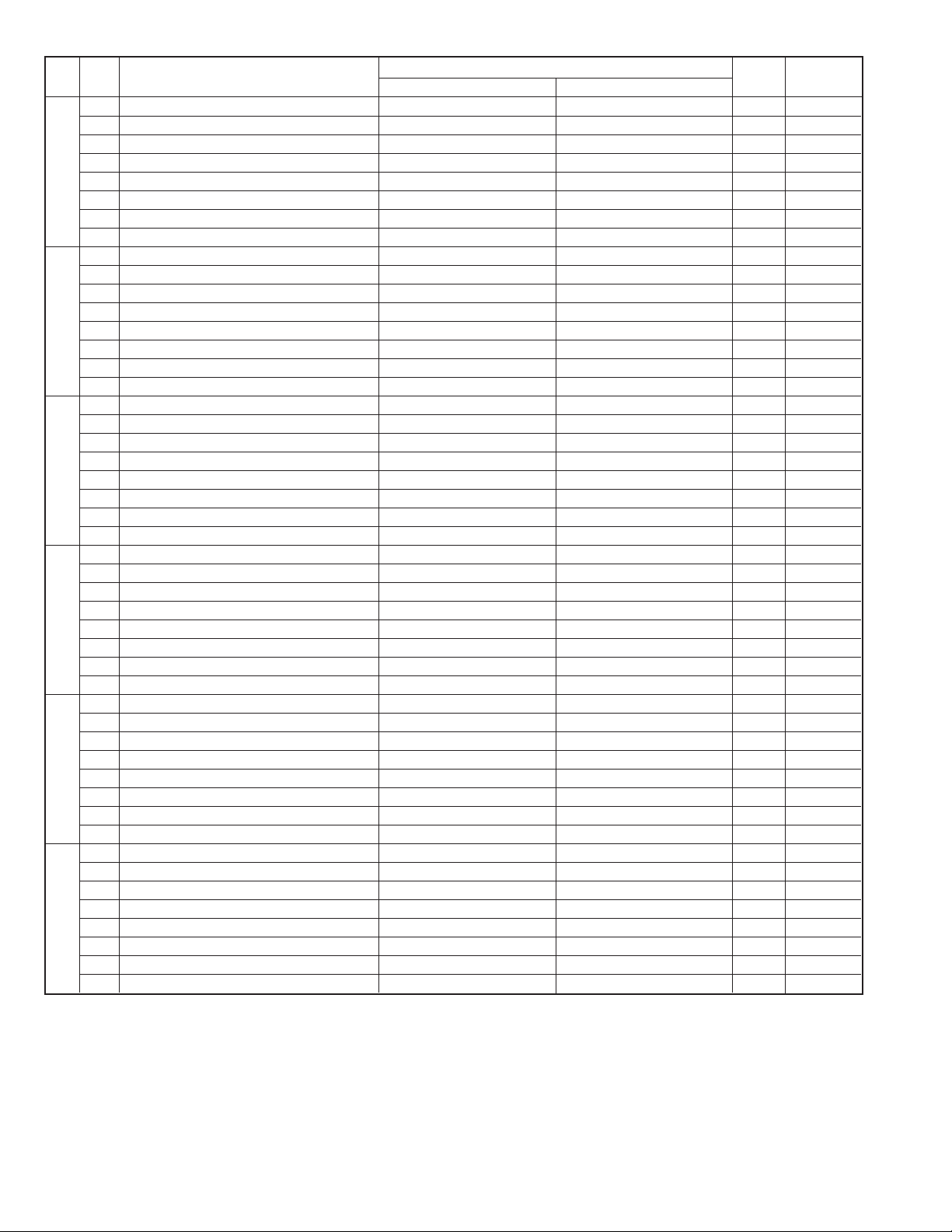

FO-5800U/C

DATA

SW

NO.

NO.

1 JBIG (Joint Bi-level Image Group) On Off 1

2 JBIG option On Off 0

3 MMR On Off 1

4MR On Off 1

SW6 Modem speed V.33 V.17 V. 29 V. 27ter

5 No. 5 0 0 1 1 1 1 0 0 0 0 1

6 No. 6 1 1 0 0 0 0 0 0 0 0 0

7 No. 7 0 1 0 1 0 1 0 1 1 0 0

8 No. 8 0 0 0 0 1 1 1 1 0 0 0

Reception speed fixed NO V. 17- V. 29- V. 27ter-

1 No. 1 0 1 0 1 0

2 No. 2 0 1 1 0 0

3 DIS receive acknowledge during Twice Once in NSF reception, twice 0 Effective to

G3 transmission in DIS reception international

SW7 comm.

4 Non-modulated carrier in V.29 On Off 0

transmission mode

5 CNG send in manual transmission On Off 1

6 Protocol monitor On Off 0

7 Line monitor On Off 0

8 Max. length for TX/RX/Copy TX: unlimited, RX: unlimited TX/Copy: 1.0m, RX: 1.5m 0

Compromised equalizer 0Km 1.8Km 3.6Km 7.2Km Valid when

1 No. 1 0 0 1 1 0 transmitting

2 No. 2 0 1 0 1 0

3 H2 mode No Yes 0

SW8

4 Signal transmission level Binary input 16 8 4 2 1 0

5 No. = 45678 (Data No.) 1

6 EX 01101 1

7 eg. Signal transmission level is set to -10dBm 0

8 1

ITEM

Switch setting and function

1

14400 12000 14400 12000

0

9600 7200 9600 7200 4800 2400

14400BPS 9600BPS 4800BPS

Initial

setting

Remarks

When 14400BPS

MODEM used,

setting to

14400BPS is

ignored.

2 – 11

Page 16

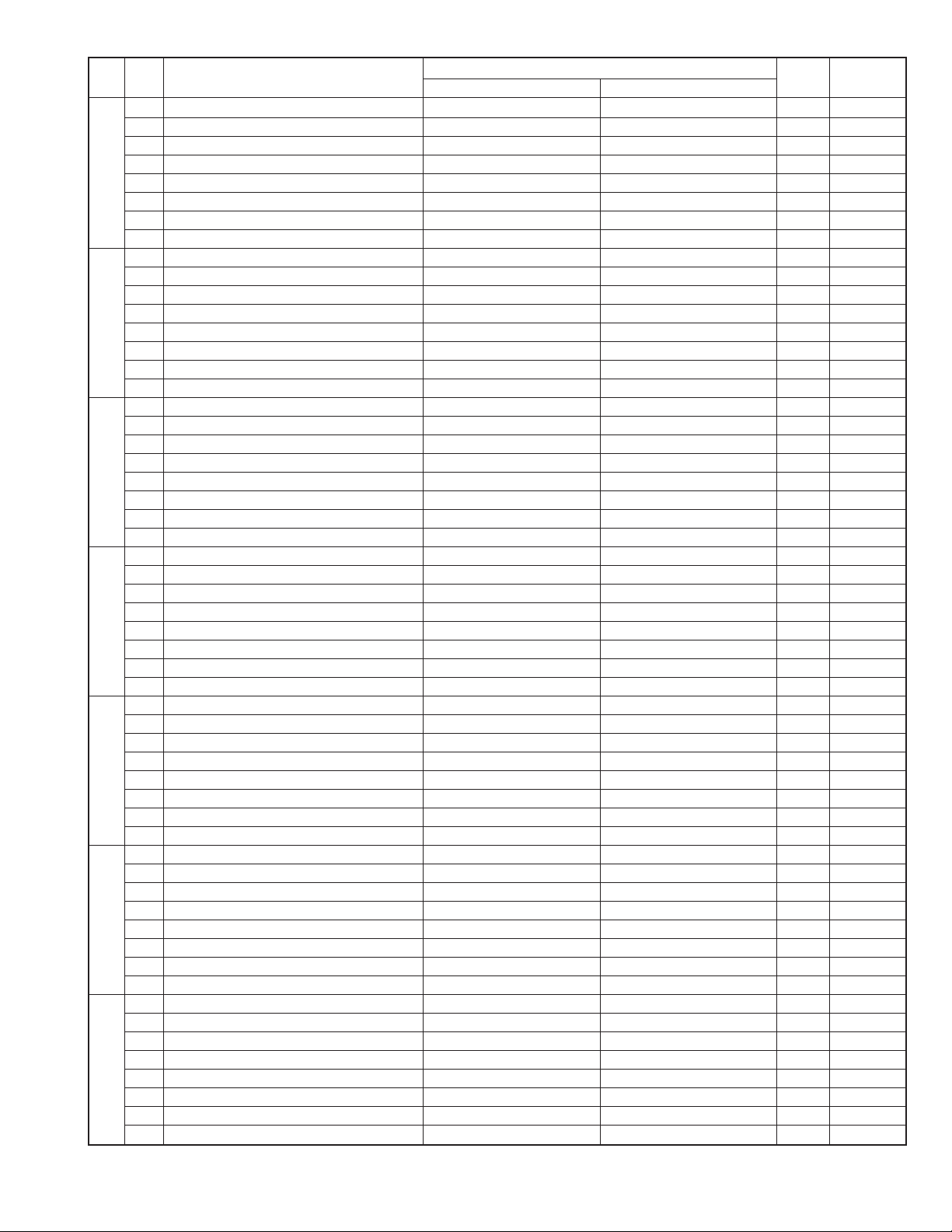

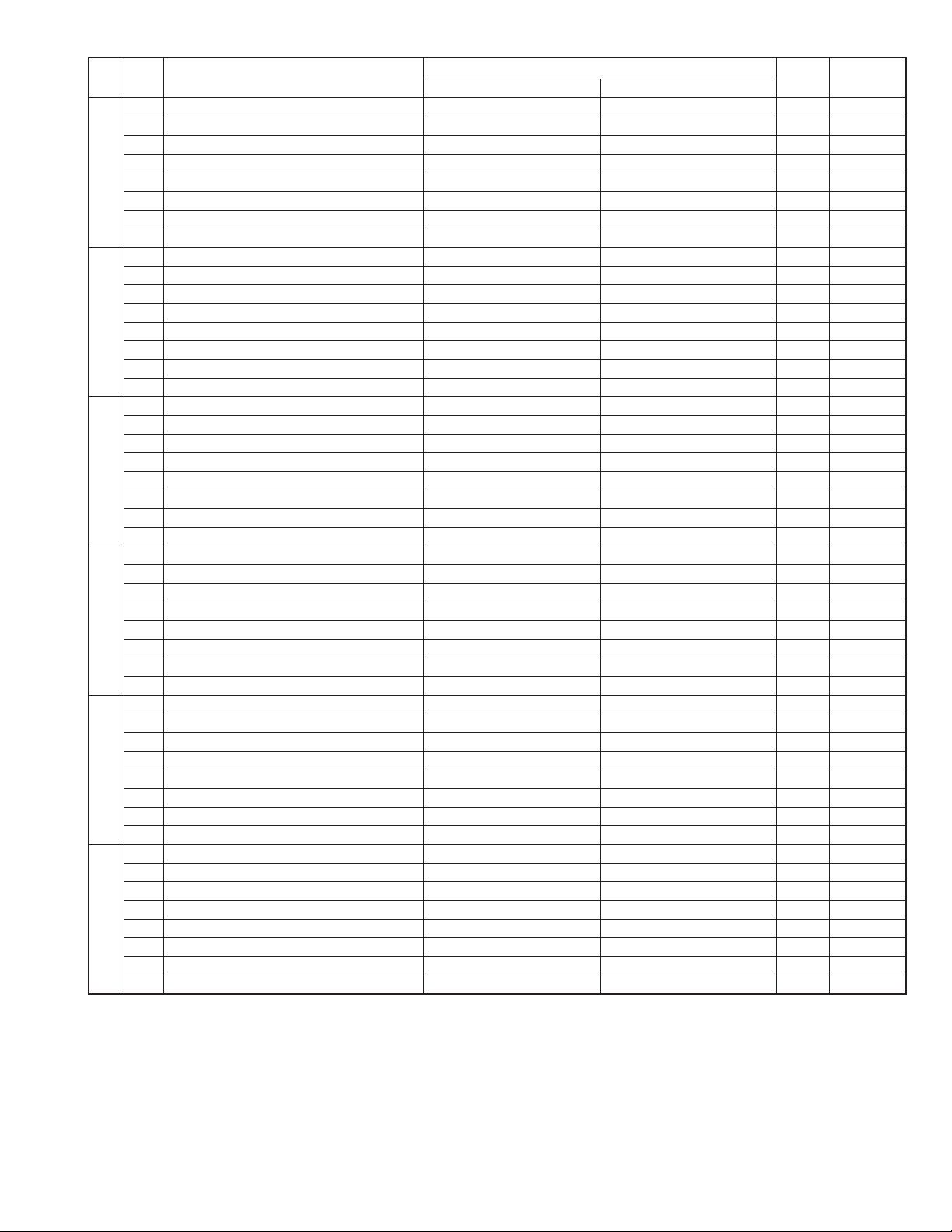

FO-5800U/C

SW

DATA

NO.

NO.

CED tone signal interval 75ms 500ms 750ms 1000ms

1 No. 1 0 0 1 1 0

2 No. 2 0 1 0 1 0

3 Equalization freeze On Off 0

SW9 4 Equalization freeze conditions All 7200bps 0

5 CED detection time 500ms 1000ms 0

Alarm buzzer 3sec 1sec No BEEP No BEEP

6 No. 5 0 0 1 1 0

7 No. 6 0 1 0 1 0

8 Action when RTN received Not Error Error 0

1 Memory retransmission times Binary input 8421 1 OPTION

2 No. = 1234(Data No.) 0

3 EX 1010 1

SW10

SW11

SW12

SW13

SW14

4 eg. Retransmission time set to 10 times. 0

5 Memory retransmission interval Binary input 8421 0 OPTION

6 No. = 5678(Data No.) 0

7 EX 0010 1

8 0

1 Reserved 1

2 Reserved 1

3 Reserved 1

4 Reserved 0

5 Reserved 1

6 Reserved 1

7 Reserved 1

8 Reserved 0

1 Reserved 1

2 Reserved 1

3 Reserved 0

EOL detection timer 13sec 25sec 5sec 5sec

4 No. 4 0 0 1 1 0

5 No. 5 0 1 0 1 0

Processing of DIS reception

after DIS transmission

6 No. 6 0 0 1 1 0

7 No. 7 0 1 0 1 0

8 The change to DB from DP by Yes No 0

1 DTMF output level (High) Binary input 16 8 4 2 1 0

2 No. = 45678 (Data No.) n = 0.5dBm 1

3 EX 01100 1

4 eg. Signal transmission level is set to -10dBm 0

5 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 DTMF output level (Low) Binary input 16 8 4 2 1 1

2 No. = 45678 (Data No.) n = 0.5dBm 0

3 EX 10000 0

4 eg. Signal transmission level is set to -10dBm 0

5 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

ITEM

Switch setting and function

1

Retransmitting

command

Breaking Apply to T.30+α

circuit T.30

0

Initial

setting

Remarks

2 – 12

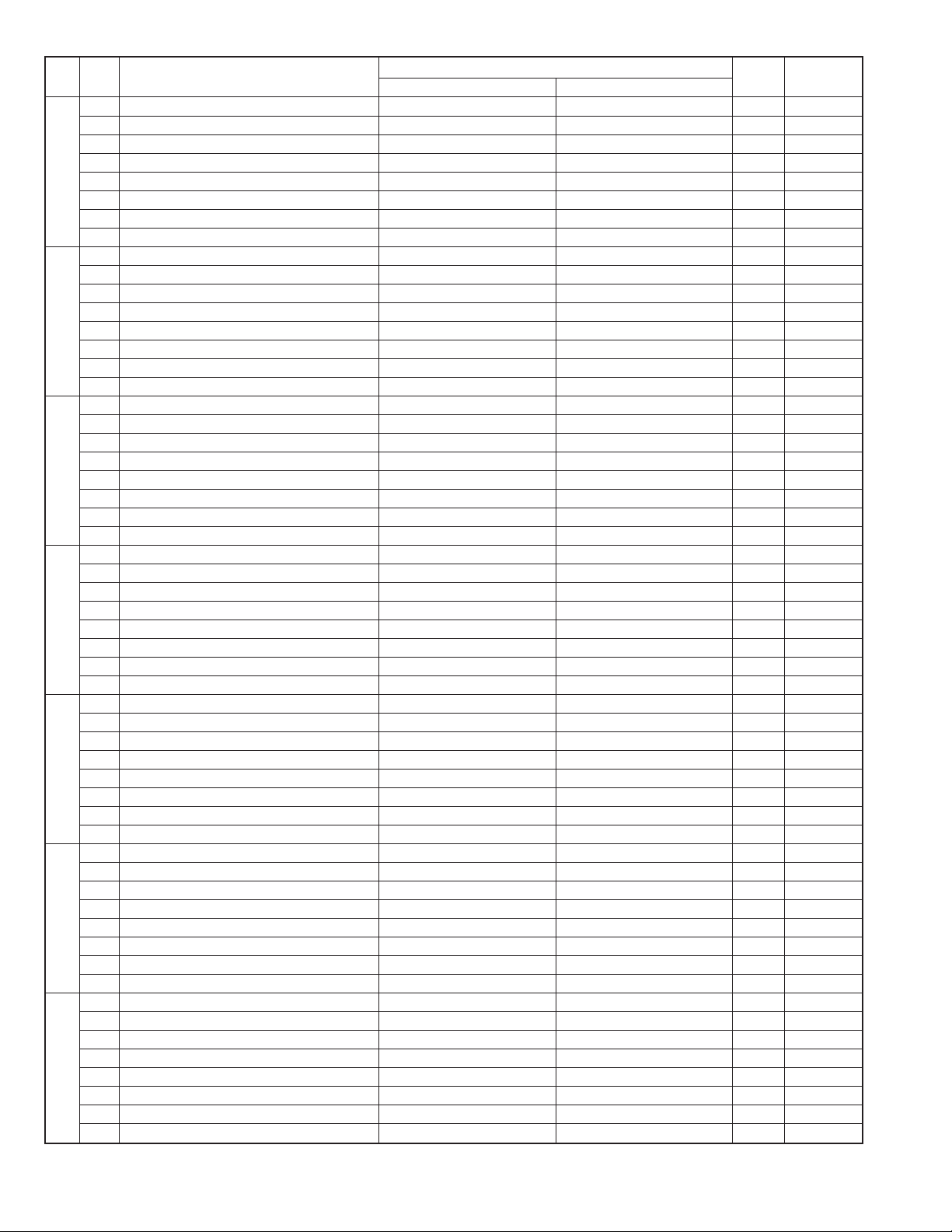

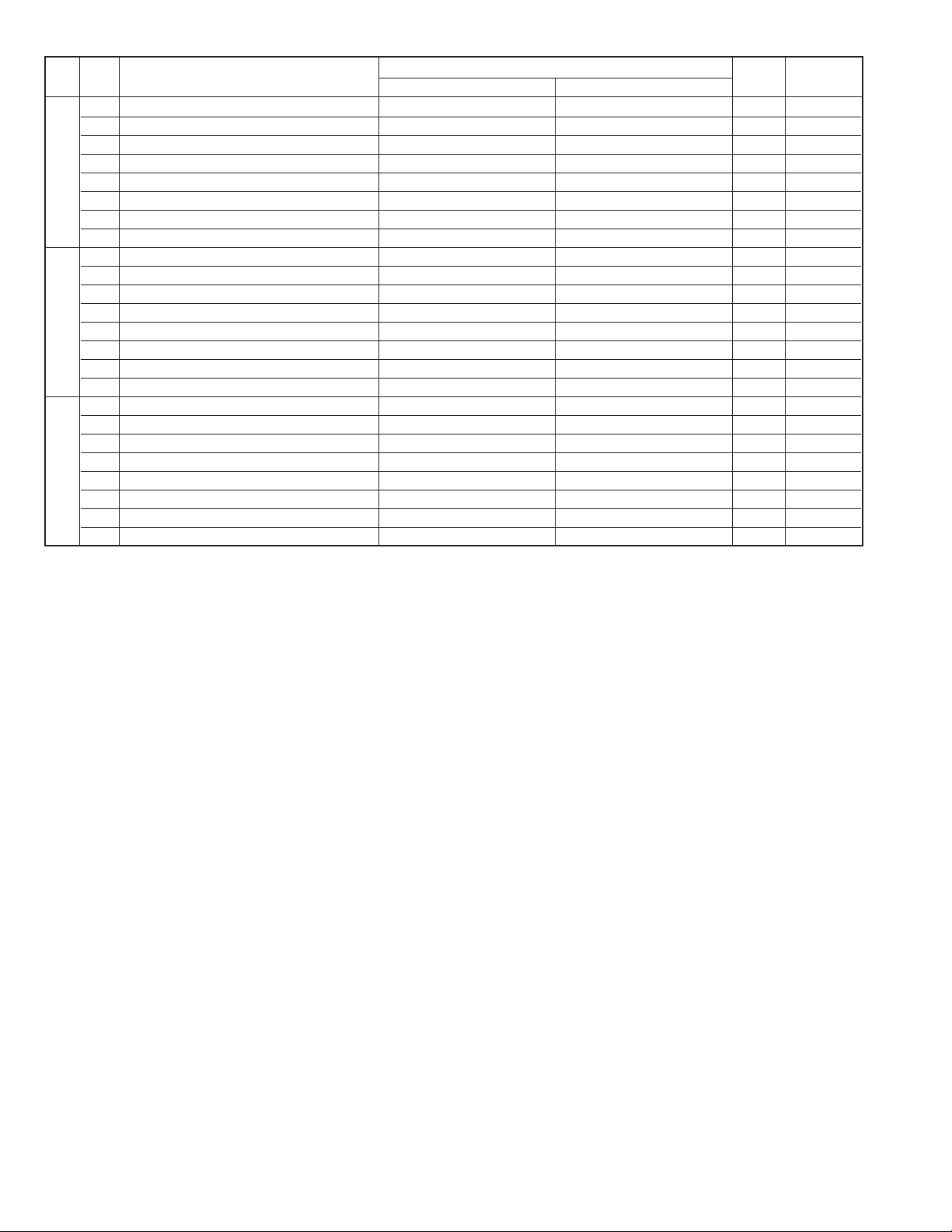

Page 17

FO-5800U/C

SW

NO.

SW15

SW16

SW17

SW18

SW19

SW20

DAT A

NO.

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

Cl Signal OFF detect enable time

5 No. 5 0 0 0 0 0 0 0 0

6 No. 6 0 0 0 0 1 1 1 1

7 No. 7 0 0 1 1 0 0 1 0

8 No. 8 0 1 0 1 0 1 0 1

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

Distinctive ringing OFF STD

5 No. 5 0 0 1 0 1 0 1 0

6 No. 6 0 0 0 1 1 0 0 0

7 No. 7 0 0 0 0 0 1 1 0

8 No. 8 0 1 0 0 0 0 0 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 1

5 Reserved 1

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 1

4 Reserved 1

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

ITEM

(ms)

Switch setting and function

1

200 300 350 400 500 700 1200

RING1 RING2 RING3 RING4 RING5

0

Initial

setting

Remarks

2 – 13

Page 18

FO-5800U/C

SW

NO.

SW21

SW22

SW23

SW24

SW25

SW26

DAT A

NO.

1 Reserved 1

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 1

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

Busy tone detection frequency

4 No. 4 0 0 0 0 1 0

5 No. 5 0 0 1 1 0 0

6 No. 6 0 1 0 1 0 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

ITEM

Switch setting and function

1

520~640Hz 300~600Hz 380~500Hz

0

reserve reserve

Initial

setting

Remarks

2 – 14

Page 19

FO-5800U/C

SW

NO.

SW27

SW28

SW29

SW30

SW31

DAT A

NO.

1 F.A.S.T (RMS) mode On Off 0

2 Reserved 0

3 V erification ST AMP Ye s No 0

4 Summer time (Day light saving) No Yes 1

Key buzzer volume Off HIGH MIDDLE LOW

5 No. 5 0 0 1 1 1

6 No. 6 0 1 0 1 0

7 Reserved 0

8 Reserved 0

Speaker volume HIGH HIGH MIDDLE LOW

1 No. 1 0 0 1 1 1

2 No. 2 0 1 0 1 1

3 Reserved 1

4 Reserved 0

Ringer volume Off HIGH MIDDLE LOW

5 No. 5 0 0 1 1 1

6 No. 6 0 1 0 1 1

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 PC I/F mode On Off 1 OPTION

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Header registration On Off 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Quick on-line function Yes No 1

Cassette selection Manual Auto-1 Auto-2 Auto-1 OPTION

1 No. 1 0 0 1 1 0

2 No. 2 0 1 0 1 1

The first priority cassette None Tray

3 No. 3 0 0 0 0

4 No. 4 0 0 1 1

5 No. 5 0 1 0 1 0

The second priority cassette None Tray

6 No. 6 0 0 0 0

7 No. 7 0 0 1 1

8 No. 8 0 1 0 1 1

ITEM

Switch setting and function

1

1st. Cass. 2nd. Cass. Tr ay OPTION

1st. Cass. 2nd. Cass. Tr ay OPTION

0

Other

Combination

Other

Combination

Initial

setting

0

1

0

1

Remarks

It is effective

only when

No.31-1/2 are

set up of manual

It is effective

only when

No.31-1/2 are

set up of manual

2 – 15

Page 20

FO-5800U/C

SW

NO.

SW32

SW33

SW34

SW35

SW36

SW37

DATA

NO.

The third priority cassette None Tray

1 No. 1 0 0 0 0 Other 0

2 No. 2 0 0 1 1 Combination 0

3 No. 3 0 1 0 1 1

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Print hold function On Off 0

Heater mode Always on Always off OPTION

1 No. 1 0 0 0

2 No. 2 0 1 1

Density adjustment of print bias Binary input 4 2 1 set to 1~6.

3 No. = 3 4 5 (Data No.) 1: faint ~ 6: deep 1 set to 0, is

4 EX 1 0 0 0 equal to 4

5 eg. Bias is set to level 4. 0 (100).

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 The default resolution for copying Super fine Fine 0 OPTION

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 1

3 Reserved 1

4 Reserved 1

5 Reserved 0

6 Reserved 1

7 Reserved 1

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 1

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 1

1 Delay time after PC printing Binary input 128 64 32 16 8 4 2 1 0

2 ( n second) No. = 1 2 3 4 5 6 7 8 (Data No.) 0

3 EX 0 0 0 0 0 1 1 0 (= 6 secs) 0

4 0

5 0

6 1

7 1

8 0

ITEM

Switch setting and function

1

1st. Cass. 2nd. Cass. Tr ay OPTION

0

Initial

setting

Remarks

It is effective

only when

No.31-1/2 are

set up of manual

2 – 16

Page 21

FO-5800U/C

SW

NO.

SW38

SW39

SW40

SW41

SW42

SW43

SW44

DATA

NO.

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

Data reduction AUTO 100%

6

(Prohibition of setting except Auto and 100%)

7 No. 7 0 0 0

8 No. 8 0 0 0

1 Automatic printing of activity report Yes (When memory full) No

2

Print out of total time and total number of pages on activity report

3 Reserved 0

4 Department function On Off 0

5 Department ID digit Binary input 8 4 2 1 0 OPTION

6 No. = 5 6 7 8 (Data No.) 1

7EX01000

8 eg. Department is set to level 4. 0

ITEM

No. 6 0 1 0

Off On 0

Switch setting and function

1

(First data is cleared when memory full)

0

Initial

setting

Remarks

0 OPTION

set to 3 ~ 9

2 – 17

Page 22

FO-5800U/C

SW

NO.

SW45

SW46

SW47

SW48

SW49

SW50

DAT A

NO.

1 Picture quality priority mode Fine standard 0 OPTION

2 Cut off mode ( When copy mode ) Continue Cut -off 0 OPTION

3 Scanning ratio in memory input 1:1 Reduce 0

4

Overseas communication mode selection function

5 Reserved 0

Reduce ratio when copy mode AUTO 100%

6

(Prohibition of setting except Auto and 100%)

7 No. 7 0 0 0

8 No. 8 0 0 0

1 Reserved 0

2 Reserved 0

Density adjustment (when Fine/STD mode) Normal Faint Deep Deep

3 No. 3 0 0 1 1 0

4 No. 4 0 1 0 1 0

Density adjustment (when Half-tone mode) Normal Faint Deep Deep

5 No. 5 0 0 1 1 0

6 No. 6 0 1 0 1 0

7 MTF correction in Half-tone mode On Off 1

8 MTF intensity in Half-tone mode Strong Weak 0

1 Cassette define L TR/A4:T ray A4 LTR 0

2 Cassette define LTR/A4:Upper A4 LTR 0

3 Cassette define LTR/A4:Lower A4 L TR 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 1

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 1

1 Secure billing code Yes No 0

2 Pause with Z key Yes No 0

3 Reserved 0

4 Z key pause time (250ms unit) Binary input 16 8421 0

5 No. = 45678(Data No.) 0

6 EX 00000 0

7 eg. Pause time 250ms 0

8 time = (n+1) x 250ms 0

1 Separate feature On Off 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Addition of header (sender information) On Off 1

6 DTMF sending by the panel test On Off 0

7 Power save system Real time Timer 1

8 Reserved 0

ITEM

Yes No 0

No. 6 0 1 1

Switch setting and function

1

0

(when Dark

mode) ONLY

(when Dark

mode) ONLY

Initial

setting

Remarks

Memory Scanning

2 – 18

Page 23

FO-5800U/C

SW

NO.

SW51

SW52

SW53

SW54

SW55

SW56

SW57

DATA

NO.

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

ITEM

Switch setting and function

1

0

Initial

setting

Remarks

2 – 19

Page 24

FO-5800U/C

SW

NO.

SW58

SW59

SW60

SW61

SW62

SW63

DATA

NO.

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 1

4 Reserved 0

5 Reserved 0

6 Reserved 1

7 Reserved 0

8 Reserved 1

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 1

3 Waiting time after dialing 90 sec

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

ITEM

Switch setting and function

1

Depends on each country’s specifications

0

Initial

setting

0

Remarks

2 – 20

Page 25

FO-5800U/C

SW

NO.

SW64

SW65

SW66

SW67

SW68

SW69

SW70

DATA

NO.

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 1

6 Reserved 1

7 Reserved 0

8 Reserved 1

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

ITEM

Switch setting and function

1

0

Initial

setting

Remarks

2 – 21

Page 26

FO-5800U/C

SW

NO.

SW71

SW72

SW73

SW74

SW75

SW76

SW77

DATA

NO.

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

ITEM

Switch setting and function

1

0

Initial

setting

Remarks

2 – 22

Page 27

FO-5800U/C

SW

NO.

SW78

SW79

SW80

SW81

SW82

SW83

SW84

DATA

NO.

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

ITEM

Switch setting and function

1

0

Initial

setting

Remarks

2 – 23

Page 28

FO-5800U/C

SW

NO.

SW85

SW86

SW87

SW88

SW89

SW90

DATA

NO.

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

ITEM

Switch setting and function

1

0

Initial

setting

Remarks

2 – 24

Page 29

FO-5800U/C

SW

NO.

SW91

SW92

SW93

SW94

SW95

SW96

DATA

NO.

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

ITEM

Switch setting and function

1

0

Initial

setting

Remarks

2 – 25

Page 30

FO-5800U/C

SW

NO.

SW97

SW98

SW99

DATA

NO.

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 0

8 Reserved 0

1 Reserved 0

2 Reserved 0

3 Reserved 0

4 Reserved 0

5 Reserved 0

6 Reserved 0

7 Reserved 1

8 Reserved 1

ITEM

Switch setting and function

1

0

Initial

setting

Remarks

2 – 26

Page 31

FO-5800U/C

• Soft switch function description

SW1 No. 1 ~ No. 4 Recall interval

Choice is made for a recall interval for speed and rapid dial numbers.

Use a binary number to program this. If set to 0 accidentally, 1 will be

assumed.

SW1 No. 5 ~ No. 8 Recall times

Choice is made as to how many recall times should be made. Use a

binary number to program this.

SW2 No. 1 Dial mode

Switch the type according to the telephone circuit connected to the facsimile.

0: PULSE DIAL

1: TONE DIAL

SW2 No. 2 Receive mode

Auto/manual receiving mode is set.

SW2 No. 3 ECM mode

Used to determine ECM mode function. Refer to the following table.

SW2 No. 4 Reserved

Set to "0".

SW2 No. 5 Polling security

This switch is employed to enable or disable the polling operation using

the ID code verification function, in order to prevent unauthorized polling

operation.

SW2 No. 6 Auto cover sheet

When "1" (=YES) is selected, the cover sheet is automatically sent after

transmission of the original to notify the receiver of the number of original sheets transmitted.

SW2 No. 7 JUNK-FAX function in manual reception

It is set whether JUNK-FAX is functioned in the manual receiving mode

or not.

SW2 No. 8 JUNK-FAX function

This function is used to receive data from a specific remote machine

(station registered in entry mode). It is the function that refused a reception in the case that TSI of remote machine matched with fax number of

the station registered.

0: No

1: Y es

SW3 No. 1 ~ No. 4 Number of rings for auto-receive

(0: No ring receive)

When the machine is set in the auto receive mode, the number of rings

before answering can be selected. It may be set from one to nine rings

using a binary number. If the soft switch was set to 1, a direct connection

is made to the facsimile. If it was set to 0 accidentally, receive ring is set

to 1. If it was above 9, receive rings are set to 9.

SW3 No. 5 ~ No. 8 Switch to auto-receive from manual receive

(0: No switch)

This setting allows machine to switch from manual to Auto Receive mode.

Setting this number to 0 forces machine to stay in Manual receive mode.

Entering the binary number 0 forces the machine to remain in the manual

answer mode. If a number between 1 and 9 is entered, the machine will

go into the answer mode after the given number of rings. However, it can

be used as an ordinary telephone if the handset is taken off the hook

before this programmed number is finished. If entry of a number above 9

by accident, it will be set to 9. In this case, it must be corrected to the

proper number.

SW4 No. 1 ~ No. 3 Communication results printout

It is possible to obtain communication results after each transaction.

Normally, the switch is set (No. 1: 0, No. 2: 0, No. 3: 1) so that the communication result is produced only a communication error is en-countered. If No. 1 was set to 1, No. 2 was set to 1 and No. 3 was set to 0, the

communication result will be produced every time a communication is

done, even if the communication was successful.

If No. 1 was set to 0, No. 2 to 1 and No. 3 to 0, the communication result

will be produced every transmission.

Setting No. 1 to 1 No. 2 to 0 and No. 3 to 0 will disable this function. No

transaction report will be printed.

If No. 1 was set to 0, No. 2 to 0 and No. 3 to 0, the communication result

is produced only after a timer and memory transmission or when a communication error is encountered.

SW4 No. 4 Image addition function to the communication result

table (for memory transmission only)

Used to set addition of sending image to the communication result table.

SW4 No. 5 Reserved

Set to "0".

SW4 No. 6 TEL billing code function

When set to "1", the TEL billing code function is enabled.

SW4 No. 7 Billing code position

When set to "1", the billing code is delivered before dialing the remote

number. When set to "0", the billing code is delivered after dialing.

SW4 No. 8 Multi-TTI feature

When this switch is set to "1", Multi TTI function is enabled.

SW5 No. 1 Time display format

When this switch is set to "0", time is displayed in 12-hour system.

When set to "1", 24-hour system.

SW5 No. 2 Date display format

Used to select date display/print formats.

0: DAY-Month-Year

1: Month-DAY-Year

SW5 No. 3 Header print