Page 1

Rev. 1.21, Oct. 2013

M471B5674QH0

M471B5173QH0

M471B1G73QH0

M474B5173QH0

M474B1G73QH0

204pin Unbuffered SODIMM

1.35V

based on 4Gb Q-die

78FBGA with Lead-Free & Halogen-Free

(RoHS compliant)

datasheet

SAMSUNG ELECTRONICS RESERVES THE RIGHT TO CHANGE PRODUCTS, INFORMATION AND

SPECIFICATIONS WITHOUT NOTICE.

Products and specifications discussed herein are for reference purposes only. All information discussed

herein is provided on an "AS IS" basis, without warranties of any kind.

This document and all information discussed herein remain the sole and exclusive property of Samsung

Electronics. No license of any patent, copyright, mask work, trademark or any other intellectual property

right is granted by one party to the other party under this document, by implication, estoppel or otherwise.

Samsung products are not intended for use in life support, critical care, medical, safety equipment, or

similar applications where product failure could result in loss of life or personal or physical harm, or any

military or defense application, or any governmental procurement to which special terms or provisions

may apply.

For updates or additional information about Samsung products, contact your nearest Samsung office.

All brand names, trademarks and registered trademarks belong to their respective owners.

(C) 2013 Samsung Electronics Co., Ltd. All rights reserved.

- 1 -

Page 2

Rev. 1.21

Unbuffered SODIMM datasheet DDR3L SDRAM

Revision History

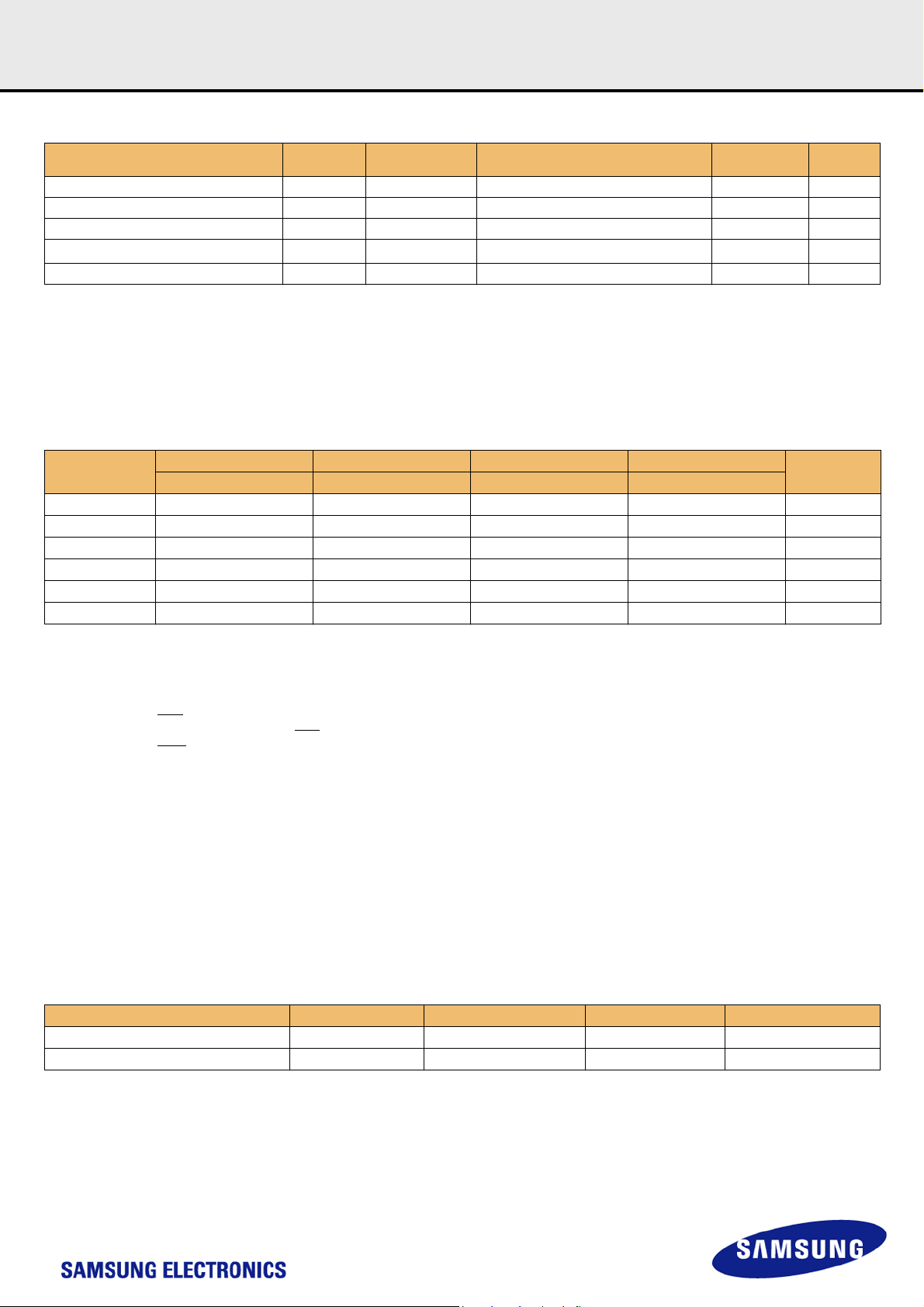

Revision No. History Draft Date Remark Editor

1.0 - First SPEC Release Jul. 2013 - S.H.Kim

1.1 - Added to 4GB(1Rx8) ECC SODIMM from Product line-up Sep. 2013 - S.H.Kim

- Corrected Typo.

1.2 - Added 2GB(1Rx16) SODIMM IDD Value. Oct. 2013 - S.H.Kim

1.21 - Added Note 3 of Chapter #1. Oct. 2013 - S.H.Kim

- 2 -

Page 3

Rev. 1.21

Unbuffered SODIMM datasheet DDR3L SDRAM

Table Of Contents

204pin Unbuffered SODIMM based on 4Gb Q-die

1. DDR3L Unbuffered SODIMM Ordering Information......................................................................................................4

2. Key Features.................................................................................................................................................................4

3. Address Configuration ..................................................................................................................................................4

4. x64 DIMM Pin Configurations (Front side/Back Side)...................................................................................................5

5. x72 DIMM Pin Configurations (Front side/Back Side)...................................................................................................6

6. Pin Description .............................................................................................................................................................7

7. SPD and Thermal Sensor for ECC SODIMMs..............................................................................................................7

8. Input/Output Functional Description..............................................................................................................................8

9. Function Block Diagram:...............................................................................................................................................10

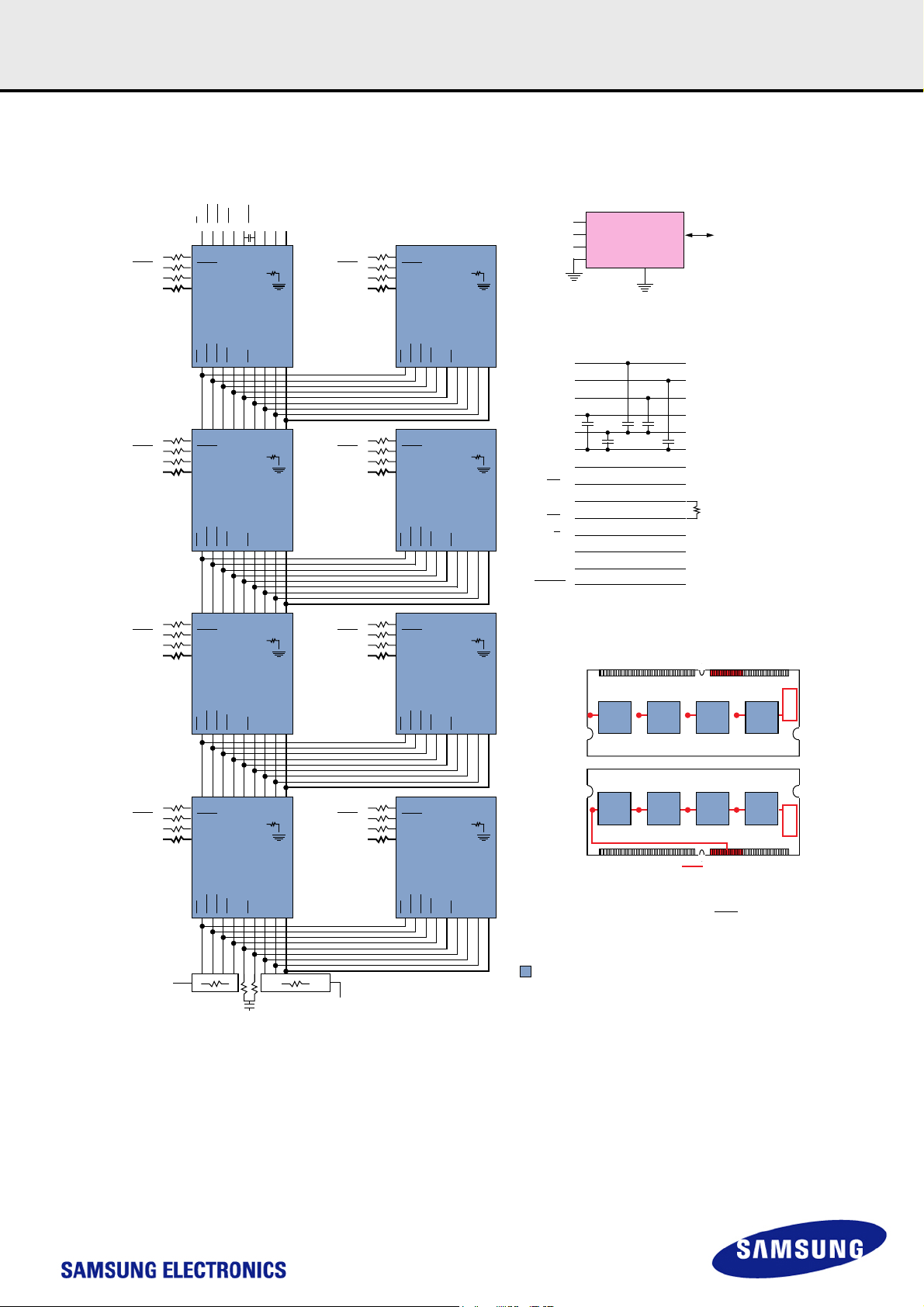

9.1 2GB, 256Mx64 Module (Populated as 1 rank of x16 DDR3 SDRAMs) ................................................................... 10

9.2 4GB, 512Mx64 Module (Populated as 1 rank of x8 DDR3 SDRAMs) ..................................................................... 11

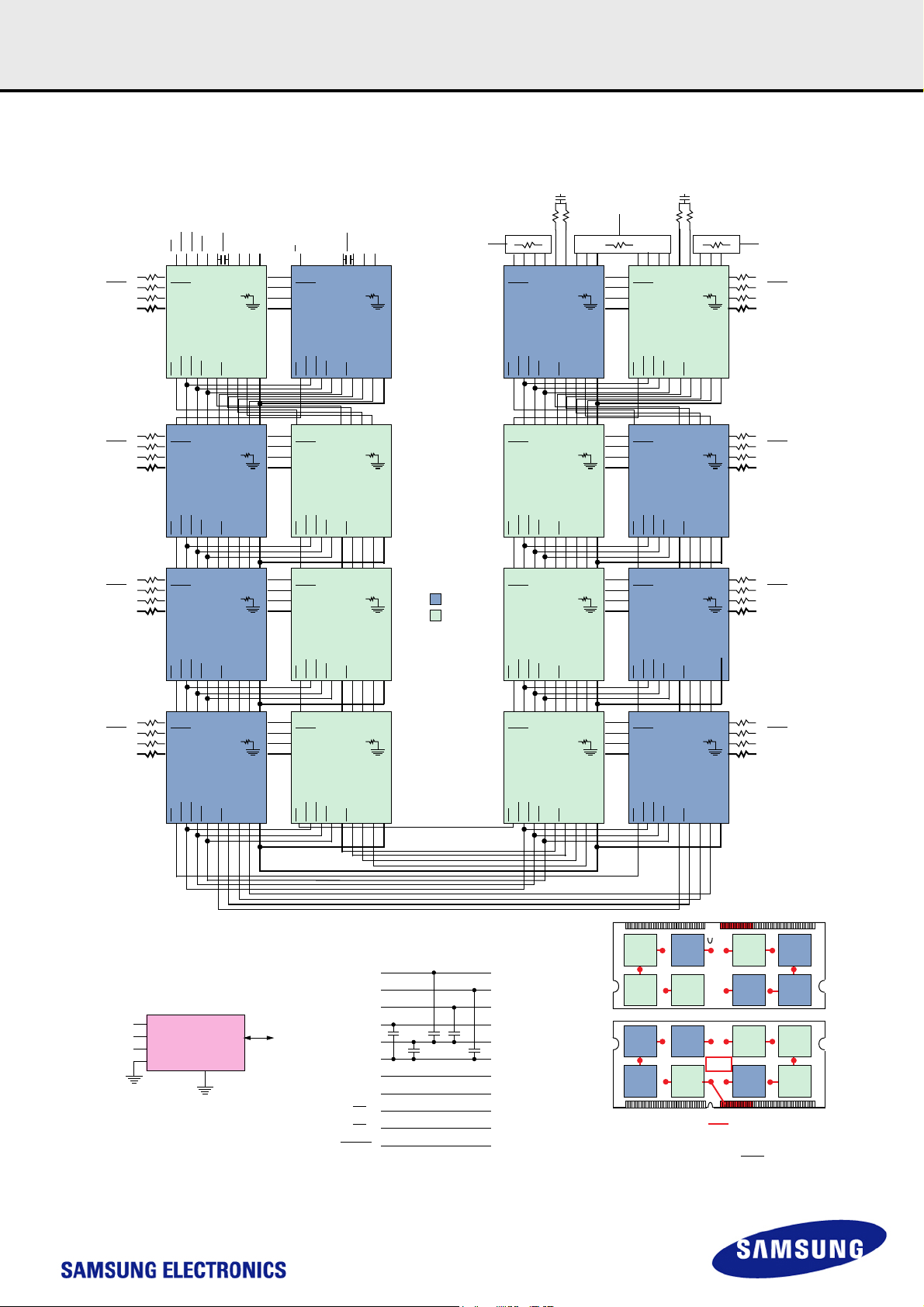

9.3 8GB, 1Gx64 Module (Populated as 2 ranks of x8 DDR3 SDRAMs)........................................................................12

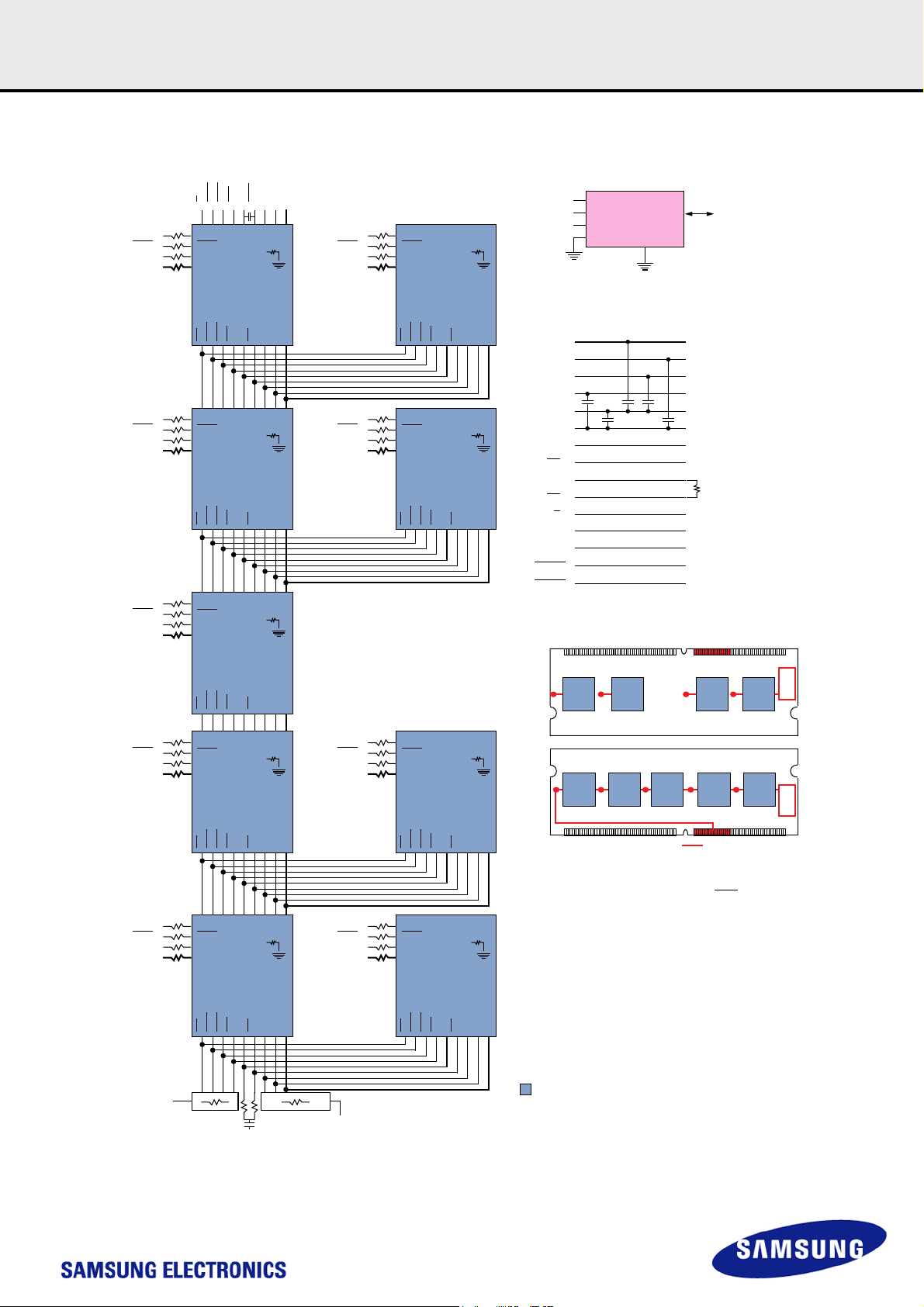

9.4 4GB, 512Mx72 Module (Populated as 1 rank of x8 DDR3 SDRAMs) ..................................................................... 13

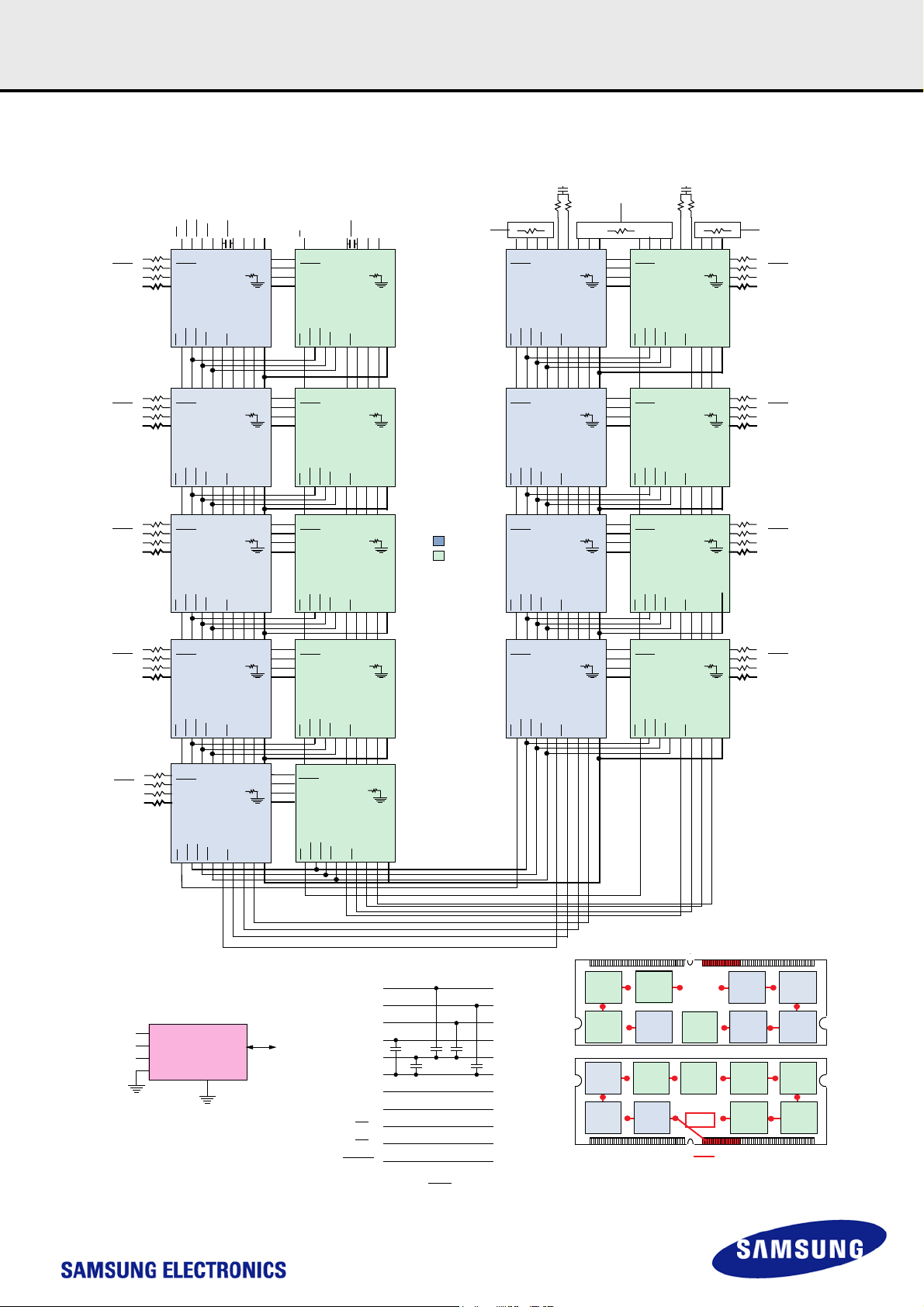

9.5 8GB, 1Gx72 Module (Populated as 2 ranks of x8 DDR3 SDRAMs)........................................................................14

10. Absolute Maximum Ratings ........................................................................................................................................15

10.1 Absolute Maximum DC Ratings............................................................................................................................. 15

10.2 DRAM Component Operating Temperature Range ..............................................................................................15

11. AC & DC Operating Conditions...................................................................................................................................15

11.1 Recommended DC Operating Conditions ............................................................................................................15

12. AC & DC Input Measurement Levels ..........................................................................................................................16

12.1 AC & DC Logic Input Levels for Single-ended Signals..........................................................................................16

12.2 V

12.3 AC and DC Logic Input Levels for Differential Signals ..........................................................................................19

12.3.1. Differential Signals Definition ......................................................................................................................... 19

12.3.2. Differential Swing Requirement for Clock (CK -

12.3.3. Single-ended Requirements for Differential Signals ......................................................................................21

12.3.4. Differential Input Cross Point Voltage ............................................................................................................ 22

12.4 Slew Rate Definition for Single Ended Input Signals.............................................................................................23

12.5 Slew rate definition for Differential Input Signals ................................................................................................... 23

13. AC & DC Output Measurement Levels .......................................................................................................................23

13.1 Single Ended AC and DC Output Levels...............................................................................................................23

13.2 Differential AC and DC Output Levels ................................................................................................................... 23

13.3 Single-ended Output Slew Rate ............................................................................................................................ 23

13.4 Differential Output Slew Rate ................................................................................................................................ 25

14. IDD specification definition..........................................................................................................................................26

15. IDD SPEC Table .........................................................................................................................................................28

16. Input/Output Capacitance ...........................................................................................................................................31

17. Electrical Characteristics and AC timing .....................................................................................................................32

17.1 Refresh Parameters by Device Density................................................................................................................. 32

17.2 Speed Bins and CL, tRCD, tRP, tRC and tRAS for Corresponding Bin ................................................................32

17.3 Speed Bins and CL, tRCD, tRP, tRC and tRAS for Corresponding Bin ................................................................32

17.3.1. Speed Bin Table Notes .................................................................................................................................. 36

18. Timing Parameters by Speed Grade ..........................................................................................................................37

18.1 Jitter Notes ............................................................................................................................................................40

18.2 Timing Parameter Notes........................................................................................................................................ 41

19. Physical Dimensions :.................................................................................................................................................42

19.1 256Mbx16 based 256Mx64 Module (1 Rank) - M471B5674QH0.......................................................................... 42

19.2 512Mbx8 based 512Mx64 Module (1 Rank) - M471B5173QH0............................................................................ 43

19.3 512Mbx8 based 1Gx64 Module (2 Ranks) - M471B1G73QH0 .............................................................................44

19.4 512Mbx8 based 512Mx72 Module (1 Rank) - M474B5173QH0............................................................................ 45

19.5 512Mbx8 based 1Gx72 Module (2 Ranks) - M474B1G73QH0 .............................................................................46

Tolerances....................................................................................................................................................18

REF

CK) and Strobe (DQS - DQS) ............................................. 19

- 3 -

Page 4

Rev. 1.21

Unbuffered SODIMM datasheet DDR3L SDRAM

1. DDR3L Unbuffered SODIMM Ordering Information

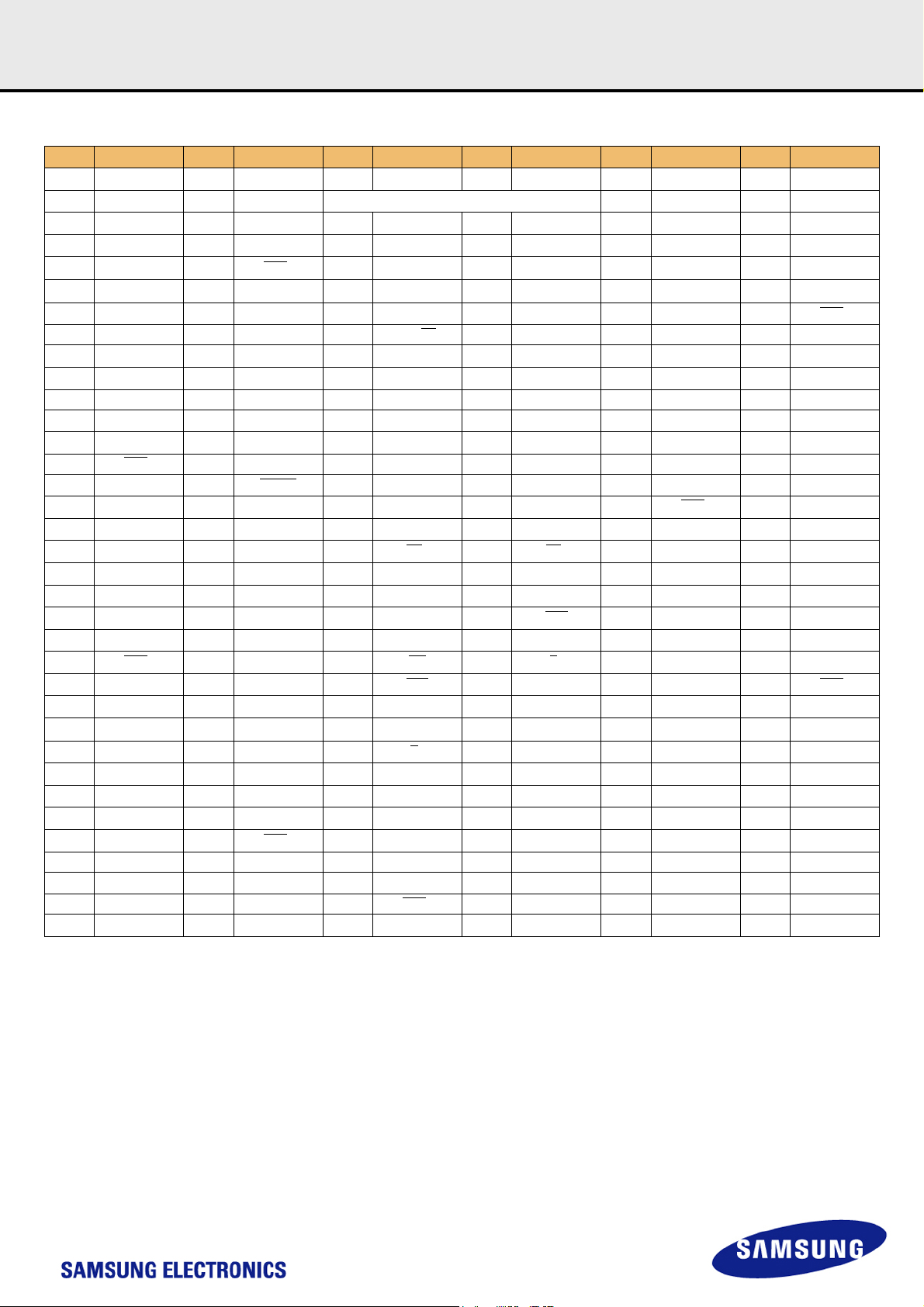

Part Number

M471B5674QH0-YH9/K0 2GB 256Mx64 256Mx16(K4B4G1646Q-HY##)*4 1 30mm

M471B5173QH0-YH9/K0 4GB 512Mx64 512Mx8(K4B4G0846Q-HY##)*8 1 30mm

M471B1G73QH0-YH9/K0 8GB 1Gx64 512Mx8(K4B4G0846Q-HY##)*16 2 30mm

M474B5173QH0-YK0

M474B1G73QH0-YK0 8GB 1Gx72 512Mx8(K4B4G0846Q-HY##)*18 2 30mm

NOTE :

1. "##" - H9/K0

2. H9 - 1333Mbps 9-9-9 / K0 - 1600Mbps 11-11-11

- DDR3L-1600(11-11-11) is backward compatible to DDR3L-1333(9-9-9)

3. Please contact Samsung for product availability.

2

3

Density Organization

4GB 512Mx72 512Mx8(K4B4G0846Q-HY##)*9 1 30mm

Component Composition

1

Number of

Rank

Height

2. Key Features

Speed

tCK(min) 2.5 1.875 1.5 1.25 ns

CAS Latency 6 7 9 11 nCK

tRCD(min) 15 13.125 13.5 13.75 ns

tRP(min) 15 13.125 13.5 13.75 ns

tRAS(min) 37.5 37.5 36 35 ns

tRC(min) 52.5 50.625 49.5 48.75 ns

• JEDEC standard 1.35V(1.28V~1.45V) & 1.5V(1.425V~1.575V) Power Supply

•V

• 400 MHz fCK for 800Mb/sec/pin, 533MHz fCK for 1066Mb/sec/pin, 667MHz fCK for 1333Mb/sec/pin, 800MHz fCK for 1600Mb/sec/pin

• 8 independent internal bank

• Programmable CAS Latency: 5,6,7,8,9,10,11

• Programmable Additive Latency(Posted CAS) : 0, CL - 2, or CL - 1 clock

• Programmable CAS Write Latency(CWL) = 5 (DDR3-800), 6 (DDR3-1066), 7 (DDR3-1333) and 8 (DDR3-1600)

• 8-bit pre-fetch

• Burst Length: 8 (Interleave without any limit, sequential with starting address “000” only), 4 with tCCD = 4 which does not allow seamless read or

• Bi-directional Differential Data Strobe

• Internal(self) calibration : Internal self calibration through ZQ pin (RZQ : 240 ohm ± 1%)

• On Die Termination using ODT pin

• Average Refresh Period 7.8us at lower then T

• Asynchronous Reset

= 1.35V(1.28V~1.45V) & 1.5V(1.425V~1.575V)

DDQ

write [either On the fly using A12 or MRS]

DDR3-800 DDR3-1066 DDR3-1333 DDR3-1600

6-6-6 7-7-7 9-9-9 11-11-11

85C, 3.9us at 85C < T

CASE

CASE

95C

Unit

3. Address Configuration

Organization Row Address Column Address Bank Address Auto Precharge

512Mx8(4Gb) based Module A0-A15 A0-A9 BA0-BA2 A10/AP

256Mx16(4Gb) based Module A0-A14 A0-A9 BA0-BA2 A10/AP

- 4 -

Page 5

Rev. 1.21

Unbuffered SODIMM datasheet DDR3L SDRAM

4. x64 DIMM Pin Configurations (Front side/Back Side)

Pin Front Pin Back Pin Front Pin Back Pin Front Pin Back

1

3

V

REFDQ

V

2

SS

4 DQ4 KEY

V

SS

71

V

SS

72

V

SS

5 DQ0 6 DQ5 73 CKE0 74 CKE1

7 DQ1 8

9

V

SS

10 DQS0 77 NC 78

V

SS

75

11 DM0 12 DQS0 79 BA2 80

13

V

SS

14

V

SS

81

15 DQ2 16 DQ6 83 A12/

V

DD

V

DD

76

82

V

A15

A14

V

DD

3

3

DD

BC 84 A11 153 DM5 154 DQS5

17 DQ3 18 DQ7 85 A9 86 A7 155

19

V

SS

20

V

SS

87

V

DD

88

V

DD

21 DQ8 22 DQ12 89 A8 90 A6 159 DQ43 160 DQ47

23 DQ9 24 DQ13 91 A5 92 A4 161

25

27

V

SS

26

DQS1 28 DM1 95 A3 96 A2 165 DQ49 166 DQ53

V

SS

93

V

DD

94

V

DD

29 DQS1 30 RESET 97 A1 98 A0 167

31

V

SS

32

V

SS

99

V

DD

100

V

DD

33 DQ10 34 DQ14 101 CK0 102 CK1 171

35 DQ11 36 DQ15 103 CK0 104 CK1 173

37

V

SS

38

V

SS

39 DQ16 40 DQ20

41 DQ17 42 DQ21

43

V

SS

44

V

SS

45 DQS2 46 DM2

47 DQS2 48

49

V

SS

50 DQ22

V

SS

51 DQ18 52 DQ23

53 DQ19 54

55

V

SS

56 DQ28

V

SS

57 DQ24 58 DQ29

59 DQ25 60

61

V

SS

62 DQS3

V

SS

105 V

107

A10/AP 108 BA1 177 DQ51 178

109

111 V

113

115

117 V

119

121

123 V

125

127 V

129

DD

106

V

DD

BA0 110 RAS 179

DD

112

V

DD

WE 114 S0 183 DQ57 184

CAS 116 ODT0 185

V

DD

A13

DD

118

3

120 ODT1 189

S1 122 NC 191 DQ58 192 DQ62

DD

124

TEST 126

SS

128

V

V

REFCA

V

DD

SS

DQ32 130 DQ36 199

63 DM3 64 DQS3 131 DQ33 132 DQ37 201 SA1 202 SCL

65

V

SS

66

V

SS

133 V

SS

134

V

SS

67 DQ26 68 DQ30 135 DQS4 136 DM4

69 DQ27 70 DQ31

137

DQS4 138

V

SS

NOTE :

1. NC = No Connect, NU = Not Used, RFU = Reserved Future Use

2. TEST(pin 125) is reserved for bus analysis probes and is NC on normal memory modules.

3. This address might be connected to NC balls of the DRAMs (depending on density); either way they will be connected to the termination resistor.

139 V

141

143

145 V

147

149

151

SS

DQ34 142 DQ39

DQ35 144

SS

DQ40 148 DQ45

DQ41 150

V

SS

V

SS

140 DQ38

V

SS

146 DQ44

V

SS

152 DQS5

156

V

SS

157 DQ42 158 DQ46

V

SS

162

V

SS

163 DQ48 164 DQ52

169

V

SS

DQS6

DQS6

V

SS

168

170

172

174 DQ54

V

SS

DM6

V

SS

175 DQ50 176 DQ55

V

SS

V

SS

180 DQ60

181 DQ56 182 DQ61

V

SS

V

SS

186 DQS7

187 DM7 188 DQS7

V

SS

190

V

SS

193 DQ59 194 DQ63

195

V

SS

196

V

SS

197 SA0 198 NC

203

V

DDSPD

V

TT

200 SDA

204

V

TT

SAMSUNG ELECTRONICS CO., Ltd. reserves the right to change products and specifications without notice.

- 5 -

Page 6

Rev. 1.21

Unbuffered SODIMM datasheet DDR3L SDRAM

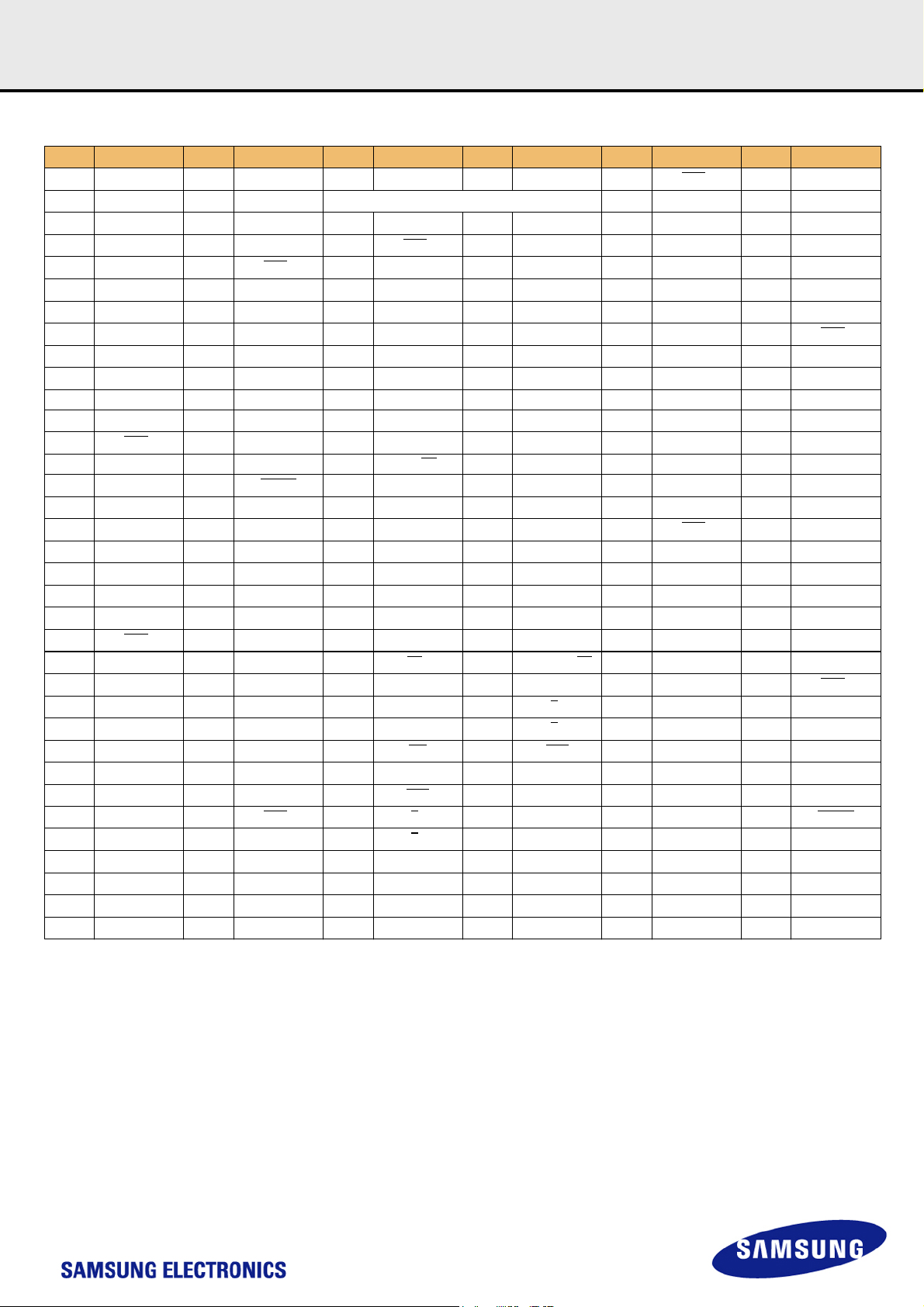

5. x72 DIMM Pin Configurations (Front side/Back Side)

Pin Front Pin Back Pin Front Pin Back Pin Front Pin Back

1

3

V

REFDQ

V

2

SS

4 DQ4 KEY

5 DQ0 6 DQ5 73

7 DQ1 8

9

V

SS

10 DQS0 77 DQS8 78

11 DM0 12 DQS0 79

13 DQ2 14

15 DQ3 16 DQ6 83 CB3 84

17

V

SS

18 DQ7 85

19 DQ8 20

21 DQ9 22 DQ12 89 CKE1 90 A14 159 DQ42 160 DQ46

23

V

SS

24 DQ13 91 BA2 92 A9 161 DQ43 162 DQ47

25 DQS1 26

27 DQS1 28 DM1 95 A12/BC 96 A11 165 DQ48 166 DQ52

29

V

SS

30 RESET 97 A8 98 A7 167 DQ49 168 DQ53

31 DQ10 32

33 DQ11 34 DQ14 101

35

V

SS

36 DQ15 103 A3 104 A4 173

37 DQ16 38

39 DQ17 40 DQ20

41

43

V

SS

42 DQ21

DQS2 44 DM2

45 DQS2 46

47

V

SS

48 DQ22

49 DQ18 50 DQ23

50 DQ19 52

53

V

SS

54 DQ28

55 DQ24 56 DQ29

57 DQ25 58

59 DM3 60 DQS3

61

V

SS

62 DQS3

63 DQ26 64

65 DQ27 66 DQ30

67

V

SS

68 DQ31

69 CB0 70

NOTE :

1. NC = No Connect, NU = Not Usable, RFU = Reserved Future Use

2. TEST(pin 125) is reserved for bus analysis probes and is NC on normal memory modules.

3. This address might be connected to NC balls of the DRAMs (depending on density); either way they will be connected to the termination resistor.

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

71 CB1 72 CB4

V

SS

74 CB5

75 DQS8 76 DM8

V

SS

V

SS

80 CB6

139

141

143

145

147

149

DQS4 140 DM4

DQS4 142 DQ38

V

SS

144 DQ39

DQ34 146

DQ35 148 DQ44

V

SS

150 DQ45

81 CB2 82 CB7 151 DQ40 152

V

REFCA

V

DD

86

V

DD

153 DQ41 154 DQS5

155

V

SS

156 DQS5

87 CKE0 88 A15 157 DM5 158

93

V

DD

94

99 A5 100 A6 169

105

107

109

111

113

115

117

119

121

123

125

127

129

131

133

135

137

V

DD

A1 106 A2 175

A0 108 BA1 177 DQ50 178

V

DD

CK0 112 Par_In, NC,CK1 181

CK0 114 Err_out, NC,CK1 183 DQ56 184

V

DD

A10/AP

BA0 120 S2 189 DM7 190

WE 122 RAS 191 DQ58 192 DQ62

V

DD

CAS 126 ODT0 195

S0 128 ODT1 197 SA0 198 EVENT

S1 130 A13 199

V

DD

DQ32 134 DQ36 203

DQ33 136 DQ37

V

SS

102

110

116

118

124

132

138

V

DD

V

DD

V

DD

V

DD

S3 187

V

DD

V

DD

V

SS

163

171

V

SS

V

SS

DQS6

DQS6

V

SS

164

170

172

174 DQ54

176 DQ55

179 DQ51 180 DQ60

V

SS

182 DQ61

185 DQ57 186 DQS7

V

SS

188 DQS7

193 DQ59 194 DQ63

V

V

DDSPD

SS

196

200 SDA

201 SA1 202 SCL

V

TT

204

V

SS

V

SS

V

SS

V

SS

V

SS

DM6

V

SS

V

SS

V

SS

V

SS

V

TT

SAMSUNG ELECTRONICS CO., Ltd. reserves the right to change products and specifications without notice.

- 6 -

Page 7

Rev. 1.21

Unbuffered SODIMM datasheet DDR3L SDRAM

6. Pin Description

Pin Name Description Number Pin Name Description Number

CK0, CK1 Clock Inputs, positive line 2 DQ0-DQ63 Data Input/Output 64

CK0, CK1 Clock Inputs, negative line 2 DM0-DM7

CKE0, CKE1 Clock Enables 2 DQS0-DQS7 Data strobes 8

RAS Row Address Strobe 1 DQS0-DQS7 Data strobes complement 8

CAS Column Address Strobe 1 RESET Reset Pin 1

WE Write Enable 1 TEST

S0, S1 Chip Selects 2

A0-A9, A11,

A13-A15

Address Inputs 14

A10/AP Address Input/Autoprecharge 1

A12/BC Address Input/Burst chop 1

BA0-BA2 SDRAM Bank Addresses 3

V

V

V

REFDQ

V

REFCA

V

DDSPD

V

DD

SS

TT

ODT0, ODT1 On-die termination control 2 NC Reserved for future use 3

SCL Serial Presence Detect (SPD) Clock Input 1 Total 204

SDA SPD Data Input/Output 1

SA0-SA1 SPD Address 2

NOTE:

*The V

DD

and V

pins are tied common to a single power-plane on these designs.

DDQ

Data Masks/ Data strobes,

Termination data strobes

Logic Analyzer specific test pin (No connect

on SODIMM)

Core and I/O Power 18

Ground 52

Input/Output Reference 2

SPD and Temp sensor Power 1

Termination Voltage 2

8

1

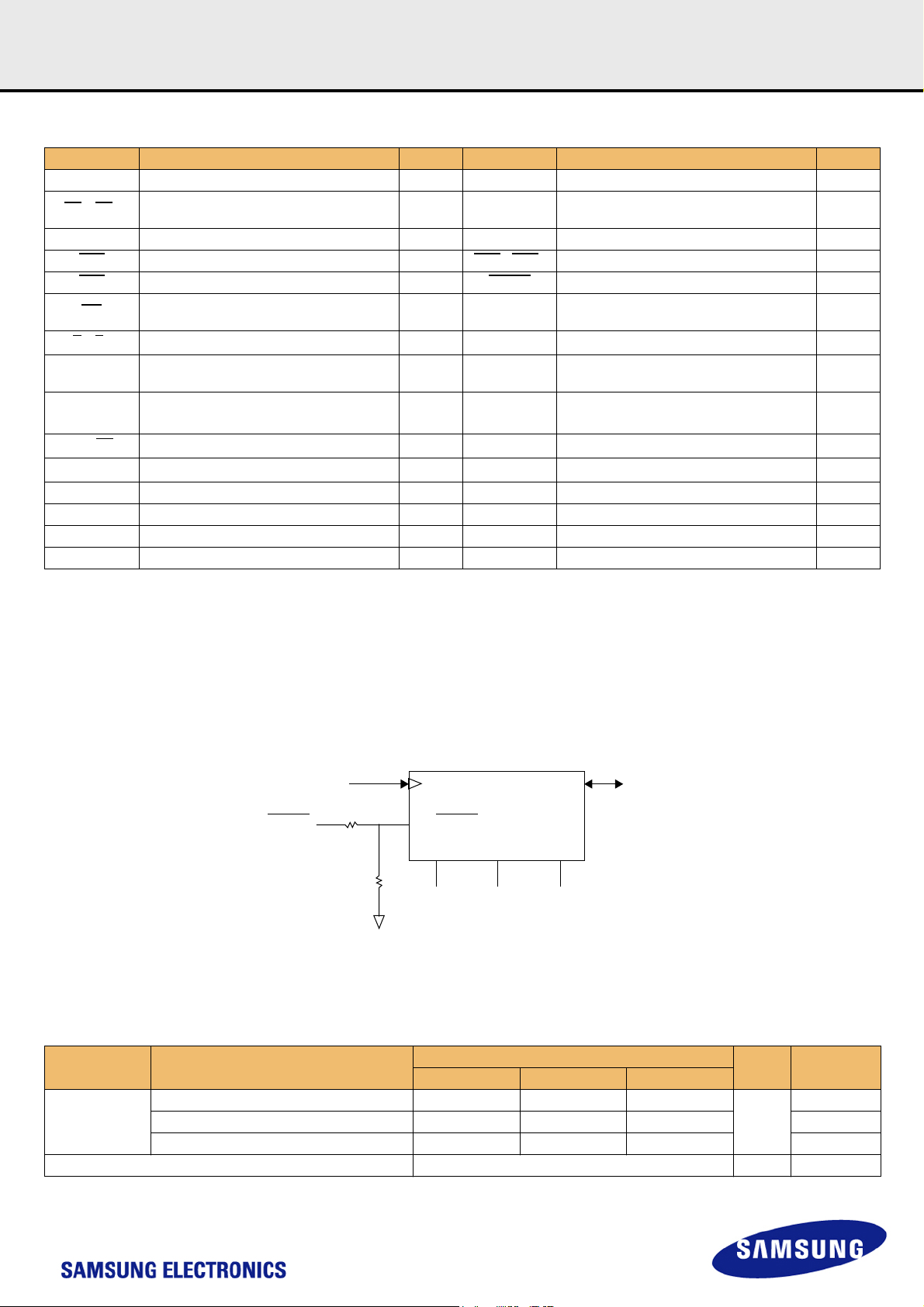

7. SPD and Thermal Sensor for ECC SODIMMs

On DIMM thermal sensor will provide DRAM temperature readout through a integrated thermal sensor.

SCL

EVENT

NOTE :

1. Raw Cards D (1Rx8 ECC) and E (2Rx8 ECC) support a thermal sensor.

2. When the SPD and the thermal sensor are placed on the module, R1 is placed but R2 is not.

When only the SPD is placed on the module, R2 is placed but R1 is not.

[ Table 1 ] Temperature Sensor Characteristics

Grade Range

75 < Ta < 95 - +/- 0.5 +/- 1.0

B

40 < Ta < 125 - +/- 1.0 +/- 2.0 -

-20 < Ta < 125 - +/- 2.0 +/- 3.0 -

Resolution 0.25 C /LSB -

R1

0

WP/EVENT

SA0 SA1 SA2

R2

0

SA0 SA1 SA2

Min. Typ. Max.

Temperature Sensor Accuracy

SDA

Units NOTE

-

C

- 7 -

Page 8

Rev. 1.21

Unbuffered SODIMM datasheet DDR3L SDRAM

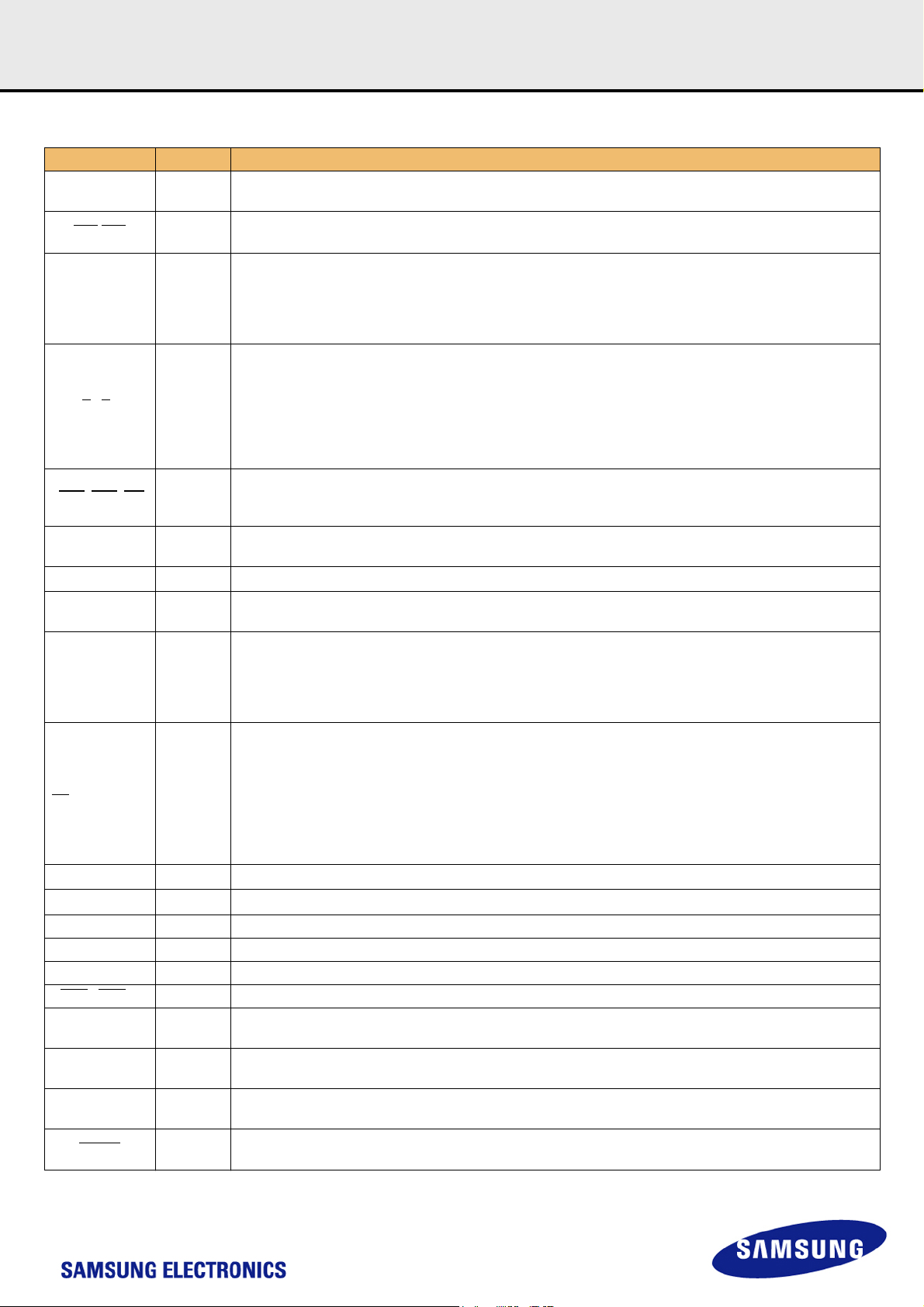

8. Input/Output Functional Description

Symbol Type Function

CK0-CK1 Input

CK0-CK1 Input

CKE0-CKE1 Input

S0-S3 Input

RAS, CAS, WE Input

ODT0-ODT1 Input

REFDQ Supply

V

REFCA Supply

V

BA0-BA2 Input

A[15:13,12/

BC,11,10/AP,9:0]

DQ[63:0], CB[7:0]

DM[8:0]

V

DD, VSS Supply Power and ground for the DDR SDRAM input buffers and core logic.

VTT Supply Termination Voltage for Address/Command/Control/Clock nets.

DQS0-DQS17 I/O Positive line of the differential data strobe for input and output data.

DQS0-DQS17 I/O Negative line of the differential data strobe for input and output data.

SA0-SA1 Input

SDA I/O

SCL Input

EVENT

Input

I/O Data and Check Bit Input/Output pins.

Input Masks write data when high, issued concurrently with input data.

OUT

(open drain)

Positive line of the differential pair of system clock inputs that drives input to the on-DIMM Clock

Driver (72b-SO-RDIMM), on-DIMM PLL (72b-SO-CDIMM), or to DRAMs on rank 0 (72b-SO-DIMM).

Negative line of the differential pair of system clock inputs that drives input to the on-DIMM Clock

Driver (72b-SO-RDIMM), on-DIMM PLL (72b-SO-CDIMM), or to DRAMs on rank 0 (72b-SO-DIMM).

CKE HIGH activates, and CKE LOW deactivates internal clock signals, and device input buffers and

output drivers of the SDRAMs. Taking CKE LOW provides PRECHARGE POWER-DOWN and

SELF REFRESH operation (all banks idle), or ACTIVE POWER DOWN (row ACTIVE in any bank).

Connected to the registering clock driver on 72b-SO-RDIMMs, connected to DRAMs on 72b-SOCDIMMs

and 72b-SO-DIMMs.

Enables the command decoders for the associated rank of SDRAM when low and disables decoders

when high. When decoders are disabled, new commands are ignored and previous operations

continue. Connected to SDRAMs on 72b-SO-CDIMMs and 72b-SO-DIMMs. For 72b-SO-RDIMMs,

other combinations of these input signals perform unique functions, including disabling all outputs

(except CKE and ODT) of the register(s) on the DIMM or accessing internal control words in the register

device(s). For modules with two registers, S[3:2] operate similarly to S[1:0] for the second set of

register outputs or register control words

When sampled at the positive rising edge of the clock, CAS_n, RAS_n, and WE_n define the operation

to be executed by the SDRAM. Connected to SDRAMs on 72b-SO-CDIMMs and 72b-SODIMMs,

connected to the registering clock driver on 72b-SO-RDIMMs.

On-Die Termination control signals. Connected to SDRAMs on 72b-SO-CDIMMs and 72b-SODIMMs,

connected to the registering clock driver on 72b-SO-RDIMMs.

Reference voltage for DQ0-DQ63 and CB0-CB7.

Reference voltage for A0-A15, BA0-BA2, RAS_n, CAS_n, WE_n, S0_n, S1_n, CKE0, CKE1,

Par_In, ODT0 and ODT1.

Selects which SDRAM bank of eight is activated.

BA0 - BA2 define to which bank an Active, Read, Write or Precharge command is being applied.

Bank address also determines mode register is to be accessed during an MRS cycle. Connected to

SDRAMs on 72b-SO-CDIMMs and 72b-SO-DIMMs, connected to the registering clock driver on

72b-SO-RDIMMs.

Provided the row address for Active commands and the column address and Auto Precharge bit for

Read/Write commands to select one location out of the memory array in the respective bank. A10 is

sampled during a Precharge command to determine whether the Precharge applies to one bank

(A10 LOW) or all banks (A10 HIGH). If only one bank is to be precharged, the bank is selected by

BA. A12 is also utilized for BL 4/8 identification for ‘’BL on the fly’’ during CAS command. The

address inputs also provide the op-code during Mode Register Set commands. Connected to

SDRAMs on 72b-SO-CDIMMs and 72b-SO-DIMMs, connected to the registering clock driver on

72b-SO-RDIMMs.

These signals are tied at the system planar to either VSS or VDDSPD to configure the serial SPD

EEPROM address range.

This bidirectional pin is used to transfer data into or out of the SPD EEPROM. A resistor must be

connected from the SDA bus line to V

This signal is used to clock data into and out of the SPD EEPROM. A resistor may be connected

from the SCL bus time to V

This signal indicates that a thermal event has been detected in the thermal sensing device.The system

should guarantee the electrical level requirement is met for the EVENT_n pin on TS/SPD part.

DDSPD on the system planar to act as a pullup.

DDSPD on the system planar to act as a pullup.

- 8 -

Page 9

Rev. 1.21

Unbuffered SODIMM datasheet DDR3L SDRAM

Symbol Type Function

V

DDSPD Supply

RESET Input

Par_In Input

Err_Out

OUT

(open drain)

Serial EEPROM positive power supply wired to a separate power pin at the connector which supports

from 3.0 Volt to 3.6 Volt (nominal 3.3V) operation.

The RESET_n pin is connected to the RESET_n pin on the register (72b-SO-RDIMM) and to the

RESET_n pin on the SDRAMs (all modules). When low, all register outputs will be driven low and

the Clock Driver clocks to the DRAMs and register(s) will be set to low level (the Clock Driver will

remain synchronized with the input clock).

Parity bit for the Address and Control bus. (“1 “: Odd, “0 “: Even). Not used on 72b-SO-DIMMs or

72b-SO-CDIMMs.

Parity error detected on the Address and Control bus. A resistor may be connected from Err_Out_n

bus line to VDD on the system planar to act as a pull up. Not used on 72b-SO-DIMMs or 72b-SOCDIMMs.

- 9 -

Page 10

Rev. 1.21

Unbuffered SODIMM datasheet DDR3L SDRAM

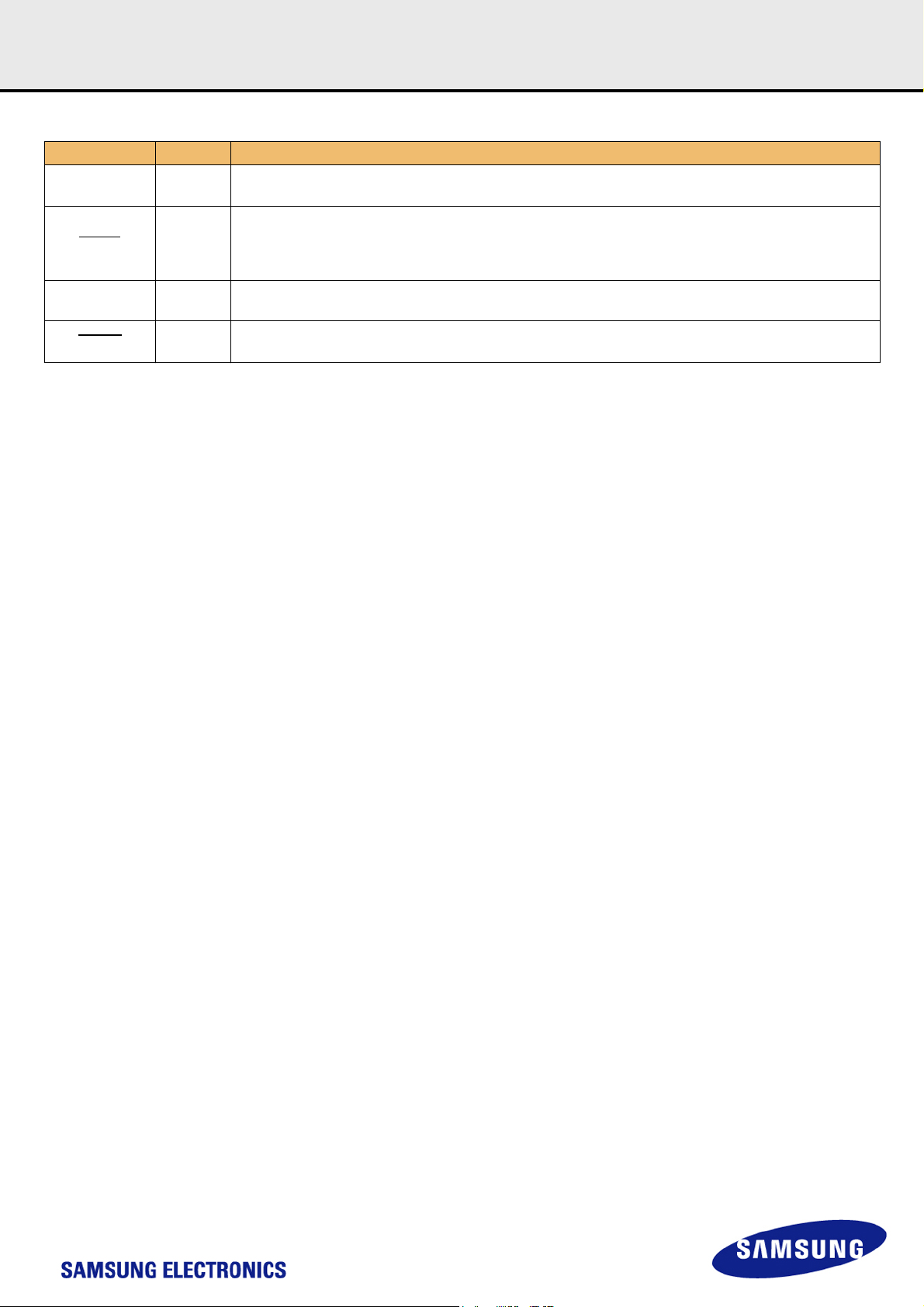

9. Function Block Diagram:

9.1 2GB, 256Mx64 Module (Populated as 1 rank of x16 DDR3 SDRAMs)

S0

RAS

CASWECK0

CK0

CKE0

ODT0

/BA[0:N]

DQS0

DQS0

DM0

DQ[0:7]

DQS1

DQS1

DM1

DQ[8:15]

DQS2

DQS2

DM2

DQ[16:23]

DQS3

DQS3

DM3

DQ[24:31]

DQS4

DQS4

DM4

DQ[32:39]

DQS5

DQS5

DM5

DQ[40:47]

LDQS

LDQS

LDM

DQ[0:7]

UDQS

UDQS

UDM

DQ[8:15]

CS

RAS

LDQS

LDQS

LDM

DQ[0:7]

UDQS

UDQS

UDM

DQ[8:15]

CS

RAS

LDQS

LDQS

LDM

DQ[0:7]

UDQS

UDQS

UDM

DQ[8:15]

240

1%

ZQ

D0

CASWECKCKCKE

240

1%

ZQ

D1

CASWECKCKCKE

240

1%

ZQ

D2

A[0:N]

ODT

A[N:0]/BA[N:0]

ODT

A[N:0]/BA[N:0]

V

V

DDSPD

V

REFCA

V

REFDQ

V

DD

V

SS

CK0

CK0 D0 - D3

CK1

CK1

ODT1

S1

CKE1

RESET D0 - D3

tt

SCL

SA0

SA1

SCL

A0

A1

A2

(SPD)

WP

SDA

V

tt

SPD

D0 - D3

D0 - D3

D0 - D3

D0 - D3, SPD

D0 - D3

Terminated near

card edge

NC

NC

NC

DQS6

DQS6

DM6

DQ[48:55]

DQS7

DQS7

DM7

DQ[56:63]

CS

RAS

LDQS

LDQS

LDM

DQ[0:7]

UDQS

UDQS

UDM

DQ[8:15]

CS

RAS

CS

RAS

CASWECKCKCKE

CASWECKCKCKE

CASWECKCKCKE

D3

240

1%

ZQ

ODT

A[N:0]/BA[N:0]

ODT

A[N:0]/BA[N:0]

ODT

A[N:0]/BA[N:0]

D1 D2D0

Address and Controllines

D3

tt

V

Note :

1. DQ wiring may differ from that shown

however ,DQ, DM, DQS and DQS

relationships are maintained as shown

Vtt

V

DD

Vtt

Rank0

- 10 -

Page 11

Rev. 1.21

Unbuffered SODIMM datasheet DDR3L SDRAM

9.2 4GB, 512Mx64 Module (Populated as 1 rank of x8 DDR3 SDRAMs)

S0

RAS

CASWECK0

CK0

CKE0

ODT0

A[0:N]

DQS0

DQS0

DM0

DQ[0:7]

DQS2

DQS2

DM2

DQ[16:23]

DQS

DQS

DM

DQ[0:7]

CS

RAS

DQS

DQS

DM

DQ[0:7]

CS

RAS

240

1%

ZQ

D0

CASWECKCKCKE

240

1%

ZQ

D1

CASWECKCKCKE

/BA[0:N]

ODT

A[0:N]/BA[0:N]

ODT

A[0:N]/BA[0:N]

DQS1

DQS1

DM1

DQ[8:15]

DQS3

DQS3

DM3

DQ[24:31]

DQS

DQS

DM

DQ[0:7]

CS

RAS

DQS

DQS

DM

DQ[0:7]

CS

RAS

240

1%

ZQ

D4

CASWECKCKCKE

240

1%

ZQ

D5

CASWECKCKCKE

ODT

A[0:N]/BA[0:N]

ODT

A[0:N]/BA[0:N]

V

DDSPD

V

REFCA

V

REFDQ

ODT1

CKE1

RESET

V

V

CK0

CK0

CK1

CK1

SCL

SA0

SA1

V

DD

SS

S1

SCL

A0

(SPD)

A1

A2

WP

tt

SDA

V

tt

SPD

D0 - D7

D0 - D7

D0 - D7

D0 - D7, SPD

D0 - D7

D0 - D7

Terminated near

card edge

NC

NC

NC

D0 - D7

DQS4

DQS4

DM4

DQ[32:39]

DQS6

DQS6

DM6

DQ[48:55]

DQS

DQS

DM

DQ[0:7]

CS

RAS

DQS

DQS

DM

DQ[0:7]

240

1%

ZQ

D2

CASWECKCKCKE

240

1%

ZQ

D3

ODT

A[0:N]/BA[0:N]

DQS5

DQS5

DM5

DQ[40:47]

DQS7

DQS7

DM7

DQ[56:63]

DQS

DQS

DM

DQ[0:7]

CS

RAS

DQS

DQS

DM

DQ[0:7]

240

1%

ZQ

D6

CASWECKCKCKE

240

1%

ZQ

D7

ODT

A[0:N]/BA[0:N]

V

tt

D7D6D5D4

V4V3V2V1

V4V3V2V1

D3D2D1D0

tt

V

Address and Controllines

NOTE :

CS

RAS

CASWECKCKCKE

Vtt

V

DD

ODT

A[0:N]/BA[0:N]

CS

RAS

CASWECKCKCKE

Vtt

ODT

A[0:N]/BA[0:N]

Rank0

1. DQ wiring may differ from that shown however ,DQ, DM, DQS and

are maintained as shown

DQS relationships

- 11 -

Page 12

Rev. 1.21

Unbuffered SODIMM datasheet DDR3L SDRAM

9.3 8GB, 1Gx64 Module (Populated as 2 ranks of x8 DDR3 SDRAMs)

DQS3

DQS3

DM3

DQ[24:31]

DQS1

DQS1

DM1

DQ[8:15]

DQS0

DQS0

DM0

DQ[0:7]

S1

RAS

DQS

DQS

DM

DQ[0:7]

CS

RAS

DQS

DQS

DM

DQ[0:7]

CS

RAS

DQS

DQS

DM

DQ[0:7]

CASWECK1

CK1

CKE1

240

1%

ZQ

D11

CASWECKCKCKE

240

1%

ZQ

D1

CASWECKCKCKE

240

1%

ZQ

D0

ODT1

A[0:N]

/BA[0:N]

ODT

A[N:0]/BA[N:0]

ODT

A[N:0]/BA[N:0]

S0

DQS

DQS

DM

DQ[0:7]

CS

RAS

DQS

DQS

DM

DQ[0:7]

CS

RAS

DQS

DQS

DM

DQ[0:7]

CK0

CK0

CKE0

240

1%

ZQ

D3

CASWECKCKCKE

240

1%

ZQ

D9

CASWECKCKCKE

240

1%

ZQ

D8

ODT0

ODT

A[N:0]/BA[N:0]

ODT

A[N:0]/BA[N:0]

Rank0

Rank1

DQS

DQS

DM

DQ[0:7]

CS

RAS

DQS

DQS

DM

DQ[0:7]

CS

RAS

DQS

DQS

DM

DQ[0:7]

V

DD

240

1%

ZQ

D12

CASWECKCKCKE

240

1%

ZQ

D6

CASWECKCKCKE

240

1%

ZQ

D7

ODT

A[N:0]/BA[N:0]

ODT

A[N:0]/BA[N:0]

Vtt

DQS4

DQS4

DM4

DQ[32:39]

DQS6

DQS6

DM6

DQ[48:55]

DQS7

DQS7

DM7

DQ[56:63]

V

DD

Vtt

Vtt

240

DQS

DQS

DM

DQ[0:7]

DQS

DQS

DM

DQ[0:7]

DQS

DQS

DM

DQ[0:7]

CS

RAS

CASWECKCKCKE

CS

RAS

CASWECKCKCKE

D4

D14

D15

1%

ZQ

240

1%

ZQ

240

1%

ZQ

ODT

ODT

A[N:0]/BA[N:0]

A[N:0]/BA[N:0]

DQS2

DQS2

DM2

DQ[16:23]

SCL

SA0

SA1

SCL

A0

A1

A2

CS

RAS

DQS

DQS

DM

DQ[0:7]

CS

RAS

CASWECKCKCKE

240

1%

ZQ

D2

CASWECKCKCKE

(SPD)

WP

ODT

A[N:0]/BA[N:0]

ODT

A[N:0]/BA[N:0]

SDA

CS

RAS

DQS

DQS

DM

DQ[0:7]

CS

RAS

CASWECKCKCKE

240

1%

ZQ

D10

CASWECKCKCKE

V

tt

V

DDSPD

V

REFCA

V

REFDQ

V

DD

V

SS

CK0

CK1

CK0

CK1

RESET

ODT

A[N:0]/BA[N:0]

ODT

A[N:0]/BA[N:0]

CS

RAS

CASWECKCKCKE

DQS

DQS

DM

DQ[0:7]

D13

CS

RAS

CASWECKCKCKE

V

tt

SPD

D0 - D15

D0 - D15

D0 - D15

D0 - D15, SPD

D0 - D7

D8 - D15

D0 - D7

D8 - D15

D0 - D7

240

1%

ODT

A[N:0]/BA[N:0]

CS

RAS

ZQ

ODT

A[N:0]/BA[N:0]

DQS

DQS

DM

DQ[0:7]

CS

RAS

V3

V3

CASWECKCKCKE

CASWECKCKCKE

V2

V4

V4

V2

D5

240

1%

ZQ

ODT

A[N:0]/BA[N:0]

ODT

A[N:0]/BA[N:0]

V1

V9

V5

V1

V5

V

tt

V1

V9

NOTE :

1. DQ wiring may differ from that shown however ,DQ, DM, DQS and

are maintained as shown

DQS5

DQS5

DM5

DQ[40:47]

V8

D6D12D3D9

V7

D7D5D10D8

V6

V6

D15D13D2D0

V7

D14D4D11D1

V8

Address and Controllines

DQS relationships

- 12 -

Page 13

Rev. 1.21

Unbuffered SODIMM datasheet DDR3L SDRAM

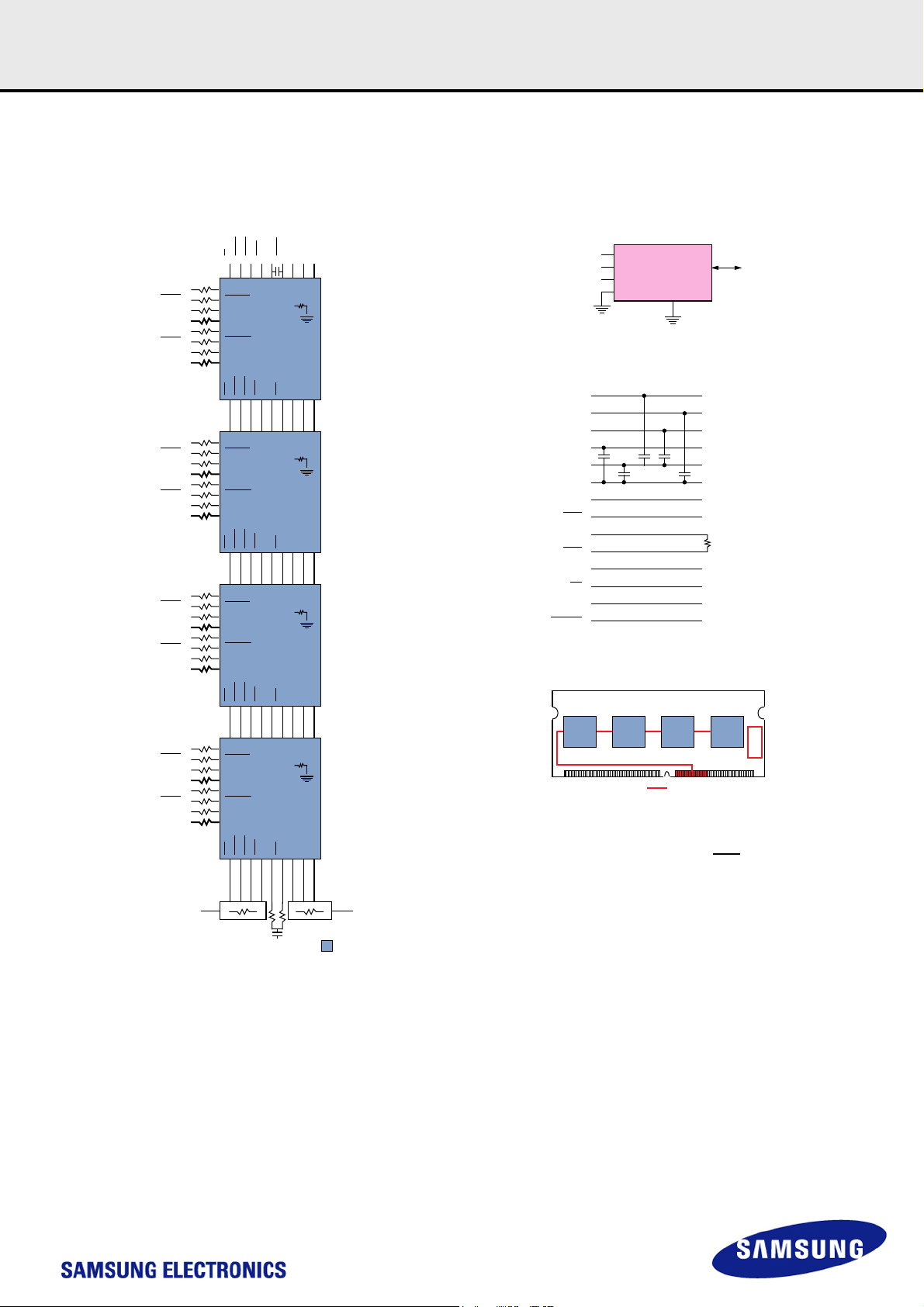

9.4 4GB, 512Mx72 Module (Populated as 1 rank of x8 DDR3 SDRAMs)

S0

RAS

CASWECK0

CK0

CKE0

ODT0

A[0:N]

DQS0

DQS0

DM0

DQ[0:7]

DQS2

DQS2

DM2

DQ[16:23]

DQS4

DQS4

DM4

CB[0:7]

DQS

DQS

DM

DQ

DQS

DQS

DM

DQ

DQS

DQS

DM

DQ

CS

CS

RAS

RAS

240

1%

ZQ

D0

CASWECKCKCKE

240

1%

ZQ

D1

CASWECKCKCKE

240

1%

ZQ

D8

/BA[0:N]

ODT

A[0:N]/BA[0:N]

ODT

A[0:N]/BA[0:N]

DQS1

DQS1

DM1

DQ[8:15]

DQS3

DQS3

DM3

DQ[24:31]

DQS

DQS

DM

DQ

CS

DQS

DQS

DM

DQ

CS

RAS

RAS

240

1%

ZQ

D4

CASWECKCKCKE

240

1%

ZQ

D5

CASWECKCKCKE

ODT

A[0:N]/BA[0:N]

ODT

A[0:N]/BA[0:N]

V

DDSPD

V

REFCA

V

REFDQ

ODT1

CKE1

ENEVT

RESET

V

V

CK0

CK0

CK1

CK1

SCL

SA0

SA1

V

DD

SS

S1

SCL

A0

(SPD)

A1

A2

WP

tt

SDA

V

tt

SPD

D0 - D8

D0 - D8

D0 - D8

D0 - D8

D0 - D8

D0 - D8

Terminated near

card edge

NC

NC

NC

Temp Sensor

D0 - D8

DQS4

DQS4

DM4

DQ[32:39]

DQS6

DQS6

DM6

DQ[48:55]

V

tt

D7D6D5D4

V4V3V2V1

V4V3V2V1

D3D2D1D0

tt

V

Address and Controllines

DQS

DQS

DM

DQ

CS

CS

RAS

RAS

CASWECKCKCKE

240

1%

ZQ

D2

CASWECKCKCKE

ODT

A[0:N]/BA[0:N]

ODT

A[0:N]/BA[0:N]

DQS5

DQS5

DM5

DQ[40:47]

DQS

DQS

DM

DQ

CS

RAS

240

1%

ZQ

D6

CASWECKCKCKE

ODT

A[0:N]/BA[0:N]

D8

NOTE :

1. DQ wiring may differ from that shown however ,DQ, DM, DQS and

240

DQS

DQS

DM

DQ

Vtt

D3

CS

RAS

CASWECKCKCKE

1%

ZQ

V

DD

ODT

A[0:N]/BA[0:N]

DQS7

DQS7

DM7

DQ[56:63]

Vtt

DQS

DQS

DM

DQ

CS

240

1%

ZQ

D7

RAS

CASWECKCKCKE

ODT

A[0:N]/BA[0:N]

Rank0

are maintained as shown

DQS relationships

- 13 -

Page 14

Rev. 1.21

Unbuffered SODIMM datasheet DDR3L SDRAM

9.5 8GB, 1Gx72 Module (Populated as 2 ranks of x8 DDR3 SDRAMs)

DQS0

DQS0

DM0

DQ[0:7]

DQS2

DQS2

DM2

DQ[16:15]

DQS4

DQS4

DM4

DQ[32:39]

DQS

DQS

DM

DQ

DQS

DQS

DM

DQ

DQS

DQS

DM

DQ

S1

CS

CS

CS

RAS

CASWECK1

240

ZQ

D1

RAS

CASWECKCKCKE

240

ZQ

D2

RAS

CASWECKCKCKE

240

ZQ

D3

RAS

CASWECKCKCKE

CK1

1%

1%

1%

CKE1

ODT1

A[0:N]

/BA[0:N]

ODT

A[N:0]/BA[N:0]

ODT

A[N:0]/BA[N:0]

ODT

A[N:0]/BA[N:0]

DQS

DQS

DM

DQ

DQS

DQS

DM

DQ

DQS

DQS

DM

DQ

S0

CS

CS

CS

RAS

RAS

RAS

CK0

CK0

CKE0

240

1%

ZQ

D10

CASWECKCKCKE

240

1%

ZQ

D11

CASWECKCKCKE

240

1%

ZQ

D12

CASWECKCKCKE

ODT0

ODT

A[N:0]/BA[N:0]

ODT

A[N:0]/BA[N:0]

ODT

A[N:0]/BA[N:0]

Rank0

Rank1

V

DD

Vtt

Vtt

240

DQS

DQS

DM

DQ

DQS

DQS

DM

DQ

DQS

DQS

DM

DQ

CS

CS

CS

D5

RAS

CASWECKCKCKE

240

D6

RAS

CASWECKCKCKE

240

D7

RAS

CASWECKCKCKE

1%

ZQ

1%

ZQ

1%

ZQ

ODT

A[N:0]/BA[N:0]

ODT

A[N:0]/BA[N:0]

ODT

A[N:0]/BA[N:0]

DQS

DQS

DM

DQ

DQS

DQS

DM

DQ

DQS

DQS

DM

DQ

C

term

D14

CS

RAS

CASWECKCKCKE

D15

CS

RAS

CASWECKCKCKE

D16

CS

RAS

CASWECKCKCKE

V

240

240

240

DD

ZQ

ZQ

ZQ

1%

ODT

1%

ODT

1%

ODT

Vtt

DQS1

DQS1

DM1

DQ[8:15]

A[N:0]/BA[N:0]

DQS3

DQS3

DM3

DQ[24:31]

A[N:0]/BA[N:0]

DQS5

DQS5

DM5

DQ[40:47]

A[N:0]/BA[N:0]

DQS6

DQS6

DM6

DQ[48:55]

DQS8

DQS8

CB[0:7]

SCL

SA0

SA1

DM8

SCL

A0

A1

A2

DQS

DQS

DM

DQ

DQS

DQS

DM

DQ

CS

CS

ZQ

D4

RAS

CASWECKCKCKE

240

ZQ

D9

RAS

CASWECKCKCKE

(SPD)

WP

1%

1%

ODT

A[N:0]/BA[N:0]

ODT

A[N:0]/BA[N:0]

SDA

DQS

DQS

DM

DQ

DQS

DQS

DM

DQ

CS

CS

RAS

RAS

240

1%

ZQ

D13

CASWECKCKCKE

240

1%

ZQ

D18

CASWECKCKCKE

V

tt

V

DDSPD

V

REFCA

V

REFDQ

V

DD

V

SS

ODT

A[N:0]/BA[N:0]

ODT

A[N:0]/BA[N:0]

240

CK0

CK1

CK0

CK1

RESET

NOTE :

1. DQ wiring may differ from that shown however ,DQ, DM, DQS and

240

D8

RAS

CASWECKCKCKE

1%

ZQ

ODT

A[N:0]/BA[N:0]

V2

V3

V

tt

SPD

DQS

DQS

DM

DQ

CS

D0 - D15

D0 - D15

D0 - D15

D0 - D15, SPD

D0 - D7

D8 - D15

D0 - D7

V4

V4

V3

D7

V2

D8 - D15

D0 - D7

DQS relationships are maintained as shown

DQS

DQS

DM

DQ

CS

RAS

D14D16

D6D17

D5

240

1%

ZQ

D17

CASWECKCKCKE

V1

D10

V1

D18

V

tt

V1

DQS7

DQS7

DM7

DQ[56:63]

ODT

A[N:0]/BA[N:0]

V8

V9

V5

V5

D2D4

V7

D1D3

V6

V6

D10D12D15D8

V7

D11D13

V9

V8

Address and Controllines

- 14 -

Page 15

Rev. 1.21

Unbuffered SODIMM datasheet DDR3L SDRAM

10. Absolute Maximum Ratings

10.1 Absolute Maximum DC Ratings

Symbol Parameter Rating Units NOTE

V

DD

V

Voltage on V

DDQ

V

NOTE :

1. Stresses greater than those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions

for extended periods may affect reliability.

2. Storage Temperature is the case surface temperature on the center/top side of the DRAM. For the measurement conditions, please refer to JESD51-2 standard.

3. VDD and V

equal to or less than 300mV.

Voltage on any pin relative to V

IN, VOUT

T

Storage Temperature -55 to +100 C 1, 2

STG

DDQ

10.2 DRAM Component Operating Temperature Range

Symbol Parameter rating Unit NOTE

T

OPER

NOTE :

1. Operating Temperature T

JESD51-2.

2. The Normal Temperature Range specifies the temperatures where all DRAM specifications will be supported. During operation, the DRAM case temperature must be maintained between 0-85C under all operating conditions

3. Some applications require operation of the Extended Temperature Range between 85C and 95C case temperature. Full specifications are guaranteed in this range, but the

following additional conditions apply:

a) Refresh commands must be doubled in frequency, therefore reducing the refresh interval tREFI to 3.9us.

b) If Self-Refresh operation is required in the Extended Temperature Range, then it is mandatory to either use the Manual Self-Refresh mode with Extended Temperature

Range capability (MR2 A6 = 0b and MR2 A7 = 1b), in this case IDD6 current can be increased around 10~20% than normal Temperature range.

Voltage on VDD pin relative to V

pin relative to V

DDQ

must be within 300mV of each other at all times;and V

SS

SS

SS

Operating Temperature Range 0 to 95 C 1, 2, 3

is the case surface temperature on the center/top side of the DRAM. For measurement conditions, please refer to the JEDEC document

OPER

-0.4 V ~ 1.975 V V 1,3

-0.4 V ~ 1.975 V V 1,3

-0.4 V ~ 1.975 V V 1

must be not greater than 0.6 x V

REF

, When VDD and V

DDQ

are less than 500mV; V

DDQ

REF

may be

11. AC & DC Operating Conditions

11.1 Recommended DC Operating Conditions

Symbol Parameter Operation Voltage

V

DD

V

DDQ

NOTE:

1. Under all conditions V

tracks with VDD. AC parameters are measured with VDD and V

2. V

DDQ

3. VDD & V

DDQ

Supply Voltage

Supply Voltage for Output

must be less than or equal to VDD.

DDQ

rating are determinied by operation voltage.

1.35V 1.283 1.35 1.45 V 1, 2, 3

1.5V 1.425 1.5 1.575 V 1, 2, 3

1.35V 1.283 1.35 1.45 V 1, 2, 3

1.5V 1.425 1.5 1.575 V 1, 2, 3

tied together.

DDQ

Rating

Min. Typ. Max.

Units NOTE

- 15 -

Page 16

Rev. 1.21

Unbuffered SODIMM datasheet DDR3L SDRAM

12. AC & DC Input Measurement Levels

12.1 AC & DC Logic Input Levels for Single-ended Signals

[ Table 2 ] Single Ended AC and DC input levels for Command and Address(1.35V)

Symbol Parameter

1.35V

V

(DC90)

IH.CA

V

(DC90)

IL.CA

V

(AC160)

IH.CA

(AC160)

V

IL.CA

V

(AC135)

IH.CA

V

(AC135)

IL.CA

V

(DC)

REFCA

NOTE :

1. For input only pins except

2. See "Overshoot and Undershoot specifications" on Component Datasheet.

3. The ac peak noise on VRef may not allow VRef to deviate from VRefDQ(DC) by more than +/-1% VDD (for reference: approx. +/- 13.5 mV).

4. For reference: approx. VDD/2 +/- 13.5 mV

5. These levels apply for 1.35 Volt operation only. If the device is operated at 1.5 V , the respective levels in JESD79-3 (VIH/L.CA(DC100), VIH/L.CA(AC175), VIHL.CA(AC150),

VIH/L.CA(AC135), VIH/L.CA(AC125)etc.) apply. The 1.5 V levels (VIH/L.CA(DC100), VIH/L.CA(AC175), VIH/L.CA(AC150), VIH/L.CA(AC135), VIHL.CA(AC125)etc.) do not

apply when the device is operated in the 1.35 voltage range.

DC input logic high

DC input logic low

AC input logic high

AC input logic low Note 2

AC input logic high

AC input logic lowM Note 2

Reference Voltage for ADD, CMD inputs

RESET, V

REF

= V

REFCA

(DC)

DDR3L-800/1066/1333/1600

Min. Max.

V

+ 90 V

REF

V

SS

V

+ 160

REF

V

+135

REF

0.49*V

DD

Unit NOTE

DD

V

- 90

REF

mV 1

mV 1

Note 2 mV 1,2,5

V

REF

- 160

mV 1,2,5

Note 2 mV 1,2,5

V

REF

0.51*V

-135

DD

mV 1,2,5

V 3,4

[ Table 3 ] Single-ended AC & DC input levels for Command and Address(1.5V)

Symbol Parameter

DDR3-800/1066/1333/1600

Min. Max.

Unit NOTE

1.5V

V

(DC100)

IH.CA

V

(DC100)

IL.CA

V

(AC175)

IH.CA

V

(AC175)

IL.CA

(AC150)

V

IH.CA

V

(AC150)

IL.CA

V

(DC)

REFCA

NOTE :

1. For input only pins except

2. See "Overshoot and Undershoot specifications" on Component Datasheet.

3. The ac peak noise on VRef may not allow VRef to deviate from VRefCA(DC) by more than +/-1% VDD (for reference: approx. +/- 15 mV).

4. For reference: approx. VDD/2 +/- 15 mV.

5. VIH(dc) is used as a simplified symbol for VIH.CA(DC100)

6. VIL(dc) is used as a simplified symbol for VIL.CA(DC100)

7. VIH(ac) is used as a simplified symbol for VIH.CA(AC175), VIH.CA(AC150), VIH.CA(AC135), and VIH.CA(AC125); VIH.CA(AC175) value is used when Vref + 0.175V is

referenced, VIH.CA(AC150) value is used when Vref + 0.150V is referenced, VIH.CA(AC135) value is used when Vref + 0.135V is referenced, and VIH.CA(AC125) value is

used when Vref + 0.125V is referenced.

8. VIL(ac) is used as a simplified symbol for VIL.CA(AC175), VIL.CA(AC150), VIL.CA(AC135) and VIL.CA(AC125); VIL.CA(AC175) value is used when Vref - 0.175V is

referenced, VIL.CA(AC150) value is used when Vref - 0.150V is referenced, VIL.CA(AC135) value is used when Vref - 0.135V is referenced, and VIL.CA(AC125) value is

used when Vref - 0.125V is referenced.

9. VrefCA(DC) is measured relative to VDD at the same point in time on the same device

DC input logic high

DC input logic low

AC input logic high

AC input logic low Note 2

AC input logic high

AC input logic low Note 2

Reference Voltage for ADD, CMD inputs

RESET, V

REF

= V

REFCA

(DC)

V

+ 100 V

REF

V

SS

V

+ 175

REF

V

+150

REF

0.49*V

DD

DD

V

- 100

REF

mV 1,5

mV 1,6

Note 2 mV 1,2,7

V

REF

- 175

mV 1,2,8

Note 2 mV 1,2,7

V

REF

0.51*V

-150

DD

mV 1,2,8

V 3,4,9

- 16 -

Page 17

Rev. 1.21

Unbuffered SODIMM datasheet DDR3L SDRAM

[ Table 4 ] Single Ended AC and DC input levels for DQ and DM(1.35V)

Symbol Parameter

V

(DC90)

IH.DQ

V

(DC90)

IL.DQ

(AC160)

V

IH.DQ

V

(AC160)

IL.DQ

V

(AC135)

IH.DQ

V

(AC135)

IL.DQ

(DC)

V

REF

DQ

NOTE :

1. For input only pins except

2. See "Overshoot and Undershoot specifications" on Component Datasheet.

3. The ac peak noise on VRef may not allow VRef to deviate from VRefDQ(DC) by more than +/-1% VDD (for reference: approx. +/- 13.5 mV).

4. For reference: approx. VDD/2 +/- 13.5 mV.

5. These levels apply for 1.35 Volt operation only. If the device is operated at 1.5 V, the respective levels in JESD79-3 ( VIH/L.DQ(DC100), VIH/L.DQ(AC175), VIH/

L.DQ(AC150), VIH/L.DQ(AC135), etc. ) apply. The 1.5 V levels (VIH/L.DQ(DC100), VIH/L.DQ(AC175), VIH/L.DQ(AC150), VIH/L.DQ(AC135), etc. ) do not apply when the

device is operated in the 1.35 voltage range.

DC input logic high

DC input logic low

AC input logic high

AC input logic low Note 2

AC input logic high

AC input logic low Note 2

Reference Voltage for DQ, DM

inputs

RESET, V

REF

= V

REFDQ

(DC)

DDR3L-800/1066 DDR3L-1333/1600

Min. Max. Min. Max.

1.35V

V

+ 90 V

REF

V

SS

V

+ 160

REF

V

+ 135

REF

0.49*V

DD

DD

V

- 90 V

REF

Note 2 - - mV 1,2,5

V

- 160

REF

Note 2

V

- 135

REF

0.51*V

DD

V

+ 90 V

REF

SS

- - mV 1,2,5

V

+ 135

REF

Note 2

0.49*V

DD

Unit NOTE

mV 1

mV 1

V

REF

DD

- 90

Note 2 mV 1,2,5

V

- 135

REF

0.51*V

DD

mV 1,2,5

V 3,4

[ Table 5 ] Single-ended AC & DC input levels for DQ and DM (1.5V)

Symbol Parameter

DDR3-800/1066 DDR3-1333/1600

Min. Max. Min. Max.

Unit NOTE

1.5V

V

(DC100)

IH.DQ

(DC100)

V

IL.DQ

(AC175)

V

IH.DQ

V

(AC175)

IL.DQ

V

(AC150)

IH.DQ

(AC150)

V

IL.DQ

V

(AC135)

IH.DQ

V

(AC135)

IL.DQ

V

(DC)

REF

DQ

NOTE :

1. For input only pins except

2. See "Overshoot and Undershoot specifications" on Component Datasheet.

3. The ac peak noise on VRef may not allow VRef to deviate from VRefDQ(DC) by more than +/-1% VDD (for reference: approx. +/- 15 mV).

4. For reference: approx. VDD/2 +/- 15 mV.

5. VIH(dc) is used as a simplified symbol for VIH.DQ(DC100)

6. VIL(dc) is used as a simplified symbol for VIL.DQ(DC100)

7. VIH(ac) is used as a simplified symbol for VIH.DQ(AC175), VIH.DQ(AC150), and VIH.DQ(AC135); VIH.DQ(AC175) value is used when Vref + 0.175V is referenced,

VIH.DQ(AC150) value is used when Vref + 0.150V is referenced, and VIH.DQ(AC135) value is used when Vref + 0.135V is referenced.

8. VIL(ac) is used as a simplified symbol for VIL.DQ(AC175), VIL.DQ(AC150), and VIL.DQ(AC135); VIL.DQ(AC175) value is used when Vref - 0.175V is referenced,

VIL.DQ(AC150) value is used when Vref - 0.150V is referenced, and VIL.DQ(AC135) value is used when Vref - 0.135V is referenced.

9. VrefCA(DC) is measured relative to VDD at the same point in time on the same device

10. Optional in DDR3 SDRAM for DDR3-800/1066/1333/1600: Users should refer to the DRAM supplier data sheetand/or the DIMM SPD to determine if DDR3 SDRAM devices

support this option.

DC input logic high

DC input logic low

AC input logic high

AC input logic low NOTE 2

AC input logic high

AC input logic low NOTE 2

AC input logic high

AC input logic low NOTE 2

Reference Voltage for DQ, DM

inputs

RESET, V

REF

= V

REFDQ

(DC)

V

+ 100 V

REF

V

SS

V

+ 175

REF

V

+ 150

REF

V

+ 135

REF

0.49*V

DD

DD

V

- 100 V

REF

+ 100 V

REF

SS

DD

V

- 100

REF

mV 1,5

mV 1,6

V

NOTE 2 - - mV 1,2,7

V

REF

NOTE 2

V

REF

NOTE 2

V

REF

0.51*V

- 175

- 150

- 135

DD

- - mV 1,2,8

V

REF

NOTE 2

V

REF

NOTE 2

0.49*V

+ 150

+ 135

DD

NOTE 2 mV 1,2,7

V

REF

- 150

mV 1,2,8

NOTE 2 mV 1,2,7,10

V

- 135

REF

0.51*V

DD

mV 1,2,8,10

V 3,4,9

- 17 -

Page 18

Rev. 1.21

Unbuffered SODIMM datasheet DDR3L SDRAM

12.2 V

Tolerances

REF

The dc-tolerance limits and ac-noise limits for the reference voltages V

(t) as a function of time. (V

V

REF

V

(DC) is the linear average of V

REF

thermore V

(t) may temporarily deviate from V

REF

stands for V

REF

(t) over a very long period of time (e.g. 1 sec). This average has to meet the min/max requirements of V

REF

voltage

and V

REFCA

(DC) by no more than ± 1% VDD.

REF

REFDQ

likewise).

Figure 1. Illustration of VREF(DC) tolerance and VREF ac-noise limits

REFCA

and V

are illustrate in Figure 1. It shows a valid reference voltage

REFDQ

REF

V

DD

V

SS

time

. Fur-

The voltage levels for setup and hold time measurements VIH(AC), VIH(DC), VIL(AC) and VIL(DC) are dependent on V

" shall be understood as V

"V

REF

This clarifies, that dc-variations of V

which setup and hold is measured. System timing and voltage budgets need to account for V

(DC), as defined in Figure 1.

REF

affect the absolute voltage a signal has to reach to achieve a valid high or low level and therefore the time to

REF

(DC) deviations from the optimum position within the

REF

REF

.

data-eye of the input signals.

This also clarifies that the DRAM setup/hold specification and derating values need to include time and voltage associated with V

Timing and voltage effects due to ac-noise on V

up to the specified limit (+/-1% of VDD) are included in DRAM timings and their associated deratings.

REF

ac-noise.

REF

- 18 -

Page 19

Rev. 1.21

Unbuffered SODIMM datasheet DDR3L SDRAM

12.3 AC and DC Logic Input Levels for Differential Signals

12.3.1 Differential Signals Definition

tDVAC

VIH.DIFF.AC.MIN

.DIFF.MIN

V

IH

0.0

half cycle

.DIFF.MAX

V

IL

.DIFF.AC.MAX

V

IL

Differential Input Voltage (i.e. DQS-DQS, CK-CK)

Figure 2. Definition of differential ac-swing and "time above ac level" tDVAC

12.3.2 Differential Swing Requirement for Clock (CK - CK) and Strobe (DQS - DQS)

DDR3-800/1066/1333/1600

Symbol Parameter

min max min max

V

IHdiff

V

ILdiff

V

(AC)

IHdiff

(AC)

V

ILdiff

NOTE :

1. Used to define a differential signal slew-rate.

2. for CK -

3. These values are not defined, however they single-ended signals CK,

CK use VIH/VIL(AC) of ADD/CMD and V

then the reduced level applies also here.

nals as well as the limitations for overshoot and undershoot. Refer to "overshoot and Undersheet Specification"

differential input high +0.18 NOTE 3 +0.20 NOTE 3 V 1

differential input low NOTE 3 -0.18 NOTE 3 -0.20 V 1

differential input high ac

2 x (VIH(AC) - V

differential input low ac NOTE 3

; for DQS - DQS use VIH/VIL(AC) of DQs and V

REFCA

REF

)

NOTE 3

2 x (VIL(AC) - V

CK, DQS, DQS need to be within the respective limits (VIH(DC) max, VIL(DC)min) for single-ended sig-

2 x (VIH(AC) - V

)

REF

REFDQ

tDVAC

time

unit NOTE1.35V 1.5V

)

REF

NOTE 3

; if a reduced ac-high or ac-low level is used for a signal group,

NOTE 3 V 2

2 x (VIL(AC) - V

REF

)

V2

- 19 -

Page 20

Rev. 1.21

Unbuffered SODIMM datasheet DDR3L SDRAM

[ Table 6 ] Allowed time before ringback (tDVAC) for CK - CK and DQS - DQS (1.35V)

DDR3L-800/1066/1333/1600

Slew Rate [V/ns]

tDVAC [ps] @ |V

min max min max

> 4.0 189 - 201 -

4.0 189 - 201 -

3.0 162 - 179 -

2.0 109 - 134 -

1.8 91 - 119 -

1.6 69 - 100 -

1.4 40 - 76 -

1.2 note - 44 -

1.0 note - note -

< 1.0 note - note -

NOTE: Rising input signal shall become equal to or greater than VIH(ac) level and Falling input signal shall become equal to or less than VIL(ac) level.

(AC)| = 320mV tDVAC [ps] @ |V

IH/Ldiff

(AC)| = 270mV

IH/Ldiff

[ Table 7 ] Allowed time before ringback (tDVAC) for CK - CK and DQS - DQS (1.5V)

DDR3-800 / 1066 / 1333 / 1600

Slew Rate [V/ns]

tDVAC [ps] @ |V

350mV

IH/Ldiff

(AC)| =

tDVAC [ps] @ |V

300mV

IH/Ldiff

(AC)| =

tDVAC [ps] @ |V

IH/Ldiff

(AC)| =

(DQS-DQS#) only (Optional)

min max min max min max

> 4.0 75 - 175 - 214

4.0 57 - 170 - 214

3.0 50 - 167 - 191

2.0 38 - 119 - 146

1.8 34 - 102 - 131

1.6 29 - 81 - 113

1.4 22 - 54 - 88

1.2 note - 19 - 56

1.0 note - note - 11

< 1.0 note - note - note

NOTE: Rising input differential signal shall become equal to or greater than VIHdiff(ac) level and Falling input differential signal shall become equal to or less than VILdiff(ac)

level.

- 20 -

Page 21

Rev. 1.21

Unbuffered SODIMM datasheet DDR3L SDRAM

12.3.3 Single-ended Requirements for Differential Signals

Each individual component of a differential signal (CK, DQS, CK, DQS) has also to comply with certain requirements for single-ended signals.

CK and CK have to approximately reach V

half-cycle.

DQS have to reach V

SEH

min / V

max (approximately the ac-levels ( VIH(AC) / VIL(AC) ) for DQ signals) in every half-cycle proceeding and following a

SEL

valid transition.

Note that the applicable ac-levels for ADD/CMD and DQ’s might be different per speed-bin etc. E.g. if V

signals, then these ac-levels apply also for the single-ended signals CK and

SEH

min / V

max (approximately equal to the ac-levels ( VIH(AC) / VIL(AC) ) for ADD/CMD signals) in every

SEL

150(AC)/VIL150(AC) is used for ADD/CMD

IH

CK .

VDD or V

VDD/2 or V

VSS or V

V

V

SEH

SEL

DDQ

min

DDQ

max

SSQ

V

SEH

/2

Figure 3. Single-ended requirement for differential signals

Note that while ADD/CMD and DQ signal requirements are with respect to V

with respect to V

ended components of differential signals the requirement to reach V

/2; this is nominally the same. The transition of single-ended signals through the ac-levels is used to measure setup time. For single-

DD

max, V

SEL

mode characteristics of these signals.

CK or DQS

V

SEL

time

, the single-ended components of differential signals have a requirement

REF

min has no bearing on timing, but adds a restriction on the common

SEH

[ Table 8 ] Single ended levels for CK, DQS, CK, DQS

Symbol Parameter

V

SEH

V

SEL

NOTE :

1. For CK,

2. V

3. These values are not defined, however the single-ended signals CK, CK, DQS, DQS need to be within the respective limits (VIH(DC) max, VIL(DC)min) for single-ended sig-

CK use VIH/VIL(AC) of ADD/CMD; for strobes (DQS, DQS) use VIH/VIL(AC) of DQs.

(AC)/VIL(AC) for DQs is based on V

IH

reduced level applies also here

nals as well as the limitations for overshoot and undershoot. Refer to "Overshoot and Undershoot Specification"

Single-ended high-level for strobes

Single-ended high-level for CK,

CK

Single-ended low-level for strobes NOTE 3

Single-ended low-level for CK, CK NOTE 3

; VIH(AC)/VIL(AC) for ADD/CMD is based on V

REFDQ

(V

DD

(V

DD

DDR3-800/1066/1333/1600

Min Max

/2)+0.175

/2)+0.175

NOTE 3 V 1, 2

NOTE 3 V 1, 2

(VDD/2)-0.175

(V

/2)-0.175

DD

; if a reduced ac-high or ac-low level is used for a signal group, then the

REFCA

Unit NOTE

V 1, 2

V 1, 2

- 21 -

Page 22

Rev. 1.21

Unbuffered SODIMM datasheet DDR3L SDRAM

12.3.4 Differential Input Cross Point Voltage

To guarantee tight setup and hold times as well as output skew parameters with respect to clock and strobe, each cross point voltage of differential input

signals (CK, CK and DQS, DQS) must meet the requirements in below table. The differential input cross point voltage VIX is measured from the actual

cross point of true and complement signal to the mid level between of VDD and VSS.

V

DD

CK, DQS

V

IX

VDD/2

V

IX

Figure 4. VIX Definition

V

IX

CK, DQS

V

SS

[ Table 9 ] Cross point voltage for differential input signals (CK, DQS) : 1.35V

Symbol Parameter

V

V

NOTE :

1. The relationbetween Vix Min/Max and VSEL/VSEH should satisfy following.

(VDD/2) + Vix(Min) - VSEL 25mV

VSEH - ((VDD/2) + Vix(Max)) 25mV

Differential Input Cross Point Voltage relative to VDD/2 for CK,CK

IX

Differential Input Cross Point Voltage relative to VDD/2 for DQS,DQS

IX

[ Table 10 ] Cross point voltage for differential input signals (CK, DQS) : 1.5V

Symbol Parameter

V

V

NOTE :

1. Extended range for V

±250 mV, and the differential slew rate of CK-

Differential Input Cross Point Voltage relative to VDD/2 for CK,CK

IX

Differential Input Cross Point Voltage relative to VDD/2 for DQS,DQS

IX

is only allowed for clock and if single-ended clock input signals CK and CK are monotonic, have a single-ended swing V

IX

CK is larger than 3 V/ ns.

DDR3L-800/1066/1333/1600

Min Max

Unit NOTE

-150 150 mV 1

-150 150 mV

DDR3-800/1066/1333/1600

Min Max

Unit NOTE

-150 150 mV

-175 175 mV 1

-150 150 mV

/ V

SEL

of at least VDD/2

SEH

- 22 -

Page 23

Rev. 1.21

Unbuffered SODIMM datasheet DDR3L SDRAM

12.4 Slew Rate Definition for Single Ended Input Signals

See "Address / Command Setup, Hold and Derating" for single-ended slew rate definitions for address and command signals.

See "Data Setup, Hold and Slew Rate Derating" for single-ended slew rate definitions for data signals.

12.5 Slew rate definition for Differential Input Signals

Input slew rate for differential signals (CK, CK and DQS, DQS) are defined and measured as shown in below.

[ Table 11 ] Differential input slew rate definition

Description

Differential input slew rate for rising edge (CK-

CK and DQS-DQS)

Differential input slew rate for falling edge (CK-CK and DQS-DQS)

NOTE : The differential signal (i.e. CK - CK and DQS - DQS) must be linear between these thresholds

Measured

From To

V

ILdiffmax

V

IHdiffmin

V

V

IHdiffmin

ILdiffmax

V

0

IHdiffmin

[V

IHdiffmin

[V

IHdiffmin

Defined by

- V

ILdiffmax] /

- V

ILdiffmax] /

Delta TRdiff

Delta TFdiff

V

ILdiffmax

delta TFdiff

delta TRdiff

Differential input slew rate definition for DQS, DQS and CK, CK

13. AC & DC Output Measurement Levels

13.1 Single Ended AC and DC Output Levels

[ Table 12 ] Single Ended AC and DC output levels

Symbol Parameter DDR3-800/1066/1333/1600 Units NOTE

VOH(DC) DC output high measurement level (for IV curve linearity) 0.8 x V

VOM(DC) DC output mid measurement level (for IV curve linearity) 0.5 x V

(DC) DC output low measurement level (for IV curve linearity) 0.2 x V

V

OL

(AC) AC output high measurement level (for output SR) VTT + 0.1 x V

V

OH

VOL(AC) AC output low measurement level (for output SR) VTT - 0.1 x V

NOTE : 1. The swing of +/-0.1 x V

load of 25 to V

TT=VDDQ

is based on approximately 50% of the static single ended output high or low swing with a driver impedance of 40 and an effective test

DDQ

/2.

DDQ

DDQ

DDQ

DDQ

DDQ

13.2 Differential AC and DC Output Levels

[ Table 13 ] Differential AC and DC output levels

Symbol Parameter DDR3-800/1066/1333/1600 Units NOTE

V

(AC) AC differential output high measurement level (for output SR) +0.2 x V

OHdiff

V

(AC) AC differential output low measurement level (for output SR) -0.2 x V

OLdiff

NOTE : 1. The swing of +/-0.2xV

load of 25 to V

TT=VDDQ

is based on approximately 50% of the static single ended output high or low swing with a driver impedance of 40 and an effective test

DDQ

/2 at each of the differential outputs.

DDQ

DDQ

V

V

V

V1

V1

V1

V1

13.3 Single-ended Output Slew Rate

With the reference load for timing measurements, output slew rate for falling and rising edges is defined and measured between VOL(AC) and VOH(AC)

for single ended signals as shown in below.

- 23 -

Page 24

Rev. 1.21

Unbuffered SODIMM datasheet DDR3L SDRAM

[ Table 14 ] Single ended Output slew rate definition

Description

Single ended output slew rate for rising edge

Single ended output slew rate for falling edge

NOTE : Output slew rate is verified by design and characterization, and may not be subject to production test.

[ Table 15 ] Single ended output slew rate

Parameter Symbol

Single ended output slew rate SRQse

Operation

Voltage

1.35V 1.75

Min Max Min Max Min Max Min Max

1.5V 2.5 5 2.5 5 2.5 5 2.5 5 V/ns

Description : SR : Slew Rate

Q : Query Output (like in DQ, which stands for Data-in, Query-Output)

se : Single-ended Signals

For Ron = RZQ/7 setting

NOTE : 1) In two cased, a maximum slew rate of 6V/ns applies for a single DQ signal within a byte lane.

- Case_1 is defined for a single DQ signal within a byte lane which is switching into a certain direction (either from high to low of low to high) while all remaining DQ

signals in the same byte lane are static (i.e they stay at either high or low).

- Case_2 is defined for a single DQ signals in the same byte lane are switching into the opposite direction (i.e. from low to high or high to low respectively). For the

remaining DQ signal switching into the opposite direction, the regular maximum limit of 5 V/ns applies.

Measured

From To

Defined by

VOL(AC) VOH(AC) [VOH(AC)-VOL(AC)] / Delta TRse

VOH(AC) VOL(AC) [VOH(AC)-VOL(AC)] / Delta TFse

DDR3-800 DDR3-1066 DDR3-1333 DDR3-1600

1)

5

1.75

1)

5

1.75

1)

5

1.75

Units

1)

5

V/ns

V

(AC)

OHdiff

VTT

V

(AC)

OLdiff

delta TRdiffdelta TFdiff

Figure 5. Single-ended output slew rate definition

- 24 -

Page 25

Rev. 1.21

Unbuffered SODIMM datasheet DDR3L SDRAM

13.4 Differential Output Slew Rate

With the reference load for timing measurements, output slew rate for falling and rising edges is defined and measured between V

(AC) for differential signals as shown in below.

diff

[ Table 16 ] Differential Output slew rate definition

Description

Differential output slew rate for rising edge

Differential output slew rate for falling edge

NOTE : Output slew rate is verified by design and characterization, and may not be subject to production test.

V

V

Measured

From To

(AC) V

OLdiff

(AC) V

OHdiff

OHdiff

OLdiff

(AC) [V

(AC) [V

OHdiff

OHdiff

(AC)-V

(AC)-V

Defined by

(AC)] / Delta TRdiff

OLdiff

(AC)]/ Delta TFdiff

OLdiff

[ Table 17 ] Differential Output slew rate

Parameter Symbol

Differential output slew rate SRQdiff

Operation

Voltage

1.35V 3.5 12 3.5 12 3.5 12 3.5 12 V/ns

1.5V 5 10 5 10 5 10 5 10 V/ns

DDR3-800 DDR3-1066 DDR3-1333 DDR3-1600

Min Max Min Max Min Max Min Max

Description : SR : Slew Rate

Q : Query Output (like in DQ, which stands for Data-in, Query-Output)

diff : Differential Signals

For Ron = RZQ/7 setting

V

(AC)

OHdiff

OLdiff

(AC) and V

Units

OH-

VTT

V

OLdiff

delta TRdiffdelta TFdiff

Figure 6. Differential output slew rate definition

(AC)

- 25 -

Page 26

Rev. 1.21

Unbuffered SODIMM datasheet DDR3L SDRAM

14. IDD specification definition

Symbol Description

IDD0

IDD1

IDD2N

IDD2P0

IDD2P1

IDD2Q

IDD3N

IDD3P

IDD4R

IDD4W

IDD5B

IDD6

IDD6ET

IDD7

IDD8

Operating One Bank Active-Precharge Current

CKE: High; External clock: On; tCK, nRC, nRAS, CL: Refer to Component Datasheet for detail pattern ; BL: 8

Command, Address, Bank Address Inputs: partially toggling ; Data IO: FLOATING; DM:stable at 0; Bank Activity: Cycling with one bank active at a time:

0,0,1,1,2,2,... ; Output Buffer and RTT: Enabled in Mode Registers

2)

; ODT Signal: stable at 0; Pattern Details: Refer to Component Datasheet for detail pat-

tern

Operating One Bank Active-Read-Precharge Current

CKE: High; External clock: On; tCK, nRC, nRAS, nRCD, CL: Refer to Component Datasheet for detail pattern ; BL: 8

and PRE; Command, Address, Bank Address Inputs, Data IO: partially toggling ; DM:stable at 0; Bank Activity: Cycling with one bank active at a time:

0,0,1,1,2,2,... ; Output Buffer and RTT: Enabled in Mode Registers

2)

; ODT Signal: stable at 0; Pattern Details: Refer to Component Datasheet for detail pat-

tern

Precharge Standby Current

CKE: High; External clock: On; tCK, CL: Refer to Component Datasheet for detail pattern ; BL: 8

Address Inputs: partially toggling ; Data IO: FLOATING; DM:stable at 0; Bank Activity: all banks closed; Output Buffer and RTT: Enabled in Mode

2)

Registers

; ODT Signal: stable at 0; Pattern Details: Refer to Component Datasheet for detail pattern

1)

; AL: 0; CS: stable at 1; Command, Address, Bank

Precharge Power-Down Current Slow Exit

CKE: Low; External clock: On; tCK, CL: Refer to Component Datasheet for detail pattern ; BL: 81); AL: 0; CS: stable at 1; Command, Address, Bank

Address Inputs: stable at 0; Data IO: FLOATING; DM:stable at 0; Bank Activity: all banks closed; Output Buffer and RTT: Enabled in Mode Registers

ODT Signal: stable at 0; Precharge Power Down Mode: Slow Exit

Precharge Power-Down Current Fast Exit

CKE: Low; External clock: On; tCK, CL: Refer to Component Datasheet for detail pattern ; BL: 8

Address Inputs: stable at 0; Data IO: FLOATING; DM:stable at 0; Bank Activity: all banks closed; Output Buffer and RTT: Enabled in Mode Registers

ODT Signal: stable at 0; Precharge Power Down Mode: Fast Exit

Precharge Quiet Standby Current

CKE: High; External clock: On; tCK, CL: Refer to Component Datasheet for detail pattern ; BL: 8

3)

1)

; AL: 0; CS: stable at 1; Command, Address, Bank

3)

1)