SAMSUNG M366S2953MTS Technical data

查询DS_M366S2953MTS供应商

Preliminary

M366S2953MTS

M366S2953MTS SDRAM DIMM

128Mx64 SDRAM DIMM based on 64Mx8, 4Banks, 8K Refresh, 3.3V Synchronous DRAMs with SPD

The Samsung M366S2953MTS is a 64M bit x 64 Synchronous

Dynamic RAM high density memory module. The Samsung

M366S2953MTS consists of sixteen CMOS 64M x 8 bit with

4banks Synchronous DRAMs in TSOP-II 400mil package and a

2K EEPROM in 8-pin TSSOP package on a 168-pin glass-epoxy

substrate. Two 0.1uF decoupling capacitors are mounted on the

printed circuit board in parallel for each SDRAM.

The M366S2953MTS is a Dual In-line Memory Module and is

intended for mounting into 168-pin edge connector sockets.

Synchronous design allows precise cycle control with the use of

system clock. I/O transactions are possible on every clock cycle.

Range of operating frequencies, programmable latencies allows

the same device to be useful for a variety of high bandwidth, high

performance memory system applications.

PC133/PC100 Unbuffered DIMM

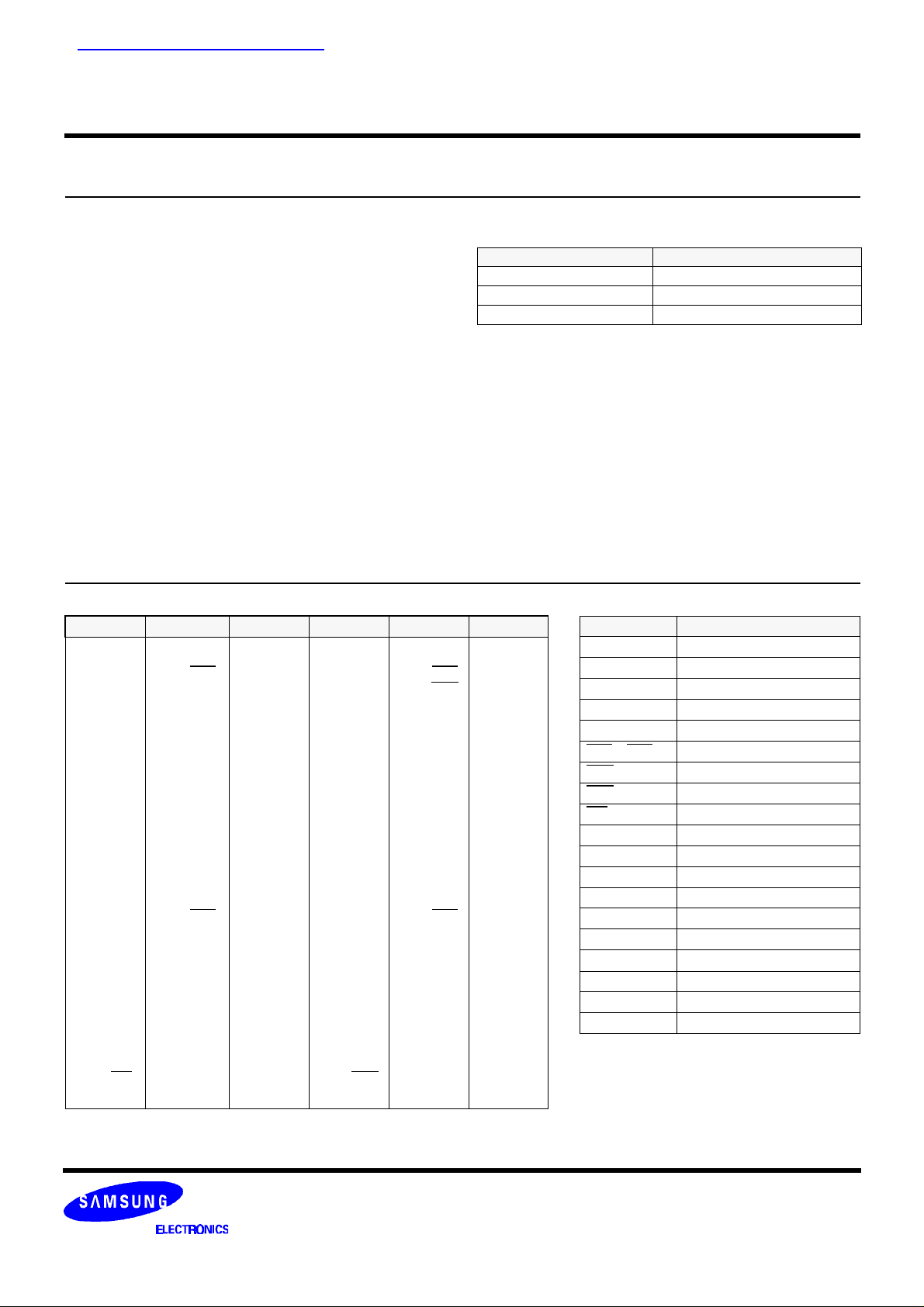

FEATUREGENERAL DESCRIPTION

• Performance range

Part No. Max Freq. (Speed)

M366S2953MTS-C75 133MHz@CL=3

M366S3953MTS-C1H 100MHz @ CL=2

M366S2953MTS-C1L 100MHz @ CL=3

• Burst mode operation

• Auto & self refresh capability (8192 Cycles/64ms)

• LVTTL compatible inputs and outputs

• Single 3.3V ± 0.3V power supply

• MRS cycle with address key programs

Latency (Access from column address)

Burst length (1, 2, 4, 8 & Full page)

Data scramble (Sequential & Interleave)

• All inputs are sampled at the positive going edge of the

system clock

• Serial presence detect with EEPROM

• PCB : Height (1,375mil), double sided component

PIN CONFIGURATIONS (Front side/back side)

CS0

DU

VSS

A0

A2

A4

A6

A8

BA1

VDD

VDD

VSS

DU

CS2

DU

VDD

NC

NC

VSS

Pin

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

Front

DQ18

DQ19

VDD

DQ20

NC

*VREF

CKE1

VSS

DQ21

DQ22

DQ23

VSS

DQ24

DQ25

DQ26

DQ27

VDD

DQ28

DQ29

DQ30

DQ31

VSS

CLK2

NC

*WP

**SDA

**SCL

VDD

Pin

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

Back

VSS

DQ32

DQ33

DQ34

DQ35

VDD

DQ36

DQ37

DQ38

DQ39

DQ40

VSS

DQ41

DQ42

DQ43

DQ44

DQ45

VDD

DQ46

DQ47

*CB4

*CB5

VSS

NC

NC

VDD

CAS

DQM4

Pin

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

Back

DQM5

CS1

RAS

VSS

A1

A3

A5

A7

A9

BA0

A11

VDD

CLK1

A12

VSS

CKE0

CS3

DQM6

DQM7

*A13

VDD

NC

NC

*CB6

*CB7

VSS

DQ48

DQ49

Pin

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

Front

VSS

DQ0

DQ1

DQ2

DQ3

VDD

DQ4

DQ5

DQ6

DQ7

DQ8

VSS

DQ9

DQ10

DQ11

DQ12

DQ13

VDD

DQ14

DQ15

*CB0

*CB1

VSS

NC

NC

VDD

WE

DQM0

Pin

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

Front

DQM1

A10/AP

CLK0

DQM2

DQM3

*CB2

*CB3

DQ16

DQ17

Pin

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

161

162

163

164

165

166

167

168

Back

DQ50

DQ51

VDD

DQ52

NC

*VREF

NC

VSS

DQ53

DQ54

DQ55

VSS

DQ56

DQ57

DQ58

DQ59

VDD

DQ60

DQ61

DQ62

DQ63

VSS

CLK3

NC

**SA0

**SA1

**SA2

VDD

PIN NAMES

Pin Name Function

A0 ~ A12 Address input (Multiplexed)

BA0 ~ BA1 Select bank

DQ0 ~ DQ63 Data input/output

CLK0 ~ CLK3 Clock input

CKE0 ~ CKE1 Clock enable input

CS0 ~ CS3 Chip select input

RAS Row address strobe

CAS Column address strobe

WE Write enable

DQM0 ~ 7 DQM

VDD Power supply (3.3V)

VSS Ground

*VREF Power supply for reference

SDA Serial data I/O

SCL Serial clock

SA0 ~ 2 Address in EEPROM

*WP Write protection

DU Don′t use

NC No connection

* These pins are not used in this module.

** These pins should be NC in the system

which does not support SPD.

SAMSUNG ELECTRONICS CO., Ltd. reserves the right to change products and specifications without notice.

REV. 0.0 Dec. 2001

M366S2953MTS

PC133/PC100 Unbuffered DIMM

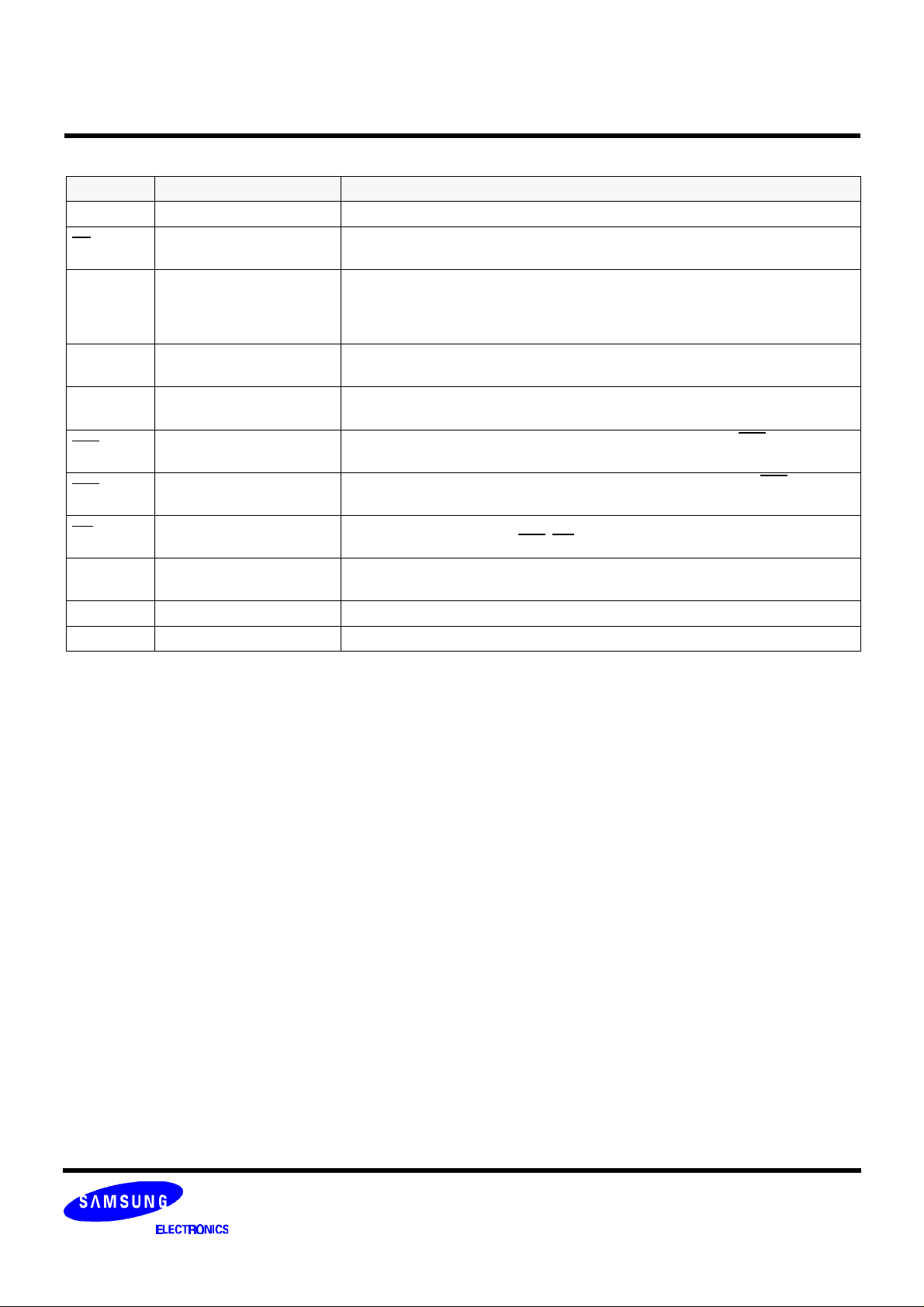

PIN CONFIGURATION DESCRIPTION

Pin Name Input Function

CLK System clock Active on the positive going edge to sample all inputs.

CS Chip select

CKE Clock enable

Disables or enables device operation by masking or enabling all inputs except

CLK, CKE and DQM.

Masks system clock to freeze operation from the next clock cycle.

CKE should be enabled at least one cycle prior to new command.

Disable input buffers for power down in standby.

CKE should be enabled 1CLK+tSS prior to valid command.

A0 ~ A12 Address

BA0 ~ BA1 Bank select address

RAS Row address strobe

CAS Column address strobe

WE Write enable

DQM0 ~ 7 Data input/output mask

DQ0 ~ 63 Data input/output Data inputs/outputs are multiplexed on the same pins.

VDD/VSS Power supply/ground Power and ground for the input buffers and the core logic.

Row/column addresses are multiplexed on the same pins.

Row address : RA0 ~ RA12, Column address : CA0 ~ CA9,CA11

Selects bank to be activated during row address latch time.

Selects bank for read/write during column address latch time.

Latches row addresses on the positive going edge of the CLK with RAS low.

Enables row access & precharge.

Latches column addresses on the positive going edge of the CLK with CAS low.

Enables column access.

Enables write operation and row precharge.

Latches data in starting from CAS, WE active.

Makes data output Hi-Z, tSHZ after the clock and masks the output.

Blocks data input when DQM active. (Byte masking)

REV. 0.0 Dec. 2001

M366S2953MTS

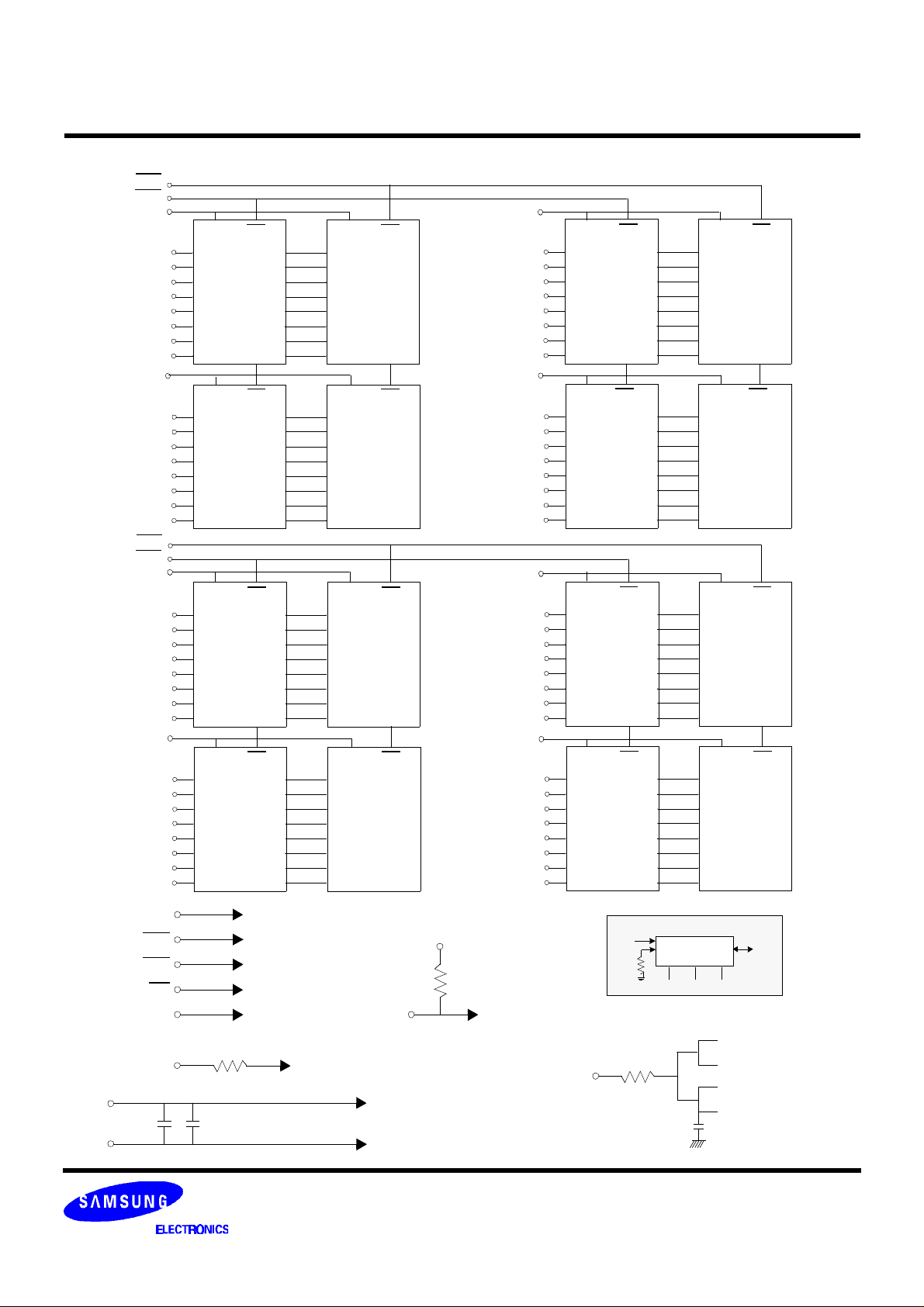

FUNCTIONAL BLOCK DIAGRAM

CS1

CS0

DQM0

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQM1

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

CS3

CS2

DQM2

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQM3

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQM CS

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQM CS

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQM CS

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQM CS

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

•

• •

U0

• •

U1

•

•

U2

•

U3

•

DQM CS

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQM CS

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQM CS

DQ0

DQ1

DQ2

U10

DQ3

DQ4

DQ5

DQ6

DQ7

DQM CS

DQ0

DQ1

DQ2

U11

DQ3

DQ4

DQ5

DQ6

DQ7

PC133/PC100 Unbuffered DIMM

DQM4

DQM CS

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

U4

U8

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQM5

DQM CS

U9

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

U5

•

DQM6

•

DQM CS

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQM7

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

•

U6

DQM CS

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

U7

DQM CS

DQ0

DQ1

DQ2

U12

DQ3

DQ4

DQ5

DQ6

DQ7

DQM CS

DQ0

DQ1

DQ2

U13

DQ3

DQ4

DQ5

DQ6

DQ7

DQM CS

DQ0

DQ1

DQ2

U14

DQ3

DQ4

DQ5

DQ6

DQ7

DQM CS

DQ0

DQ1

DQ2

U15

DQ3

DQ4

DQ5

DQ6

DQ7

A0 ~ An, BA0 & 1

RAS

CAS

WE

CKE0

DQn

VDD

Vss

SDRAM U0 ~ U15

SDRAM U0 ~ U15

SDRAM U0 ~ U15

SDRAM U0 ~ U15

SDRAM U0 ~ U7

CKE1

10Ω

Every DQpin of SDRAM

•

•

Two 0.1uF Capacitors

per each SDRAM

•

•

VDD

10KΩ

•

To all SDRAMs

SCL

47K

SDRAM U8 ~ U15

10Ω

CLK0/1/2/3

Serial PD

WP

Ω

A1 A2A0

SA1 SA2SA0

•

•

•

•

SDA

U0/U1/U2/U3

U4/U5/U6/U7

U8/U9/U10/U11

U12/U13/U14/U15

1.5pF

REV. 0.0 Dec. 2001

Loading...

Loading...