Samsung KS9286B, KS9286B-L Datasheet

DIGITAL SIGNAL PROCESSOR for CDPKS9286B/KS9286B-L

DIGITAL SIGNAL PROCESSOR

The KS9286B is a CMOS integrated circuit designed for

the Digital Audio Signal Processor for Compact Disc

Player. It is a monolithic IC that builts-in 16-bit Digital

Analog Convertor, ESP Interface and Digital De-emphasis

additional conventional DSP function.

FEATURES

• EFM data demodulation

80-QFP-1420C

ORDERING INFORMATION

• Frame sync detection/protection/insertion

• Powerful error correction (C1: 2error, C2: 4erasure)

• Interpolation

• 8fs digital filter (51th+13th+9th)

• Subcode data serial output

• CLV servo controller

• Micom interface

• Digital audio output

• Digital de-emphasis

• ESP interface

• Built-in 16K SRAM

• Built-in Digital PLL

• Double speed play available

• Built-in 16-bit D/A converter

• Operating Voltage range

KS9286B : 5V

KS9286B-L : 3.4V

Device Package Tempe. Range

KS9286B

KS9286B-L

80-QFP-1420C -20oC ~ +75oC

1

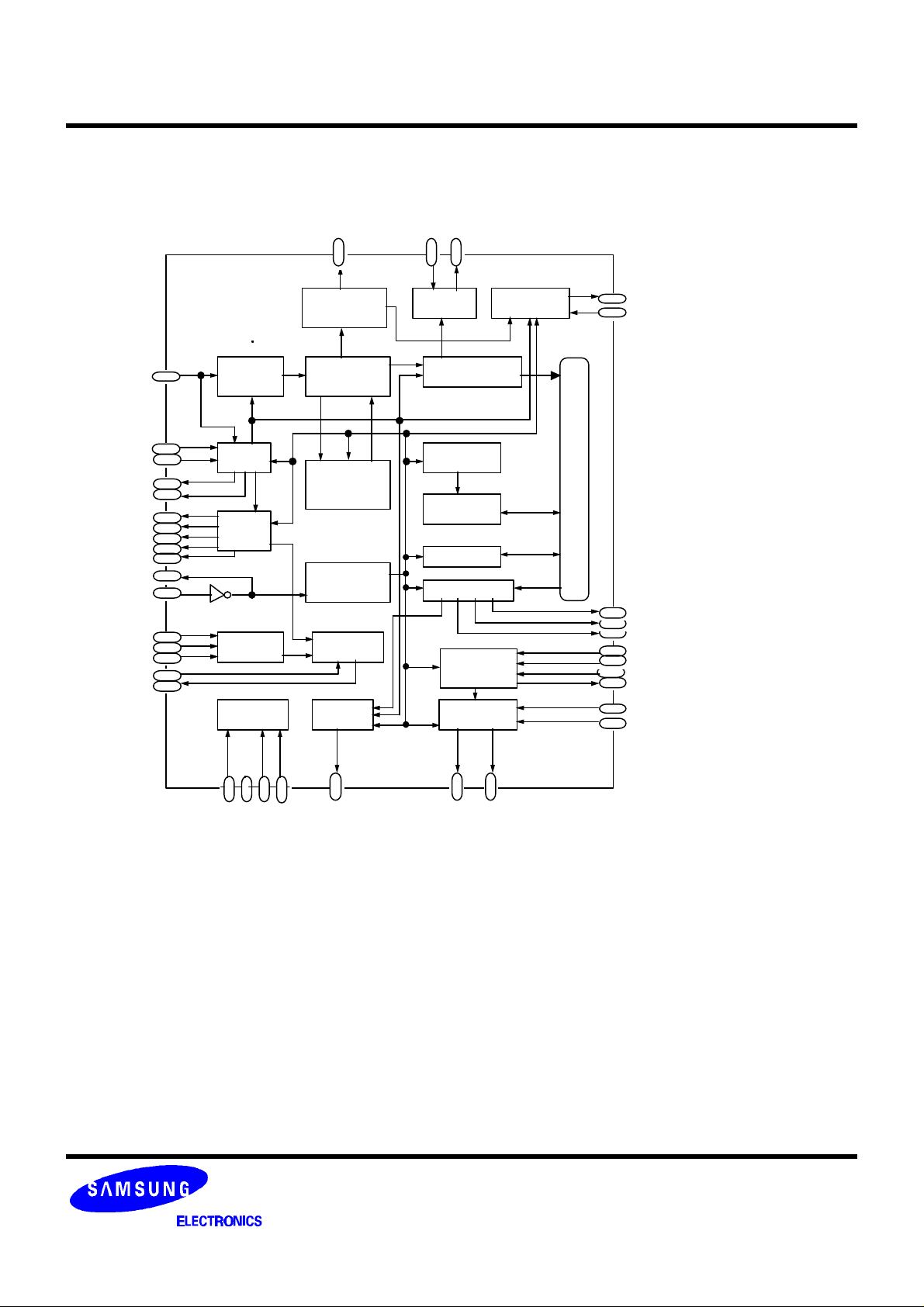

BLOCK DIAGRAM

L

S0S1

26

SUBCODE

SYNC

DETECTOR

SDAT

SBCK

33

32

SUBCODE

OUTPUT

DIGITAL SIGNAL PROCESSOR for CDPKS9286B/KS9286B-L

SUBCODE-Q

REGIS TER

SQDT

30

SQCK

29

EFMI

CNTVOL

DPFIN

DPFOUT

DPDO

SMEF

SMON

SMDP

SMDS

LOCK

XOUT

XIN

MDAT

MCK

MLT

TRCNT

/ISTAT

66

5

3

4

2

72

73

75

76

70

9

8

37

38

36

69

68

EFM

PHASE

DETECTOR

DIGITAL

PLL

CLV

SERVO

CPU

INTERFACE

MODE

SELECTOR

63

62

61

CDROM

TEST0

XTALSE

65

TEST1

23BIT

SHIFT

REGIS TER

FRAME SYNC

DETECTOR

PROTECTOR

INSERTOR

X-TAL

TIMING

GENERATOR

TRACK

COUNTER

DIGITAL

OUTPUT

7

DATX

EFM

DEMODULATOR

ADDRESS

GENERATOR

16K

SRAM

ECC

INTERPOLATOR

DIGITAL

FILTER

& DE-EMPH

D/A

CONVERTER

20

1919

LCHOUT

RCHOUT

8BIT DATA BUS

LRCHO

11

ADATAO

12

14

BCKO

BCKI

77

ADATAI

67

LRCHI

80

24

EMPH

VREFL1

17

22

VREFH1

2

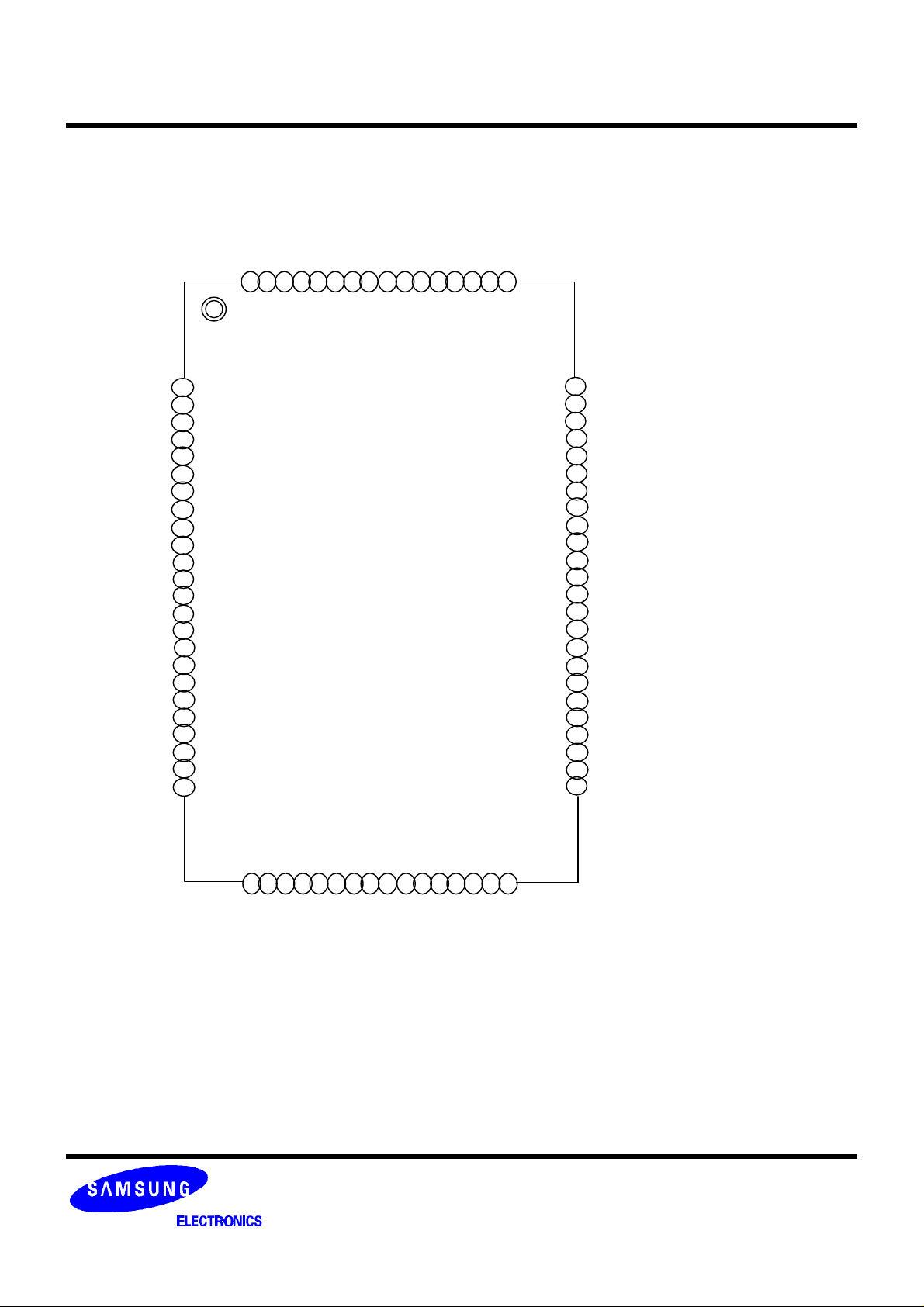

PIN CONFIGURATION

DIGITAL SIGNAL PROCESSOR for CDPKS9286B/KS9286B-L

AVDDI

DPDO

DPFIN

DPFOUT

CNTVOL

AVSS 1

DATX

XIN

XOUT

WDCHO

LRCHO

ADATAO

DVSS1

BCKO

C2PO

VREFL2

VREFL1

AVDD2

RCHOUT

LCHOUT

AVSS 2

VREFH1

VREFH2

EMPH

DSPEED

TESTV

LRCHI

807978777675747372717069686766

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

BCKI

DVDD2

SMON

SMDP

SMDS

LOCK

SMEF

PBFR

KS9286 B

ADATAI

TRCNT

/ISTAT

TEST1

EFMI

65

SRAM

64

CDROM

63

FOK

62

XTALSEL

61

/CS

60

/WE

59

C16M

58

C4M

57

/JIT

56

ULKFS

55

FSDW

54

DVSS2

53

/PBCK

52

FLAG5

51

FLAG4

50

FLAG3

49

FLAG2

48

FLAG1

47

RD0

46

RD1

45

RD2

44

RD3

43

RD4

42

RD5

41

252627282930313233343536373839

MCK

MDAT

MLT

MUTE

DVDD1SDAT

SBCK

SQOK

SQDT

SQCK

/ESP

RESETS0S1

LKFS

40

RD6

RD7

3

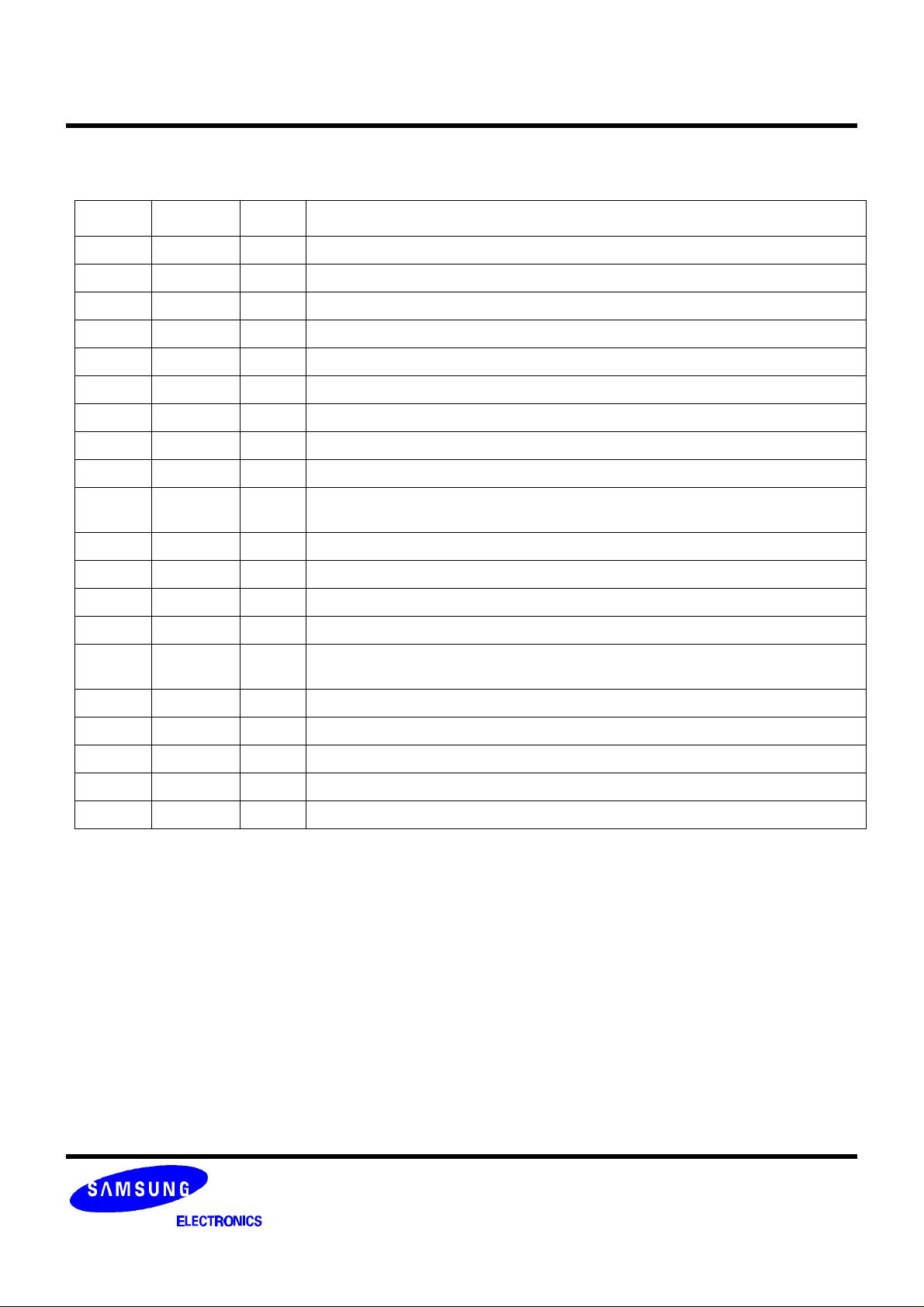

PIN DESCRIPTION

DIGITAL SIGNAL PROCESSOR for CDPKS9286B/KS9286B-L

PIN NO

1 AVDD1 - Analog VCC1

2 DPDO O Charge pump output for Digital PLL

3 DPFIN I Filter input for Digital PLL

4 DPFOUT O Filter output for Digital PLL

5 CNTVOL I VCO control voltage for Digital PLL

6 AVSS1 - Analog Ground1

7 DATX O Digital Audio output data

8 XIN I X'tal oscillator input

9 XOUT O X'tal oscillator output

10 WDCHO O Word clock output of 48bit/Slot (88.2KHz)

11 LRCHO O Channel clock output of 48 bit/Slot (44.1KHz)

12 ADATAO O Serial audio data output of 48 bit/Slot (MSB first)

13 DVSS1 - Digital Ground1

14 BCKO O Audio data bit clock output of 48 bit/Slot (2.1168MHz)

15 C2PO O C2 Pointer for output audio data

SYMBOL IO DESCRIPTION

16 VREFL2 I Input terminal2 of reference voltage "L" (Floating)

17 VREFL1 I Input terminal1 of reference voltage "L" (GND connection)

18 AVDD2 - Analog VCC2

19 RCHOUT O Right-Channel audio output through D/A converter

20 LCHOUT O Left-Channel audio output through D/A converter

21 AVSS2 - Analog ground2

22 VREFH1 I Input terminal1 of reference voltage "H" (VDD connection)

23 VREFH2 I Input terminal2 of reference voltage "H" (Floating)

24 EMPH O H: Emphasis ON, L: Emphasis OFF

25 LKFS O The Lock Status output of frame sync

26 S0S1 O Output of subcode sync signal(S0+S1)

27 RESET I System reset at "L"

28 /ESP I ESP function ON/OFF control ("L": ESP function ON, "H": ESP function OFF)

29 SQCK I Clock for output Subcode-Q data

4

PIN DESCRIPTION (continued)

DIGITAL SIGNAL PROCESSOR for CDPKS9286B/KS9286B-L

PIN NO

30 SQDT O Serial output of Subcode-Q data

31 SQOK O The CRC (Cycle Redundancy Check) check result signal output of Subcode-Q

32 SBCK I Clock for output subcode data

33 SDAT O Subcode serial data output

34 DVDD1 - Digital VDD1

35 MUTE I Mute control input ("H": Mute ON)

36 MLT I Latch Signal Input from Micom (Schmit Trigger)

37 MDAT I Serial data input from Micom (Schmit Trigger)

38 MCK I Serial clock input from Micom (Schmit Trigger)

39 RD7 I/O SRAM data I/O port 8 (MSB)

40 RD6 I/O SRAM data I/O port 7

41 RD5 I/O SRAM data I/O port 6

42 RD4 I/O SRAM data I/O port 5

43 RD3 I/O SRAM data I/O port 4

44 RD2 I/O SRAM data I/O port 3

SYMBOL IO DESCRIPTION

45 RD1 I/O SRAM data I/O port 2

46 RD0 I/O SRAM data I/O port 1 (LSB)

47 FLAG1 I/O Monitoring output for error correction (RA0)

48 FLAG2 I/O Monitoring output for error correction (RA1)

49 FLAG3 I/O Monitoring output for error correction (RA2)

50 FLAG4 I/O Monitoring output for error correction (RA3)

51 FLAG5 I/O Monitoring output for error correction (RA4)

52 /PBCK I/O Output of VCO/2 (4.3218MHz) (RA5)

53 DVSS2 I/O Digital ground 2

54 FSDW I/O Window or unprotected frame sync (RA6)

55 ULKFS I/O Frame sync protection state (RA7)

56 /JIT I/O Display of either RAM overflow or underflow for + 4 frame jitter margin (RA8)

57 C4M I/O Only monitoring signal (4.2336MHz) (RA9)

58 C16M I/O 16.9344MHz signal output(RA10)

59 /WE I/O Terminal for test

60 /CS I/O Terminal for test

5

PIN DESCRIPTION (continued)

DIGITAL SIGNAL PROCESSOR for CDPKS9286B/KS9286B-L

PIN NO

61 XTALSEL I Mode Selection1 (H: 33.8688MHz, L: 16.9344MHz)

62 FOK I SERVO FOK Signal input terminal

63 CDROM I Mode Selection2 (H: CD-ROM, L: CDP)

64 SRAM I TEST input terminal (GND connection)

65 TEST1 I TEST input terminal (GND connection)

66 EFMI I EFM signal input

67 ADATAI I Serial audio data input of 48 bit/Slot (MSB first)

68 /ISTAT O The internal status output

69 TRCNT I Tracking counter input signal

70 LOCK O Output signal of LKFS condition sampled PBFR/16 (if LKFS is "H", LOCK is "H",

71 PBFR O Write frame clock (Lock: 7.35KHz)

72 SMEF O LPF time constant control of the spindle servo error signal

73 SMON O ON/OFF control signal for spindle servo

74 DVDD2 - Digital VDD2

75 SMDP O Spindle Motor drive (Rough control in the SPEED mode, Phase control in the PHASE

SYMBOL IO DESCRIPTION

if LKFS is sampled "L" at least 8 times by PBFR/16, LOCK is "L".)

mode)

76 SMDS O Spindle Motor drive (Velocity control in the PHASE mode)

77 BCKI I Audio data bit clock input of 48 bit/Slot (2.1168MHz)

78 TESTV I TEST input terminal (GND connection)

79 DSPEED I TEST input terminal (VDD connection)

80 LRCHI I Channel clock input of 48 bit/Slot (44.1KHz)

6

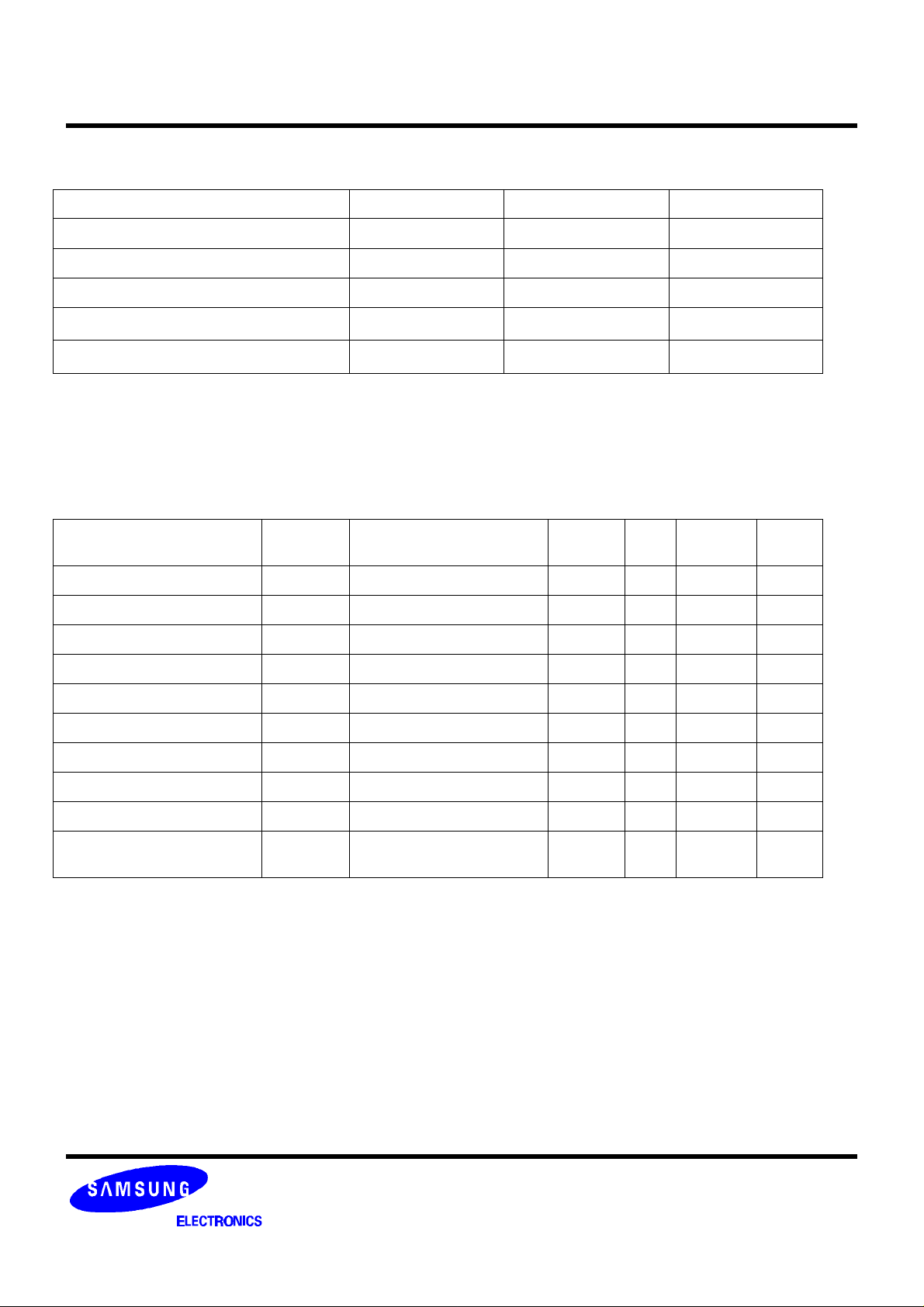

DIGITAL SIGNAL PROCESSOR for CDPKS9286B/KS9286B-L

ABSOLUTE MAXIMUM RATINGS

Characteristic Symbol Value Unit

Supply Voltage VDD -0.3 ~ 7.0 V

Input Voltage VI -0.3 ~ 7.0 V

Output Voltage VO -0.3 ~ 7.0 V

Operating Temperature TOPR -20 ~ 75

Storage Temperature TSTG -40 ~ 125

o

C

o

C

ELECTRICAL CHARACTERISTIC

1. DC Characteristic

(Vcc=5V, Vss=0V, Ta=25

Characteristic Symbol

'H' INPUT VOLTAGE1 VIH(1) (Note1) 0.7VDD - - V

'L' INPUT VOLTAGE1 VIL(1) (Note1) - - 0.3VDD V

'H' INPUT VOLTAGE2 VIH(2) (Note2) 0.8VDD - - V

'L' INPUT VOLTAGE2 VIL(2) (Note2) - - 0.2VDD V

'H' OUTPUT VOLTAGE1 VOH(1) IOH=-1mA (Note3) VDD-0.5 - VDD V

'L' OUTPUT VOLTAGE1 VOL(1) IOL=1mA (Note3) 0 - 0.4 V

'H' OUTPUT VOLTAGE2 VOH(2) IOH=-1mA (Note4) VDD-0.5 - VDD V

o

C, unless otherwise specified)

Conditions

Test

Min Typ Max Unit

'L' OUTPUT VOLTAGE2 VOL(2) IOL=2mA (Note4) 0 - 0.4 V

INPUT LEAK CURRENT ILKG VI=0~VDD (Note5) -5 - 5 uA

THREE STATE OUTPUT

LEAK CURRENT

(Note1) Related pins : XTALSEL, TEST0, CDROM, SRAM, TEST1, EFMI, ADATAI, BCKI, DSPEED & LRCHI

(Note2) Related pins : All bi-direction pins & RESET, MLT, MCK, MDAT, MUTE, TRCNT

(Note3) Related pins : All output pins except (Note4) and OSCILATOR, DPFOUT

(Note4) Related pins : /ISTAT

(Note5) Related pins : XIN

(Note6) Related pins : SMEF, SMDP, SMDS & DPDO

IO(LKG) VO=0~VDD (Note6) -5 - 5 uA

7

DIGITAL SIGNAL PROCESSOR for CDPKS9286B/KS9286B-L

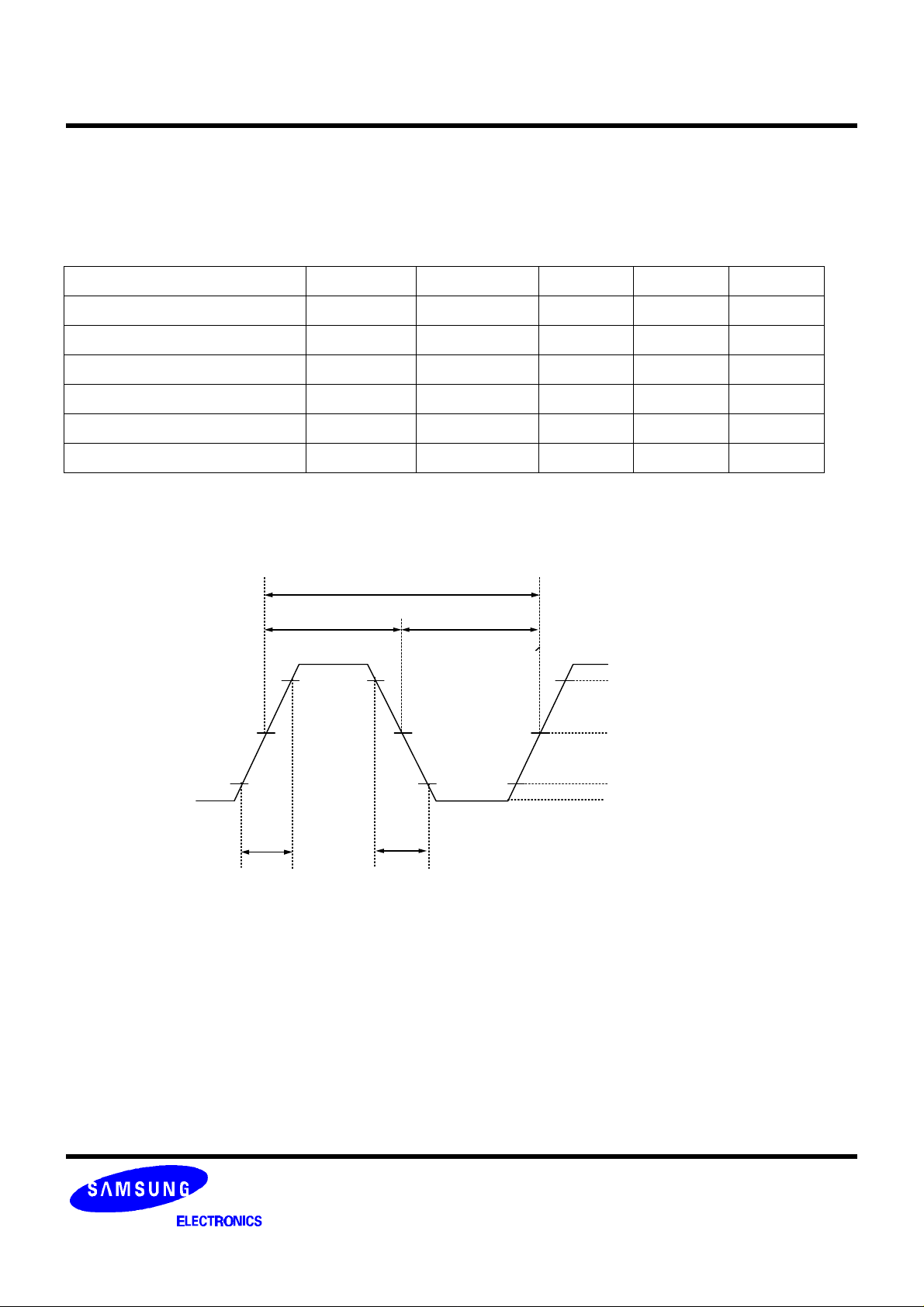

2. AC CHARACTERISTIC

A. XIN (When the pulse is input)

(Vcc=5V, Vss=0V, Ta=25

Characteristic Symbol Min Typ Max UNIT

'H' LEVEL PULSE WIDTH TWH 13 - - ns

'L' LEVEL PULSE WIDTH TWL 13 - - ns

PULSE FREQUENCY TCK 26 - - ns

INPUT 'H' LEVEL VIH VDD-1.0 - - V

INPUT 'L' LEVEL VIL - - 0.8 V

RISING & FALLING TIME TR,TF - - 8 ns

o

C, unless otherwise specified)

TR

TCK

TWH TWL

VIH

VIHx0 .9

VDD/2

VIL*0.1

VIL

TF

8

DIGITAL SIGNAL PROCESSOR for CDPKS9286B/KS9286B-L

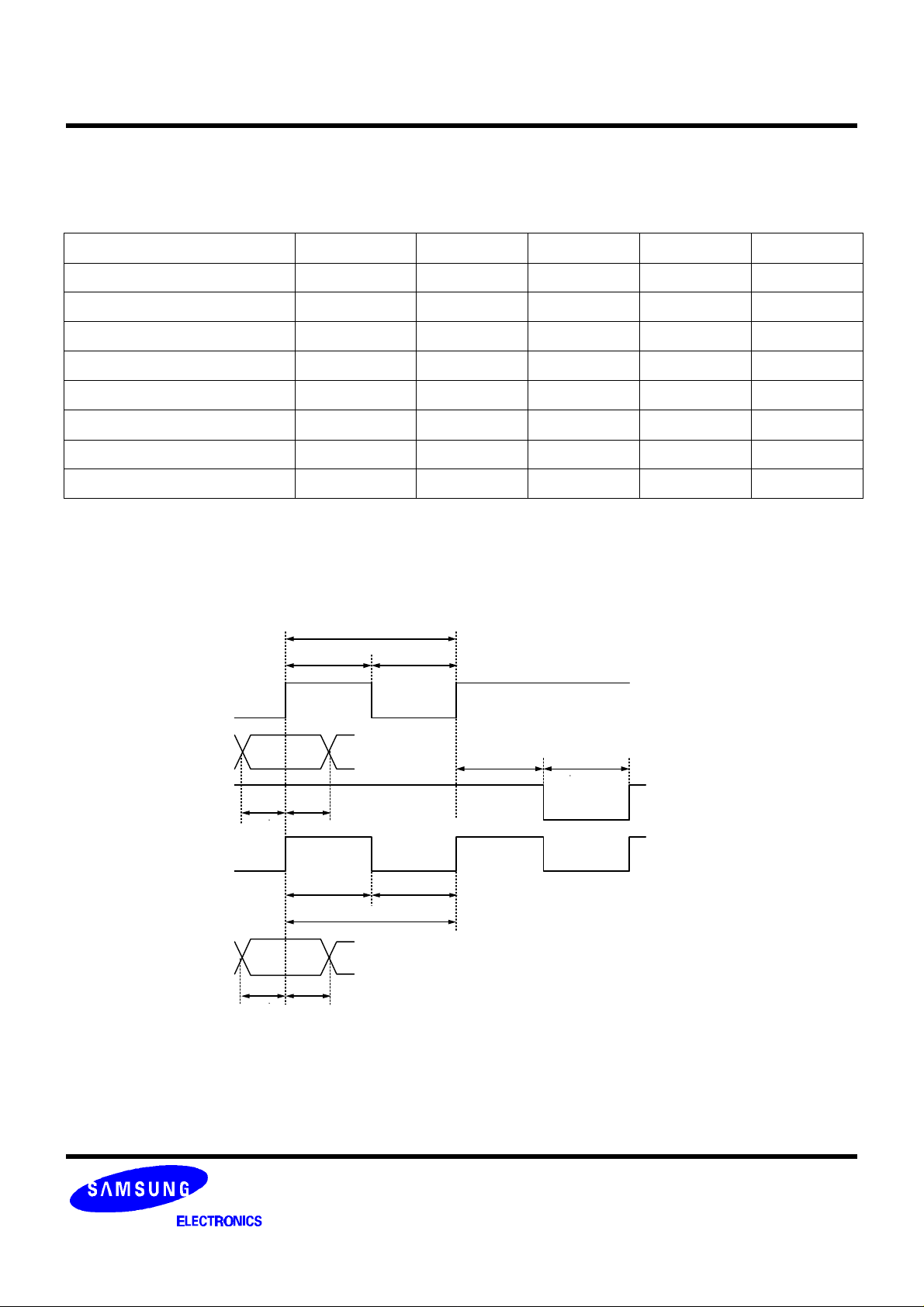

B. MCK, MDAT, MLT & TRCNT

(Vcc=5V, Vss=0V, Ta=25

Characteristic Symbol Min Typ Max Unit

CLOCK FREQUENCY FCK1 - - 1 MHz

CLOCK PULE WIDTH TW 300 - - ns

SETUP TIME TSU 300 - - ns

HOLD TIME TH 300 - - ns

DELAY TIME TD 300 - - ns

LATCH PULSE WIDTH TWCK1 300 - - ns

TRCNT, SQCK FREQUENCY FCK2 - - 1 MHz

TRCNT, SQCK PULSE WIDTH TWCK2 300 - - ns

o

C, unless otherwise specified)

MCK

MDAT

MLT

TRCNT

SQCK

SQDAT

1/FCK 1

TWCK1 TWCK1

TD TW

THTSU

TWCK2 TWCK2

1/FCK2

THTSU

9

DIGITAL SIGNAL PROCESSOR for CDPKS9286B/KS9286B-L

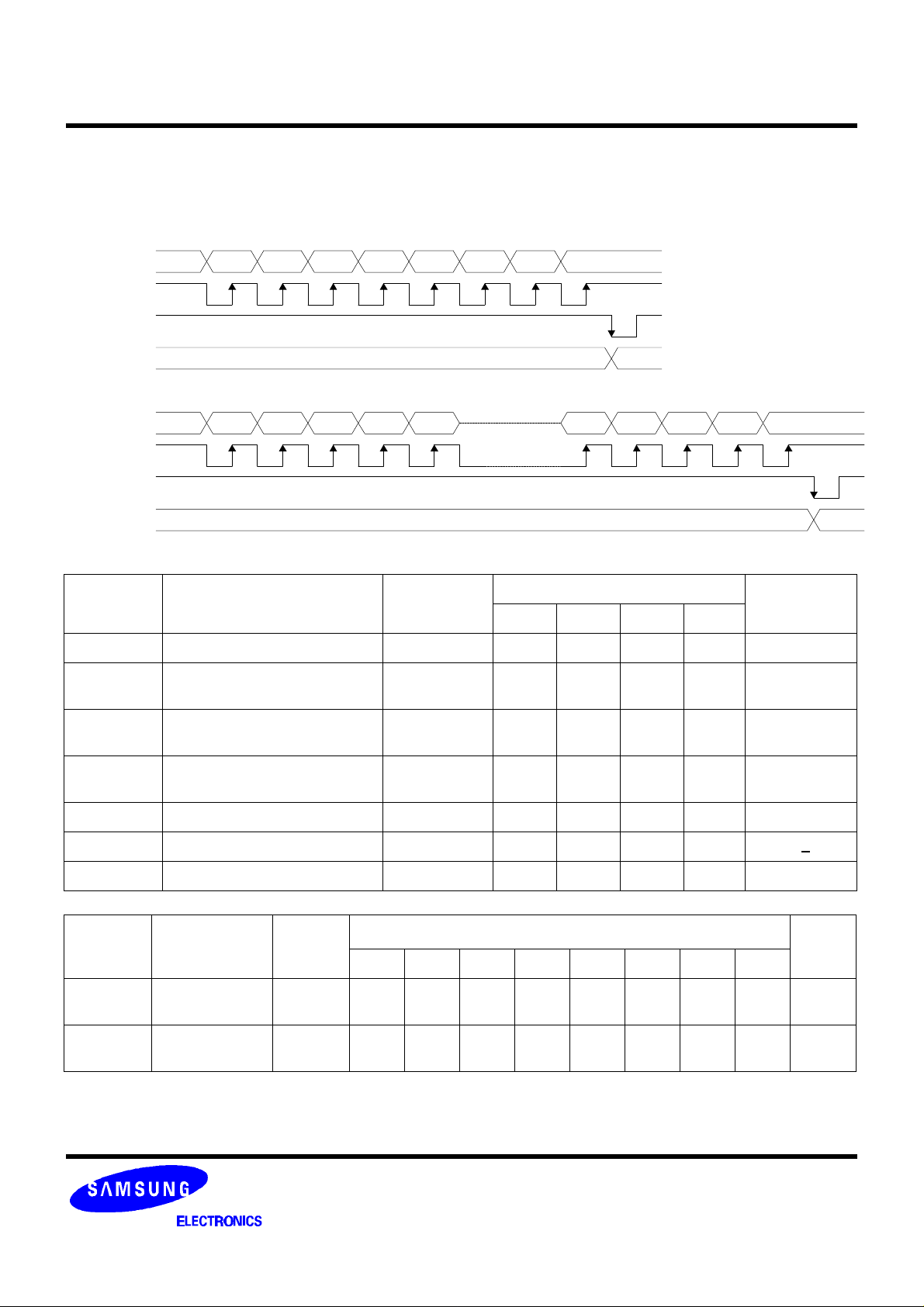

FUNCTION DESCRIPTION

1. Micom Interface

The data inputted from Micom is inputted to MDAT and transfered by MCK, and the inputted signal is loaded to

control register by means of MLT. The timing chart is as follows.

MDAT

MCK

MLT

Register

(9X ~ FX)

MDAT

MCK

D0 D1 D2 D3 D4 D5 D6 D7 <MSB>

Valid

D0 D1 D2 D3 D4 D15 <MSB>D11 D12 D13 D14

¡ó

¡ó

MLT

Register

(88XX, 8DXX)

Fig.1. Micom data input timing chart

CONTROL

ADDRESS

COMMENT

REGSTER

D7~D4

D3 D2 D1 D0

CNTL-Z DATA CONTROL 9X ZCMT - NCLV CRCQ S0S1

CNTL-S

FRAME SYNC PROTECTION

ATTENUATION CONTROL

AX FSEM FSEL WSEL ATTM LKFS

DATA

/ISTAT

PIN

Valid

CNTL-L

CNTL-U

TRACKING COUNTER

LOWER 4 BITS

TRACKING COUNTER

UPPER 4 BITS

BX TRC3 TRC2 TRC1 TRC0 /COMPLETE

CX TRC7 TRC6 TRC5 TRC4 /COUNT

CNTL-W CLV CONTROL DX - WB WP GAIN FOK

CNTL-C CLV-MODE EX CM3 CM2 CM1 CM0 /(Pw > 64)

CNTL-D DOUBLE-SPEED FX 0 0 DS1 DS2 TRCNT

CONTROL

ADDRESS

DATA

/ISTAT

COMMENT

REGSTER

CNTL-F

CNTL-H

FUNCTION

CONTROL

ESP,MONITOR

PIN CONTROL

D15~D8

88XX - -

D7 D6 D5 D4 D3 D2 D1 D0

DEEM

ERA_

OFF

- - - - Hi-Z

8DXX - - - - - -

ESP_

ON

DUMB

Table 1. Control register & data

* Send the 9X, AX, DX, FX command when output the S0S1, LKFS, FOK, TRCNT signal to /ISTAT pin

also just send MDAT, MCK except MLT

PIN

Hi-Z

10

DIGITAL SIGNAL PROCESSOR for CDPKS9286B/KS9286B-L

1) CNTL-Z REGISTER

It is a register to control zero cross mute of audio data, phase terminal

control, phase servo control and having or not of CRCF in data SQDT.

DATA = 0 DATA = 1

ZCMT D3 Zero cross mute is OFF Zero cross mute is ON

- D2 - -

NCLV D1 The phase servo is acted by frame sync The phase servo is controlled by base

counter

CRCQ D0 SQDT outputs except for SQOK SQDT=CRCF when S0S1='H'

Table 2. CNTL-Z register & data

2) CNTL-S REGISTER

It is a register to control frame sync protection and attenuation.

FSEM FSEL FRAME WSEL CLOCK ATTM MUTE dB

0 0 2 0 + 3 0 0 0

0 1 4 1 + 7 0 1 -

1 0 8 1 0 -12

1 1 13 1 1 -12

Table 3. CNTL-S register & data

3) CNTL-L, U REGISTER

After the counter of track that must be counted is inputted from Micom, the data

is loaded to tracking counter by CNTL-L, U register.

8

11

Loading...

Loading...