Page 1

PROGRAMMING

MANUAL

Programmable Controllers

SYSMAC

CQM1/CPM1/CPM1A/SRM1

Cat. No. W228-E1-08

Page 2

CQM1/CPM1/CPM1A/SRM1 Programmable Controllers

Programming Manual

Revised December 2005

Page 3

iv

Page 4

Notice:

OMRON products are manufactured for use accordin g to proper procedures by a qualified operator

and only for the purposes described in this manual.

The following conventions are used to ind icate and classify pr ecautions in this manual . Always heed

the information provided with them . Failure to heed precautions can result in in jur y to people or damage to property.

!DANGER Indicates an immine ntly hazardous situation whi ch, if not avoided, will result in death or

serious inj ury.

!WARNING Indicates a potentially hazardous situatio n which, if not avoided, could resu lt in death or

serious inj ury.

!Caution Indicates a potentially hazardous situat ion which, if not avoided, may result in mino r or

moderate injury, or property damage.

OMRON Product References

All OMRON products are capitalized in this manual. The word “Unit” is also capitalized when it refers to

an OMRON product, regardless of whether or not it appears in the proper name of the product.

The abbreviation “Ch,” which appears in some displays and on some OMRON produ cts, often means

“word” and is abbreviated “Wd” in documentation in this sense.

The abbreviation “PC” means Programmable Controller and is not used as an abbreviation for anything

else.

Visual Aids

The following headings appear in the left co lumn of the manual to help you locate different types of

information.

OMRON, 1993

All rights reserved. No part of this publicatio n may b e repro d uced, sto red in a retrieval system, or transmitted, in any form, or

by any means, mechanical, electronic, photocopying, recording, or otherwise, without the prior written permission of

OMRON.

No patent liability is assumed with respect to the use of the information contained herein. Moreover, because OMRON is constantly striving to improve its high-quality products, the information contained in this manual is subject to change without

notice. Every precaution has been taken in the preparation of this manual. Nevertheless, OMRON assumes no responsibility

for errors or omissions. Neither is any liability assumed for damages resulting from the use of the information contained in

this publication.

Note Indicates information of pa rticular interest for efficient and convenient opera-

tion of the product.

1,2,3... 1. Indicates lists of one sort or another, such as procedures, checklists, etc.

v

Page 5

vi

Page 6

TABLE OF CONTENTS

PRECAUTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xiii

1 Intended Audience . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xiv

2 General Precautions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xiv

3 Safety Precautions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xiv

4 Operating Environment Precautions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xv

5 Application Precautions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xvi

6 Conformance to EC Directives . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xix

SECTION 1

PC Setup and Other Features . . . . . . . . . . . . . . . . . . . . . 1

1-1 PC Setup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

1-2 Basic PC Operation and I/O Processes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

1-3 Pulse Output Function (CQM1 Only). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

1-4 Pulse Output Function (CPM1A Only). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

1-5 CQM1 Interrupt Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

1-6 CPM1/CPM1A Interrupt Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

1-7 SRM1 Interrupt Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

1-8 CompoBus/S Distributed I/O Functions (SRM1 Only) . . . . . . . . . . . . . . . . . . . . . 88

1-9 Communications Functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

1-10 Calculating with Signed Binary Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

SECTION 2

Special Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

2-1 Expansion Instructions (CQM1/SRM1 Only). . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

2-2 Advanced I/O Instructions (CQM1 Only). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

2-3 Macro Function. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

2-4 Differential Monitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

2-5 Analog Settings (CQM1-CPU42-EV1/CPM1/CPM1A Only) . . . . . . . . . . . . . . . . 132

2-6 Quick-response Inputs (CPM1/CPM1A Only). . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

SECTION 3

Memory Areas. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

3-1 CQM1 Memory Area Functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

3-2 CPM1/CPM1A Memory Area Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

3-3 SRM1 Memory Area Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

3-4 SRM1 Flash Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

3-5 Using Memory Cassettes (CQM1 Only). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

3-6 Operation without a Battery . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 52

SECTION 4

Ladder-diagram Programming. . . . . . . . . . . . . . . . . . . . 155

4-1 Basic Procedure. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

4-2 Instruction Terminology . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

4-3 Basic Ladder Diagrams. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

4-4 Controlling Bit Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 177

4-5 Work Bits (Internal Relays) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 179

4-6 Programming Precautions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 181

4-7 Program Execution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 183

vii

Page 7

TABLE OF CONTENTS

SECTION 5

Instruction Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 185

5-1 Notation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 188

5-2 Instruction Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 188

5-3 Data Areas, Definer Values, and Flags . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 188

5-4 Differentiated Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 190

5-5 Coding Right-hand Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 191

5-6 Instruction Tables. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 194

5-7 Ladder Diagram Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 200

5-8 Bit Control Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 201

5-9 NO OPERATION – NOP(00) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 205

5-10 END – END(01) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 205

5-11 INTERLOCK and INTERLOCK CLEAR – IL(02) and ILC(03). . . . . . . . . . . . . 205

5-12 JUMP and JUMP END – JMP(04) and JME(05) . . . . . . . . . . . . . . . . . . . . . . . . . 207

5-13 User Error Instructions:

FAILURE ALARM AND RESET – FAL(06) and

SEVERE FAILURE ALARM – FALS(07). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 209

5-14 Step Instructions:

STEP DEFINE and STEP START–STEP(08)/SNXT(09) . . . . . . . . . . . . . . . . . . 210

5-15 Timer and Counter Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 212

5-16 Shift Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 229

5-17 Data Movement Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 237

5-18 Comparison Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 248

5-19 Conversion Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 258

5-20 BCD Calculation Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 285

5-21 Binary Calculation Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 296

5-22 Special Math Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 307

5-23 Logic Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 316

5-24 Increment/Decrement Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 319

5-25 Subroutine Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 321

5-26 Special Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 323

5-27 Communications Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 349

5-28 Advanced I/O Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 354

SECTION 6

Host Link Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . 359

6-1 Communications Procedure. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 360

6-2 Command and Response Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 362

6-3 Host Link Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 366

SECTION 7

PC Operations and Processing Time. . . . . . . . . . . . . . . . 391

7-1 CQM1 Cycle Time and I/O Response Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 392

7-2 CPM1/CPM1A Cycle Time and I/O Response Time . . . . . . . . . . . . . . . . . . . . . . 410

7-3 SRM1 Cycle Time and I/O Response Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 422

viii

Page 8

TABLE OF CONTENTS

SECTION 8

Troubleshooting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 433

8-1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 434

8-2 Programming Console Operation Errors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 434

8-3 Programming Errors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 435

8-4 User-defined Errors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 436

8-5 Operating Errors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 437

8-6 Error Log. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 441

8-7 Host Link Errors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 442

8-8 Troubleshooting Flowcharts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 444

Appendices

A Programming Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 451

B Error and Arithmetic Flag Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 457

C Memory Areas . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 461

D Using the Clock Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 479

E I/O Assignment Sheet . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 481

F Program Coding Sheet . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 483

G List of FAL Numbers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 487

H Extended ASCII . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 489

I CPM1/CPM1A and CQM1 Memory Area Comparison . . . . . . . . . . . . . . . . . . . . 491

Glossary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 493

Index. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 509

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 517

ix

Page 9

Page 10

About this Manual:

This manual describe s programming of the CQM1, CPM1, CPM1A, and SRM1 Programmable Controllers, including memo r y s tr ucture, memory contents, lad der- diagram i nstr uctio ns, etc., an d inclu des

the sections described below. Refer to the CQM1 Operation Manual, CPM1 Operation Manual,

CPM1A Operation Manual, a nd SRM1 Master C ontrol Units Operation Manual for hardware informa-

tion and Programming Co nsole operating procedure s. Refer to the SSS Operation Manual: C-series

PCs for SSS operating procedures.

Note The SRM1 is a specialized p rogrammable controll er and is normally called a CompoBus/S

Master Control Unit. The SRM1, however, is programmed in the sa me way as the other Programmable Controllers and it is treated and referred to as a PC in this manual.

Please read this manual carefully and be sure you understand the information provided before

attempting to program and operate the CQM1, CPM1, CPM1A or SRM1.

Section 1 explains the PC Setup and related PC functions, including interrupt processing and communications. The PC Setup can be used to control the operating parameters of the PC.

Section 2 provides an introduction to new PC features, including the new instructions available

through expansion instructions and a new monitoring feature call differential monitoring.

Section 3 describ es the structure of the PC’s memory areas, and explains how to use them. It also

describes Memory Cassette ope rations use d to transfer data between the CQ M1 and a Me mory Cassette.

Section 4 explai ns the ba si c s tep s an d conc e pts involved in writing a basic ladder diag r a m pr ogram. It

introduces the instr uc tions that are used to build the basic st ru cture of the ladder d iagram and control

its execution.

Section 5 individually des cribes the ladder-di agram programming instruct ions that can be used with

the PC.

Section 6 explains the me thod s and pr oced ur es for using h ost link commands, whi ch can b e u sed for

host link communications via the PC ports.

Section 7 explains the internal processing of the PCs, and the time required for processing and execution. Refer to this section to gain an understanding of the precise timing of PC operation.

Section 8 describes how to diagnose and correct the hardware and software errors that can occur during PC operation.

The following appendices are also provided: A Programming Instructions, B Error and Arithmetic

Flag Operation, C Memory Areas, D Using the Clock Function, E I/O Assignment Sheet,

F Program Coding Sheet, G List of FAL Numbers, H Extended ASCII, an d I CPM1A and CPM1

Memory Area Comparison.

!WARNING Failure to read and understand the informati on provided i n this ma nual may result in p er-

sonal injury or death, damage to th e product, or product failure. Please r ea d ea ch section

in its entirety and be sure you understand the information provided in the section and

related sections before attempting any of the procedures or operations given.

xi

Page 11

Page 12

PRECAUTIONS

This section provides general precautions for using the Programmable Controller (PC) and related devices.

The information contained in this section is important for the safe and reliable application of the Programmable

Controller. You must read this section and understa nd the information contained before attempting to set up or

operate a PC system.

1 Intended Audience . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xiv

2 General Precautions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xiv

3 Safety Precautions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xiv

4 Operating Environment Precautions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xv

5 Application Precautions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xvi

6 Conformance to EC Directives . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xix

xiii

Page 13

Intended Audience 1

1 Intended Audience

This manual is intended for the following personnel, who must also have

knowledge of electrical systems (an electrical engineer or the equivalent).

• Personnel in charge of installing FA systems.

• Personnel in charge of designing FA systems.

• Personnel in charge of managing FA systems and facilities.

2 General Precautions

The user must operate t he product according to t he performance specifications described in the operation manuals.

Before using the product under conditions which are not described in the

manual or applying the produ ct to nuclear control s ystems, railroad systems,

aviation systems, vehicles, combustion systems, me dical equipmen t, amusement machines, safety equipment, and oth er systems, machines, and equi pment that may have a serious influence on lives and property if used

improperly, consult your OMRON representative.

Make sure that the ratings and performan ce charact er is ti cs of the pr od uc t are

sufficient for the systems, machi nes, and equipment, and be sure to provide

the systems, machines, and equipment with double safety mechanisms.

This manual provides informat ion for programming and operat ing the Un it. B e

sure to read this manual before attempting to use the Unit and keep this manual close at hand for reference during operation.

!WARNING It is extremely impor tant th at a PC and all PC Units be u sed for the spe cified

purpose and under the specified conditions, especially in applications that can

directly or indirectly affect human life. You must consult with your OMRON

representative before applying a PC Sy stem to the above-mentioned a pplic ations.

3 Safety Precautions

!WARNING Do not attempt to take any Unit apart while the power is being supplied. Doing

so may result in electric shock.

!WARNING Do not touch any of the termi na ls w hil e the power is being sup pl ied . Doing s o

may result in electric shock.

!WARNING Do not attempt to disassemble, repair, or modify any Units. Any attempt to do

so may result in malfunction, fire, or electric shock.

!Caution Tighten the screws on the ter minal block of the AC Power Supply Unit to the

torque specified in th e manual. Loose screws may result in burning or malfunction.

!Caution Execute online edit only after confirming that no adverse effects will be

caused by extending the cycle time. Other wise, the input signals may not be

readable.

xiv

Page 14

Operating Environment Precautions 4

!Caution Confirm safety at the destination node before transferring a program to

another node or changing t he I/O m emo ry area. Doing eit her of these without

confirming safety may result in injury.

!Caution When connecting the PC t o a personal compute r or other peri pheral device,

either ground the 0-V side of the PC or do not gro und the PC a t all . Alth ough

some grounding method s shor t the 24-V side, as shown in th e following diagram, never do so with the PC.

INCORRECT Grounding: Shorting the 24-V side of the Power Supply

Non-isolated DC power

supply

24 V

0 V 0 V

PC Peripheral device

4 Operating Environment Precautions

!Caution Do not operate the control system in the following locations:

• Locations subject to direct sunlight.

• Locations subject to temperatures or humidity outside the range specified

in the specifications.

• Locations subject to condensation as the result of severe changes in temperature.

• Locations subject to corrosive or flammable gases.

• Locations subject to dust (especially iron dust) or salts.

• Locations subject to exposure to water, oil, or chemicals.

• Locations subject to shock or vibration.

!Caution Take appropriate and sufficient counter measures when installing systems in

the following locations:

0 V

• Locations subject to static electricity or other forms of noise.

• Locations subject to strong electromagnetic fields.

• Locations subject to possible exposure to radioactivity.

• Locations close to power supplies.

!Caution The operating environment of the PC System ca n have a large effect on the

longevity and reliability of the sy stem. Improper operating environme nts can

lead to malfunction, failure, and other unforeseeable problems with the PC

System. Be sure that the op erating environment is within the sp ecified cond itions at installation and remai ns within the specifi ed conditions dur ing the life

of the system.

xv

Page 15

Application Precautions 5

5 Application Precautions

Observe the following precautions when using the PC System.

!WARNING Always heed these precautions. Failure to abide by the following precautions

could lead to serious or possibly fatal injury.

• Always ground the system to 100 Ω or less when installing the Units. Not

connecting to a ground of 100 Ω or less may result in electric shock.

• Always turn OFF the power supply to the PC before attempting any of the

following. Not turning OFF the power supply may result in mal function or

electric shock.

• Mounting or dismounting Power Supply Units, I/O Units, CPU Units,

Memory Cassettes, or any other Units.

• Assembling the Units.

• Setting DIP switches or rotary switches.

• Connecting or wiring the cables.

• Connecting or disconnecting the connectors.

!Caution Failure to abide by the following precautions could lead to faulty operation of

the PC or the system, or could damage the PC or PC Units. Always heed

these precautions.

• Fail-safe measures must be taken by the customer to ensure safety in the

event of incorrect, missing, or abnorm al signals caused by broken signal

lines, momentary power interruptions, or other causes.

• Interlock circuits, limit circuits, and similar safety measures in external circuits (i.e., not in the Programmable Controller) must b e provided by the

customer.

• Always use the power supply voltage sp ecified in the manual. An incorrect voltage may result in malfunction or burning.

• Take appropriate me asures to ensure that the specified power with th e

rated voltage and frequency i s supplied. Be particula rly careful in places

where the power supply is unstable. An incorrect power supply may result

in malfunction.

• Install external breakers and take other safety measures against short-circuiting in exter nal wiring. Insufficient safety measur es against short-circuiting may result in burning.

• Do not apply voltages to the Input Units in excess of the rated input voltage. Excess voltages may result in burning.

• Do not apply voltages or connect lo ads to the Output Units in exces s of

the maximum swi tching capacity. Excess voltage or loads may r esult in

burning.

• Disconnect the functional ground terminal when performing withstand

voltage tests. Not disconnecting the functional ground terminal may result

in burning.

• Install and wire the Unit properly as specified in the manual. Improper

installation of the Unit may result in malfunction.

• Be sure that all the mounting screws , ter min al scre ws, and cable connector screws are tightened to the torque specified in the r elevant manuals.

Incorrect tightening torque may result in malfunction.

xvi

Page 16

Application Precautions 5

• Leave the label attached to the Unit when wiring. Removing the label may

result in malfunction.

• Remove the label after the completion of wiring to ensure proper heat dissipation. Leaving the label attached may result in malfunction.

• Use crimp terminals for wiring. Do not connect bare stranded wires

directly to terminals. Connection of bare stranded wires may result in

burning.

• Double-check all the wiring before turning ON the power supply. Incorrect

wiring may result in burning.

• Mount the Unit only after checking the terminal block completely.

• Be sure that the terminal bloc ks, Memory Units, expansion cables, an d

other items with locking devices are properly locked into place. Improper

locking may result in malfunction.

• Check the user program for proper execution before actually running it on

the Unit. Not checking the program may result in an unexpected operation.

• Confirm that no adverse effect will occur in the system before attemptin g

any of the following. Not doing so may result in an unexpected operation.

• Changing the operating mode of the PC.

• Force-setting/force-resetting any bit in memory.

• Changing the present value of any word or any set value in memory.

• Resume operation only after trans ferring to the new CPU Un it the contents of the DM and HR Areas required for resuming operation. Not doing

so may result in an unexpected operation.

• Do not place objects on top of the cables. Doing so may break the cables.

• Before touching the Unit, be sure to fir s t to uch a grounded metallic obj ec t

in order to discharge any static built-up. Not doing so may result in malfunction or damage.

• Do not touch the Expansion I/O Unit Connectin g Cable while the power is

being supplied in order to prevent any malfunction due to static electricity.

• When replacing parts, be sure to confirm th at the rating of a new part is

correct. Not doing so may result in malfunction or burning.

!Caution Always clear memory before beginning to program the CPM1, CPM1A or

SRM1. Although me mory is clear ed before the CPU Unit is shippe d (except

for bits with specific functi ons), AR 1314, which tur ns ON when the inter nal

capacitor cannot back up memory, may ha ve turned ON during shipment.

!Caution If the CPM1 or CPM1A will be turned OFF for periods exceeding the data

backup period of the internal capacitor, design the system so that it will not be

influenced if data in the DM, HR, and CNT area s is cleared when power is

turned OFF.

!Caution Either switch the CPM1 or CPM1 A to RUN or MONITOR mode, or turn OFF

and ON power to the CPM1 or CPM1A after chang ing from a Programming

Device any data that is backed up in flas h memory. Thi s data includes the

user program, read-only DM area (DM 6144 to DM 6599), and the PC Setup

(DM 6600 to DM 6655).

xvii

Page 17

Application Precautions 5

• The user program and memory area data in the CPM 1 or CPM1A are

backed up either by an inter nal capa citor or in f lash memory as shown i n

the following table.

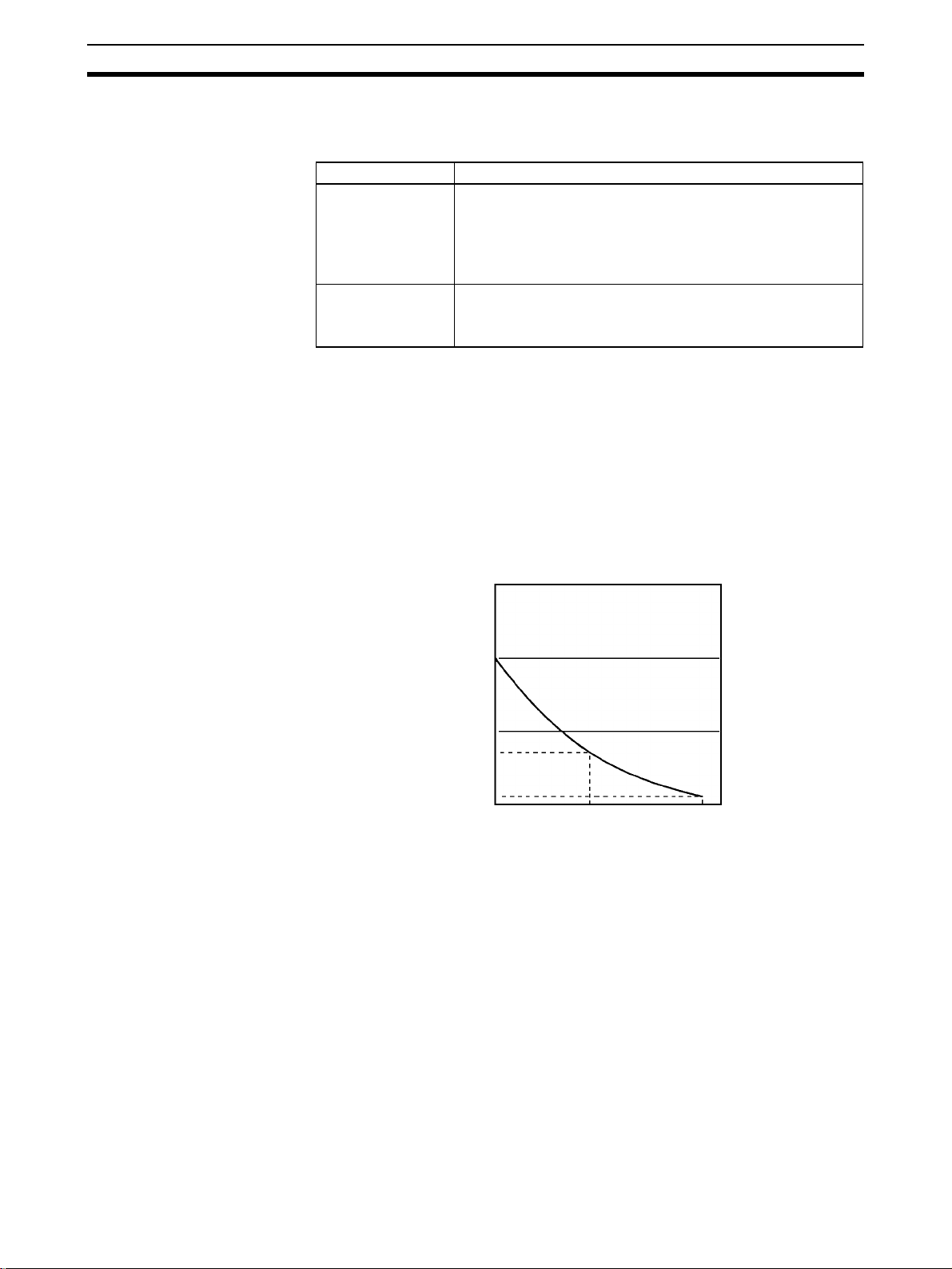

Backup method Data

Internal capacitor Read/write DM area (DM 0000 to DM 0999, DM 1022, and

Flash memory User program

DM 1023)

Error log area (DM 1000 to DM 1021)

HR area (HR 00 to HR 19)

Counter area (CNT 000 to CNT 127)

Read-only DM area (DM 6144 to DM 6599)

PC Setup (DM 6600 to DM 6655)

Note

1. The IR, TR, LR, and ti mer areas are not no rmall y ba cked up when power

is turned OFF and all contents will be cleared the next time power is turned

ON. (The PC Setup s et ting in DM 660 1 c an be us ed t o ba ck up thi s data.

Refer to details on the PC Setup later in this manual for details.)

2. The bits in the AR and SR areas have special functions and are set according to these functions when power is turned ON.

• The capacitor backup time depends on the ambient temperature, as

shown in the following graph. The backup time, however, assumes that

the capacitor is fu lly charged, which requires t hat power be supplied to

the CPU Unit continuously for at least 15 minutes.

20

10

Backup time (days)

7

1

25 40 80

Ambient temperature (°C)

xviii

If the power remains OFF for a period exceeding the data backup period,

AR 1314 will turn ON to indicate that the capacitor can no longer back up data

and the data backed up by the capacitor will be cleared. AR 13 14 will rem ain

ON unless it i s tu rned OFF using I/O monitor ope rati ons, us ing m emo ry clear

operations, or from the user program.

If desired, the PC Setu p setting in DM 6604 can be set to cr eate a fatal error

and thus stop the system when AR 1314 goes ON.

• The data stored in flash memory will not be lost even if power remains

OFF for a period exceeding the data backup period, because the data

stored in flash memor y will be read to the CPU Unit when the CPM1 or

CPM1A is turned ON.

• If the power is turned OFF without changing the mode from PROGRAM

mode to RUN or MONITOR mode after having made changes in the data

that is backed up in flash memory, the changes wi ll no t be written to flas h

memory. If the power is then left OFF for more than 20 days (at 25

°C), the

Page 18

Conformance to EC Directives 6

changes (i.e., the contents of the RAM) will be erased and the data values

will become undefined.

!Caution Be sure that the SRM1 syste m is not influe nced by any undefined data if the

data in the DM, HR, or CNT area is c leare d wh en t he S RM1 ha s b een turned

OFF for a period exceeding the data backup period of the internal lithium battery. If the AR 1414 flag is ON, the dat a will be held unles s it is turne d OFF

using the I/O Monito r ope ration, in structions, etc. The s yst em can be stopped

by designating DM 6604 in the PC Setup so that a memory error occurs when

the power interruption hold area is not held (with AR 1314 ON)

• A lithium battery in the C PU Unit is used to back up the counter values

and the contents of the DM area, and HR ar ea. The deterioration of the

lithium batter y capacity depends o n the ambient temperature. T he standard service life is 12 years at an ambient temperature of 40°C when

operating 8 hours a day.

If the power remains off for a per iod exceeding the data backup per iod, the

contents of the Data Memory (DM), Hold Relay (HR), and Counter (CNT)

Areas in the CPU Un it may be cleared and the A R 1314 flag (which t urns ON

when the power interruption hold area is not held) may turn ON.

If the contents of th e CP U Un it’s program area are lo st, the pr ogram sto re d i n

flash memory will be r ead to th e CPU Unit’s program area when the SRM 1 is

started up because the contents in the read-only area (DM 6144 through

DM 6599) and PC Setup (DM 6600 through DM 6655) will be written to flash

memory.

• However, if the power is turned OFF without changing the mod e even if

changes are made in the read-only DM area (DM 6144 through DM

6599), or PC Setup (DM 6600 through DM 6655) using a peripheral

device, the contents of changes will not be written to flash memory.

Although the data in thes e areas is backed up by the lithium battery, contents of changes will disappear if the service life of the lithium battery

expires. In this case, programs in the fl ash memor y will be automa tically

read into the user program memory.

The changes can be saved by switching the SRM1 to RUN or MONITOR

mode or turning OFF and restarting the SRM1 soon after the changes are

made.

6 Conformance to EC Directives

The CQM1 PCs comp ly with EC Directives. To ensure tha t the machine or

device i n w h ich a C QM1 P C i s us ed c omp li es w i th EC D i re ct ives, the PC must

be installed as follows:

1,2,3... 1. The PC must be installed within a control panel.

2. Reinforced insulation or double insulation must be used for the DC power

supplies used for the communications and I/O power supplies.

3. PCs complying with EC Directives also conform to the Common Emission

Standard (EN50081-2). When a PC is built into a machine, however, noise

can be generated by switching devices us in g r el ay outputs and ca us e th e

overall machine to fail to meet the Stan dard. If this occurs, surge kil lers

must be connected or other measures taken external to the PC.

The following methods represent typical met hods for reduc ing noise, and

may not be sufficient in all cases. Required countermeasures will vary de-

xix

Page 19

Conformance to EC Directives 6

pending on the devices connected to the con trol pa nel , wiring, the configuration of the system, and other conditions.

Determining if Countermeasures Are Required

Refer to EN50081-2 for more details.

Countermeasur es are not required if the f requency of load switching for the

whole system including the PC is less than 5 times per minute.

Countermeasures are required if the frequency of load switching for the whole

system including the PC is more than 5 times per minute.

Countermeasure Examples

When switching an inductive load, co nne ct a n su r ge pr ot ec tor, diodes, etc., in

parallel with the load or contact as shown below.

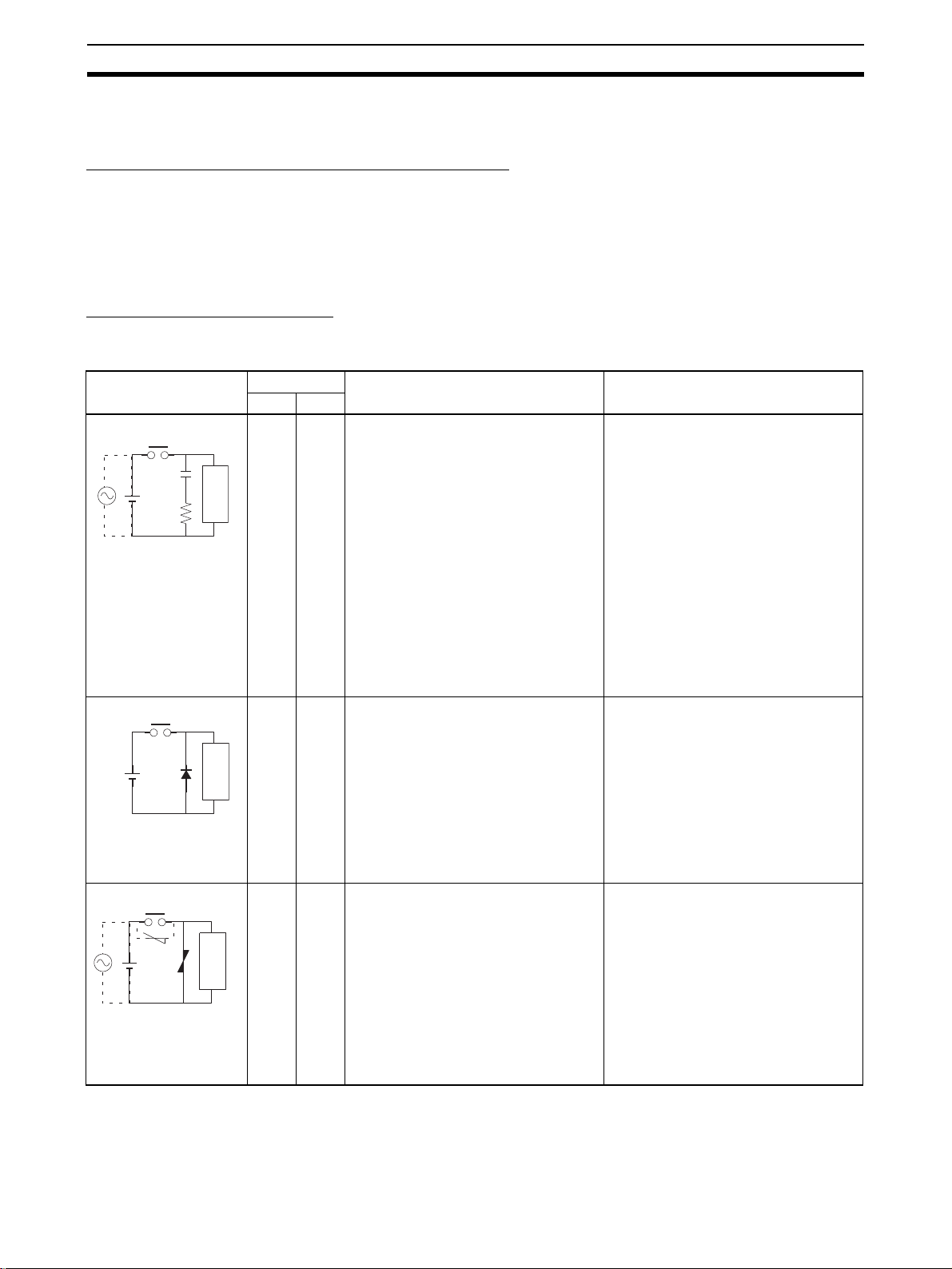

Circuit Current Characteristic Required element

AC DC

CR method

Power

supply

Diode method

Power

supply

Varistor method

Power

supply

Yes Yes If the load is a relay or solenoid, there

is a time lag between the moment the

circuit is opened and the moment the

load is reset.

If the supply voltage is 24 or 48 V,

Inductive

load

No Yes The diode connected in parallel with

Inductive

load

Yes Yes The varistor method prevents the impo-

Inductive

load

insert the surge protector in parallel

with the load. If the supply voltage is

100 to 200 V, insert the surge protector

between the contacts.

the load changes energy accumulated

by the coil into a current, which then

flows into the coil so that the current

will be converted into Joule heat by the

resistance of the inductive load.

This time lag, b etw een the moment the

circuit is opened and the moment the

load is reset, caused by this method is

longer than that caused by the CR

method.

sition of high voltage between the contacts by using the constant voltage

characteristic of the varistor. There is

time lag between the moment the circuit is opened an d the moment the load

is reset.

If the supply voltage is 24 or 48 V,

insert the varistor in parallel with the

load. If the supply v o ltage is 100 to 2 00

V, insert the varistor between the contacts.

The capacitance of the capacitor must

be 1 to 0.5 µF per contact current of

1 A and resistance of the resistor must

be 0.5 to 1 Ω per c ontact v ol tage of 1V.

These values, however, vary with the

load and the characteristics of the

relay. Decide these values from tes ting,

and take into consideration that the

capacitance suppresses spark discharge when the contacts are separated and the resistance limits the

current that flows into the load when

the circuit is closed again.

The dielectric strength of the capacitor

must be 200 to 300 V. If the circuit is an

AC circuit, use a capacitor with no

polarity.

The reversed dielectric strength value

of the diode must be at least 10 times

as large as the circuit voltage value.

The forward current of the diode must

be the same as or larger than the load

current.

The reversed dielectric strength value

of the diode may be two to three times

larger than the supply voltage if the

surge protector is applied to electronic

circuits with low circuit voltages.

---

xx

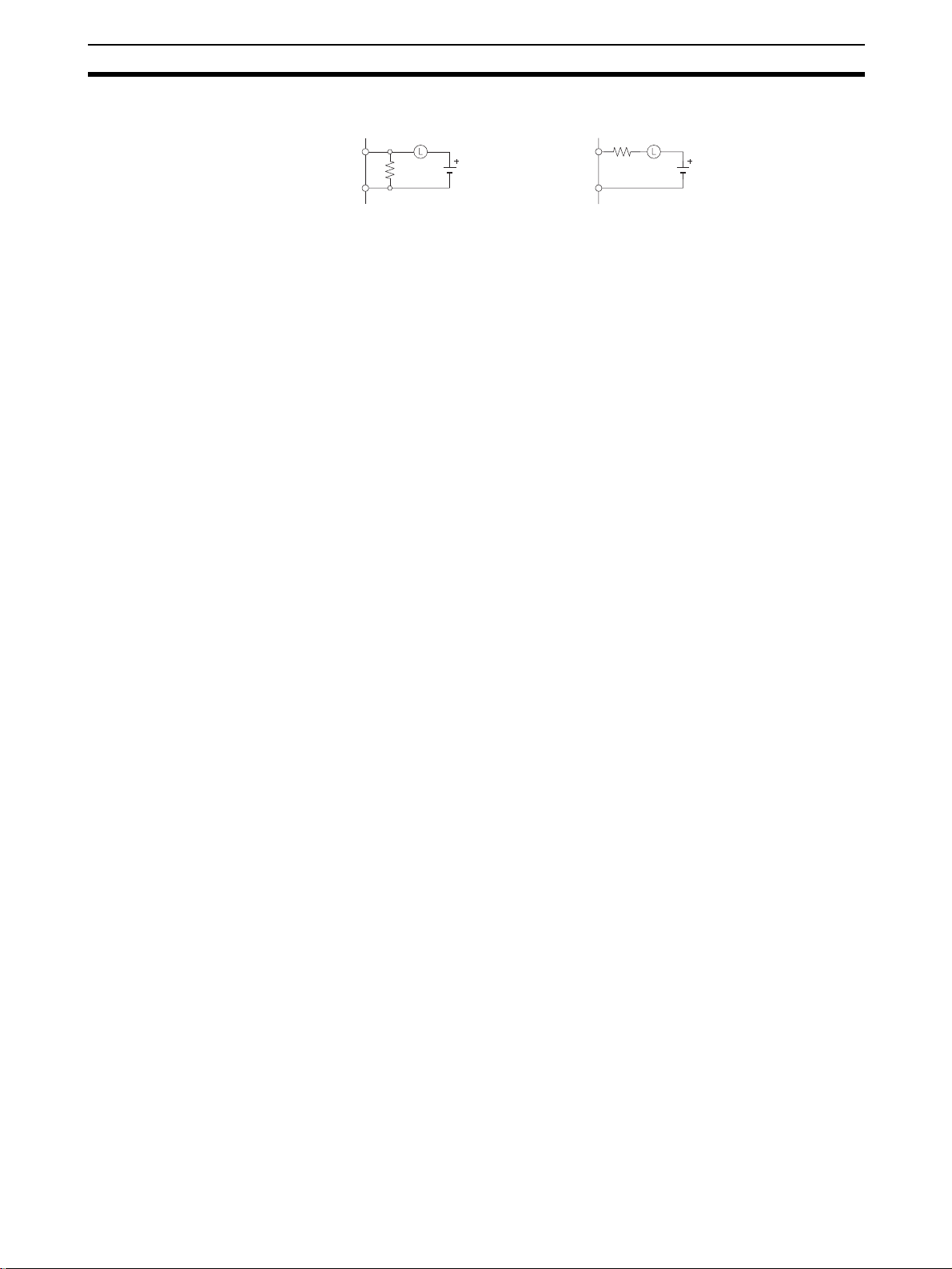

When switching a load with a high inr ush current, such as an incandes cent

lamp, suppress the inrush current as shown below.

Page 20

Conformance to EC Directives 6

g

r

Countermeasure 1

OUT

R

COM

Providing a dark current of approx.

one-third of the rated value

throu

h an incandescent lamp

Countermeasure 2

R

OUT

COM

Providing a limiting resisto

xxi

Page 21

Conformance to EC Directives 6

xxii

Page 22

SECTION 1

PC Setup and Other Features

This section explains the PC Setup and other CQM1 /CPM1/CPM1A/SRM1 featur es, including interrupt processing and

communications. The PC Setup can be used to control the operating parameters of the CQM1/CPM1/CPM1A/SRM1. To

change the PC Setup, refer to the CQM1 Operation Manual, CPM1 Operation Manual, CPM1A Operation Manual or

SRM1 Master Control Units Operation Manual for Programming Console procedu res. Refer to the SSS O peration M anual:

C-series PCs for SSS procedures.

If you are not familiar with OMRON PCs or ladder diagram program, you can read 1-5 PC Setup as an overview of the

operating parameters available for the CQM1/CPM1/CPM1A/SRM1, but may then want to read SECTION 3 M emory

Areas, SECTION 4 Ladder-diagram Programming, and related instructions in Section SECTION 5 Instruction Set before

completing this section.

1-1 PC Setup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

1-1-1 Changing the PC Setup. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

1-1-2 CQM1 PC Setup Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

1-1-3 CPM1/CPM1A PC Setup Settings . . . . . . . . . . . . . . . . . . . . . . . . . . 9

1-1-4 SRM1 PC Setup Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

1-2 Basic PC Operation and I/O Processes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

1-2-1 Startup Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

1-2-2 Hold Bit Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

1-2-3 Program Memory Write-protection (CPM1/CPM1A Only). . . . . . . 17

1-2-4 RS-232C Port Servicing Time (CQM1/SRM1 Only). . . . . . . . . . . . 18

1-2-5 Peripheral Port Servicing Time. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

1-2-6 Cycle Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

1-2-7 Input Time Constants . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

1-2-8 High-speed Timers (CQM1 Only) . . . . . . . . . . . . . . . . . . . . . . . . . . 20

1-2-9 DSW(87) Input Digits & Output Refresh Method (CQM1 On l y) . . 21

1-2-10 Error Log Settings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

1-3 Pulse Output Function (CQM1 Only). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

1-3-1 Types of Pulse Outputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

1-3-2 Standard Pulse Output from an Output Point. . . . . . . . . . . . . . . . . . 23

1-3-3 Standard Pulse Output from Ports 1 and 2 . . . . . . . . . . . . . . . . . . . . 25

1-3-4 Variable-duty-ratio Pulse Output from Ports 1 and 2 . . . . . . . . . . . . 32

1-3-5 Determining the Status of Ports 1 and 2. . . . . . . . . . . . . . . . . . . . . . 34

1-4 Pulse Output Function (CPM1A Only). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

1-4-1 Programming Example in Continuous Mode. . . . . . . . . . . . . . . . . . 36

1-4-2 Programming Example in Independent Mode . . . . . . . . . . . . . . . . . 36

1-4-3 Using Pulse Output Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

1-4-4 Changing the Frequency. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

1-4-5 Stopping Pulse Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

1-5 CQM1 Interrupt Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

1-5-1 Types of Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

1-5-2 Input Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

1-5-3 Masking All Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

1-5-4 Interval Timer Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

1-5-5 High-speed Counter 0 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

1-5-6 High-speed Counter 0 Overflows/Underflows . . . . . . . . . . . . . . . . . 53

1-5-7 High-spee d Counter 1 and 2 Interrupts (CQM1-CPU43-EV1) . . . . 55

1-5-8 Absolute High-speed Counter Interrupts (CQM1-CPU44-EV1). . . 62

1

Page 23

1-6 CPM1/CPM1A Interrupt Functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

1-6-1 Types of Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

1-6-2 Input Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

1-6-3 Masking All Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

1-6-4 Interval Timer Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

1-6-5 High-speed Counter Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

1-7 SRM1 Interrupt Functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

1-7-1 Types of Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

1-7-2 Interval Timer Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

1-8 CompoBus/S Distributed I/O Functions (SRM1 Only). . . . . . . . . . . . . . . . . . 88

1-9 Communications Functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

1-9-1 CQM1 PC Setup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

1-9-2 Wiring Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

1-9-3 CQM1 Host Link Communications . . . . . . . . . . . . . . . . . . . . . . . . . 93

1-9-4 CPM1/CPM1A Host Link Communications. . . . . . . . . . . . . . . . . . . 95

1-9-5 SRM1 Host Link Communications. . . . . . . . . . . . . . . . . . . . . . . . . . 97

1-9-6 RS-232C Communications (CQM1/SRM1 Only) . . . . . . . . . . . . . . 100

1-9-7 CQM1 One-to-one Link Communications . . . . . . . . . . . . . . . . . . . . 102

1-9-8 CPM1/CPM1A One-to-one Link Communications . . . . . . . . . . . . . 104

1-9-9 CPM1/CPM1A NT Link Communications. . . . . . . . . . . . . . . . . . . . 1 05

1-9-10 SRM1 One-to-one Link Communications . . . . . . . . . . . . . . . . . . . . 106

1-9-11 SRM1 NT Link Communications. . . . . . . . . . . . . . . . . . . . . . . . . . . 108

1-9-12 SRM1 No Protocol Communications . . . . . . . . . . . . . . . . . . . . . . . . 109

1-9-13 Tr ansmission Data Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

1-9-14 Tr ansmission Flags . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

1-9-15 No Protocol Communications Program Example. . . . . . . . . . . . . . . 112

1-10 Calculating with Signed Binary Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

1-10-1 Definition of Signed Binary Data . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

1-10-2 Arithmetic Flags . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

1-10-3 Inputting Signed Binary Data Using Decimal Values. . . . . . . . . . . . 115

1-10-4 Using Signed-binary Expansion Instructions (CQM1 Only) . . . . . . 115

1-10-5 Application Example Using Signed Binary Data . . . . . . . . . . . . . . . 116

2

Page 24

PC Setup Section 1-1

1-1 PC Setup

The PC Setup compr ises various operating parameters that contro l CQM1/

CPM1/CPM1A/SRM1 operation. In order to make the maximum use of

CQM1/CPM1/CPM1A/SRM1 functionality when using interrupt processing

and communications fu nctions, the PC Setup may be customized accor ding

to operating conditions.

At the time of shipping, the defaults are set for general operating conditions,

so that the CQM1/CPM1/CPM1A/SRM1 can be used without having to

change the settings. You are, however, advised to check the default values

before operation.

Default Values The default values for the PC Setup are 0000 for all words. The default values

can be reset at any time by turning ON SR 25210.

!Caution When data memory (DM) is cleared from a Programming Device, the PC

Setup settings will also be cleared to all zeros.

1-1-1 Changing the PC Setup

PC Setup settings are accessed at various times depending on the setting, as

described below.

• DM 6600 to DM 6614: Accessed only when PC’s power supply is turned

on.

• DM 6615 to DM 6644: Accessed only when program execution begins.

• DM 6645 to DM 6655: Accessed regularly when the power is on.

Since changes in the PC Setup become effective only at the times given

above, the CQM1/CPM1/CPM1A/SRM1 will have to be restarted to make

changes in DM 6600 to DM 6614 effective, and program execution will have to

be restarted to make changes in DM 6615 to DM 6644 effective.

When DM 6602 bits 00 to 03 are set to protect the program memory , DM 6602

cannot be changed using the PC Setup operation of the Support Software. To

change DM 6602, use the I/O Monitor or DM Edit operation.

Making Changes from a

Peripheral Device

The PC Setup can be read, but not wr itten into, from the user program. Writing can be done only by using a Programming Device.

Although the PC Se tup is stored in DM 6600 to DM 665 5, settings can be

made and changed only from a Programming Device (e.g., SSS, or Programming Console). DM 6600 to DM 6644 can be set or changed only while in

PROGRAM mode. DM 6645 to DM 6655 can be set or changed while in either

PROGRAM mode or MONITOR mode.

The following settings can be made in PROGRAM mode from the SSS us ing

menu operations. All other se ttin gs must b e ma de u sing th e hexadeci ma l s etting operation.

• Startup Mode (DM 6600)

• I/O Hold Bit Status and Forced Status Hold Bit Status (DM 6601)

• Cycle Monitor Time (DM 6618)

• Cycle Time (DM 6619)

• RS-232C Port Settings (DM 6645 to DM 6649)

Note The RS-232C Port Setti ngs (DM 6645 to DM 6649) are no t used in CPM1/

CPM1A PCs because these PCs aren’t equipped with an RS-232C port.

3

Page 25

PC Setup Section 1-1

Errors in the PC Setup If an incorrect PC Setup settin g is acc essed, a non-fatal error (er ror code 9B)

will be generated, the c orresponding error flag (AR 2400 to AR 2402 in th e

CQM1, AR 1300 to AR 1302 in the CPM1/ CPM1A/SRM1) wil l be turned ON ,

and the default setting will be used instead of the incorrect setting.

1-1-2 CQM1 PC Setup Settings

The PC Setup is broadly divided into four categories: 1) Settings rela ted to

basic CQM1 operation and I/O proces ses, 2) Settin gs related to pulse o utput

functions, 3) Settings re lated to in terr upts, and 4) Set tings related t o communications. This section wi ll explain the settings according to these classifications.

The following table shows the setting in order in the DM area. For details, refer

to the page numbers shown.

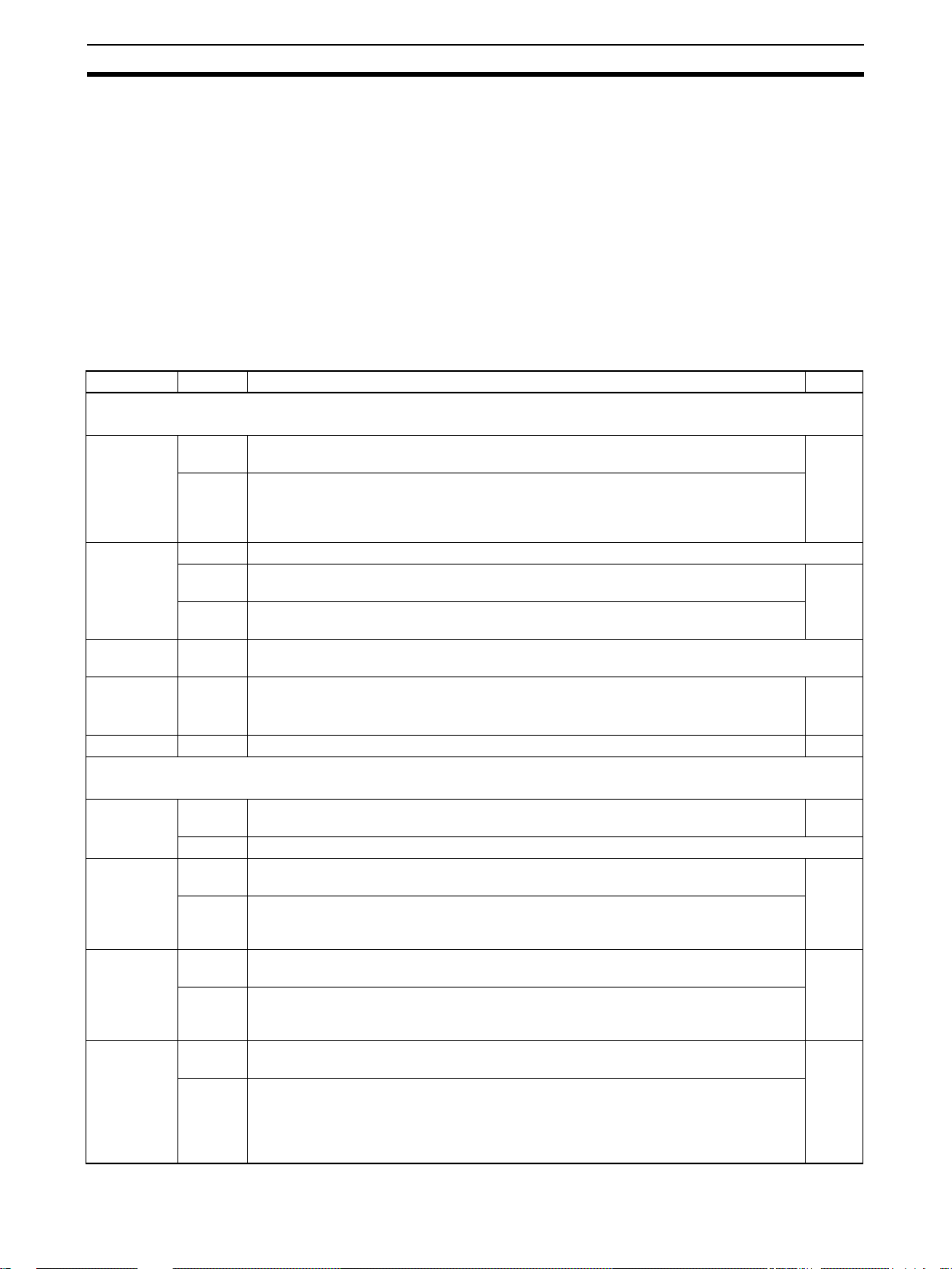

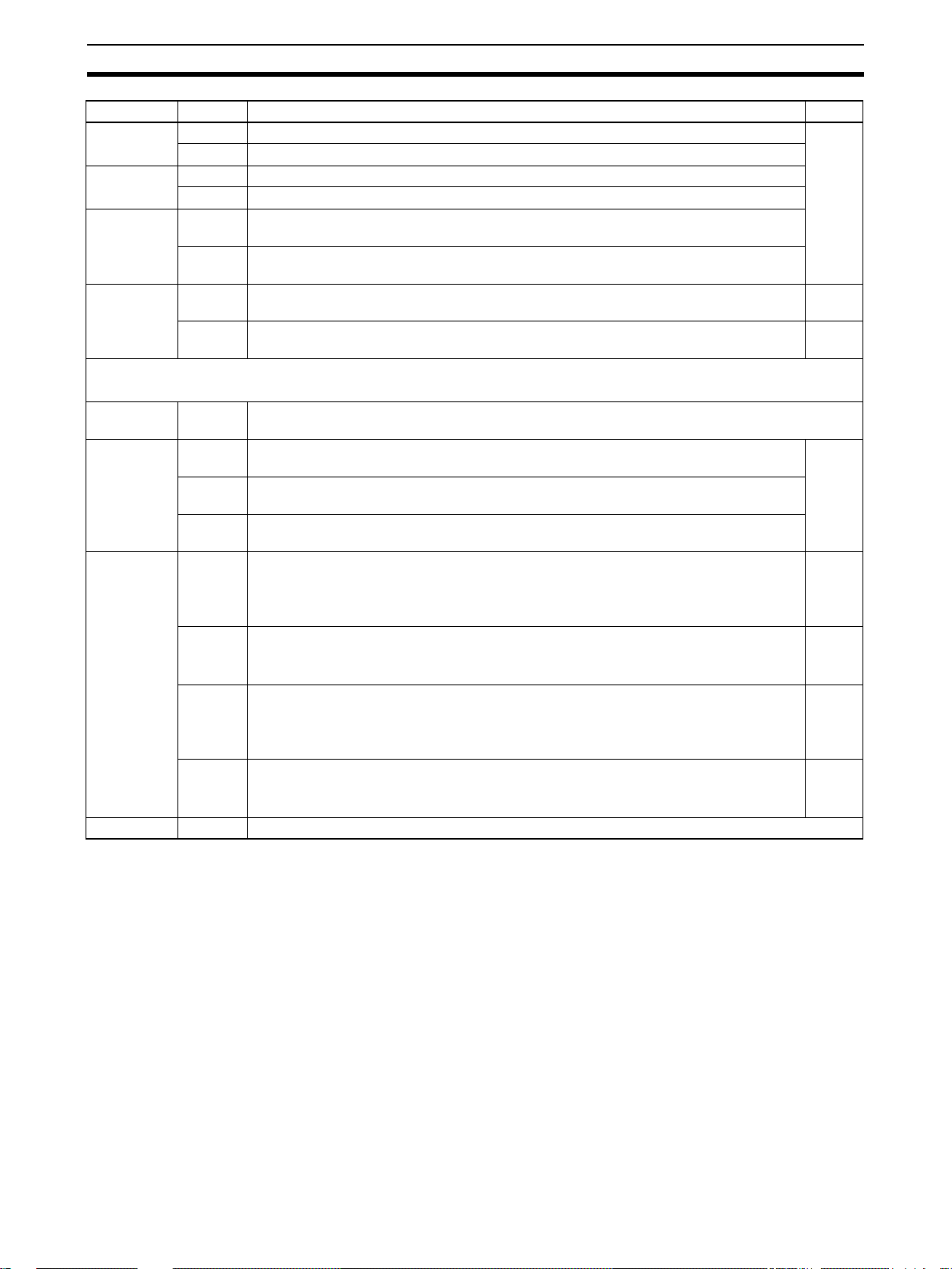

Word(s) Bit(s) Function Page

Startu p Processing (DM 6600 to DM 6614)

The following settings are effective after transfer to the PC only after the PC is restarted.

DM 6600 00 to 07 Startup mode (effective when bits 08 to 15 are set to 02).

00: PROGRAM; 01: MONITOR 02: RUN

08 to 15 Startup mode designation

00: Programming Console switch

01: Continue operating mode last used before power was turned off

02: Setting in 00 to 07

DM 6601 00 to 07 Not used.

08 to 11 IOM Hold Bit (SR 25212) Status

0: Reset; 1: Maintain

12 to 15 Forced Status Hold Bit (SR 25211) Status

DM 6602 to

DM 6610

DM 6611 00 to 15 CQM1-CPU43-EV1: Mode setting for ports 1 and 2

DM 6612 00 to 15 CQM1-CPU44-EV1: Origin compensation setting for port 2 (4-digit BCD) 63

Pulse Output and Cycle Time Settings (DM 6615 to DM 6619)

The following settings are effective after transfer to the PC the next time operation is started.

DM 6615 00 to 07 Word for pulse output.

DM 6616 00 to 07 Servicing time for RS-232C port (effective when bits 08 to 15 are set to 01)

DM 6617 00 to 07 Servicing time for peripheral port (effective when bits 08 to 15 are set to 01)

DM 6618 00 to 07 Cycle monitor time (effective when bits 08 to 15 are set to 01, 02, or 03)

00 to 15 Not used.

08 to 15 Not used.

08 to 15 RS-232C port servicing setting enable

08 to 15 Peripheral port servicing setting enable

08 to 15 Cycle monitor enable (Setting in 00 to 07 x unit; 99 s max.)

0: Reset; 1: Maintain

0000: High-speed counter mode; 0001: Pulse output mode

CQM1-CPU44-EV1: Origin compensation setting for port 1 (4-digit BCD)

00: IR 100; 01: IR101; 02: IR 102... 15: IR 115

00 to 99 (BCD): Percentage of cycle time used to service RS-232C port.

00: 5% of the cycle time

01: Use time in 00 to 07.

00 to 99 (BCD): Percentage of cycle time used to service peripheral.

00: 5% of the cycle time

01: Use time in 00 to 07.

00 to 99 (BCD): Setting (see 08 to 15)

00: 120 ms (setting in bits 00 to 07 disabled)

01: Setting unit: 10 ms

02: Setting unit: 100 ms

03: Setting unit: 1 s

16

17

25, 63

24

18

18

21

4

Page 26

PC Setup Section 1-1

Word(s) Bit(s) Function Page

DM 6619 00 to 15 Cycle time

0000: Variable (no minimum)

0001 to 9999 (BCD): Minimum time in ms

Interrupt Processing (DM 6620 to DM 6639)

The following settings are effective after transfer to the PC the next time operation is started.

DM 6620 00 to 03 Input constant for IR 00000 to IR 00007

0: 8 ms; 1: 1 ms; 2: 2 ms; 3: 4 ms; 4: 8 ms; 5: 16 ms; 6: 32 ms; 7: 64 ms; 8: 128 ms

04 to 07 Input constant for IR 00008 to IR 00015 (Setting same as bits 00 to 03)

08 to 15 Input constant for IR 001

00: 8 ms; 01: 1 ms; 02: 2 ms ; 03 : 4 m s; 04: 8 ms; 05: 16 ms; 06: 32 ms; 07: 64 ms; 08:

128 ms

DM 6621 00 to 07 Input constant for IR 002 (Setting same as for IR 001.)

08 to 15 Input constant for IR 003 (Setting same as for IR 001.)

DM 6622 00 to 07 Input constant for IR 004 (Setting same as for IR 001.)

08 to 15 Input constant for IR 005 (Setting same as for IR 001.)

DM 6623 00 to 07 Input constant for IR 006 (Setting same as for IR 001.)

08 to 15 Input constant for IR 007 (Setting same as for IR 001.)

DM 6624 00 to 07 Input constant for IR 008 (Setting same as for IR 001.)

08 to 15 Input constant for IR 009 (Setting same as for IR 001.)

DM 6625 00 to 07 Input constant for IR 010 (Setting same as for IR 001.)

08 to 15 Input constant for IR 011 (Setting same as for IR 001.)

DM 6626 00 to 07 Input constant for IR 012 (Setting same as for IR 001.)

08 to 15 Input constant for IR 013 (Setting same as for IR 001.)

DM 6627 00 to 07 Input constant for IR 014 (Setting same as for IR 001.)

08 to 15 Input constant for IR 015 (Setting same as for IR 001.)

DM 6628 00 to 03 Interrupt enable for IR 00000 (0: Normal input; 1: Interrupt input) 40

04 to 07 Interrupt enable for IR 00001 (0: Normal input; 1: Interrupt input)

08 to 11 Interrupt enable for IR 00002 (0: Normal input; 1: Interrupt input)

12 to 15 Interrupt enable for IR 00003 (0: Normal input; 1: Interrupt input)

DM 6629 00 to 07 Number of high-speed timers for interrupt refreshing

00 to 15 (BCD; e.g., set 15 for 00 to 14)

08 to 15 High-speed timer interrupt refresh enable

00: 16 timers (setting in bits 00 to 07 disabled)

01: Use setting in 00 to 07

DM 6630 00 to 07 First input refresh word for I/O interrupt 0: 00 to 11 (BCD) 40

08 to 15 Number of input refresh words for I/O interrupt 0: 00 to 12 (BCD)

DM 6631 00 to 07 First input refresh word for I/O interrupt 1: 00 to 11 (BCD)

08 to 15 Number of input refresh words for I/O interrupt 1: 00 to 12 (BCD)

DM 6632 00 to 07 First input refresh word for I/O interrupt 2: 00 to 11 (BCD)

08 to 15 Number of input refresh words for I/O interrupt 2: 00 to 12 (BCD)

DM 6633 00 to 07 First input refresh word for I/O interrupt 3: 00 to 11 (BCD)

08 to 15 Number of input refresh words for I/O interrupt 3: 00 to 12 (BCD)

DM 6634 00 to 07 First input refresh word for high-speed counter 1: 00 to 11 (BCD) 40

08 to 15 Number of input refresh words for high-speed counter 1: 00 to 12 (BCD)

DM 6635 00 to 07 First input refresh word for high-speed counter 1: 00 to 11 (BCD) 40

08 to 15 Number of input refresh words for high-speed counter 1: 00 to 12 (BCD)

18

19

20

5

Page 27

PC Setup Section 1-1

Word(s) Bit(s) Function Page

DM 6636 00 to 07 First input refresh word for interval timer 0: 00 to 07 (BCD) 45, 50

08 to 15 Number of input refresh words for interval timer 0: 00 to 08 (BCD)

DM 6637 00 to 07 First input refresh word for interval timer 1: 00 to 07 (BCD)

08 to 15 Number of input refresh words for interval timer 1: 00 to 08 (BCD)

DM 6638 00 to 07 First input refresh word for interval timer 2 (also used for high-speed counter 0): 00 to

08 to 15 Number of input refresh words for interval timer 2: 00 to 08 (BCD)

DM 6639 00 to 07 Output refresh method

08 to 15 Number of digits for DIGITAL SWITCH (DSW(87)) instruction

High-speed Counter Settings (DM 6640 to DM 6644)

The following settings are effective after transfer to the PC the next time operation is started.

DM 6640,

DM 6641

DM 6642 00 to 03 High-speed counter 0 mode

DM 6643 00 to 03 CQM1-CPU43-EV1: Port 1 input setting

DM 6644 00 to 15 Port 2 settings (Identical to the port 1 settings in DM 6643.)

00 to 15 Not used.

04 to 07 High-speed counter 0 reset mode

08 to 15 High-speed counter 0 enable

04 to 07 CQM1-CPU43-EV1: Por t 1 reset setting

08 to 11 CQM1-CPU43-EV1: Por t 1 counting mode setting

12 to 15 CQM1-CPU43-EV1: Por t 1 pulse type setting

07 (BCD)

(also used for high-speed counter 0)

21, 393

00: Cyclic; 01: Direct

21, 124

00: 4 digits; 01: 8 digits

50

0: Up/down counter mode; 4: Incrementing counter mode

0: Z phase and software reset; 1: Software reset only

00: Don’t use high-speed counter; 01: Use high-speed counter with settings in 00 to 07

55, 62

0: Differential phase input; 1: Pulse/Direction input; 2: Up/Down input

CQM1-CPU44-EV1: Port 1 input setting

0: 8-bit input; 1: 10-bit input; 2: 12-bit input

57

0: Z phase and software reset; 1: Software reset only

CQM1-CPU44-EV1: Not used. Set to 0.

56, 62

0: Linear mode; 1: Ring mode

CQM1-CPU44-EV1: Port 1 mode setting

0: BCD mode; 1: 360° mode

25, 32

0: Standard pulse output (0.5 duty ratio); 1: Variable-duty-ratio pulse output

CQM1-CPU44-EV1: Not used. Set to 0.

6

Page 28

PC Setup Section 1-1

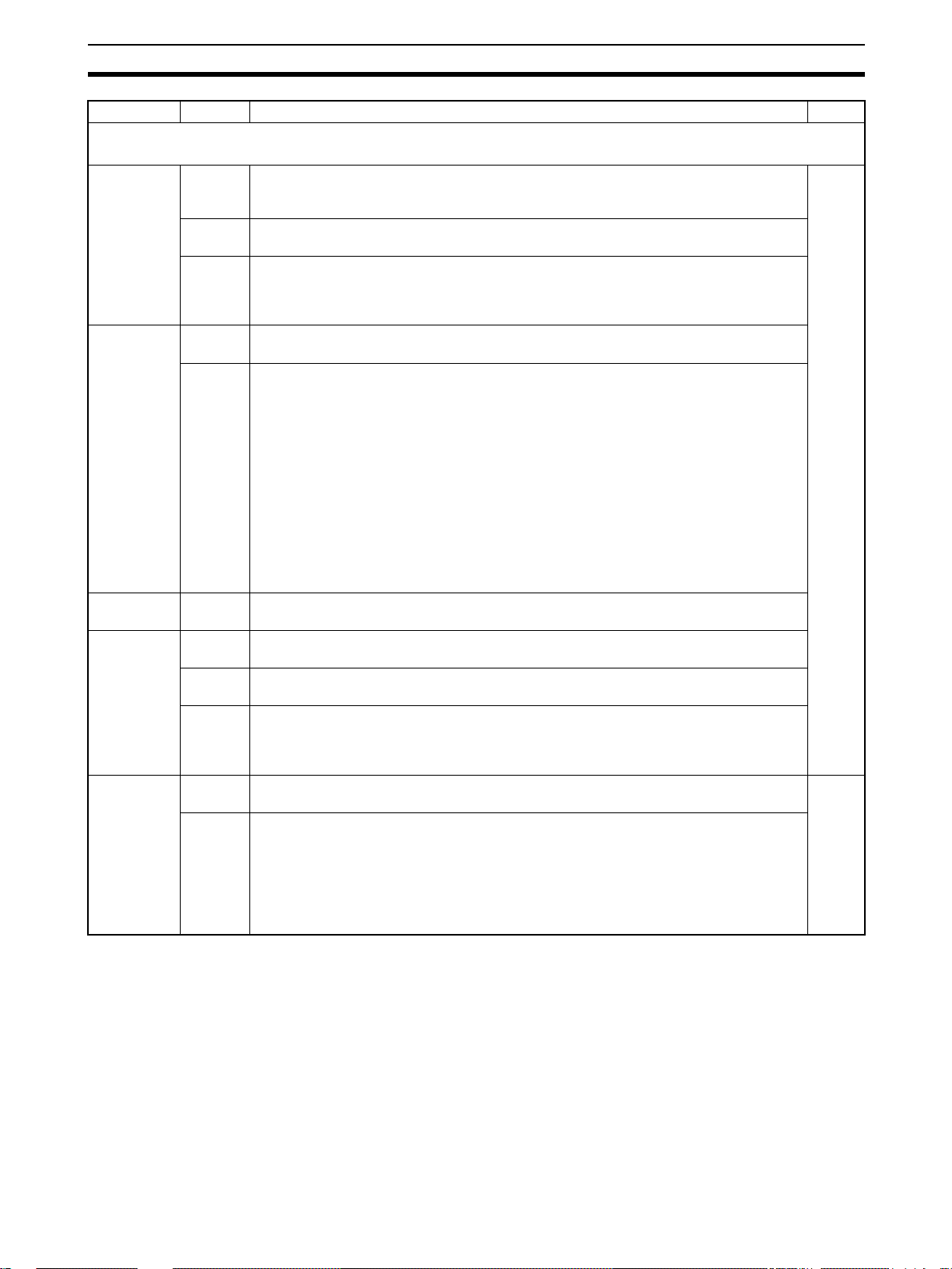

Word(s) Bit(s) Function Page

RS-232C Port Settings

The following settings are effective after transfer to the PC.

DM 6645 00 to 07 Port settings

00: Standard (1 start bit, 7-bit data, even parity, 2 stop bits, 9,600 bps)

01: Settings in DM 6646

08 to 11 Link words for 1:1 link (Effective when bits 12 to 15 are set to 3.)

0: LR 00 to LR 63; 1: LR 00 to LR 31; 2: LR 00 to LR 15

12 to 15 Communications mode

0: Host link; 1: RS-232C (no protocol); 2: 1:1 data link slave; 3: 1:1 data link master;

4: NT Link (1:1) (NT Link setting is only applicable to the CQM1-CPU4@-EV1 CPU

Units.)

DM 6646 00 to 07 Baud rate

00: 1.2K, 01: 2.4K, 02: 4.8K, 03: 9.6K, 04: 19.2K

08 to 15 Frame format

Start Length Stop Parity

00: 1 bit 7 bits 1 bit Even

01: 1 bit 7 bits 1 bit Odd

02: 1 bit 7 bits 1 bit None

03: 1 bit 7 bits 2 bit Even

04: 1 bit 7 bits 2 bit Odd

05: 1 bit 7 bits 2 bit None

06: 1 bit 8 bits 1 bit Even

07: 1 bit 8 bits 1 bit Odd

08: 1 bit 8 bits 1 bit None

09: 1 bit 8 bits 2 bit Even

10: 1 bit 8 bits 2 bit Odd

11: 1 bit 8 bits 2 bit None

DM 6647 00 to 15 Transmission delay (Host Link)

0000 to 9999 (BCD): Set in units of 10 ms, e.g., setting of 0001 equals 10 ms

DM 6648 00 to 07 Node number (Host link, effective when bits 12 to 15 of DM 6645 are set to 0.)

00 to 31 (BCD)

08 to 11 Start code enable (RS-232C, effective when bits 12 to 15 of DM 6645 are set to 1.)

0: Disable; 1: Set

12 to 15 End code enable (RS-232C, effective when bits 12 to 15 of DM 6645 are set to 1.)

0: Disable (number of bytes received)

1: Set (specified end code)

2: CR, LF

DM 6649 00 to 07 Start code (RS-232C)

00 to FF (binary)

08 to 15 When bits 12 to 15 of DM 6648 are set to 0:

Number of bytes received

00: Default setting (256 bytes)

01 to FF: 1 to 255 bytes

When bits 12 to 15 of DM 6648 are set to 1:

End code (RS-232C)

00 to FF (binary)

90

90

7

Page 29

PC Setup Section 1-1

Word(s) Bit(s) Function Page

Peripheral Port Settings

The following settings are effective after transfer to the PC.

These settings are effective when a CQM1-CIF01 Connecting Cable is used.

They are not effective when a CQM1-CIF11 Connecting Cable or Programming Console is used.

DM 6650 00 to 07 Port settings

00: Standard (1 start bit, 7-bit data, even parity, 2 stop bits, 9,600 bps)

01: Settings in DM 6651

08 to 11 Not used.

12 to 15 Communications mode

0: Host link; 1: RS-232C

DM 6651 00 to 07 Baud rate

00: 1.2K, 01: 2.4K, 02: 4.8K, 03: 9.6K, 04: 19.2K

08 to 15 Frame format

Start Length Stop Parity

00: 1 bit 7 bits 1 bit Even

01: 1 bit 7 bits 1 bit Odd

02: 1 bit 7 bits 1 bit None

03: 1 bit 7 bits 2 bit Even

04: 1 bit 7 bits 2 bit Odd

05: 1 bit 7 bits 2 bit None

06: 1 bit 8 bits 1 bit Even

07: 1 bit 8 bits 1 bit Odd

08: 1 bit 8 bits 1 bit None

09: 1 bit 8 bits 2 bit Even

10: 1 bit 8 bits 2 bit Odd

11: 1 bit 8 bits 2 bit None

DM 6652 00 to 15 Transmission delay (Host Link)

0000 to 9999: In ms.

DM 6653 00 to 07 Node number (Host link, effective when bits 12 to 15 of DM 6650 are set to 0.)

00 to 31 (BCD)

08 to 11 Start code enable (RS-232C, effective when bits 12 to 15 of DM 6650 are set to 1.)

0: Disable; 1: Set

12 to 15 End code enable (RS-232C, effective when bits 12 to 15 of DM 6650 are set to 1.)

0: Disable (number of bytes received)

1: Set (specified end code)

2: CR, LF

DM 6654 00 to 07 Start code (RS-232C, effective when bits 08 to 11 of DM 6653 are set to 1.)

00 to FF (binary)

08 to 15 When bits 12 to 15 of DM 6653 are set to 0:

Number of bytes received

00: Default setting (256 bytes)

01 to FF: 1 to 255 bytes

When bits 12 to 15 of DM 6653 are set to 1:

End code (RS-232C)

00 to FF (binary)

90

90

Error Log Settings (DM 6655)

The following settings are effective after transfer to the PC.

DM 6655 00 to 03 Style

0: Shift after 10 records have been stored

1: Store only first 10 records (no shifting)

2 to F: Do not store records

04 to 07 Not used.

08 to 11 Cycle time monitor enable

0: Detect long cycles as non-fatal err ors

1: Do not detect long cycles

12 to 15 Low battery error enable

0: Detect low battery voltage as non-fatal error

1: Do not detect low batter voltage

8

22

22

Page 30

PC Setup Section 1-1

1-1-3 CPM1/CPM1A PC Setup Settings

The PC Setup is broadly divided into four categories: 1) Settings rela ted to

basic PC operation and I/O processes, 2) Settings related to the cycle time, 3)

Settings related to inter r upt s, and 4) S ettings re la ted to c ommun icati ons. This

section will explain the settings according to these classifications.

The following table shows the settings for CPM1/CPM1A PCs in o rder. Refer

to the page number in the last column for more details on that setting.

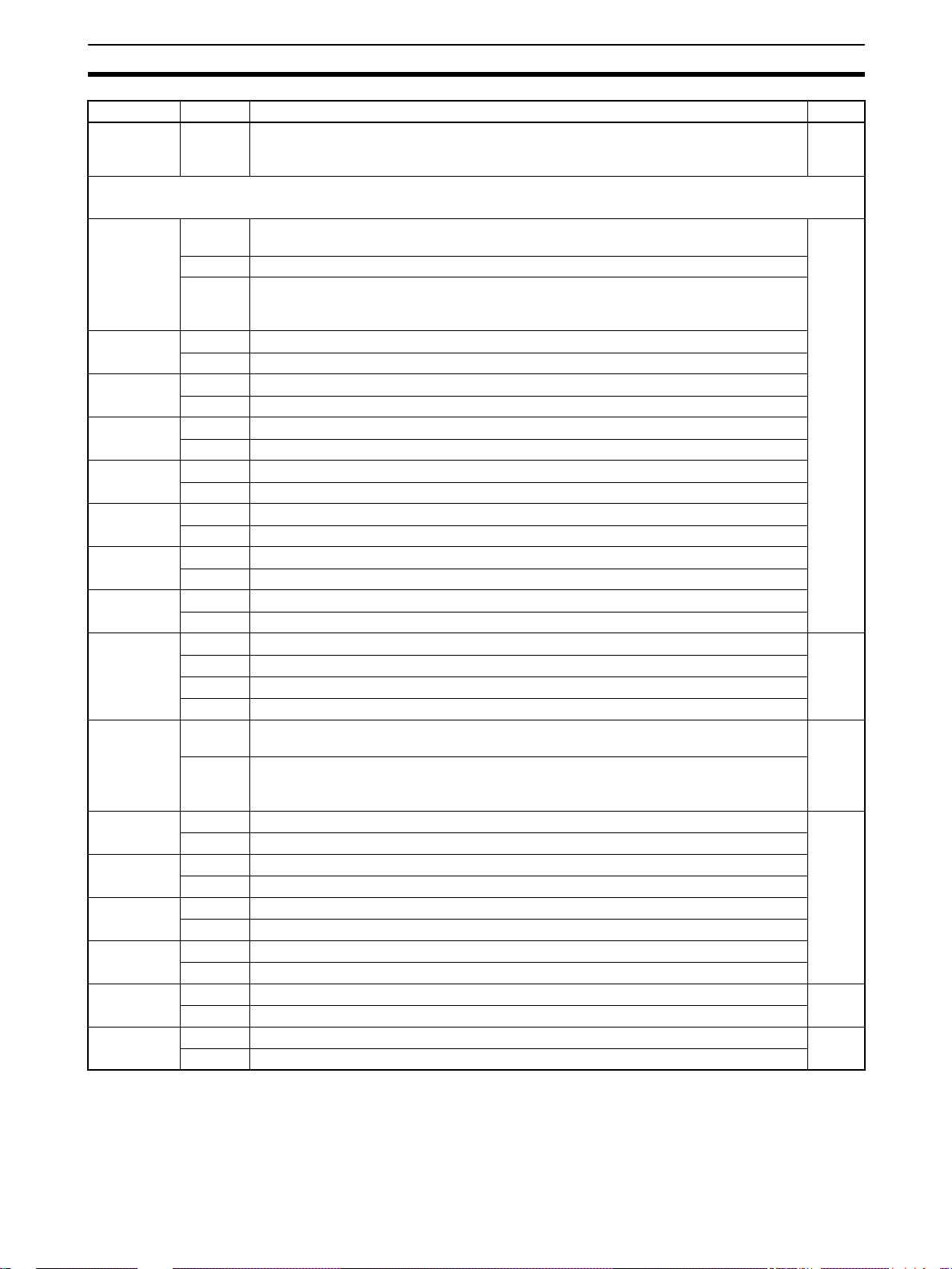

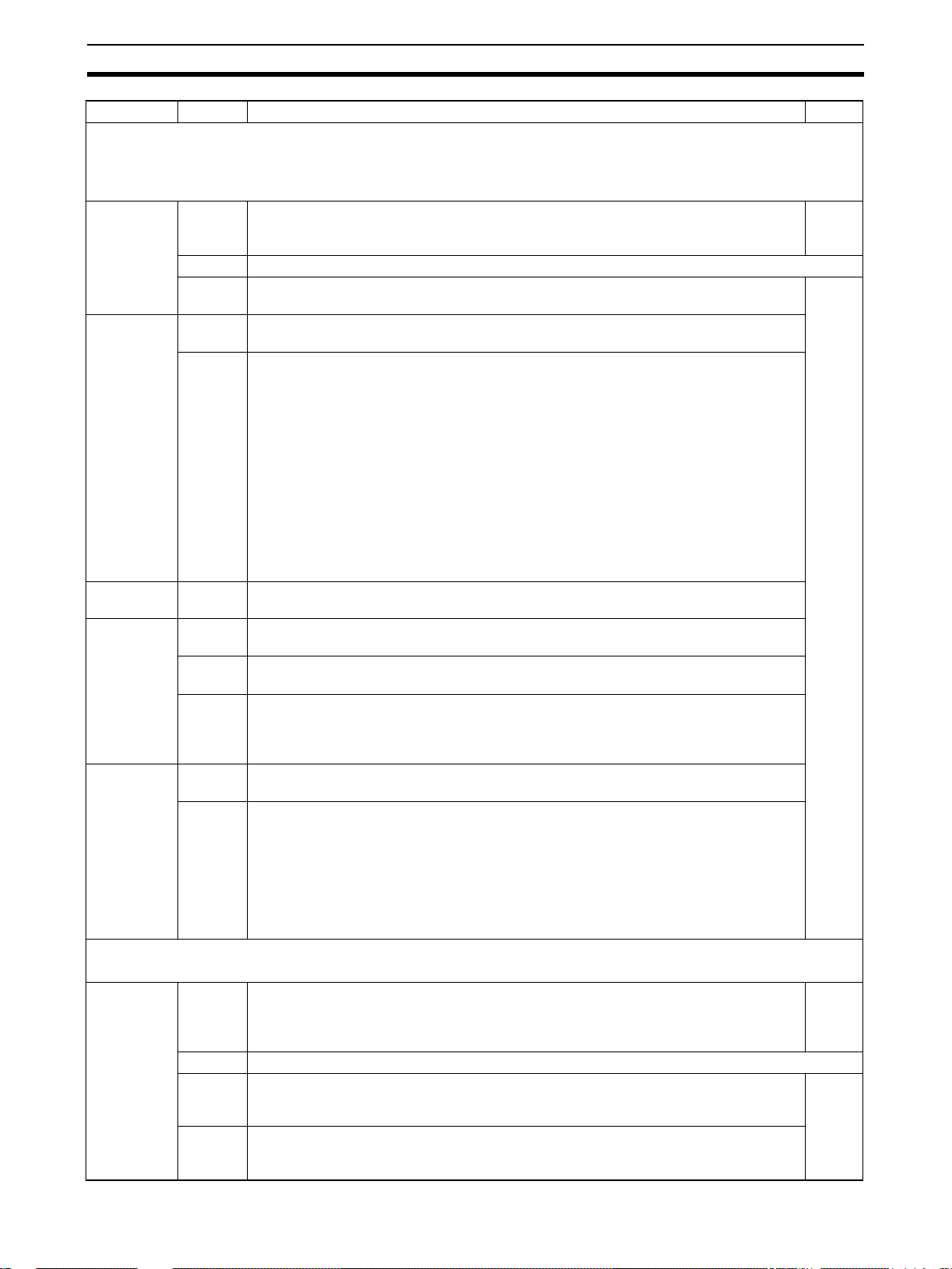

Word(s) Bit(s) Function Page

Startu p Processing (DM 6600 to DM 6614)

The following settings are effective after transfer to the PC only after the PC is restarted.

DM 6600 00 to 07 Startup mode (effective when bits 08 to 15 are set to 02).

08 to 15 Startup mode designation

DM 6601 00 to 07 Not used. 17

08 to 11 IOM Hold Bit (SR 25212) Status at Startup

12 to 15 Forced Status Hold Bit (SR 25211) Status at Startup

DM 6602 00 to 03 Program memory write-protection

04 to 07 Programming Console display language

08 to 15 Not used.

DM 6603 00 to 15 Not used.

DM 6604 00 to 07 00: If data could not be saved with the built-in capacitor (AR 1314 ON), a memory error will not

08 to 15 Not used.

DM 6605 to

DM 6614

Cycle Time Settings (DM 6615 to DM 6619)

The following settings are effective after transfer to the PC the next time operation is started.

DM 6615,

DM 6616

DM 6617 00 to 07 Servicing time for peripheral port (effective when bits 08 to 15 are set to 01)

DM 6618 00 to 07 Cycle monitor time (effective when bits 08 to 15 are set to 01, 02, or 03)

DM 6619 00 to 15 Cycle time

00 to 15 Not used.

00 to 15 Not used.

08 to 15 Peripheral port servicing setting enable

08 to 15 Cycle monitor enable (Setting in 00 to 07 x unit; 99 s max.)

00: PROGRAM; 01: MONITOR 02: RUN

00: Programming Console switch

01: Continue operating mode last used before power was turned off. (See note 1.)

02: Setting in 00 to 07

0: Reset; 1: Maintain (See note 3.)

0: Reset; 1: Maintain (See note 3.)

0: Program memory unprotected

1: Program memory write-protected (except DM 6602 itself)

0: English; 1: Japanese

be generated.

01: If data could not be saved with the built-in capacitor (AR 1314 ON), a memory error will be

generated.

00 to 99 (BCD): Percentage of cycle time used to service peripheral.

00: 5% of the cycle time

01: Use time in 00 to 07.

00 to 99 (BCD): Setting (see 08 to 15)

00: 120 ms (setting in bits 00 to 07 disabled)

01: Setting unit: 10 ms

02: Setting unit: 100 ms

03: Setting unit: 1 s

0000: Variable (no minimum)

0001 to 9999 (BCD): Minimum time in ms

16

17

18

21

18

9

Page 31

PC Setup Section 1-1

Word(s) Bit(s) Function Page

Interrupt Processing (DM 6620 to DM 6639)

The following settings are effective after transfer to the PC the next time operation is started.

DM 6620 00 to 03 Input constant for IR 00000 to IR 00002

04 to 07 Input constant for IR 00003 and IR 00004 (Setting same as bits 00 to 03)

08 to 11 Input constant for IR 00005 and IR 00006 (Setting same as bits 00 to 03)

12 to 15 Input constant for IR 00007 and IR 00011 (Setting same as bits 00 to 03)

DM 6621 00 to 07 Input constant for IR 001

08 to 15 Input constant for IR 002 (Setting same as for IR 001.)

DM 6622 00 to 07 Input constant for IR 003 (Setting same as for IR 001.)

08 to 15 Input constant for IR 004 (Setting same as for IR 001.)

DM 6623 00 to 07 Input constant for IR 005 (Setting same as for IR 001.)

08 to 15 Input constant for IR 006 (Setting same as for IR 001.)

DM 6624 00 to 07 Input constant for IR 007 (Setting same as for IR 001.)

08 to 15 Input constant for IR 008 (Setting same as for IR 001.)

DM 6625 00 to 07 Input constant for IR 009 (Setting same as for IR 001.)

08 to 15 Not used.

DM 6626 to

DM 6627

DM6628 00 to 03 Interrupt enable for IR 00003 (0: Normal input; 1: Interrupt input; 2: Quick-response) 40

DM 6629 to

DM 6641

High-speed Counter Settings (DM 6640 to DM 6644)

The following settings are effective after transfer to the PC the next time operation is started.

DM 6640 to

DM 6641

DM 6642 00 to 03 High-speed counter mode

DM 6643,

DM 6644

00 to 15 Not used.

04 to 07 Interrupt enable for IR 00004 (0: Normal input; 1: Interrupt input; 2: Quick-response)

08 to 11 Interrupt enable for IR 00005 (0: Normal input; 1: Interrupt input; 2: Quick-response)

12 to 15 Interrupt enable for IR 00006 (0: Normal input; 1: Interrupt input; 2: Quick-response)

00 to 15 Not used. 40

00 to 15 Not used.

04 to 07 High-speed counter reset mode

08 to 15 High-speed counter enable

00 to 15 Not used.

0: 8 ms; 1: 1 ms; 2: 2 ms; 3: 4 ms; 4: 8 ms; 5: 16 ms; 6: 32 ms; 7: 64 ms; 8: 128 ms

00: 8 ms; 01: 1 ms; 02: 2 ms; 03: 4 ms; 04: 8 ms; 05: 16 ms ; 06: 32 ms; 07: 64 ms ; 08:

128 ms

0: Up/down counter mode; 4: Incrementing counter mode

0: Z phase and software reset; 1: Software reset only

00: Don’t use high-speed counter; 01: Use high-speed counter with settings in 00 to 07

19

50

10

Page 32

PC Setup Section 1-1

Word(s) Bit(s) Function Page

Peripheral Port Settings

The following settings are effective after transfer to the PC.

DM 6645 to

DM 6649

DM 6650 00 to 07 Port settings

DM 6651 00 to 07 Baud rate

DM 6652 00 to 15 Transmission delay (Host Link) (See note 4.)

DM 6653 00 to 07 Node number (Host link)

DM 6654 00 to 15 Not used.

Error Log Settings (DM 6655)

The following settings are effective after transfer to the PC.

DM 6655 00 to 03 Style

00 to 15 Not used. 90

00: Standard (1 start bit, 7-bit data, even parity, 2 stop bits, 9,600 bps)

01: Settings in DM 6651

(Other settings will cause a non-fatal error and AR 1302 will turn ON.)

08 to 11 Link area for one-to-one PC link via peripheral port:

0: LR 00 to LR 15

12 to 15 Communications mode

0: Host link; 2: One-to-one PC link (slave); 3: One-to-one PC link (master); 4: NT Link

(Other settings will cause a non-fatal error and AR 1302 will turn ON.)

00: 1.2K, 01: 2.4K, 02: 4.8K, 03: 9.6K, 04 : 19.2K, 0 5 to 07 : Cannot b e used (see note 2)

(Other settings will cause a non-fatal error and AR 1302 will turn ON.)

08 to 15 Frame format

Start Length Stop Parity

00: 1 bit 7 bits 1 bit Even

01: 1 bit 7 bits 1 bit Odd

02: 1 bit 7 bits 1 bit None

03: 1 bit 7 bits 2 bit Even

04: 1 bit 7 bits 2 bit Odd

05: 1 bit 7 bits 2 bit None

06: 1 bit 8 bits 1 bit Even

07: 1 bit 8 bits 1 bit Odd

08: 1 bit 8 bits 1 bit None

09: 1 bit 8 bits 2 bit Even

10: 1 bit 8 bits 2 bit Odd

11: 1 bit 8 bits 2 bit None

(Other settings will cause a non-fatal error and AR 1302 will turn ON.)

0000 to 9999: In ms.

(Other settings will cause a non-fatal error and AR 1302 will turn ON.)

00 to 31 (BCD)

(Other settings will cause a non-fatal error and AR 1302 will turn ON.)

08 to 15 Not used.

22

0: Shift after 7 records have been stored

1: Store only first 7 records (no shifting)

2 to F: Do not store records

04 to 07 Not used.

08 to 11 Cycle time monitor enable

0: Detect long cycles as non-fatal err ors

1: Do not detect long cycles

12 to 15 Not used.

Note 1. When the startup mode is set to continue the operating mode last used be-

fore the power was turned off, that operatin g mo de wil l be r et ain ed by the

built-in capacitor. If the power remains off for longer than the backup time

of the capacitor, the data may be lost. (For details on the holding time, refer

to the CPM1A or CPM1 Operation Manual.)

11

Page 33

PC Setup Section 1-1

2. Do not set to “05” to “07.” If set to this value , the CPM1/CPM1A will not operate properly and the RUN PC Setup Error Flag (AR 1302 O N) will not

turn ON.

3. Retention of IOM Hold Bit (SR 25212) Status

If the “IOM Hold Bit Status at Startup” (D M 6601, bits 08 to 11) is set to

“Maintain” with the IOM Hold Bit (SR 25212) turned ON, operation can be

started w ith the I/O m emor y (I/O, IR, LR) status j ust as it was before the

power was turned OFF. ( The input area is ref reshed at star tup, however,

so it is overwritten by the most recently updated input status.)

Retention of Forced Status Hold Bit (SR 25211) Status

If the “Forced Status Hold Bit Status at Startup” (DM 6601, bits 12 to 15) is

set to “Maintain” with the Forced Status Hold Bit (SR 2521 1) turned O N,

operation can be star ted with the forced set/reset status ju st as it was before the power was turned OFF. (When starting up in RUN Mode, however,

the forced set/reset status is cleared.)

Even if the “IOM Hold Bit Status at Startup” or “Forced Status Hold Bit Status at Startup” is set to “Maintain,” the IOM Hold Bit (SR 25212) or Forced

Status Hold Bit (SR 25211) status may be cleared if the power remains

OFF for longer than the b ackup time of the built-i n capacitor. (For details

on the holding t ime, refer to the CPM1A or CPM1 Operation Manual.) At

this time the I/O memory will also be cleared, so set up the system so that

clearing the I/O memory will not cause problems.

4. The transmission delay is the delay between the previous transmission

and the next transmission.

Host computer

Programmable Controller

Command

Command

Response

Transmission delay time

Response

5. If an out-of-range value is set, the following communications conditions will

result. In that case, reset the value so that it is within the permissible range.

Communications mode: Host Link

Communications format: Standard settings

(1 start bit, 7-bit data; even parity, 2 stop bits,

9,600 bps)

Transmission delay: No

Node number: 00

12

Page 34

PC Setup Section 1-1

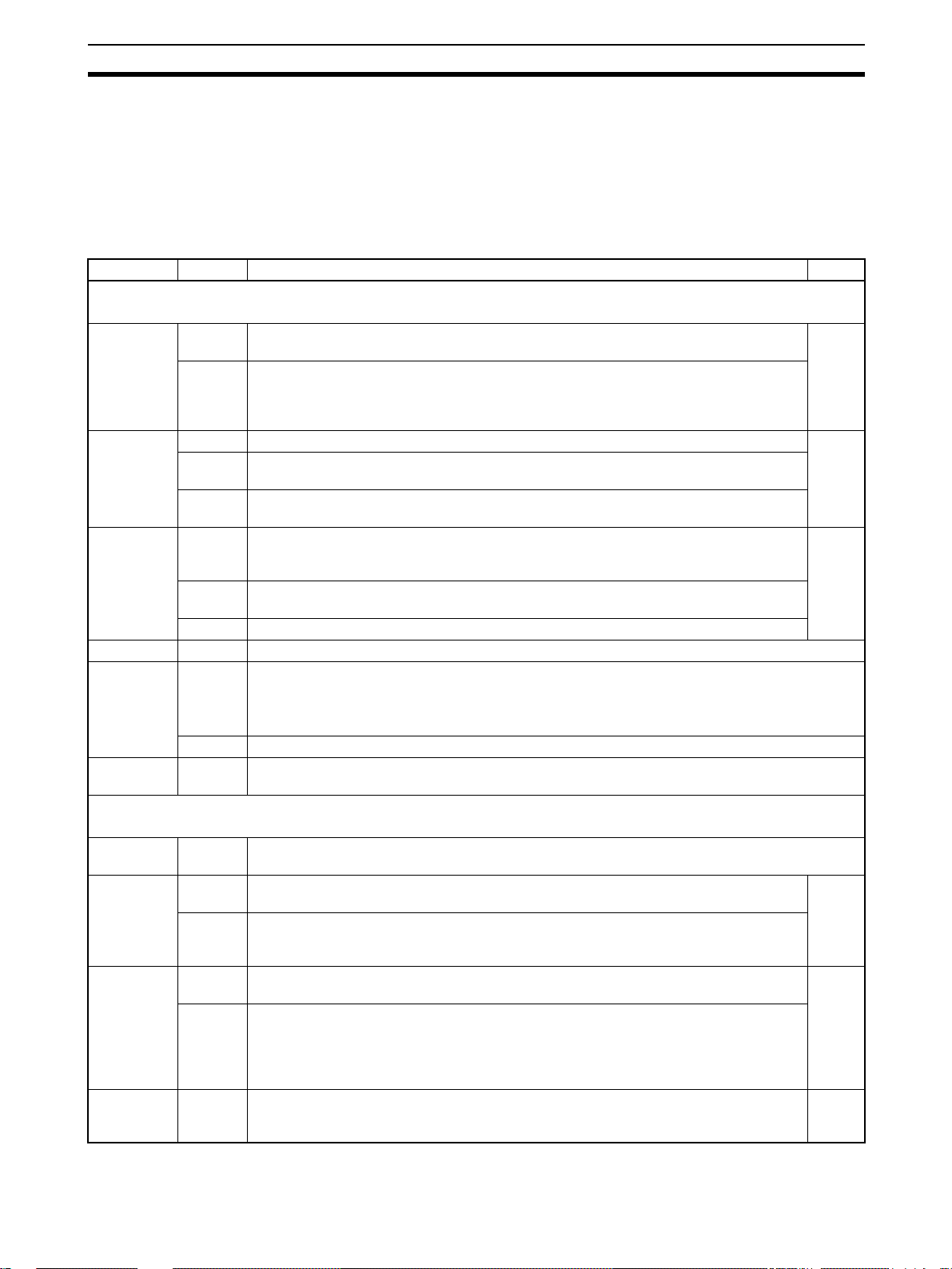

1-1-4 SRM1 PC Setup Settings

The PC Setup is broadly divided into three categor ies: 1) Settings rel ated to

basic PC operation and I/O pr ocesses, 2) Settings related to the cycle time,

and 3) Settings related to co mmunications. This section will explain the settings according to these classifications.

The following table shows the settings for SRM1 PCs in order. Refer to the

page number in the last column for more details on that setting.

Word(s) Bit(s) Function Page

Startu p Processing (DM 6600 to DM 6614)

The following settings are effective after transfer to the PC only after the PC is restarted.

DM 6600 00 to 07 Startup mode (effective when bits 08 to 15 are set to 02).

08 to 15 Startup mode designation

DM 6601 00 to 07 Not used. 17

08 to 11 IOM Hold Bit (SR 25212) Status

12 to 15 Forced Status Hold Bit (SR 25211) Status

DM 6602 00 to 03 Program memory write-protection

04 to 07 Programming Console display language

08 to 11 Expansion Instructions

12 to 15 Not used.

DM 6603 00 to 03 Maximum number of CompoBus/S devices

04 to 15 Not used.

DM 6604 00 to 07 00: If data could not be sa ved for a po w e r i nterrupti on (AR 1314 ON), a memory error will not be

08 to 15 Not used.

DM 6605 to

DM 6614

Cycle Time Settings (DM 6615 to DM 6619)

The following settings are effective after transfer to the PC the next time operation is started.

DM 6615 00 to 15 Not used.

DM 6616 00 to 07 Servicing time for RS-232C port (effective when bits 08 to 15 are set)

DM 6617 00 to 07 Servicing time for peripheral port (effective when bits 08 to 15 are set to 01)

00 to 15 Not used.

08 to 15 RS-232C port servicing enable

08 to 15 Peripheral port servicing setting enable

00: PROGRAM; 01: MONITOR 02: RUN

00: Programming Console switch

01: Continue operating mode last used before power was turned off

02: Setting in 00 to 07

0: Reset; 1: Maintain (See caution on page page 17.)

0: Reset; 1: Maintain

0: Program memory unprotected

1: Program memory write-protected (except DM 6602 itself)

0: English; 1: Japanese

0: Default settings; 1: User settings

0: Max. no. 32

1: Max. no. 16

generated.

01: If data could not be saved for a power interruption (AR 1314 ON), a memory error will be

generated.

00 to 99 (BCD): Percentage for cycle time used to service peripheral.

00: 5% of the cycle time

01: Use time in 00 to 07.

00 to 99 (BCD): Percentage of cycle time used to service peripheral.

00: 5% of the cycle time

01: Use time in 00 to 07.

16

17

18

18

13

Page 35

PC Setup Section 1-1

Word(s) Bit(s) Function Page

DM 6618 00 to 07 Cycle monitor time (effective when bits 08 to 15 are set to 01, 02, or 03)

08 to 15 Cycle monitor enable (Setting in 00 to 07 x unit; 99 s max.)

DM 6619 00 to 15 Cycle time

DM 6620 to

DM 6644

RS-232C Port Settings

The following settings are effective after transfer to the PC.

DM 6645 00 to 03 Port settings

DM 6646 00 to 07 Baud rate

DM 6647 00 to 15 Transmission delay (Host Link)

DM 6648 00 to 07 Node number (Host link, effective when bits 12 to 15 of DM 6645 ar e set to 0.)

DM 6649 00 to 07 Start code (RS-232C)

00 to 15 Not used.

04 to 07 CTS control settings

08 to 11 Link words for 1:1 link

12 to 15 Communications mode

08 to 15 Frame format

08 to 11 Start code enable (RS-232C, effective when bits 12 to 15 of DM 6645 are set to 1.)

12 to 15 End code enable (RS-232C, effective when bits 12 to 15 of DM 6645 are set to 1.)

08 to 15 When bits 12 to 15 of DM 6648 are set to 0:

00 to 99 (BCD): Setting (see 08 to 15)

00: 120 ms (setting in bits 00 to 07 disabled)

01: Setting unit: 10 ms

02: Setting unit: 100 ms

03: Setting unit: 1 s

0000: Variable (no minimum)

0001 to 9999 (BCD): Minimum time in ms

0: Standard (1 start bit, 7-bit data, even parity, 2 stop bits, 9,600 bps)

1: Settings in DM 6646

0: Disable; 1: Set

0: LR 00 to LR 15; Other: Not effective