E2E1026-27-Y4

¡ Semiconductor MSM66101

¡ Semiconductor

This version: Jan. 1998

Previous version: Nov. 1996

MSM66101

OLMS-66K Series 16-Bit Microcontroller

GENERAL DESCRIPTION

The MSM66101 is a high performance microcontroller that employs OKI original nX-8/100 CPU

core. This chip includes a 16-bit CPU, ROM, RAM, I/O ports, multifunction 16-bit timers, 10bit A/D converter, serial I/O port, and pulse width modulator (PWM).

FEATURES

• 64K address space for program memory : Internal ROM : 12K bytes

• 64K address space for data memory : Internal RAM : 384 bytes

• High-speed execution

Minimum cycle for instruction : 400ns @ 10MHz

• Powerful instruction set : Instruction set superior in orthogonal matrix

8/16-bit data transfer instructions

8/16-bit arithmetic instructions

Multiplication and division operation

instructions

Bit manipulation instructions

Bit logic instrucitons

ROM table reference instructions

• Abundant addressing modes : Register addressing

Page addressing

Pointing register indirect addressing

Stack addressing

Immediate value addressing

• I/O port

Input-output port : 5 ports ¥ 8 bits

(Each bit can be assigned to input or output)

Input port : 1 port ¥ 8 bits

• Built-in multifunctional 16-bit timer : 2

Following 4 modes can be set for each timer :Auto-reload timer mode

Clock output mode

Capture register mode

Real time output mode

• Serial port : 1 channel

generator)

• 12-bit pulse width modulator : 2

• Watchdog timer

• Transition detector : 4

• 10-bit A/D converter : 8 channels

• Interrupts

Nonmaskable : 1

Maskable : Internal 10/external 2

• Stand-by function

STOP mode : Software clock stop mode

HALT mode : Software CPU stop mode

HOLD mode : Hardware CPU stop mode

(UART mode with baud rate

1/28

¡ Semiconductor MSM66101

• Package options:

64-pin plastic shrink DIP (SDIP64-P-750-1.78) : (Product name: MSM66101-¥¥¥SS)

64-pin plastic QFP (QFP64-P-1414-0.80-BK) :

68-pin plastic QFJ (PLCC) (QFJ68-P-S950-1.27) : (Product name: MSM66101-¥¥¥JS)

64-pin ceramic piggyback (ADIP64-C-750-1.78) : (Product name: MSM66G101VS)

* The piggyback type is used only for engineering samples.

¥¥¥ indicates the code number.

(Product name: MSM66101-¥¥¥GS-BK)

2/28

¡ Semiconductor MSM66101

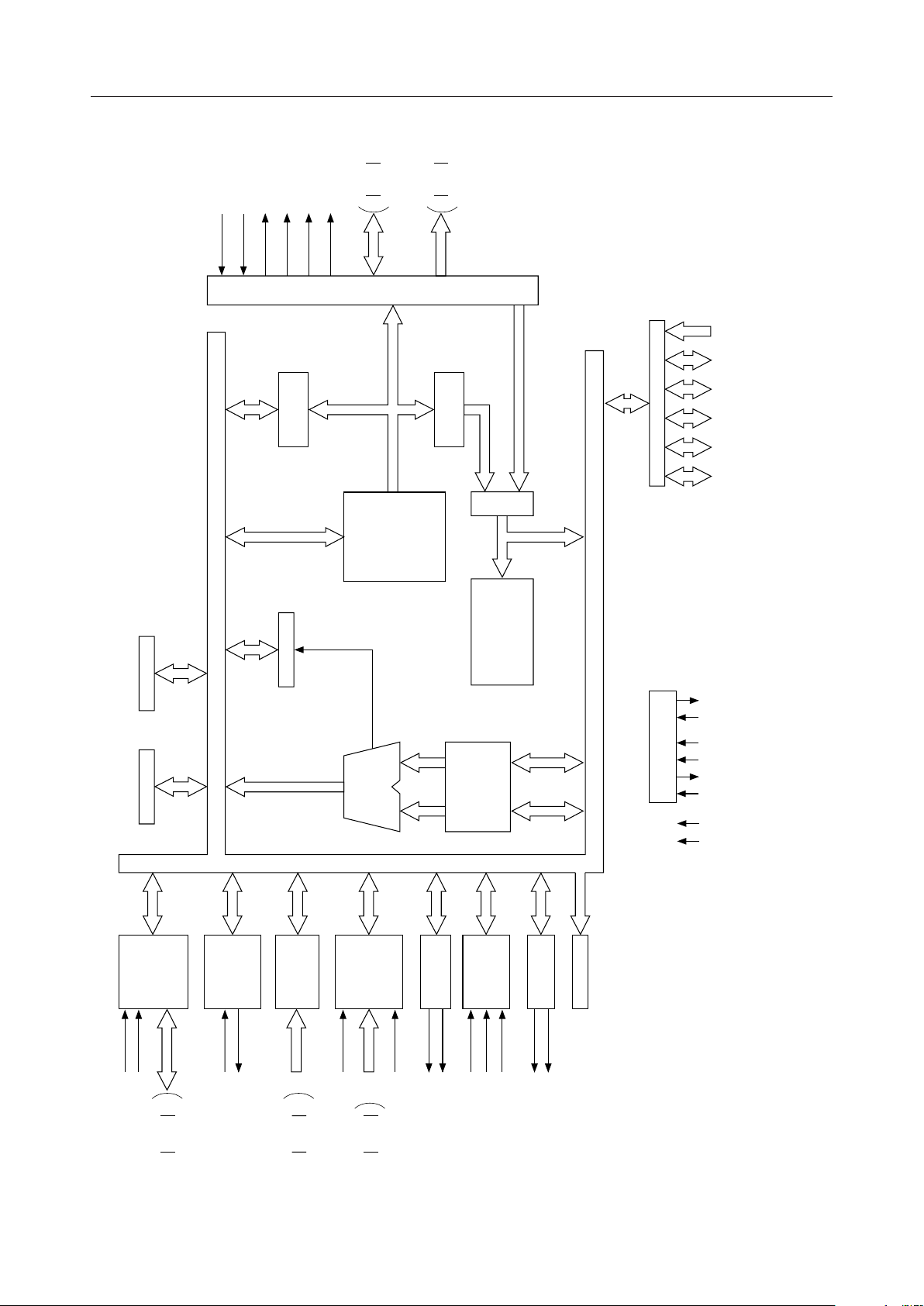

BLOCK DIAGRAM

A8 /P1.0

EA

READY

ALE

PSENRDWR

AD0/P0.0

AD7/P0.7

A15/P1.7

SSP LRB

BUS P

O

RAM

PSW

R

384 ¥ 8 bits

T

C

O

N

CONT.

MEMORY

ALU

.

T

PORT

P2 P3 P4 P5

P1

P0

PC

ROM

12K ¥ 8 bits

IR

RAP

DEC.

INSTRUCTION

HLDA/P2.5

HOLD/P2.4

CONT.

FLT

RES

OSC1

OSC0

GND

V

DD

ALU CONT.

R.

ACC

TEMPORARY

CONSTANTS

SYSTEM

0–1

TIMER

P4.0/TM0CK

P4.1/TM1CK

P3.4/TM0IO

SERIAL

P3.5/TM1IO

P3.1/RXD

PORT

P3.0/TXD

TION D.

TRANSI-

P4.4/TRNS0

P4.7/TRNS3

A/D

REF

V

P5.0/AI 0

CONV.

AGND

P5.7/AI 7

0,1

PWM

NMI

P4.2/PWM0

P4.3/PWM1

CONT.

INTERRUPT

P3.2/INT0

P3.3/INT1

WDT

CONT.

PERIPHERAL

RESOUT

P2.3/CLKOUT

3/28

¡ Semiconductor MSM66101

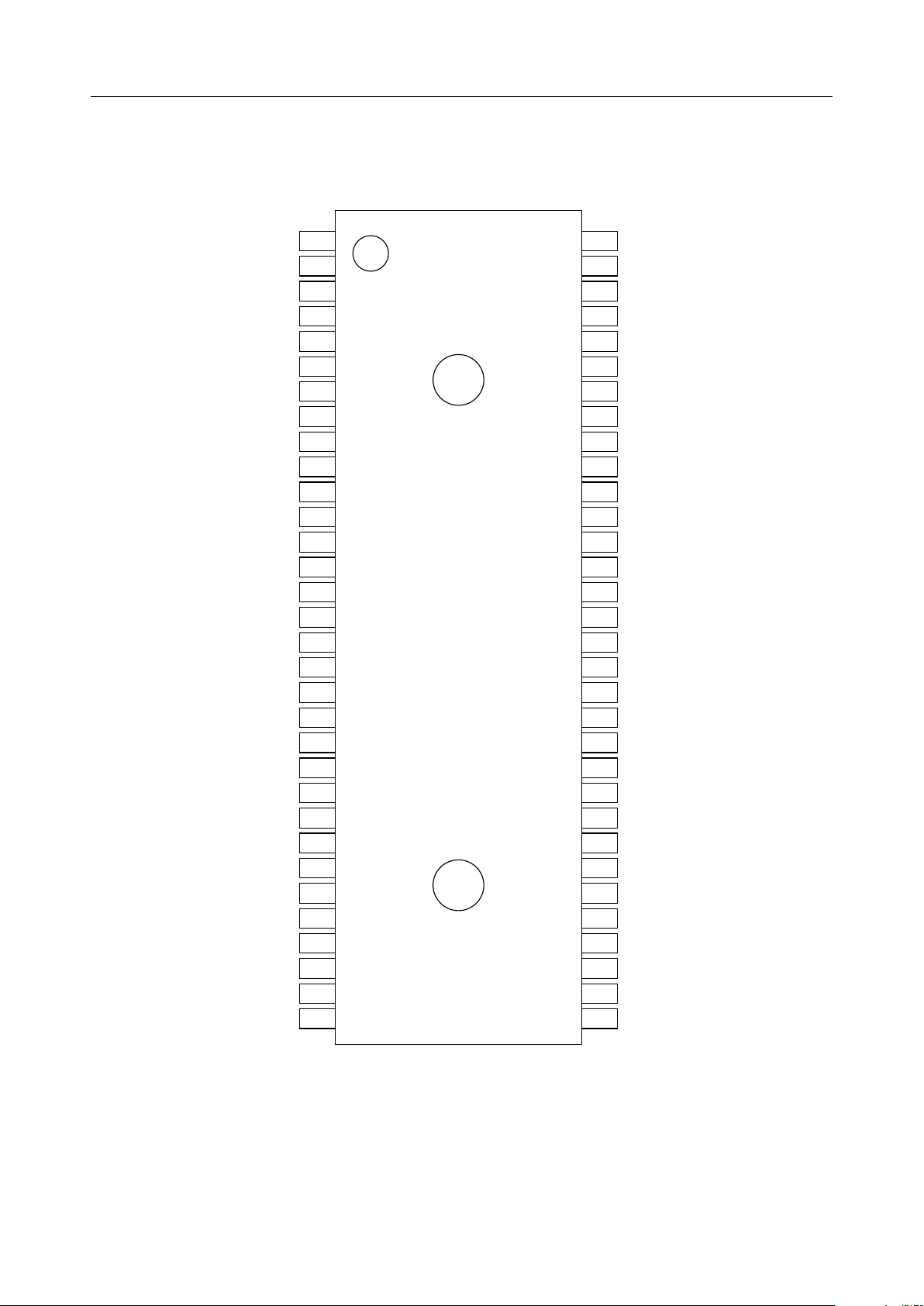

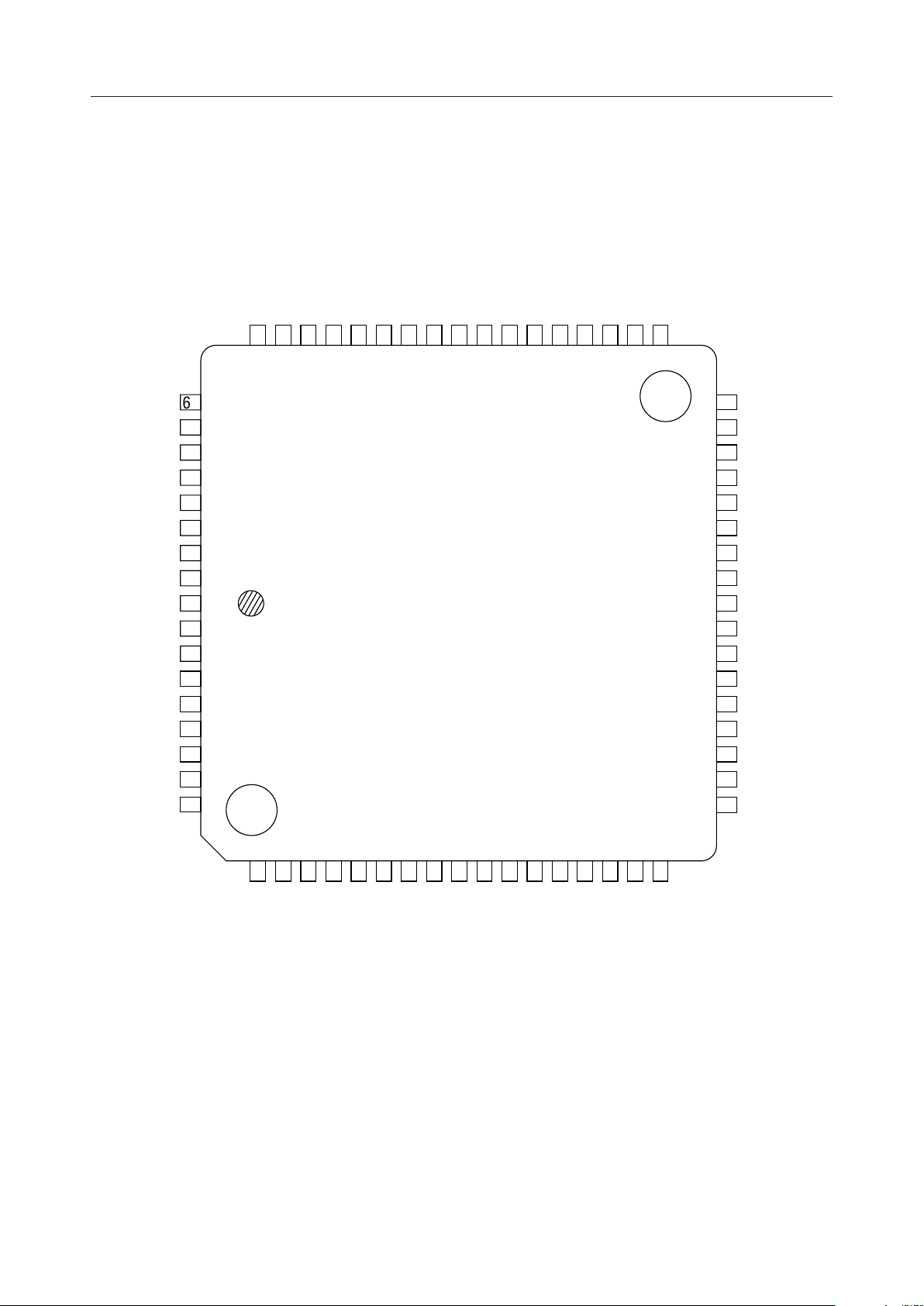

PIN CONFIGURATION (TOP VIEW)

AD0/P0.0

AD1/P0.1

AD2/P0.2

AD3/P0.3

AD4/P0.4

AD5/P0.5

AD6/P0.6

AD7/P0.7

A8/P1.0

A9/P1.1

A10/P1.2

A11/P1.3

A12/P1.4

A13/P1.5

A14/P1.6

A15/P1.7

P2.0

P2.1

P2.2

CLKOUT/P2.3

RESOUT P3.6

ALE P3.5/TM1IO

PSEN P3.4/TM0IO

RD P3.3/INT1

WR P3.2/INT0

READY P3.1/RXD

FLT P2.7

RES P2.6

OSC0 P2.5/HLDA

OSC1 P2.4/HOLD

GND NMI

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

EA P3.0/TXD

28

29

30

31

32

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

V

DD

V

REF

AGND

P5.7/AI7

P5.6/AI6

P5.5/AI5

P5.4/AI4

P5.3/AI3

P5.2/AI2

P5.1/AI1

P5.0/AI0

P4.7/TRNS3

P4.6/TRNS2

P4.5/TRNS1

P4.4/TRNS0

P4.3/PWM1

P4.2/PWM0

P4.1/TM1CK

P4.0/TM0CK

P3.7

64-Pin Plastic Shrink DIP

4/28

¡ Semiconductor MSM66101

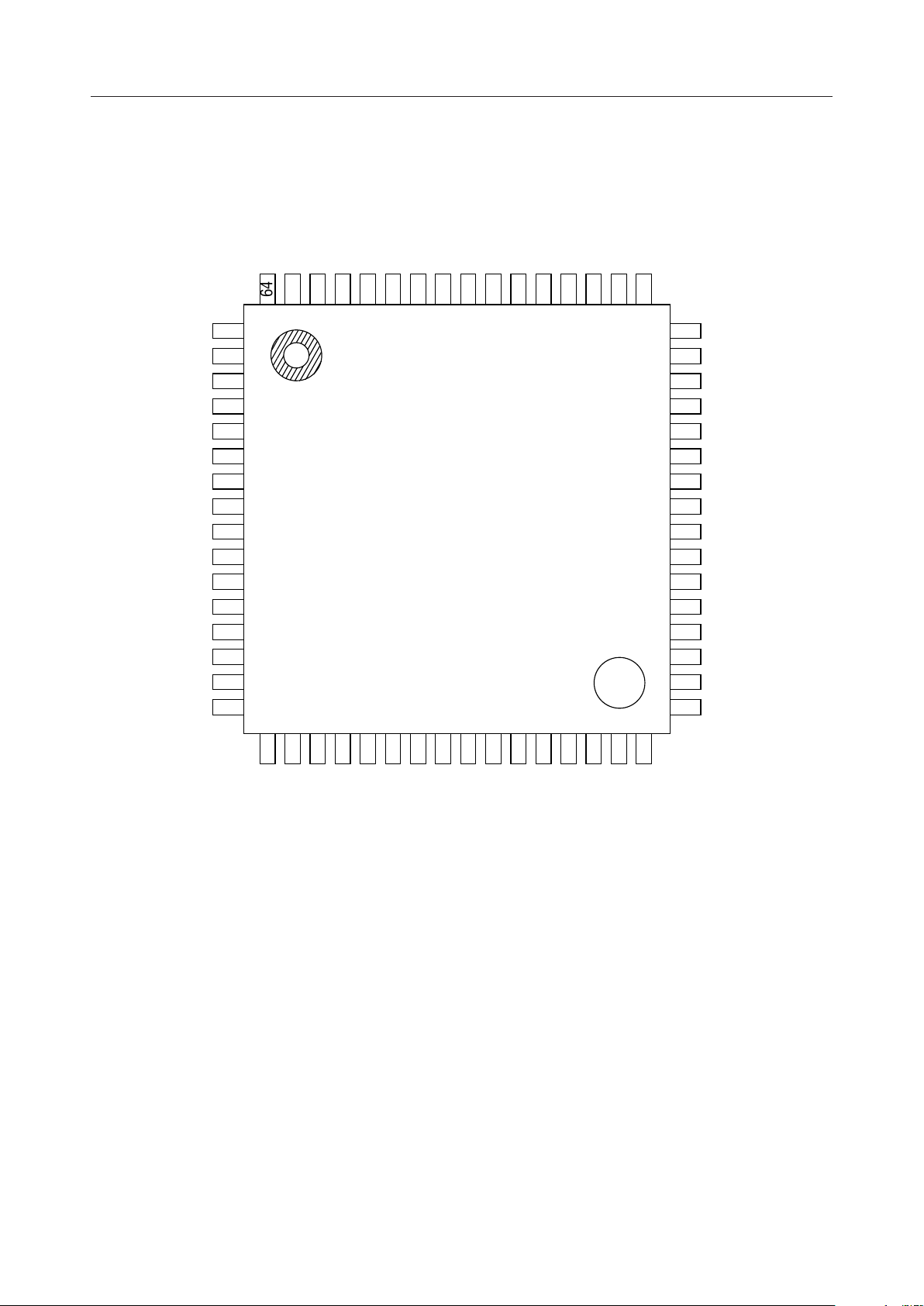

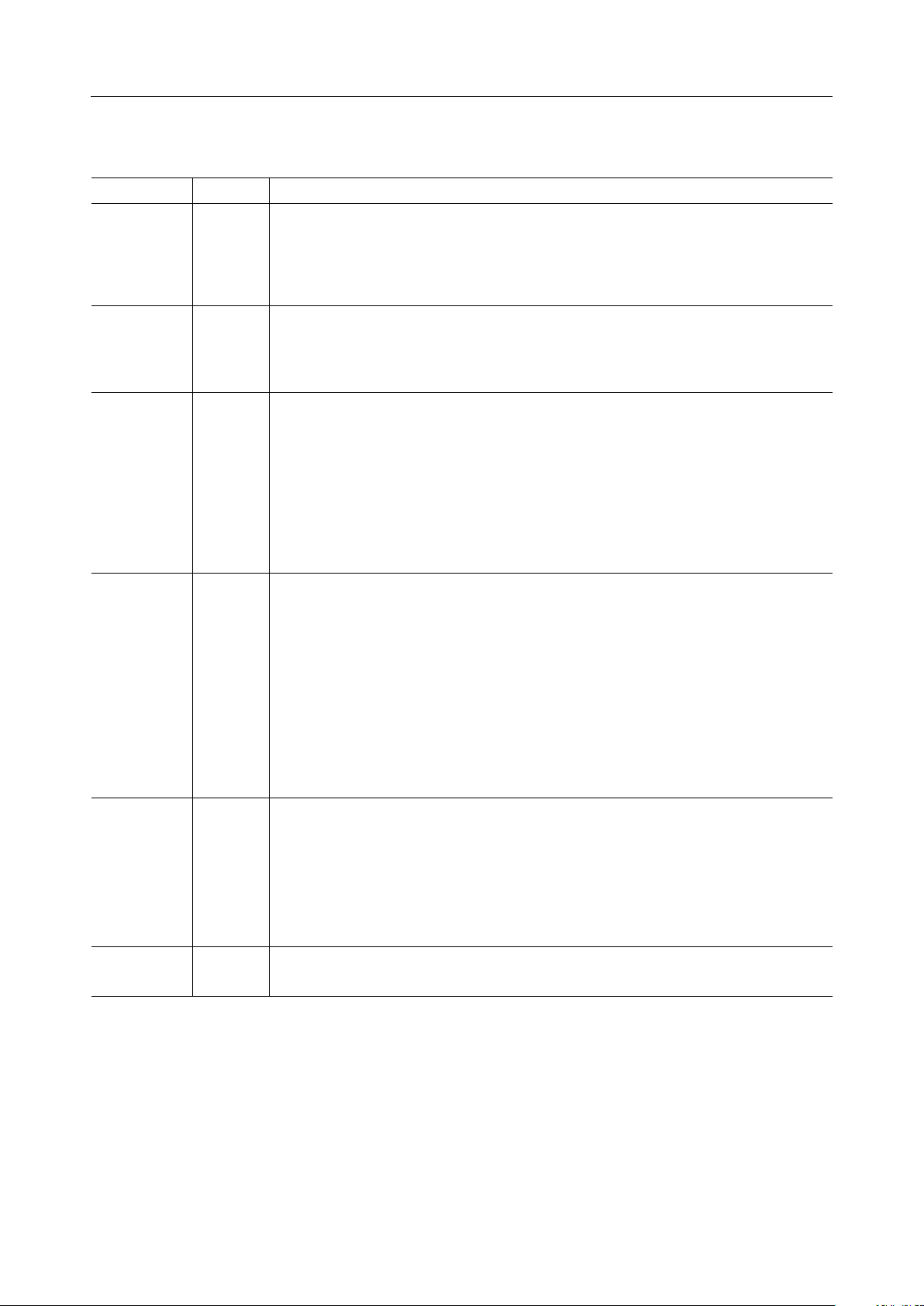

PIN CONFIGURATION (TOP VIEW) (Continued)

A8/P1.0

A9/P1.1

A10/P1.2

A11/P1.3

A12/P1.4

A13/P1.5

A14/P1.6

A15/P1.7

P2.0

P2.1

P2.2

10

11

12CLKOUT/P2.3

13RESOUT

14ALE

15PSEN

16RD

P0.7/AD7

P0.6/AD6

P0.5/AD5

P0.4/AD4

P0.3/AD3

P0.2/AD2

P0.1/AD1

64

63

62

61

60

59

58

1

2

3

4

5

6

7

8

9

DDVREF

P0.0/AD0

V

57

56

55

AGND

54

53 P5.7/AI7

52 P5.6/AI6

54 P5.5/AI5

50 P5.4/AI4

49 P5.3/AI3

48

P5.2/AI2

47

P5.1/AI1

46

P5.0/AI0

45

P4.7/TRNS3

44

P4.6/TRNS2

43

P4.5/TRNS1

42

P4.4/TRNS0

41

P4.3/PWM1

40

P4.2/PWM0

39

P4.1/TM1CK

38

P4.0/TM0CK

37 P3.7/TM3IO

36 P3.6/TM2IO

35 P3.5/TM1IO

34 P3.4/TM0IO

33 P3.3/INT1

17

WR

18

19

EA

READY

20

21

22

23

24

FLT

RES

OSC0

OSC1

GND

64-Pin Plastic QFP

25

26

NMI

HOLD/P2.4

27

28TXC/P2.6

29RXC/P2.7

HLDA/P2.5

30TXD/P3.0

31RXD/P3.1

32INT0/P3.2

5/28

¡ Semiconductor MSM66101

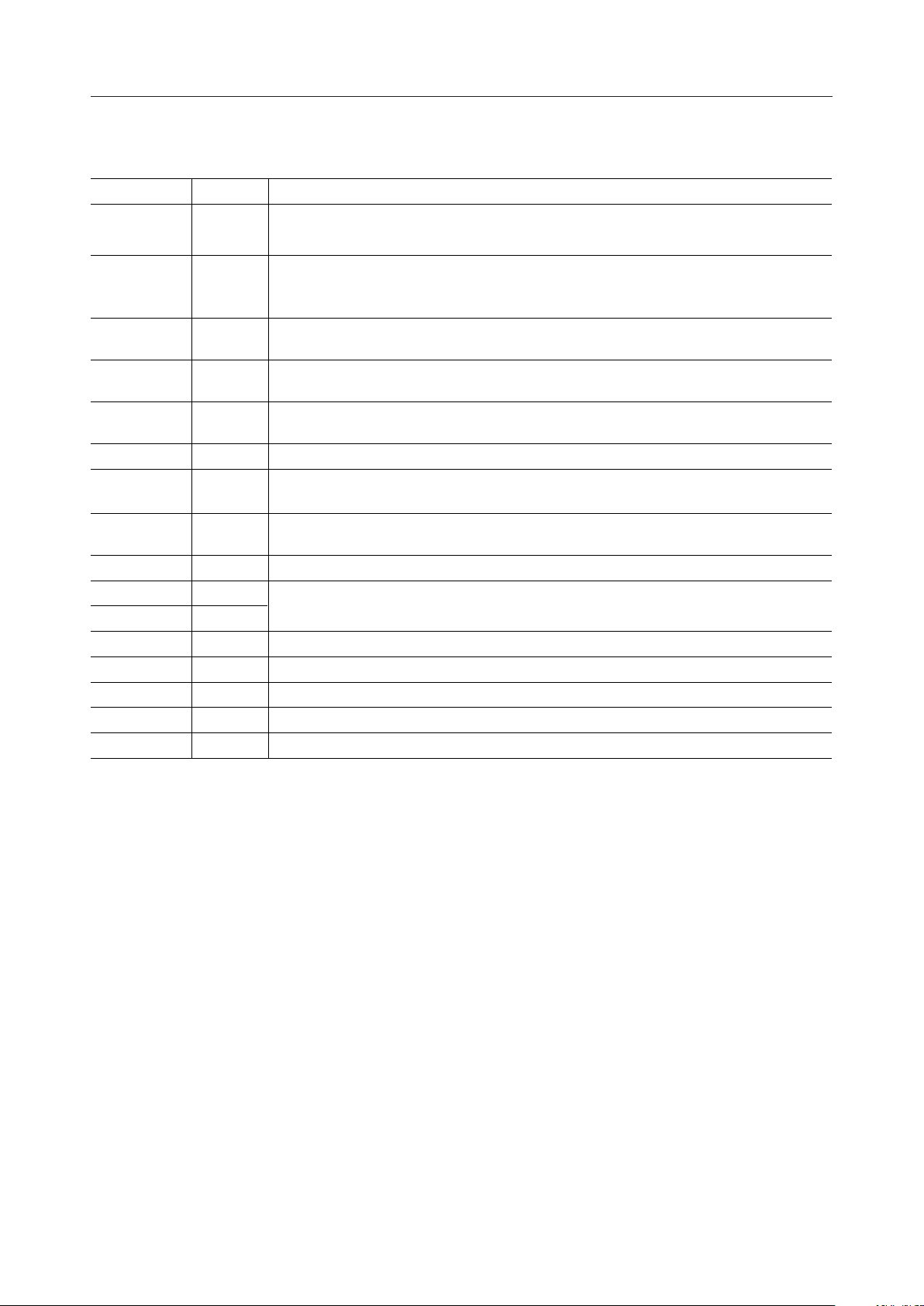

PIN CONFIGURATION (TOP VIEW) (Continued)

P5.2/AI2

P5.1/AI1

P5.0/AI0

P4.7/TRNS3

P4.6/TRNS2

P4.5/TRNS1

P4.4/TRNS0

60

59

58

57

56

55

P4.3/PWM1

54

53

P4.1/TM1CK

52

51

P4.0/TM0CKNCP3.7

50

49

48

P3.6

P3.5/TM1IO

47

46

P3.4/TM0IO

P3.3/INT1

45

44

AI3/P5.3

AI4/P5.4

AI5/P5.5

AI6/P5.6

AI7/P5.7

AGND

V

REF

V

DD

V

DD

AD0/P0.0

AD1/P0.1

AD2/P0.2

AD3/P0.3

AD4/P0.4

AD5/P0.5

AD6/P0.6

AD7/P0.7

61

62

63

64

65

66

67

68

P3.2/INT0

43

P3.1/RXD

42

P3.0/TXD

41

P2.7

40

P2.6

39

P2.5/HLDA

38

P2.4/HOLD

37

NMI

36

1

2

3

4

5

6

7

8

9

35

34

33

32

31

30

29

28

27

GND

GND

OSC1

OSC0

RES

FLT

EA

READY

WR

10

11

A8/P1.0

A9/P1.1

12

13

14

15

16

17

18

NC P4.2/PWM0

P2.0

A10/P1.2

A11/P1.3

A12/P1.4

A13/P1.5

A14/P1.6

A15/P1.7

NC: No-connection pin

68-Pin Plastic QFJ (PLCC)

19

20

P2.1

21

22

P2.2

CLKOUT/P2.3

23

24

ALE

RESOUT

25

PSEN

26

RD

6/28

¡ Semiconductor MSM66101

PIN DESCRIPTIONS

Type DescriptionSymbol

P0.0–P0.7/

AD0–AD7

I/O

P0: 8-bit input-output port. Each bit can be assigned to input or output.

AD: Outputs the lower 8 bits of program counter during external program memory

fetch, and receives the addressed instruction under the control of PSEN.

Also outputs the address and outputs or inputs data during an external data

memory access instruction under the control of ALE, RD, and WR.

P1.0–P1.7/

A8–A15

I/O

P1: 8-bit input-output port. Each bit can be assigned to input or output.

A: Outputs the upper 8 bits of program counter (PC

memory fetch. Also this pin outputs the upper 8 bits of address during external data

memory access instructions.

P2.0–P2.2

P2.3/CLKOUT CLKOUT:

I/O

P2: 8-bit input-output port. Each bit can be assigned to input or output.

Output pin for supplying a clock to peripheral circuits. Output frequency

range is equal to or twice the system clock.

P2.4/HOLD

P2.5/HLDA

HOLD: Input pin to request the CPU to enter the hardware power-down state.

HLDA: HOLD ACKNOWLEDGE: the HLDA signal appears in response to the HOLD

signal and indicates that the CPU has entered the power-down state.

P2.6

P2.7

P3.0/T

P3.1/R

D

X

D

X

I/O

P3.2/INT0 R

P3: 8-bit input-output port. Each bit can be assigned to be an input or an output.

TXD: Serial port transmitter data output pin.

D: Serial port receiver data input pin with high impedance.

X

P3.3/INT1 INT: Interrupt Request Input pin.

P3.4/TM0IO

P3.5/TM1IO

P3.6

P3.7

TM0IO-TM1IO: One of the following signals is output or input.

• Clock at twice the frequency range of the 16-bit timer overflow

• Load trigger signal to the capture register input

• Setting value output

Whether the signal is input or output depends on the mode.

) during external program

8–15

P4.0/TM0CK P4: 8-bit input-output port. Each bit can be assigned to an input or an output.

I/O

P4.1/TM1CK TM0CK, TM1CK: Clock input pins of timer 0, timer 1.

P4.2/PWM0

P4.3/PWM1

P4.4

– P4.7/

TRANS: The input pins which sense the rising edge and set the flag.

PWM: 12-bit pulse-width modulator output pin.

TRANS0 – 3

P5.0 – P5.7/

AI0 –AI7

I

P5: 8-bit input port.

AI: Analog signal input pin for A/D converter.

7/28

¡ Semiconductor MSM66101

PIN DESCRIPTIONS (Continued)

Type DescriptionSymbol

RESOUT

O

Outputs 'H' level when the CPU is in RESET status.

Reset to 'L' level in some programs.

ALE

PSEN Program Store Enable:

RD Output strobe activated during a bus read cycle.

WR Output strobe during a bus write cycle.

EA Normally set to 'H' level.

FLT If FLT is 'H' level, ALE, WR, RD, PSEN are set to 'H' level when reset.

RES RESET input pin.

OSC0

OSC1

NMI Nonmaskable interrupt input pin (falling edge)

V

REF

AGND Ground for A/D converter.

V

DD

GND Ground.

O

O

O

O

IREADY Used when the CPU accesses low speed peripherals.

I

I

I

I

O

I

I

I

I

I

Address Latch Enable:

Used to enable data on to the bus from the external data memory.

Used as write strobe to external data memory.

If set to 'L' level, the CPU fetches the code from external program memory.

If FLT is set to 'L', ALE, WR, RD, PSEN are set to floating level when reset.

Clock oscillation pins

Reference voltage input pin for A/D converter.

System power supply.

The timing pulse to latch the lower 8 bits of the address

output from port 0 when the CPU accesses the external

memory.

The strobe pulse to fetch to external program

memory.

8/28

¡ Semiconductor MSM66101

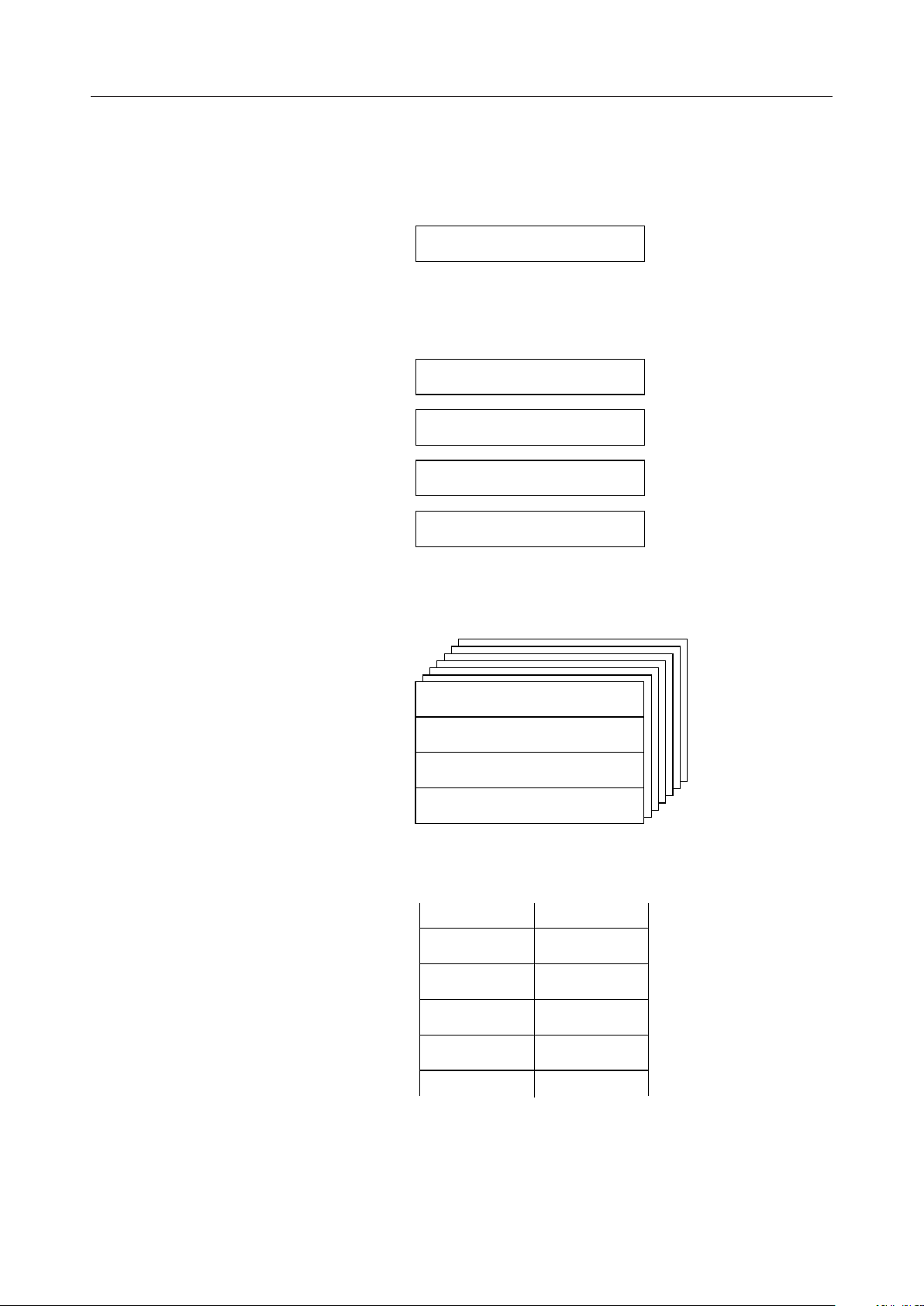

REGISTERS

Accumulator

15 0

ACC

Control Register (CR)

15 0

Program Status Word

Program Counter

Local Register Base

System Stack Pointer

Pointing Register (PR)

Index Register 1

Index Register 2

Data Pointer

User Stack Pointer

PSW

PC

LRB

SSP

15 0

X1

X2

DP

USP

Local Register

7070

ER0

ER1

ER2

ER3

R1

R3

R5

R7

R0

R2

R4

R6

9/28

Loading...

Loading...