E2E1017-27-Y3

¡ Semiconductor

This version: Jan. 1998

Previous version: Nov. 1996

MSM65X227¡ Semiconductor

MSM65X227

8-Bit Microcontroller (with 4K-Byte EEPROM)

GENERAL DESCRIPTION

The MSM65X227 is a high-performance, 8-bit microcontroller that employs OKI original

CPU core, the nX-8/50. The MSM65X227 includes a minimum instruction execution time of

667 ns (@6 MHz) that enables high-speed processing. It has 60K-byte program memory

space, internal 4K bytes of EEPROM (general memory space), 1K-byte data memory (384

bytes for local memory space and 640 bytes for general memory space), a timer, a serial port

and an A/D converter. The MSM65X227, which has no internal program ROM, is provided

with the special time-division data/address bus that can be connected to an extrernal

program ROM.

FEATURES

• Operating range

Operating frequency : 0 to 6MHz

Operating voltage : 4.5 to 5.5V

Operating temperature : – 40 to +85°C

• Memory space : 128K bytes

Program memory space : 60K bytes

Internal EEPROM : 4K bytes

Internal data memory : 1K bytes

• Minimum instruction execution time : 667ns @ 6MHz

• Ample instruction set : 81 basic instructions

8/16-bit operation instructions

Bit manipulation instructions

Complex function instructions

• Ample addressing modes

• Timer : 8-bit auto-reload timer ¥ 2 (one is shared

with the baud rate generator)

Watchdog timer ¥ 1

• Counter : Time base counter ¥ 1

• Serial port : Serial port ¥ 1 (UART/clock synchronous

system)

• A/D converter : 8 bits ¥ 4 channels

• I/O port : 7 ports, 48 bits

Input-output port : 5 ports ¥ 8 bits, 1 port ¥ 4 bits

Input-port : 1 port ¥ 4 bits

• External interrupts : 2

• Interrupt sources : 10

• Package:

100-pin plastic TQFP (TQFP100-P-1414-0.50-K) (Product name: MSM65X227TS-K)

1/18

2/18

MSM65X227¡ Semiconductor

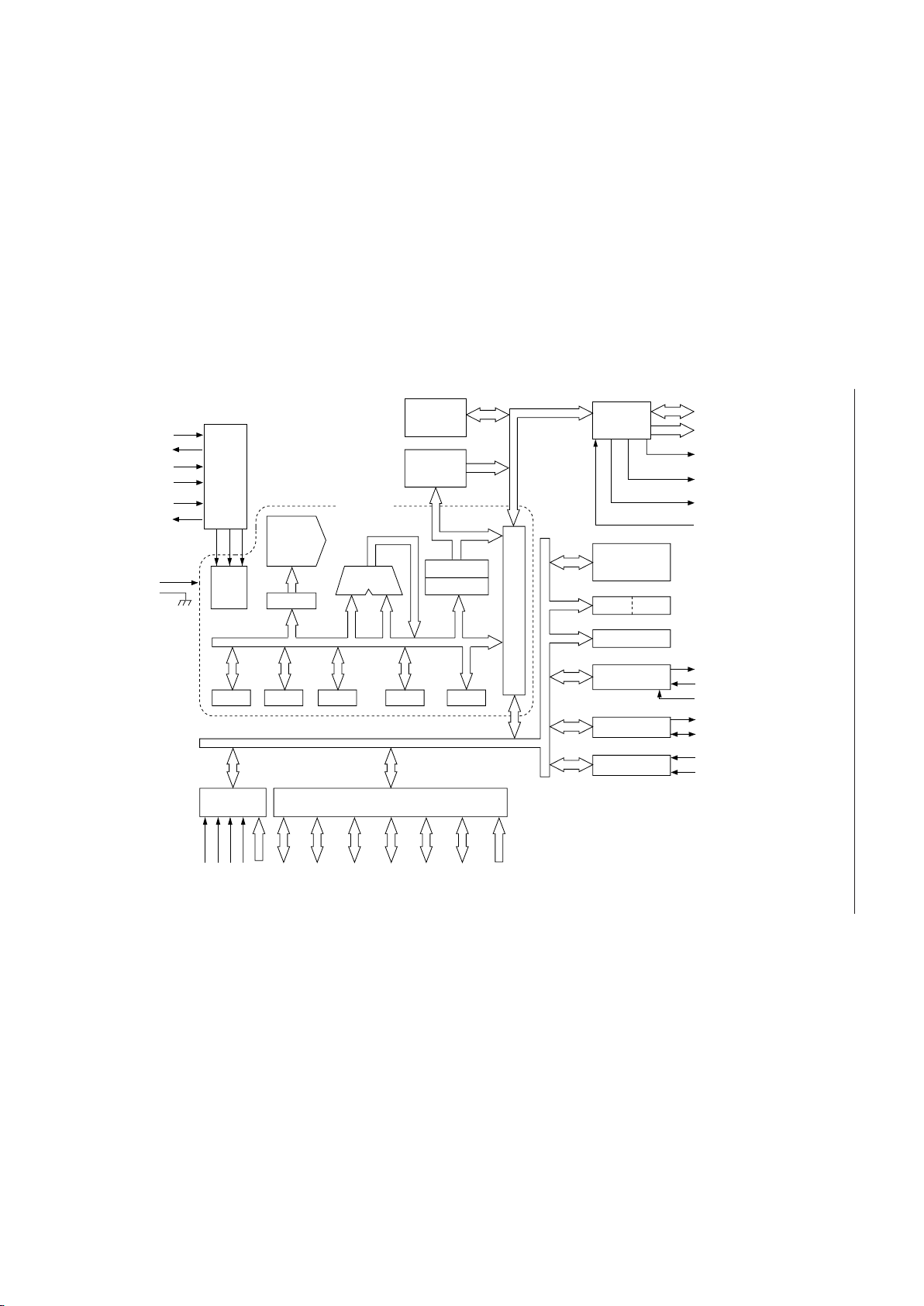

BLOCK DIAGRAM

OSC0

OSC1

RESET

HSTOP*

V

DD

GND

OSC

CONT.

RAM

(640 bytes)

EXT.MEM.

CONT.

INST.

DEC.

T/C

IR

ALU

GMAR

PC

AR

BR PSW SP LMAR

BUS

CONT.

I/O PORT

RAM

(384 bytes)

TBC WDT

8-bit TIMERx2

INTERRUPT CONT.

AD0-7

A8-16

RD

WR

ALE

T1OUT*

T0CK*

GATE*

INT0*

INT1*

P0 P1 P2

* is secondary function of each port.

XT

XT

EEPROM

(4K bytes)

EXWR

WUP TIMER

SIO

TXD*

RXD*

**P5 is a 4-bit input-output port.

***P6 is a 4-bit input only port.

P3 P4 P5** P6***

8-bit A/D C

¥ 4ch

AI0*- AI3*

AGND

VRLVRHAV

DD

CPU CORE

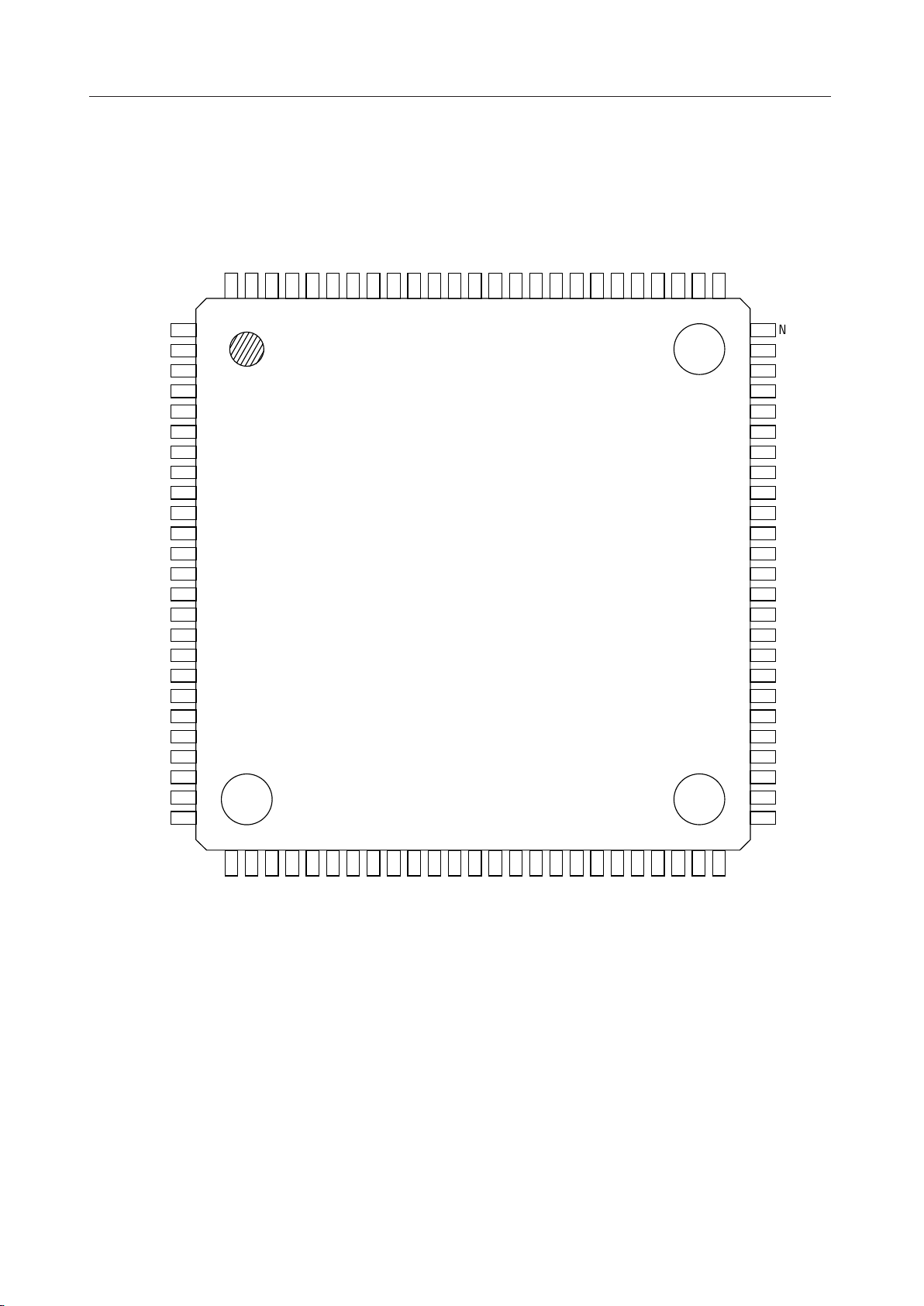

PIN CONFIGURATION (TOP VIEW)

NC

P1.4

P1.5

P1.6

P1.7

NC

P0.0

P0.1

P0.2

92

93

94

95

96

97

98

99

100

1

NC

2NC

3P0.3

4P0.4

5P0.5

6P0.6

7P0.7

8XT

9NC

10XT

11GND

12OSC0

13NC

14OSC1

15ALE

16NC

17RD

18WR

19RESET

20EXWR

21AGND

22P6.0

23P6.1

24P6.2

25P6.3

P1.3

91

P1.2

90

P1.1

89

NC

88

P1.0

87

P2.7

86

NC

85

P2.6

84

P2.5

83

P2.4

82

NC

81

P2.3

80

P2.2

79

P2.1

78

P2.0

77

MSM65X227¡ Semiconductor

A16

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

NC

A15

A14

A13

NC

A12

A11

A10

A9

A8

V

DD

P3.7

NC

P3.6

P3.5

NC

P3.4

P3.3

P3.2

P3.1

P3.0

AD7

AD6

AD5

NC

26

V

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

RL

RH

DD

V

AV

P5.0

P5.1

P5.2

P5.3

NC

P4.0

P4.1

P4.2

P4.3

NC

P4.4

NC

P4.5

P4.6

P4.7

AD0

AD1

AD2

NC

AD3

AD4

NC

NC: No-connection Pin

100-Pin Plastic TQFP

3/18

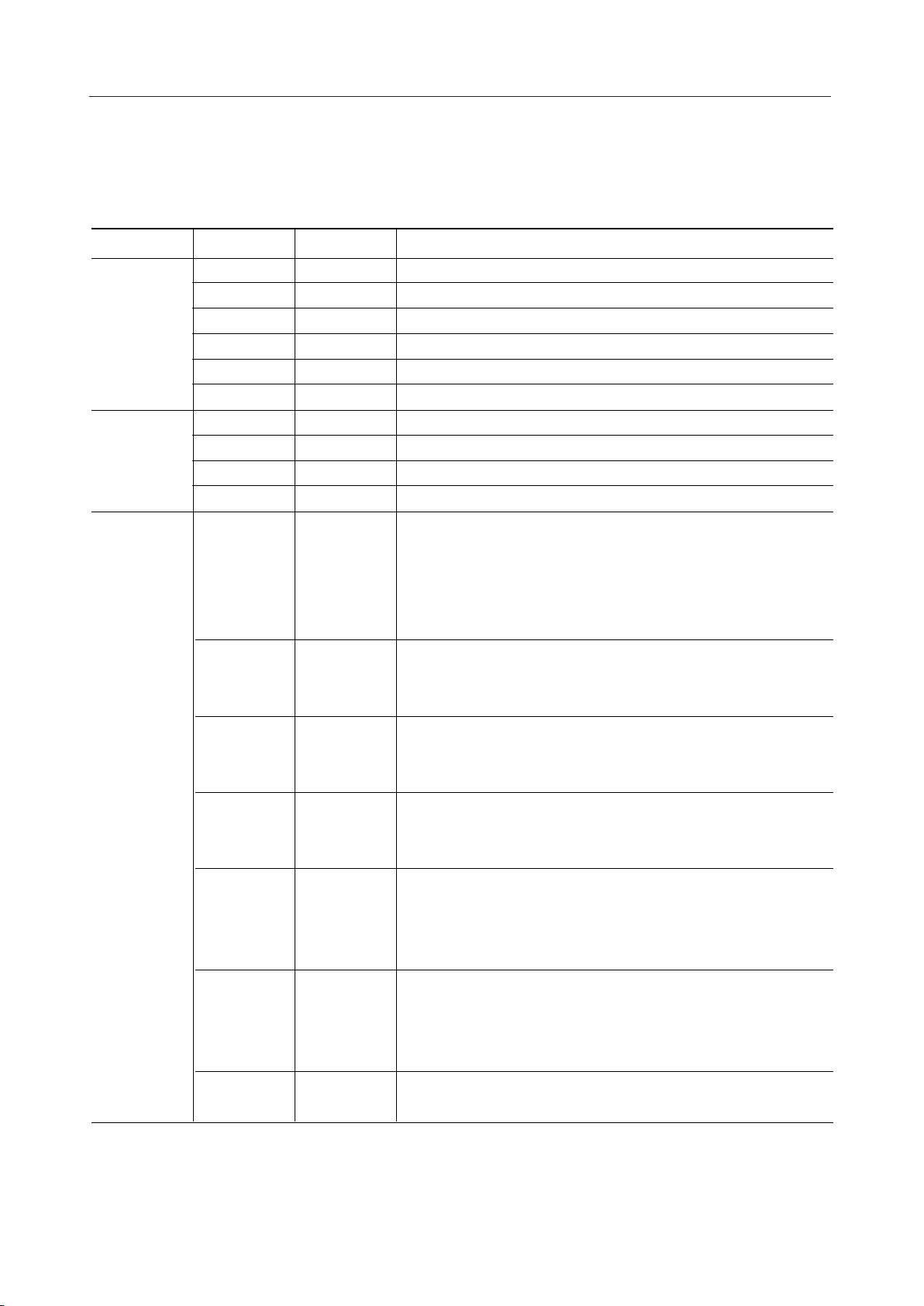

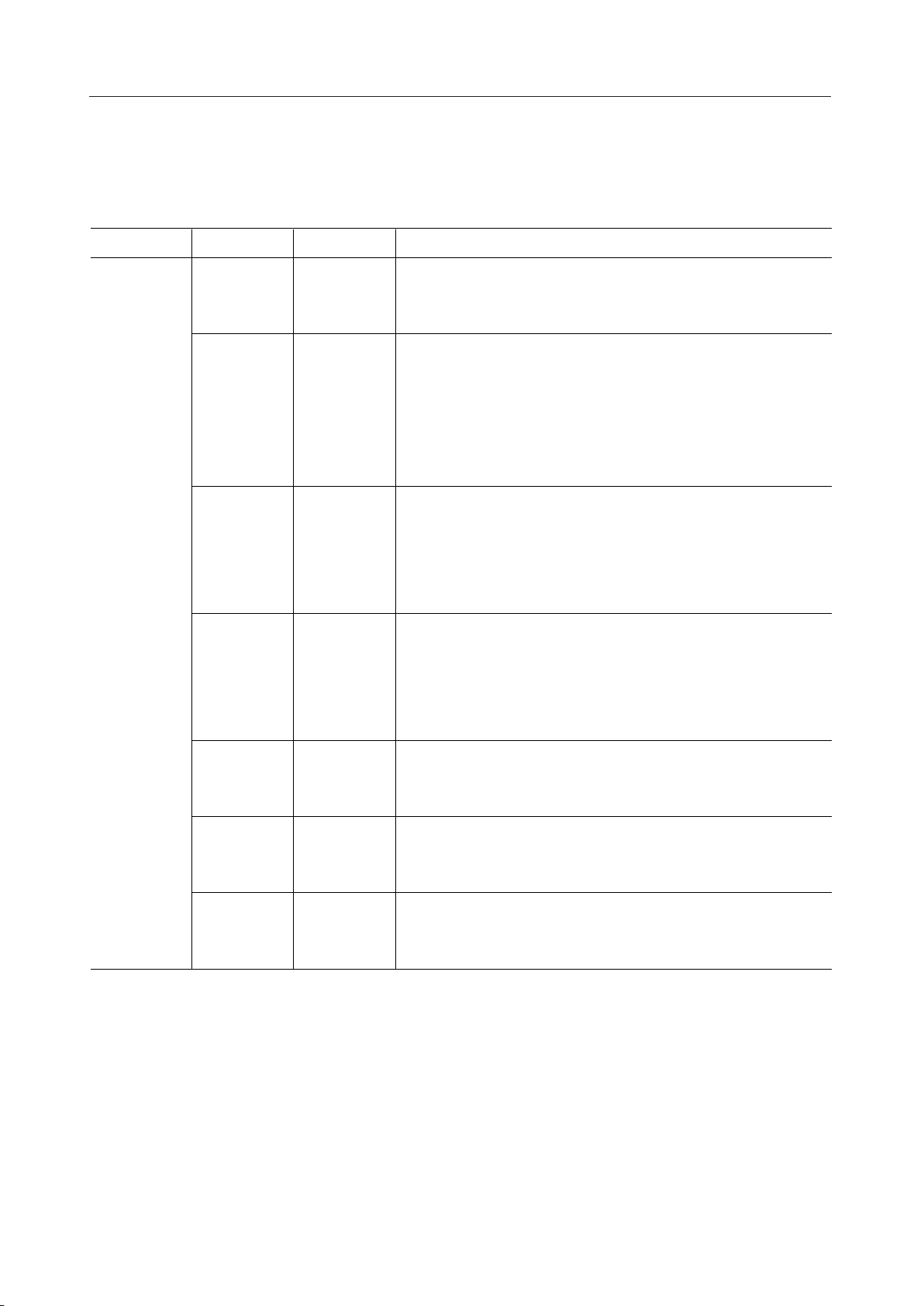

PIN DESCRIPTION

Basic Functions

Function Symbol Type Description

MSM65X227¡ Semiconductor

Power Supply

Oscillation

V

DD

GND

AV

DD

AGND Analog ground—

V

RH

V

RL

OSC0 CPU oscillation input pinI

OSC1 CPU oscillation output pinO

XT CPU start-up timer oscillation input pinI

XT CPU start-up timer oscillation output pinO

RESET

EXWR I

—

—

Digital power supply (5V)

Digital ground

Analog power supply (5V)—

Analog reference voltage (5V)—

Analog reference voltage (ground)—

System reset input:

When this pin goes into the "L" state, the internal state is

I

initialized and the execution of an instruction starts from address

0040H. The input is pulled up to V

with an internal pull-up

DD

resistor.

External write enable pin :

Sampled at a system reset and enables external EEPROM write

and read during the "L" level.

Control

RD O

WR O

ALE O

AD0 - AD7 I/O

A8 - A16 O

Read signal at external memory access:

Read cycle in memory is indicated when the signal goes into the

"L" level during external memory access.

Write-signal during external memory access:

Write cycle in memory is indicated when the signal goes into the

"L" level during external memory access.

Address latch signal at external memory access:

The MSM65X227 uses a time dividing address/data bus. This

signal uses the lower 8 bits of the address as a strobe signal to

latch the external latch circuit.

8-bit address/data bus:

Address/data bus performs lower 8-bit address output,

instruction fetch or data read/write along with the ALE, RD and

WR pins.

9-bit address bus:

Address bus for the upper 9 bits.

4/18

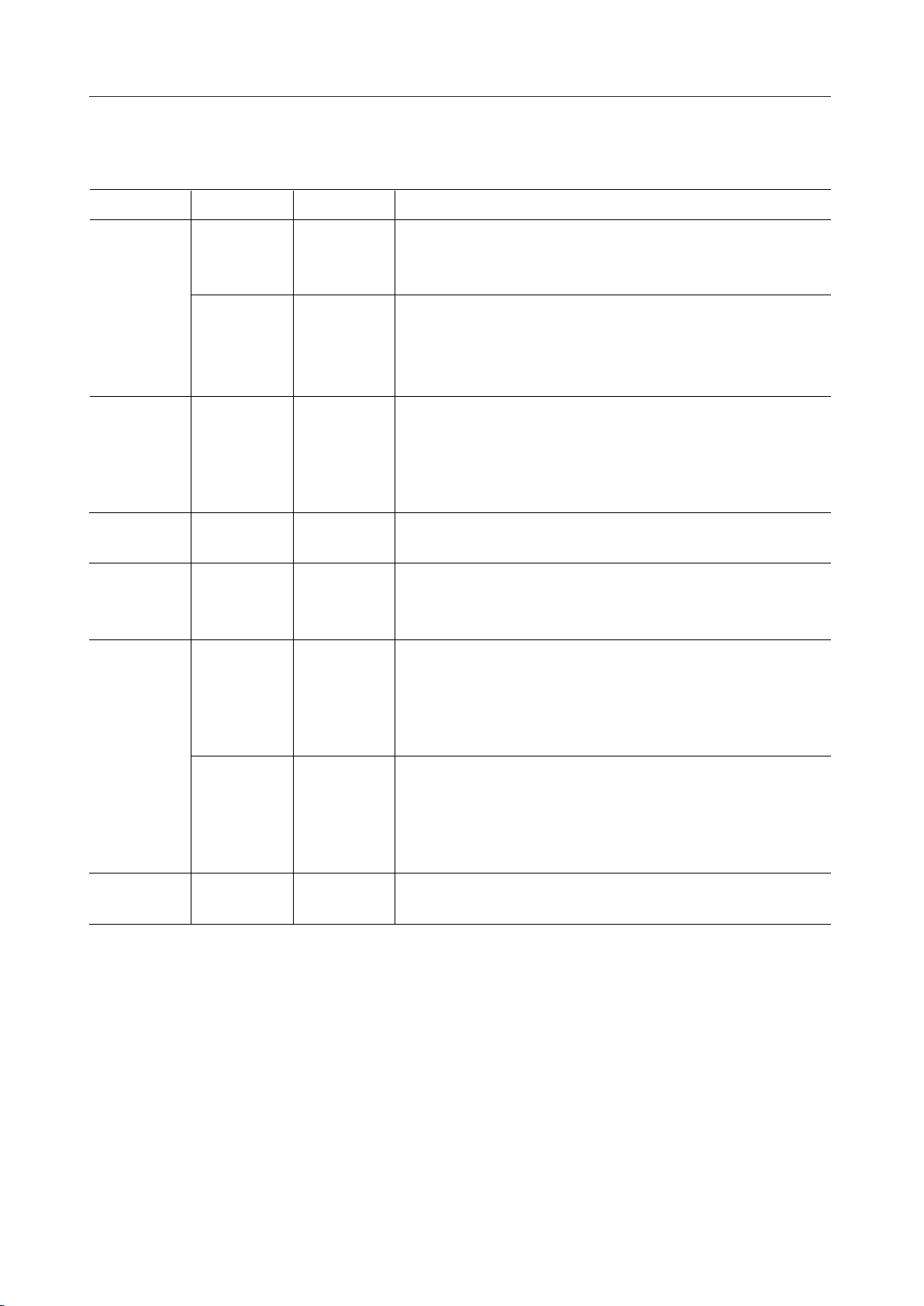

Basic Functions (Continued)

MSM65X227¡ Semiconductor

Function

Port

Symbol Type Description

8-bit input-output port (Port 0):

P0.0 - P0.7

P1.0 - P1.7

I/O

I/O

I/OP2.0 - P2.7

I/OP3.0 - P3.7

Users can specify input or output at each bit with the port 0

direction register (P0DIR).

8-bit input-output port (Port 1):

Users can specify input or output at each bit with the port 1

direction register (P1DIR).

In the input mode, ports can be set as inputs with a pull-up

resistor at each bit.

A secondary function shown in the next table is assigned at the

P1.7 pin.

8-bit input-output port ( Port 2):

Users can specify input or output at each bit by the port 2

direction register (P2DIR).

Each pin of Port 2 is assigned a secondary function shown in the

next table.

8-bit input-output port (Port 3):

Users can specify input or output at each bit by the port 3

direction register (P3DIR).

A secondary function shown in the next table is assigned at the

P3.0 pin.

8-bit input-output port (Port 4):

I/OP4.0 - P4.7

I/OP5.0 - P5.3

IP6.0 - P6.3

Users can specify input or output at each bit with the port 4

direction register (P4DIR).

4-bit input-output port (Port 5):

Users can specify input or output at each bit with the port 5

direction register (P5DIR).

4-bit input port (Port 6):

Each pin of Port 6 functions as an analog input channel during

A/D conversion.

5/18

Secondary Functions

Function Symbol Type Description

Secondary function of P1.7:

External

Interrupt

Control

INT0 I

INT1 I

HSTOP I

Input pin of external interrupt 0. "Receive" is enabled at

rising/falling edges or at the "L" level.

Secondary function of P2.0:

Input pin of external interrupt 1. "Receive" is enabled at

rising/falling edges or at the "L" level. Can also be used as a gate

signal input pin that enables/disables the count of Timer 0.

Secondary function of P3.0:

Hardware stop mode input pin. Changes to hardware stop mode

by setting this pin to the "L" level when the HSTP bit of SBYCON

is 1. In hardware stop mode, the oscillation of OSC is halted to

reduce power consumption.

MSM65X227¡ Semiconductor

Timer 0

Timer 1

Serial Port

A/D Converter

T0CK

T1OUT

RXD

O

I/O

OTXD

I

IAI0 - AI3

Secondary function of P 2.1:

External clock input pin of Timer 0.

Secondary function of P 2.2:

This pin outputs a waveform with a period equal to two times of

overflow of Timer 1.

Secondary function of P 2.3:

As UART: Receive data input pin of asynchronous

communication.

As clock synchronization: Send/receive data input-output pin of

clock synchronous communication.

Secondary function of P 2.4:

As UART: Send data output pin of asynchronous

communication.

As clock synchronization: Synchronized clock output pin of

clock synchronous communication.

Secondary function of P 6.0 to P 6.3:

Functions as an analog input channel at A/D conversion.

6/18

Loading...

Loading...