OKI MSM65P524-xxxGS-BK, MSM65P524-xxxJS, MSM65P524-xxxSS, MSM65524A-xxxSS, MSM65524A-xxxGS-BK Datasheet

...

E2E1016-27-Y6

¡ Semiconductor MSM65524A/65P524

¡ Semiconductor

This version: Jan. 1998

Previous version: Nov. 1996

MSM65524A/65P524

8-Bit Microcontroller with A/D Converter

GENERAL DESCRIPTION

The MSM65524A is a high-performance 8-bit microcontroller that employs OKI original nX-8/

50 CPU core. With a minimum instruction execution time of 400 ns (10MHz clock), the

MSM65524A is capable of high-speed processing, and includes 16K bytes of program memory,

384 bytes of data memory, timers, serial ports, an A/D converter and PWMs on chip. Also

available are the MSM65P524, which replaces the on-chip program memory with one-time

PROM, and the MSM65X524A, which uses the external program memory.

FEATURES

• Operating range

Operating frequency : 0 to 10MHz (VDD=4.5 to 5.5V)

0 to 5MHz (VDD=2.7 to 5.5V)

Operating voltage : 2.7 to 5.5V

Operating temperature : –40 to +85°C

• Memory space : 64K bytes

Internal program memory : 16K bytes

Internal data memory : 384 bytes

• Minimum instruction execution time : 400ns @ 10 MHz

• Powerful instruction set : 83 basic instructions

8/16-bit operation instructions

Bit manipulation instructions

Compound function instructions

• Abundant addressing modes

• Multiplication/division operation functions : 8 ¥ 8 Æ 16

16 ÷ 8 Æ 16 ... 8

• I/O port

Input-output port : 5 ports ¥ 8 bits

1 port ¥ 4 bits

Input port : 1 port ¥ 8 bits

• Timers : 8-bit auto-reload timer ¥ 2

16-bit auto-reload timer ¥ 1

Watchdog timer ¥ 1

• Counters : Time base counter ¥ 1

16-bit free-running counter ¥ 1

• Capture input : 1 channel

• Compare output : 2 channels

• Serial ports : Shift register ¥ 1

Serial port with baud rate generator

(UART/Synchronous) ¥ 1

• A/D converter : 8 bits ¥ 8 channels

• PWM : 8 bits ¥ 2 channels

PWM with auto-reload timer for period

setting

1/27

¡ Semiconductor MSM65524A/65P524

• External interrupts : 3

• Interrupt sources : 19

• Package options

64-pin plastic shrink DIP (SDIP64-P-750-1.78) : (Product name: MSM65524A-¥¥¥SS,

MSM65P524-¥¥¥SS)

64-pin plastic QFP (QFP64-P-1414-0.80-BK) : (Product name: MSM65524A-¥¥¥GS-BK,

MSM65P524-¥¥¥GS-BK)

68-pin plastic QFJ (PLCC) (QFJ68-P-S950-1.27): (Product name: MSM65524A-¥¥¥JS,

MSM65P524-¥¥¥JS)

¥¥¥ indicates the code number.

2/27

3/27

¡ Semiconductor MSM65524A/65P524

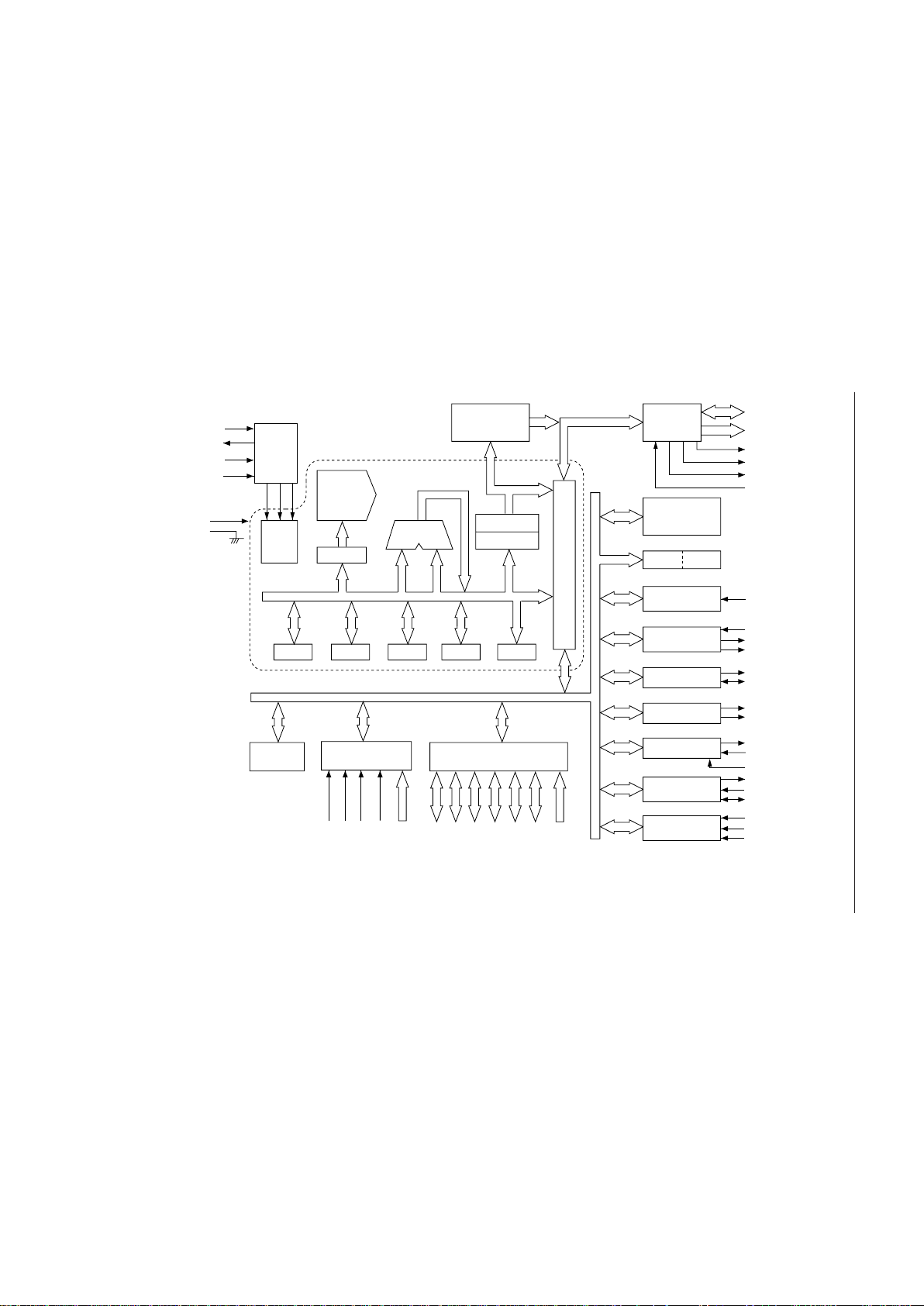

BLOCK DIAGRAM

OSC 0

OSC 1

RESET

HSTOP*

V

DD

GND

OSC

CONT.

ROM

(16K bytes)

EXT.MEM.

CONT.

CPU CORE

INST.

DEC.

T/C

IR

ALU

GMAR

PC

AR BR PSW SP LMAR

BUS

CONT.

I/O PORT

RAM

(384 bytes)

TBC WDT

16-bit TIMER

16-bit FRC

CAP¥1, CMP¥2

SIO

AD0-7*

A8-15*

RD

WR*

ALE

EA

T2CK*

GATE*

CAP*

CMP0*

CMP1*

TXD*

RXD*

P2 P3 P4 P5

* Secondary functions of ports

8

8

8

8

8

8-bit TIMER¥4**

T1OUT*

T0CK*

8-bit SHIFT-REG.

INTERRUPT CONT.

SFTO*

SFTI*

SFTCK*

INT0*

INT1*

INT2*

MUL/DIV

P1P0 P6

8-bit PWM¥2

PWM0*

PWM1*

8-bit A/D C ¥ 8ch

** One timer doubles as the SIO baud rate

generator, another doubles as a PWM

clock source.

AVDDVRHVRLAGND

AI0*- AI7*

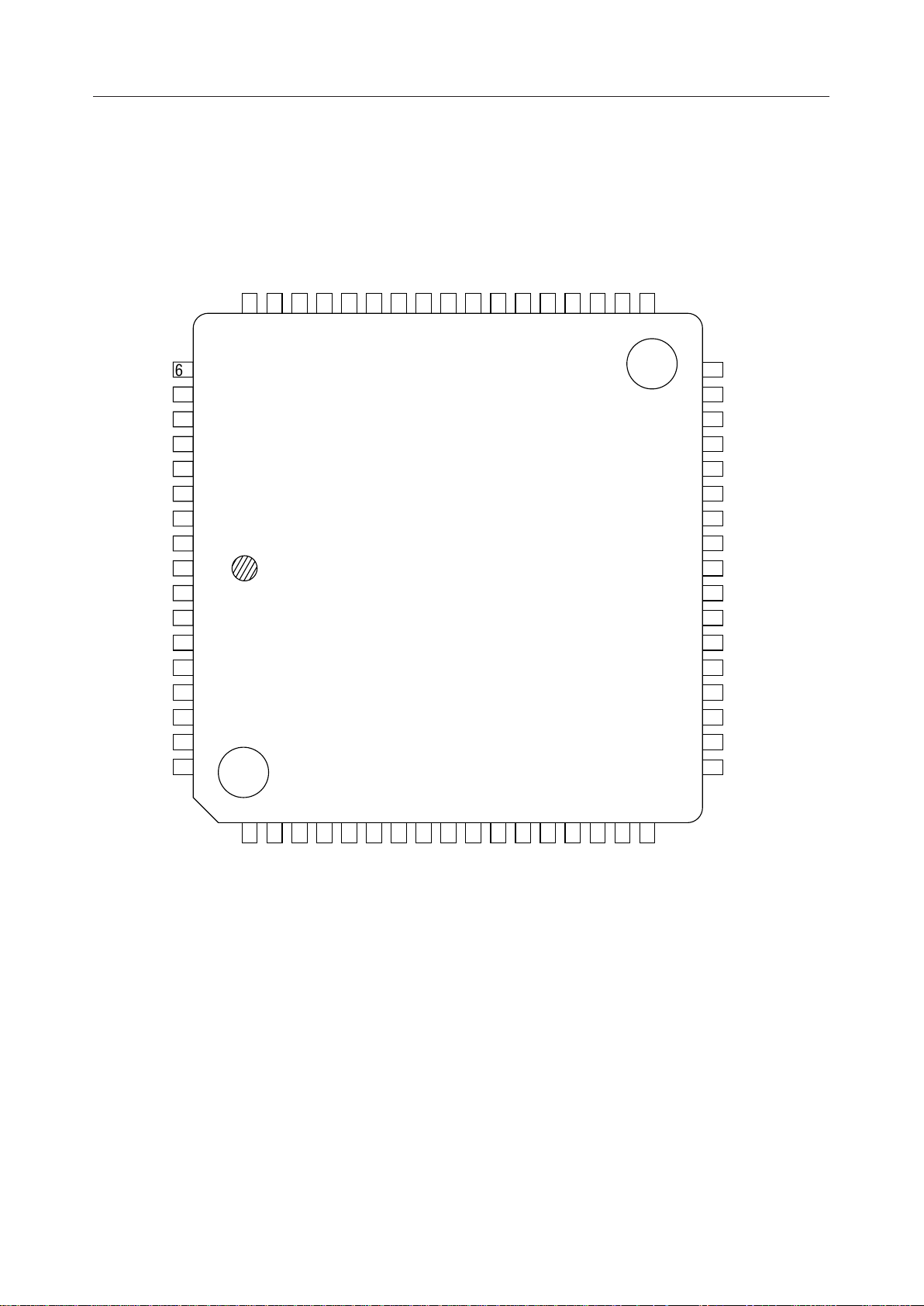

¡ Semiconductor MSM65524A/65P524

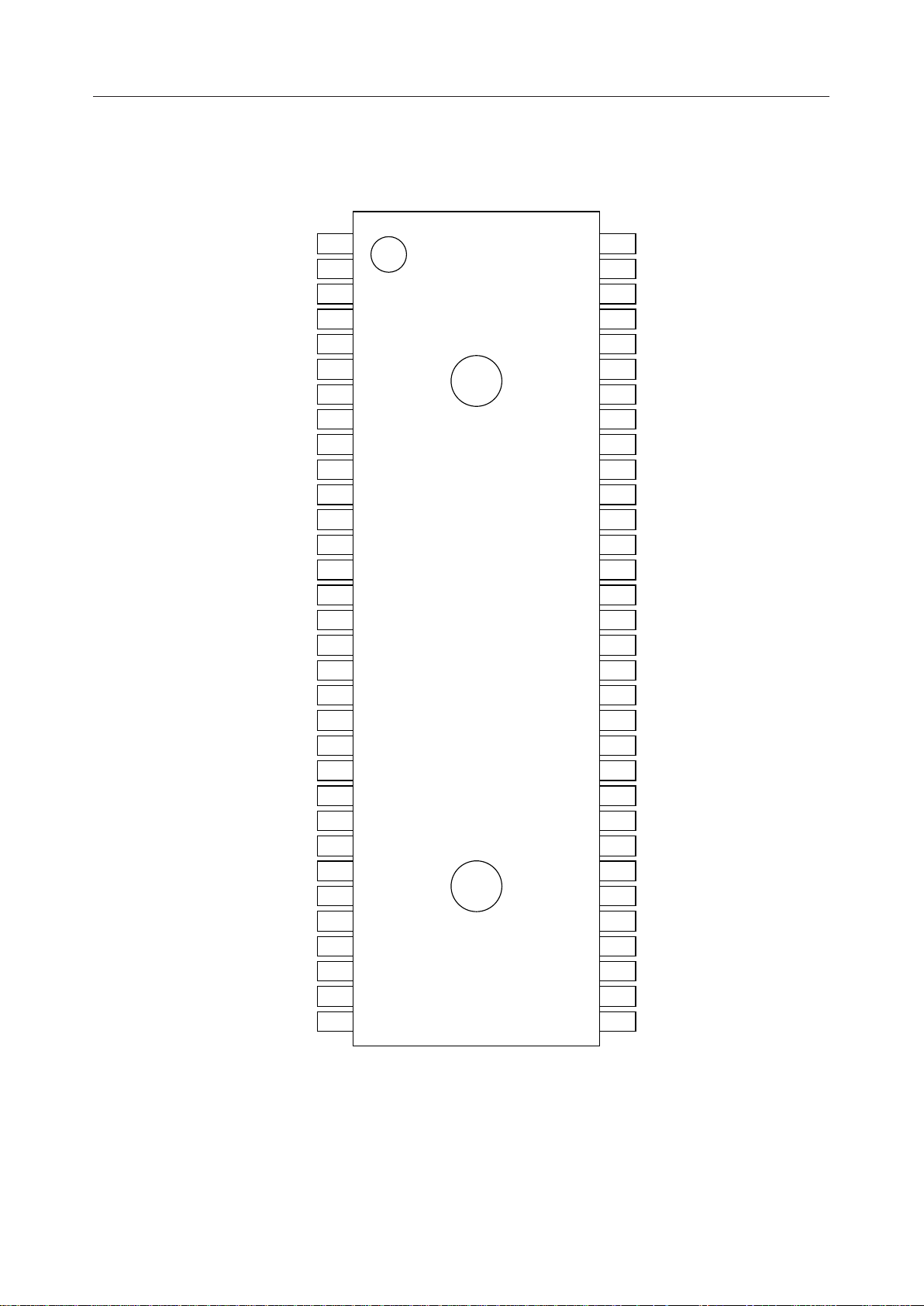

PIN CONFIGURATION (TOP VIEW)

P5.0/PWM0

P5.1/PWM1

P5.2

P5.3

P4.0

P4.1

P4.2

P4.3

P4.4

P4.5

P4.6

P4.7

P3.0/T2CK

P3.1/CAP

P3.2/CMP0

P3.3/CMP1

P3.4/INT2

P3.5/SFTO

P3.6/SFTI

P3.7/SFTCK

RESET P0.7/AD7

P2.0/RXD EA

P2.1/TXD ALE

P2.2/INT0 RD

P2.3/INT1/GATE P1.7/A15

P2.4/T0CK P1.6/A14

P2.5/HSTOP P1.5/A13

P2.6/WR P1.4/A12

P2.7/T1OUT P1.3/A11

OSC1 P1.2/A10

OSC0 P1.1/A9

GND P1.0/A8

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

V

DD

AV

DD

V

RH

V

RL

P6.7/AI7

P6.6/AI6

P6.5/AI5

P6.4/AI4

P6.3/AI3

P6.2/AI2

P6.1/AI1

P6.0/AI0

AGND

P0.0/AD0

P0.1/AD1

P0.2/AD2

P0.3/AD3

P0.4/AD4

P0.5/AD5

P0.6/AD6

64-Pin Plastic Shrink DIP

4/27

¡ Semiconductor MSM65524A/65P524

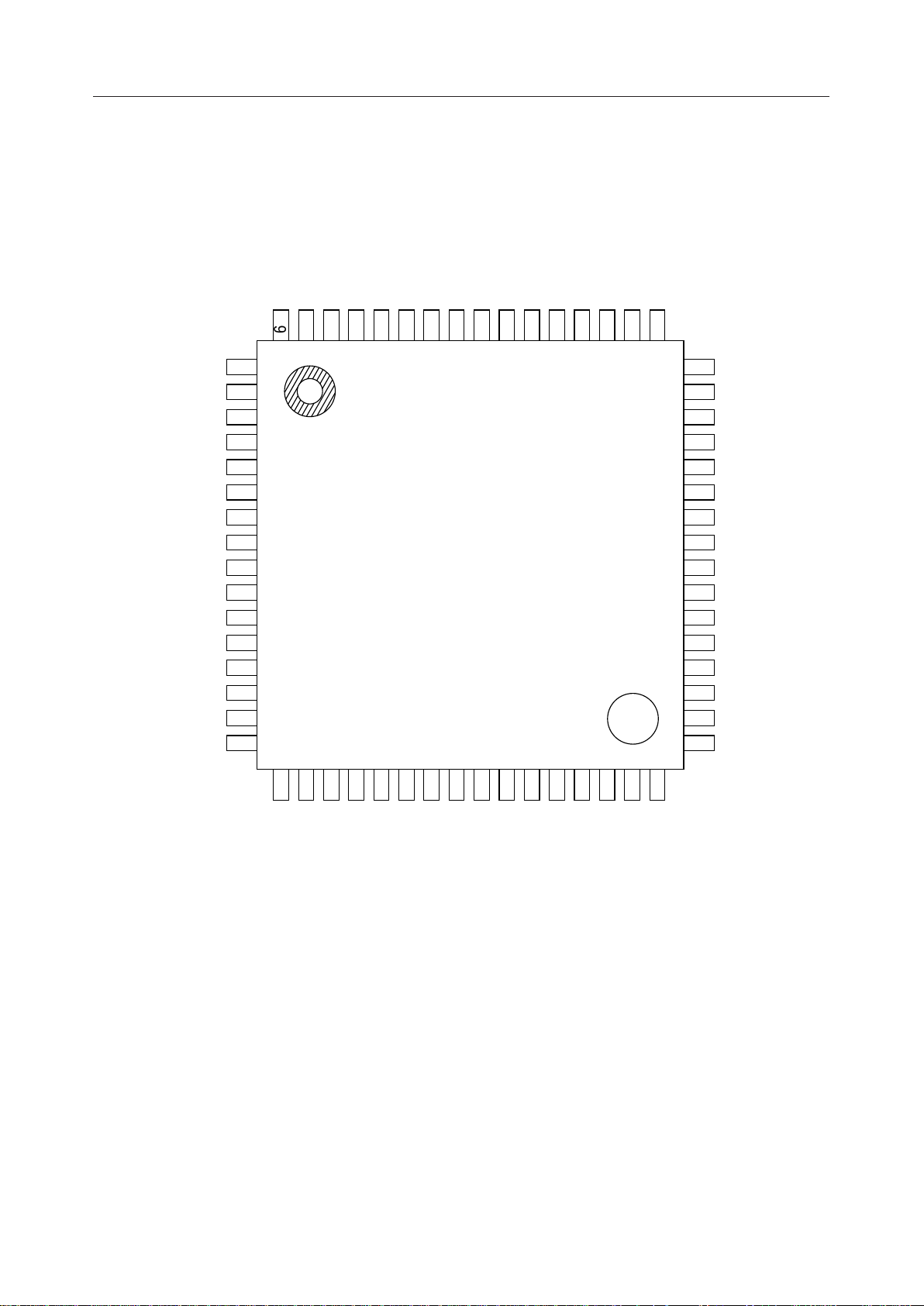

PIN CONFIGURATION (TOP VIEW) (Continued)

P4.4

P4.5

P4.6

P4.7

P3.0/T2CK

P3.1/CAP

P3.2/CMP0

P3.3/CMP1

P3.4/INT2

P3.5/SFTO

P3.6/SFTI

10

11

12P3.7/SFTCK

13RESET

14P2.0/RXD

15P2.1/TXD

16P2.2/INT0

P4.3

P4.2

P4.1

P4.0

P5.3

P5.2

P5.1/PWM1

64

63

62

61

60

59

58

1

2

3

4

5

6

7

8

9

DD

P5.0/PWM0

V

57

56

AVDDV

55

RH

54

53 VRL52 P6.7/AI7

54 P6.6/AI6

50 P6.5/AI5

49 P6.4/AI4

48

47

46

45

44

43

42

41

40

39

38

37 P0.6/AD6

36 P0.7/AD7

35 EA

34 ALE

33 RD

P6.3/AI3

P6.2/AI2

P6.1/AI1

P6.0/AI0

AGND

P0.0/AD0

P0.1/AD1

P0.2/AD2

P0.3/AD3

P0.4/AD4

P0.5/AD5

17

18

19

20

P2.4/T0CK

P2.3/INT1/GATE

P2.6/WR

P2.5/HSTOP

21

22

23

24

25

26

OSC0

GND

P1.0/A8

P1.1/A9

OSC1

P2.7/T1OUT

64-Pin Plastic QFP

27

28P1.3/A11

P1.2/A10

29P1.4/A12

30P1.5/A13

31P1.6/A14

32P1.7/A15

5/27

¡ Semiconductor MSM65524A/65P524

PIN CONFIGURATION (TOP VIEW) (Continued)

P6.3/AI3

P6.2/AI2

P6.1/AI1

P6.0/AI0

AGND

P0.0/AD0

P0.1/AD1

60

59

58

57

56

55

P0.2/AD2

54

53

P0.3/AD3

52

P0.4/AD4

51

P0.5/AD5

50

P0.6/AD6

49

P0.7/AD7EAALE

48

47

46

45

RD

44

P6.4/AI4

P6.5/AI5

P6.6/AI6

P6.7/AI7

V

RL

V

RH

AV

DD

NC

V

DD

P5.0/PWM0

P5.1/PWM1

P5.2

P5.3

P4.0

P4.1

P4.2

P4.3

61

62

63

64

65

66

67

68

P1.7/A15

43

P1.6/A14

42

P1.5/A13

41

P1.4/A12

40

P1.3/A11

39

P1.2/A10

38

P1.1/A9

37

P1.0/A8

36

1

2

3

4

5

6

7

8

9

NC

35

GND

34

OSC0

33

OSC1

32

P2.7/T1OUT

31

P2.6/WR

30

P2.5/HSTOP

29

P2.4/T0CK

28

P2.3/INT1/GATE

27

10

P4.4

11

P4.5

12

13

14

15

16

17

18

P4.6

P4.7

P3.0/T2CK

P3.1/CAP

P3.2/CMP0

NC NC

P3.3/CMP1

NC: No-connection pin

68-Pin Plastic QFJ (PLCC)

19

20

P3.4/INT2

P3.6/SFTI

P3.5/SFTO

21

22

P3.7/SFTCK

23

24

RESET

P2.0/RXD

25

26

P2.1/TXD

P2.2/INT0

6/27

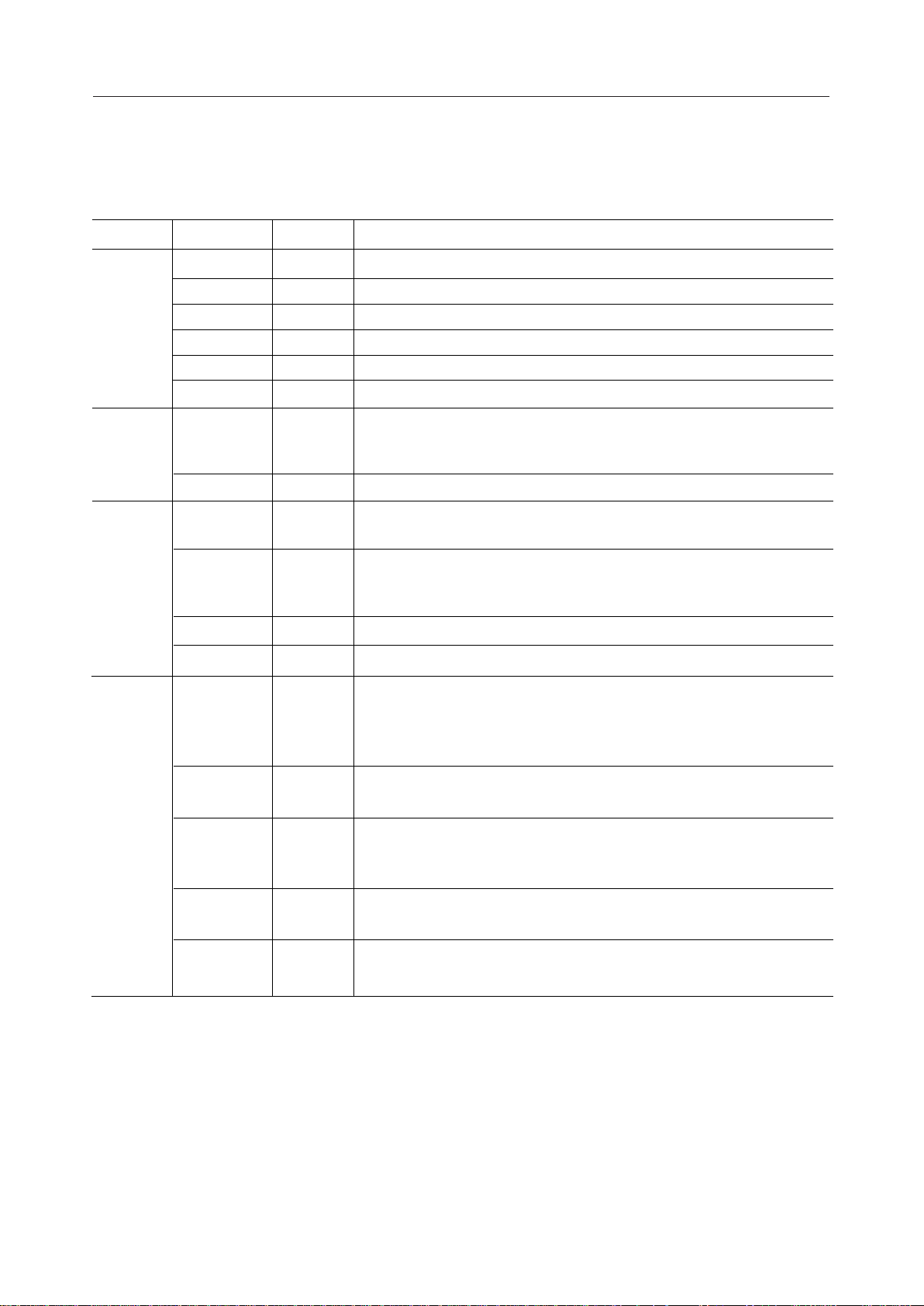

¡ Semiconductor MSM65524A/65P524

PIN DESCRIPTION

Basic Functions

Function Symbol Type Description

Power

Supply

Oscillation

Control

V

DD

GND

AV

DD

AGND

V

RH

V

RL

OSC0

—

—

—

—

—

—

I

+5V digital power supply

0V digital ground

+5V analog power supply

0V analog ground

+5V analog reference voltage

0V analog reference voltage

System clock input pin. Quartz oscillator or ceramic oscillator is

connected between OSC0 and OSC1. For external clock, input at OSC0,

leaving OSC1 open.

OSC1

RESET System reset input (program starts from address 0040H);

O

I

System clock output pin

internal pull-up resistance

EA Program memory select input pin.

I

"L" level input for external program memory; "H" level input for internal

program memory.

RD Read strobe signal during external memory accessO

ALE Address latch signal during external memory accessO

PORT 0 8-bit Input-output port

I/O

During external memory access, becomes address/data bus for address

output, instruction fetch or data read/write along with ALE, RD and WR

pins.

Port

PORT 1 8-bit Input-output port

I/O

Address bus during external memory access

PORT 2

PORT 3

I/O

8-bit Input-output port ¥ 3. Secondary functions shown in following table

are added for ports 2 and 3.

PORT 4

PORT 5 4-bit Input-output port

I/O

Secondary functions shown in following table are added for port 5.

PORT 6 8-bit Input port

I

Functions as analog input channel during A/D conversion.

7/27

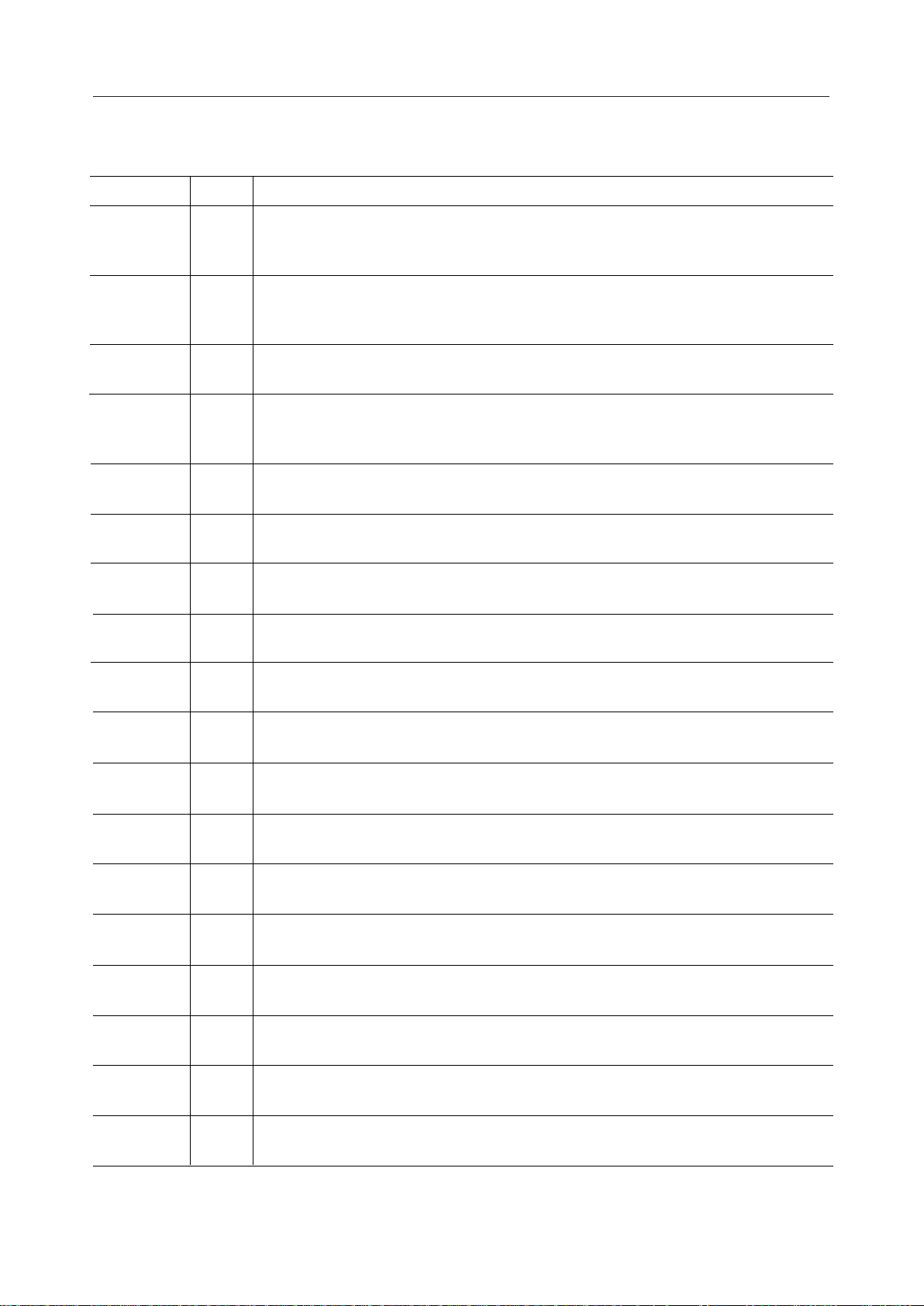

¡ Semiconductor MSM65524A/65P524

Secondary Functions

Symbol Type Description

RXD P2.0 secondary function

TXD P2.1 secondary function

INT0 P2.2 secondary function

INT1/GATE P2.3 secondary functions

T0CK P2.4 secondary function

HSTOP P2.5 secondary function

WR P2.6 secondary function

T1OUT P2.7 secondary function

I/O

UART: Input pin for serial port receive data.

Synchronous: Input/output pin for serial port transmit/receive data.

O

UART: Output pin for serial port transmit data.

Synchronous: Output pin for serial port synchronizing clock.

I

External interrupt 0 input pin.

I

External interrupt 1 input pin. Also used as input pin for gate signal

for timer 0 count enable/disable.

I

Timer 0 external clock input pin.

I

Hard stop mode input pin; stops system clock oscillation with "L" level input.

O

Write strobe signal output pin during external data memory access.

O

Output pin for signal that 2-divided timer 1 overflow.

T2CK P3.0 secondary function

CAP P3.1 secondary function

CMP0 P3.2 secondary function

CMP1 P3.3 secondary function

INT2 P3.4 secondary function

SFTO P3.5 secondary function

SFTI P3.6 secondary function

SFTCK P3.7 secondary function

PWM0 P5.0 secondary function

I

Timer 2 external clock input pin.

I

Capture trigger input pin.

O

Compare output channel 0 output pin.

O

Compare output channel 1 output pin.

I

External interrupt 2 input signal.

O

Shift register data output pin.

I

Shift register data input pin.

I/O

Shift register synchronizing clock input/output pin.

O

PWM channel 0 output pin.

PWM1 P5.1 secondary function

O

PWM channel 1 output pin.

8/27

¡ Semiconductor MSM65524A/65P524

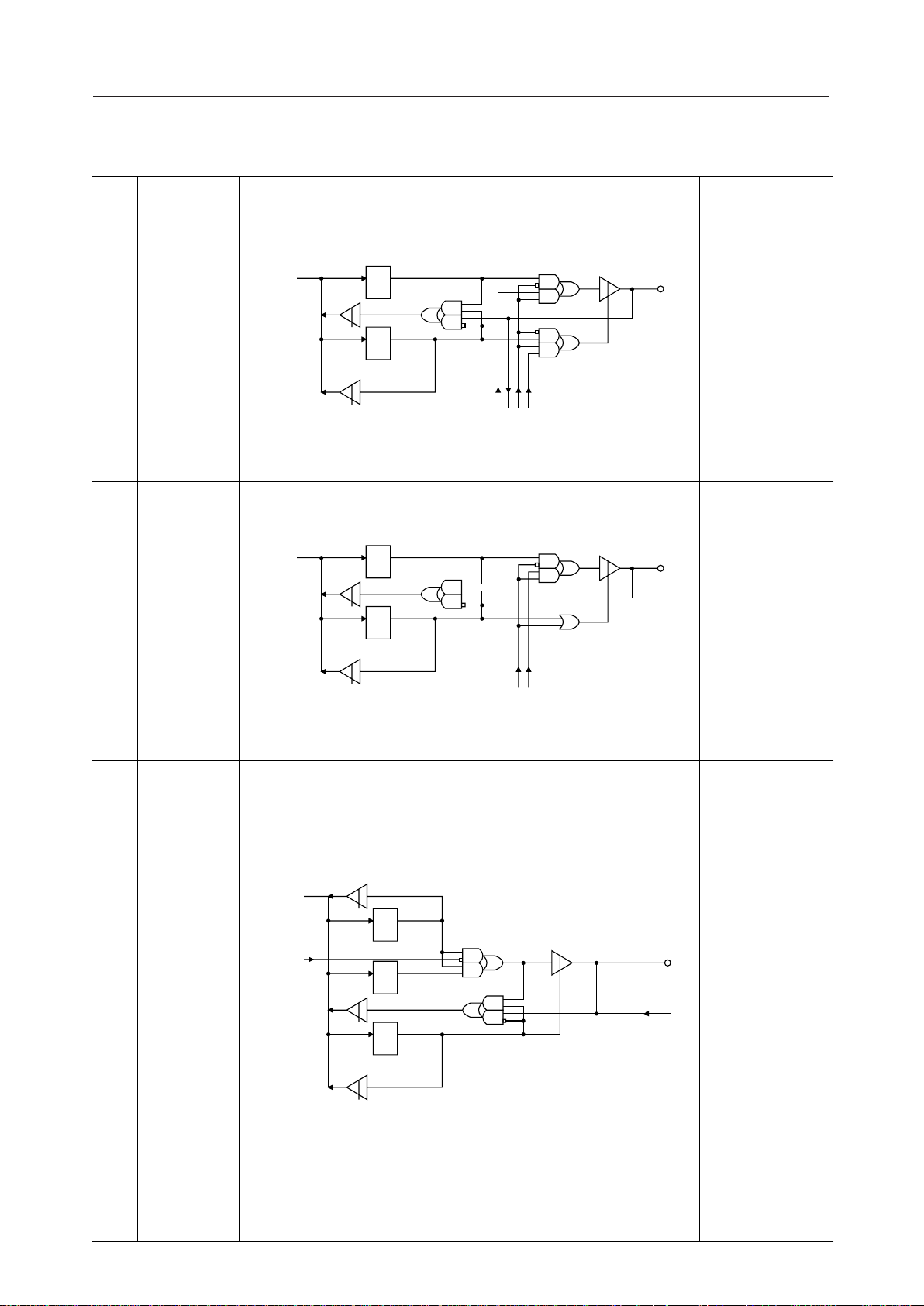

Port Circuit Configuration

Type Port

P0.0/AD0 to

1

P0.7/AD7

P1.0/A8 to

2

P1.7/A15

Data Bus

Data Bus

Circuit Configuration

P0D

P0

DIR

External Memory Control

P1D

P1

DIR

PORT0

PORT1

Electrical Characteristics

(V

=5V)

DD

"H" Input Voltage:

• V

=2.4V

IH

"L" Input Voltage:

• V

=0.8V

IL

"H" Output Voltage:

• V

=3.75V

OH

• I

=–400mA

OH

"L" Output Voltage:

• V

=0.4V

OL

• I

=3.2mA

OL

"H" Input Voltage:

• V

=2.4V

IH

"L" Input Voltage:

• V

=0.8V

IL

"H" Output Voltage:

• V

=3.75V

OH

• I

=–200mA

OH

3

P2.0/RXD,

P2.1/TXD,

P2.6/WR,

P2.7/T1OUT,

P3.2/CMP0,

P3.3/CMP1,

P3.5/SFTO,

P3.7/SFTCK,

P5.0/PWM0,

P5.1/PMW1

Data Bus

Secondary

Output

Function

Px

MOD

PxD

Px

DIR

External Memory Control

PORTx

Secondary

Input

Function

(x=2 to 5)

"L" Output Voltage:

• V

=0.4V

OL

• I

=1.6mA

OL

"H" Input Voltage:

• V

=2.4V

IH

"L" Input Voltage:

• V

=0.8V

IL

P2.6/WR

"H" Output Voltage:

• V

=3.75V

OH

• I

=–400mA

OH

"L" Output Voltage:

• V

=0.4V

OL

• I

=3.2mA

OL

Ports other than

P2.6/WR

"H" Output Voltage:

• V

=3.75V

OH

• I

=–200mA

OH

"L" Output Voltage:

• V

=0.4V

OL

• I

=1.6mA

OL

9/27

Loading...

Loading...