OKI MSM6597A-xxxGS-AK, MSM6597A-xxxGS-K Datasheet

E2D0040-39-22

¡ Semiconductor MSM6597A-xxx

¡ Semiconductor

This version: Feb. 1999

Previous version: May. 1997

MSM6597A-xxx

3-Mbit Serial Voice ROM

GENERAL DESCRIPTION

The MSM6597A is a MSM6597 short TAT process version.

The MSM6597A is a serial voice ROM with a 1,048,576-word ¥ 1-bit ¥ 3-bank configuration.

The MSM6597A has a built-in internal address-generating circuit. A single, external clock input

allows continuous, serial read operations. The internal addresses are automatically incremented

by 1 by read operation. 1024 words in X direction and 1024 words in Y direction can be addressed

by inputting external serial addresses. Banks are switched with CS1, CS2, and CS3.

A read and playback device with predetermined messages can easily be configured by storing voice

data into the MSM6597A and by combining it with one of Oki's recording and playback ICs and with

one of Oki's serial registers.

A serial register is required to drive the MSM6597A when used with the MSM6388 or MSM6588. (The

MSM6597A does not operate without a serial register.)

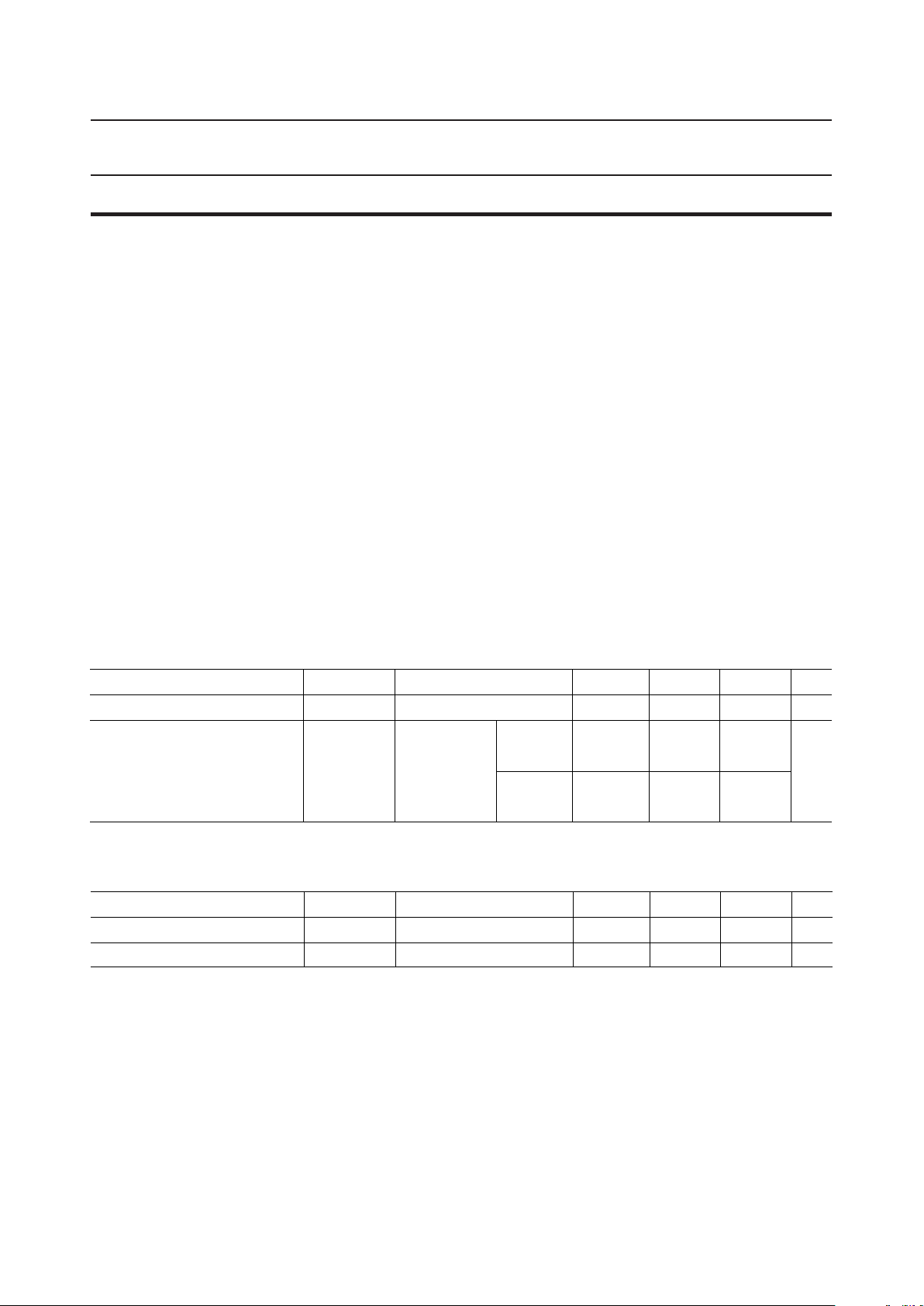

The major differences between the MSM6597A and MSM6597 are shown below.

MSM6597A DC Characteristics

V

= 3.5 to 5.5 V, Ta = –40 to +85°C

DD

Parameter Symbol Condition Min. Max. Unit

Current Consumption (1) I

Current Consumption (2) I

DD

DS

t

= 2.5 ms— 20mA

RDC

CS1 = CS2 = CS3

= V

– 0.2 V

DD

Ta = –40

to +70°C

Ta = –40

to +85°C

—

—

Typ.

9

—

MSM6597 DC Characteristics

= 3.5 to 5.5 V, Ta = –40 to +85C°

V

DD

Parameter Symbol Condition Min. Max. Unit

Current Consumption (1) I

Current Consumption (2) I

DD

DS

t

= 2.5 ms — 15 mA

RDC

CS1 = CS2 = CS3 = V

– 0.2 V

DD

Typical values are at V

—10mA—

Typ.

—

= 5.0 V, Ta = 25°C

DD

For other detailes, refer to individual sections in this data sheet.

10

mA

50—

FEATURES

• Configuration : 1,048,576 words ¥ 1 bit ¥ 3 banks

• Serial access : Read cycle time of 2.5 ms

• Shorter-TAT processing

• Power-supply voltage : 5 V single supply

• Package options :

24-pin plastic SOP (SOP24-P-430-1.27-K) (Product name : MSM6597A-xxxGS-K)

30-pin plastic SSOP (SSOP30-P-56-0.65-K) (Product name : MSM6597A-xxxGS-AK)

1/9

¡ Semiconductor MSM6597A-xxx

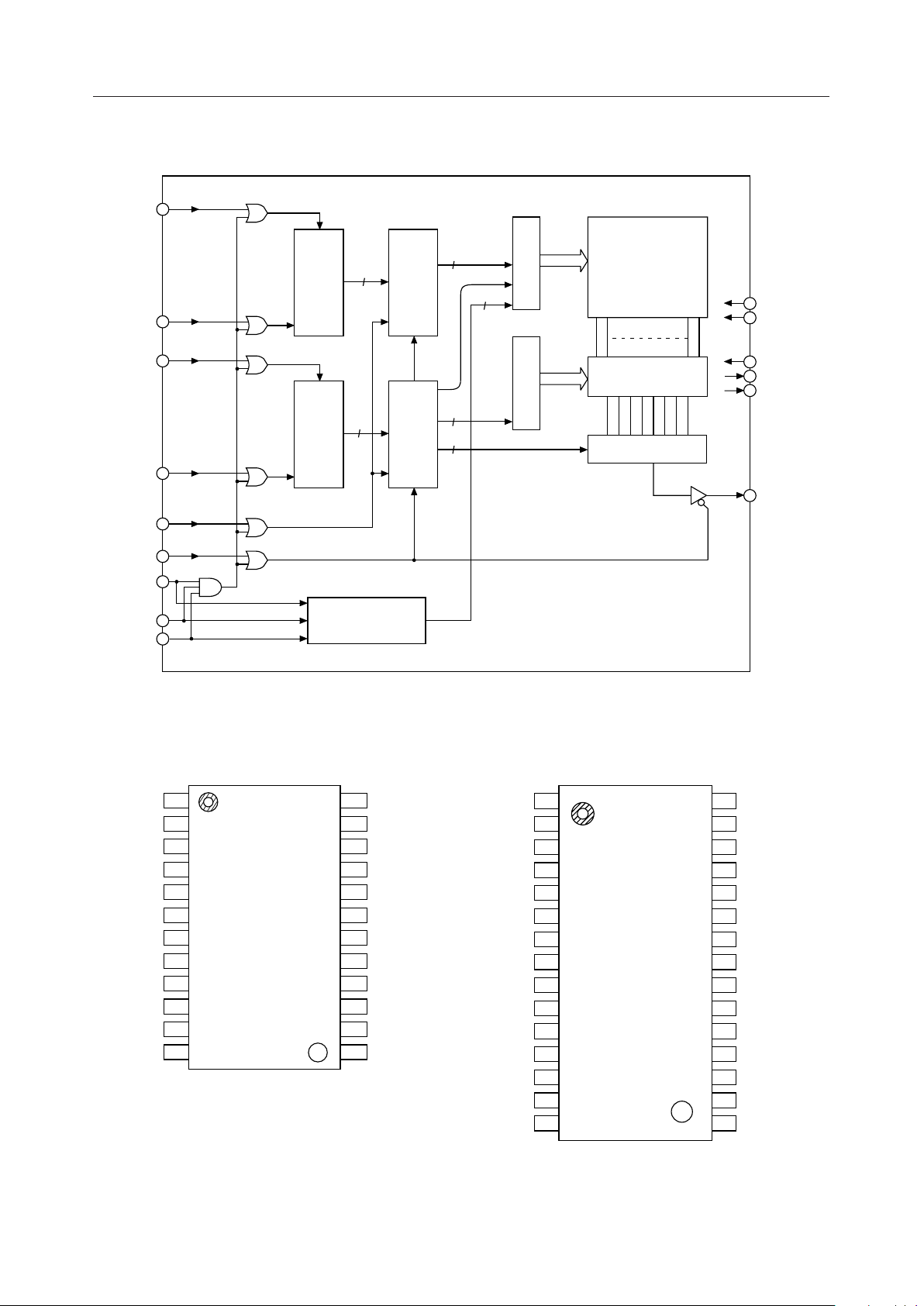

BLOCK DIAGRAM

SADX

SASX

SADY

SASY

TAS

RDCK

CS1

CS2

CS3

Sin

10

REGISTER

X-ADDRESS

CK

Sin

10

REGISTER

Y-ADDRESS

CK

CS CONTROLLER

COUNTER

X-ADDRESS

LD

CK

COUNTER

Y-ADDRESS

LD

CK

10

6

3

Memory Cell

1

2

X-DECODERY-DECODER

Matrix

393216 x 8

V

DD

GND

TEST

MULTIPLEXER

TESTO1

TESTO2

MULTIPLEXER

DOUT

PIN CONFIGURATION (TOP VIEW)

SADY

SASY

CS2

CS1

NC

NC

NC

NC

SADX

SASX

TAS

V

DD

1

2

3

4

5

6

7

8

9

10

11

12

NC : No connection

24-Pin Plastic SOP

24

23

22

21

20

19

18

17

16

15

14

13

GND

CS3

DOUT

TESTO1

NC

NC

NC

NC

NC

RDCK

TESTO2

TEST

SADY

SASY

CS2

NC

CS1

NC

NC

NC

NC

NC

NC

SADX

SASX

TAS

V

DD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

NC : No connection

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

GND

CS3

DOUT

TESTO1

NC

NC

NC

NC

NC

NC

NC

NC

RDCK

TESTO2

TEST

30-Pin Plastic SSOP

2/9

¡ Semiconductor MSM6597A-xxx

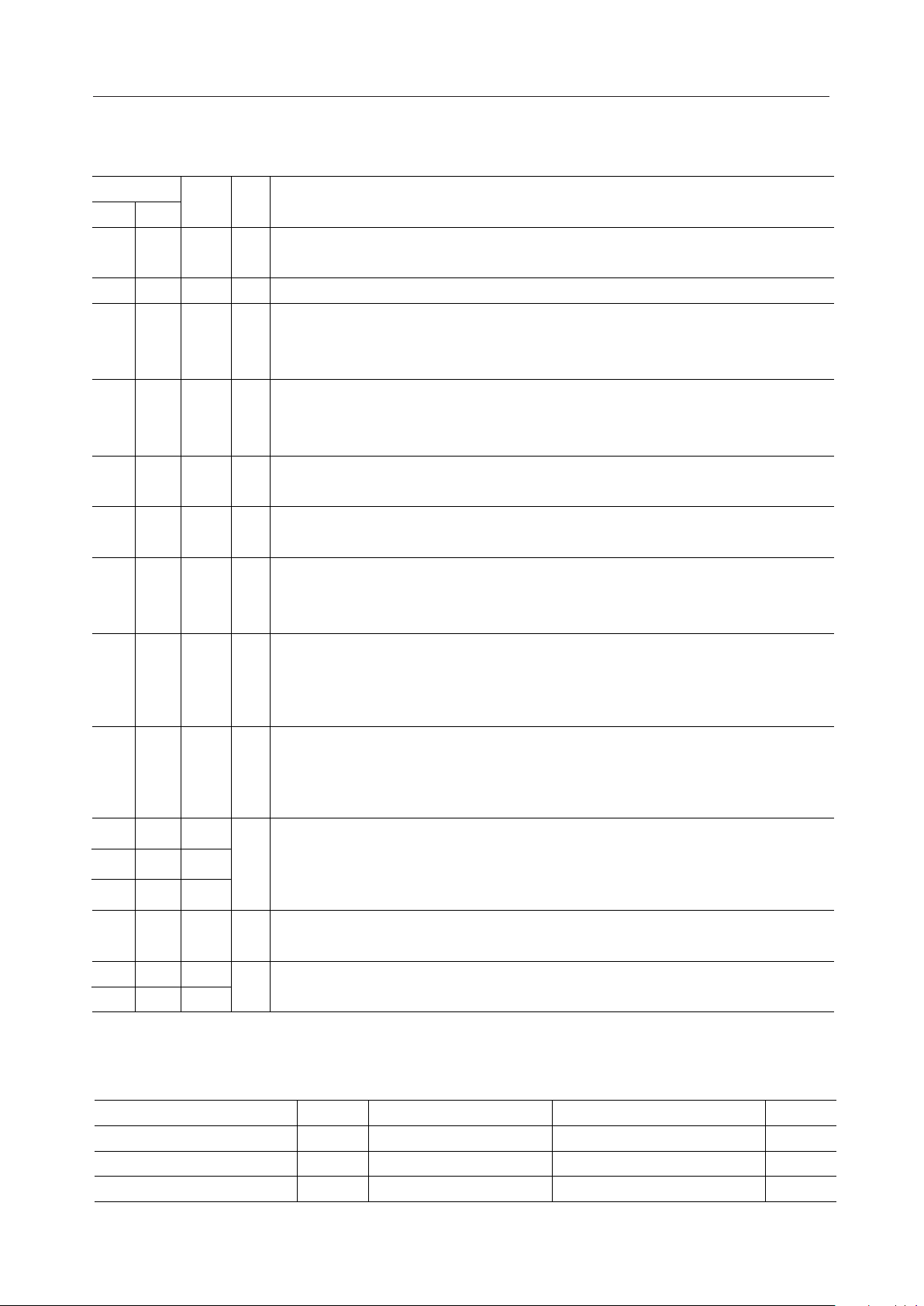

PIN DESCRIPTIONS

12

Pin

V

DD

GND

Type

Power supply pin. Insert a bypass capacitor of 0.1 mF or more between this pin and the

—

GND pin.

— Ground pin

Symbol

SSOPSOP

15

3024

Description

(SERIAL ADDRESS) This pin inputs the starting X address of a read operation.

Addressing in units of 1024 words is possible. The 1024-word address data can be

SADX

129

I

input as 10-bit (AX0 - AX9) serial data via the SADX pin.

(SERIAL ADDRESS) This pin inputs the starting Y address of a read operation.

11

SADY

Addressing in units of 1024 words is possible. The 1024-word address data can be

I

input as 10-bit (AY0 - AY9) serial data via the SADY pin.

(SERIAL ADDRESS STROBE) This is the clock input pin which is used to store the

1310

SASX

I

serial address data of the X address into the device's internal register.

(SERIAL ADDRESS STROBE) This is the clock input pin which is used to store the

22

ISASY

serial address data of the Y address into the device's internal register.

(ADDRESS TRANSFER STROBE) This is the input pin for loading the serial address

TAS

1411

data into the internal address counter.

I

The X and Y addresses are stored at the falling edge of TAS.

(READ CLOCK) This is the clock input pin for reading information out of the data

RDCK

1815

register. Internal operation starts at the falling edge of RDCK. The information in the

I

data register is output on the DOUT pin. The internal address counter is automatically

incremented by 1 at the falling edge of RDCK.

(DATA OUT) The data output pin is always kept in a high-impedance state when CS1,

CS2, and CS3 are all kept "H" or when RDCK is kept "H". This pin reflects the "H" or "L"

O

level data being read, and the current data is hold until RDCH is asserted High.

(CHIP SELECT) When either CS1, CS2, or CS3 is "L", bank 1, bank 2, or bank 3 is

selected, respectively. Setting all three signals "H" disables all input and output

I

pins. These pins enable parallel use of multiple serial voice ROMs by connecting the

data output pins.

Pin for testing. Apply "L" level.

I

O Pins for testing. Leave these pins open.

4

3

23

2822

29

1613

2721

1714

5

3

DOUT

CS1

CS2

CS3

TEST

TESTO1

TESTO2

ABSOLUTE MAXIMUM RATINGS

Parameter Symbol Condition Rating Unit

Power Supply Voltage V

Input Voltage V

Storage Temperature T

DD

IN

STG

Ta = 25°C –0.3 to +7.0 V

Ta = 25°C –0.3 to VDD+0.3 V

— –55 to +150 °C

3/9

Loading...

Loading...