NSC COPC912WM, COPC912N Datasheet

TL/DD12060

COP912C/COP912CH 8-Bit Microcontroller

August 1996

COP912C/COP912CH 8-Bit Microcontroller

General Description

The COP912C/COP912CH are members of the COP8

TM

8-bit MicroController family. They are fully static Microcontrollers, fabricated using double-metal silicon gate microCMOS technology. These low cost MicroControllers are

complete microcomputers containing all system timing, interrupt logic, ROM, RAM, and I/O necessary to implement

dedicated control functions in a variety of applications. Features include an 8-bit memory mapped architecture,

MICROWlRE

TM

serial I/O, a 16-bit timer/counter with capture register and a multi-sourced interrupt. Each I/O pin has

software selectable options to adapt the device to the specific application. The device operates over voltage ranges

from 2.3V to 4.0V (COP912C) and from 4.0V to 5.5V

(COP912CH). High throughput is achieved with an efficient,

regular instruction set operating at a minimum of 2 ms per

instruction rate.

Key Features

Y

Lowest cost COP8 microcontroller

Y

16-bit multi-function timer supporting

Ð PWM mode

Ð External event counter mode

Ð Input capture mode

Y

768 bytes of ROM

Y

64 bytes of RAM

I/O Features

Y

Memory mapped I/O

Y

Software selectable I/O options (TRI-STATEÉOutput,

Push-Pull Output, Weak Pull-Up Input, High Impedance

Input)

Y

Schmitt trigger inputs on Port G

Y

MICROWIRE/PLUSTMSerial I/O

Y

Packages: 20 DIP/SO with 16 I/O pins

CPU/Instruction Set Features

Y

Instruction cycle time of 2 ms for COP912CH and

2.5 ms for COP912C

Y

Three multi-sourced interrupts servicing

Ð External Interrupt with selectable edge

Ð Timer interrupt

Ð Software interrupt

Y

Versatile and easy to use instruction set

Y

8-bit Stack Pointer (SP)Ðstack in RAM

Y

Two 8-bit Register Indirect Memory Pointers (B, X)

Fully Static CMOS

Y

Low current drain (typicallyk1 mA)

Y

Single supply operation: 2.3V to 4.0V or 4.0V to 5.5V

Y

Temperature range: 0§Ctoa70§C

Development Support

Y

Emulation and OTP devices

Y

Real time emulation and full program debug offered by

MetaLink Development System

Applications

Y

Electronic keys and switches

Y

Remote Control

Y

Timers

Y

Alarms

Y

Small industrial control units

Y

Low cost slave controllers

Y

Temperature meters

Y

Small domestic appliances

Y

Toys and games

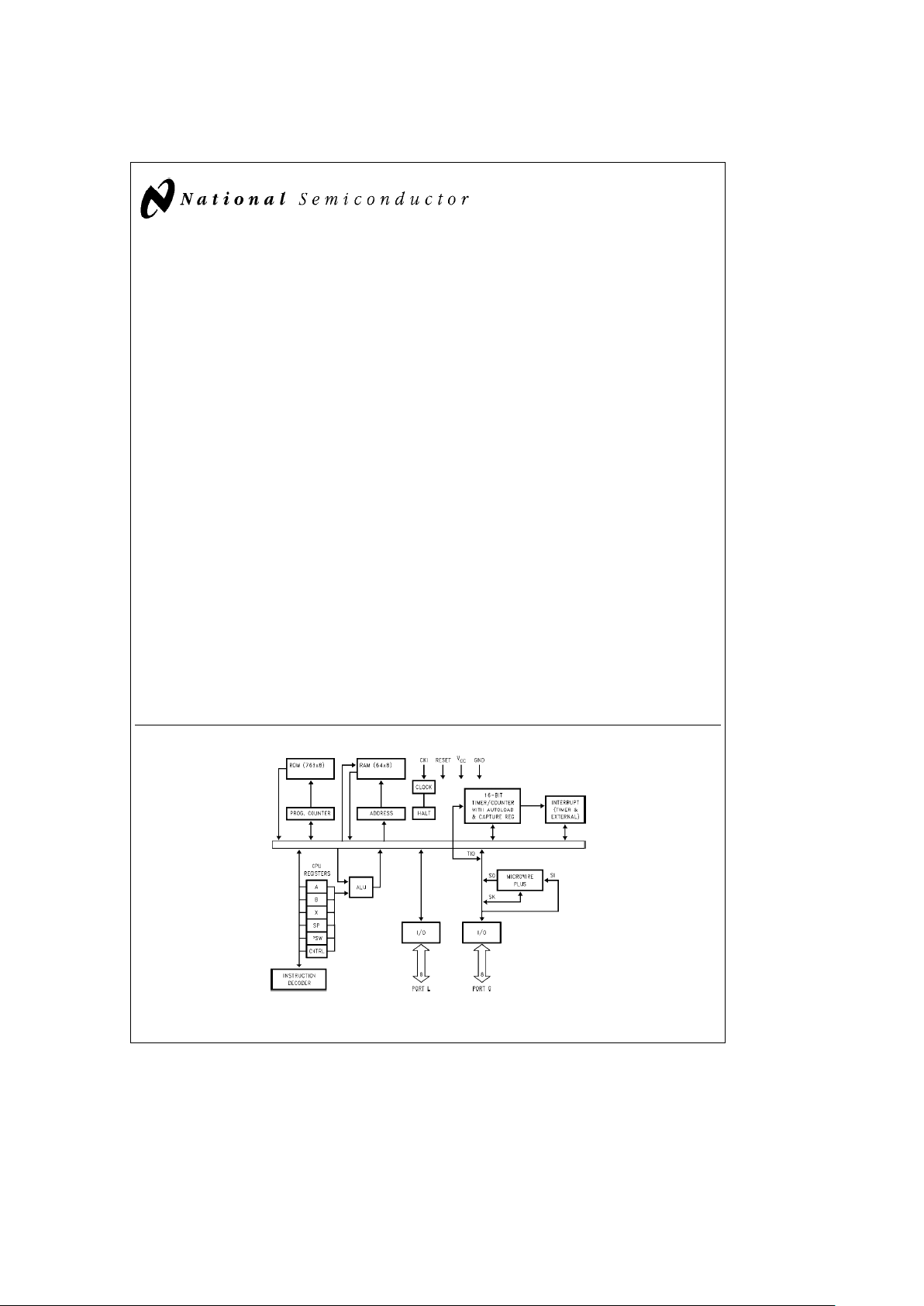

Block Diagram

TL/DD/12060– 1

TRI-STATEÉis a registered trademark of National Semiconductor Corporation.

COP8

TM

, MICROWIRE/PLUSTM, WATCHDOGTMand MICROWIRETMare trademarks of National Semiconductor Corporation.

PC

É

is a registered trademark of International Business Machines Corp.

iceMaster

TM

is a trademark of MetaLink Corporation.

C

1996 National Semiconductor Corporation RRD-B30M96/Printed in U. S. A.

http://www.national.com

Absolute Maximum Ratings

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales

Office/Distributors for availability and specifications.

Supply Voltage (V

CC

) 6.0V

Voltage at Any Pin

b

0.3V to V

CC

a

0.3V

Total Current into V

CC

Pin (Source) 80 mA

Total Current out of GND Pin (Sink) 80 mA

Storage Temperature Range

b

65§Ctoa150§C

Note:

Absolute maximum ratings indicate limits beyond which damage

to the device may occur. DC and AC electrical specifications are not

ensured when operating the device at absolute maximum ratings.

DC Electrical Characteristics COP912C/COP912CH; 0

§

CsT

A

s

a

70§C unless other specified

Parameter Conditions Min Typ Max Units

Operating Voltage

912C 2.3 4.0 V

912CH 4.0 5.5 V

Power Supply Ripple 1 (Note 1) Peak to Peak 0.1 V

CC

V

Supply Current (Note 2)

CKIe4 MHz V

CC

e

5.5V, tce2.5 ms 6.0 mA

CKI

e

4 MHz V

CC

e

4.0V, tce2.5 ms 2.5 mA

HALT Current V

CC

e

5.5V, CKIe0 MHz

k

18mA

INPUT LEVELS (VIH,VIL)

Reset, CKI:

Logic High 0.9 V

CC

V

Logic Low 0.1 V

CC

V

All Other Inputs

Logic High 0.7 V

CC

V

Logic Low 0.2 V

CC

V

Hi-Z Input Leakage/TRI-STATE Leakage V

CC

e

5.5V

b

2

a

2 mA

Input Pullup Current V

CC

e

5.5V 250 mA

G-Port Hysteresis 0.05 V

CC

0.35 V

CC

V

Output Current Levels

Source (Push-Pull Mode) V

CC

e

4.0V, V

OH

e

3.8V 0.4 mA

V

CC

e

2.3V, V

OH

e

1.8V 0.2 mA

Sink (Push-Pull Mode) V

CC

e

4.0V, V

OL

e

1.0V 4.0 mA

V

CC

e

2.3V, V

OL

e

0.4V 0.7 mA

Allowable Sink/Source Current Per Pin 3mA

Input Capacitance (Note 3) 7pF

Load Capacitance on D2 (Note 3) 1000 pF

Note 1: Rate of voltage change must be less then 0.5 V/ms.

Note 2: Supply current is measured after running 2000 cycles with a square wave CKI input, CKO open, inputs at rails and outputs open.

Note 3: Characterized, not tested.

TL/DD/12060– 2

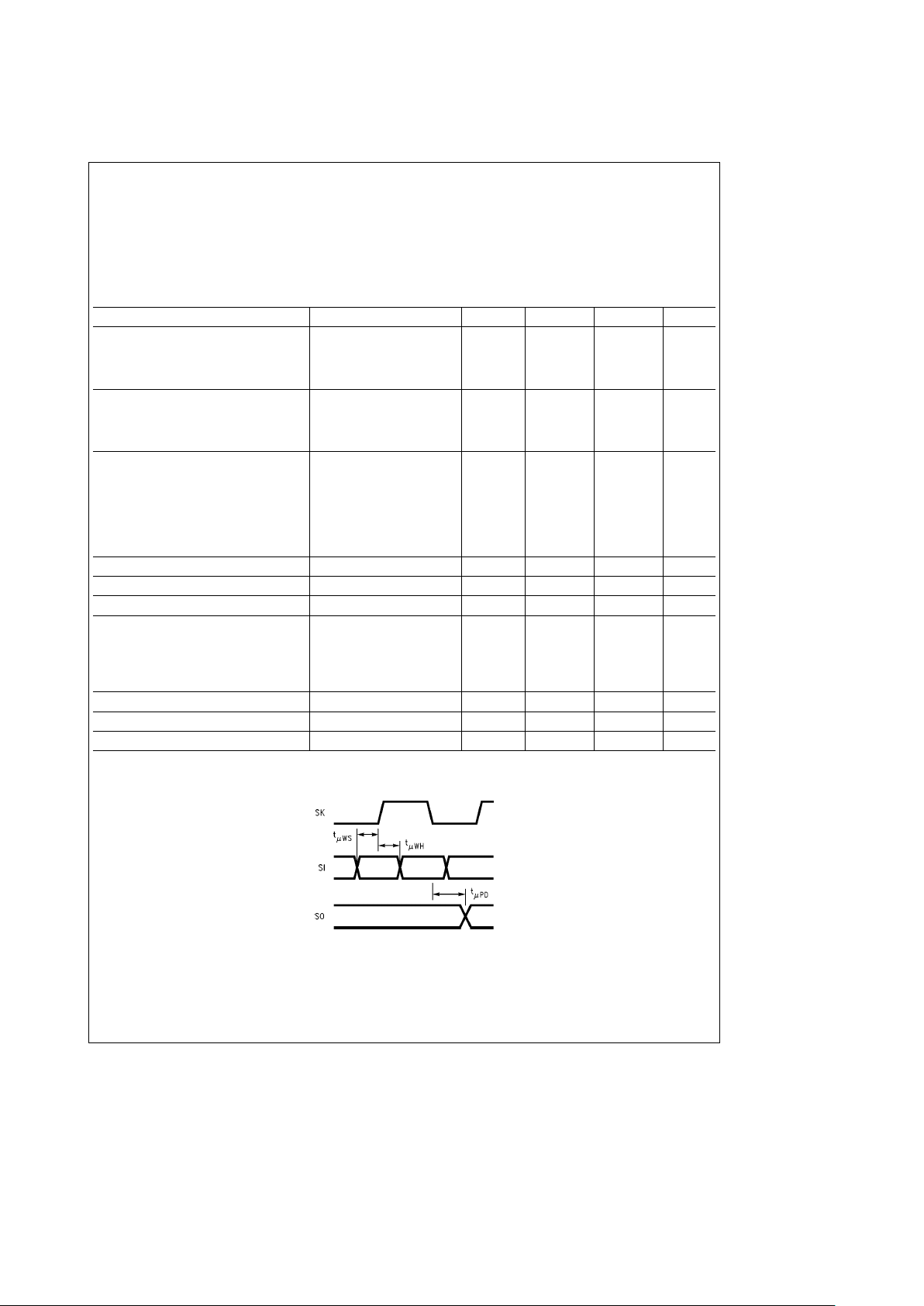

FIGURE 1. MICROWIRE/PLUS Timing

http://www.national.com 2

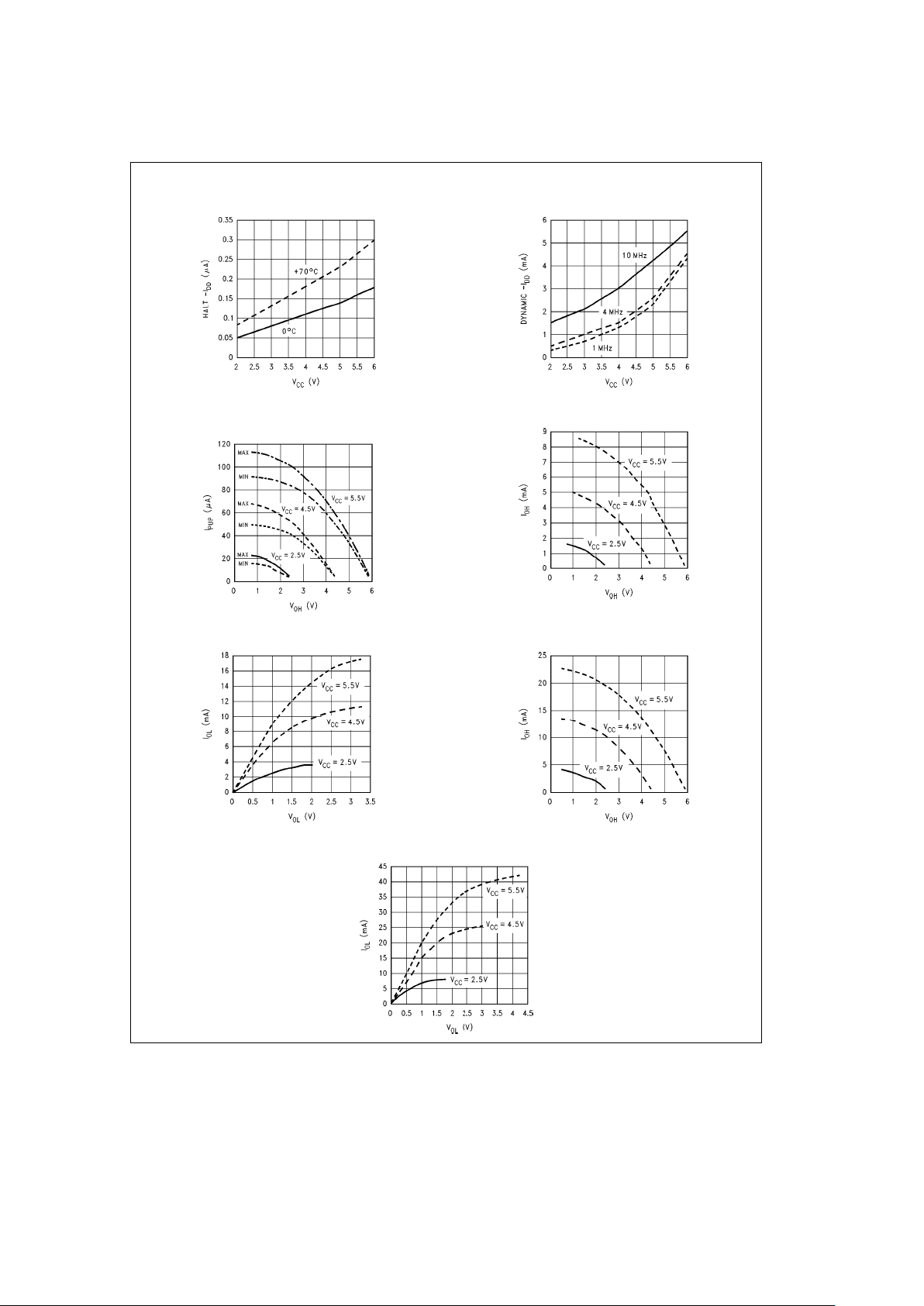

Typical Performance Characteristics

HaltÐI

DD

TL/DD/12060– 16

DynamicÐIDD(Crystal Clock Option)

TL/DD/12060– 17

Port L/G Weak Pull-Up

Source Current

TL/DD/12060– 18

Port L/G Push-Pull Source Current

TL/DD/12060– 19

Port L/G Push-Pull Sink Current

TL/DD/12060– 20

Port D Source Current

TL/DD/12060– 21

Port D Sink Current

TL/DD/12060– 22

http://www.national.com3

AC Electrical Characteristics COP912C/COP912CH; 0

§

CsT

A

s

a

70§C unless otherwise specified

Parameter Conditions Min Typ Max Units

INSTRUCTION CYCLE TIME (tc)

Crystal/Resonator 4.0V

s

V

CC

s

5.5V 2 DC ms

2.3V

s

V

CC

k

4.0V 2.5 DC ms

R/C Oscillator 4.0V

s

V

CC

s

5.5V 3 DC ms

2.3V

s

V

CC

k

4.0V 7.5 DC ms

Inputs

t

Setup

4.0VsV

CC

s

5.5V 200 ns

2.3V

s

V

CC

k

4.0V 500 ns

t

Hold

4.0VsV

CC

s

5.5V 60 ns

2.3V

s

V

CC

k

4.0V 150 ns

Output Propagation Delay R

L

e

2.2 kX,C

L

e

100 pF

t

PD1,tPD0

SO, SK 4.0VsV

CC

s

5.5V 0.7 ms

2.3V

s

V

CC

k

4.0V 1.75 ms

All Others 4.0V

s

V

CC

s

5.5V 1 ms

2.3V

s

V

CC

k

4.0V 5 ms

Input Pulse Width

Interrupt Input High Time 1 tc

Interrupt Input Low Time 1 tc

Timer Input High Time 1 tc

Timer Input Low Time 1 tc

MICROWIRE Setup Time (t

mWS

)20ns

MICROWIRE Hold Time (t

mWH

)56ns

MICROWIRE Output 220 ns

Propagation Delay (t

mPD

)

Reset Pulse Width 1.0 ms

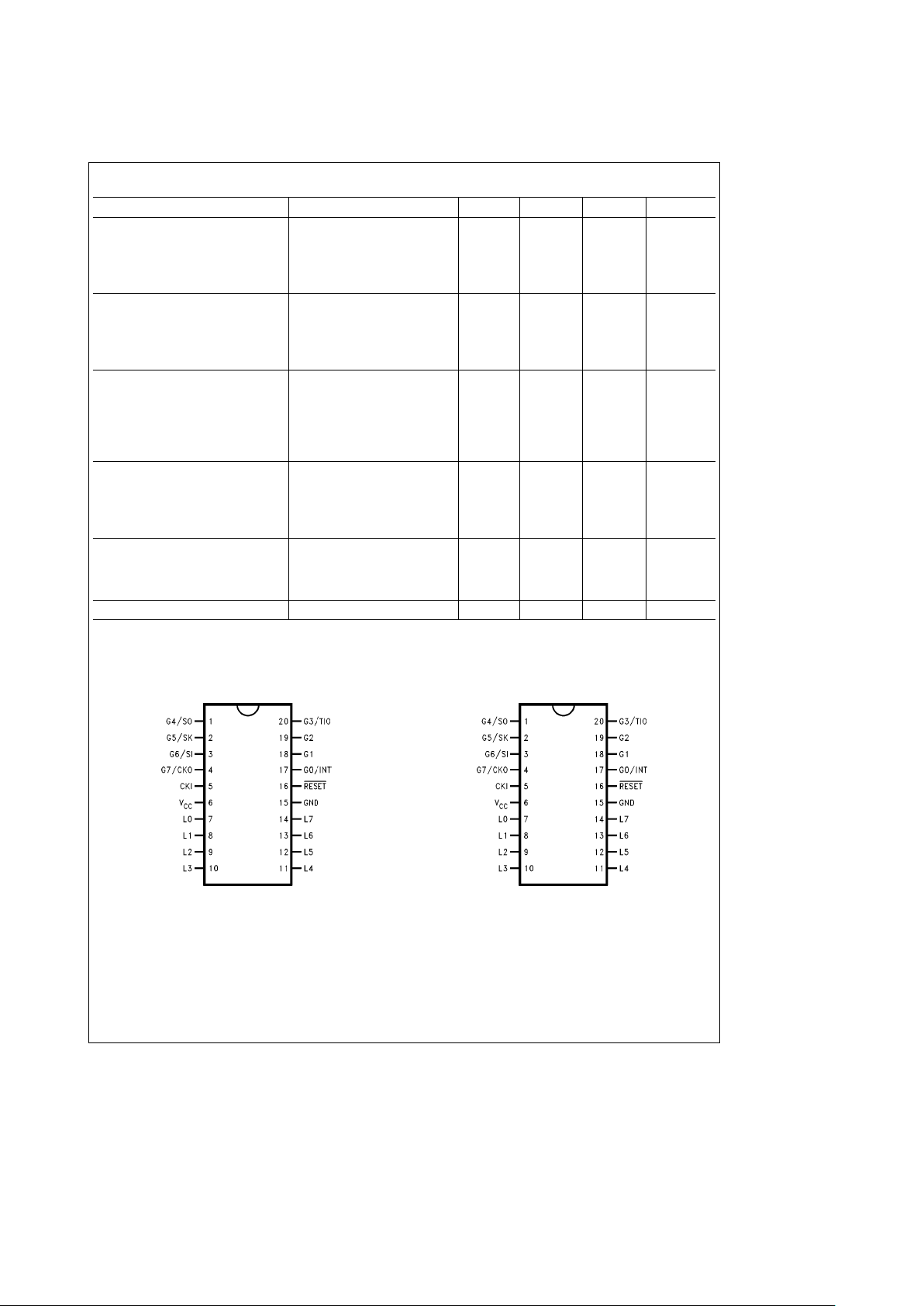

COP912C/COP912CH Pinout

Top View

20 DIP

TL/DD/12060– 3

Order Number COP912C-XXX/N, COP912CH-XXX/N

20 SO Wide

TL/DD/12060– 4

Order Number COP912C-XXX/WM,

COP912CH-XXX/WM

FIGURE 2. COP912C/COP912CH Pinout

http://www.national.com 4

Pin Description

VCCand GND are the power supply pins.

CKI is the clock input. This can come from an external

source, a R/C generated oscillator or a crystal (in conjunction with CKO). See Oscillator description.

RESET

is the master reset input. See Reset description.

PORT L is an 8-bit I/O port.

There are two registers associated to configure the L port: a

data register and a configuration register Therefore, each L

I/O bit can be individually configured under software control

as shown below:

Port L Config. Port L Data

PORT L

Setup

0 0 Hi-Z Input (TRI-STATE)

0 1 Input with Weak Pull-Up

1 0 Push-Pull Zero Output

1 1 Push-Pull One Output

Three data memory address locations are allocated for this

port, one each for data register[00D0], configuration register[00D1]and the input pins[00D2].

PORT G is an 8-bit port with 6 I/O pins (G0–G5) and 2 input

pins (G6, G7).

All eight G-pins have Schmitt Triggers on the inputs.

There are two registers associated to configure the G port:

a data register and a configuration register. Therefore each

G port bit can be individually configured under software control as shown below:

Port G Port G PORT G

Config. Data Setup

0 0 Hi-Z Input (TRI-STATE)

0 1 Input with Weak Pull-Up

1 0 Push-Pull Zero Output

1 1 Push-Pull One Output

Three data memory address locations are allocated for this

port, one for data register[00D4], one for configuration register[00D5]and one for the input pins[00D6]. Since G6

and G7 are Hi-Z input only pins, any attempt by the user to

configure them as outputs by writing a one to the configuration register will be disregarded. Reading the G6 and G7

configuration bits will return zeroes. Note that the chip will

be placed in the Halt mode by writing a ‘‘1’’ to the G7 data

bit.

Six pins of Port G have alternate features:

G0 INTR (an external interrupt)

G3 TIO (timer/counter input/output)

G4 SO (MICROWIRE serial data output)

G5 SK (MICROWIRE clock I/O)

G6 SI (MICROWIRE serial data input)

G7 CKO crystal oscillator output (selected by mask option)

or HALT restart input/general purpose input (if clock option is R/C- or external clock)

Pins G1 and G2 currently do not have any alternate functions.

The selection of alternate Port G functions are done through

registers PSW[00EF]to enable external interrupt and

CNTRL[00EE]to select TIO and MICROWIRE operations.

Functional Description

The internal architecture is shown in the block diagram.

Data paths are illustrated in simplified form to depict how

the various logic elements communicate with each other in

implementing the instruction set of the device.

ALU AND CPU REGISTERS

The ALU can do an 8-bit addition, subtraction, logical or

shift operations in one cycle time. There are five CPU registers:

A is the 8-bit Accumulator register

PC is the 15-bit Program Counter register

PU is the upper 7 bits of the program counter (PC)

PL is the lower 8 bits of the program counter (PC)

B is the 8-bit address register and can be auto incre-

mented or decremented

X is the 8-bit alternate address register and can be auto

incremented or decremented.

SP is the 8-bit stack pointer which points to the subroutine

stack (in RAM).

B, X and SP registers are mapped into the on chip RAM.

The B and X registers are used to address the on chip RAM.

The SP register is used to address the stack in RAM during

subroutine calls and returns. The SP must be preset by software upon initialization.

MEMORY

The memory is separated into two memory spaces: program

and data.

PROGRAM MEMORY

Program memory consists of 768 x 8 ROM. These bytes of

ROM may be instructions or constant data. The memory is

addressed by the 15-bit program counter (PC). There are no

‘‘pages’’ of ROM, the PC counts all 15 bits. ROM can be

indirectly read by the LAlD instruction for table lookup.

DATA MEMORY

The data memory address space includes on chip RAM, I/O

and registers. Data memory is addressed directly by the instruction or indirectly through B, X and SP registers. The

device has 64 bytes of RAM. Sixteen bytes of RAM are

mapped as ‘‘registers’’, these can be loaded immediately,

decremented and tested. Three specific registers: X, B, and

SP are mapped into this space, the other registers are available for general usage.

Any bit of data memory can be directly set, reset or tested.

I/O and registers (except A and PC) are memory mapped;

therefore, I/O bits and register bits can be directly and individually set, reset and tested.

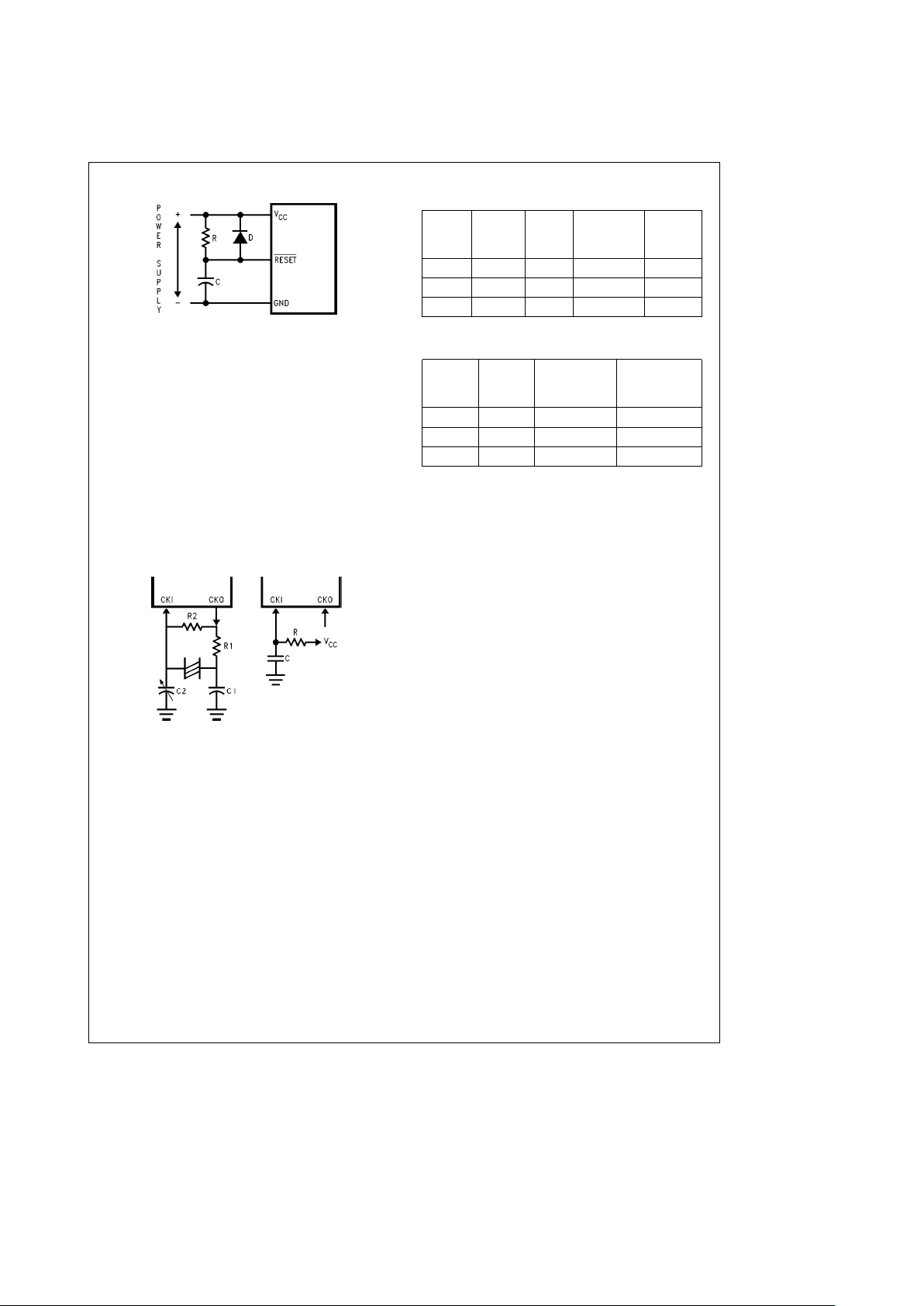

RESET

The RESET input pin when pulled low initializes the microcontroller. Upon initialization, the ports L and G are placed

in the TRl-STATE mode. The PC, PSW and CNTRL registers are cleared. The data and configuration registers for

ports L and G are cleared. The external RC network shown

in

Figure 3

should be used to ensure that the RESET pin is

held low until the power supply to the chip stabilizes.

http://www.national.com5

Functional Description (Continued)

TL/DD/12060– 5

RCl5 x POWER SUPPLY RISE TIME

FIGURE 3. Recommended Reset Circuit

OSCILLATOR CIRCUITS

The device can be driven by a clock input which can be

between DC and 5 MHz.

CRYSTAL OSCILLATOR

By selecting CKO as a clock output, CKI and CKO can be

connected to create a crystal controlled oscillator. Table I

shows the component values required for various standard

crystal values.

R/C OSCILLATOR

By selecting CKI as a single pin oscillator, CKI can make an

R/C oscillator. CKO is available as a general purpose input

and/or HALT control. Table II shows variation in the oscillator frequencies as functions of the component (R and C)

value.

TL/DD/12060– 6

FIGURE 4. Clock Oscillator Configurations

TABLE I. Crystal Oscillator Configuration

R1 R2 C1 C2

CKI

(kX)(mX) (pF) (pF)

Freq.

(MHz)

0 1 30 30–36 5

0 1 30 30–36 4

5.6 1 200 100–150 0.455

TABLE II. RC Oscillator Configuration

(Part-to-Part Variation, T

A

e

25§C)

R C CKI Freq.

Intr.

(kX) (pF) (MHz)

Cycle

(ms)

3.3 82 2.2 to 2.7 3.7 to 4.6

5.6 100 1.1 to 1.3 7.4 to 9

6.8 100 0.9 to 1.1 8.8 to 10.8

Note: 3ksRs200 kX,50pFsCs200 pF.

HALT MODE

The device is a fully static device. The device enters the

HALT mode by writing a one to the G7 bit of the G data

register. Once in the HALT mode, the internal circuitry does

not receive any clock signal and is therefore frozen in the

exact state it was in when halted. In this mode the chip will

only draw leakage current.

The device supports two different ways of exiting the HALT

mode. The first method is with a low to high transition on the

CKO (G7) pin. This method precludes the use of the crystal

clock configuration (since CKO is a dedicated output), and

so may be used either with an RC clock configuration (or an

external clock configuration). The second method of exiting

the HALT mode is to pull the RESET low.

Note: To allow clock resynchronization, it is necessary to program two

NOP’s immediately after the device comes out of the HALT mode.

The user must program two NOP’s following the ‘‘enter HALT mode’’

(set G7 data bit) instruction.

http://www.national.com 6

Functional Description (Continued)

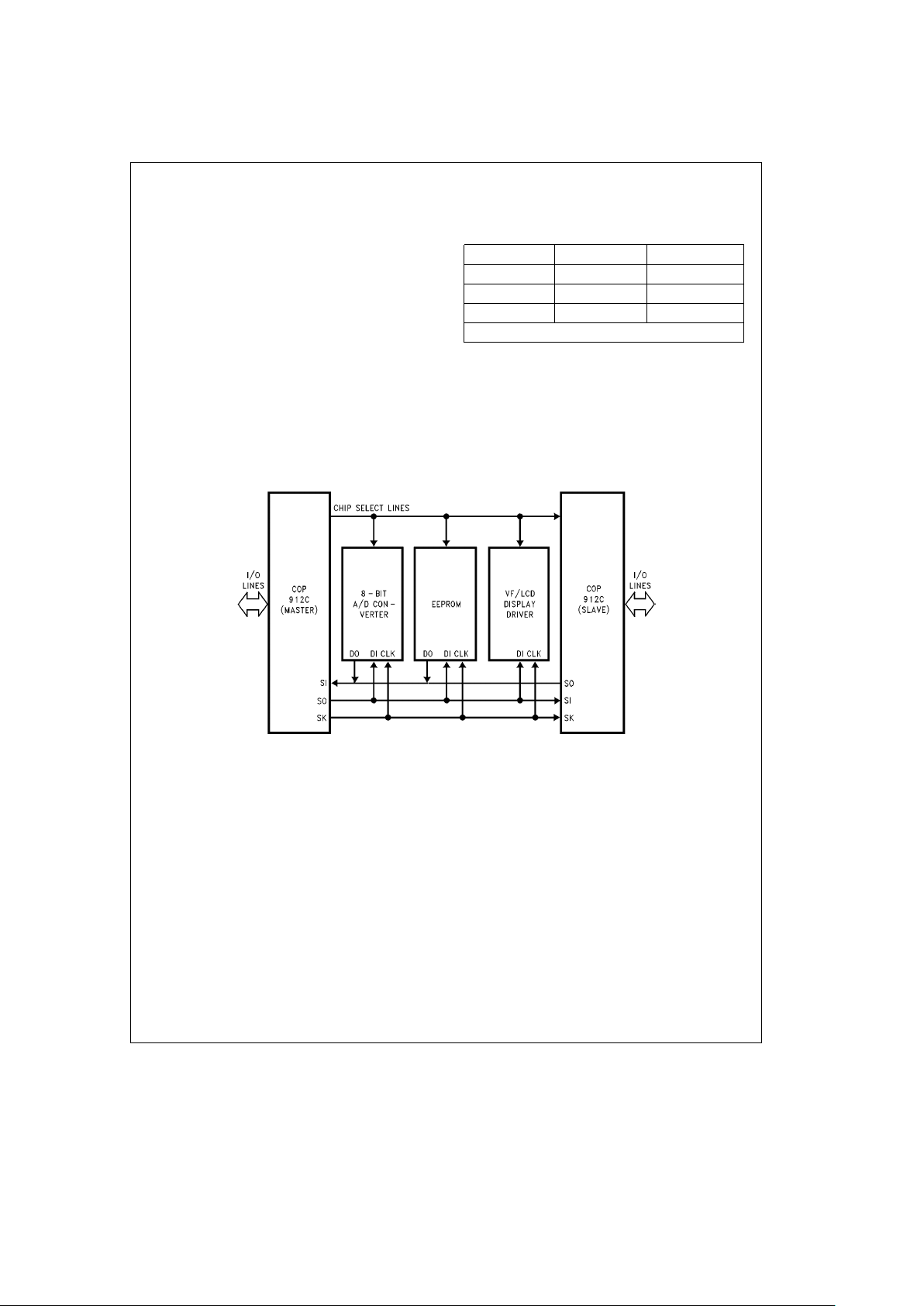

MICROWIRE/PLUS

MICROWIRE/PLUS is a serial synchronous communications interface. The MICROWIRE/PLUS capability enables

the device to interface with any of National Semiconductor’s

MICROWIRE peripherals (i.e., A/D converters, display drivers, EEPROMS etc.) and with other microcontrollers which

support the MICROWIRE interface. It consists of an 8-bit

serial shift register (SIO) with serial data input (SI), serial

data output (SO) and serial shift clock (SK).

Figure 5

shows

a block diagram of the MICROWIRE logic.

The shift clock can be derived from either the internal

source or from an external source. Operating the

MICROWIRE arrangement with the internal clock source is

called the Master mode of operation. Similarly, operating

the MICROWIRE arrangement with an external shift clock is

called the Slave mode of operation.

The CNTRL register is used to configure and control the

MICROWIRE mode. To use the MICROWIRE, the MSEL bit

in the CNTRL register is set to one. The SK clock rate is

selected by the two bits, SL0 and SL1, in the CNTRL register.

The following table details the different clock rates that may

be selected.

SK Divide Clock Rates

SL1 SL0 SK

0 0 2xtc

0 1 4xtc

1 x 8xtc

Where tc is the instruction cycle clock.

MICROWIRE/PLUS OPERATION

Setting the BUSY bit in the PSW register causes the MICROWIRE/PLUS to start shifting the data. It gets reset

when eight data bits have been shifted. The user may reset

the BUSY bit by software to allow less than 8 bits to shift.

The device may enter the MICROWIRE/PLUS mode either

as a Master or as a Slave.

Figure 5

shows how two microcontrollers and several peripherals may be interconnected

using the MICROWIRE/PLUS arrangement.

TL/DD/12060– 7

FIGURE 5. MICROWIRE/PLUS Application

http://www.national.com7

Functional Description (Continued)

WARNING: The SIO register should only be loaded when

the SK clock is low. Loading the SIO register while the SK

clock is high will result in undefined data in the SIO register.

Setting the BUSY flag when the input SK clock is high in the

MICROWIRE/PLUS slave mode may cause the current SK

clock for the SIO shift register to be narrow. For safety, the

BUSY flag should only be set when the input SK clock is

low.

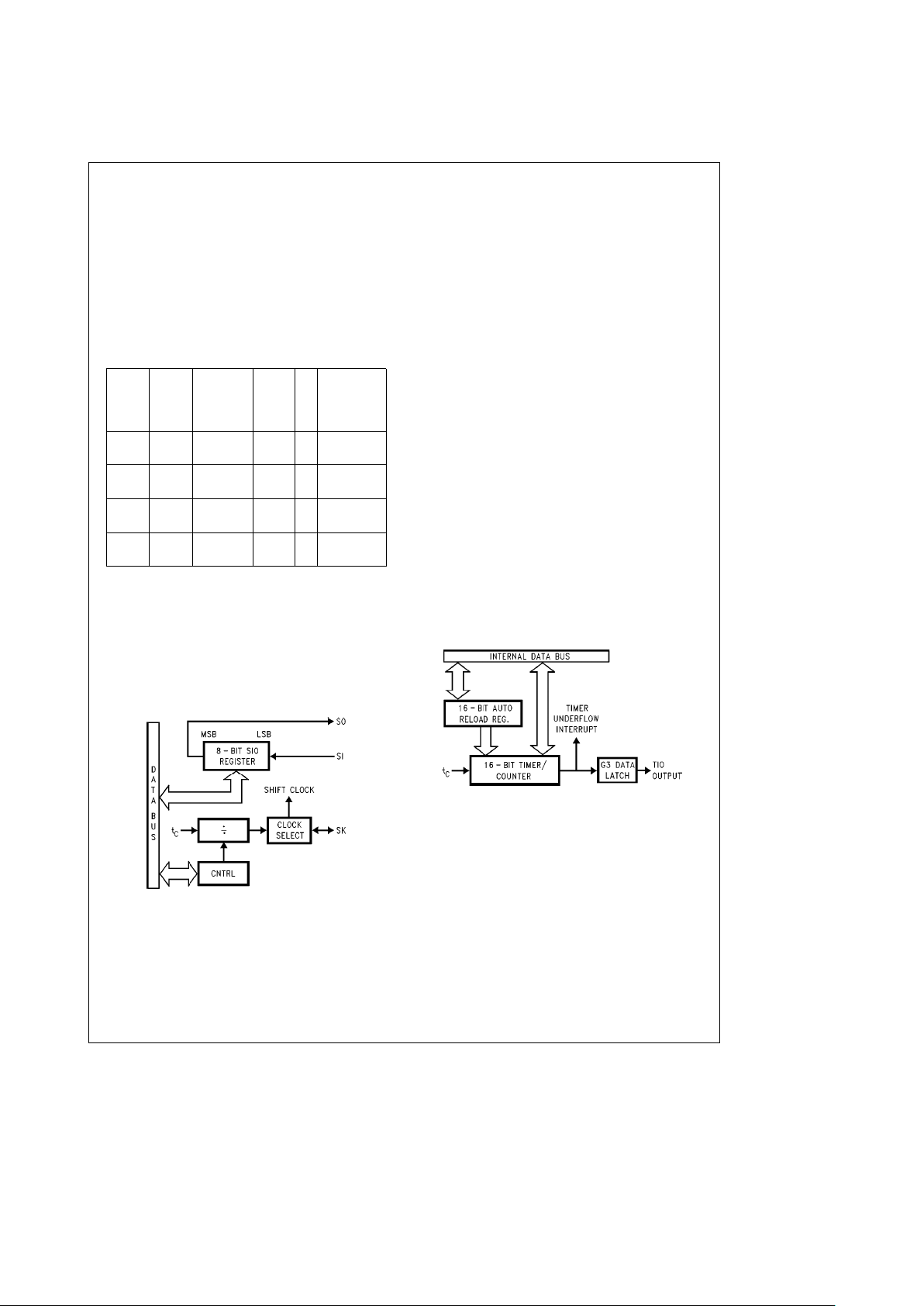

Table III summarizes the settings required to enter the Master/Slave modes of operations.

The table assumes that the control flag MSEL is set.

TABLE III. MICROWIRE/PLUS G Port Configuration

G4 G5

(SO) (SK) G4 G5 G6

Operation

Config. Config. Pin Pin Pin

Bit Bit

1 1 SO Int. SK SI MICROWIRE

Master

0 1 TRI-STATE Int. SK SI MICROWIRE

Master

1 0 SO Ext. SK SI MICROWIRE

Slave

0 0 TRI-STATE Ext. SK SI MICROWIRE

Slave

MICROWIRE/PLUS MASTER MODE OPERATION

In MICROWIRE/PLUS Master mode operation, the SK shift

clock is generated internally. The MSEL bit in the CNTRL

register must be set to allow the SK and SO functions onto

the G5 and G4 pins. The G5 and G4 pins must also be

selected as outputs by setting the appropriate bits in the

Port G configuration register. The MICROWIRE Master

mode always initiates all data exchanges. The MSEL bit in

the CNTRL register is set to enable MICROWIRE/PLUS. G4

and G5 are selected as output.

TL/DD/12060– 8

FIGURE 6. MICROWIRE/PLUS Block Diagram

MICROWIRE/PLUS SLAVE MODE

In MICROWIRE/PLUS Slave mode operation, the SK shift

clock is generated by an external source. Setting the MSEL

bit in the CNTRL register enables the SO and SK functions

onto the G port. The SK pin must be selected as an input

and the SO pin as an output by resetting and setting their

respective bits in the G port configuration register.

The user must set the BUSY flag immediately upon entering

the slave mode. This will ensure that all data bits sent by the

master will be shifted in properly. After eight clock pulses,

the BUSY flag will be cleared and the sequence may be

repeated.

Note: In the Slave mode the SIO register does not stop shifting even after

the busy flag goes low. Since SK is an external output, the SIO register stops shifting only when SK is turned off by the master.

Note: Setting the BUSY flag when the input SK clock is high in the MICRO-

WIRE/PLUS slave mode may cause the current SK clock for the SIO

register to be narrow. When the BUSY flag is set, the MICROWIRE

logic becomes active with the internal SIO shift clock enabled. If SK is

high in slave mode, this will cause the internal shift clock to go from

low in standby mode to high in active mode. This generates a rising

edge, and causes one bit to be shifted into the SIO register from the

SI input. For safety, the BUSY flag should only be set when the input

SK clock is low.

Note: The SIO register must be loaded only when the SK shift clock is low.

Loading the SIO register while the SK clock is high will result in undefined data in the SIO register.

Timer/Counter

The device has an on board 16-bit timer/counter (organized

as two 8-bit registers) with an associated 16-bit autoreload/

capture register (also organized as two 8-bit registers). Both

are read/write registers.

The timer has three modes of operation:

PWM (PULSE WIDTH MODULATION) MODE

The timer counts down at the instruction cycle rate (2 ms

max). When the timer count underflows, the value in the

autoreload register is copied into the timer. Consequently,

the timer is programmable to divide by any value from 1 to

65536. Bit 5 of the timer CNTRL register selects the timer

underflow to toggle the G3 output. This allows the user to

generate a square wave output or a pulse-width-modulated

output. The timer underflow can also be enabled to interrupt

the processor. The timer PWM mode is shown in

Figure 7

.

TL/DD/12060– 10

FIGURE 7. Timer in PWM Mode

http://www.national.com 8

Loading...

Loading...