PRELIMINARY DATA SHEET

GaAs INTEGRATED CIRCUIT

PG173TA

PPPP

L-BAND PA DRIVER AMPLIFIER

DESCRIPTION

The PPG173TA is L-Band PA driver amplifier developed for digital cellular telephone and PCS applications. This

device feature high output power and low distortion with 2.8 V low voltage and 25 mA low current operation. It is

housed in a very small 6 pin mini-mold package available on tape-and-reel and easy to install and contributes to

miniaturizing the systems.

FEATURES

DD

Low Operation Voltage : V

{

Low distortion : P

{

External output matching

Low operation Current : IDD = 25 mA typ. @ VDD = 2.8 V, fRF = 925 to 960 MHz, P

{

External output matching

6 pin mini-mold package

{

= 2.8 V

adj 1

= –60 dBc typ. @ VDD = 2.8 V, fRF = 925 to 960 MHz, P

out

= +9 dBm

out

= +9 dBm

APPLICATION

Digital Cellular: PDC, GSM, IS-95, IS-136, PCS etc.

{

ORDERING INFORMATION

PART NUMBER PACKAGE PACKING FORM

P

PG173TA-E3 6 pin Mini-Mold Carrier tape width is 8 mm, Quantity is 3 kpcs per reel.

Remark

For sample order, please contact your local NEC sales office. (Part number for sample order:

PG173TA)

P

ABSOLUTE MAXIMUM RATINGS (TA = 25°C)

PARAMETERS SYMBOL RATINGS UNIT

Supply Voltage V

Input Power P

Total Power Dissipation P

Operating Temperature T

Storage Temperature T

Mounted on a 50 u 50 u 1.6 mm double copper clad epoxy glass PWB, T

Note

DD

in

tot

A

stg

6.0 V

–8 dBm

Note

170

–30 to +90 °C

–35 to +150 °C

mW

A

= +85°C

Caution The IC must be handled with care to prevent static discharge because its circuit composed of

GaAs HJ-FET.

Document No. P13059EJ1V0DS00 (1st edition)

Date Published November 1997 N

Printed in Japan

The information in this document is subject to change without notice.

1997©

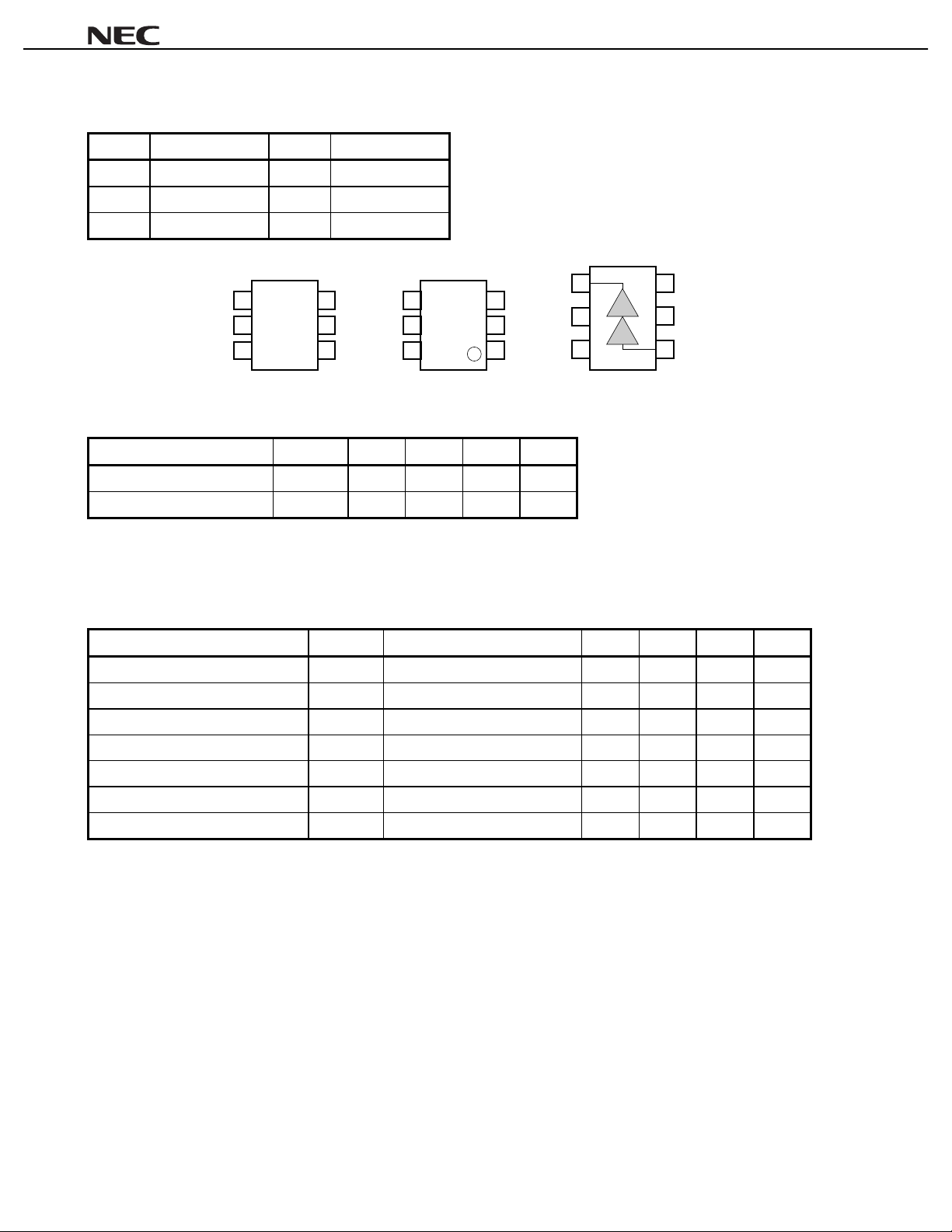

PIN CONNECTION AND INTERNAL BLOCK DIAGRAM

Pin No. Connection Pin No. Connection

PPPP

PG173TA

1V

2 GND 5 GND

3V

DD1

DD2

& OUT 6 IN

3

2

1

4 Non Connection

(Top View)

4

5

G1C

6

(Bottom View)

4

5

6

3

2

1

RECOMMENDED OPERATING CONDITIONS (TA = 25°C)

PARAMETERS SYMBOL MIN. TYP. MAX. UNIT

Supply Voltage 1, 2 V

Input Power P

DD1, 2

in

+2.7 +2.8 +3.0 V

–18 dBm

ELECTRICAL CHARACTERISTICS

(Unless otherwise specified, T

A

= 25°C, V

DD1

= V

DD2

= +2.8 V,

External output matching)

3

2

1

/4DQPSK modulated signal input,

SSSS

4

5

6

PARAMETERS SYMBOL TEST CONDITIONS MIN. TYP. MAX. UNIT

Operating Frequency f 925 960 MHz

DD

adj1

adj2

L

Pin = –18 dBm 27 28.5 dB

Pin = –18 dBm 25 30 mA

out

P

= +9 dBm, 'f = r50 kHz –60 –55 dBc

out

P

= +9 dBm, 'f = r100 kHz –65 –60 dBc

in

out

External matching 10 dB

10 dB

Linear Gain G

Total Current I

Adjacent Channel Power Leakage 1 P

Adjacent Channel Power Leakage 2 P

Input Return Loss RL

Output Return Loss RL

Preliminary Data Sheet2

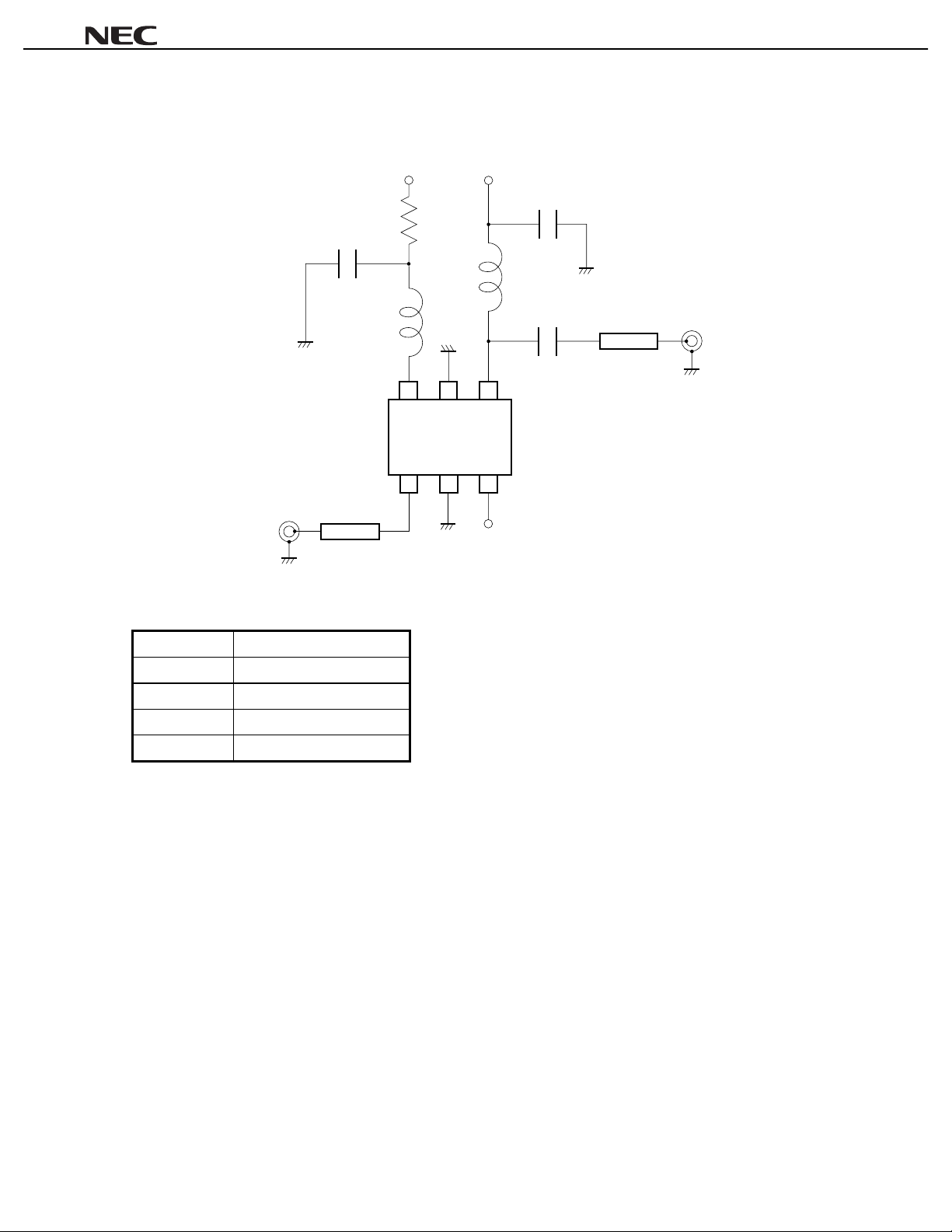

EVALUATION CIRCUIT (Preliminary)

DD1

V

= V

DD2

= +2.8 V, f = 925 to 960 MHz

R1

V

DD1

PPPP

PG173TA

V

DD2

C2

IN

Using the NEC Evaluation board

C1, C2 1000 pF

C3 2.0 pF

R1 10 :

L1 8.2 nH

L2 10 nH

C1

Zo = 50

L1

Ω

L2

1

2

G1C

65

C3

3

4

Non Connection

Zo = 50

OUT

Ω

Preliminary Data Sheet 3

Loading...

Loading...