NEC UPG101P, UPG101B, UPG100B Datasheet

DATA SHEET

GaAs INTEGRATED CIRCUIT

PPPP

PG100P,

PPPP

PG101P

WIDE BAND AMPLIFIER CHIPS

1992©

Document No. P12402EJ2V0DS00 (2nd edition)

(Previous No. IC-3144)

Date Published February 1997 N

Printed in Japan

DATA SHEET

DESCRIPTION

P

PG100P and PPG101P are GaAs integrated circuits designed as wide band amplifiers. Both devices are

available in chip form.

P

PG100P is low noise amplifier from 50 MHz to 3 GHz and PPG101P is a medium power amplifier in the same

frequency band. These devices are most suitable for the IF stage of microwave communication system and the

measurement equipment.

FEATURES

• Wide band : f = 50 MHz to 3 GHz

ORDERING INFORMATION

PART NUMBER FORM

P

PG100P chip

P

PG101P chip

ABSOLUTE MAXIMUM RATINGS (TA = 25 °C)

P

PG100P

P

PG101P

Drain Voltage V

DD

+8 +10 V

Gate Voltage V

GG

ð

8

ð

8V

Input Voltage V

in

ð

3 to +0.6

ð

5 to +0.6 V

Input Power P

in

+15 +15 dBm

Total Power Dissipation P

tot

*1

1.5 1.5 W

Operating Temperature T

opr

*2

ð

65 to +125

ð

65 to +125 °C

Storage Temperature T

stg

ð

65 to +175

ð

65 to +175 °C

*1

Mounted with AuSn hard solder

*2

The temperature of base material baside the chip

2

PPPP

PG100P,

PPPP

PG101P

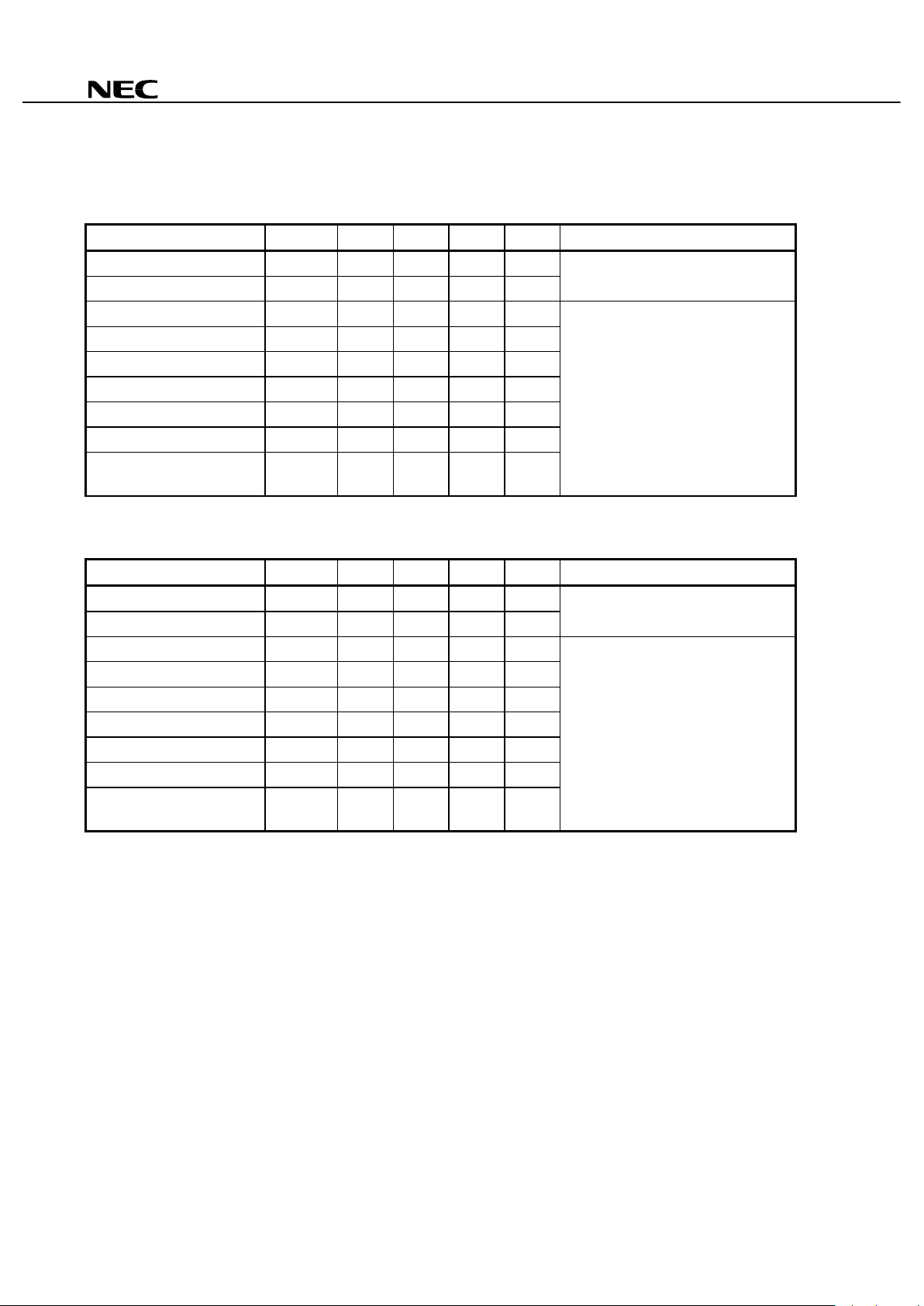

ELECTRICAL CHARACTERISTICS (TA = 25 °C)

*3

P

PG100P (VDD = +5 V, VGG = ð5 V)

CHARACTERISTICS SYMBOL MIN. TYP. MAX. UNIT TEST CONDITIONS

Drain Current I

DD

30 45 60 mA RF OFF

Gate Current I

GG

0.7 1.5 mA

Power Gain Gp 14 16 dB f = 0.05 to 3 GHz

Gain Flatness

'

Gp r1.5 dB

Noise Figure NF 2.7 3.5 dB

Input Return Loss RL

in

710 dB

Output Return Loss RL

out

710 dB

Isolation I

SOL

30 40 dB

Output Power at 1 dB Gain

Compression Point

P

O(1 dB)

+3 +6 dBm

P

PG101P (VDD = +8 V, VGG = ð5 V)

CHARACTERISTICS SYMBOL MIN. TYP. MAX. UNIT TEST CONDITIONS

Drain Current I

DD

70 100 140 mA RF OFF

Gate Current I

GG

1.0 3.0 mA

Power Gain Gp 12 14 dB f = 0.05 to 3 GHz

Gain Flatness

'

Gp r1.5 dB

Noise Figure NF 5 7 dB

Input Return Loss RL

in

68 dB

Output Return Loss RL

out

68 dB

Isolation I

SOL

30 40 dB

Output Power at 1 dB Gain

Compression Point

P

O(1 dB)

+16 +18 dBm

*3

These characteristics are based on performance of devices mounted in the standard package shown in Fig. 1.

3

PPPP

PG100P,

PPPP

PG101P

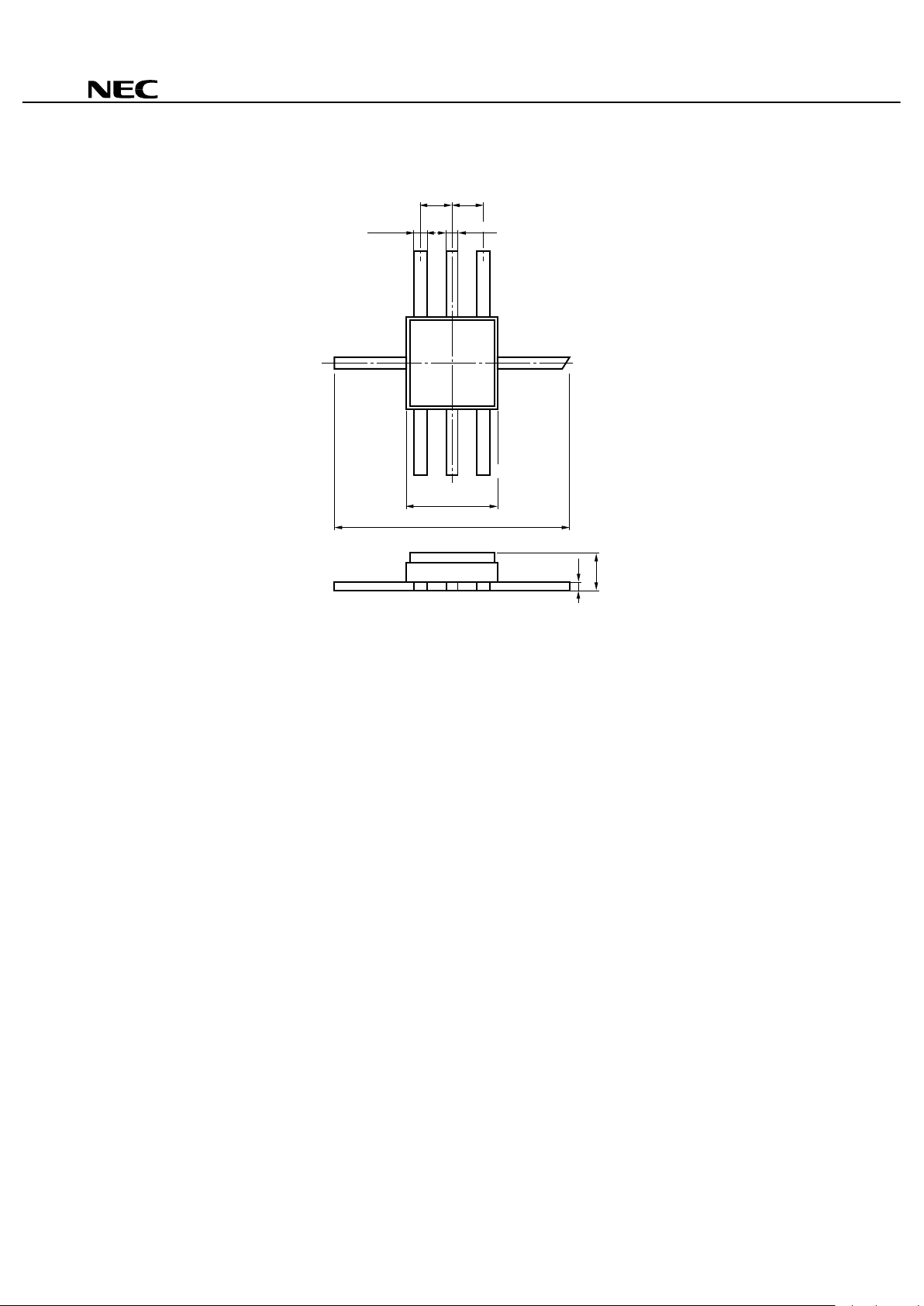

Fig. 1 8 Pin Ceramic Package

34 2

76

15

1.27±0.1 1.27±0.1

4–0.6

3.8±0.2

4–0.4

8

10.6 MAX.

1.7 MAX.

0.2

+0.05

–0.02

Loading...

Loading...