NEC UPD17P068GF-3BA Datasheet

DATA SHEET

MOS INTEGRATED CIRCUIT

µ

PD17P068

4-BIT SINGLE-CHIP MICROCONTROLLER

WITH ON-CHIP HARDWARE FOR TV SYSTEMS

The µPD17P068 is a one-time PROM version of the µPD17068 that has on-chip mask ROM.

The µPD17P068, which can be programmed only once, is suited for testing during development of µPD17068

systems and limited production runs.

µ

Use this data sheet together with

µ

PD17P068 does not provide a level of reliability intended for mass production of the customer's

The

products. Use it only for functional evaluation when experimenting or doing product trial tests.

PD17068 documents.

FEATURES

• Compatible with the

µ

PD17068

• One-time PROM : 12160 × 16 bits

• Operating voltage : VDD = 5 V ± 10 %

ORDERING INFORMATION

Part Number Package

µ

PD17P068GF-3BA 100-pin plastic QFP (14 × 20mm)

Document No. U10336EJ1V0DS00

Date Published November 1995 P

Printed in Japan

The information in this document is subject to change without notice.

©

1995

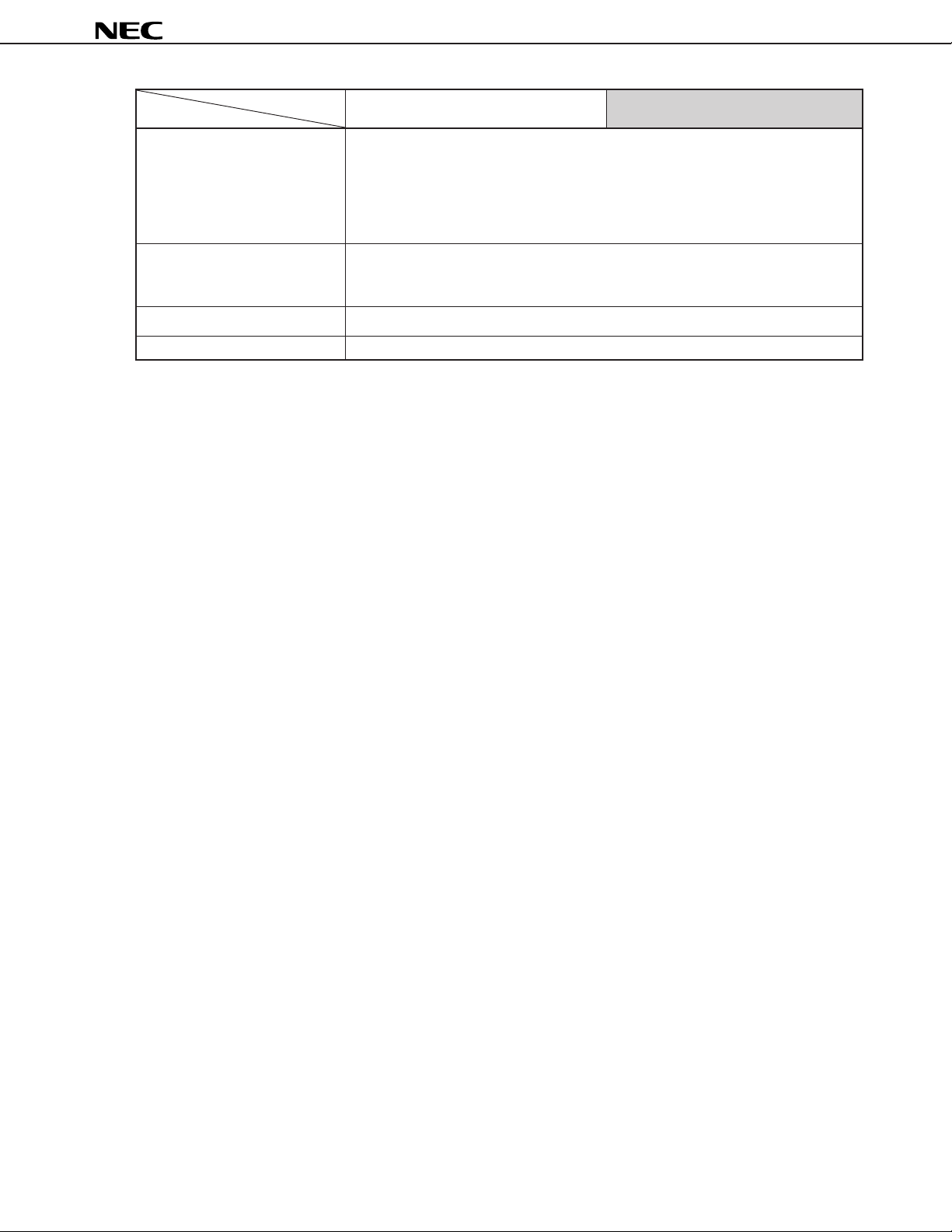

FUNCTIONAL OUTLINE

µ

PD17P068

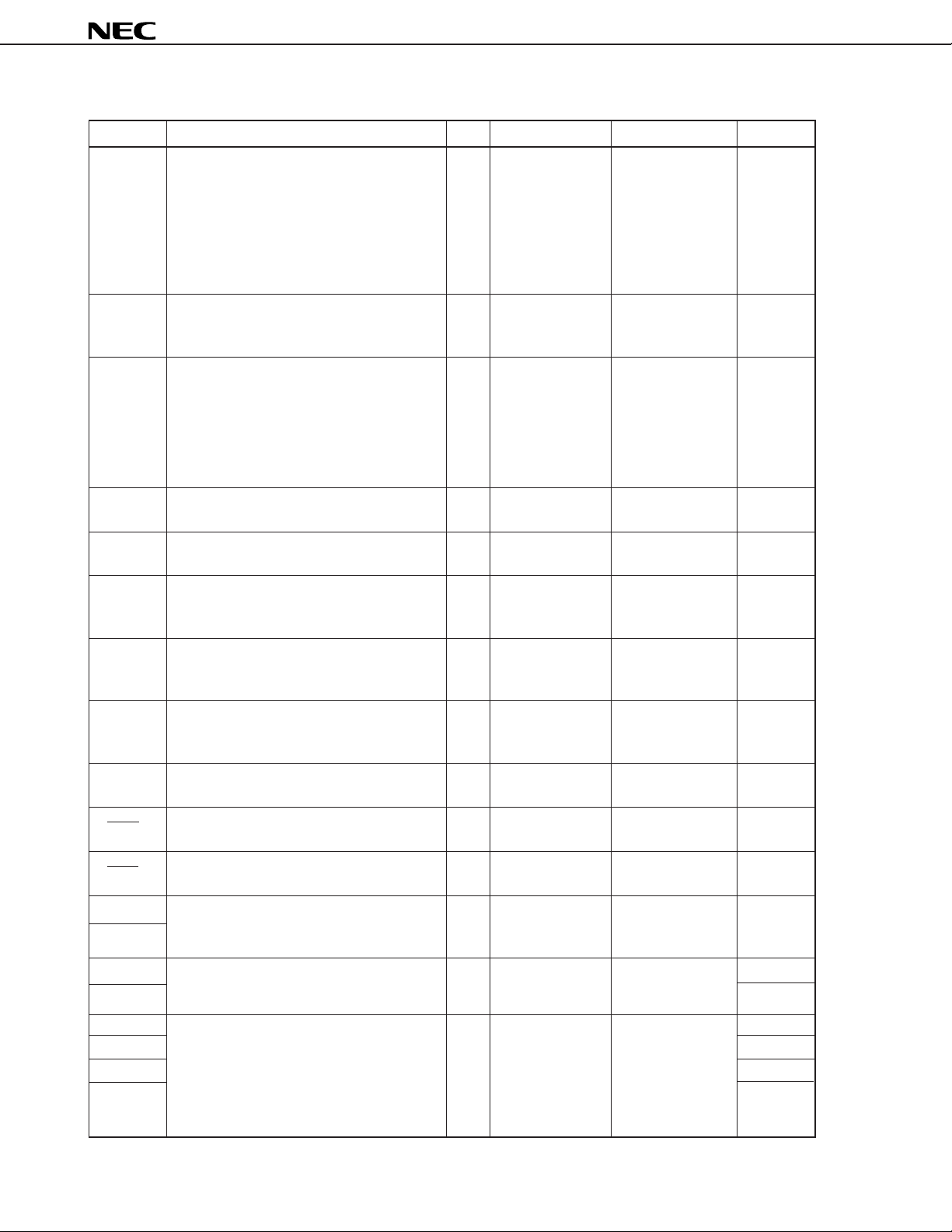

Part Number

Item

Program memory (ROM) • 12160 × 16 bits

Table reference area: 12160 × 16 bits

Character ROM (CROM) • 6144 × 16 bits

Data memory (RAM)

Video RAM (VRAM) • 672 × 4 bits (also used as data memory (RAM))

System register • 12 × 4 bits

Register file • 12 × 4 bits

General port register • 12 × 4 bits

Instruction execution time • 2 µs (when using 8-MHz crystal resonator)

Stack levels • 12 levels (stack manipulation possible)

General ports • Input ports : 4

IDC

(Image Display Controller)

• 1007 × 4 bits (including area serving also as VRAM)

Data buffer: 4 × 4 bits, general register: 16 × 4 bits

• I/O ports : 19

• Output ports : 21

• Number of displayable characters : 192 characters max. per screen

• Display format : 16 × 16-dot mode 15 lines × 24 columns

• Character types : 255 types (user programmable)

• Character format : 16 × 16 dots and 14 × 16 dots selectable

• Color : 15 colors

• Character size : Vertical : 16 sizes (specifiable for

µ

PD17068

Mask ROM One-time PROM

(up to 350 characters with program)

: 14 × 16-dot mode 17 lines × 24 columns

(2 dots can be placed between

characters)

Horizontal : 24 sizes (specifiable for

µ

PD17P068

each line)

each character)

• 2 systems

Serial interface Serial interface 0 (compatible with 2-wire system, 3-wire system and I2C Bus)

Serial interface 1 (3-wire system)

D/A converter • 8 bits × 9 channels (PWM output, 12.5 V max.)

A/D converter • 6 bits × 8 channels (successive approximation by software)

• 10 channels (maskable interrupt)

Interrupt External interrupt : 3 channels (INT0, INTNC, VSYNC, HSYNC)

Internal interrupt : 7 channels (timer 0, 1, serial interface 0, 1, basic timer 2,

VRAM pointer, timer 0 overflow)

2

µ

PD17P068

Part Number

Item

Timer 0 : 10 µs to 204.75 ms (interrupt)

Timer 1 : 1 µs to 256 ms (interrupt)

Timer

Reset • Reset with CE pin (CE pin: Low level → High level)

Supply voltage VDD = 5 V ± 10 %

Package 100-pin plastic QFP (14 × 20 mm)

Basic timer 0 : 1, 5, 100 ms (carry)

Basic timer 1 : 125 µs, 1 ms, 5 ms, 100 ms, external (carry)

Basic timer 2 : 125 µs, 1 ms, 5 ms, 100 ms, external (interrupt)

Watch timer : Date, Hour, Minute, Second (counter)

• Power-on reset

• Power interruption detection

µ

PD17068

µ

PD17P068

3

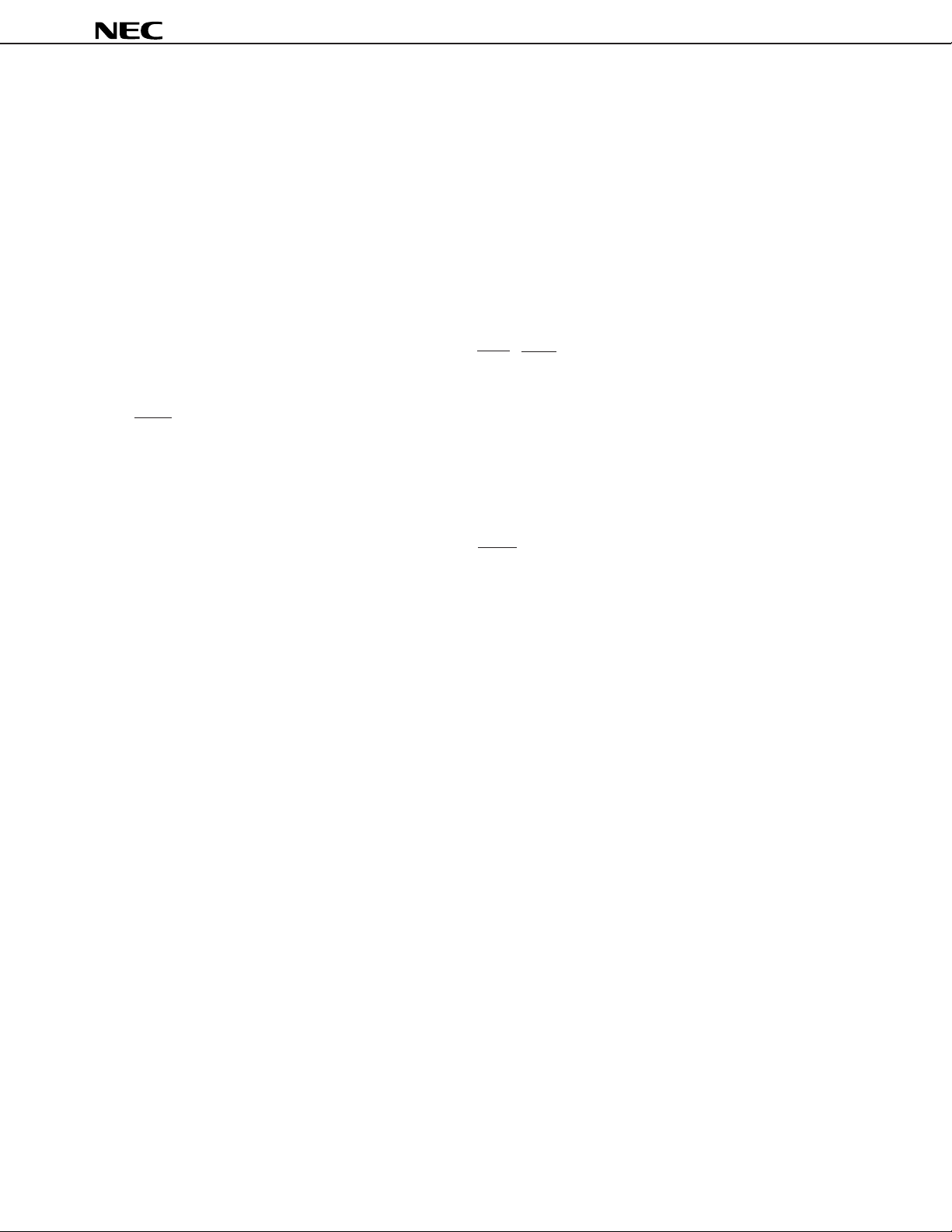

BLOCK DIAGRAM

VCO

PSC

EO

IN

OSC

OSC

OUT

H

SYNC

V

SYNC

RED

GREEN

BLUE

BLANK

2

)

I (P0B

3

HSCNT (P0B

)

PLL

OSC

Circuit

IDC

Hsync

Counter

RAM

×

1007 4 bits

VRAM

×

(672 4 bits)

SYSTEM REG.

RF

ALU

A/D

Converter

D/A

Converter

OSC

Watch

Timer

µ

PD17P068

ADC

0

ADC1(P0D0/MD0/XT

ADC

2

(P0D1/MD1/XTIN)

3

(P0D2/MD2)

ADC

4

(P0D3/MD3)

ADC

5

(P1C0/D0)

ADC

7

(P1C2/D2)

ADC

PWM0(P2C0)

PWM

3

(P2C3)

PWM

4

(P2B0)

PWM

7

(P2B3)

8

(P2A0)

PWM

XTIN(P0D1/ADC2)

XT

OUT

(P0D0/ADC1)

1

CKOUT (P1B

)

OUT

)

0

-P0A

P0A

P0B0-P0B

P0C0-P0C

P0D0-P0D

P1A0-P1A

P1B0-P1B

4-D7

(D

P1C0-P1C

P1D0-P1D

P2A

P2B0-P2B

P2C0-P2C

P2D0-P2D

XIN/CLK

X

)

OUT

4

3

4

3

3

4

4

3

3

4

4

3

Instruction

Decoder

One-time PROM

×

12160 16 bits

CROM

×

6144 16 bits

Program Counter

Port

3

4

4

3

0

Stack

×

12 14 bits

Timer0

Timer1

Basic

Timer0

Basic

Timer1

Basic

Timer2

TMIN (P1B3)

SDA (P0A0)

3

4

4

3

2

3

Main

Oscillator

CPU

Peripheral

Serial

I/O0

Serial

I/O1

SCL (P0A1)

0

(P0A2)

SCK

SO

0

(P0A3)

SI

0

(P0B0)

SCK1(P2D0)

SO1(P2D1)

SI1(P2D2)

STP

/P1B

RLS

GND0, GND

4

V

CE

DD

2

1

Reset

Interrupt

INTNC(VPP)

INT

0

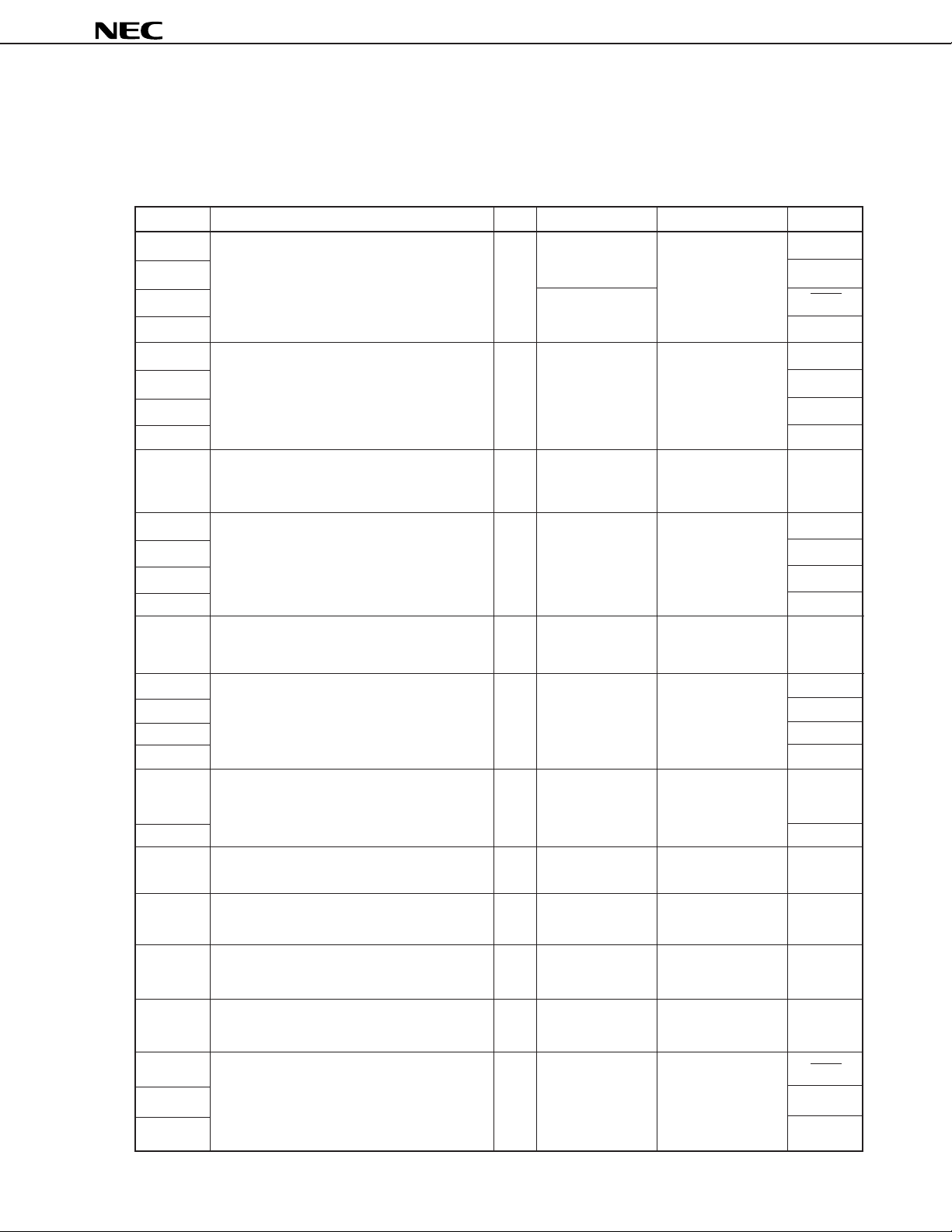

PIN CONFIGURATION (Top View)

(1) Normal operation mode

P1D3CEPSCEOGND2GND1NCNCNCNC

100

99 98 97 96 95 94 93 92 91 90 89 88 87 86 85 84 83 82 81

31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50

3/TMIN

P1B

P1B

2 /RLS STP

P1B

1/CKOUT

0 /PWM8

P2A

P2D

P2D 1 /SO1

P2D 0 /SCK1

OSCOUT

OSCIN

P1D2

P1D1

P1D0

INT0

NC

NC

P1B

NC

NC

P1A

P1A2

NC

NC

NC

P1A

P1A0

NC

NC

NC

2/SI1

NC

GND0

1

2

3

4

5

6

7

8

9

0

10

11

12

3

13

14

15

16

17

1

18

19

20

21

22

23

24

25

26

27

28

29

30

VCO

DD1

NC

DD0

V

V

XIN

NC

µ

PD17P068GF-3BA

XOUT

µ

PD17P068

INT NC

XTOUT/ADC1 /P0D0

XTIN /ADC 2/P0D1

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

P0D2 /ADC3

P0D3 /ADC4

P1C0 /ADC5

P1C1 /ADC6

NC

2/ADC7

P1C

P1C3

NC

ADC

0

NC

P0C0

NC

1

P0C

NC

P0C

2

NC

P0C3

NC

P2C

0/PWM0

NC

1/PWM1

P2C

NC

2/PWM2

P2C

NC

3/PWM3

P2C

NC

P2B0 /PWM4

P2B1 /PWM5

P2B2 /PWM6

P2B3 /PWM7

RED

NC

GREEN

BLUE

BLANK

SYNC

H

NC

VSYNC

NC

P0B3 /HSCNT

NC

2/I

P0B

1

P0B

NC

NC

P0B0/SI0

P0A3/SO0

P0A1 /SCL

P0A2/SCK0

P0A0 /SDA

5

(2) PROM programming mode

100

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50

(OPEN)

(L)

(OPEN)

D

D

(OPEN)

D

D

(OPEN)

(L)

(OPEN)

GND

(OPEN)

(L)

7

6

5

4

0

2

1

(L)

(OPEN)

(L)

(OPEN)

GND

GND

(OPEN)

DD1VDD0

V

CLK

(OPEN)

VPPMD0MD

99 98 97 96 95 94 93 92 91 90 89 88 87 86 85 84 83 82 81

µ

PD17P068GF-3BA

µ

PD17P068

1

MD

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

2

MD

3

D

0

D

1

(OPEN)

2

D

D

3

(OPEN)

(OPEN)

(L)

(L)

(OPEN)

(L)

(OPEN)

(L)

(OPEN)

(L)

(OPEN)

Caution Contents in parentheses indicate how to handle unused pins in PROM programming mode.

L: Connect to GND via a resistor (470 Ω) separately.

OPEN: Leave unconnected.

6

µ

PD17P068

PIN IDENTIFICATIONS

ADC0-ADC7 : A/D converter input P1C0-P1C3 : Port 1C

BLANK : Blanking signal output P1D0-P1D3 : Port 1D

BLUE : Character signal output P2A0 : Port 2A

CE : Chip enable P2B

CKOUT : Watch timer adjustment P2C0-P2C3 : Port 2C

output P2D0-P2D2 : Port 2D

CLK : Address update clock input PSC : Pulse swallow control output

0-D7 : Data input/output PWM0-PWM8 : Pulse-width modulation output

D

EO : Error out RED : Character signal output

0-GND2 : Ground RLSSTP : Clock stop release signal input

GND

GREEN : Character signal output SCK0, SCK1 : Shift clock input/output

HSCNT : Horizontal synchronizing SCL : Shift clock input/output

signal counter input SDA : Serial data input/output

SYNC : Horizontal synchronizing Sl0, Sl1 : Serial data input

H

signal input SO0 , SO1:Serial data output

I : Character signal output TMIN : Event input of basic timer 1 or 2

0, INTNC : External interrupt request VCO : Local oscillation input

INT

signal input VDD0, VDD1 : Positive power supply

0-MD3 : Operation mode select VPP : Program voltage application

MD

NC : No connection VSYNC : Vertical synchronizing signal input

OSCIN, OSCOUT : LC oscillation for IDC XIN, XOUT : Main clock oscillation

0-P0A3 : Port 0A XTIN, XTOUT : Watch timer oscillation

P0A

P0B0-P0B3 : Port 0B

P0C0-P0C3 : Port 0C

0-P0D3 : Port 0D

P0D

P1A0-P1A3 : Port 1A

P1B0-P1B3 : Port 1B

0-P2B3 : Port 2B

7

µ

PD17P068

CONTENTS

1. PIN FUNCTIONS ................................................................................................................................. 9

1.1 Normal Operation Mode ........................................................................................................................... 9

1.2 PROM Programming Mode .................................................................................................................... 13

1.3 Pin Equivalent Circuits .......................................................................................................................... 14

1.4 Handling of Unused Pins....................................................................................................................... 19

1.5 Notes on Using the CE and INTNC Pins (Only in Normal Operation Mode) ................................... 21

2. WRITE, READ, AND VERIFY OF ONE-TIME PROM (PROGRAM MEMORY)............................ 22

2.1 Operation Modes in Program Memory Write/Read/Verify................................................................. 23

2.2 PROM Write Procedure .......................................................................................................................... 24

2.3 PROM Read Procedure .......................................................................................................................... 25

3. ELECTRICAL SPECIFICATIONS .................................................................................................... 26

4. PACKAGE DRAWING ...................................................................................................................... 31

APPENDIX DEVELOPMENT TOOLS.................................................................................................... 32

8

µ

PD17P068

1. PIN FUNCTIONS

1.1 Normal Operation Mode

(1) Port pins

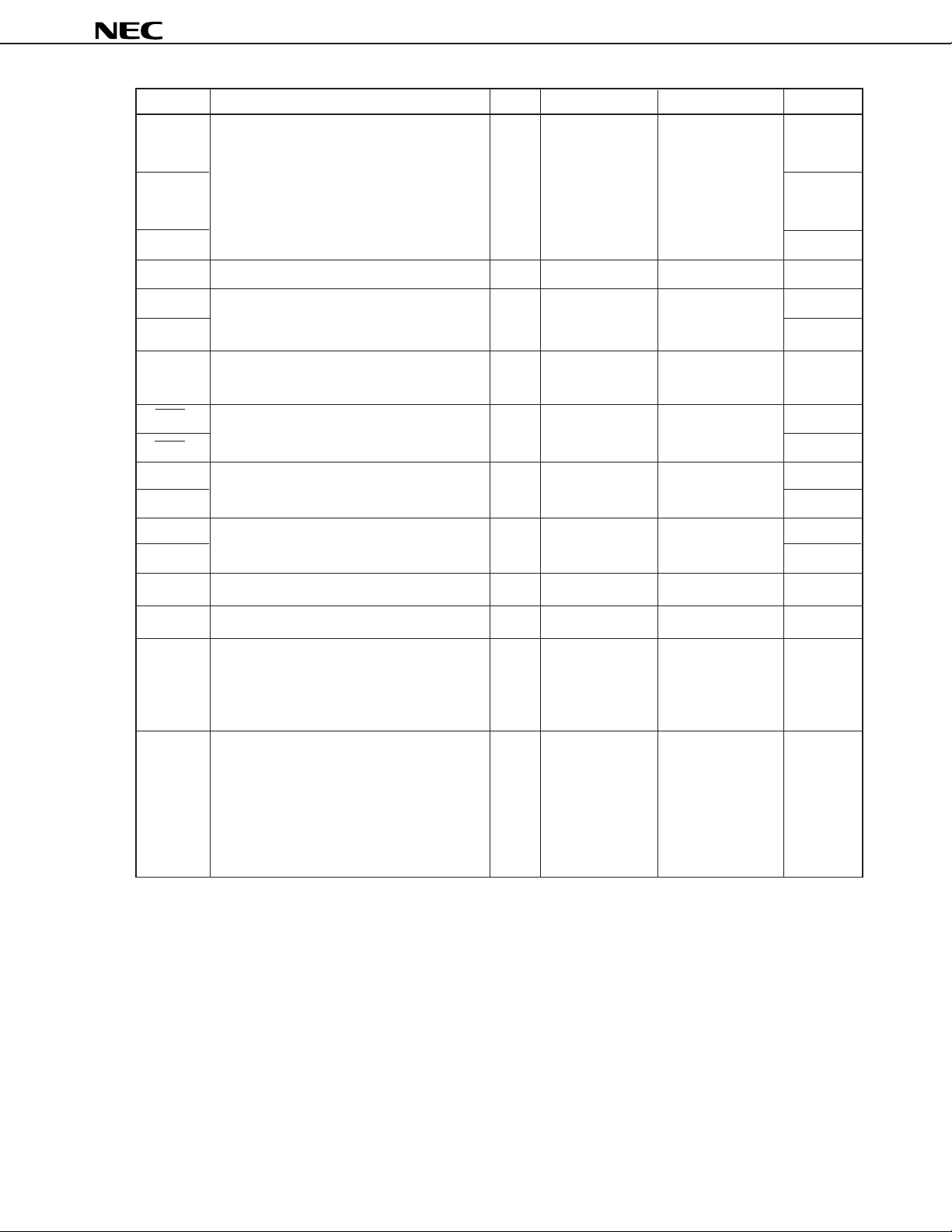

Pin Name Description I/O Output Type When Reset Shared by

P0A0 SDA

P0A1 SCL

P0A2 SCK0

P0A3 SO0

P0B0 Sl0

P0B1 —

P0B2 l

P0B3 HSCNT

P0C0

—

P0C3

P0D0 ADC1/XTOUT

P0D1 ADC2/XTIN

P0D2 ADC3

P0D3 ADC4

P1A0

—

P1A3

P1B0 —

P1B1 CKOUT

P1B2 RLSSTP

P1B3 TMIN

P1C0 ADC5

P1C2 ADC7

P1C3 —

P1D0

—

P1D3

P2A0 PWM8

P2B0 PWM4

P2B3 PWM7

4-bit I/O port.

These pins serve as a bit-selectable N-ch open drain

4-bit input/output port. All these pins

are set to input pins when power (VDD) I/O Input

is turned on, when clock is stopped, or

when reset signal is input to the CE pin.

4-bit I/O port.

These pins serve as a bit-selectable 4-bit

input/output port. All these pins are set to

input pins when power (VDD) is turned

on, when clock is stopped, or when reset

signal is input to the CE pin.

These pins serve as a 4-bit output port.

The output state of each pin is undefined O CMOS push-pull Undefined output

after power (VDD) is turned on.

These pins serve as a 4-bit input port. I — Input with pull-

These pins serve as a 4-bit output port. O Middle voltage, Undefined output

4-bit I/O port.

These pins serve as a bit-selectable 4-bit I/O CMOS push-pull Input

input/output port.

4-bit I/O port. These pins serve as 4-bit- I/O CMOS push-pull Input

selectable 4-bit I/O port.

These pins serve as a 4-bit output port. O CMOS push-pull Undefined output

This pin serves as a 1-bit output port. O Undefined output

These pins serve as a 4-bit output port. O Undefined output

CMOS push-pull

I/O CMOS push-pull Input

down resistor

N-ch open-drain

high current

N-ch open-drain

Middle voltage

N-ch open-drain

Middle voltage

P2C0 PWM0

P2C3 PWM3

P2D0 SCK1

P2D1 SO1

P2D2 Sl1

These pins serve as a 4-bit output port. O Undefined output

These pins serve as a bit-selectable 3-bit

input/output port. All these pins are set to

input pins when power (VDD) is turned on, I/O CMOS push-pull Input

when clock is stopped, or when reset

signal is input to the CE pin.

N-ch open-drain

Middle voltage

9

µ

PD17P068

(2) Non-port pins

Pin Name Description I/O Output Type When Reset Shared by

This pin outputs signals from the charge

pump of the PLL frequency synthesizer.

If the frequency divided from the local

EO oscillator (VCO) frequency is higher (lower) O CMOS 3-state High-impedance —

than the reference frequency, high (low)

level is output from this pin, respectively.

When the two frequencies match, this pin

is placed in the high-impedance state.

This pin outputs pulse swallow control

PSC signal. This signal switches division ratio O CMOS push-pull Output —

for the dedicated prescaler µPB595.

This pin is the input of the local oscillator.

The output signal coming from the local

oscillator (VCO) in the tuner and divided by

VCO the dedicated prescaler µPB595 should be I — —

input to this pin, where the µPB595 is a

two-module prescaler capable of frequency

division up to 1 GHz.

Internally

pulled down

HSCNT I — Input P0B3

BLANK O CMOS push-pull Low level output —

RED data that correspond the R signal (one of O CMOS push-pull Low level output —

GREEN that correspond the G signal (one of the O CMOS push-pull Low level output —

BLUE that correspond the B signal (one of the O CMOS push-pull Low level output —

I O CMOS push-pull Input P0B2

HSYNC I — Input —

VSYNC I — Input —

OSCIN

OSCOUT

ADC0

ADC1

ADC2

ADC3

ADC4

ADC5

ADC7

This pin is the input of the H sync signal

counter.

This active-high pin outputs blanking

signals to delete video signals.

This active-high pin outputs character

the RGB signals of IDC).

This active-high pin outputs character data

RGB signals of IDC).

This active-high pin outputs character data

RGB signals of IDC).

This pin outputs character data that

correspond the I signal of IDC.

The H sync signals for IDC should be

input to this pin in an active-low manner.

The V sync signals for IDC should be input

to this pin in an active-low manner.

These are the input and output pins of the

LC oscillation circuit for IDC. Adjust the — — — —

oscillation frequency to 10 MHz.

These are the analog input pins of the

6-bit resolution A/D converter.

These are the analog input pins of the

6-bit resolution A/D converter.

I — Input

I — Input

P0D0/XTOUT

P0D1/XTIN

P0D2

P0D3

P1C0

P1C2

—

10

µ

PD17P068

Pin Name Description I/O Output Type When Reset Shared by

PWM0 P2C0

PWM3 P2C3

PWM4 These are the output pins of the O N-ch open-drain P2B0

8-bit resolution D/A converter. Middle-voltage

PWM7 P2B3

PWM8 P2A0

TMIN This pin is the input of basic timer 1 or 2. I — Input P1B3

Low-level output

or high impedance

XTIN

XTOUT

CKOUT O CMOS push-pull Input P1B1

SCK0 P0A2

SCK1 P2D0

Sl0 P0B0

Sl1 P2D2

SO0 P0A3

SO1 P2D1

SCL These pins input and output shift clocks. I/O N-ch open-drain Input P0A1

SDA These pins input and output serial data. I/O N-ch open-drain Input P0A0

INT0 request is issued at the rising or falling I — Input —

INTNC commands from a remote control unit I — Input —

A 32.768-kHz crystal resonator for watch

timer operation should be connected to — — —

these pins.

This pin outputs the signal to control the

watch timer.

These pins input and output shift clocks. I/O CMOS push-pull Input

These pins input serial data. I — Input

These pins output serial data. O CMOS push-pull Input

This pin inputs interrupt request signal

from external device. An interrupt

edge of the input signal applied to this

pin.

This pin inputs interrupt request signal

with noise canceller. Using this pin to

input signals with noise such as

simplifies programming processes.

The interrupt request issuing timing is

programmable to either rising or falling

edge of the input signal to this pin.

P0D1/ADC2

P0D0/ADC1

11

Loading...

Loading...