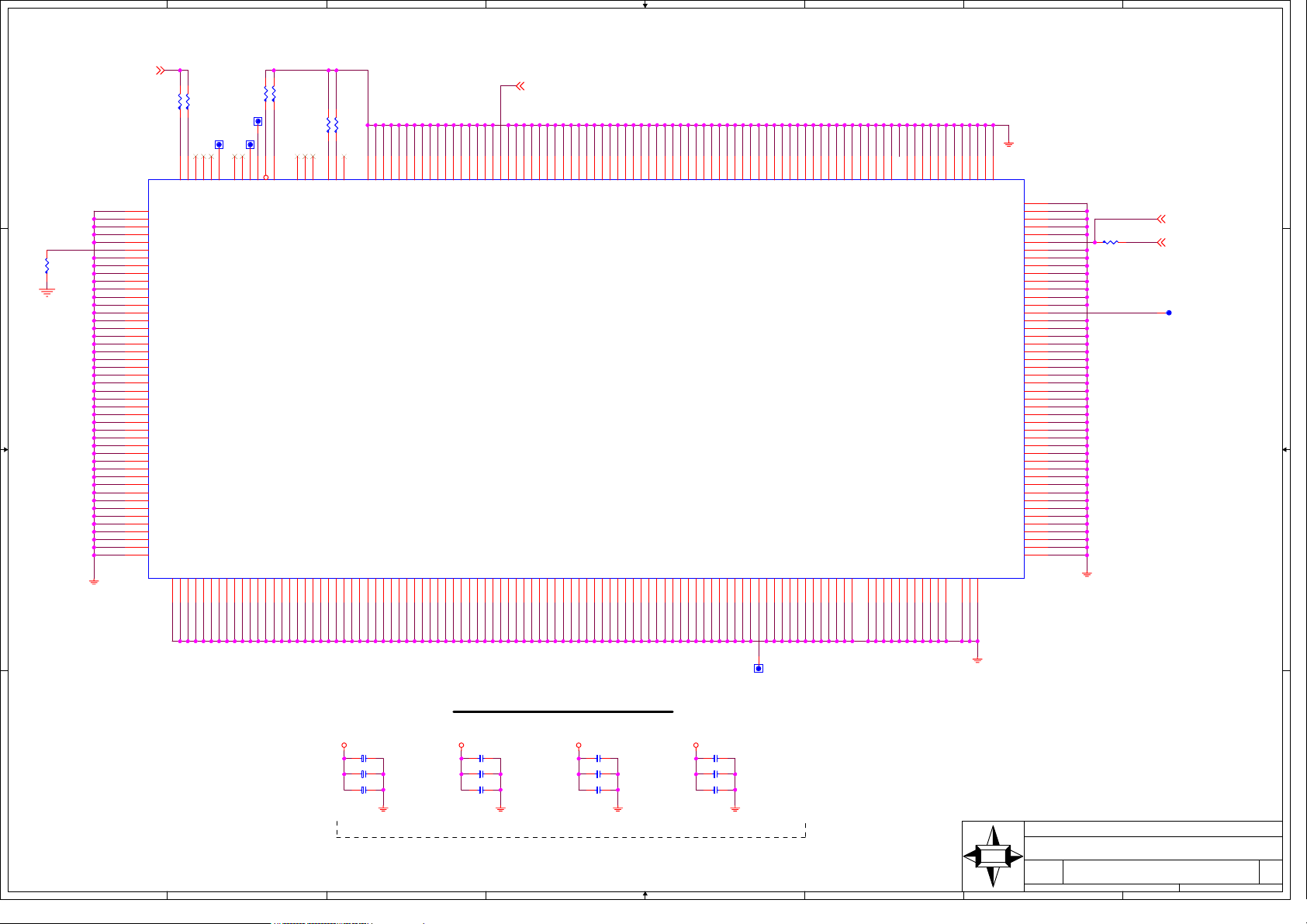

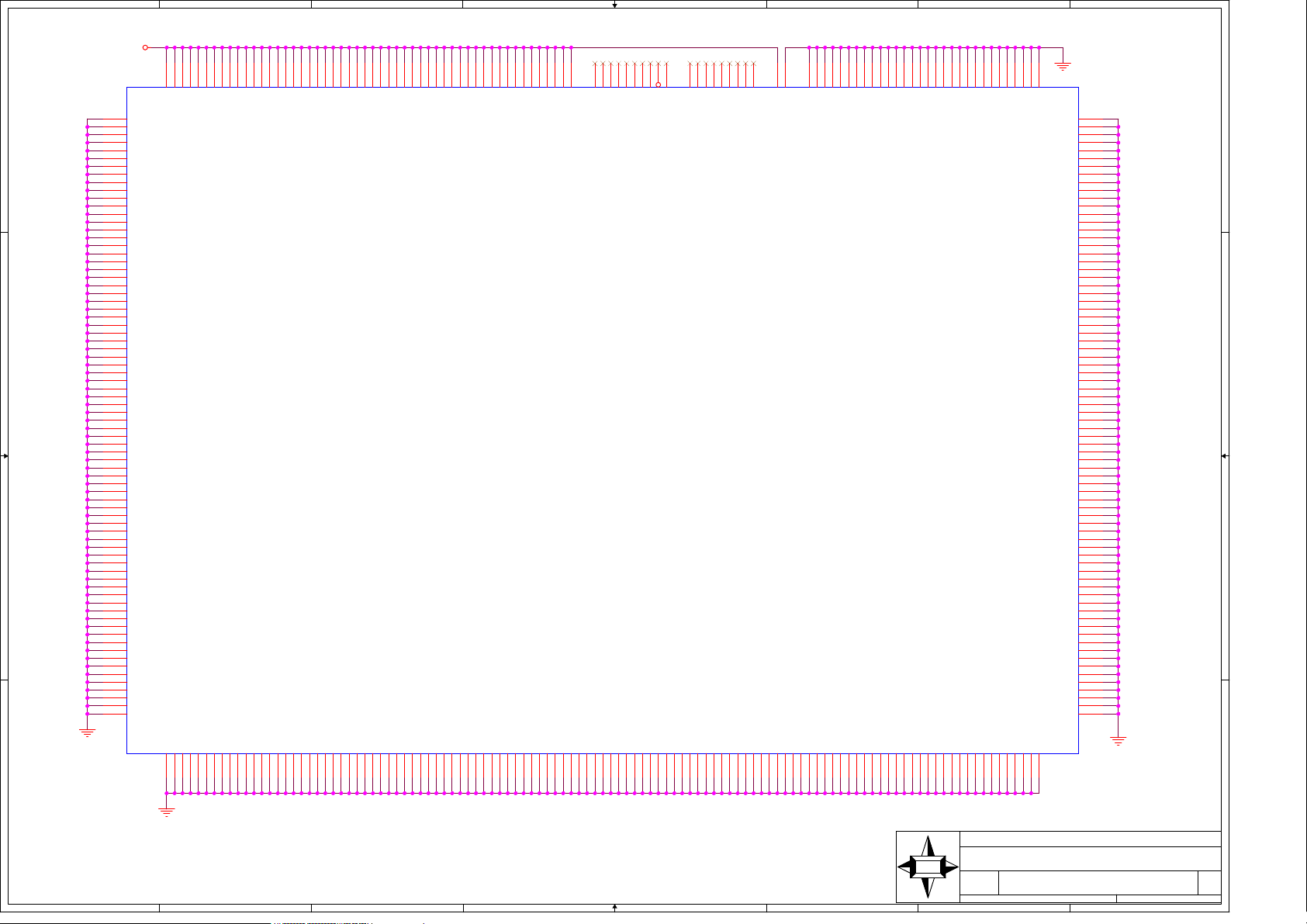

MSI MS-7315 Schematic 950707

A

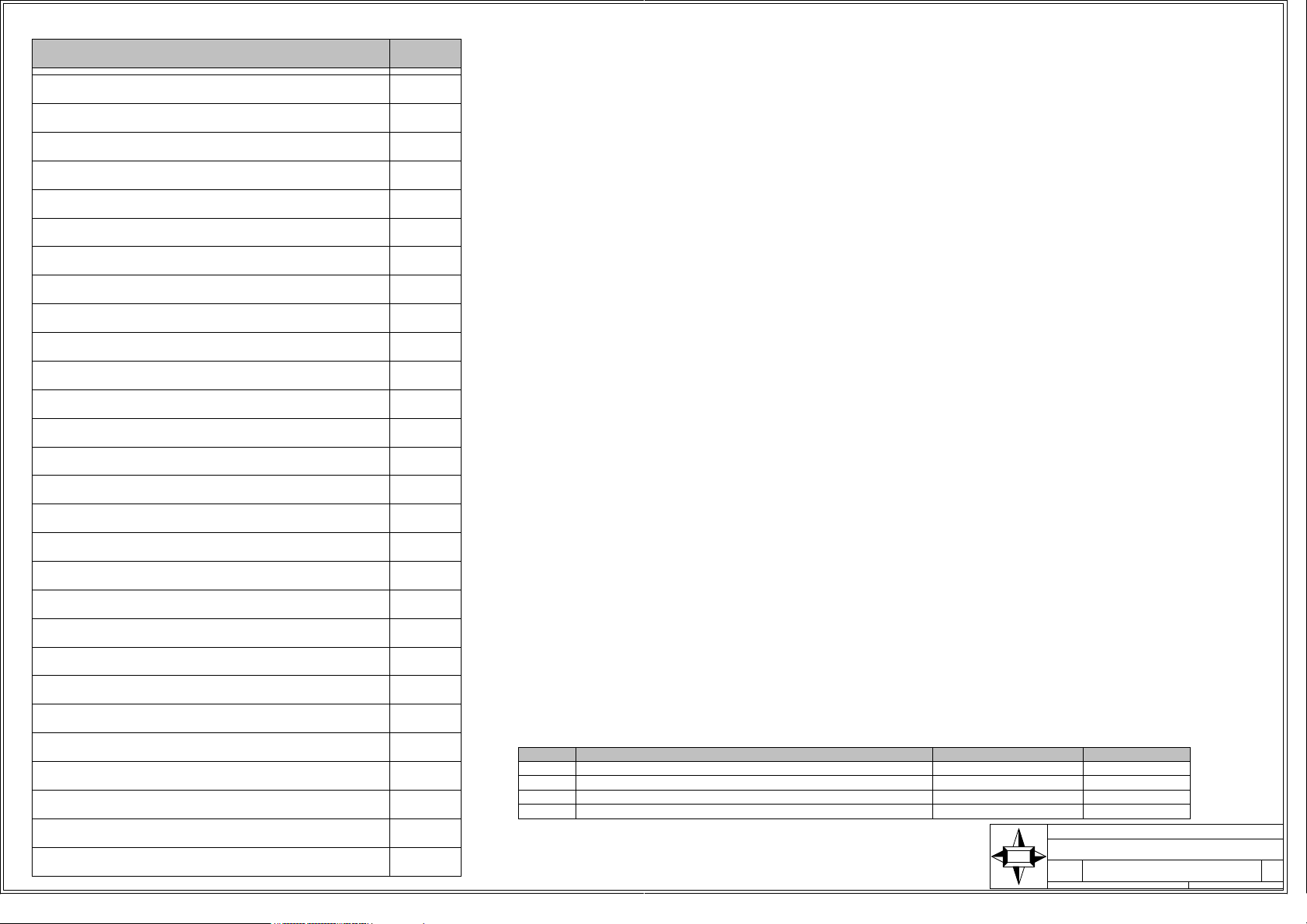

CONTENT SHEET

1

Cover Sheet, Block diagram

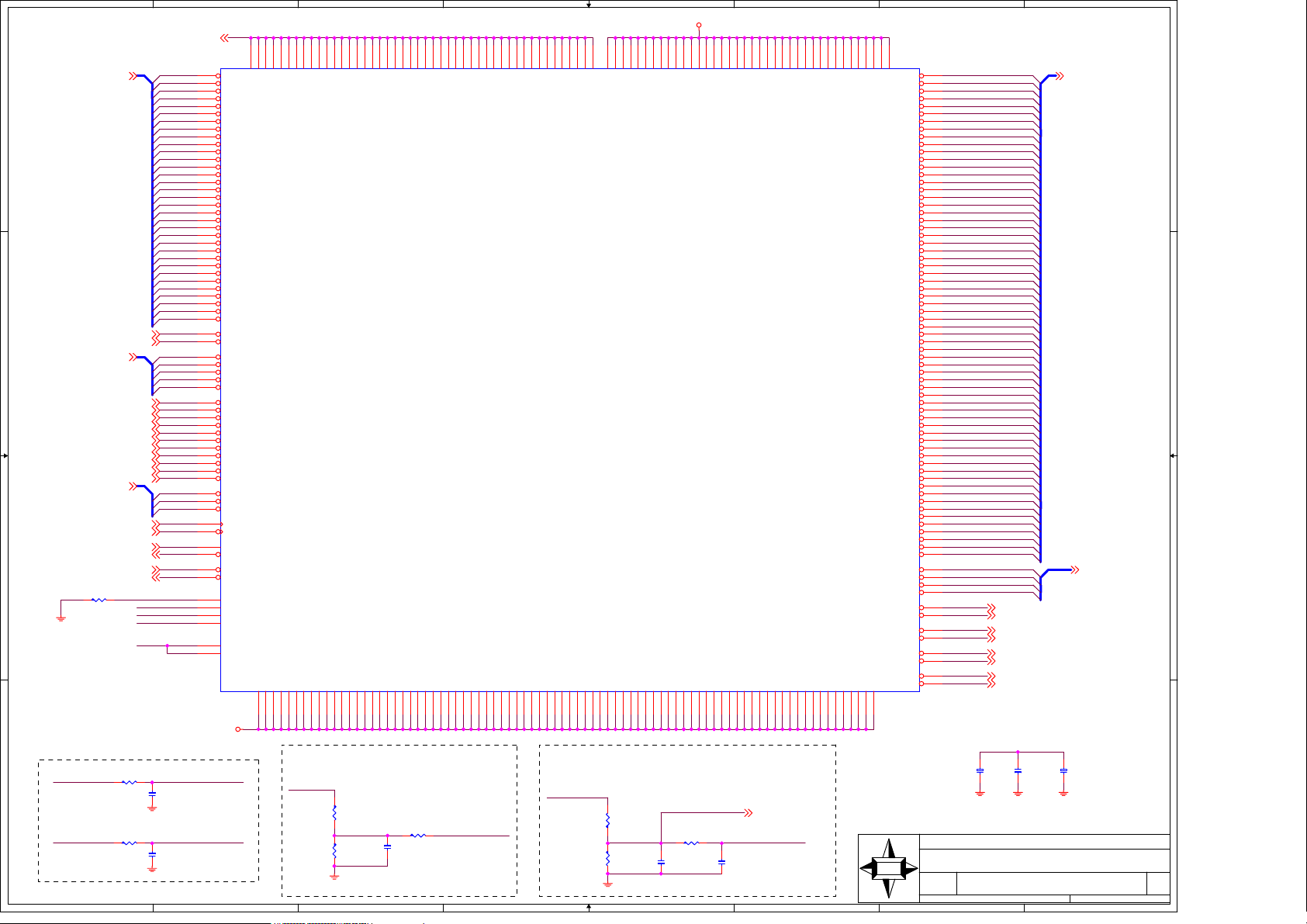

Intel LGA775 CPU - Signals

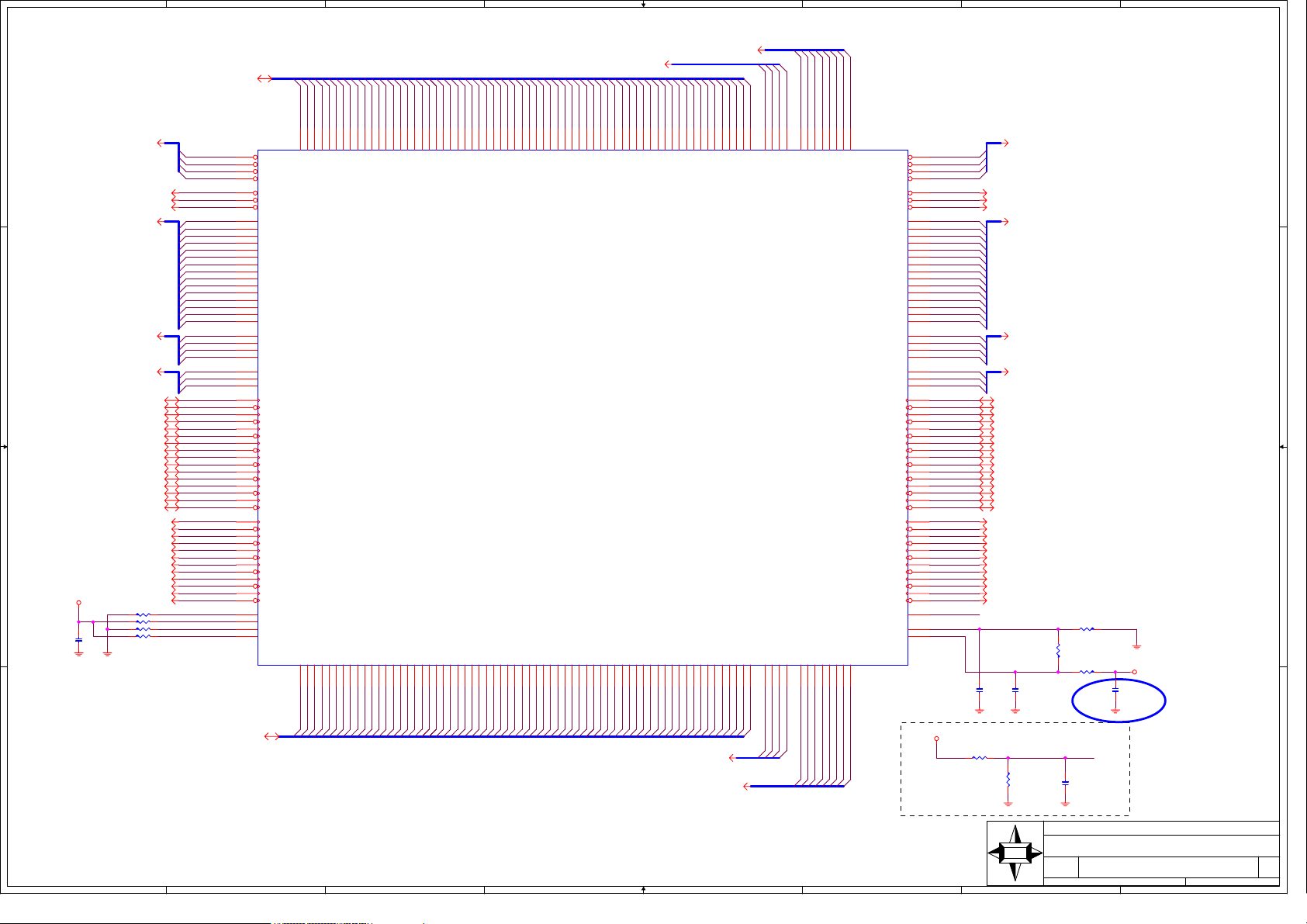

Intel LGA775 CPU - Power

Intel LGA775 CPU - GND

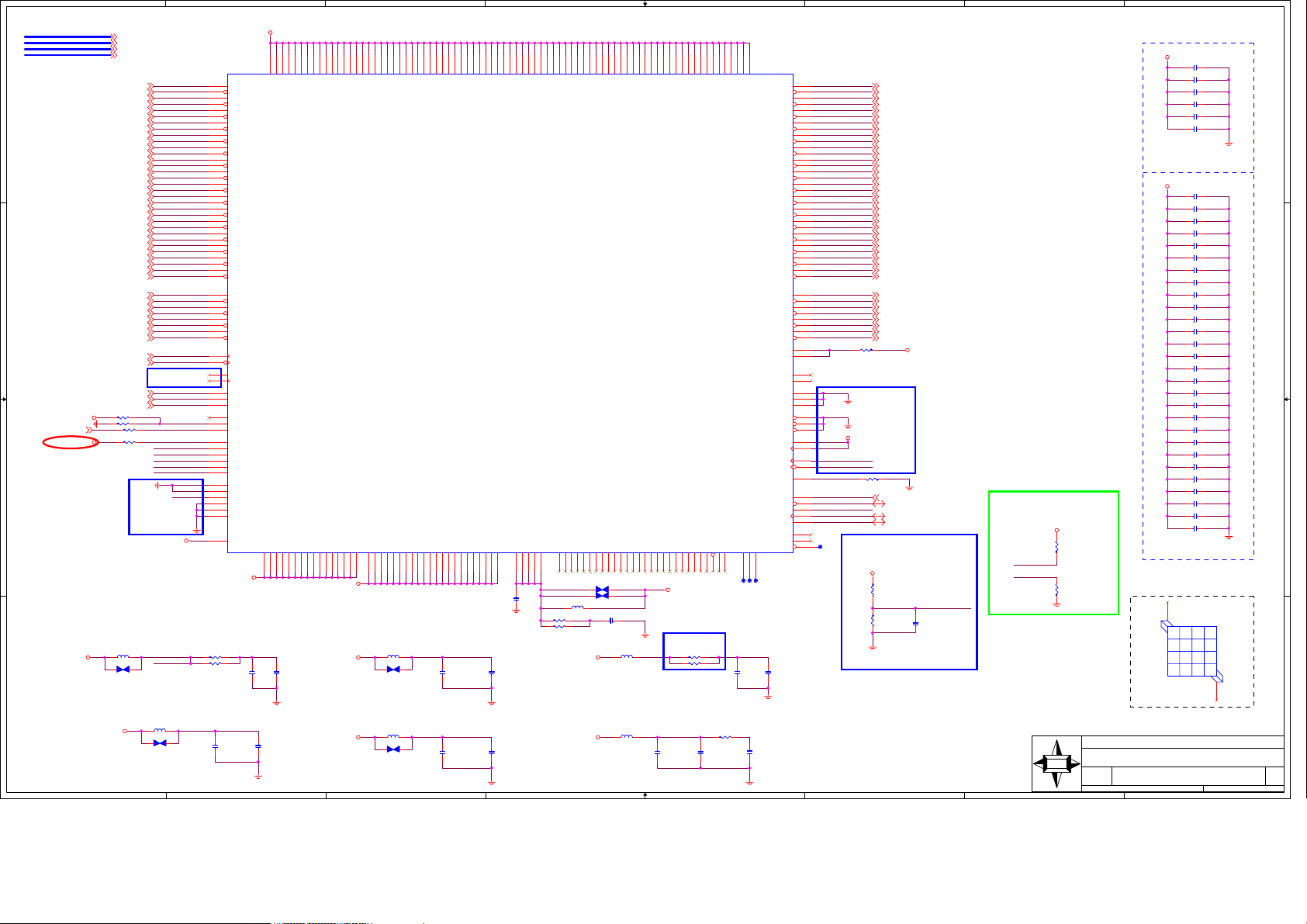

Intel Broadwater - CPU

Intel Broadwater - Memory

Intel Broadwater - PCI Express

Intel Broadwater - GND

ICH8

DDR2 DIMM 1 , 2 , 3 & 4

Clock Gen ICS9LPRS512

W83627DHG / LPC

PS2 / LPT / COM Port

A A

SATA / RTC / FAN Control

LAN - INTEL 82562V

Azalia Codec (ALC888)

PCIE X16 & X1 SLOT

PCI SLOT 1 & 2

ATX & F_Panel

USB Connectors

1-2

3

4

5

6

7

8

9

10-12

13~15

16

17

18

19

20

21

22

23

24

25

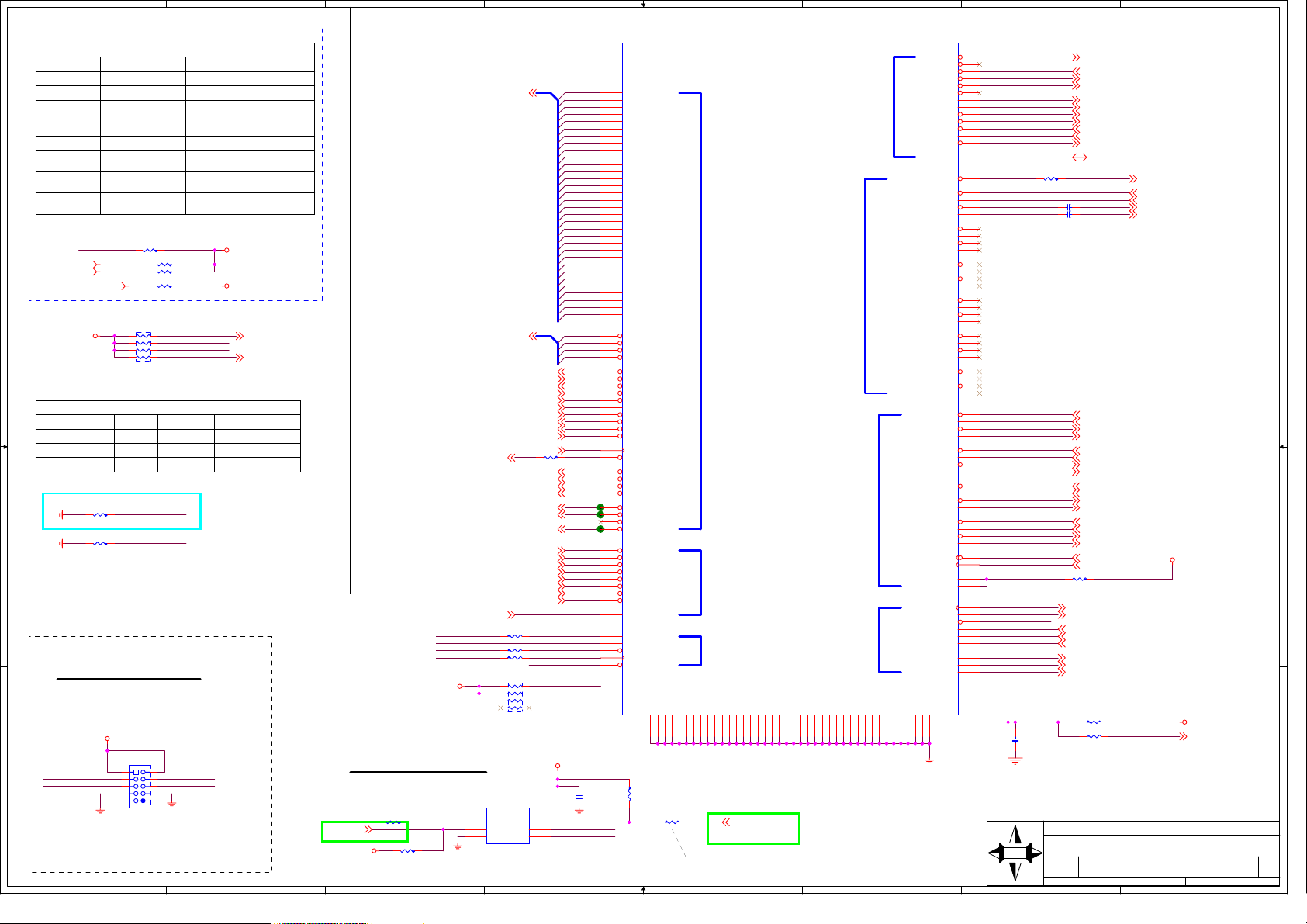

MS-7315 P1

CPU:

System Chipset:

On Board Device:

Main Memory:

Expansion Slots:

Intel Pentium 4 Cedar Mill / Prescott , Pentium D Smithfield /

Presler and Conroe family processors in LGA775 Package.

Intel Broadwater-P (North Bridge)

Intel ICH8DH (South Bridge)

BIOS -- SPI Flash 8M

Azalia Codec -- ALC888

LPC Super I/O -- W83627DHG /EHG(Ver:H)

LAN -- INTEL 82562V (10/100)

CLOCK Gen -- ICS 9LPRS512 (56pin)

1394 Controller -- VT6307 / VT6308 (2-port)

Hi-USB to PATA Bridge -- CY7C68300C-56PVXC (SSOP-56)

Dual-channel DDR-II * 4 (Max 4GB)

PCI EXPRESS X16 SLOT *1

PCI EXPRESS X1 SLOT * 1

PCI SLOT * 2

uATX

Version: 0.A

(Dalas)

IEEE1394-VIA6307 / 6308

MS7 ACPI Controller

VRD 11 - ISL6312 (4 Phases)

IDE Connector

GPIO & JUMPER SETTING

Revision History

Manual Parts

Power Delivery / PWOK / Reset Map

26

27

28

29

30

31

32

33~35

Intersil PWM:

Controller: Intersil ISL6312 (4 Phases)

Driver: Intersil ISL6612

Option Function

A

BW-965P/ICH8DH/W83627EHG/ALC888/82562V/USB to IDE

1

Orcad Configure BOM

cfg-A

MICRO-STAR INT'L CO.,LTD

MSI

Size Document Description Rev

Custom

Date:

Friday, July 07, 2006

MS-7315

COVER SHEET

Sheet of

135

0.A

1

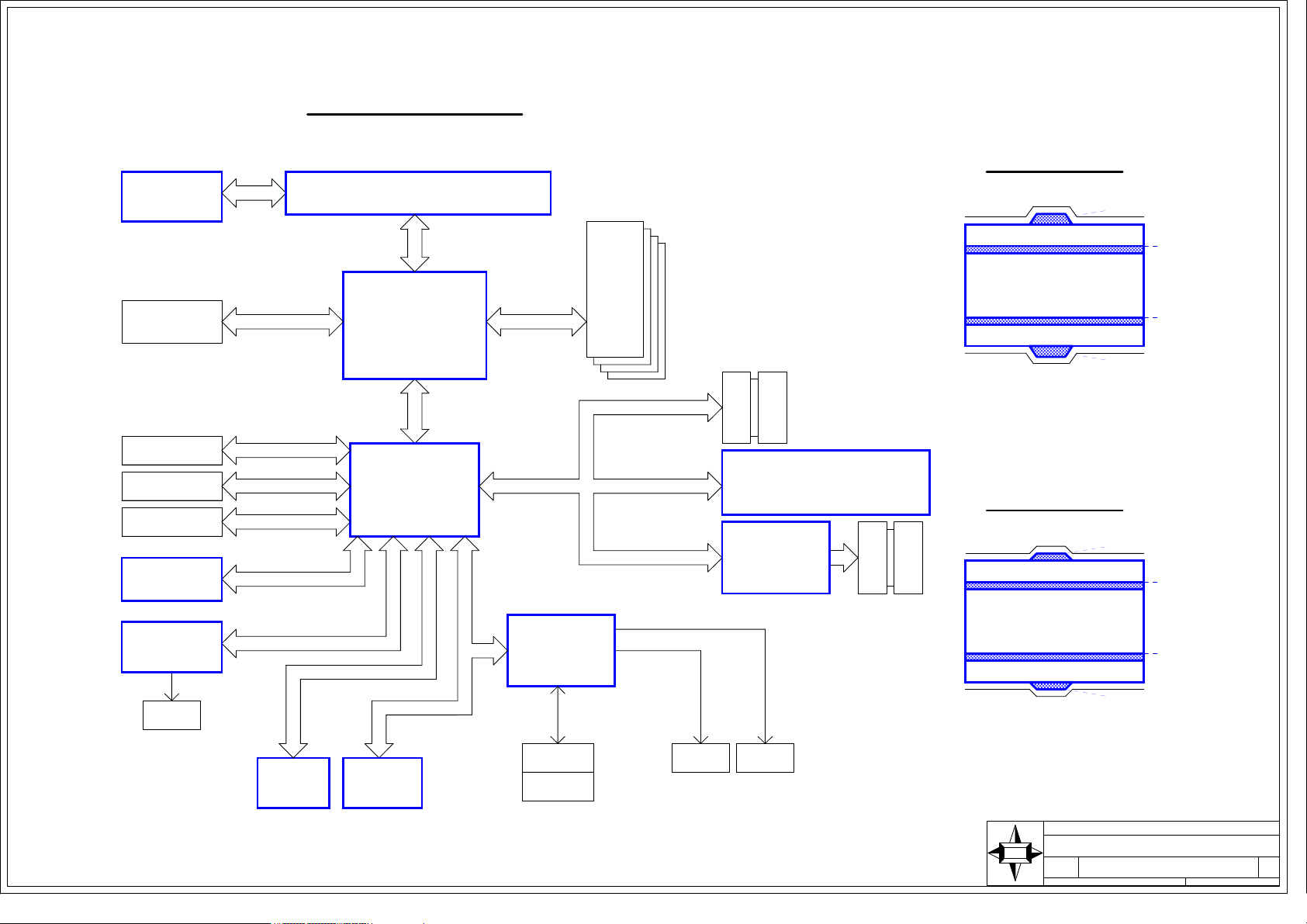

Block Diagram

Board Stack-up

VRD 11

ISL6312

4-Phase PWM

Intel LGA775 Processor

FSB 533/800/1066

FSB

DDR2 533/667/800

4 DDR II

DIMM

PCI_E X16

Connector

A A

PCI_E X1

PCI EXPRESS X16

PCI EXPRESS X1

Broadwater - P

GMCH

DMI

DDRII

Modules

PCI Slot 1

PCI Slot 2

LAN

SATA-II 0~3

USB Port 0~7

SATA2

USB2.0

ICH8 (DH)

PCI

INTEL 82562V (10/100)

J1394_1

J1394_2

1394

HD Audio Codec

ALC888

HD Audio Link

VT6307/6308

(1080 Prepreg Considerations)

Solder Mask

PREPREG 2.7mils

CORE 50mils

Solder Mask

PREPREG 2.7mils

Single End 50ohm Top/Bottom : 4mils

USB2.0 - 90ohm : 15/4.5/7.5/4.5/15

SATA - 95ohm : 15/4/8/4/15

LAN - 100ohm : 15/4/8/4/15

PCIE - 95ohm : 15/4/8/4/15

IEEE1394 - 110ohm : 15/4/9/4/15

IDE : 15/4/8/4/15

1.9mils Cu plus plating

1.9mils Cu plus plating

Board Stack-up

(2116 Prepreg Considerations)

Solder Mask

PREPREG 4.7mils

1/2 oz. Cu plus plating

1 oz. (1.2mils)

Cu Power

Plane

1 oz. (1.2mils)

Cu GND

Plane

1 oz. Cu Power

Plane

Hi-USB to PATA

CY7C68301C

-56PVXC

IDE

USB2.0

SPI

SPI

LPC

Flash ROM Debug Port

LPC Bus

LPC SIO

Winbond

W83627EHG

(W83627DHG)

Keyboard

Mouse

CORE 47mils

1 oz. Cu Ground

Plane

Parallel

Serial

Solder Mask

PREPREG 4.7mils

1/2 oz. Cu plus plating

Single End 60ohm Top/Bottom : 5mils

IEEE1394 - 110ohm Top : 5/7/5

PCIE, LAN, SATA - 100ohm Top : 5/6/5

USB2.0 - 90ohm Top : 7.5/7.5/7.5

MICRO-STAR INT'L CO.,LTD

MSI

Size Document Description Rev

Custom

Date:

1

Friday, July 07, 2006

MS-7315

BLOCK DIAGRAM

Sheet of

0.A

235

8

D D

H_TDI

H_TDO

H_TMS

H_TRST#

H_TCK

THERMDA

THERMDC

H_TESTHI13

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

H_DBI#[0..3]6

H_IERR#4

H_FERR#4,10

H_STPCLK#10

H_INIT#10

H_DBSY#6

H_DRDY#6

H_TRDY#6

C C

H_ADS#6

H_LOCK#6

H_BNR#6

H_HIT#6

H_HITM#6

H_BPRI#6

H_DEFER#6

TRMTRIP#4,10

H_PROCHOT#4,11

H_IGNNE#10

ICH_H_SMI#10

H_A20M#10

6/26 UPDATE

B B

VTT_OUT_RIGHT

H_D#[0..63]6

A A

R577 X_62R/2

CPU_BSEL016

CPU_BSEL116

CPU_BSEL216

H_PWRGD4,11

H_CPURST#4,6

H_D#63

H_D#62

H_D#61

H_D#60

H_D#59

H_D#58

H_D#57

H_D#56

H_D#55

H_D#54

7

G11

D19

C20

AB2

AB3

AD3

AD1

AF1

AC1

AG1

AE1

AL1

AK1

AE8

AL2

AH2

AE6

G10

D16

A20

AA2

G29

H30

G30

G23

B22

A22

A19

B19

B21

C21

B18

A17

B16

C18

H_A#[3..35]6

A8

F2

R3

M3

P3

H4

B2

C1

E3

D2

C3

C2

D4

E4

G8

G7

M2

N2

P2

K3

L2

N5

C9

Y1

V2

N1

U8A

DBI0#

DBI1#

DBI2#

DBI3#

EDRDY#

IERR#

MCERR#

FERR#/PBE#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

TESTI_13

RSVD#AH2

RESERVED0

RESERVED1

RESERVED2

RESERVED3

RESERVED4

RESERVED5

BOOTSELECT

LL_ID0

LL_ID1

BSEL0

BSEL1

BSEL2

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

D53#

B15

H_D#53

D52#

D51#

C14

C15

H_D#51

H_D#52

D50#

D49#

A14

D17

H_D#50

H_D#49

6

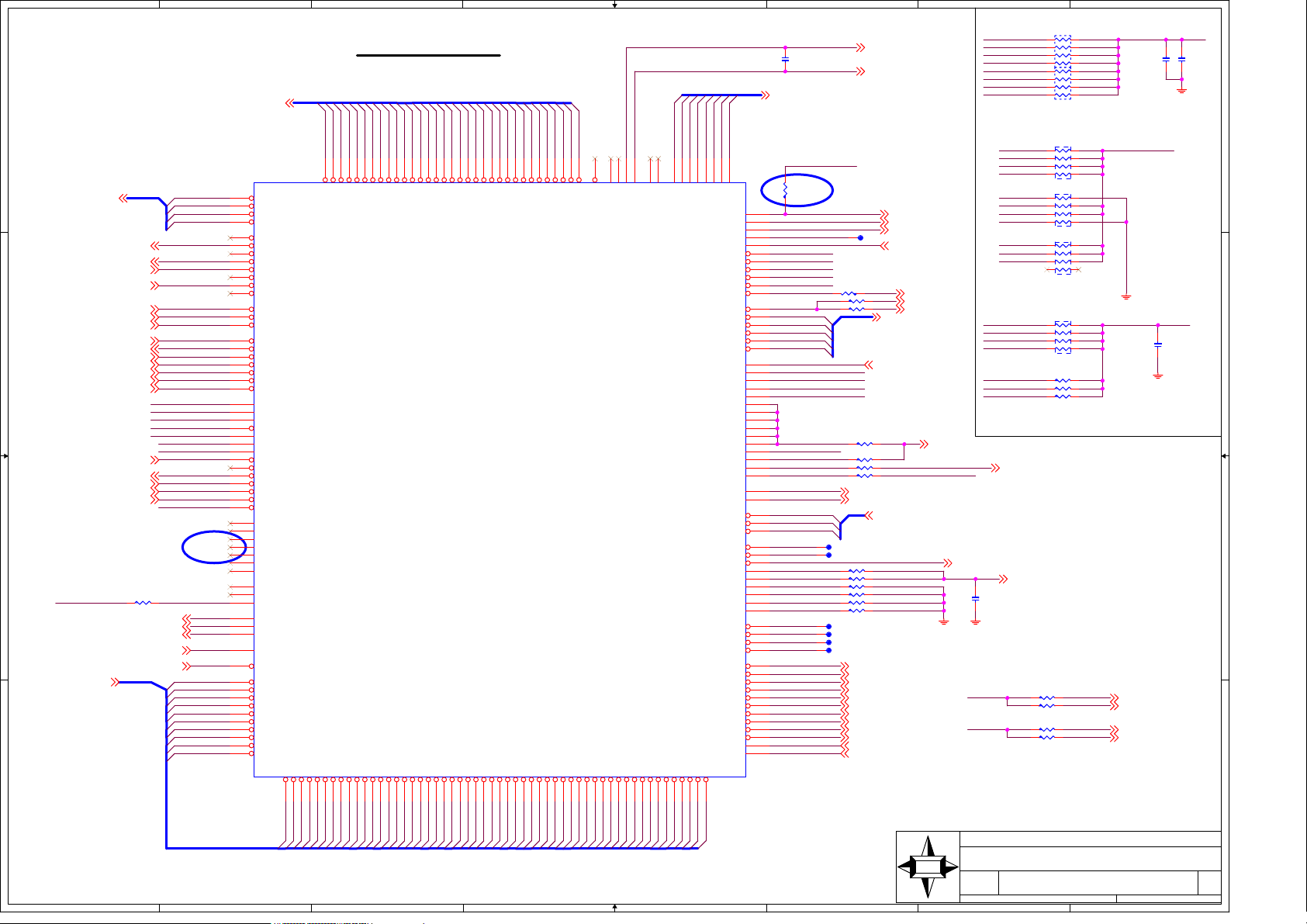

CPU SIGNAL BLOCK

H_A#28

H_A#27

H_A#31

H_A#32

H_A#35

H_D#48

H_A#34

AJ6

A35#

D48#

D20

H_D#47

H_A#33

AJ5

A34#

D47#

G22

H_D#46

AH5

A33#

D46#

D22

H_D#45

AH4

A32#

D45#

E22

H_D#44

H_A#30

AG5

AG4

A31#

D44#

F21

G21

H_D#43

H_A#29

AG6

A30#

A29#

D43#

D42#

E21

H_D#42

AF4

AF5

A28#

A27#

D41#

D40#

F20

E19

H_D#41

H_D#40

H_A#26

AB4

E18

H_D#39

H_A#25

AC5

A26#

A25#

D39#

D38#

F18

H_D#38

H_A#23

H_A#24

AB5

AA5

A24#

A23#

D37#

D36#

F17

G17

H_D#36

H_D#37

H_A#22

H_A#21

AD6

AA4

A22#

A21#

D35#

D34#

E16

G18

H_D#34

H_D#35

H_A#18

H_A#20

H_A#19

A20#Y4A19#Y6A18#W6A17#

D33#

D32#

E15

G16

G15

H_D#31

H_D#32

H_D#33

H_A#16

H_A#17

H_A#15

H_A#14

AB6

A16#W5A15#V4A14#V5A13#U4A12#U5A11#T4A10#

D31#

D30#

D29#

D28#

F15

F14

G14

G13

H_D#29

H_D#28

H_D#30

H_D#27

H_A#13

D27#

D26#

E13

H_D#26

H_A#11

H_A#12

D25#

D24#

F12

D13

H_D#25

H_D#24

5

H_A#8

H_A#10

H_A#7

H_A#9

U6

A9#T5A8#R4A7#M4A6#L4A5#M5A4#P6A3#

D23#

D22#

D21#

F11

E10

D10

H_D#20

H_D#23

H_D#21

H_D#22

H_A#3

H_A#4

H_A#5

H_A#6

L5

D20#D7D19#E9D18#F9D17#F8D16#G9D15#

D11

H_D#14

H_D#15

H_D#17

H_D#18

H_D#19

H_D#16

AC2

DBR#

D14#

C12

H_D#13

D13#

B12

H_D#12

AN4

AN3

VCC_SENSE

D12#D8D11#

C11

H_D#11

VSS_SENSE

AN5

AN6

VSS_MB_REGULATION

VCC_MB_REGULATION

D10#

D9#

B10

A11

H_D#9

H_D#10

AJ3

D8#

A10

H_D#8

H_D#7

4

VCC_VRM_SENSE

VSS_VRM_SENSE

VID3

VID7

VID6

VID4

VID5

AM7

AM5

AL4

AK4

AK3

ITP_CLK1

AL6

VID6#

VID5#

VID4#

VID3#

VID_SELECT

ITP_CLK0

RSVD#AM7

GTLREF0

GTLREF1

GTLREF_SEL

GTLREF2

TESTHI12

TESTHI11

TESTHI10

FORCEPH

RSVD#G6

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

LINT1/NMI

LINT0/INTR

D7#A7D6#B7D5#B6D4#A5D3#C6D2#A4D1#C5D0#

B4

H_D#0

H_D#2

H_D#5

H_D#6

H_D#3

H_D#4

H_D#1

VID2

VID1

VID0

AM3

AL5

AM2

VID2#

VID1#

VID0#

AN7

H1

H2

H29

E24

AG3

BPM5#

AF2

BPM4#

AG2

BPM3#

AD2

BPM2#

AJ1

BPM1#

AJ2

BPM0#

G5

PCREQ#

J6

REQ4#

K6

REQ3#

M6

REQ2#

J5

REQ1#

K4

REQ0#

W2

P1

H5

G4

TESTHI9

G3

TESTHI8

F24

TESTHI7

G24

TESTHI6

G26

TESTHI5

G27

TESTHI4

G25

TESTHI3

F25

TESTHI2

W3

TESTHI1

F26

TESTHI0

AK6

G6

G28

BCLK1#

F28

BCLK0#

A3

RS2#

F5

RS1#

B3

RS0#

U3

AP1#

U2

AP0#

F3

BR0#

T2

COMP5

J2

COMP4

R1

COMP3

G2

COMP2

T1

COMP1

A13

COMP0

J17

DP3#

H16

DP2#

H15

DP1#

J16

DP0#

AD5

R6

C17

G19

E12

B9

A16

G20

G12

C8

L1

K1

ZIF-SOCK775-15u-in

EC85

C10U6.3X5R6

VID[0..7] 28

VTT_OUT_RIGHT

R62

680R/2

CPU_GTLREF0

CPU_GTLREF1

GTLREF_SEL

CPU_MCH_GTLREF

H_BPM#5

H_BPM#4

H_BPM#3

H_BPM#2

H_BPM#1

H_BPM#0

H_PECI

H_REQ#4

H_REQ#3

H_REQ#2

H_REQ#1

H_REQ#0

H_TESTHI12

H_TESTHI11

H_TESTHI10

H_TESTHI9

H_TESTHI8

H_TESTHI2_7

H_TESTHI1

H_TESTHI0

FORCEPH

RSVD_G6

H_RS#2

H_RS#1

H_RS#0

TEST-U3

TEST-U2

H_COMP5

H_COMP4

H_COMP3

H_COMP2

H_COMP1

H_COMP0

TEST-J17

TEST-H16

TEST-H15

TEST-J16

3

VCC_VRM_SENSE 28

VSS_VRM_SENSE 28

6/23 UPDATE

VRD_VIDSEL 28

CPU_GTLREF0 4

CPU_GTLREF1 4

T4

CPU_MCH_GTLREF 6

R574 X_0R/2

R499 X_0R/2

R500 0R/2

R145 51R/2

R142 51R/2

R83 X_130R/2

R102 X_51R/2

T2

T1

R94 49.9R1%/2

R106 49.9R1%/2

R99 49.9R1%/2

R124 49.9R1%/2

R95 49.9R1%/2

R151 49.9R1%/2

T5

T7

T3

T6

H_REQ#[0..4] 6

H_TESTHI12 5

CK_H_CPU# 16

CK_H_CPU 16

H_RS#[0..2] 6

H_ADSTB#1 6

H_ADSTB#0 6

H_DSTBP#3 6

H_DSTBP#2 6

H_DSTBP#1 6

H_DSTBP#0 6

H_DSTBN#3 6

H_DSTBN#2 6

H_DSTBN#1 6

H_DSTBN#0 6

H_NMI 10

H_INTR 10

TP_CPU_G1 5

ICH8_PECI 10,17

IO_PECI 17

V_FSB_VTT 4,6,12,16,17,27

VTT_OUT_RIGHT

VTT_OUT_LEFT

H_BR#0 4,6

THERMDA

THERMDC

2

VID2

VID0

VID5

VID4

VID7

VID3

VID6

VID1

H_BPM#0

H_BPM#1

H_BPM#5

H_BPM#3

H_TRST#

H_BPM#4

H_TDO

H_TCK

H_TDI

H_BPM#2

H_TMS

H_TESTHI11

H_TESTHI9

H_TESTHI10

H_TESTHI8

H_TESTHI1

H_TESTHI13

VTT_OUT_RIGHT 4,5

VTT_OUT_LEFT 4,5

C75

C0.1U16Y2

R616 0R/2

R617 X_0R/2

R619 0R/2

R618 X_0R/2

RN2

8P4R-680R

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

RN3

8P4R-680R

1 2

3 4

5 6

7 8

RN5 8P4R-51R/2

1 2

3 4

5 6

7 8

RN6 8P4R-51R/2

1 2

3 4

5 6

7 8

RN8 8P4R-51R/2

1 2

3 4

5 6

7 8

RN10 8P4R-51R/2

R122 51R/2

R101 51R/2

R103 51R/2

1

VTT_OUT_RIGHT

C65

C0.1U16Y2

VTT_OUT_RIGHT

VTT_OUT_LEFTH_TESTHI12

THERMDA_IO 17

THERMDA_ICH8 11

THERMDC_IO 17

THERMDC_ICH8 11

C0.1U16Y2

C69

C0.1U16Y2

C60

MICRO-STAR INT'L CO.,LTD

MSI

Size Document Description Rev

Custom

Date:

8

7

6

5

4

3

Friday, July 07, 2006

2

MS-7315

LGA775 - SIGNALS

Sheet of

335

1

0.A

8

VCCP

AF22

AF21

AF9

VCC#AF19

VCC#AF18

VCC#AF15

VCC#AF14

VCC#AF12

VCC#AF11

VCC#AE9

VCC#AE23

VCC#AE22

VCC#AE21

VCC#AE19

VCC#AE18

VCC#AE15

VCC#AE14

VCC#AE12

VCC#AE11

VCC#AD8

VCC#AD30

VCC#AD29

VCC#AD28

VCC#AD27

VCC#AD26

VCC#AD25

VCC#AD24

VCC#AD23

VCC#AC8

VCC#AC30

VCC#AC29

VCC#AC28

VCC#AC27

VCC#AC26

VCC#AC25

VCC#AC24

VCC#AC23

VCC#AB8

VCC#AA8

AF8

VCC#AF9

VCC#AF8

VCC#AF22

VCC#AF21

VCC#Y28

VCC#Y29

VCC#Y30

VCC#Y8

Y8

Y28

Y29

Y30

U8B

VCCP

D D

C C

AF19

AF18

AF15

AF14

AF12

AF11

AE9

AE23

AE22

AE21

AE19

AE18

AE15

AE14

AE12

AE11

AD8

AD30

AD29

AD28

AD27

AD26

AD25

AD24

AD23

AC8

AC30

AC29

AC28

AC27

AC26

AC25

AC24

AC23

AB8

AA8

VCCP

7

AG30

AG29

AG28

AG27

AG26

AG25

AG22

AG21

AG19

AG18

AG15

AG14

AG12

AG11

VCC#AG25

VCC#AG22

VCC#AG21

VCC#AG19

VCC#AG18

VCC#AG15

VCC#AG14

VCC#AG12

VCC#AG11

VCC#W28

VCC#W29

VCC#W30

VCC#W8

VCC#Y23

VCC#Y24

VCC#Y25

VCC#Y26

VCC#Y27

W8

Y23

Y24

Y25

Y26

Y27

W30

W29

W28

W27

VCC#AG28

VCC#AG27

VCC#AG26

VCC#W25

VCC#W26

VCC#W27

W25

W26

VCC#AG30

VCC#AG29

VCC#W24

W23

W24

AG8

VCC#AG8

VCC#V8V8VCC#W23

AG9

VCC#AG9

VCC#U8

U8

AH12

AH11

VCC#AH12

VCC#AH11

VCC#U29

VCC#U30

U29

U30

AH14

VCC#AH14

VCC#U28

U28

AH18

AH15

VCC#AH18

VCC#AH15

VCC#U26

VCC#U27

U26

U27

AH21

AH19

VCC#AH21

VCC#AH19

VCC#U24

VCC#U25

U24

U25

AH22

U23

6

AH8

AH9

AJ11

AJ12

AJ14

AJ15

AJ18

AH27

AH26

AH25

AH28

AH29

AH30

VCC#AH8

VCC#AH27

VCC#AH26

VCC#AH25

VCC#AH22

VCC#AH28

VCC#AH29

VCC#AH30

VCC#T25

VCC#T26

VCC#T27

VCC#T28

VCC#T29

VCC#T30

VCC#T8T8VCC#U23

T24

T25

T26

T27

T28

T29

T30

AJ19

VCC#AH9

VCC#AJ11

VCC#AJ12

VCC#AJ14

VCC#AJ15

VCC#AJ18

VCC#AJ19

VCC#N29

VCC#N30

VCC#N8

VCC#P8P8VCC#R8

VCC#T23

VCC#T24

N8

R8

T23

N29

N30

AJ21

AJ22

VCC#AJ21

VCC#AJ22

VCC#N27

VCC#N28

N27

N28

AJ25

AJ26

VCC#AJ25

VCC#AJ26

VCC#N25

VCC#N26

N25

N26

AJ8

AJ9

VCC#AJ8

VCC#AJ9

VCC#N24

N23

N24

5

AK11

AK12

VCC#AK11

VCC#M8M8VCC#N23

M30

4

AL11

AL12

AL14

AL15

AL18

AL19

AL21

AL22

AL25

AL26

AL29

AL30

AL8

AL9

AM11

AM12

AM14

AM15

AM18

AM19

VCC#AM11

VCC#AM12

VCC#J24

VCC#J25

J23

J24

VCC#AM14

VCC#AM15

VCC#J22

VCC#J23

J21

J22

AM21

VCC#AM18

VCC#AM19

VCC#J20

VCC#J21

J19

J20

AK14

AK15

AK18

AK19

AK21

AK22

AK25

AK26

AK8

AK9

VCC#AL8

VCC#AK8

VCC#AK9

VCC#AL11

VCC#AL12

VCC#AL14

VCC#AL15

VCC#AL18

VCC#AL19

VCC#AL21

VCC#AK12

VCC#AK14

VCC#AK15

VCC#AK18

VCC#AK19

VCC#AK21

VCC#AK22

VCC#AK25

VCC#AK26

VCC#K28

VCC#K29

VCC#K30

VCC#K8K8VCC#L8L8VCC#M23

VCC#M24

VCC#M25

VCC#M26

VCC#M27

VCC#M28

VCC#M29

VCC#M30

K28

K29

K30

M23

M24

M25

M26

M27

M28

M29

VCC#AL22

VCC#K24

VCC#K25

VCC#K26

VCC#K27

K23

K24

K25

K26

K27

VCC#AL25

VCC#J8J8VCC#J9J9VCC#K23

J30

VCC#AL26

VCC#AL29

VCC#J29

VCC#J30

J28

J29

VCC#AL30

VCC#J27

VCC#J28

J26

J27

VCC#AL9

VCC#J26

J25

AM22

AM25

VCC#AM21

VCC#AM22

VCC#J18

VCC#J19

J15

J18

AM26

AM29

VCC#AM25

VCC#AM26

VCC#J14

VCC#J15

J13

J14

AM30

AM8

VCC#AM29

VCC#AM30

VCC#J12

VCC#J13

J11

J12

3

AM9

VCC#AM8

VCC#AM9

VCC#J10

VCC#J11

J10

AN11

AN12

VCC#AN11

VCC#AN12

VCC#AN8

VCC#AN9

AN8

AN9

AN14

AN15

AN18

AN19

VCC#AN14

VCC#AN15

VCC#AN18

VCC#AN19

VTT_OUT_RIGHT

VTT_OUT_LEFT

VCC#AN25

VCC#AN26

VCC#AN29

VCC#AN30

AN25

AN26

AN29

AN30

AN21

AN22

A23

VCCA

B23

VSSA

VCC#AN22

VCCPLL

VTT#A25

VTT#A26

VTT#A27

VTT#A28

VTT#A29

VTT#A30

VTT#B25

VTT#B26

VTT#B27

VTT#B28

VTT#B29

VTT#B30

VTT#C25

VTT#C26

VTT#C27

VTT#C28

VTT#C29

VTT#C30

VTT#D25

VTT#D26

VTT#D27

VTT#D28

VTT#D29

VTT#D30

VTT_SEL

RSVD#F29

1122334

D23

C23

A25

A26

A27

A28

A29

A30

B25

B26

B27

B28

B29

B30

C25

C26

C27

C28

C29

C30

D25

D26

D27

D28

D29

D30

AM6

AA1

J1

F27

F29

4

VCC#AN21

VCC-IOPLL

VTTPWRGD

ZIF-SOCK775-15u-in

2

H_VCCA

H_VSSA

H_VCCPLL

H_VCCIOPLL

VTT_PWG

VTT_OUT_RIGHT

VTT_OUT_LEFT

VTT_SEL

6/23 UPDATE

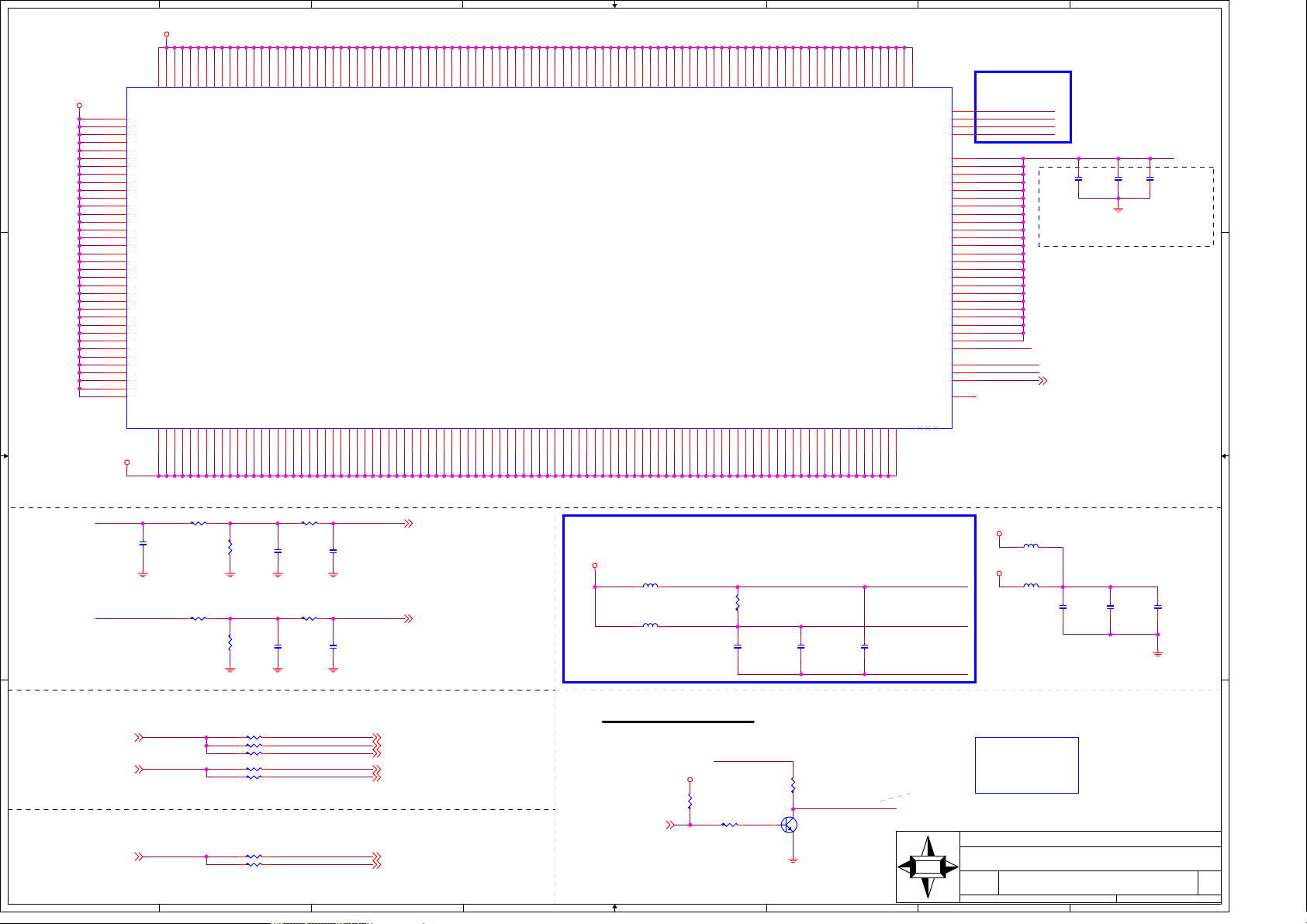

V_FSB_VTT

C130

C169

C10U10Y5

C10U10Y5

CAPS FOR FSB GENERIC

VTT_SEL 27

1

C118

C10U6.3X5R6

VTT_OUT_RIGHT

B B

VTT_OUT_RIGHT

R120 124R1%/2

C621

C10U6.3X5R6

R115 124R1%/2

R121

210R1%/2

R114

210R1%/2

PLACE AT CPU END OF ROUTE

VTT_OUT_RIGHT

VTT_OUT_LEFT3,5 H_PWRGD 3,11

A A

VTT_OUT_LEFT

R93 130R1%/2

R90 62R/2

R54 62R/2

R100 X_100R/2

R126 62R/2

PLACE AT ICH END OF ROUTE

V_FSB_VTT3,6,12,16,17,27

8

R309 62R/2

R319 62R/2

7

R118 10R/2

C76

C1U16Y3

R116 10R/2

C71

C1U16Y3

H_PROCHOT#

H_IERR#

H_CPURST#

H_PWRGD

H_BR#0

TRMTRIP#V_FSB_VTT

H_FERR#

C79

C220P50N2

C77

C220P50N2

CPU_GTLREF0 3

*GTLREF VOLTAGE SHOULD BE

0.63*VTT = 0.756V

CPU_GTLREF1 3

H_PROCHOT# 3,11VTT_OUT_RIGHT3,5

H_IERR# 3

H_CPURST# 3,6

H_BR#0 3,6

TRMTRIP# 3,10

H_FERR# 3,10

6

*PLACE COMPONENTS AS CLOSE AS POSSIBLE TO PROCESSOR SOCKET

*TRACE WIDTH TO CAPS MUST BE NO SMALLER THAN 12MILS

V_FSB_VTT

L3 10uH/8/125mA/Rdc=0.7

R585

0R/2

L34 10uH/8/125mA/Rdc=0.7

C109

C1U16Y3

C114

C22U10X50805

C117

C1U16Y3

H_VCCIOPLL

H_VCCA

H_VSSA

V_FSB_VTT

L35 10uH/8/125mA/Rdc=0.7

V_1P5_ICH

L36 X_10uH/8/125mA/Rdc=0.7

X_C1U16Y3

6/23 UPDATE

C132

H_VCCPLL

C134

C103P25X2

C126

C10U10Y5

VTT_PWRGOOD

VTT_PWG SPEC :

VCC5_SB

VID_GD#16,27,28

VTT_OUT_RIGHT

R59

1KR/2

R58 1KR/2

R60

680R/2

Q6

2N3904

1.25V VTT_PWRGOOD

VTT_PWG

MSI

5

4

3

High > 0.9V

Low < 0.3V

Trise < 150ns

MICRO-STAR INT'L CO.,LTD

Size Document Description Rev

Custom

Date:

Wednesday, July 12, 2006

2

MS-7315

LGA775 - POWER

Sheet of

435

1

0.A

8

VTT_OUT_RIGHT3,4

R78

R89

VSS#A12

VSS#A15

VSS#A18

VSS#A2

VSS#A21

VSS#A24

VSS#A6

VSS#A9

VSS#AA23

VSS#AA24

VSS#AA25

VSS#AA26

VSS#AA27

VSS#AA28

VSS#AA29

VSS#AA3

VSS#AA30

VSS#AA6

VSS#AA7

VSS#AB1

VSS#AB23

VSS#AB24

VSS#AB25

VSS#AB26

VSS#AB27

VSS#AB28

VSS#AB29

VSS#AB30

VSS#AB7

VSS#AC3

VSS#AC6

VSS#AC7

VSS#AD4

VSS#AD7

VSS#AE10

VSS#AE13

VSS#AE16

VSS#AE17

VSS#AE2

VSS#AE20

VSS#AE24

VSS#AE25

VSS#AE26

VSS#AE27

VSS#AE28

VSS#AE29

AE29

H_COMP6

H_COMP7

AE3

COMP6Y3COMP7

VSS#AE30

AE5

AE30

49.9R1%/2

AE4

RSVD#AE4

VSS#AE5

VSS#AE7

AE7

D D

R578

X_1KR/2

C C

B B

49.9R1%/2

A12

A15

A18

A2

A21

A24

A6

A9

AA23

AA24

AA25

AA26

AA27

AA28

AA29

AA3

AA30

AA6

AA7

AB1

AB23

AB24

AB25

AB26

AB27

AB28

AB29

AB30

AB7

AC3

AC6

AC7

AD4

AD7

AE10

AE13

AE16

AE17

AE2

AE20

AE24

AE25

AE26

AE27

AE28

U8C

7

R108

TP2

RSVD#E5E5RSVD#E6E6RSVD#E7

VSS#AF20

AF23

R152

24.9R1%/2

R97

R96

RSVD#J3

VSS#AF3

51R/2

P5

N4

W1

AC4

MSID[1]V1MSID[0]

RSVD#P5

RSVD#N4

RSVD#AC4

VSS#AF30

VSS#AF6

VSS#AF7

VSS#AG10

VSS#AG13

VSS#AG16

VSS#AG17

AF6

AF7

AF30

AG10

AG13

AG16

AG17

51R/2

1

H_COMP8

1

E7

VSS#AF23

AF24

J3

F23

F6

B13

IMPSEL#

RSVD#F23

RSVD#B13

VSS#AF24

VSS#AF25

VSS#AF26

VSS#AF27

VSS#AF28

VSS#AF29

AF3

AF25

AF26

AF27

AF28

AF29

51R/2

TP3

TP4

1

D14

D1

E23

RSVD#D1

RSVD#E23

RSVD#D14

VSS#AF10

VSS#AF13

VSS#AF16

VSS#AF17

AF10

AF13

AF16

AF17

AF20

AG20

VSS#AG20

VSS#Y7Y7VSS#Y5Y5VSS#Y2

VSS#AG23

AG23

AG24

6

V30

V29

V28

V27

V26

V25

V24

Y2

V6

V3

W4

VSS#V7V7VSS#V6

VSS#V3

VSS#W7W7VSS#W4

VSS#V30

VSS#AG24

VSS#AG7

VSS#AH1

VSS#AH10

VSS#AH13

VSS#AH16

VSS#AH17

VSS#AH20

AH1

AG7

AH10

AH13

AH16

AH17

AH20

V23

U1

VSS#T7T7VSS#T6T6VSS#T3

VSS#V29

VSS#AH23

AH23

AH24

VSS#U7U7VSS#U1

VSS#V28

VSS#V27

VSS#V26

VSS#V25

VSS#V24

VSS#V23

VSS#AH24

VSS#AH3

VSS#AH6

VSS#AH7

VSS#AJ10

VSS#AJ13

VSS#AJ16

VSS#AJ17

VSS#AJ20

VSS#AJ23

AH3

AH6

AH7

AJ10

AJ13

AJ16

AJ17

AJ20

AJ23

5

H_TESTHI12 3

T3

R30

R29

R28

R5

VSS#R7R7VSS#R5

VSS#R30

VSS#R29

VSS#R28

VSS#AJ24

VSS#AJ27

VSS#AJ28

VSS#AJ29

VSS#AJ30

VSS#AJ4

AJ4

AJ24

AJ27

AJ28

AJ29

AJ30

R27

AJ7

4

P30

P29

P28

P27

P26

P25

P24

P23

VSS#P24

VSS#AK7

M1

L30

L29

L28

N3

VSS#N7N7VSS#N6N6VSS#N3

VSS#M7M7VSS#M1

VSS#P23

VSS#AL10

VSS#AL13

VSS#AL16

VSS#AL17

VSS#AL20

VSS#AL23

AL10

AL13

AL16

AL17

AL20

AL23

AL24

L27

L6

L3

VSS#L7L7VSS#L6

VSS#L3

VSS#L30

VSS#L29

VSS#L28

VSS#L27

VSS#AL24

VSS#AL27

VSS#AL28

VSS#AL3

VSS#AL7

VSS#AM1

VSS#AM10

AL3

AL7

AM1

AL27

AL28

AM10

K2

K5

L26

L25

L24

L23

VSS#K7K7VSS#K5

VSS#L26

VSS#L25

VSS#L24

VSS#L23

VSS#AM13

VSS#AM16

VSS#AM17

VSS#AM20

VSS#AM23

VSS#AM24

AM13

AM16

AM17

AM20

AM23

AM24

AM27

R26

R25

R24

R23

P4

R2

VSS#P7P7VSS#P4

VSS#R2

VSS#P30

VSS#P29

VSS#P28

VSS#P27

VSS#P26

VSS#R27

VSS#R26

VSS#R25

VSS#R24

VSS#R23

VSS#AJ7

VSS#AK10

VSS#AK13

VSS#AK16

VSS#AK17

VSS#AK2

VSS#AK20

VSS#AK23

AK2

AK10

AK13

AK16

AK17

AK20

AK23

VSS#P25

VSS#AK24

VSS#AK27

VSS#AK28

VSS#AK29

VSS#AK30

VSS#AK5

AK5

AK7

AK24

AK27

AK28

AK29

AK30

3

H17

H18

H19

H20

H21

H22

H23

H24

H25

H26

H27

J7

VSS#J4J4VSS#J7

VSS#K2

VSS#AM27

VSS#AM28

VSS#AM4

AM4

AM28

H28

H9

VSS#H3H3VSS#H6H6VSS#H7H7VSS#H8H8VSS#H9

VSS#AN1

VSS#AN10

VSS#AN13

VSS#AN16

AN1

AN10

AN13

AN16

VSS#H24

VSS#H25

VSS#H26

VSS#H27

VSS#H28

VSS#AN17

VSS#AN2

VSS#AN20

VSS#AN23

VSS#AN24

VSS#AN27

AN2

AN17

AN20

AN23

AN24

AN27

VSS#H14

VSS#H13

VSS#H17

VSS#H18

VSS#H19

VSS#H20

VSS#H21

VSS#H22

VSS#H23

VSS#H12

VSS#H11

VSS#H10

VSS#G1

VSS#F7

VSS#F4

VSS#F22

VSS#F19

VSS#F16

VSS#F13

VSS#F10

VSS#E8

VSS#E29

VSS#E28

VSS#E27

VSS#E26

VSS#E25

VSS#E20

VSS#E2

VSS#E17

VSS#E14

VSS#E11

VSS#D9

VSS#D6

VSS#D5

VSS#D3

VSS#D24

VSS#D21

VSS#D18

VSS#D15

VSS#D12

VSS#C7

VSS#C4

VSS#C24

VSS#C22

VSS#C19

VSS#C16

VSS#C13

VSS#C10

VSS#B8

VSS#B5

VSS#B24

VSS#B20

VSS#B17

VSS#AN28

VSS#B1B1VSS#B11

VSS#B14

ZIF-SOCK775-15u-in

B11

B14

AN28

H14

H13

H12

H11

H10

G1

F7

F4

F22

F19

F16

F13

F10

E8

E29

E28

E27

E26

E25

E20

E2

E17

E14

E11

D9

D6

D5

D3

D24

D21

D18

D15

D12

C7

C4

C24

C22

C19

C16

C13

C10

B8

B5

B24

B20

B17

2

R571 51R/2

TP_CPU_E29

1

TP_CPU_G1 3

VTT_OUT_LEFT 3,4

TP17

1

TP1

CPU DECOUPLING CAPACITORS

VCCP VCCP

EC23

C22U6.3X5R6

EC25

A A

C22U6.3X5R6

EC35

C22U6.3X5R6

VCCP

EC24

X_C10U10X6

EC20

C22U6.3X5R6

EC34

X_C10U10X6

EC22

C22U6.3X5R6

EC30

C22U6.3X5R6

EC33

C22U6.3X5R6

VCCP

EC21

X_C10U10X6

EC31

X_C10U10X6

EC32

C22U6.3X5R6

MICRO-STAR INT'L CO.,LTD

Place these caps within socket cavity

8

7

6

5

4

3

MSI

Size Document Description Rev

Custom

Friday, July 07, 2006

2

MS-7315

LGA775 - GND

Sheet ofDate:

535

1

0.A

8

7

6

5

4

3

2

1

V_1P25_CORE

V_FSB_VTT3,4,12,16,17,27

P29

P27

P26

P24

P23

N29

N26

N24

N23

M29

M24

M23

L24

L23

K24

K23

J24

J23

H24

H23

G26

G24

G23

F26

F24

F23

E29

E27

E26

E23

D29

D28

D27

C30

C29

C27

B30

B29

B28

B27

A30

A28

R27

R26

R24

R23

AG19

AG18

AG17

AG15

AG14

AF26

AF25

AF24

AF22

AF20

AF18

AF17

AF15

AF14

AE27

AE26

AE25

AE23

AE21

AE19

AE17

AD27

AD26

AD18

AD17

AD15

AD14

AC27

AC26

AC17

AC15

AC14

AB27

AB26

AB18

AB17

AA27

AA26

VCC_116

VCC_117

VCC_118

VCC_119

VCC_120

VCC_121

VCC_122

HDINV#0

HDINV#1

HDINV#2

HDINV#3

HDSTBP0#

HDSTBN0#

HDSTBP1#

HDSTBN1#

HDSTBP2#

HDSTBN2#

HDSTBP3#

HDSTBN3#

VCC_79

VCC_81

VCC_82

VCC_83

Broadwater-P

P20

Y11

AG25

AG21

AG20

HD0

HD1

HD2

HD3

HD4

HD5

HD6

HD7

HD8

HD9

HD10

HD11

HD12

HD13

HD14

HD15

HD16

HD17

HD18

HD19

HD20

HD21

HD22

HD23

HD24

HD25

HD26

HD27

HD28

HD29

HD30

HD31

HD32

HD33

HD34

HD35

HD36

HD37

HD38

HD39

HD40

HD41

HD42

HD43

HD44

HD45

HD46

HD47

HD48

HD49

HD50

HD51

HD52

HD53

HD54

HD55

HD56

HD57

HD58

HD59

HD60

HD61

HD62

HD63

R40

P41

R41

N40

R42

M39

N41

N42

L41

J39

L42

J41

K41

G40

F41

F42

C42

D41

F38

G37

E42

E39

E37

C39

B39

G33

A37

F33

E35

K32

H32

B34

J31

F32

M31

E31

K31

G31

K29

F31

J29

F29

L27

K27

H26

L26

J26

M26

C33

C35

E41

B41

D42

C40

D35

B40

C38

D37

B33

D33

C34

B35

A32

D32

M40

J33

G29

E33

L40

M43

G35

H33

G27

H27

B38

D38

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

H_DSTBP#0 3

H_DSTBN#0 3

H_DSTBP#1 3

H_DSTBN#1 3

H_DSTBP#2 3

H_DSTBN#2 3

H_DSTBP#3 3

H_DSTBN#3 3

H_D#[0..63] 3

H_DBI#[0..3] 3

K42

N32

N34

M38

N37

M36

R34

N35

N38

U37

N39

R37

P42

R39

V36

R38

U36

U33

R35

V33

V35

Y34

V42

V38

Y36

Y38

Y39

AA37

M34

U34

G43

W40

Y40

W41

Y43

U42

V41

AA42

W42

G39

U40

U41

AA41

U39

R32

U32

AM17

C31

AM18

D23

C25

D25

B25

D24

B24

J42

L39

J40

L37

L36

F40

L35

L38

J37

T43

J13

U12A

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HA32#

HA33#

HA34#

HA35#

HADSTB0#

HADSTB1#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HADS#

HTRDY#

HDRDY#

HDEFER#

HITM#

HHIT#

HLOCK#

HBREQ0#

HBNR#

HBPRI#

HDBSY#

HRS0#

HRS1#

HRS2#

HCLKP

HCLKN

PWROK

HCPURST#

RSTIN#

ICH_SYNC#

HRCOMP

HSCOMP

HSCOMP#

HSWING

HDVREF

HAVREF

VTT_1

VTT_2

VCC_1

AJ12

VTT_3

VCC_2

AJ11

AJ10

VTT_4

VTT_5

VCC_3

VCC_4

AJ9

VTT_6

VCC_5

AJ8

VTT_7

VCC_6

AJ7

VTT_8

VCC_7

AJ6

AJ5

VTT_9

VTT_10

VCC_8

VCC_9

AJ4

VTT_11

VCC_10

AJ3

AJ2

VTT_12

VTT_13

VCC_11

VCC_12

AH4

AH2

VTT_14

VTT_15

VCC_13

VCC_14

AH1

VTT_16

VCC_15

AG13

AG12

VTT_17

VTT_18

VCC_16

VCC_17

AG11

AG10

VTT_19

VTT_20

VCC_18

VCC_19

AG9

AG8

VTT_21

VTT_22

VCC_20

VCC_21

AG7

VTT_23

VCC_22

AG6

AG5

VTT_24

VTT_25

VCC_23

VCC_24

AG4

AG3

VTT_26

VTT_27

VCC_25

VCC_26

AG2

AF13

VTT_28

VTT_29

VCC_27

VCC_28

AF12

VTT_30

VCC_29

AF11

AD24

VTT_31

VTT_32

VCC_30

VCC_31

AD22

AD20

VTT_33

VTT_34

VCC_32

VCC_80

AC25

VTT_35

VCC_34

AC23

AC21

VTT_36

VTT_37

VCC_35

VCC_36

AC19

AC13

VTT_38

VTT_39

VCC_37

VCC_38

AC6

VTT_40

VCC_39

AB24

AB22

VTT_41

VTT_42

VCC_40

VCC_41

AB20

AA25

VTT_43

VTT_44

VCC_42

VCC_43

AA23

VTT_45

VCC_44

AA21

AA19

VTT_46

VCC_45

VCC_46

AA13

AA3

VCC_84

VCC_85

VCC_86

VCC_87

VCC_88

VCC_89

VCC_90

VCC_91

VCC_93

VCC_94

VCC_95

VCC_96

VCC_97

VCC_98

VCC_99

VCC_100

VCC_101

VCC_102

VCC_103

VCC_104

VCC_105

VCC_106

VCC_107

VCC_108

VCC_109

VCC_110

VCC_111

VCC_112

VCC_113

VCC_114

VCC_115

VCC_47

VCC_48

VCC_49

VCC_50

VCC_51

VCC_52Y6VCC_53

VCC_54

VCC_55

VCC_56V9VCC_57

VCC_58

VCC_59U9VCC_60U6VCC_61U3VCC_62

VCC_63

VCC_64N9VCC_65N8VCC_66N6VCC_67N3VCC_68L6VCC_69J6VCC_70J3VCC_71J2VCC_72G2VCC_73

Y24

Y22

Y20

Y13

V13

V12

V10

U13

U10

N12

N11

F11

VCC_74F9VCC_75D4VCC_76

C13

VCC_77C9VCC_78

PWRGD11,27

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

HXRCOMP

HXSCOMP

HXSCOMPB

HXSWING

H_A#[3..35]3

D D

H_ADSTB#03

C C

H_ADSTB#13

H_REQ#[0..4]3

H_ADS#3

H_TRDY#3

H_DRDY#3

H_DEFER#3

H_HITM#3

H_HIT#3

H_LOCK#3

H_BR#03,4

H_BNR#3

H_BPRI#3

H_DBSY#3

H_RS#[0..2]3

CK_H_MCH16

CK_H_MCH#16

H_CPURST#3,4

B B

PLTRST#10,27

ICH_SYNC#11

R189 16.5R1%/2

MCH_GTLREF

V_1P25_CORE

V_FSB_VTT

HXSWING SHOULD BE 1/4*VTT

V_FSB_VTT

A A

V_FSB_VTT

R182 49.9R1%/2

R183 49.9R1%/2

8

C179

X_C2.7P25N2

C177

X_C2.7P25N2

HXSCOMP

HXSCOMPB

V_FSB_VTT

R181

300R1%/2

R184 49.9R1%/2

R180

100R1%/2

7

6

C175

C103P25X2

HXSWING

V_FSB_VTT

5

*GTLREF VOLTAGE SHOULD BE

0.63*VTT=0.756V

R187

124R1%/2

CPU_MCH_GTLREF

R188 51R/2

R186

210R1%/2

C180

C1U16Y3

4

CPU_MCH_GTLREF 3

MCH_GTLREF

C186

C220P50N2

C171

X_C0.1U16Y2

C176

C1U16Y3

C172

C0.1U16Y2

MICRO-STAR INT'L CO.,LTD

MSI

Size Document Description Rev

Custom

Date:

3

Friday, July 07, 2006

2

MS-7315

Broadwater - CPU

635

Sheet of

1

0.A

8

7

6

5

4

3

2

1

SCKE_B[0..3]14,15

DQM_B[0..7]14

DATA_B[0..63]14

DQM_B7

DQM_B4

DQM_B2

DQM_B5

DQM_B0

DQM_B3

DQM_B1

DQM_B6

SCKE_B2

SCKE_B0

SCKE_B3

DATA_B13

DATA_B14

DATA_B12

AR11

AU9

SDQ_B11

SDQ_B12

SDQ_B13

SDQ_A11

SDQ_A12

SDQ_A13

AW2

AW3

DATA_B16

DATA_B15

AV12

AU12

SDQ_B14

SDQ_B15

SDQ_A14

SDQ_A15

BA5

BB4

DATA_B17

AU15

AV13

SDQ_B16

SDQ_B17

SDQ_A16

SDQ_A17

AY7

BC7

DATA_B18

DATA_B19

AU17

AT17

SDQ_B18

SDQ_A18

AY11

AW11

DATA_B22

DATA_B20

DATA_B21

AU13

AM13

SDQ_B19

SDQ_B20

SDQ_B21

SDQ_A19

SDQ_A20

SDQ_A21

BB6

BA6

DATA_B23

AV15

AW17

SDQ_B22

SDQ_B23

SDQ_A22

SDQ_A23

BA10

BB10

DATA_B24

DATA_B25

AV24

AT23

SDQ_B24

SDQ_B25

SDQ_A24

SDQ_A25

AT18

AR18

DATA_B26

DATA_B27

AT26

AP26

SDQ_B26

SDQ_A26

AT21

AU21

DATA_B28

DATA_B30

DATA_B29

AU23

AW23

SDQ_B27

SDQ_B28

SDQ_B29

SDQ_A27

SDQ_A28

SDQ_A29

AP17

AN17

DATA_B31

DATA_B32

AR24

AN26

SDQ_B30

SDQ_B31

SDQ_A30

SDQ_A31

AP20

AV20

DATA_B34

DATA_B33

AW37

AV38

AN36

SDQ_B32

SDQ_B33

SDQ_A32

SDQ_A33

AV42

AP42

AU40

DATA_B35

DATA_B36

AN37

AU35

SDQ_B34

SDQ_B35

SDQ_B36

SDQ_A34

SDQ_A35

SDQ_A36

AV40

AN39

DATA_B38

DATA_B37

AR35

AN35

SDQ_B37

SDQ_B38

SDQ_A37

SDQ_A38

AV41

AR42

DATA_B40

DATA_B39

AR37

AM35

SDQ_B39

SDQ_A39

AP41

AN41

DATA_B43

DATA_B42

DATA_B41

AM38

AJ34

SDQ_B40

SDQ_B41

SDQ_B42

SDQ_A40

SDQ_A41

SDQ_A42

AK42

AM39

DATA_B44

DATA_B45

AL38

AR39

SDQ_B43

SDQ_B44

SDQ_A43

SDQ_A44

AK41

AN40

DATA_B47

DATA_B46

AM34

AL37

SDQ_B45

SDQ_B46

SDQ_A45

SDQ_A46

AL42

AN42

DATA_B48

DATA_B49

AL32

AG38

AJ38

SDQ_B47

SDQ_B48

SDQ_A47

SDQ_A48

AJ40

AL39

AH43

DATA_B51

DATA_B52

DATA_B50

AF35

AF33

SDQ_B49

SDQ_B50

SDQ_B51

SDQ_A49

SDQ_A50

SDQ_A51

AF39

AE40

DATA_B53

DATA_B54

AJ37

AJ35

AG33

SDQ_B52

SDQ_B53

SDQ_A52

SDQ_A53

AJ42

AJ41

AF41

DATA_B55

DATA_B56

AF34

AD36

SDQ_B54

SDQ_B55

SDQ_B56

SDQ_A54

SDQ_A55

SDQ_A56

AF42

AD40

DATA_B58

DATA_B57

AC33

AA34

SDQ_B57

SDQ_B58

SDQ_A57

SDQ_A58

AB41

AD43

DATA_B59

AA36

AA40

DATA_B8

DATA_B4

DATA_B1

DATA_B3

DATA_B6

DATA_B0

AN7

AN8

SDQ_B0

SDQ_A0

AR5

AR4

DATA_B2

AW5

AW7

SDQ_B1

SDQ_B2

SDQ_A1

SDQ_A2

AV3

AV2

AN5

SDQ_B3

SDQ_A3

AP3

D D

SCS_A#[0..3]13,15

RAS_A#13,15

CAS_A#13,15

WE_A#13,15

MAA_A[0..14]13,15

C C

ODT_A[0..3]13,15

SBS_A[0..2]13,15

DQS_A013

DQS_A#013

DQS_A113

DQS_A#113

DQS_A213

DQS_A#213

DQS_A313

DQS_A#313

DQS_A413

DQS_A#413

DQS_A513

DQS_A#513

DQS_A613

DQS_A#613

DQS_A713

DQS_A#713

P_DDR0_A13

N_DDR0_A13

P_DDR1_A13

N_DDR1_A13

P_DDR2_A13

B B

VCC_DDR

C152

C0.1U16Y2

N_DDR2_A13

P_DDR3_A13

N_DDR3_A13

P_DDR4_A13

N_DDR4_A13

P_DDR5_A13

N_DDR5_A13

R258 20R1%/2

R264 20R1%/2

R167 20R1%/2 R268 1KR1%/2

R164 20R1%/2

SCS_A#0

SCS_A#1

SCS_A#2

SCS_A#3

RAS_A#

CAS_A#

WE_A#

MAA_A0

MAA_A1

MAA_A2

MAA_A3

MAA_A4

MAA_A5

MAA_A6

MAA_A7

MAA_A8

MAA_A9

MAA_A10

MAA_A11

MAA_A12

MAA_A13

MAA_A14

ODT_A0

ODT_A1

ODT_A2

ODT_A3

SBS_A0

SBS_A1

SBS_A2

DQS_A0

DQS_A#0

DQS_A1

DQS_A#1

DQS_A2

DQS_A#2

DQS_A3

DQS_A#3

DQS_A4

DQS_A#4

DQS_A5

DQS_A#5

DQS_A6

DQS_A#6

DQS_A7

DQS_A#7

P_DDR0_A

N_DDR0_A

P_DDR1_A

N_DDR1_A

P_DDR2_A

N_DDR2_A

P_DDR3_A

N_DDR3_A

P_DDR4_A

N_DDR4_A

P_DDR5_A

N_DDR5_A

SRCOMP0

SRCOMP1

SRCOMP2

SRCOMP3

AW35

BA35

BA34

BB38

BB33

AY35

BB34

BA31

BB25

BA26

BA25

AY25

BA23

AY24

AY23

BB23

BA22

AY33

BB22

AW21

AY38

BA21

AY37

BA38

BB35

BA39

BA33

AW32

BB21

AT20

AU18

AR41

AR40

AL41

AL40

AG42

AG41

AC42

AC41

AU31

AR31

AP27

AN27

AV33

AW33

AP29

AP31

AM26

AM27

AT33

AU33

BB40

BA40

AU4

AR3

BB3

BA4

BB9

BA9

AN2

AN3

U12B

SCS_A0#

SCS_A1#

SCS_A2#

SCS_A3#

SRAS_A#

SCAS_A#

SWE_A#

SMA_A0

SMA_A1

SMA_A2

SMA_A3

SMA_A4

SMA_A5

SMA_A6

SMA_A7

SMA_A8

SMA_A9

SMA_A10

SMA_A11

SMA_A12

SMA_A13

SMA_A14

SODT_A0

SODT_A1

SODT_A2

SODT_A3

SBS_A0

SBS_A1

SBS_A2

SDQS_A0

SDQS_A0#

SDQS_A1

SDQS_A1#

SDQS_A2

SDQS_A2#

SDQS_A3

SDQS_A3#

SDQS_A4

SDQS_A4#

SDQS_A5

SDQS_A5#

SDQS_A6

SDQS_A6#

SDQS_A7

SDQS_A7#

SCLK_A0

SCLK_A0#

SCLK_A1

SCLK_A1#

SCLK_A2

SCLK_A2#

SCLK_A3

SCLK_A3#

SCLK_A4

SCLK_A4#

SCLK_A5

SCLK_A5#

SRCOMP0

SRCOMP1

SRCOMP2

SRCOMP3

DATA_B5

AN6

AN9

SDQ_B4

SDQ_B5

SDQ_A4

SDQ_A5

AP2

AU1

DATA_B7

AU7

AT11

SDQ_B6

SDQ_B7

SDQ_A6

SDQ_A7

AV4

AY2

DATA_B9

DATA_B10

AP13

AU11

SDQ_B8

SDQ_B9

SDQ_A8

SDQ_A9

AY3

BB5

DATA_B11

AR13

SDQ_B10

SDQ_A10

AY6

DATA_B60

DATA_B61

AD34

AF38

SDQ_B59

SDQ_B60

SDQ_B61

SDQ_A59

SDQ_A60

SDQ_A61

AE42

AE41

DATA_B63

DATA_B62

AC34

AA33

SDQ_B62

SDQ_B63

SDQ_A62

SDQ_A63

AB42

AC39

SCKE_B1

AY12

AW12

SCKE_B0

SCKE_B1

SCKE_A0

SCKE_A1

AY20

BC20

BB11

BA11

SCKE_B2

SCKE_B3

SCKE_A2

SCKE_A3

AY21

BA19

AR7

AW9

SDM_B0

SDM_B1

SDM_A0

SDM_A1

BA2

AR2

AW13

AP23

SDM_B2

SDM_A2

AY9

AN18

AU37

AM37

SDM_B3

SDM_B4

SDM_A3

SDM_A4

AU43

AM43

AG39

AD38

SDM_B5

SDM_B6

SDM_A5

SDM_A6

AC40

AG40

SDM_B7

SDM_A7

SCS_B0#

SCS_B1#

SCS_B2#

SCS_B3#

SRAS_B#

SCAS_B#

SWE_B#

SMA_B0

SMA_B1

SMA_B2

SMA_B3

SMA_B4

SMA_B5

SMA_B6

SMA_B7

SMA_B8

SMA_B9

SMA_B10

SMA_B11

SMA_B12

SMA_B13

SMA_B14

SODT_B0

SODT_B1

SODT_B2

SODT_B3

SBS_B0

SBS_B1

SBS_B2

SDQS_B0

SDQS_B0#

SDQS_B1

SDQS_B1#

SDQS_B2

SDQS_B2#

SDQS_B3

SDQS_B3#

SDQS_B4

SDQS_B4#

SDQS_B5

SDQS_B5#

SDQS_B6

SDQS_B6#

SDQS_B7

SDQS_B7#

SCLK_B0

SCLK_B0#

SCLK_B1

SCLK_B1#

SCLK_B2

SCLK_B2#

SCLK_B3

SCLK_B3#

SCLK_B4

SCLK_B4#

SCLK_B5

SCLK_B5#

SVREF

SMRCOMPVOL

SMRCOMPVOH

Broadwater-P

BB27

BB30

AY27

AY31

AW26

AW29

BA27

BB17

AY17

BA17

BC16

AW15

BA15

BB15

BA14

AY15

BB14

AW18

BB13

BA13

AY29

AY13

BA29

BA30

BB29

BB31

AY19

BA18

BC12

AV6

AU5

AR12

AP12

AP15

AR15

AT24

AU26

AW39

AU39

AL35

AL34

AG35

AG36

AC36

AC37

AV31

AW31

AU27

AT27

AV32

AT32

AU29

AR29

AV29

AW27

AN33

AP32

AM6

AM8

AM10

SCS_B#0

SCS_B#1

SCS_B#2

SCS_B#3

RAS_B#

CAS_B#

WE_B#

MAA_B0

MAA_B1

MAA_B2

MAA_B3

MAA_B4

MAA_B5

MAA_B6

MAA_B7

MAA_B8

MAA_B9

MAA_B10

MAA_B11

MAA_B12

MAA_B13

MAA_B14

ODT_B0

ODT_B1

ODT_B2

ODT_B3

SBS_B0

SBS_B1

SBS_B2

DQS_B0

DQS_B#0

DQS_B1

DQS_B#1

DQS_B2

DQS_B#2

DQS_B3

DQS_B#3

DQS_B4

DQS_B#4

DQS_B5

DQS_B#5

DQS_B6

DQS_B#6

DQS_B7

DQS_B#7

P_DDR0_B

N_DDR0_B

P_DDR1_B

N_DDR1_B

P_DDR2_B

N_DDR2_B

P_DDR3_B

N_DDR3_B

P_DDR4_B

N_DDR4_B

P_DDR5_B

N_DDR5_B

MCH_VREF_A

C280

C103P25X2

SCS_B#[0..3] 14,15

RAS_B# 14,15

CAS_B# 14,15

WE_B# 14,15

MAA_B[0..14] 14,15

ODT_B[0..3] 14,15

SBS_B[0..2] 14,15

DQS_B0 14

DQS_B#0 14

DQS_B1 14

DQS_B#1 14

DQS_B2 14

DQS_B#2 14

DQS_B3 14

DQS_B#3 14

DQS_B4 14

DQS_B#4 14

DQS_B5 14

DQS_B#5 14

DQS_B6 14

DQS_B#6 14

DQS_B7 14

DQS_B#7 14

P_DDR0_B 14

N_DDR0_B 14

P_DDR1_B 14

N_DDR1_B 14

P_DDR2_B 14

N_DDR2_B 14

P_DDR3_B 14

N_DDR3_B 14

P_DDR4_B 14

N_DDR4_B 14

P_DDR5_B 14

N_DDR5_B 14

DDR_RCOMPVOL

R272

3.01KR1%/2

DDR_RCOMPVOH

C279

C103P25X2

DDR_RCOMPVOL = 0.2 * VCC_DDR

DDR_RCOMPVOH = 0.8 * VCC_DDR

R271 1KR1%/2

VCC_DDR

C653

C0.1U16Y2

DQM_A1

SCKE_A0

SCKE_A1

DATA_A8

DATA_A4

DATA_A1

DATA_A2

DATA_A0

DATA_A[0..63]13

DATA_A3

DATA_A10

DATA_A5

DATA_A12

DATA_A7

DATA_A6

DATA_A13

DATA_A9

DATA_A11

DATA_A20

DATA_A17

DATA_A15

DATA_A18

DATA_A14

DATA_A16

DATA_A25

DATA_A26

DATA_A24

DATA_A22

DATA_A19

DATA_A21

DATA_A23

DATA_A31

DATA_A29

DATA_A33

DATA_A27

DATA_A28

DATA_A34

DATA_A32

DATA_A30

DATA_A41

DATA_A45

DATA_A46

DATA_A44

DATA_A43

DATA_A39

DATA_A36

DATA_A38

DATA_A42

DATA_A37

DATA_A40

DATA_A35

DATA_A53

DATA_A51

DATA_A48

DATA_A47

DATA_A49

DATA_A50

DATA_A58

DATA_A52

DATA_A59

DATA_A57

DATA_A55

DATA_A60

DATA_A56

DATA_A54

SCKE_A2

DATA_A61

DATA_A63

DATA_A62

SCKE_A[0..3]13,15

A A

DQM_A[0..7]13

DQM_A4

DQM_A2

DQM_A6

DQM_A0

SCKE_A3

DQM_A3

DQM_A7

DQM_A5

VCC_DDR

R273 1KR1%/2

R274

1KR1%/2

MCH_VREF_A

C286

C0.1U16Y2

PLACE 0.1UF CAP

CLOSE TO MCH

6/23 UPDATE

MICRO-STAR INT'L CO.,LTD

MSI

Size Document Description Rev

Custom

Date:

8

7

6

5

4

3

2

Friday, July 07, 2006

MS-7315

Broadwater - Memory

Sheet of

735

1

0.A

8

EXP_A_TXP_[0..15] 22

EXP_A_TXN_[0..15] 22

EXP_A_RXP_[0..15] 22

EXP_A_RXN_[0..15] 22

EXP_A_RXP_022

EXP_A_RXN_022

EXP_A_RXP_122

D D

C C

EXP_A_RXN_122

EXP_A_RXP_222

EXP_A_RXN_222

EXP_A_RXP_322

EXP_A_RXN_322

EXP_A_RXP_422

EXP_A_RXN_422

EXP_A_RXP_522

EXP_A_RXN_522

EXP_A_RXP_622

EXP_A_RXN_622

EXP_A_RXP_722

EXP_A_RXN_722

EXP_A_RXP_822

EXP_A_RXP_922

EXP_A_RXN_922

EXP_A_RXP_1022

EXP_A_RXN_1022

EXP_A_RXP_1122

EXP_A_RXN_1122

EXP_A_RXP_1222

EXP_A_RXN_1222

EXP_A_RXP_1322

EXP_A_RXN_1322

EXP_A_RXP_1422

EXP_A_RXN_1422

EXP_A_RXP_1522

DMI_ITP_MRP_010

DMI_ITN_MRN_010

DMI_ITP_MRP_110

DMI_ITN_MRN_110

DMI_ITP_MRP_210

DMI_ITN_MRN_210

DMI_ITP_MRP_310

DMI_ITN_MRN_310

CK_PE_100M_MCH16

CK_PE_100M_MCH#16

6/23 UPDATE

V_1P25_CORE

EXP_PRSNT_N22

V_1P25_CORE

B B

V_1P25_CORE

A A

R219 1KR1%/2

R220 X_1KR1%/2

R232 0R/2

R197 0R/2

6/23 UPDATE

X_L10U_100mA_0805

V_1P25_CORE

8

X_COPPER

EXP_A_RXP_0

EXP_A_RXN_0

EXP_A_RXP_1

EXP_A_RXN_1

EXP_A_RXP_2

EXP_A_RXN_2

EXP_A_RXP_3

EXP_A_RXN_3

EXP_A_RXP_4

EXP_A_RXN_4

EXP_A_RXP_5

EXP_A_RXN_5

EXP_A_RXP_6

EXP_A_RXN_6

EXP_A_RXP_7

EXP_A_RXN_7

EXP_A_RXP_8

EXP_A_RXN_8

EXP_A_RXP_9

EXP_A_RXN_9

EXP_A_RXP_10

EXP_A_RXN_10

EXP_A_RXP_11

EXP_A_RXN_11

EXP_A_RXP_12

EXP_A_RXN_12

EXP_A_RXP_13

EXP_A_RXN_13

EXP_A_RXP_14

EXP_A_RXN_14

EXP_A_RXP_15

EXP_A_RXN_15

DMI_ITP_MRP_0 DMI_MTP_IRP_0

DMI_ITN_MRN_0

DMI_ITP_MRP_1

DMI_ITN_MRN_2

DMI_ITP_MRP_3

DMI_ITN_MRN_3

CK_PE_100M_MCH

CK_PE_100M_MCH#

H_BSL0

H_BSL016

H_BSL1

H_BSL116

H_BSL2

H_BSL216

EXP_SLR

EXP_EN

VCC_CL_PLL

VCCA_HPLLVCCA_HPLL

VCCA_MPLL

VCCA_DPLLA

VCCA_DPLLB

VCCA_GPLL

VCCA_EXP

VCC3

L7

CP9

X_L10U_100mA_0805

X_COPPER

VCCA_MPLL

L8

CP10

R610 1R1%/3

R611 1R1%/3

U12C

F15

EXP_RXP0

G15

EXP_RXN0

K15

EXP_RXP1

J15

EXP_RXN1

F12

EXP_RXP2

E12

EXP_RXN2

J12

EXP_RXP3

H12

EXP_RXN3

J11

EXP_RXP4

H11

EXP_RXN4

F7

EXP_RXP5

E7

EXP_RXN5

E5

EXP_RXP6

F6

EXP_RXN6

C2

EXP_RXP7

D2

EXP_RXN7

G6

EXP_RXP8

G5

EXP_RXN8

L9

EXP_RXP9

L8

EXP_RXN9

M8

EXP_RXP10

M9

EXP_RXN10

M4

EXP_RXP11

L4

EXP_RXN11

M5

EXP_RXP12

M6

EXP_RXN12

R9

EXP_RXP13

R10

EXP_RXN13

T4

EXP_RXP14

R4

EXP_RXN14

R6

EXP_RXP15

R7

EXP_RXN15

W2

DMI_RXP0

V1

DMI_RXN0

Y8

DMI_RXP1

Y9

DMI_RXN1

AA7

DMI_RXP2

AA6

DMI_RXN2

AB3

DMI_RXP3

AA4

DMI_RXN3

B12

GCLKP

B13

GCLKN

G17

SDV0_CTRLDATA

E17

SDVO_CTRLCLK

G20

BSEL0

J20

BSEL1

J18

BSEL2

G18

MTYPE

E18

EXP_SLR

J17

EXP_EN

Y32

VCC_CL_PLL

C23

VCCA_HPLL

A24

VCCA_MPLL

A22

VCCA_DPLLA

C22

VCCA_DPLLB

B15

VCCA_EXPPLL

C17

VCCA_DAC_17

B16

VCCA_DAC_18

A16

VCCA_EXP_19

C21

VCCD_CRT_20

B21

VCCDQ_CRT_21

D16

VSS_1

B17

VCC33

V_1P25_CORE

VCCA_HPLL

C207

X_C10U10Y5

7

C188

C10U10Y5

7

V_1P25_CORE

AL26

AL24

AL23

VCC_CL_1

VCC_CL_2

VCC_EXP_1

VCC_EXP_2

VCC_EXP_3

AD9

AD8

AD11

AD10

C187

C0.1U16Y2

C197

C0.1U16Y2

AL21

AL20

VCC_CL_3

VCC_CL_4

VCC_CL_5

VCC_EXP_4

VCC_EXP_5

VCC_EXP_6

AD7

AD6

AL18

AL17

AL15

VCC_CL_6

VCC_CL_7

VCC_CL_8

VCC_EXP_7

VCC_EXP_8

VCC_EXP_9

AD5

AD4

AD2

V_1P25_CORE

V_1P25_CORE

AK29

AK30

VCC_CL_9

VCC_CL_10

VCC_EXP_10

VCC_EXP_11

AD1

AC4

VCC_DDR

AK27

AJ31

AG31

VCC_CL_11

VCC_CL_12

VCC_EXP_12

VCC_EXP_13

AE4

AC3

AC2

AF31

AD32

VCC_CL_13

VCC_CL_14

VCC_CL_15

VCC_EXP_14

VCC_EXP_15

VCC_EXP_16

AE3

AE2

AC32

AA32

AJ30

AJ29

AJ27

AG30

VCC_CL_16

VCC_CL_17

VCC_CL_18

VCC_CL_19

VCC_CL_20

VCCSM_1

VCCSM_2

VCCSM_3

VCCSM_4

BC39

BC34

BC30

BC26

BC22

L9

X_L10U_100mA_0805

CP11

X_COPPER

L10

X_L10U_100mA_0805

CP12

X_COPPER

6

AG29

AG27

VCC_CL_21

VCC_CL_22

VCC_CL_23

VCCSM_5

VCCSM_6

VCCSM_7

BC18

BC14

6

AG26

AF30

VCC_CL_24

VCC_CL_25

VCCSM_8

VCCSM_9

BB39

BB37

AF29

AF27

VCC_CL_26

VCC_CL_27

VCCSM_10

VCCSM_11

BB32

BB28

AD30

AD29

AC30

VCC_CL_28

VCC_CL_29

VCCSM_12

VCCSM_13

BB26

BB24

BB20

VCCA_DPLLA

C201

X_C10U10Y5

VCCA_DPLLB

C217

X_C10U10Y5

AC29

AL12

VCC_CL_30

VCC_CL_31

VCC_CL_32

VCCSM_14

VCCSM_15

VCCSM_16

BB18

BB16

AL11

AL10

VCC_CL_33

VCC_CL_34

VCCSM_17

VCCSM_18

BB12

AY32

AL9

AL8

VCC_CL_35

VCC_CL_36

VCCSM_19

VCCSM_20

AW24

AW20

AL7

AL6

AL5

VCC_CL_37

VCC_CL_38

VCCSM_21

VCCSM_22

AV26

AV18

C157

C1U16Y3

C199

C0.1U16Y2

C202

C0.1U16Y2

AL4

AL3

VCC_CL_39

VCC_CL_40

VCC_CL_41

VCC_SMCLK_1

BB41

AL2

AK26

VCC_CL_42

VCC_CL_43

VCC_SMCLK_3

VCC_SMCLK_2

AY42

BA42

AK24

BB42

AK23

AK21

VCC_CL_44

VCC_CL_45

VCC_CL_46

VCC_SMCLK_5

VCC_SMCLK_4

BA43

V_CKDDR

R161 1R1%/2

R160 1R1%/2

V_1P25_CORE

5

AK20

AK18

AK17

AK15

AK3

AK2

AK1

AJ13

AD31

AC31

AA31

Y31

AJ26

AJ24

AJ23

AJ21

AJ20

AJ18

AJ17

AJ15

AJ14

VCC_CL_47

VCC_CL_48

VCC_CL_49

VCC_CL_50

VCC_CL_51

VCC_CL_52

VCC_CL_53

VCC_CL_54

VCC_CL_55

VCC_CL_56

VCC_CL_57

VCC_CL_58

VCC_CL_59

VCC_CL_60

VCC_CL_61

VCC_CL_62

VCC_CL_63

VCC_CL_64

VCC_CL_65

VCC_CL_66

VCC_CL_67

RESERVED_2

RESERVED_4

RESERVED_5

RESERVED_6

RESERVED_7

RESERVED_8

RESERVED_9

RESERVED_10

RESERVED_3

RESERVED_1

H18

BB19

AN21

L6 X_L10U_100mA_0805

5

RESERVED_11

RESERVED_12

RESERVED_13

RESERVED_14

RESERVED_15

RESERVED_16

RESERVED_17

RESERVED_18

RESERVED_19

RESERVED_20

Y12

U30

U31

R29

BB2

CP6 X_COPPER

CP7 X_COPPER

AJ32

AL31

AF32

AN32

AG32

AM31

AM21

AW42

C151 C10U10Y5 R267

L13

L10U_100mA_0805

L12

VCC3

L0.1U_50mA

X_C10U10Y5

AA9

AA10

C226

AA11

6/23 UPDATE

VCCA_EXP

R30

VCC_DDR

R237 1R1%/2

R238 1R1%/2

C0.1U16Y2

AA30

AA29

Y30

VCC_CL_68

VCC_CL_69

RESERVED_21

RESERVED_22

U12

U11

R12

C228

Y29

V30

V29

VCC_CL_70

VCC_CL_71

VCC_CL_72

VCC_CL_73

RESERVED_25

RESERVED_23

RESERVED_24

RESERVED_26

F13

R13

AP21

X_C10U10Y5

R498 1R1%/2

4

U29

U27

AL13

VCC_CL_74

VCC_CL_75

VCC_CL_76

RESERVED_28

RESERVED_27

V31

AA39

T8

VCCA_GPLL

C239

C227

C103P25X2

4

AK14

AL29

VCC_CL_77

VCC_CL_78

TEST2

BC43

T11

AL27

EXP_TXP0

EXP_TXN0

EXP_TXP1

EXP_TXN1

VCC_CL_79

EXP_TXP2

EXP_TXN2

EXP_TXP3

EXP_TXN3

EXP_TXP4

EXP_TXN4

EXP_TXP5

EXP_TXN5

EXP_TXP6

EXP_TXN6

EXP_TXP7

EXP_TXN7

EXP_TXP8

EXP_TXN8

EXP_TXP9

EXP_TXN9

EXP_TXP10

EXP_TXN10

EXP_TXP11

EXP_TXN11

EXP_TXP12

EXP_TXN12

EXP_TXP13

EXP_TXN13

EXP_TXP14

EXP_TXN14

EXP_TXP15

EXP_TXN15

DMI_TXP0

DMI_TXN0

DMI_TXP1

DMI_TXN1

DMI_TXP2

DMI_TXN2

DMI_TXP3

DMI_TXN3

EXP_COMPO

EXP_COMPI

DDC_DATA

DDC_CLK

DREFCLKP

DREFCLKN

CL_PWROK

CL_RST#

CL_VERF

CL_DATA

ALLZTEST

XORTEST

TEST1

TEST0

Broadwater-P

A43

BC1

T9

HSYNC

VSYNC

GREEN

BLUE

RED#

GREEN#

BLUE#

REFSET

CL_CLK

TESTIN#

C236

C0.1U16Y2

RED

D11

D12

B11

A10

C10

D9

B9

B7

D7

D6

B5

B6

B3

B4

F2

E2

F4

G4

J4

K3

L2

K1

N2

M2

P3

N4

R2

P1

U2

T2

V3

U4

V7

V6

W4

Y4

AC8

AC9

Y2

AA2

AC11

AC12

C15

D15

B18

C19

B20

C18

D19

D20

L13

M13

C14

D13

A20

AM15

AA12

AM5

AD13

AD12

K20

F20

A14

EXP_A_TXP_0

EXP_A_TXN_0

EXP_A_TXP_1

EXP_A_TXN_1

EXP_A_TXP_2

EXP_A_TXN_2

EXP_A_TXP_3

EXP_A_TXN_3

EXP_A_TXP_4

EXP_A_TXN_4

EXP_A_TXP_5

EXP_A_TXN_5

EXP_A_TXP_6

EXP_A_TXN_6

EXP_A_TXP_7

EXP_A_TXN_7

EXP_A_TXP_8

EXP_A_TXN_8

EXP_A_TXP_9

EXP_A_TXN_9

EXP_A_TXP_10

EXP_A_TXN_10

EXP_A_TXP_11

EXP_A_TXN_11

EXP_A_TXP_12

EXP_A_TXN_12

EXP_A_TXP_13

EXP_A_TXN_13

EXP_A_TXP_14

EXP_A_TXN_14

EXP_A_TXP_15

EXP_A_TXN_15

DMI_MTN_IRN_0

DMI_MTP_IRP_1

DMI_MTN_IRN_1DMI_ITN_MRN_1

DMI_MTP_IRP_2DMI_ITP_MRP_2

DMI_MTN_IRN_2

DMI_MTP_IRP_3

DMI_MTN_IRN_3

GRCOMP

R259 24.9R1%/2

VCC3

CK_96M_DREF

CK_96M_DREF#

DACREFSET

MCH_CLPWROK

CL_VREF_MCH

T10

R205 0R/2

V_1P25_CORE

3

EXP_A_TXP_0 22

EXP_A_TXN_0 22

EXP_A_TXP_1 22

EXP_A_TXN_1 22

EXP_A_TXP_2 22

EXP_A_TXN_2 22

EXP_A_TXP_3 22

EXP_A_TXN_3 22

EXP_A_TXP_4 22

EXP_A_TXN_4 22

EXP_A_TXP_5 22

EXP_A_TXN_5 22

EXP_A_TXP_6 22

EXP_A_TXN_6 22

EXP_A_TXP_7 22

EXP_A_TXN_7 22

EXP_A_TXP_8 22

EXP_A_TXN_8 22EXP_A_RXN_822

EXP_A_TXP_9 22

EXP_A_TXN_9 22

EXP_A_TXP_10 22

EXP_A_TXN_10 22

EXP_A_TXP_11 22

EXP_A_TXN_11 22

EXP_A_TXP_12 22

EXP_A_TXN_12 22

EXP_A_TXP_13 22

EXP_A_TXN_13 22

EXP_A_TXP_14 22

EXP_A_TXN_14 22

EXP_A_TXP_15 22

EXP_A_TXN_15 22EXP_A_RXN_1522

DMI_MTP_IRP_0 10

DMI_MTN_IRN_0 10

DMI_MTP_IRP_1 10

DMI_MTN_IRN_1 10

DMI_MTP_IRP_2 10

DMI_MTN_IRN_2 10

DMI_MTP_IRP_3 10

DMI_MTN_IRN_3 10

V_1P25_CORE

6/23 UPDATE

MCH_CLPWROK 11

CL_RST 11

CL_N_CLK 11

CL_N_DATA 11

CL_VREF_MCH = 0.349V

R266

1KR/2

CL_VREF_MCH

C278

392/2

C0.1U16Y2

6/23 UPDATE

3

2

Reserved for Non-Graphic

V_1P25_CORE

R234

CK_96M_DREF

CK_96M_DREF#

10KR/2

R497

0R/2

MSI

Size Document Description Rev

Custom

Date:

2

1

Place close to GMCH

VCC_DDR

C168 C2.2U6.3Y3

C229 X_C2.2U6.3Y3

C223 C2.2U6.3Y3

C215 C2.2U6.3Y3

C198 C2.2U6.3Y3

C185 C2.2U6.3Y3

MCH MEMORY DECOUPLING

V_1P25_CORE

C571 X_C10U10Y5/BACK

C573 X_C10U10Y5/BACK

C289 X_C10U10Y5

C288 X_C10U10Y5

C255 X_C10U10Y5

C273 C10U10Y5

C574 X_C10U10Y5/BACK

C275 C10U10Y5

C572 X_C10U10Y5/BACK

C570 X_C10U10Y5/BACK

C272 X_C10U10Y5

C281 C10U10Y5

C283 X_C10U10Y5

C276 C10U10Y5

C569 X_C10U10Y5/BACK

C274 X_C10U10Y5

C340 C0.1U16Y2

C252 C0.1U16Y2

C267 C0.1U16Y2

C285 X_C0.1U16Y2

C313 C0.1U16Y2

C284 C0.1U16Y2

C333 C0.1U16Y2

C322 X_C0.1U16Y2

C358 C0.1U16Y2

C354 X_C0.1U16Y2

C353 C0.1U16Y2

C341 X_C0.1U16Y2

MCH CORE DECOUPLING

1

U12_1

1

Broadwater_Hearsink

MICRO-STAR INT'L CO.,LTD

MS-7315

Friday, July 07, 2006

Broadwater - PCI Express

Sheet of

1

2

2

835

0.A

8

V_1P25_CORE

AA17

AA15

U12D

BC37

D D

C C

B B

BC32

BC28

BC24

BC10

BC5

AY41

AW43

AW41

AW1

AV37

AV35

AV27

AV23

AV21

AV17

AV11

AU42

AU38

AU32

AU24

AU20

AU6

AU2

AT31

AT29

AT15

AT13

AT12

AR38

AR33

AR32

AR27

AR26

AR23

AR21

AR20

AR17

AR9

AR6

AP43

AP24

AP18

AN38

AN31

AN29

AN24

AN23

AN20

AN15

AN13

AN12

AN11

AN4

AM42

AM40

AM36

AM33

AM29

AM24

AM23

AM20

AM11

AM9

AM7

AM4

AM2

AM1

AL36

AL33

AK43

BB7

AY4

AV9

AV7

AP1

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12

VSS_13

VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

VSS_63

VSS_64

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

VSS_75

VSS_76

AA14

VCC_123

VCC_124

VCC_125

Y27

Y26

VCC_126

Y18

Y17

VCC_127

VCC_128

Y15

Y14

VCC_129

VCC_130

7

W27

W26

VCC_131

VCC_132

W25

W23

VCC_133

VCC_134

W21

W19

VCC_135

VCC_136

W18

W17

VCC_137

VCC_138

V27

V26

VCC_139

VCC_140

V25

V24

VCC_141

VCC_142

V23

V22

VCC_143

VCC_144

V21

V20

VCC_145

VCC_146

V19

V18

VCC_147

VCC_148

6

V17

V15

VCC_149

VCC_150

V14

U26

VCC_151

VCC_152

U25

U24

VCC_153

VCC_154

U23

U22

VCC_155

VCC_156

U21

U20

VCC_157

VCC_158

U19

U18

VCC_159

VCC_160

U17

U15

VCC_161

VCC_162

U14

R20

VCC_163

VCC_164

R18

R17

VCC_165

VCC_166

R15

R14

VCC_167

VCC_168

5

P15

P14

VCC_169

VCC_170

AG24

AG23

VCC_171

VCC_172

AG22

VCC_173

VCC_174

4

M20

L15

L18

M18

F17

L17

N17

N18

N15

RESERVED_29

RESERVED_30

RESERVED_31

K17

N20

BC42

BC2

BB43

BB1

B43

B42

NC_1

NC_2

NC_3

NC_4

NC_5

NC_6

RESERVED_33

RESERVED_34

RESERVED_35

RESERVED_36

RESERVED_37

RESERVED_32

RESERVED_38

NC_7

A42

NC_8B2NC_9

M11

L12

VSS

VCC

A41

VSS_293A3VSS_292A5VSS_291

3

C43

VSS_290C1VSS_289

R21

W20

VSS_288E1VSS_287

VSS_286

W22

VSS_285

W24

VSS_284

AA18

VSS_283

AC18

VSS_282

AE18

VSS_281

2

M42

VSS_270

M35

VSS_269

M37

VSS_268

VSS_267

VSS_266N5VSS_265N7VSS_264

N10

VSS_263

VSS_262

VSS_261

VSS_260

VSS_259

VSS_258

VSS_257

VSS_256

VSS_255

VSS_254

VSS_253

VSS_252

VSS_251

VSS_250

VSS_249

VSS_248

VSS_247

VSS_246

VSS_245

VSS_244

VSS_243

VSS_242

VSS_241

VSS_240

VSS_239

VSS_238

VSS_237

VSS_236

VSS_235

VSS_234

VSS_233

VSS_232

VSS_231

VSS_230

VSS_229

VSS_228

VSS_227

VSS_226

VSS_225

VSS_224

VSS_223

VSS_222

VSS_221

VSS_220

VSS_219

VSS_218

VSS_217

VSS_216

VSS_215

VSS_214

VSS_213

VSS_212

VSS_211

VSS_210

VSS_209

VSS_208

VSS_207

VSS_206

VSS_205

VSS_204

VSS_203

VSS_202

VSS_201

VSS_200

VSS_199

VSS_198

VSS_197

VSS_196

VSS_195

VSS_194

VSS_193

VSS_192

VSS_191

VSS_190

VSS_189

VSS_188

N13

N21

N27

N31

N33

N36

P2

P17

P18

P21

P30

P43

R3

R5

R8

R11

R31

R33

R36

T1

T42

U5

U7

U8

U35

U38

V2

V5

V8

V11

V32

V34

V37

V39

V43

W3

Y1

Y5

Y7

Y10

Y19

Y21

Y23

Y25

Y33

Y35

Y37

Y42

AA5

AA8

AA20

AA22

AA24

AA35

AA38

AB1

AB2

AB19

AB21

AB23

AB25

AB43

AC5

AC7

AC10

AC20

AC22

AC24

AC35

AC38

AD19

AD21

AD23

AD25

AD33

AD35

AE20

AE22

AE24

AF19

AF21

AF23

AY40

BA1

BC3

BC41

M33

VSS_280

VSS_279

VSS_278

VSS_277

VSS_276

VSS_275

VSS_274

VSS_273

VSS_272

VSS_271

1

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96M7VSS_97M1VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105L7VSS_106L5VSS_107L3VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114K2VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120J9VSS_121J7VSS_122J5VSS_123

VSS_124

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137G9VSS_138G7VSS_139G1VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145F3VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154E9VSS_155E3VSS_156

VSS_157

VSS_158

VSS_159

VSS_160D3VSS_161

VSS_162

VSS_163C6VSS_164C5VSS_165C4VSS_166

VSS_167

VSS_168

VSS_169

VSS_170

VSS_171

VSS_172

VSS_173

VSS_174

VSS_175

VSS_176

VSS_177

VSS_178

VSS_179

VSS_180A7VSS_181

VSS_182

VSS_183

VSS_184

VSS_185

VSS_186

VSS_187

J38

J35