1

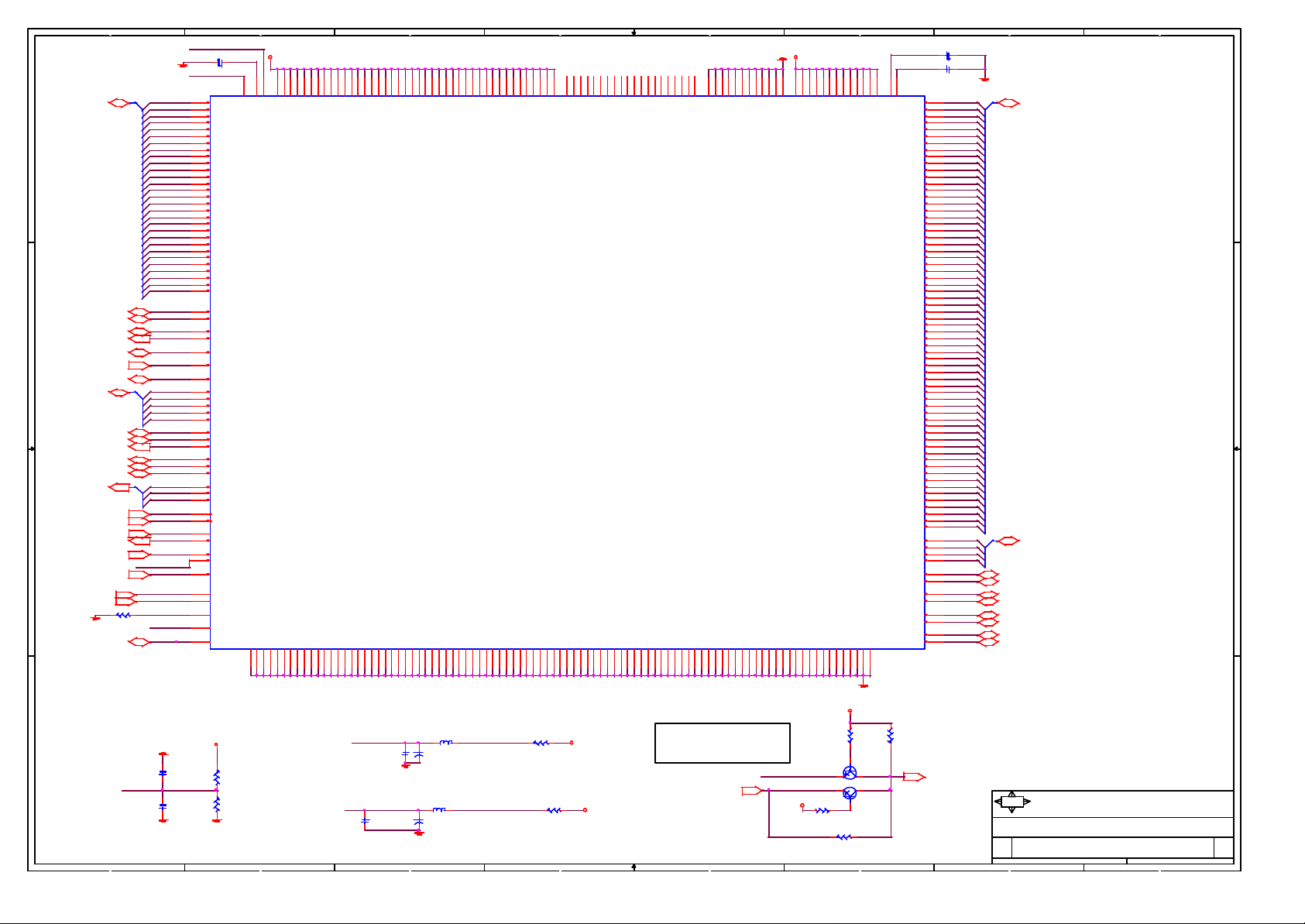

Cover Sheet 1

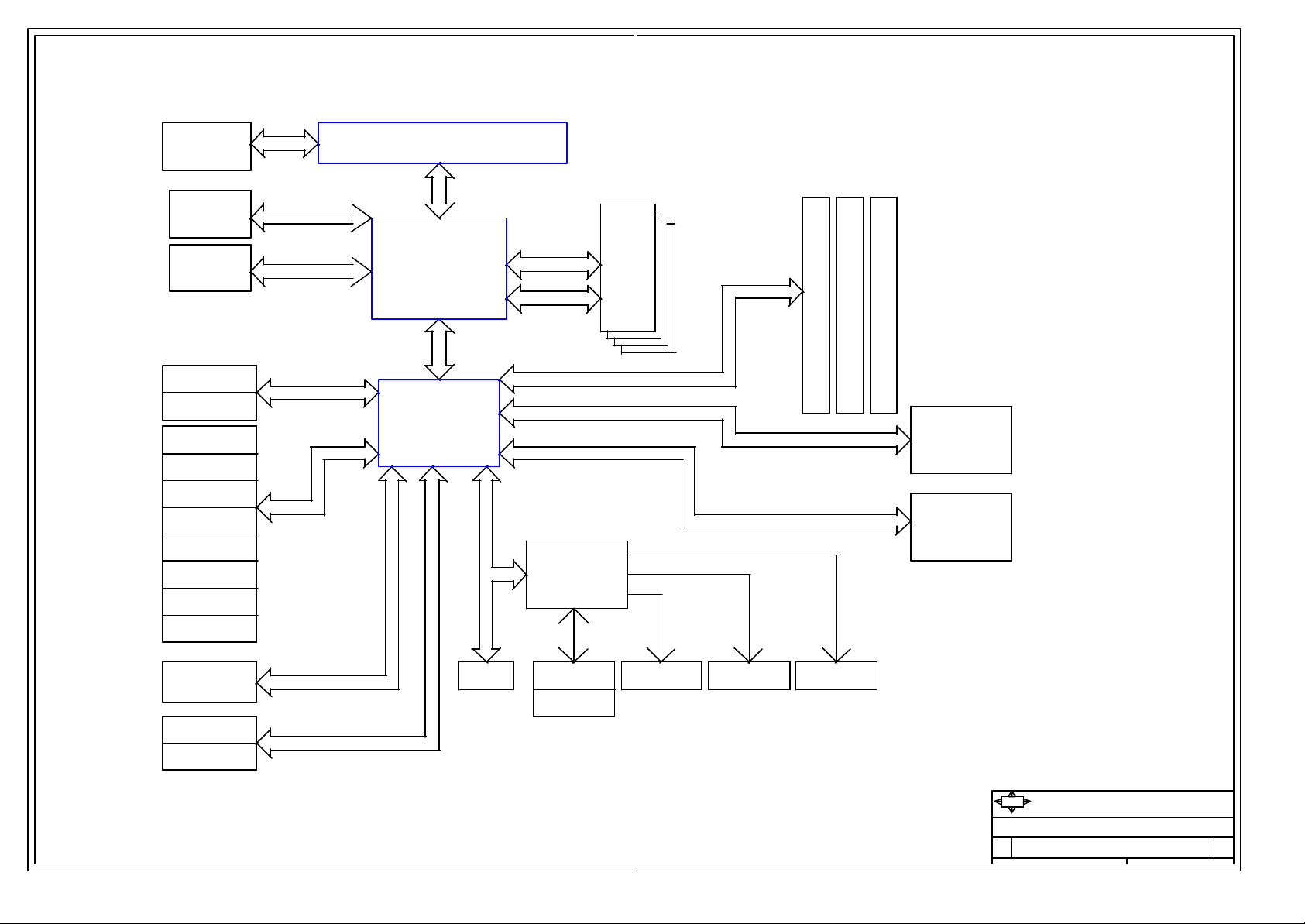

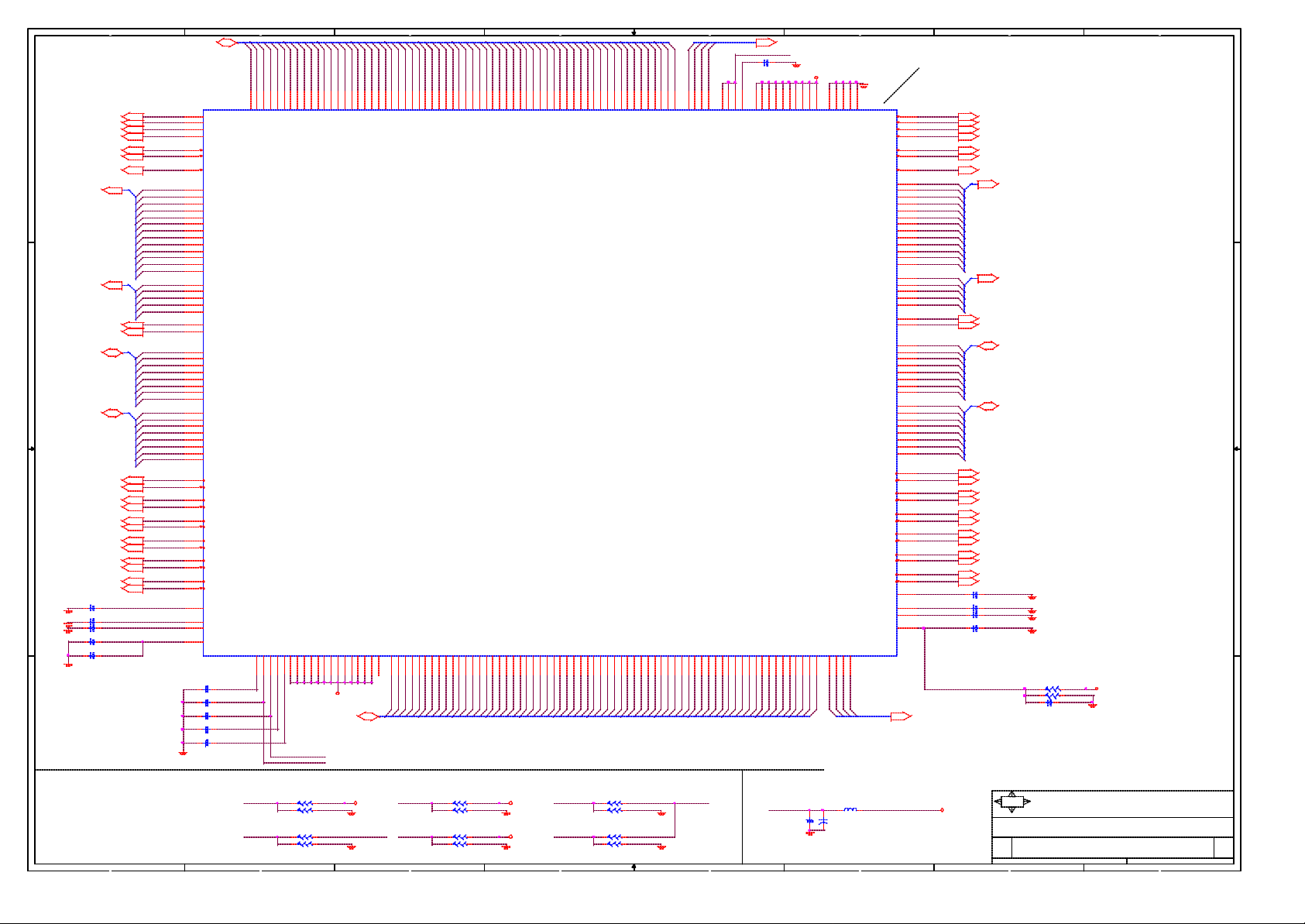

Block Diagram

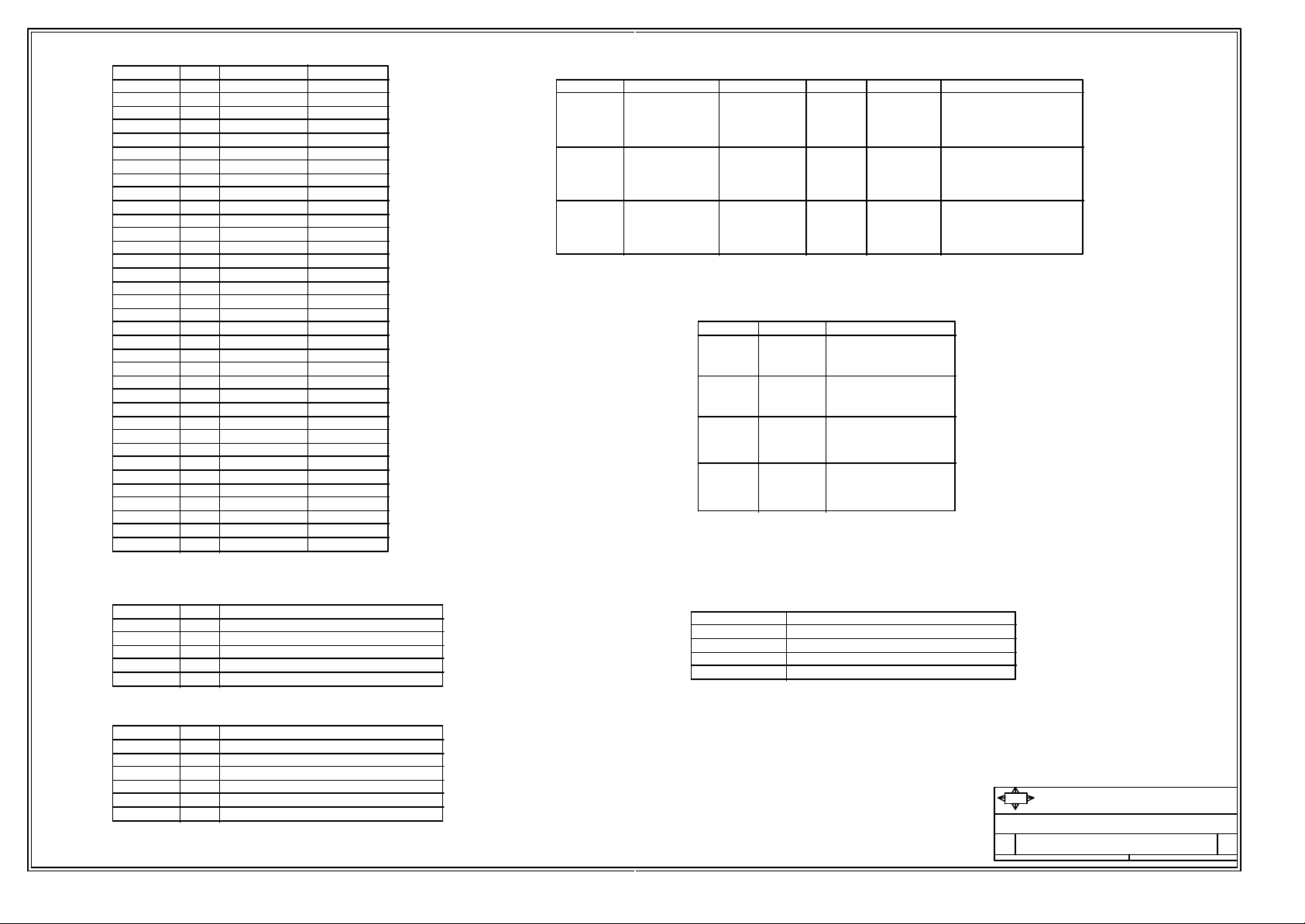

GPIO

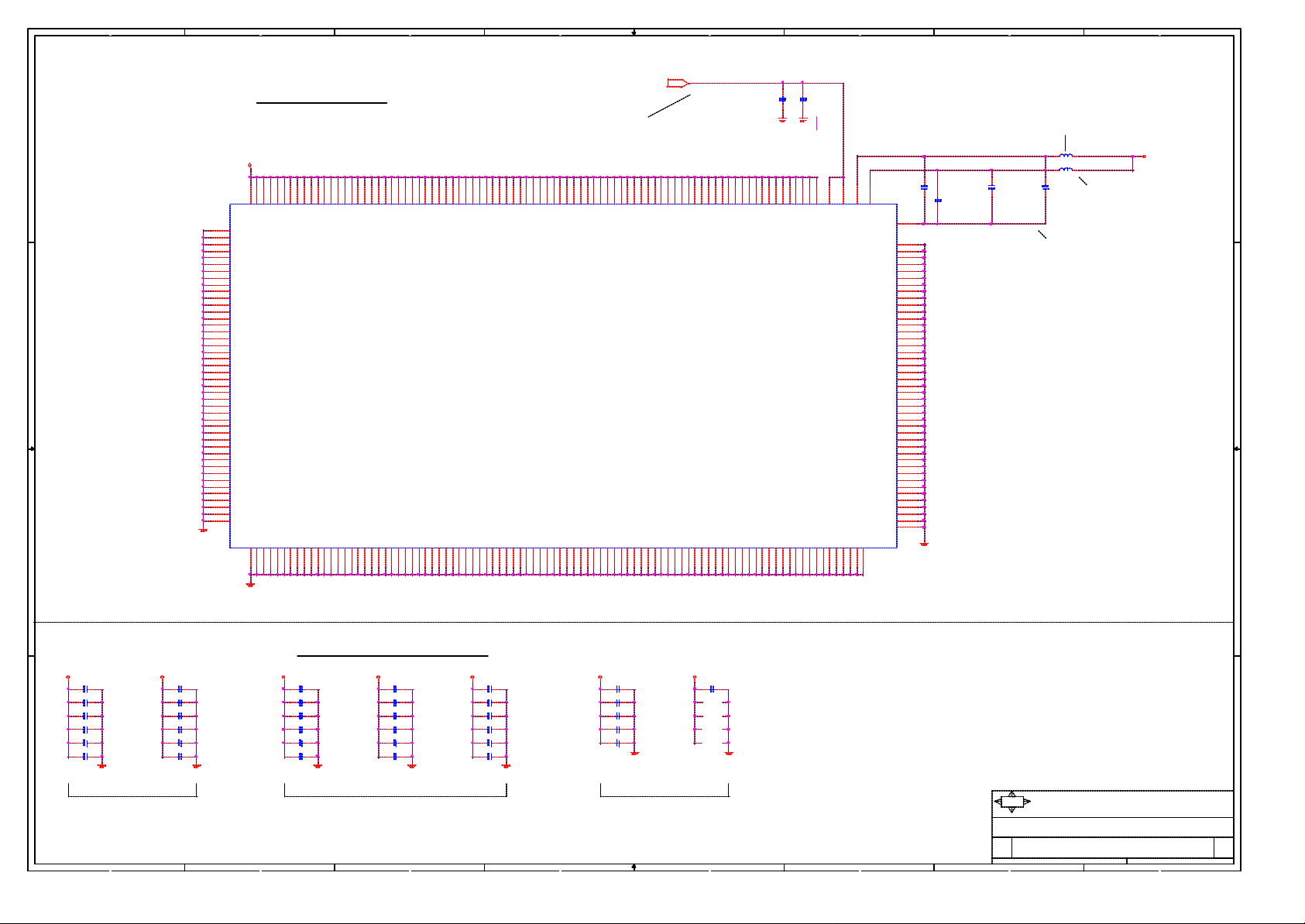

Intel mPGA478B CPU - Signals

Intel Springdale - Host Signals

Intel Springdale - Memory Signals

Intel Springdale - AGP Signals

DDR DIMM 1,2

DDR DIMM 3,4

Broadcom BCM 4401/5705

Intel ICH5 - PCI & IDE & AC97 Signals

Intel ICH5 - Other Signals

A A

CY28404 & FWH & FDD & TPM

AC97 Audio & D-LED

AGP 4X/8X Slot & Ext PCI

PCI Slots 1 & 2 & 3

ATA33/66/100 IDE & Video Connectors

USB Connectors

2

3

4

5Intel mPGA478B CPU - Power

6

7

8

9

10

11

12

13

14

15LPC I/O -47M192

16

17

18

19

20

21W83302 ACPI controller

MS(6772)

Intel (R) Springdale (GMCH) + ICH5 Chipset

Intel Northwood & Prescott mPGA478B Processor

CPU:

Intel Northwood/Prescott

System Chipset:

Intel Springdale - GMCH (North Bridge)

Intel ICH5 (South Bridge)

On Board Chipset:

BIOS -- FWH EEPRO M

AC'97 Codec -- SigmaTel 9752/9766/ALC203

LPC Super I/O -- SMSC 47M192

LAN --Broadcom BCM4401/5705

CLOCK -- Cypress CY28404

Main Memory:

DDR * 4 (Max 4GB)

Expansion Slots:

PCI2.3 SLOT * 3

ST PWM:

Controller: ST L6710

Version 0A

Front Panel & Fan

VRD 10

AGP & DDR Power

22

23

24

25IEEE1394-TSB43AB23

MICRO-STAR INt'L CO., LTD.

MSI

Title

Size Document Number Rev

星期四, 二月

1

Date: Sheet of

13, 2003

COVER SHEET

MS-6772

1 26

0A

1

VRM 10

ST L6710

Intel mPAG478B Processor

Block Diagram

2-Phas e PWM

FSB

AGP 1.5V

4X/8X

Connec tor

Analog

Video

Out

IDE Primary

UltraDMA 33/66/100

Springdale

Link

HUB

64bit DDR

Channel 1

64bit DDR

Channel 2

IDE Secondary

ICH5

A A

USB Port 0

4 DDR

DIMM

Modules

(1+1)

PCI BUS

PCI BUS

PCI BUS

PCI Slot 2

PCI Slot 1

PCI Slot 3

IEEE1394

TSB43AB23

USB Port 1

USB Port 2

USB Port 3

USB

LPC Bus

LAN

BCM4401/5705

USB Port 4

LP C SIO

USB Port 5

SMSC

47M192

USB Port 6

USB Port 7

AC'97 Codec

Serial ATA 0

Serial ATA 1

AC'97 Link

Serial ATA

Flas h

Keyboard

Mous e

Floopy Parallel Serial

1

MSI

Title

Size Document Number Rev

Date: Sheet of

MICRO-STAR INt'L CO., LTD.

BLOCK DIAGRAM

30, 2003

MS-6772

星期四, 一月

2 26

0A

1

ICH5

GPIO 0

GPIO 1

GPIO 2

GPIO 3

GPIO 4

GPIO 5

GPIO 6

GPIO 7

GPIO 8

GPIO 9

GPIO 10

GPIO 11

GPIO 12

GPIO 13

GPIO 14

GPIO 15

GPIO 16

GPIO 17

GPIO 18

GPIO 19

GPIO 20

GPIO 21

GPIO 22 GPO22

GPIO 23

I

ISA_REQ#

I

PREQ#5

I

PIRQ#E

I

PIRQ#F

I

PIRQ#G

I

PIRQ#H

I

SIO_SMI#

I

RECOVER#

I

8051_WAKE#

I

OC4#

I

OC5#

I

IR_WAKE#

I

GPI12

I

SIO_PME#

I OC#6

OC#7

I

ISA_GNT#

O

O

PGNT#5

O

8051_PWR

GPO19

O

O

GPO20

O

IR_PWR

OD

GPO23

O

GPIO 24 I/O GPIO24

FunctionTypeGPIO Pin

GPIO 25 I/O

A A

*

GPIO 27

GPIO 28

GPIO 32

GPIO 33

GPIO 34

GPIO 40 PREQ#4

GPIO 41

GPIO 48

GPIO 49

GPIO25

I/O

ISA_NOGO

I/O GPIO28

BIOS_WP#

I/O

I/O

SATA LED

I/O

GPIO34

I

GPI41

I

O PGNT#4

CPUPWRGD

OD

Power well

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

RESUME

RESUME

RESUME

RESUME

RESUME

RESUME

RESUME

RESUME

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

RESUME

RESUME

RESUME

RESUME

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

default output

default output

default output

default output

default output

default output

default output

PCI Config.

DEVICE

INTA#

INTB#

PCI_REQ#0PCI Slot 1

PCI_GNT#0

INTC#

INTD#

PCI Slot 2

INTB#

INTC#

PCI_REQ#1 AD17 PCICLK1

PCI_GNT#1

INTD#

INTA#

PCI Slot 3 PCI_REQ#2 AD18

INTC#

INTD#

PCI_GNT#2

INTA#

INTB#

IDSEL

AD16

DDR DIMM Config.

DEVICE

DIMM 1 MCLK_A0/MCLK_A0#

DIMM 2

DIMM 3

DIMM 4

1010000B

1010001B

1010010B

1010011B

CLOCKREQ#/GNT#

PCICLK0

PCICLK2

CLOCKADDRESS

MCLK_A1/MCLK_A1#

MCLK_A2/MCLK_A2#

MCLK_A3/MCLK_A3#

MCLK_A3/MCLK_A3#

MCLK_A4/MCLK_A4#

MCLK_B0/MCLK_B0#

MCLK_B1/MCLK_B1#

MCLK_B2/MCLK_B2#

MCLK_B3/MCLK_B3#

MCLK_B4/MCLK_B4#

MCLK_B5/MCLK_B5#

CLK GEN PIN OUTMCP1 INT Pin

13 (PCI_CLK0)

14 (PCI_CLK1)

15 (PCI_CLK2)

FWH

TypeGPIO Pin

GP I 0 PD_DET

GP I 1

*

GP I 3

GP I 4

SIO

TypeGPIO Pin

GP12 DLED1

GP13

GP15

GP26

Function

I

I

SD_DET

I

Pull down through 1K ohms (unused)GP I 2

Pull down through 1K ohms (unused)

I

MODEL Select

I

Function

O

O

DLED2

O

DLED3GP14

DLED4

O

I

VID5

IGP43

VID4

PCI RESET DEVICE

Signals

PCIRST#_ICH5 AGP slot,FWH,MS5,

PCIRST#1

HD_RST#

1

Target

Springdale,LAN, Super I/O,1394,TPM

PCI slot 1-3, ext PCI slotPCIRST#2

Primary, Scondary IDE

MSI

Title

Size Document Number Rev

Date: Sheet of

MICRO-STAR INt'L CO., LTD.

General Purpose Spec

12, 2003

MS-6772

星期三, 二月

3 26

0A

8

D D

HDBI#[0..3](6)

FERR#(13)

STPCLK#(13)

HINIT#(13,14)

HDBSY#(6)

HDRDY#(6)

HTRDY#(6)

HADS#(6)

HLOCK#(6)

HBNR#(6)

HITM#(6)

HBPRI#(6)

C C

B B

HDEFER#(6)

THERMD+(15)

THERMD-(15)

TRMTRIP#(13)

PROCHOT#(6)

IGNNE#(13)

A20M#(13)

BOOT(23)

BSEL0(14)

BSEL1(14)

CPU_GD(13)

CPURST#(6)

HD#[0..63](6)

HDBI#0

HDBI#1

HDBI#2

HDBI#3

HIT#(6)

ITP_TDI

ITP_TDO

ITP_TMS

ITP_TRST#

ITP_TCK

PROCHOT#

SMI#(13)

SLP#(13)

BOOT

CPU_GD

CPURST#

HD#63

HD#62

HD#61

HD#60

HD#59

HD#58

HD#57

HD#56

HD#55

HD#54

7

HA#[3..31](6)

CPU1A

E21

DBI0#

G25

DBI1#

P26

DBI2#

V21

DBI3#

AC3

IERR#

V6

MCERR#

B6

FERR#

Y4

STPCLK#

AA3

BINIT#

W5

INIT#

AB2

RSP#

H5

DBSY#

H2

DRDY#

J6

TRDY#

G1

ADS#

G4

LOCK#

G2

BNR#

F3

HIT#

E3

HITM#

D2

BPRI#

E2

DEFER#

C1

TDI

D5

TDO

F7

TMS

E6

TRST#

D4

TCK

B3

THERMDA

C4

THERMDC

A2

THERMTRIP#

AF26

GND/SKTOCC#

C3

PROCHOT#

B2

IGNNE#

B5

SMI#

C6

A20M#

AB26

SLP#

A22

RESERVED0

A7

RESERVED1

AE21

RESERVED2

AF24

RESERVED3

AF25

RESERVED4

AD1

BOOTSELECT

AE26

OPTIMIZED/COMPAT#

AD6

BSEL0

AD5

BSEL1

AB23

PWRGOOD

AB25

RESET#

AA24

D63#

AA22

D62#

AA25

D61#

Y21

D60#

Y24

D59#

Y23

D58#

W25

D57#

Y26

D56#

W26

D55#

V24

D54#

6

CPU SIGNAL BLOCK

HA#17

A18#

D33#

M23

HA#16

A17#

D32#

H25

HA#15

A16#

D31#

K23

HA#14

A15#

D30#

J24

HA#13

A14#

D29#

L22

HA#12

A13#

D28#

M21

HA#11

A12#

D27#

H24

A11#

D26#

HA#25

HA#27

HA#30

HA#26

HA#29

HA#31

HA#28

AB1Y1W2V3U4T5W1R6V2T4U3P6U1T2R3P4P3R2T1N5N4N2M1N1M4M3L2M6L3K1L6K4K2

A35#

A34#

A33#

A32#

A31#

A30#

A29#

A28#

A27#

A26#

D53#

D52#

D51#

D50#

D49#

D48#

D47#

D46#

D45#

D44#

D43#

D42#

D41#

V22

U21

V25

U23

U24

U26

T23

T22

T25

T26

R24

R25

P24

HA#18

HA#22

HA#20

HA#23

HA#24

HA#19

HA#21

A25#

A24#

A23#

A22#

A21#

A20#

A19#

D40#

D39#

D38#

D37#

D36#

D35#

D34#

R21

N25

N26

M26

N23

M24

P21

N22

HA#10

A10#

D25#

G26

L21

HA#9

HA#8

A9#

D24#

D26

HA#7

A8#

D23#

F26

HA#6

A7#

D22#

E25

HA#5

A6#

D21#

F24

HA#4

A5#

D20#

F23

HA#3

A4#

D19#

G23

A3#

D18#

E24

D17#

H22

5

AE25A5A4

DBR#

D16#

D15#

D25

J21

VCC_SENSE

VSS_SENSE

D14#

D13#

D12#

D23

C26

H21

AD26

ITP_CLK1

D11#

D10#

G22

AC26

ITP_CLK0

D9#

B25

C24

VID5

AD2

AD3

VIDPWRGD

D8#

D7#

C23

B24

VCC_SENSE (23)

VSS_SENSE (23)

VID1

VID2

VID4

VID3

AE1

AE2

AE3

AE4

VID4#

VID3#

VID2#

VID5#

D6#

D5#

D4#

D3#

D22

C21

A25

A23

VID0

AE5

VID1#

VID0#

GTLREF3

GTLREF2

GTLREF1

GTLREF0

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

BCLK1#

BCLK0#

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

COMP1

COMP0

DP3#

DP2#

DP1#

DP0#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

LINT1/NMI

LINT0/INTR

D2#

D1#

D0#

PGA-S478-GD10-F02

CRITICAL

B22

B21

4

CPUVID_GD (23)

VID[0..5] (15,23)

AA21

AA6

F20

F6

AB4

BPM#5

BPM#4

AA5

BPM#3

Y6

BPM#2

AC4

BPM#1

AB5

AC6

BPM#0

HREQ#4

H3

HREQ#3

J3

HREQ#2

J4

K5

HREQ#1

HREQ#0

J1

TESTHI12

AD25

TESTHI11

A6

Y3

TESTHI10

TESTHI9

W4

TESTHI8

U6

AB22

AA20

AC23

AC24

AC20

TESTHI2

AC21

TESTHI1

AA2

AD24

TESTHI0

AF23

AF22

F4

HRS#2

HRS#1

G5

HRS#0

F1

V5

AC1

HBR#0

H6

COMP1

P1

COMP0

L24

L25

K26

K25

J26

R5

L5

W23

P23

J23

F21

W22

R22

K22

E22

E5

D1

VIDPWRGD DC Specifications

VIL

VIH

I t must rout to the enable pin of PWM and CK-409.

VIDGD to Vccp delay time is from 1ms to 10ms.

VIDGD rising time is 150ns.

X7R

C116 C220P16X

16V

R69 62R

R137 62R

R93 62R

R97 62R

R102 62R

R82 62R

R87 62R

R78 62R

R106 61.9R1%

R109 61.9R1%

0.9

GTLREF (6)

HREQ#[0..4] (6)

VCCP

CPU_CLK# (14)

CPU_CLK (14)

HRS#[0..2] (6)

HBR#0 (6)

HADSTB#1 (6)

HADSTB#0 (6)

HDSTBP#3 (6)

HDSTBP#2 (6)

HDSTBP#1 (6)

HDSTBP#0 (6)

HDSTBN#3 (6)

HDSTBN#2 (6)

HDSTBN#1 (6)

HDSTBN#0 (6)

NMI (13)

INTR (13)

Min MaxTyp

3

2

1

CPU GTL REFERNCE VOLTAGE BLOCK

0.3

VCCP

VTT

R189

R142

200R1%

200R1%

GTLREF

C147

C0.01U50X

X7R X7R

0.63*Vccp

C197

C0.1U16X

R153

169R1%

CPU ITP BLOCK

ITP_TDI

ITP_TRST#

ITP_TMS

ITP_TDO

ITP_TCK

R76 150R

R92 680R

R104 39R

R77 75R

R81 27R

VCCP

VCCP

HD#53

HD#52

HD#51

HD#50

HD#49

HD#48

HD#47

HD#46

HD#45

HD#43

HD#44

HD#42

HD#41

HD#40

HD#38

HD#39

HD#37

HD#36

HD#35

HD#33

HD#34

HD#32

HD#31

HD#30

HD#29

HD#28

HD#27

HD#26

HD#25

HD#23

HD#24

HD#22

HD#21

HD#20

HD#18

HD#19

HD#17

HD#16

HD#15

HD#14

HD#13

HD#12

HD#11

HD#10

HD#9

HD#8

HD#7

HD#6

HD#5

HD#4

HD#3

HD#2

HD#1

HD#0

CPU STRAPPING RESISTORS

A A

8

7

BPM#4

R91 62R

BPM#5

R83 62R

BPM#2 CPU_GD

R80 62R

BPM#3

R95 62R

BPM#1

R89 62R

BPM#0

R85 62R

VCCP

6

ALL COMPONENTS CLOSE TO CPU

5

PROCHOT#

HBR#0

CPURST#

R140 62R

R75 300R

R101 220R

R86 62R

VCCP

4

MSI

Title

Size Document Number Rev

3

Date: Sheet of

MICRO-STAR INt'L CO., LTD.

Intel mPGA478B - Signals

28, 2003

6772

2

星期五, 二月

4 26

1

0A

8

7

6

5

4

3

2

1

D15

D17

VCC

VCC

VSS

VSS

E7E9F10

D19D7D9

VCC

VSS

VCC_VID

C33

C1U10Y

E10

E12

E14

E16

E18

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

F12

F14

F16

F18F2F22

F25F5F8

CPU VOLTAGE BLOCK

VCC_VID(21,23)

VID Voltage is from 1.14V to 1.32V.

It is derived from 3.3V.

It should be able to source 150mA.

D D

VCCP

A10

A12

A14

A16

A18

A20A8AA10

AA12

AA14

AA16

AA18

AA8

AB11

AB13

AB15

AB17

AB19

AB7

AB9

AC10

AC12

AC14

AC16

AC18

AC8

AD11

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

AE16

AE18

AE20

AE6

AE8

AF11

AF13

AF15

AF17

CPU1B

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

D10

VSS

A11

VSS

A13

VSS

A15

VSS

A17

VSS

A19

VSS

A21

VSS

A24

VSS

A26

VSS

A3

VSS

A9

VSS

AA1

VSS

AA11

VSS

AA13

VSS

AA15

VSS

AA17

VSS

AA19

VSS

AA23

C C

B B

AA26

AB10

AB12

AB14

AB16

AB18

AB20

AB21

AB24

AC11

AC13

AC15

AC17

AC19

AC2

AC22

AC25

AC5

AC7

AC9

VSS

VSS

AA4

VSS

AA7

VSS

AA9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AB3

VSS

AB6

VSS

AB8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AD10

AD12

AD14

AD16

AD18

AD21

AD4

AD23

AD8

AE11

AE13

AE15

AE17

AE19

AE22

AE24

AE7

AE9

AF1

AF10

AF12

AF14

AF16

AF18

AF20

AF6

AF8

B10

B12

B14

B16

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

B18

B23

B20

B26B4B8

C11

C13

AF19

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

C15

C17C2C19

C22

C25C5C7C9D12

It d rives the power logic of BSEL[1:0] and VID[5:0].

VID to VIDGD delay time is from 1ms to 10ms.

VID to VIDGD deassertion time is 1ms for max.

AF2

AF21

AF5

AF7

AF9

B11

B13

B15

B17

B19B7B9

C10

C12

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D14

D16

D18

D20

D21D3D24D6D8E1E11

C14

C16

C18

C20C8D11

D13

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

E13

E15

E17

E19

E23

E4

E26

E20E8F11

VCC

VCC

VSS

VSS

Near processor

F13

F15

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

G21G6G24

G3H1H23

1.2V 150mA

C41

0.1u

F17

F19

F9

VCC

VCC

VSS

VSS

VCC

VSS

H26H4J2

AF4

VSS

VCC-VID

VSS

AF3

VCC-VIDPRG

VSS

VSS

VSS

J22

J25J5K21

AD20

VCC-IOPLL

VSS

C42

X_1u C43

AE23

VCCA

AD22

VSSA

Y5

VSS

Y25

VSS

Y22

VSS

Y2

VSS

W6

VSS

W3

VSS

W24

VSS

W21

VSS

V4

VSS

V26

VSS

V23

VSS

V1

VSS

U5

VSS

U25

VSS

U22

VSS

U2

VSS

T6

VSS

T3

VSS

T24

VSS

T21

VSS

R4

VSS

R26

VSS

R23

VSS

R1

VSS

P5

VSS

P25

VSS

P22

VSS

P2

VSS

N6

VSS

N3

VSS

N24

VSS

N21

VSS

M5

VSS

M25

VSS

M22

VSS

M2

VSS

L4

VSS

L26

VSS

L23

VSS

L1

VSS

K6

VSS

K3

VSS

K24

VSS

VSS

PGA-S478-GD10-F02

CRITICAL

X_C1U10Y

It support DC current if 100mA.

CPU_IOPLL

C46

C22U10Y1206

10V

VSSA

The ESL is less than 5nH, and the ESR is less than 0.3ohm.

L2 10U100m_0805

L3 10U100m_0805

DC voltage drop should

C38

be less than 70mV.

X_C10U10Y1206

10V

VCCP

CPU DECOUPLING CAPACITORS

VCCP

A A

Place these caps within socket cavity Place these caps within south side of processor

VCCP VCCP VCCP VCCPVCCP VCCP

C93

C10U10Y1206

C89

C10U10Y1206

C85

C10U10Y1206

C77

C10U10Y1206

C72

C10U10Y1206

C67

C10U10Y1206

8

C94

C10U10Y1206

C90

C10U10Y1206

C86

C10U10Y1206

C78

C10U10Y1206

C73

C10U10Y1206

C68

C10U10Y1206

7

C24

C10U10Y1206

C12

X_10u-1206

C21

X_10u-1206

C29

C10U10Y1206

C16

X_10u-1206

C8

X_10u-1206

Place these caps within north side of processor

C23

C10U10Y1206

C13

X_10u-1206

C15

X_10u-1206

C27

C10U10Y1206

C10

X_10u-1206

C25

C10U10Y1206

6

C22

10u-1206

C14

X_10u-1206

C11

X_10u-1206

C26

C10U10Y1206

C28

C10U10Y1206

C9

X_10u-1206

4

C117

C10U10Y1206

MSI

Title

Size Document Number Rev

3

Date: Sheet of

MICRO-STAR INt'L CO., LTD.

Intel mPGA478B - Power

28, 2003

6772

2

星期五, 二月

5 26

1

0A

C118

C10U10Y1206

C119

C10U10Y1206

C120

C10U10Y1206

C121

C10U10Y1206

C122

C10U10Y1206

5

8

HA#[3..31](4)

D D

HADSTB#0(4)

HADSTB#1(4)

HBR#0(4)

HREQ#[0..4](4)

HRS#[0..2](4)

PROCHOT#(4)

BSEL0_SPG(14)

BSEL1_SPG(14)

HBPRI#(4)

HBNR#(4)

HLOCK#(4)

HADS#(4)

HIT#(4)

HITM#(4)

HDEFER#(4)

HTRDY#(4)

HDBSY#(4)

HDRDY#(4)

MCH_CLK(14)

MCH_CLK#(14)

MS5_POK(21)

CPURST#(4)

PCIRST#1(11,14,15,21,25)

R162 20R1%

GTLREF(4)

ICH_SYNC#

C C

B B

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HRS#0

HRS#1

HRS#2

HRCOMP

HSWING

VCCA_FSB

C143 0.1u

VCCA_DPLL

U10A

D26

D30

L23

E29

B32

K23

C30

C31

J25

B31

E30

B33

J24

F25

D34

C32

F28

C34

J27

G27

F29

E28

H27

K24

E32

F31

G30

J26

G26

B30

D28

B24

B26

B28

E25

F27

B29

J23

L22

C29

J21

K21

E23

L21

D24

E27

G24

G22

C27

B27

B7

C7

AE14

E8

AK4

AJ8

L20

L13

L12

E24

C25

F23

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HAD_STB0#

HAD_STB1#

BREQ0#

BPRI#

BNR#

HLOCK#

ADS#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HIT#

HITM#

DEFER#

HTRDY#

DBSY#

DRDY#

RS0#

RS1#

RS2#

HCLKP

HCLKN

PWROK

CPURST#

RSTIN#

ICH_SYNC#

PROCHOT#

BSEL0

BSEL1

HDRCOMP

HDSWING

HDVREF

7

B3

A31

VCCA_FSB

VCCA_DPLL

VSS

VSS

C10

C8

B4

VCCA_FSB

VSS

C12

C14

VCC_AGP

J6J7J8J9K6K7K8K9L6L7L9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

C16

C18

C20

C22

C24

C26

C28D1D11

D9

6

N11N9P10

P11

R11

T16

T17

T18

T19

U16

U17

U20

V16

V18

V20

N10

M10

M11M8M9

L10

L11

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

D13

D15

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D17

D19

D21

D23

D25

D27

D29

D31

T20

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D33

D35

F3F5F8

E3

F1

E1

W16

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

F18

F20

F22

F14

F16

F10

F12

W19

F24

5

W20

Y16

Y17

Y18

Y19

Y20

A3

A33

A35B2B25

B34C1C23

C35

E26

M31

AF13

AF23

AJ12

VCC

VSS

F26

NCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

G31

G35

H12

H14

H16H2H20

H5

G28

H18

H8

H9

R25

NC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

H22

VSS

H24

H26

H30

H33

J10

J12

J14

J16

4

VTT

AN1

AP2

AR3

AR33

AR35

A7A9A11

A13

A16

A20

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

J18

J20

J22

J28

J32

J35

K11

K12

K14

K16

K18

K20

A23

K22

A25

VSS

VSS

VSS

VSS

K25

A27

A29

A32

VSS

VSS

VSS

VSS

K33

K27

K29

D5D6D7E6E7

C4

VTT

VTT

VSS

VSS

VSS

VSS

VSS

VSS

VSS

L24M3M6

L25

L26

L35

L31

VTT

VTT

VSS

VSS

F7

A4A5A6B5B6C5C6

VTT

VTT

VTT

VTT

VSS

VSS

VSS

VSS

M26

M27

M28

M30

VTT

VSS

M33N1N4

3

VTT

VTT

VSS

VSS

VTT_FSB1

VTT_FSB2

A15

A21

HD0#

VTT

VTT

HD1#

HD2#

VTT_FSB

VTT_FSB

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

DINV_0#

DINV_1#

DINV_2#

DINV_3#

HD_STBP0#

HD_STBN0#

HD_STBP1#

HD_STBN1#

HD_STBP2#

HD_STBN2#

HD_STBP3#

HD_STBN3#

VSS

INTEL-SpringDale

CRITICAL

C179 C0.47U16Y

C165 C0.47U16Y

HD#0

B23

HD#1

E22

HD#2

B21

D20

HD#3

HD#4

B22

HD#5

D22

HD#6

B20

HD#7

C21

E18

HD#8

HD#9

E20

HD#10

B16

HD#11

D16

HD#12

B18

B17

HD#13

HD#14

E16

HD#15

D18

HD#16

G20

HD#17

F17

E19

HD#18

HD#19

F19

HD#20

J17

HD#21

L18

HD#22

G16

G18

HD#23

HD#24

F21

HD#25

F15

HD#26

E15

HD#27

E21

J19

HD#28

HD#29

G14

HD#30

E17

HD#31

K17

HD#32

J15

L16

HD#33

HD#34

J13

HD#35

F13

HD#36

F11

HD#37

E13

K15

HD#38

HD#39

G12

HD#40

G10

HD#41

L15

HD#42

E11

K13

HD#43

HD#44

J11

HD#45

H10

HD#46

G8

HD#47

E9

B13

HD#48

HD#49

E14

HD#50

B14

HD#51

B12

HD#52

B15

D14

HD#53

HD#54

C13

HD#55

B11

HD#56

D10

HD#57

C11

E10

HD#58

HD#59

B10

HD#60

C9

HD#61

B9

HD#62

D8

B8

HD#63

HDBI#0

C17

HDBI#1

L17

HDBI#2

L14

C15

HDBI#3

B19

C19

L19

K19

G9

F9

D12

E12

2

HD#[0..63] (4)

HDBI#[0..3] (4)

HDSTBP#0 (4)

HDSTBN#0 (4)

HDSTBP#1 (4)

HDSTBN#1 (4)

HDSTBP#2 (4)

HDSTBN#2 (4)

HDSTBP#3 (4)

HDSTBN#3 (4)

1

VCC3

0.1u

I=30mA

VCCA_FSB

I=35mA

VCCA_DPLL

C208

+

C205

0.1u

ESR is 0.1mohm to GMCH

+

EC26

CD100U10EL7

6

L5 0.82U30m

EC24

CD100U10EL7

L7 100N300m

FSB

DPLL

R198 0R

R200 1R1%

VCC_AGP

VCC_AGP

5

VTT

A A

X7R

C191

C0.01U50X

HSWING

C149

X7R

16V

8

1/4*Vccp

R186

301R1%

R150

100R1%C0.01U50X

7

ICH_SYNC# MS5_POK ICH_PWROK

0 0

1

1 1 1

10

0

0

0

0

MS5_POK(21)

4

ICH_SYNC#

MS5_POK

VCC3

R383 X_220

R333

X_220

Q45 X_2N3904S

Q47 X_2N3904S

R331 0R

3

R332

X_1K

ICH_PWROK (13)

MSI

Title

Size Document Number Rev

Date: Sheet of

MICRO-STAR INt'L CO., LTD.

Intel Springdale - CPU Signals

27, 2003

6772

2

星期四, 二月

6 26

1

0A

8

MCS_A#0(9)

MCS_A#1(9)

MCS_A#2(9)

D D

C C

B B

A A

MCS_A#3(9)

MRAS_A#(9)

MCAS_A#(9)

MWE_A#(9)

MA_A[0..12](9)

MAB_A[1..5](9)

MBA_A0(9)

MBA_A1(9)

MDQM_A[0..7](9)

MDQS_A[0..7](9)

MCLK_A0(9)

MCLK_A#0(9)

MCLK_A1(9)

MCLK_A#1(9)

MCLK_A2(9)

MCLK_A#2(9)

MCLK_A3(9)

MCLK_A#3(9)

MCLK_A4(9)

MCLK_A#4(9)

MCLK_A5(9)

MCLK_A#5(9)

C0.01U50XC269

C0.01U50XC263

C0.01U50XC270 0.1uC262

0.1uC136

C135 C2.2U6.3Y

8

MDQ_A[0..63](9) MCKE_A[0..3] (9)

U10B

AA34

SCS_A0#

Y31

SCS_A1#

Y32

SCS_A2#

W34

SCS_A3#

AC33

SRAS_A#

Y34

SCAS_A#

AB34

SWE_A#

AJ34

MA_A0

MA_A1

MA_A2

MA_A3

MA_A4

MA_A5

MA_A6

MA_A7

MA_A8

MA_A9

MA_A10

MA_A11

MA_A12

MAB_A1

MAB_A2

MAB_A3

MAB_A4

MAB_A5

MDQM_A0

MDQM_A1

MDQM_A2

MDQM_A3

MDQM_A4

MDQM_A5

MDQM_A6

MDQM_A7

MDQS_A0

MDQS_A1

MDQS_A2

MDQS_A3

MDQS_A4

MDQS_A5

MDQS_A6

MDQS_A7

XRCOMP

XCOMPH

XCOMPL

XVREF

SMAA_A0

AL33

SMAA_A1

AK29

SMAA_A2

AN31

SMAA_A3

AL30

SMAA_A4

AL26

SMAA_A5

AL28

SMAA_A6

AN25

SMAA_A7

AP26

SMAA_A8

AP24

SMAA_A9

AJ33

SMAA_A10

AN23

SMAA_A11

AN21

SMAA_A12

AL34

SMAB_A1

AM34

SMAB_A2

AP32

SMAB_A3

AP31

SMAB_A4

AM26

SMAB_A5

AE33

SBA_A0

AH34

SBA_A1

AP12

SDM_A0

AP16

SDM_A1

AM24

SDM_A2

AP30

SDM_A3

AF31

SDM_A4

W33

SDM_A5

M34

SDM_A6

H32

SDM_A7

AN11

SDQS_A0

AP15

SDQS_A1

AP23

SDQS_A2

AM30

SDQS_A3

AF34

SDQS_A4

V34

SDQS_A5

M32

SDQS_A6

H31

SDQS_A7

AK32

SMDCLK_A0

AK31

SMDCLK_A0#

AP17

SMDCLK_A1

AN17

SMDCLK_A1#

N33

SMDCLK_A2

N34

SMDCLK_A2#

AK33

SMDCLK_A3

AK34

SMDCLK_A3#

AM16

SMDCLK_A4

AL16

SMDCLK_A4#

P31

SMDCLK_A5

P32

SMDCLK_A5#

AK9

SMXRCOMP

AN9

SMXCOMPVOH

AL9

SMXCOMPVOL

E34

SMVREF_A

C144 C0.47U16Y

C162 C0.22U16Y

C170 C0.01U50X

C234 C0.22U16Y

C241 0.1u

7

MDQ_A1

MDQ_A0

AP10

AP11

SDQ_A0

E35

XRCOMP

YRCOMP

7

MDQ_A2

MDQ_A3

AM12

AN13

SDQ_A1

SDQ_A2

SDQ_A3

VCC_DDR

VCC_DDR

VCC_DDR

AA35

R35

MDQ_A4

AM10

AR21

VCC_DDR_C3

VCC_DDR_C2

6

MDQ_A9

MDQ_A11

MDQ_A17

MDQ_A6

MDQ_A7

MDQ_A5

AL10

AL12

AP13

SDQ_A4

SDQ_A5

SDQ_A6

VCC_DDR

VCC_DDR

VCC_DDR

AL7

AR15

AL6

R290 42.2R1%

R287 42.2R1%

R180 42.2R1%

R161 42.2R1%

MDQ_A14

MDQ_A8

MDQ_A10

MDQ_A15

MDQ_A12

MDQ_A13

MDQ_A16

AP14

AM14

AL18

AP19

AL14

AN15

AP18

AM18

AP22

AM22

SDQ_A7

SDQ_A8

SDQ_A9

SDQ_A10

SDQ_A11

SDQ_A12

SDQ_A13

SDQ_A14

SDQ_A15

SDQ_A16

VCC_DDR

VCC_DDR

AM1

AM2

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

AR4

AR5

AN8

AP3

AP4

AP5

AP6

AP7

VCC_DDR C268 C2.2U6.3Y

MDQ_B[0..63](10)

values still need verification

VCC_DDR

VCC_DDR_C3

AA35AA33

MDQ_A18

MDQ_A19

AL24

AN27

SDQ_A17

SDQ_A18

SDQ_A19

VCC_DDR

VCC_DDR

VCC_DDR

AR7

AR31

MDQ_A21

MDQ_A20

MDQ_A22

AP21

AL22

AP25

SDQ_A20

SDQ_A21

SDQ_B0

AJ10

AE15

MDQ_B0

MDQ_B1

XCOMPL

XCOMPH

MDQ_A24

MDQ_A23

AP27

AP28

SDQ_A22

SDQ_A23

SDQ_A24

SDQ_B1

SDQ_B2

SDQ_B3

AL11

AE16

MDQ_B2

MDQ_B3

6

MDQ_A25

MDQ_A28

MDQ_A27

MDQ_A26

AP29

AP33

AM33

AM28

SDQ_A25

SDQ_A26

SDQ_A27

SDQ_A28

SDQ_B4

SDQ_B5

SDQ_B6

SDQ_B7

AL8

AF12

AK11

AG12

MDQ_B5

MDQ_B7

MDQ_B6

MDQ_B4

R289 31.6KR1%

R251 10.2KR1%

R252 31.6KR1%

MDQ_A29

MDQ_A30

MDQ_A31

AN29

AM31

AN34

SDQ_A29

SDQ_A30

SDQ_B8

SDQ_B9

AE17

AL13

AK17

MDQ_B9

MDQ_B8

MDQ_B10

MDQ_A33

MDQ_A32

AH32

AG34

SDQ_A31

SDQ_A32

SDQ_A33

SDQ_B10

SDQ_B11

SDQ_B12

AL17

AK13

MDQ_B11

MDQ_B12

MDQ_A36

MDQ_A34

MDQ_A35

AF32

AD32

AH31

SDQ_A34

SDQ_A35

SDQ_B13

SDQ_B14

AJ14

AJ16

AJ18

MDQ_B15

MDQ_B14

MDQ_B13

MDQ_A37

MDQ_A38

AG33

AE34

SDQ_A36

SDQ_A37

SDQ_A38

SDQ_B15

SDQ_B16

SDQ_B17

AE19

AE20

MDQ_B17

MDQ_B16

MDQ_A40

MDQ_A39

MDQ_A41

AD34

AC34

AB31

SDQ_A39

SDQ_A40

SDQ_A41

SDQ_B18

SDQ_B19

SDQ_B20

AG23

AK23

AL19

MDQ_B20

MDQ_B18

MDQ_B19

VCC_DDR

VCC_DDR

MDQ_A43

MDQ_A44

MDQ_A42

V32

V31

AD31

SDQ_A42

SDQ_A43

SDQ_B21

SDQ_B22

AK21

AJ24

AE22

MDQ_B22

MDQ_B23

MDQ_B21

5

MDQ_A45

MDQ_A46

MDQ_A47

AB32

U34

U33

SDQ_A44

SDQ_A45

SDQ_A46

SDQ_B23

SDQ_B24

SDQ_B25

AK25

AH26

AG27

MDQ_B24

MDQ_B26

MDQ_B25

YCOMPL

R33

YCOMPH

R34

5

MDQ_A49

MDQ_A48

MDQ_A51

MDQ_A50

T34

T32

K34

K32

SDQ_A47

SDQ_A48

SDQ_A49

SDQ_A50

SDQ_B26

SDQ_B27

SDQ_B28

SDQ_B29

AF27

AJ26

AJ27

AD25

MDQ_B27

MDQ_B30

MDQ_B28

MDQ_B29

R143 31.6KR1%

R145 10.2KR1%R283 10.2KR1%

R166 10.2KR1%

R146 31.6KR1%

MDQ_A52

MDQ_A53

T31

P34

SDQ_A51

SDQ_A52

SDQ_A53

SDQ_B30

SDQ_B31

SDQ_B32

AF28

AE30

MDQ_B31

MDQ_B32

MDQ_A56

MDQ_A55

MDQ_A54

L34

L33

J33

SDQ_A54

SDQ_A55

SDQ_B33

SDQ_B34

AC27

AC30

Y29

MDQ_B33

MDQ_B35

MDQ_B34

MDQ_A57

MDQ_A58

H34

E33

SDQ_A56

SDQ_A57

SDQ_A58

SDQ_B35

SDQ_B36

SDQ_B37

AE31

AB29

MDQ_B37

MDQ_B36

MDQ_A59

MDQ_A61

MDQ_A60

F33

K31

J34

SDQ_A59

SDQ_A60

SDQ_B38

SDQ_B39

AA26

AA27

AA30

MDQ_B38

MDQ_B40

MDQ_B39

MCKE_A1

MCKE_A0

MDQ_A62

MDQ_A63

G34

F34

AL20

AN19

SCKE_A0

SDQ_A61

SDQ_A62

SDQ_A63

SDQ_B40

SDQ_B41

SDQ_B42

SDQ_B43

SDQ_B44

W30

U27

T25

AA31

V29

MDQ_B44

MDQ_B45

MDQ_B41

MDQ_B43

MDQ_B42

VCC_DDR_C2

R35

4

MCKE_A3

MCKE_A2

AM20

AP20

SCKE_A1

SCKE_A2

SCKE_A3

SDQ_B45

SDQ_B46

SDQ_B47

U25

R27

MDQ_B47

MDQ_B46

4

AB25

AC25

VCCA_DDR

SDQ_B48

SDQ_B49

P29

R30

K28

MDQ_B49

MDQ_B48

MDQ_B50

VCCA_DDR

AC26

AL35

VCCA_DDR

VCCA_DDR

VCCA_DDR

SDQ_B50

SDQ_B51

SDQ_B52

L30

R31

R26

MDQ_B53

MDQ_B52

MDQ_B51

AN4

AM3

AN5

VCC_DDR

VCC_DDR

SDQ_B53

SDQ_B54

SDQ_B55

P25

L32

K30

MDQ_B55

MDQ_B56

MDQ_B54

0.1uC200

AM5

AM6

AM7

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

SDQ_B56

SDQ_B57

SDQ_B58

SDQ_B59

H29

F32

G33

MDQ_B59

MDQ_B57

MDQ_B58

VCCA_DDR

C239

0.1u

VCC_DDR

AM8

AN2

AN6

VCC_DDR

VCC_DDR

SDQ_B60

SDQ_B61

N25

M25

J29

MDQ_B62

MDQ_B61

MDQ_B60

AN7

P3P6P8

N35

N32

VSS

VSS

VCC_DDR

VCC_DDR

SDQ_B62

SDQ_B63

SCKE_B0

SCKE_B1

G32

AK19

AF19

AG19

MCKE_B2

MDQ_B63

MCKE_B0

MCKE_B1

L10 1U1_1206

+

EC29

CD100U10EL7

ALE

3

SCS_B0#

VSS

VSS

VSS

SCS_B1#

SCS_B2#

SCS_B3#

SRAS_B#

SCAS_B#

SWE_B#

SMAA_B0

SMAA_B1

SMAA_B2

SMAA_B3

SMAA_B4

SMAA_B5

SMAA_B6

SMAA_B7

SMAA_B8

SMAA_B9

SMAA_B10

SMAA_B11

SMAA_B12

SMAB_B1

SMAB_B2

SMAB_B3

SMAB_B4

SMAB_B5

SBA_B0

SBA_B1

SDM_B0

SDM_B1

SDM_B2

SDM_B3

SDM_B4

SDM_B5

SDM_B6

SDM_B7

SDQS_B0

SDQS_B1

SDQS_B2

SDQS_B3

SDQS_B4

SDQS_B5

SDQS_B6

SDQS_B7

SCMDCLK_B0

SCMDCLK_B0#

SCMDCLK_B1

SCMDCLK_B1#

SCMDCLK_B2

SCMDCLK_B2#

SCMDCLK_B3

SCMDCLK_B3#

SCMDCLK_B4

SCMDCLK_B4#

SCMDCLK_B5

SCMDCLK_B5#

SMYRCOMP

SMYCOMPVOH

SMYCOMPVOL

SMVREF_B

SCKE_B2

SCKE_B3

INTEL-SpringDale

CRITICAL

AE18

MCKE_B3

3

Its current is 5.1A.

U26

T29

V25

W25

W26

W31

W27

MA_B0

AG31

AJ31

MA_B1

MA_B2

AD27

MA_B3

AE24

MA_B4

AK27

MA_B5

AG25

AL25

MA_B6

MA_B7

AF21

MA_B8

AL23

MA_B9

AJ22

MA_B10

AF29

AL21

MA_B11

MA_B12

AJ20

MAB_B1

AE27

MAB_B2

AD26

AL29

MAB_B3

MAB_B4

AL27

MAB_B5

AE23

Y25

AA25

MDQM_B0

AG11

MDQM_B1

AG15

AE21

MDQM_B2

MDQM_B3

AJ28

MDQM_B4

AC31

MDQM_B5

U31

MDQM_B6

M29

J31

MDQM_B7

MDQS_B0

AF15

MDQS_B1

AG13

MDQS_B2

AG21

AH27

MDQS_B3

MDQS_B4

AD29

MDQS_B5

U30

MDQS_B6

L27

MDQS_B7

J30

AG29

AG30

AF17

AG17

N27

N26

AJ30

AH29

AK15

AL15

N31

N30

AA33

YRCOMP

YCOMPH

R34

YCOMPL

R33

AP9

YVREF

MCKE_B[0..3] (10)

VCC_AGP

MCS_B#0 (10)

MCS_B#1 (10)

MCS_B#2 (10)

MCS_B#3 (10)

MRAS_B# (10)

MCAS_B# (10)

MWE_B# (10)

MBA_B0 (10)

MBA_B1 (10)

MCLK_B0 (10)

MCLK_B#0 (10)

MCLK_B1 (10)

MCLK_B#1 (10)

MCLK_B2 (10)

MCLK_B#2 (10)

MCLK_B3 (10)

MCLK_B#3 (10)

MCLK_B4 (10)

MCLK_B#4 (10)

MCLK_B5 (10)

MCLK_B#5 (10)

C0.01U50XC160

C0.01U50XC159

C0.01U50XC132

Title

Size Document Number Rev

Date: Sheet of

2

MA_B[0..12] (10)

MAB_B[1..5] (10)

MDQM_B[0..7] (10)

MDQS_B[0..7] (10)

R291 150R1%

R286 150R1%

MSI

星期四, 二月

27, 2003

2

1

VCC_DDR

6.3V

MICRO-STAR INt'L CO., LTD.

Intel Springdale - Memory Signals

6772

7 26

1

0A

8

AE6

GAD[0..31](17)

D D

VCC_AGP

VCC_AGP

GC_BE#[0..3](17)

ST[0..2](17)

GDEVSEL#(17)

SBA[0..7](17)

R243 43.2R1%

R345 226R1%

R344 147R1%

R342 113R1%

8

AD_STB0(17)

AD_STB#0(17)

AD_STB1(17)

AD_STB#1(17)

GGNT#(17)

GFRAME#(17)

GIRDY#(17)

GTRDY#(17)

GSTOP#(17)

MCH_66(14)

SB_STB(17)

SB_STB#(17)

DBI_LO(17)

C0.01U50XC251

GSWING(17)

C0.01U50XC265

AGP_REF(17)

C C

B B

A A

GAD0

GAD1

AC11

AD5

GAD3

AE5

GAD4

AA10

AC9

GAD5

GAD6

AB11

GAD7

AB7

GAD8

AA9

GAD9

AA6

AA5

GAD10

GAD11

W10

GAD12

AA11

GAD13

W6

GAD14

W9

V7

GAD15

GAD16

AA2

GAD17

Y4

GAD18

Y2

GAD19

W2

Y5

GAD20

GAD21

V2

GAD22

W3

GAD23

U3

GAD24

T2

T4

GAD25

GAD26

T5

GAD27

R2

GAD28

P2

GAD29

P5

P4

GAD30

GAD31

M2

GC_BE#0

Y7

GC_BE#1

W5

AA3

GC_BE#2

GC_BE#3

U2

AC6

AC5

V4

V5

N6

M7

ST0

N3

ST1

N5

ST2

N2

RBF#

RBF#(17)

WBF#(17)

GPAR(17)

PIPE#(17)

R10

WBF#

R9

U6

V11

AB5

AB4

W11

AB2

H4

SBA0

R6

P7

SBA1

SBA2

R3

SBA3

R5

SBA4

U9

SBA5

U10

U5

SBA6

SBA7

T7

U11

T11

M4

M5

GRCOMP

AC2

AC3

GSWING

AD2

H_SWING=(0.8*VCC_AGP)+-2%

C317 0.1u

C324 0.1u

H_SWING=(0.233*VCC_AGP)+-2%

7

U10C

GAD0/DVOB_HSYNC

GAD1/DVOB_VSYNC

GAD2/DVOB_D1

GAD3/DVOB_D0

GAD4/DVOB_D3

GAD5/DVOB_D2

GAD6/DVOB_D5

GAD7/DVOB_D4

GAD8/DVOB_D6

GAD9/DVOB_D9

GAD10/DVOB_D8

GAD11/DVOB_D11

GAD12/DVOB_D10

GAD13/DVOBC_CLKINT

GAD14/DVOB_FLDSTL

GAD15/MDDC_DATA

GAD16/DVOC_VSYNC

GAD17/DVOC_HSYNC

GAD18/DVOC_BLANK#

GAD19/DVOC_D0

GAD20/DVOC_D1

GAD21/DVOC_D2

GAD22/DVOC_D3

GAD23/DVOC_D4

GAD24/DVOC_D7

GAD25/DVOC_D6

GAD26/DVOC_D9

GAD27/DVOC_D8

GAD28/DVOC_D11

GAD29/DVOC_D10

GAD30/DVOBC_INTR#

GAD31/DVOC_FLDSTL

GCBE0/DVOB_D7

GCBE1/DVOB_BLANK#

GCBE2

GCBE3/DVOC_D5

GADSTBF0/DVOB_CLK

GADSTBS0/DVOB_CLK#

GADSTBF1/DVOC_CLK

GADSTBS1/DVOC_CLK#

GREQ

GGNT

GST0

GST1

GST2

GRBF

GWBF

GFRAME/MDVI_DATA

GIRDY/MI2CCLK

GTRDY/MDVI_CLK

GDEVSEL/MI2CDATA

GSTOP/MDDC_CLK

GPAR/ADD_DETECT

GCLKIN

GSBA0#/ADD_ID0

GSBA1#/ADD_ID1

GSBA2#/ADD_ID2

GSBA3#/ADD_ID3

GSBA4#/ADD_ID4

GSBA5#/ADD_ID5

GSBA6#/ADD_ID6

GSBA7#/ADD_ID7

GSBSTBF

GSBSTBS

DBI_HI

DBI_LO

GRCOMP/DVOBC_RCOMP

GVSWING

GVREF

VSS

VSS

VSS

AE1

AD30

AD33

AD28

HL_SWING

HL_SWING

HL_VREF

HL_VREF

7

P26

P27

P9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AE10

AE11

AE12

AE13

AE4

800mV

HL_SWING (13)

350mV

HL_VREF (13)

VSS

VSS

P28

AE25

P30

VSS

VSS

AE26

P33R1R4

VSS

VSS

AE32

VSS

VSS

AE35

6

R32T1T3

T6T8T9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AF3

AF11

AF14

AF6

AF9

VSS

VSS

AF16

VSS

VSS

AF18

T10

VSS

VSS

AF20

VCCP

VSS

VSS

T26

AF22

VSS

VSS

T27

AF24

VSS

VSS

6

T28

AF25

VSS

VSS

T30

AF30

T33

VSS

VSS

AF33

VSS

VSS

C156

0.1u

T35

VSS

VSS

AG4

U4

AG8

VSS

VSS

U18

VSS

VSS

AG14

V6

U19

U32V3V8V9V10

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AG16

AG18

AG20

AG22

AG24

VSS

VSS

C260

0.1u

AG26

VSS

VSS

AG28

VSS

VSS

V17

AG32

VSS

VSS

V19

VSS

VSS

AG35

V26

AH3

V27

VSS

VSS

AH6

V28

V30W4W17

VSS

VSS

VSS

VSS

VSS

VSS

AH12

AH10

V33

AH14

VSS

VSS

VSS

VSS

AH16

5

Y3

W18

W32Y6Y8Y9Y26

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AH18

AH20

AH22

AH24

AH30

5

Y28

Y30

Y33

Y35

Y27

AA1

AA4

AA32

AB10

AB26

AB3

AB6

AB8

VSS

VSS

AH33

Y10

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AK3

AJ1

AJ4

AJ9

AJ32

AJ35

AK8

AK10

VSS

VSS

AK12

VSS

VSS

AK14

VSS

VSS

AK16

VSS

VSS

AK18

VSS

VSS

AK20

VSS

VSS

AK22

VSS

VSS

AB9

AK24

VSS

VSS

AK26

VSS

VSS

AK28

Springdale Decoupling Capacitors

4

AB27

AB28

VSS

VSS

VSS

VSS

AL1

AL32

VCC_DDR

4

AB30

VSS

VSS

AM9

AB33

VSS

VSS

AM11

AC1

VSS

VSS

AM13

C243 0.1u

AC4

AC32

AC35

AD3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AM15

AM17

AM19

AM21

C264

0.1u

C261

0.1u

VSS

VSS

AD6

AM23

VSS

VSS

AD8

AM25

VSS

VSS

AD9

AM27

VSS

VSS

AD10

AM29

VSS

VSS

AM35

VSS

AN10

3

C266 0.1u

VCC_AGP

L1L5Y1J1J2J3K2K3K4K5J4J5L4L2L3

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AN12

AN14

AN16

AN18

AN20

AN22

AN24

AN26

3

AN28

AN30

AN32

AR9

VCC_AGP

VCC_AGP

VCC_AGP

VSS

VSS

VSS

AR11

AR13

AR16

VTTVCC_AGP

AG1

Y11

HI0

HI1

HI2

VCCA_AGP

VCCA_AGP

HI3

HI4

HI5

HI6

HI7

HI8

HI9

HI10

HI_STRF

HI_STRS

HI_RCOMP

HI_SWING

HI_VREF

CI0

CI1

CI2

CI3

CI4

CI5

CI6

CI7

CI8

CI9

CI10

CISTRF

CISTRS

CI_RCOMP

CI_SWING

CI_VREF

DREFCLK

DDCA_CLK

DDCA_DATA

VSYNC

HSYNC

BLUE

BLUE#

GREEN

GREEN#

RED

RED#

REFSET

VCC_DAC

VCC_DAC

VCCA_DAC

VSSA_DAC

EXTTS#

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

VSS

VSS

VSS

VSS

VSS

VSS

VSS

INTEL-SpringDale

AR23

AR20

CRITICAL

AF5

AG3

AK2

AG5

AK5

AL3

AL2

AL4

AJ2

AH2

AJ3

AH5

AH4

AD4

AE3

AE2

AK7

AH7

AD11

AF7

AD7

AC10

AF8

AG7

AE9

AH9

AG6

AJ6

AJ5

AG2

AF2

AF4

G4

F2

H3

E2

G3

H7

G6

H6

G5

F4

E4

D2

G1

G2

C0.01U50X

C2

D3

AP8

AG9

AG10

AN35

AP34

AR1

AR25

AR27

AR29

AR32

C195

C1U10Y

C201

0.1u

2

VCC_AGP

C228

0.1u

C222

0.1u

HL0

HL1GAD2

HL2

HL3

HL4

HL5

HL6

HL7

HL8

HL9

HL10

HL_COMP

HL_SWING

HL_VREF

CI_RCOMP

CI_SWING

CI_VREF

GSET

R220 137R1%

C217

C213

C0.01U50X

Title

Size Document Number Rev

Date: Sheet of

HL[0..10] (13)

HI_RCOMP Calculation

R=[(1.5V-08V)/0.8V]*60ohm=52.5ohm

HL_STRF (13)

HL_STRS (13)

R261 52.3R1%

C0.01U50XC252

C0.01U50XC282

R270 52.3R1%

DOT_48 (14)

3VDDCCL (19)GREQ#(17)

3VDDCDA (19)

CRT_VSYNC (19)

CRT_HSYNC (19)

CRT_B (19)

CRT_G (19)

CRT_R (19)

VCC3

VCCA_DAC

VCC_AGP

MSI

VCC_AGP

VCC_AGP

C0.01U50XC250

C0.01U50XC276

L9 100N300m

+

EC27

XX

R262 226R1%

R255 147R1%

R281 113R1%

MICRO-STAR INt'L CO., LTD.

Intel Springdale - AGP & HLink & LAN Signals

27, 2003

6772

2

星期四, 二月

1

R237 0R

CI_SWING

CI_VREF

1

VCC_DAC

1.7V/60mA

8 26

800mV

350mV

0A

Loading...

Loading...