5

4

3

2

1

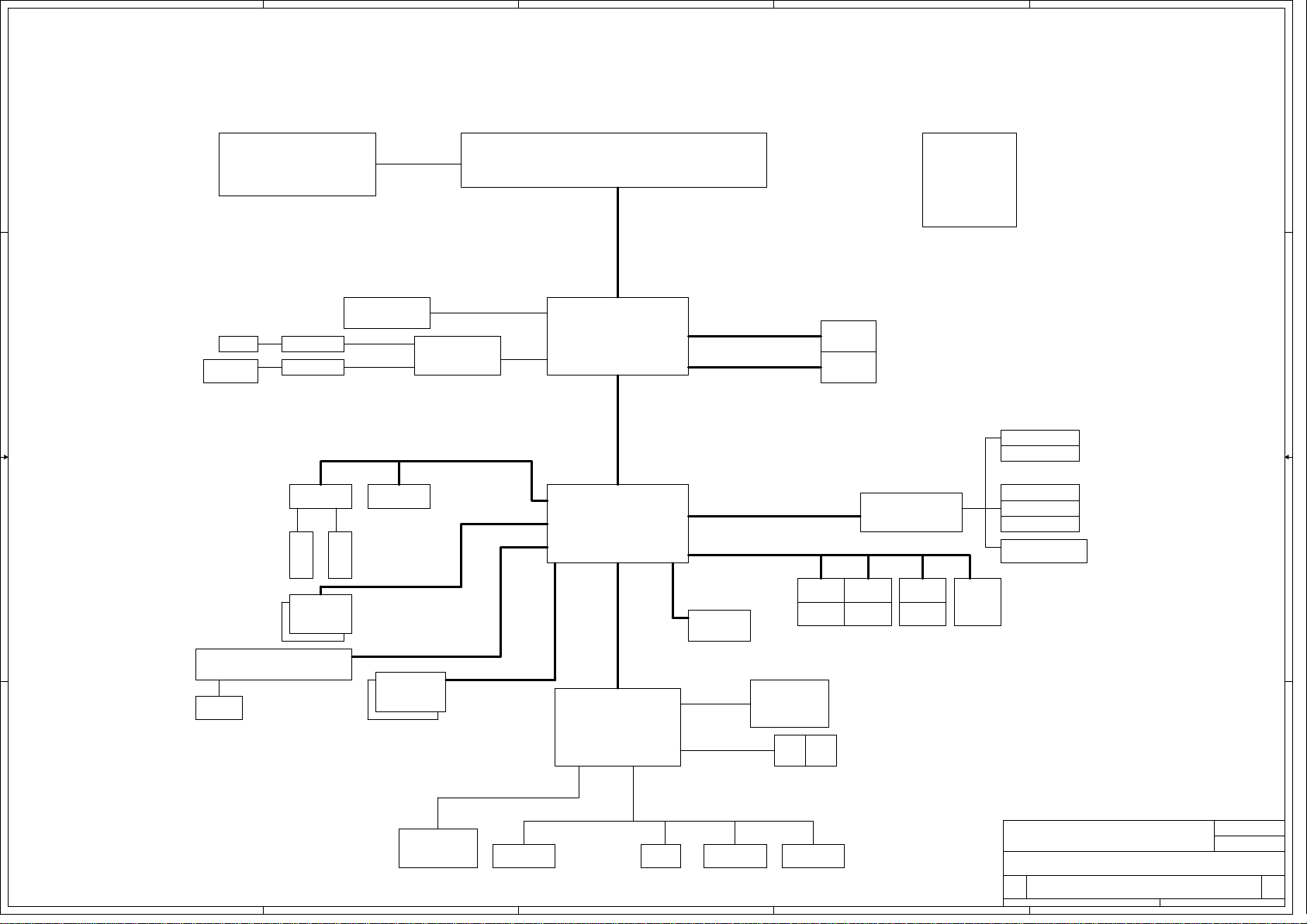

Cover Sheet

Block Diagram

D D

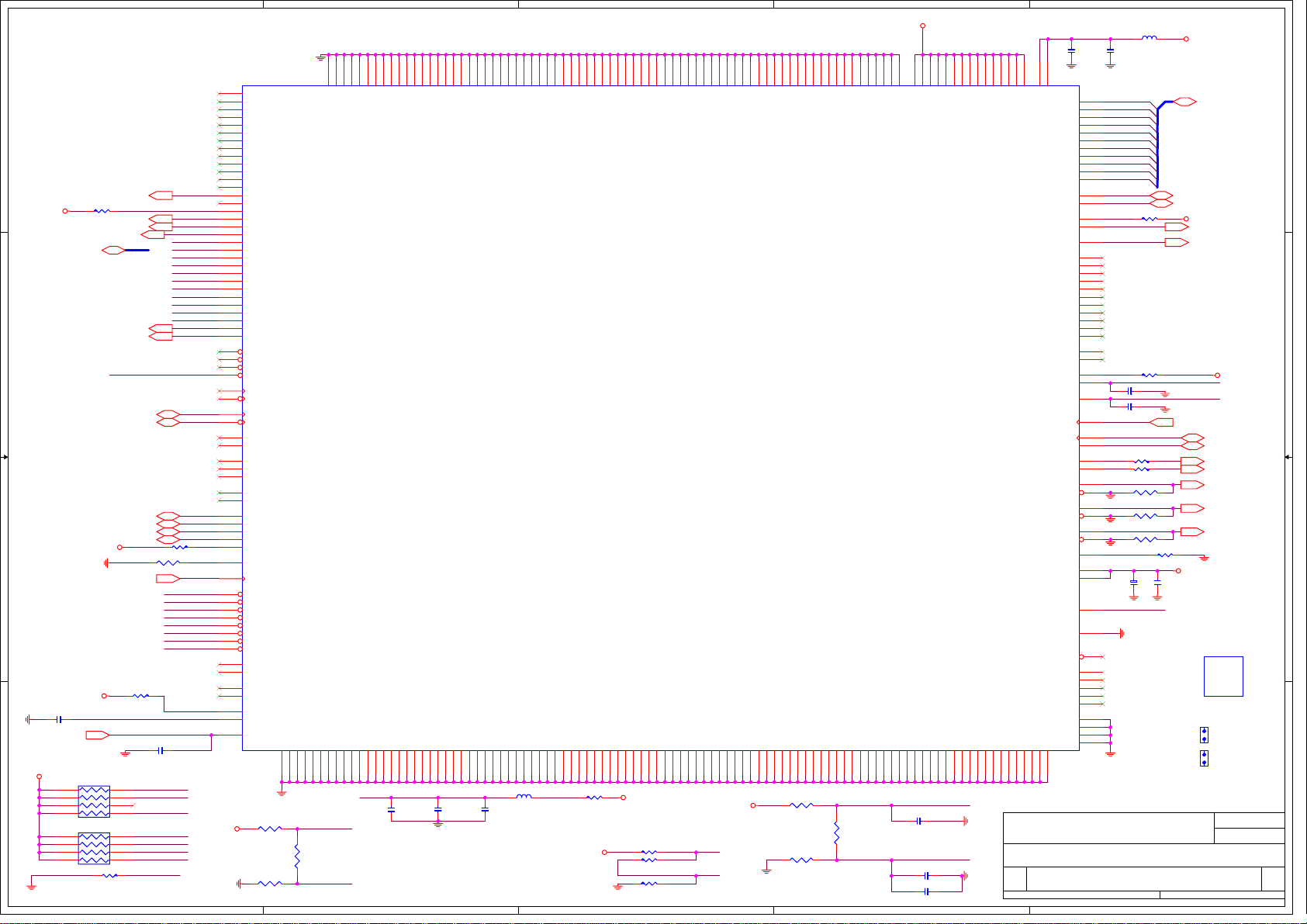

CLOCK ICS952619 / IDE & SATA Connectors

mPGA478-B INTEL CPU Sockets

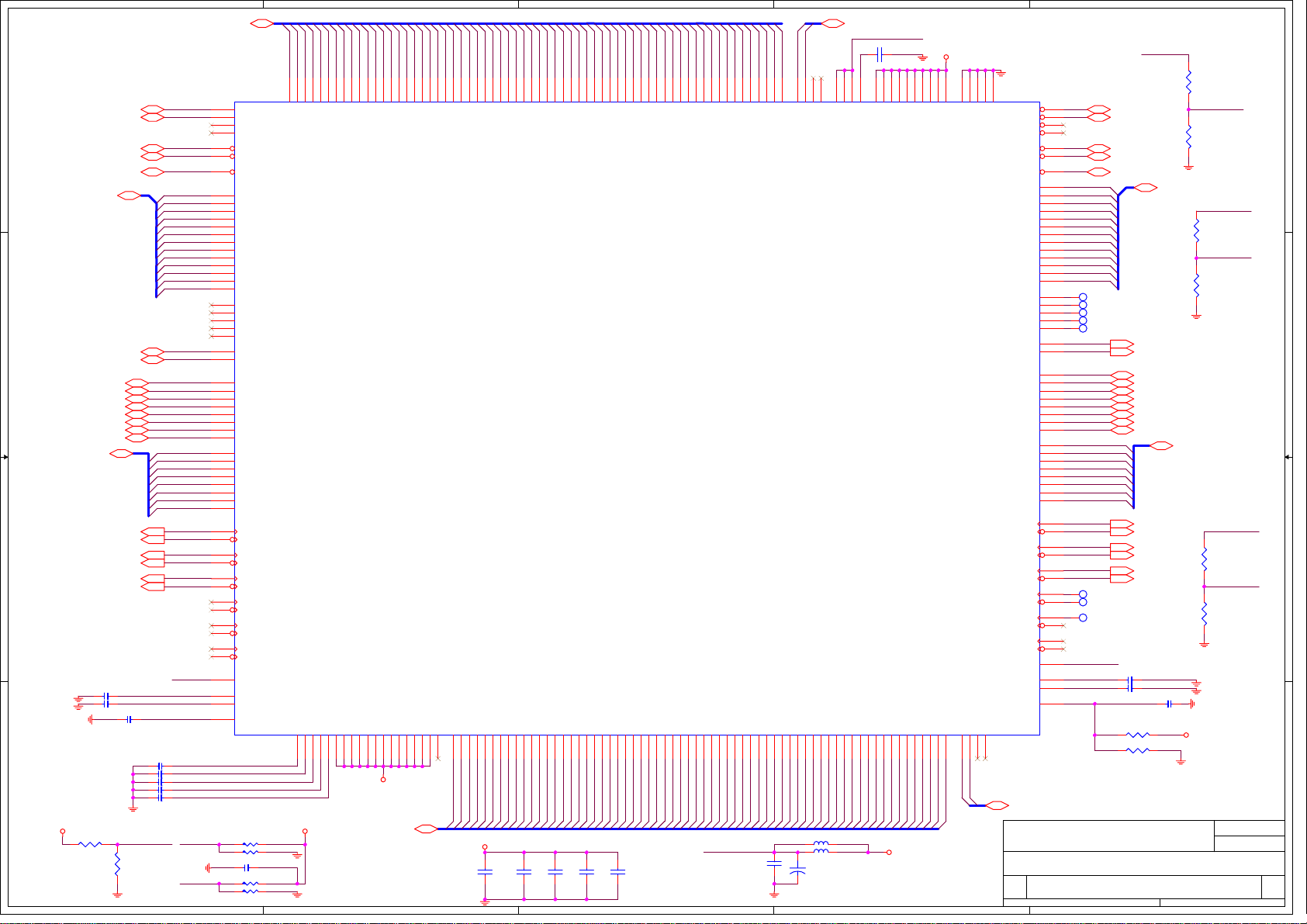

INTEL Springdale GMCH

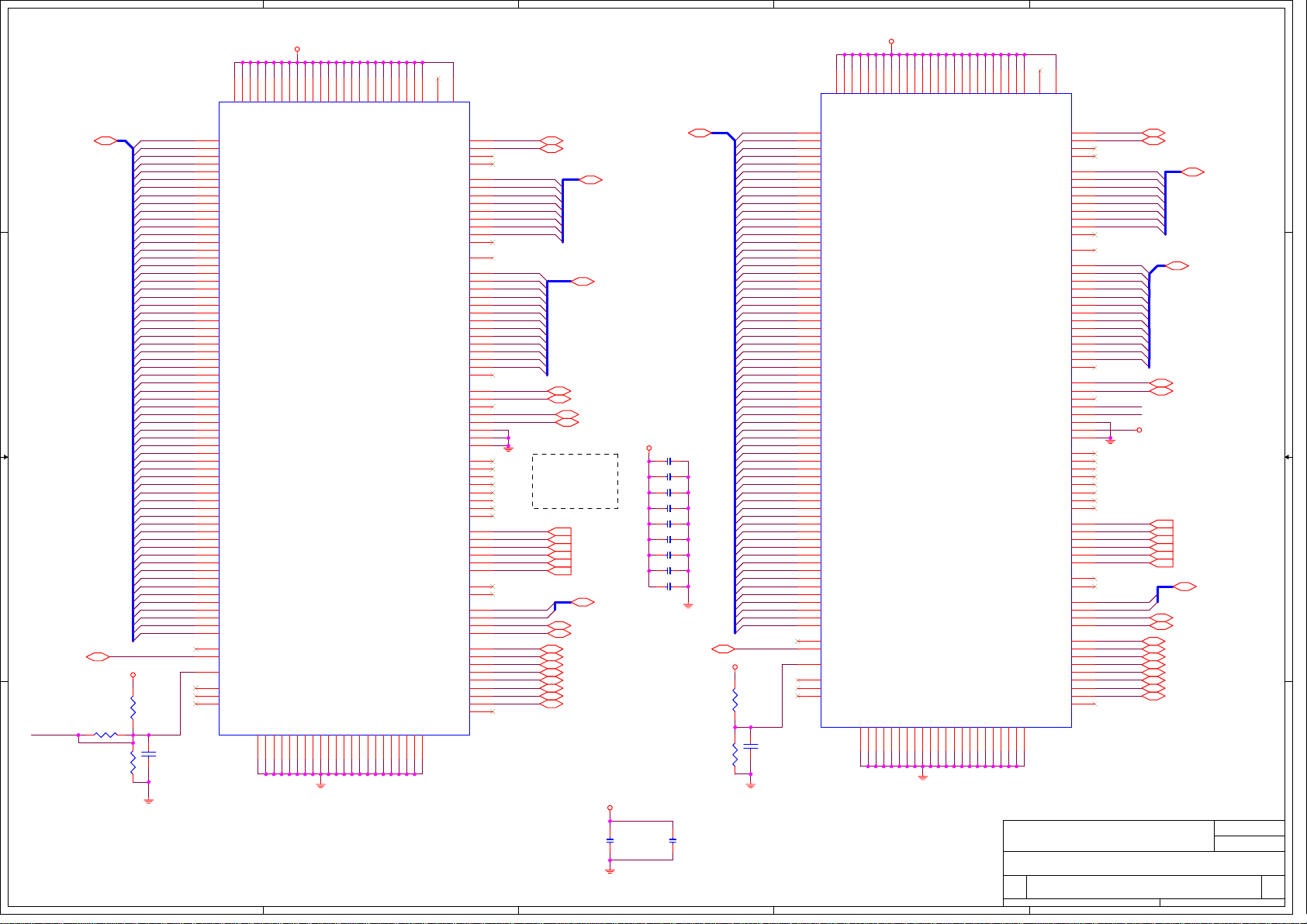

DDR SLOT

DDR TERMINATOR

CH7009

VGA , DVI and TV OUT connectors

INTEL ICH5

1

2

3

4 - 5

6 - 8

9

10

11

12

13,14

MS-6765

VERSION:1.0

STD:

INTEL Springdale GMCH + ICH5 + 10/100LAN

OPTION A:

INTEL Springdale GMCH + ICH5 + gigabit LAN

CPU:

Prescott mPGA-478B Processor

System Chipset:

INTEL Springdale GMCH + ICH5

PCI SLOT / FWH 15

C C

AC'97 CODEC

AUDIO CONNEC TOR S and SMBus Isolation

USB PORT

2-PORT IEEE1394 - NEC_uPD72874

LPC I/O(SMsC LPC47M133) and LM86

COM & LPT & FDD & FAN

LAN connector

ATX Connector , Front Connector and PS2 connector

VRM 10.0 Intersil 6556B

B B

ACPI CONTRO LLE R W8 3302 MS-5

GMCH VTT power

GPIO setting

ALC650 + SPDIF

16

17

18

19

20

21

22LAN Broadcom 10/100 and gigabit LAN

23

24

25

26

27

28

On Board Chip:

Expansion Slots:

LPC Super I/O -- SMsC LPC47M133

BIOS -- FWH

AC' 97 CODE C -- ALC650

CLOCK GENERATION --ICS952619

LAN -- Broadcom

DVO -- CH7009 DV+

TV-OUT

1394 -- NEC uPD72874(Optional)

PCI2.3 SLOT* 1 ( RISER CARD PCI*2 )

A A

Engineer

MICRO-STAR INt'L CO., LTD.

Title

Size Proj e ct Name Re v

C

5

4

3

2

Date: Sheet

COVER SHEET

MS-6765

1

Shun Min Hsu

Drawn by

Shun Min Hsu

1.0

of

282003/05/07

1

5

4

3

2

1

D D

System Block Diagram

VRM 10

Intersil 6556

Intel mPAG478B Processor

3-Phase PWM

400/533/800MHz

System Bus

VGA

CONNECTOR

C C

DVI-A

AV &

S-VIDEO

TMDS LCD

TV-OUT

IEEE

1394

PCI

SLOT 1

CH 7009A

IDE

PCI

REAR

B B

FRONT

2 IDE

Ports

33MHz@133MB/s

10/100 or gigabit LAN

2 SATA

RJ45

Ports

INTEL

Springdale GMCH

Hub Interface 1.5

266 MB/s

INTEL ICH5

LPC Bus

LPC Super

I/O SMSC

47M133

2.7 GB/s(DDR400)

2.7 GB/s(DDR400)

DDR SDRAM

AC'97

12.288MHz@1.536MB/s

USB2.0

240MHz@60MB/s

USB 0

FWH

FAN ON/OFF

CONTROL

KEYBOARD

PS/2

MOUSE

USB 1

FRONT PORT

FAN1 FAN2

DIMM 1

DIMM 2

USB 2

USB 3

Audio Codec

ALC650

Clock gen.

ICS952619

Audio port

USB 4

USB 5

REAR

PORT

USB 6

For USB

Card

Reader

FRONT

MIC-in

Line-out

REAR

MIC-in

Line-in

Line-out

SPDIF Out

A A

Engineer

2

Shun Min Hsu

Drawn by

Shun Min Hsu

1.0

282003/05/07

LM86

5

4

GPIOs

COM1 PARALLEL FLOPPY

3

2

MICRO-STAR INt ' L CO., LTD.

Title

Size Project Name Rev

A3

Date: Sheet of

System Block Diagram

MS-6765

1

5

4

3

2

1

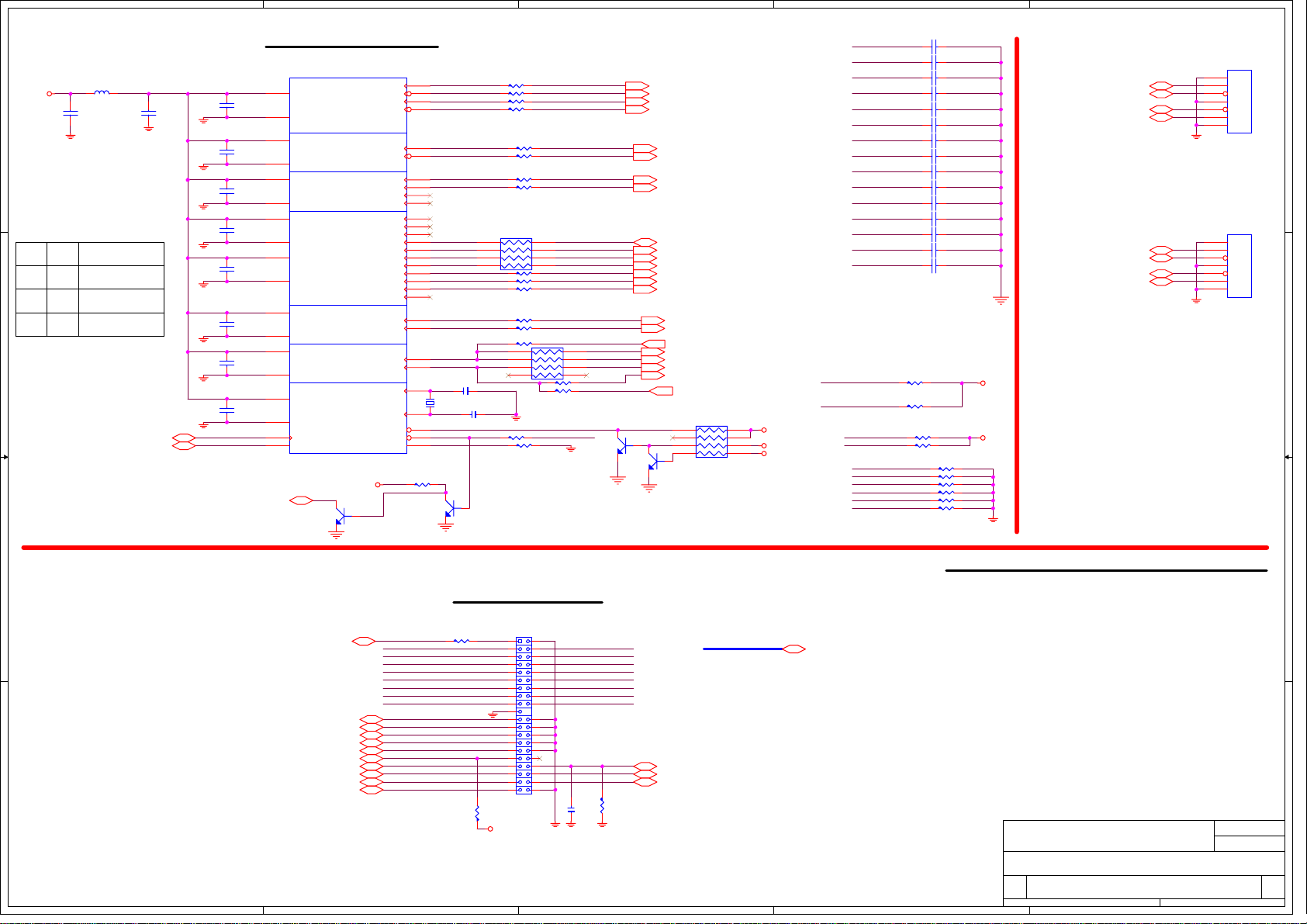

Clock Generator - ICS952619

U1

C7

10u-0805

CLK_VCC3

C5

0.1u-0603

C10

0.1u-0603

C14

0.1u-0603

C17

0.1u-0603

C21

0.1u-0603

C22

0.1u-0603

C23

0.1u-0603

C25

0.1u-0603

DBRESET#4,14,24

41

CPU_VDD

44

CPU_GND

35

SRC_VDD

38

SRC_GND

28

3V66_VDD

29

3V66_GND

10

PCI_VDD1

11

PCI_GND1

17

PCI_VDD2

18

PCI_GND2

25

48_VDD

24

48_GND

3

REF_VDD

6

REF_GND

48

VDD

47

GND

32

SCLK

33

SDATA

ICS952619_SSOP48

2N3904S

Q49

VCC3

D D

FB1 80L-0805

CB1

0.1u-0603

FS0 FS1 Frequency

010

C C

100MHz

0

133MHz

10

200MHz

SMBCLK_ISO17,26

SMBDATA_ISO17,26

CPU0

CPU0#

CPU1

CPU1#

SRC#

3V66_0

3V66_1

3V66_2

VCH/3V66_4

FS_2/PCI_F0

FS_4/PCI_F1

PCI_F2

FS_3/48M_0

SEL24_48#/24_48M

FS_A/REF0

FS_B/REF1

VTT_GD/PD#

VCC3

Trace length less than 0.5inchs

40

39

43

42

37

SRC

36

31

30

27

26

7

8

9

12

PCI0

13

PCI1

14

PCI2

15

PCI3

16

PCI4

19

PCI5

20

PCI6

21

PCI7

23

22

1

2

4

X1

5

X2

34

45

RST#

46

IREF

R415 1K-0603

2N3904S

Q48

12

34

56

78

MCHCLK

MCHCLK#

CPUCLK0

CPUCLK-0

SATA_100#

MCH_66

ICH_66

LAN_PCLK

PCICLK1

PCICLK2

FWH_PCLK

ICH_PCLK

SIO_PCLK

1394PCLK

12

34

56

78

CLK_VCC3

DOT_CLK

ICH_48

2N3904S

R1 33-0603

R2 33-0603

R3 33-0603

R4 33-0603

SATA100 SATA_100

R5 33-0603

SATA100#

R6 33-0603

MCH66

R7 33-0603

ICH66

R8 33-0603

RN1

33-8P4R

R9 33-0603

R10 33-0603

R11 33-0603

R12 33-0603

R13 33-0603

R14 10K-0603

FS_SEL0

RN2

FS_SEL1

33-8P4R

R400 33-0603

56p-0603C24

Y1

14M-32pf-HC49S-D

IREF

R15 10K-0603

56p-0603C26

R18 1K-0603

R20 475RST

SIO_14

ICH_14

ADO_14M

Q1

2N3904S

Q2

MCHCLK 6

MCHCLK# 6

CPUCLK0 4

CPUCLK-0 4

SATA_100 14

SATA_100# 14

MCH_66 7

ICH_66 14

LAN_PCLK 22

PCICLK1 15

PCICLK2 15

FWH_PCLK 15

ICH_PCLK 13

SIO_PCLK 20

1394PCLK 19

DOT_CLK 7

ICH_48 14

BSEL0 4,6,14

SIO_14 20

ICH_14 14

ADO_14M 16

VDI_CLK 11

BSEL1 4,6,14

RN3 8.2K-8P4R

1 2

3 4

5 6

7 8

VCC3

VCC3

VCCP

MCH_66

ICH_66

LAN_PCLK

PCICLK1

PCICLK2

FWH_PCLK

ICH_PCLK

SIO_PCLK

1394PCLK

DOT_CLK

ICH_48

SIO_14

ADO_14M

ICH_14

VDI_CLK

C1 X-0603-C

C2 X-0603-C

C3 X-0603-C

C4 X-0603-C

C6 X-0603-C

C8 X-0603-C

C9 X-0603-C

C11 X-0603-C

C12 X-0603-C

C13 X-0603-C

C15 X-0603-C

C16 X-0603-C

C18 X-0603-C

C19 X-0603-C

C20 X-0603-C

used only for EMI issue

SMBCLK_ISO

SMBDATA_ISO

BSEL0

BSEL1

MCHCLK

MCHCLK#

CPUCLK0

CPUCLK-0

SATA_100

SATA_100#

R16 4.7K-0603

R17 4.7K-0603

R19 1K-0603

R21 1K-0603

R22 49.9RST

R23 49.9RST

R24 49.9RST

R25 49.9RST

R26 49.9RST

R27 49.9RST

VCC3

VCC3

SATA1

1

GND

SATA_TX014

SATA_TX#014

SATA_RX#014

SATA_RX014

SATA_TX114

SATA_TX#114

SATA_RX#114

SATA_RX114

2

3

4

5

6

7

1

2

3

4

5

6

7

HT+

HTGND

HRHR+

GND

SATA

SATA2

GND

HT+

HTGND

HRHR+

GND

SATA

SERIAL ATA CONNECTOR

B B

PRIMARY IDE BLOCK

IDE1

HDRST#

HDRST#26

PD_DREQ13

PD_IOW#13

PD_IOR#13

PD_IORDY13

PD_DACK#13

IRQ1413

PD_A113

PD_A013

PD_CS#113

A A

5

PD_LED24

4

PDD7

PDD6

PDD5

PDD4

PDD3

PDD2

PDD1

PDD0

R29 33-0603

CN-BH-D2x20-1:21-BL-ZBT-S1

1

2

3 4

5 6

7 8

91110

12

13 14

1615

17 18

19

22

21

24

23

26

25

28

27

30

29

32

31

34

33

36

35

38

37

4039

R33

10K-0603

VCC3

PDD8

PDD9

PDD10

PDD11

PDD12

PDD13

PDD14

PDD15

C28

4700p-0603

R31

10K-0603

3

PD_DET 13

PD_A2 13

PD_CS#3 13

PDD[0..15] 13

2

ATA100 IDE CONNECTORS

* Trace Width : 5mils

* Trace Spacing : 7mils

* Length(longest)-Length(shortest)<0.5"

* Trace Length less than 6"

MICRO-STAR INt ' L CO., LTD.

Title

Clock Generator , IDE ,and SATA connectors

Size Project Name Rev

A3

Date: Sheet of

MS-6765

1

Engineer

Drawn by

3

Shun Min Hsu

Shun Min Hsu

1.0

282003/05/07

5

4

3

2

1

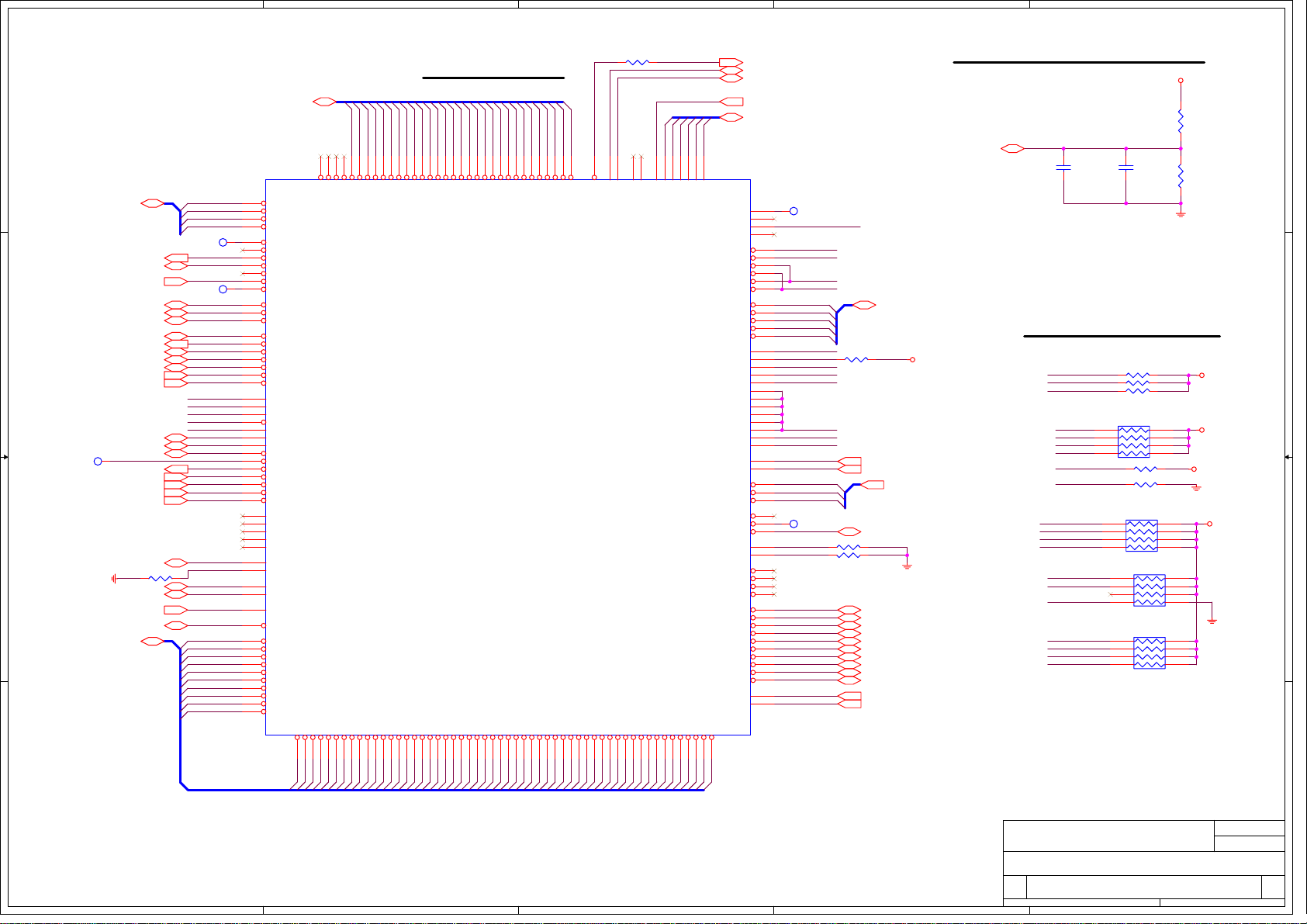

CPU GTL REFERNCE VOLTAGE BLOCK

Length < 1.5inch.

GTLREF16

GTLREF1

C29

220p-0603

Every pin put one 220pF cap near it.

Trace Width 15mils, Space 15mils.

Keep the voltage dividers within 1.5 inches of the

first GTLREF Pin

CPU STRAPPING RESISTORS

VCCP

ALL COMPONENTS CLOSE TO CPU

PROCHOT#

CPU_GD

HBR#0

BPM#0

BPM#1

BPM#5

BPM#4

ITP_TDI

ITP_TRST#

CPURST#

TESTHI12

TESTHI0

TESTHI2

ITP_TMS

ITP_TDO

ITP_TCK

TESTHI1

TESTHI10

TESTHI9

TESTHI8

VCCP

C30

0.1u-0603

R37 120-0603

R38 300-0603

R39 200-0603

RN4 62-8P4R

1 2

3 4

5 6

7 8

R40 150-0603

R41 680-0603

RN5

1 2

3 4

5 6

7 8

62-8P4R

RN6

1 2

3 4

5 6

7 8

62-8P4R

RN7

1 2

3 4

5 6

7 8

62-8P4R

R35

200RST

R36

169RST

VCCP

VCCP

VCCP

VCCP

AD26

D11#

G22

HD#10

AC26

ITP_CLK1

D10#

B25

HD#9

ITP_CLK0

D9#

DBRESET#

VID1

VID2

VID4

VID3

VID5

AE1

AE2

AE3

AE4

AD3

AD2

VID4#

VID3#

VID2#

VID5#

VIDPWRGD

D8#

D7#

D6#

D5#

D4#

D3#

B24

A25

C24

HD#8

A23

C23

D22

C21

HD#2

HD#4

HD#3

HD#5

HD#6

HD#7

DBRESET# 3,14,24

VCC_SENSE 25

VSS_SENSE 25

VID_GD 25,26

VID[0..5] 25

VID0

AE5

VID1#

D2#

VID0#

D1#

B22

HD#1

AA21

GTLREF0

AA6

GTLREF1

F20

GTLREF2

F6

GTLREF3

AB4

BPM5#

AA5

BPM4#

Y6

BPM3#

AC4

BPM2#

AB5

BPM1#

AC6

BPM0#

H3

REQ4#

J3

REQ3#

J4

REQ2#

K5

REQ1#

J1

REQ0#

AD25

TESTHI12

A6

TESTHI11

Y3

TESTHI10

W4

TESTHI9

U6

TESTHI8

AB22

TESTHI7

AA20

TESTHI6

AC23

TESTHI5

AC24

TESTHI4

AC20

TESTHI3

AC21

TESTHI2

AA2

TESTHI1

AD24

TESTHI0

AF23

BCLK1#

AF22

BCLK0#

F4

RS2#

G5

RS1#

F1

RS0#

V5

AP1#

AC1

AP0#

H6

BR0#

P1

COMP1

L24

COMP0

L25

DP3#

K26

DP2#

K25

DP1#

J26

DP0#

R5

ADSTB1#

L5

ADSTB0#

W23

DSTBP3#

P23

DSTBP2#

J23

DSTBP1#

F21

DSTBP0#

W22

DSTBN3#

R22

DSTBN2#

K22

DSTBN1#

E22

DSTBN0#

E5

LINT1/NMI

D1

LINT0/INTR

D0#

NORTHWOOD/PRESCOTT

CRITICAL

B21

HD#0

1

.

HREQ#4

HREQ#3

HREQ#2

HREQ#1

HREQ#0

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI2

TESTHI1

TESTHI0

HRS#2

HRS#1

HRS#0

1

.

COMP1

COMP0

TP1

GTLREF1

BPM#5

BPM#4

BPM#1

BPM#0

R391 62-0603

TP10

R42 61.9RST

R43 61.9RST

HREQ#[0..4] 6

CPUCLK-0 3

CPUCLK0 3

HRS#[0..2] 6

HBR#0 6

HADSTB#1 6

HADSTB#0 6

HDSTBP#3 6

HDSTBP#2 6

HDSTBP#1 6

HDSTBP#0 6

HDSTBN#3 6

HDSTBN#2 6

HDSTBN#1 6

HDSTBN#0 6

NMI 14

INTR 14

CPU SIGNAL BLOCK

R34 X-0603-R

HA#[3..31]6

D D

HA#9

HA#8

HA#5

HA#6

HA#7

HA#4

A9#L2A8#M6A7#L3A6#K1A5#L6A4#K4A3#

D24#

D23#

D22#

D21#

L21

F26

F24

E25

D26

HD#23

HD#21

HD#22

HD#20

HD#24

D20#

F23

HD#19

HA#3

K2

D19#

G23

HD#18

D18#

E24

HD#17

D17#

H22

HD#16

AE25

D16#

D25

HD#15

DBR#

D15#

J21

HD#14

A5

D14#

D23

HD#13

A4

VCC_SENSE

D13#

C26

HD#12

VSS_SENSE

D12#

H21

HD#11

HA#31

HA#28

HA#30

HA#29

HA#25

HA#24

HA#26

HA#27

HA#22

HA#23

HA#21

HA#18

HA#17

HA#20

HA#19

HA#16

HA#15

HA#14

HA#12

HA#13

HA#11

HA#10

CPU1A

HDBI#[0..3]6

FERR#14

STPCLK#14

HINIT#14,15

HDBSY#6

HDRDY#6

HTRDY#6

HADS#6

1

.

HD#[0..63]6

HLOCK#6

HBNR#6

HIT#6

HITM#6

HBPRI#6

HDEFER#6

CPU_TMPA20

VTIN_GND20

TRMTRIP#14

PROCHOT#6,14

IGNNE#14

HSMI#14,20

A20M#14

CPUSLP#14

BOOT25,27

R44 X-0603-R

BSEL03,6,14

BSEL13,6,14

CPU_GD14

CPURST#6

C C

TP8

B B

A A

HDBI#0

HDBI#1

HDBI#2

HDBI#3

ITP_TDI

ITP_TDO

ITP_TMS

ITP_TRST#

ITP_TCK

CPU_TMPA

TRMTRIP#

PROCHOT#

IGNNE#

HSMI#

A20M#

CPUSLP#

OPTIMIZ

BSEL0

BSEL1

CPU_GD

CPURST#

HD#63

HD#62

HD#61

HD#60

HD#59

HD#58

HD#57

HD#56

HD#55

HD#54

E21

DBI0#

G25

DBI1#

P26

DBI2#

V21

DBI3#

1

AC3

TP4

.

TP7

.

V6

B6

Y4

AA3

W5

AB2

1

H5

H2

J6

G1

G4

G2

F3

E3

D2

E2

C1

D5

F7

E6

D4

B3

C4

A2

AF26

C3

B2

B5

C6

AB26

A22

A7

AE21

AF24

AF25

AD1

AE26

AD6

AD5

AB23

AB25

AA24

AA22

AA25

Y21

Y24

Y23

W25

Y26

W26

V24

IERR#

MCERR#

FERR#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

SLP#

RESERVED0

RESERVED1

RESERVED2

RESERVED3

RESERVED4

BOOTSELECT

OPTIMIZED/COMPAT#

BSEL0

BSEL1

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

AB1

A35#

A34#Y1A33#W2A32#V3A31#U4A30#T5A29#W1A28#R6A27#V2A26#T4A25#U3A24#P6A23#U1A22#T2A21#R3A20#P4A19#P3A18#R2A17#T1A16#N5A15#N4A14#N2A13#M1A12#N1A11#M4A10#

D53#

D52#

D51#

D50#

D49#

D48#

D47#

D46#

D45#

D44#

D43#

D42#

D41#

D40#

D39#

D38#

D37#

D36#

D35#

T23

T22

T25

V22

V25

U21

U23

HD#50

HD#53

HD#51

HD#52

T26

U24

U26

HD#47

HD#49

HD#48

P24

R24

R25

R21

HD#40

HD#42

HD#41

HD#43

HD#44

HD#45

HD#46

P21

N25

N26

N23

M26

M24

HD#34

HD#38

HD#37

HD#35

HD#39

HD#36

D34#

N22

HD#33

D33#

M23

HD#32

D32#

H25

HD#31

D31#

K23

HD#30

D30#

J24

HD#29

D29#

L22

HD#28

D28#

M21

HD#27

D27#

HD#26

H24

M3

D26#

G26

HD#25

D25#

Engineer

4

Shun Min Hsu

Drawn by

Shun Min Hsu

1.0

282003/05/07

MICRO-STAR INt ' L CO., LTD.

Title

Size Project Name Rev

A3

5

4

3

2

Date: Sheet of

Intel mPGA478B Signals

MS-6765

1

5

4

3

2

1

AF4

VCC-VID

VSS

VSSH4VSSJ2VSS

1.2V 150mA

VCC_VID

CPU_IOPLL

AE23

AF3

AD20

VCCA

VSSA

VCC-IOPLL

VCC-VIDPRG

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSJ5VSS

NORTHWOOD/PRESCOTT

J22

J25

K21

CRITICAL

AD22

Y5

Y25

Y22

Y2

W6

W3

W24

W21

V4

V26

V23

V1

U5

U25

U22

U2

T6

T3

T24

T21

R4

R26

R23

R1

P5

P25

P22

P2

N6

N3

N24

N21

M5

M25

M22

M2

L4

L26

L23

L1

K6

K3

K24

C33

22u-1206

VSSA

It must close bulk caps.

It support DC current if 100mA.

L1 10uH-0805-100mA

L2 10uH-0805-100mA

C34

X-0805-C

DC voltage drop should

be less than 70mV.

VCCP

VCC_VID

CPU VOLTAGE BLOCK

It is derived from 3.3V.

D D

VCCP

A10

A12

A14

A16

A18

A20

AA10

AA12

AA14

AA16

AA18

AA8

AB11

AB13

AB15

AB17

AB19

AB7

AB9

AC10

AC12

VCC

VSS

AE9

VCC

VSS

AF1

VCC

VSS

AC14

VCC

VCC

VCC

VSS

VSS

VSS

AF10

AF12

AF14

AF16

CPU1B

VCC

VCC

VCC

VCC

VCC

VCC

VCCA8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

D10

VSS

A11

VSS

A13

VSS

A15

VSS

A17

VSS

A19

VSS

A21

VSS

A24

VSS

A26

VSS

A3

VSS

A9

VSS

AA1

VSS

AA11

VSS

AA13

VSS

AA15

C C

B B

AA17

AA19

AA23

AA26

AA4

AA7

AA9

AB10

AB12

AB14

AB16

AB18

AB20

AB21

AB24

AB3

AB6

AB8

AC11

AC13

AC15

AC17

AC19

AC2

AC22

AC25

AC5

AC7

AC9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AD4

AD8

AD10

AD12

AD14

AD16

AE11

AD18

AD21

AD23

VCC

VSS

VSS

VSS

VSS

VSS

VSS

AE13

AE7

AE15

AE17

AE19

AE22

AE24

It should be able to source 150mA.

It drives th e p ower logic of BSEL[1:0] and VID[5:0].

VID to VIDGD delay time is from 1ms to 10ms.

VID to VIDGD deassertion time is 1ms for max.

AC16

AC18

AC8

AD11

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

AE16

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSB4VSSB8VSS

B10

B12

B14

B16

B18

B23

B20

AF6

AF8

AF18

AF20

B26

AE18

C11

It must rout to the enable pin of PWM and CK-409.

VIDGD to Vccp delay time is from 1ms to 10ms.

VIDGD rising time is 150ns.

AE20

AE6

AE8

AF11

AF13

AF15

AF17

AF19

AF2

AF21

AF5

AF7

AF9

B11

B13

B15

B17

B19

C10

C12

C14

C16

C18

C20

D11

D13

D15

D17

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCB7VCCB9VCC

VCC

VCC

VCC

VCC

VCC

VCCC8VCC

VCC

VCC

VSS

VSS

VSS

VSSC2VSS

VSS

VSS

VSSC5VSSC7VSSC9VSS

VSS

VSS

VSS

VSS

VSS

VSSD3VSS

VSSD6VSSD8VSSE1VSS

VSS

VSS

VSS

VSS

VSS

VSSE7VSSE9VSS

VSSE4VSS

E11

E13

E15

E17

E19

E23

C13

C15

C17

C19

C22

C25

D12

D14

D16

D18

D20

D21

D24

E26

C31

1u-0603

D19

E10

E12

E14

E16

E18

E20

VCC

VCC

VCCD7VCCD9VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSSF2VSS

VSS

F10

F12

F14

F16

F18

F22

F25

F11

VCC

VCCE8VCC

VSSF5VSSF8VSS

G21

F13

F15

F17

VCC

VCC

VSSG3VSSH1VSS

G24

C32

4.7u-0805

F19

F9

VCC

VCC

VSSG6VSS

H23

VCC

H26

CPU DECOUPLING CAPACITORS

VCCP VCCP VCCP VCCP VCCP VCCPVCCP

C35

22u-1206

C42

22u-1206

C49

22u-1206

C56

22u-1206

C63

A A

22u-1206

5

C36

22u-1206

C43

22u-1206

C50

22u-1206

C57

22u-1206

C64

22u-1206

C37

22u-1206

C44

22u-1206

C51

22u-1206

C58

22u-1206

C65

22u-1206

C68

22u-1206

Place these caps within north side of processorPlace these caps within socket cavity Place these caps within south side of processor

4

C45

X-1206-C

C52

X-1206-C

C59

X-1206-C

C66

X-1206-C

3

C46

X-1206-C

C53

X-1206-C

C60

X-1206-C

C67

X-1206-C

C40

22u-1206

C47

22u-1206

C54

22u-1206

C61

22u-1206

C41

X-1206-C

C48

22u-1206

C55

X-1206-C

C62

22u-1206

Engineer

5

Shun Min Hsu

Drawn by

Shun Min Hsu

1.0

282003/05/07

MICRO-STAR INt ' L CO., LTD.

Title

Size Project Name Rev

A3

2

Date: Sheet of

Intel mPGA478B Power

MS-6765

1

VCC_AGP

L3

0.82uH-0603

D D

VCC_AGP

R45

1RST

L4

100nH-0603

C C

B B

BSEL03,4,14

BSEL13,4,14

A A

R53

102RST

VCC3

5

+

C69

100u-16V

0.1u-0603

HA#[3..31]4

VCCA_DPLL

+

C74

100u-16V

0.1u-0603

HADSTB#04

HADSTB#14

HLOCK#4

HREQ#[0..4]4

HDEFER#4

HTRDY#4

HDBSY#4

HDRDY#4

HRS#[0..2]4

MCHCLK3

MCHCLK#3

PWR_GD14,26

CPURST#4

PCIRST#115,20,22,26

PROCHOT#4,14

R47 2.49KST

R48 2KST

R49 2KST

R50 2.49KST

R51 20RST

VTT

GTLREF14

R52

301RST

C76

0.01u-0603

R401 X-0603-R

R402 X-0603-R

5

C71

C75

HBR#04

HBPRI#4

HBNR#4

HADS#4

HITM#4

HIT#4

HDSWING

SEL0

SEL1

33-0603

TP11

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HRS#0

HRS#1

HRS#2

R46

.

SEL0

SEL1

HRCOMP

R54

200RST

VCCA_DPLL

D26

D30

L23

E29

B32

K23

C30

C31

J25

B31

E30

B33

J24

F25

D34

C32

F28

C34

J27

G27

F29

E28

H27

K24

E32

F31

G30

J26

G26

B30

D28

B24

B26

B28

E25

F27

B29

J23

L22

C29

J21

K21

E23

L21

D24

E27

G24

G22

C27

B27

B7

C7

AE14

E8

AK4

1

AJ8

L20

L13

L12

E24

C25

F23

VTT

VCCA_FSB

C70

0.1u-0603

U2A

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HAD_STB0#

HAD_STB1#

BREQ0#

BPRI#

BNR#

HLOCK#

ADS#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HIT#

HITM#

DEFER#

HTRDY#

DBSY#

DRDY#

RS0#

RS1#

RS2#

HCLKP

HCLKN

PWROK

CPURST#

RSTIN#

ICH_SYNC#

PROCHOT#

BSEL0

BSEL1

HDRCOMP

HDSWING

HDVREF

GTLREF1

C77

0.1u-0603

A31

B4

B3

VCCA_FSB

VCCA_FSB

VCCA_DPLL

VSS

VSS

VSS

C8

C12

C10

VCCJ6VCCJ7VCCJ8VCCJ9VCCK6VCCK7VCCK8VCCK9VCCL6VCCL7VCC

VSS

VSS

C14

C16

VTT

C18

VSS

C20

VSS

VSS

VSS

C22

C24

1 2

3 4

5 6

7 8

C26

VSS

4

VSS

C28

RN8

X-8P4R

4

VSSD1VSS

VSS

D9

D11

L9

D13

VSS

L10

D15

VCC

VSS

3

VCC_AGP VTT

L11

D17

VCC

VSS

D19

VCCM8VCC

VSS

M9

D21

M10

VSS

D23

VCCP

VCC

VSS

M11

VCC

VSS

D25

N10

VCCN9VCC

VCC

VSS

VSS

D27

D29

N11

D31

VCC

VSS

P10

VSS

D33

P11

D35

VCC

VSS

R11

E1

VCC

VSS

T16

VCC

VSSE3VSS

VTT

C78

T17

T18

T19

U16

U17

T20

VCC

VCC

VCC

VCC

VCC

VCC

VSSF3VSSF5VSSF8VSS

VSS

VSS

F1

F10

F12

C79

10u-0805

U20

F14

VCC

VSS

V16

F16

0.1u-0603

VCC

VSS

V18

V20

W16

W19

W20

Y16

Y17

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

F18

F20

F22

F24

F26

G31

G28

C80

C81

0.1u-0603

A33NCA35NCB2NCB25NCB34NCC1NCC23NCC35NCE26NCM31NCAF13NCAF23NCAJ12NCAN1NCAP2NCAR3NCAR33NCAR35

Y18

Y19

Y20

NCA3NC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

H5

VSSH8VSS

H9

0.1u-0603

H12

H14

H16

VCC_AGP

C83

H18

VSS

H20

G35

0.1u-0603

VSS

H2

C82

3

VSS

VSS

H22

H24

10u-0805

VSS

R25

NC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

J10

J12

J14

J16

H33

0.1u-0603

J18

C85

0.1u-0603

H26

H30

C84

VSS

VSSA7VSSA9VSS

VSS

VSS

VSS

VSS

VSS

VSS

J20

J22

J28

J32

J35

K11

C87

C86

10u-0805

2

VTT_FSB1

VTT_FSB2

VTTD5VTTD6VTTD7VTTE6VTTE7VTT

VSS

VSS

VSS

VSS

L25

L26

L35

L31

F7

VSSM3VSSM6VSS

M26

M27

A11

A13

A16

A20

A23

A25

A27

A29

A32

C4

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

K12

K14

K16

K18

VSS

VSS

VSS

VSS

VSS

VSS

VSS

L24

K33

K20

K22

K25

K27

K29

C6

VTTA4VTTA5VTTA6VTTB5VTTB6VTTC5VTT

VSS

VSS

VSS

VSS

VSSN1VSS

Intel Springdale

CRITICAL

N4

M28

M30

M33

A15

A21

HD0#

HD1#

HD2#

HD3#

VTT_FSB

VTT_FSB

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

DINV_0#

DINV_1#

DINV_2#

DINV_3#

HD_STBP0#

HD_STBN0#

HD_STBP1#

HD_STBN1#

HD_STBP2#

HD_STBN2#

HD_STBP3#

HD_STBN3#

B23

E22

B21

D20

B22

D22

B20

C21

E18

E20

B16

D16

B18

B17

E16

D18

G20

F17

E19

F19

J17

L18

G16

G18

F21

F15

E15

E21

J19

G14

E17

K17

J15

L16

J13

F13

F11

E13

K15

G12

G10

L15

E11

K13

J11

H10

G8

E9

B13

E14

B14

B12

B15

D14

C13

B11

D10

C11

E10

B10

C9

B9

D8

B8

C17

L17

L14

C15

B19

C19

L19

K19

G9

F9

D12

E12

MICRO-STAR INt ' L CO., LTD.

0.1u-0603

Title

X-0603-C

X-0603-C

C339

Size Project Name Rev

A3

Date: Sheet of

X-0603-C

C337

C338

2

Intel SpringDale CPU signals

MS-6765

1

C72 0.47u-0603

C73 0.47u-0603

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

HDBI#0

HDBI#1

HDBI#2

HDBI#3

1

HD#[0..63] 4

HDBI#[0..3] 4

HDSTBP#0 4

HDSTBN#0 4

HDSTBP#1 4

HDSTBN#1 4

HDSTBP#2 4

HDSTBN#2 4

HDSTBP#3 4

HDSTBN#3 4

6

Engineer

Shun Min Hsu

Drawn by

Shun Min Hsu

1.0

282003/05/07

5

P26

VSS

VSS

AD33

VSS

VSS

VSS

AE1

AE4

AD28

AGP_SWING

R71

39.2RST

AGP_VREF

P9

VSS

VSS

VSS

VSS

VSS

AE10

AE11

AE12

U2C

AE6

GAD0/DVOB_HSYNC

AC11

GAD1/DVOB_VSYNC

AD5

GAD2/DVOB_D1

AE5

GAD3/DVOB_D0

VAD0

VAD1

VAD2

VAD3

VAD4

VAD7

VAD6

VAD9

VAD8

VAD11

VAD10

R65330-0603

R638.2K-0603

VAID0

VAID1

VAID2

VAID3

VAID4

VAID5

VAID6

VAID7

VCC_AGP

AA10

GAD4/DVOB_D3

AC9

GAD5/DVOB_D2

AB11

GAD6/DVOB_D5

AB7

GAD7/DVOB_D4

AA9

GAD8/DVOB_D6

AA6

GAD9/DVOB_D9

AA5

GAD10/DVOB_D8

W10

GAD11/DVOB_D11

AA11

GAD12/DVOB_D10

W6

GAD13/DVOBC_CLKINT

W9

GAD14/DVOB_FLDSTL

V7

GAD15/MDDC_DATA

AA2

GAD16/DVOC_VSYNC

Y4

GAD17/DVOC_HSYNC

Y2

GAD18/DVOC_BLANK#

W2

GAD19/DVOC_D0

Y5

GAD20/DVOC_D1

V2

GAD21/DVOC_D2

W3

GAD22/DVOC_D3

U3

GAD23/DVOC_D4

T2

GAD24/DVOC_D7

T4

GAD25/DVOC_D6

T5

GAD26/DVOC_D9

R2

GAD27/DVOC_D8

P2

GAD28/DVOC_D11

P5

GAD29/DVOC_D10

P4

GAD30/DVOBC_INTR#

M2

GAD31/DVOC_FLDSTL

Y7

GCBE0/DVOB_D7

W5

GCBE1/DVOB_BLANK#

AA3

GCBE2

U2

GCBE3/DVOC_D5

AC6

GADSTBF0/DVOB_CLK

AC5

GADSTBS0/DVOB_CLK#

V4

GADSTBF1/DVOC_CLK

V5

GADSTBS1/DVOC_CLK#

N6

GREQ

M7

GGNT

N3

GST0

N5

GST1

N2

GST2

R10

GRBF

R9

GWBF

U6

GFRAME/MDVI_DATA

V11

GIRDY/MI2CCLK

AB5

GTRDY/MDVI_CLK

AB4

GDEVSEL/MI2CDATA

W11

GSTOP/MDDC_CLK

AB2

GPAR/ADD_DETECT

H4

GCLKIN

R6

GSBA0#/ADD_ID0

P7

GSBA1#/ADD_ID1

R3

GSBA2#/ADD_ID2

R5

GSBA3#/ADD_ID3

U9

GSBA4#/ADD_ID4

U10

GSBA5#/ADD_ID5

U5

GSBA6#/ADD_ID6

T7

GSBA7#/ADD_ID7

U11

GSBSTBF

T11

GSBSTBS

M4

DBI_HI

M5

DBI_LO

AC2

GRCOMP/DVOBC_RCOMP

AC3

GVSWING

AD2

GVREF

R69

60.4RST

R76

100RST

AD30

D D

DV_VSYNC11

DV_HSYNC11

VA_DE11

BCINTR#11

FLD_STL11

MDD_DATA11

MI2C_CLK11

MDD_CLK11

MI2C_DATA11

VCC_AGP

330-0603

POUT11

VAD5

VACLK11

VACLK#11

MCH_663

R6643.2RST

AGP_SWING

AGP_VREF

0.1u-0603C93

VAID6

VAID4

VAID5

VAID1

VAID0

VAID3

VAID2

VAID7

5

VCC_AGP

C C

B B

VCC_AGP

A A

R55 8.2K-0603

VAD[0..11]11

Default ID:11111110

the same with MS-6557

VCC_AGP

0.1u-0603C92

AGP_VREF11

RN9 8.2K-8P4R

1 2

3 4

5 6

7 8

RN10 8.2K-8P4R

1 2

3 4

5 6

7 8

R75

P27

VSS

VSS

AE13

P28

P30

VSS

VSS

AE25

AE26

P33

VSS

VSS

VSSR1VSSR4VSS

VSS

VSS

VSS

AF3

AE32

AE35

VCCA_DAC

0.01u-0603

VSS

4

R32

AF6

4

VSS

VSST1VSS

VSS

AF9

C94

T3

VSS

AF11

T10

T26

T27

T28

VSST6VSST8VSST9VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AF14

VSS

AF16

AF18

AF20

AF22

AF24

AF25

C95

0.1u-0603

T30

T33

VSS

AF30

AF33

T35

VSS

VSS

AG4

U18

VSSU4VSS

VSS

VSS

VSS

AG8

AG14

C96

22u-1206

V6

U19

U32

VSS

VSS

VSS

VSSV3VSSV8VSSV9VSS

VSS

VSS

VSS

VSS

VSS

VSS

AG16

AG18

AG20

AG22

AG24

AG26

L6 100nH-0603

V10

V17

V19

VSS

VSS

VSS

VSS

VSS

VSS

AG28

AG32

AG35

R67 1RST

1.7V/250mA

VCC_AGP

3

V27

V33

V26

V28

V30

VSS

VSS

VSS

VSS

VSS

VSS

AH3

AH6

AH12

AH10

W17

W18

VSS

VSS

VSSW4VSS

VSS

VSS

VSS

VSS

AH14

AH16

AH18

AH20

VCC_DAC

R72 X-0603-R

R73 X-0603-R

R77 X-0603-R

VSS

VSS

W32

AH22

VSS

VSS

Y3

VSS

VSS

AH24

3

Y26

Y10

VSSY6VSSY8VSSY9VSS

VSS

VSS

VSS

VSS

VSS

AJ1

AJ4

AJ9

AH30

AH33

Y28

Y27

VSS

VSS

VSS

VSS

VSS

AJ32

AJ35

CI_SWING

CI_VREF

Y30

Y33

Y35

VSS

VSS

VSS

VSS

AK3

AK8

AK10

VCC_AGP

VSS

VSS

AA1

AK12

VSS

VSS

AA4

AK14

VSS

VSS

AA32

VSS

VSS

AK16

AB10

AB26

AB3

AK18

AB27

AB6

AB8

AB9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AL1

AK20

AK22

AK24

AK26

AK28

R68 226RST

R74 113RST

AC1

AC4

AC32

AB28

AB30

AB33

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AM9

AL32

AM13

AM15

AM17

AM11

R70

147RST

VSS

VSS

AC35

VSS

VSS

AM19

AD3

AD6

VSS

VSS

VSS

VSS

AM21

AM23

2

VCC_AGP

AD8

AD9

AD10

VSS

VSS

VSS

VCC_AGPL1VCC_AGPL5VCC_AGPY1VCC_AGPJ1VCC_AGPJ2VCC_AGPJ3VCC_AGPK2VCC_AGPK3VCC_AGPK4VCC_AGPK5VCC_AGPJ4VCC_AGPJ5VCC_AGPL4VCC_AGPL2VCC_AGP

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AN10

AN12

AM27

AM29

AM35

HI_SWING

C97 0.1u-0603

HUB_MREF

C98 0.1u-0603

C718 1u-0603

2

AN14

AM25

1

1u-0603

C89

HL0

HL1

HL2

HL3

HL4

HL5

HL6

HL7

HL8

HL9

HL10

R56

HL_RCOMP

HI_SWING

HUB_MREF

R57 X-0603-R

C90 X-0603-C

C91 X-0603-C

DOT_CLK

R58 33-0603

R59 33-0603

R60

75-0603

R61

75-0603

R62

75-0603

CB2

VCCA_DAC

MS-6765

L5

80L-0603

HL_STBF 14

HL_STBS 14

51.1RST

CI_SWING

CI_VREF

DOT_CLK 3

R64 137RST

VCC3

CB3

0.1u-0603

1

VCC_AGP

HL[0..10] 14

VCC_AGP

HI_SWING 14

HUB_MREF 14

VCC_AGP

3VDDCCL 12

3VDDCDA 12

CRT_VSYNC 12

CRT_HSYNC 12

BLUE 12

GREEN 12

RED 12

HS4

SPRINGDALE-HEATSINK

JMCH1

HS-HOOK

JMCH2

HS-HOOK

Engineer

Shun Min Hsu

Drawn by

Shun Min Hsu

7

282003/05/07

1.0

VCCA_AGP

C88

AG1

Y11

VCCA_AGP

VCCA_AGP

HI10

HI_STRF

HI_STRS

HI_SWING

HI_VREF

CI10

CISTRF

CISTRS

CI_SWING

CI_VREF

DREFCLK

VSYNC

HSYNC

BLUE

BLUE#

GREEN

GREEN#

RED

RED#

REFSET

VCC_DAC

VCC_DAC

EXTTS#

VSS

VSS

VSS

VSS

VSS

VSS

Intel Springdale

CRITICAL

AR23

AR20

0.1u-0603

AF5

HI0

AG3

HI1

AK2

HI2

AG5

HI3

AK5

HI4

AL3

HI5

AL2

HI6

AL4

HI7

AJ2

HI8

AH2

HI9

AJ3

AH5

AH4

AD4

AE3

AE2

AK7

CI0

AH7

CI1

AD11

CI2

AF7

CI3

AD7

CI4

AC10

CI5

AF8

CI6

AG7

CI7

AE9

CI8

AH9

CI9

AG6

AJ6

AJ5

AG2

AF2

AF4

G4

F2

H3

E2

G3

H7

G6

H6

G5

F4

E4

D2

G1

G2

0.1u-0603

C2

D3

AP8

AG9

AG10

AN35

AP34

AR1

AR25

AR27

AR29

AR32

L3

HI_RCOMP

CI_RCOMP

DDCA_CLK

DDCA_DATA

VCCA_DAC

VSSA_DAC

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

VSS

VSS

VSS

AN16

AN18

AN20

AN22

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AR9

AN24

AN26

AN28

AN30

AN32

AR11

AR13

AR16

MICRO-STAR INt ' L CO., LTD.

Title

Size Project Name Rev

A3

Date: Sheet of

Intel SpringDale AGP & LAN

5

DDRMD_A[0..63]9,10

DDRMD_A0

DDRMD_A1

DDRMD_A2

DDRMD_A3

DDRMD_A6

DDRMD_A7

DDRMD_A4

DDRMD_A5

AP10

AP11

AM12

AN13

AM10

AL10

SDQ_A0

SDQ_A1

VCC_DDR

E35

SDQ_A2

SDQ_A3

VCC_DDR

VCC_DDR

R35

AA35

SDQ_A4

SDQ_A5

VCC_DDR

VCC_DDR

AR15

AR21

AL12

SDQ_A6

VCC_DDR

AL6

U2B

MA_A0

MA_A1

MA_A2

MA_A3

MA_A4

MA_A5

MA_A6

MA_A7

MA_A8

MA_A9

MA_A10

MA_A11

MA_A12

SDMA0

SDMA1

SDMA2

SDMA3

SDMA4

SDMA5

SDMA6

SDMA7

XRCOMP

XCOMPH

XCOMPL

SMVREF_A

XCOMPL

XCOMPH

AA34

SCS_A0#

Y31

SCS_A1#

Y32

SCS_A2#

W34

SCS_A3#

AC33

SRAS_A#

Y34

SCAS_A#

AB34

SWE_A#

AJ34

SMAA_A0

AL33

SMAA_A1

AK29

SMAA_A2

AN31

SMAA_A3

AL30

SMAA_A4

AL26

SMAA_A5

AL28

SMAA_A6

AN25

SMAA_A7

AP26

SMAA_A8

AP24

SMAA_A9

AJ33

SMAA_A10

AN23

SMAA_A11

AN21

SMAA_A12

AL34

SMAB_A1

AM34

SMAB_A2

AP32

SMAB_A3

AP31

SMAB_A4

AM26

SMAB_A5

AE33

SBA_A0

AH34

SBA_A1

AP12

SDM_A0

AP16

SDM_A1

AM24

SDM_A2

AP30

SDM_A3

AF31

SDM_A4

W33

SDM_A5

M34

SDM_A6

H32

SDM_A7

AN11

SDQS_A0

AP15

SDQS_A1

AP23

SDQS_A2

AM30

SDQS_A3

AF34

SDQS_A4

V34

SDQS_A5

M32

SDQS_A6

H31

SDQS_A7

AK32

SMDCLK_A0

AK31

SMDCLK_A0#

AP17

SMDCLK_A1

AN17

SMDCLK_A1#

N33

SMDCLK_A2

N34

SMDCLK_A2#

AK33

SMDCLK_A3

AK34

SMDCLK_A3#

AM16

SMDCLK_A4

AL16

SMDCLK_A4#

P31

SMDCLK_A5

P32

SMDCLK_A5#

AK9

SMXRCOMP

AN9

SMXCOMPVOH

AL9

SMXCOMPVOL

E34

SMVREF_A

VCC_DDR_C1

VCC_DDR_C2

VCC_DDR_C3

VCC_DDR_C4

VCC_DDR_C5

R87 30.1KST

R88 10KST

CB4 2.2u-0805

R90 10KST

R91 30.1KST

MCS_A#09,10

MA_A[0..12]9,10

SDMA09,10

SDMA19,10

SDMA29,10

SDMA39,10

SDMA49,10

SDMA59,10

SDMA69,10

SDMA79,10

SDQS_A[0..7]9,10

R86 42.2RST

MCS_A#19,10

MRAS_A#9,10

MCAS_A#9,10

MWE_A#9,10

MBA_A09,10

MBA_A19,10

MCLK_A09

MCLK_A#09

MCLK_A19

MCLK_A#19

MCLK_A29

MCLK_A#29

0.01u-0603C102

0.01u-0603C103

C106 2.2u-0805

XRCOMP

R89

42.2RST

5

SDQS_A0

SDQS_A1

SDQS_A2

SDQS_A3

SDQS_A4

SDQS_A5

SDQS_A6

SDQS_A7

C107 0.47u-0603

C109 2.2u-0805

C110 0.1u-0603

C111 0.1u-0603

C112 0.1u-0603

D D

C C

B B

A A

MEM_STR MEM_STR

DDRMD_A8

DDRMD_A9

AP13

AP14

AM14

SDQ_A7

SDQ_A8

VCC_DDR

VCC_DDR

AL7

AM1

AM2

DDRMD_B[0..63]9,10

DDRMD_A10

DDRMD_A11

DDRMD_A12

AL18

AP19

SDQ_A9

SDQ_A10

SDQ_A11

VCC_DDR

VCC_DDR

VCC_DDR

AP3

AN8

MEM_STR

4

DDRMD_A13

AL14

AN15

SDQ_A12

SDQ_A13

VCC_DDR

VCC_DDR

AP4

AP5

4

DDRMD_A14

DDRMD_A15

AP18

AM18

SDQ_A14

VCC_DDR

AP6

AP7

DDRMD_A16

DDRMD_A17

AP22

AM22

SDQ_A15

SDQ_A16

SDQ_A17

VCC_DDR

VCC_DDR

VCC_DDR

AR4

AR5

DDRMD_A18

DDRMD_A19

AL24

AN27

SDQ_A18

VCC_DDR

AR7

AR31

DDRMD_A20

DDRMD_A21

AP21

AL22

SDQ_A19

SDQ_A20

SDQ_A21

VCC_DDR

SDQ_B0

AJ10

DDRMD_B0

DDRMD_A22

DDRMD_A23

AP25

AP27

SDQ_A22

SDQ_A23

SDQ_B1

SDQ_B2

AL11

AE15

DDRMD_B1

DDRMD_B2

MEM_STR

3

MCKE_A[0..1] 9,10

MCKE_A0

DDRMD_A26

DDRMD_A27

DDRMD_A30

DDRMD_A31

DDRMD_A28

DDRMD_A29

DDRMD_A34

DDRMD_A35

DDRMD_A38

DDRMD_A39

DDRMD_A36

DDRMD_A37

DDRMD_A32

DDRMD_A24

DDRMD_A25

AP28

AP29

AP33

SDQ_A24

SDQ_A25

SDQ_A26

SDQ_B3

SDQ_B4

SDQ_B5

AL8

AF12

AE16

DDRMD_B3

DDRMD_B4

DDRMD_B5

DDRMD_B6

10u-0805

C116

DDRMD_A33

AM33

AM28

AN29

AM31

AN34

AH32

AG34

AF32

AD32

SDQ_A27

SDQ_A28

SDQ_A29

SDQ_A30

SDQ_A31

SDQ_A32

SDQ_A33

SDQ_A34

SDQ_A35

SDQ_B6

SDQ_B7

SDQ_B8

SDQ_B9

SDQ_B10

SDQ_B11

SDQ_B12

SDQ_B13

SDQ_B14

AJ14

AJ16

AL13

AL17

AK11

AE17

AK17

AK13

AG12

DDRMD_B10

DDRMD_B11

DDRMD_B12

DDRMD_B13

DDRMD_B14

DDRMD_B7

DDRMD_B8

C117

DDRMD_B15

DDRMD_B9

10u-0805

0.1u-0603

C118

DDRMD_A42

DDRMD_A43

DDRMD_A46

DDRMD_A47

DDRMD_A44

DDRMD_A45

DDRMD_A40

DDRMD_A41

AH31

AG33

AE34

AD34

AC34

AB31

V32

V31

SDQ_A36

SDQ_A37

SDQ_A38

SDQ_A39

SDQ_A40

SDQ_A41

SDQ_A42

SDQ_A43

SDQ_B15

SDQ_B16

SDQ_B17

SDQ_B18

SDQ_B19

SDQ_B20

SDQ_B21

SDQ_B22

AJ18

AE19

DDRMD_B16

C119

AJ24

AL19

AE20

AK23

AK21

AG23

DDRMD_B17

DDRMD_B18

DDRMD_B19

DDRMD_B20

DDRMD_B21

DDRMD_B22

DDRMD_B23

1u-0603

0.1u-0603

C120

DDRMD_A50

DDRMD_A51

DDRMD_A54

DDRMD_A55

DDRMD_A52

DDRMD_A53

DDRMD_A48

DDRMD_A49

AD31

AB32

U34

U33

T34

T32

K34

K32

SDQ_A44

SDQ_A45

SDQ_A46

SDQ_A47

SDQ_A48

SDQ_A49

SDQ_A50

SDQ_A51

SDQ_B23

SDQ_B24

SDQ_B25

SDQ_B26

SDQ_B27

SDQ_B28

SDQ_B29

SDQ_B30

AJ26

AJ27

AF27

AE22

AK25

AH26

AD25

AG27

DDRMD_B24

DDRMD_B25

DDRMD_B26

DDRMD_B27

DDRMD_B28

DDRMD_B29

DDRMD_B30

DDRMD_B31

3

T31

P34

SDQ_A52

SDQ_A53

SDQ_B31

SDQ_B32

AF28

AE30

DDRMD_B32

DDRMD_A56

DDRMD_A57

L34

L33

J33

H34

SDQ_A54

SDQ_A55

SDQ_A56

SDQ_B33

SDQ_B34

SDQ_B35

Y29

AE31

AC27

AC30

DDRMD_B33

DDRMD_B34

DDRMD_B35

DDRMD_B36

VCCA_DDR

0.1u-0603

DDRMD_A58

DDRMD_A59

DDRMD_A60

E33

F33

SDQ_A57

SDQ_A58

SDQ_A59

SDQ_B36

SDQ_B37

SDQ_B38

AB29

AA26

DDRMD_B37

DDRMD_B38

DDRMD_B39

C114

DDRMD_A61

K31

J34

SDQ_A60

SDQ_B39

AA27

AA30

DDRMD_B40

DDRMD_A62

DDRMD_A63

G34

F34

SDQ_A61

SDQ_A62

SDQ_A63

SDQ_B40

SDQ_B41

SDQ_B42

T25

U27

W30

DDRMD_B41

DDRMD_B42

DDRMD_B43

MCKE_A1

AL20

AN19

AM20

AP20

AB25

SCKE_A0

SCKE_A1

SCKE_A2

SCKE_A3

SDQ_B43

SDQ_B44

SDQ_B45

SDQ_B46

SDQ_B47

SDQ_B48

V29

P29

U25

R27

R30

AA31

DDRMD_B44

DDRMD_B45

DDRMD_B46

DDRMD_B47

DDRMD_B48

DDRMD_B49

L41 80L-0805

L7 X-1206-L

+

C115

100u-16V

AC25

VCCA_DDR

SDQ_B49

K28

DDRMD_B50

AC26

VCCA_DDR

SDQ_B50

L30

DDRMD_B51

VCCA_DDR

VCCADDR

AN4

AL35

VCCA_DDR

VCCA_DDR

SDQ_B51

SDQ_B52

SDQ_B53

P25

R31

R26

DDRMD_B52

DDRMD_B53

DDRMD_B54

0.1u-0603

C99

AM3

AN5

VCC_DDR

VCC_DDR

VCC_DDR

SDQ_B54

SDQ_B55

SDQ_B56

L32

K30

DDRMD_B55

DDRMD_B56

VCC_AGP

2

AM5

AM6

VCC_DDR

SDQ_B57

F32

H29

DDRMD_B57

DDRMD_B58

2

AM7

AM8

VCC_DDR

VCC_DDR

VCC_DDR

SDQ_B58

SDQ_B59

SDQ_B60

N25

G33

DDRMD_B59

DDRMD_B60

MEM_STR

AN2

AN6

AN7

VCC_DDR

VCC_DDR

VCC_DDR

SDQ_B61

SDQ_B62

SDQ_B63

J29

G32

M25

DDRMD_B61

DDRMD_B62

DDRMD_B63

1

VCC_DDR_C3

P8

N35

N32

VSS

VSS

SCKE_B0

SCKE_B1

AF19

AK19

MCKE_B0

MCKE_B1

VSSP3VSSP6VSS

SCMDCLK_B0

SCMDCLK_B0#

SCMDCLK_B1

SCMDCLK_B1#

SCMDCLK_B2

SCMDCLK_B2#

SCMDCLK_B3

SCMDCLK_B3#

SCMDCLK_B4

SCMDCLK_B4#

SCMDCLK_B5

SCMDCLK_B5#

SMYRCOMP

SMYCOMPVOH

SMYCOMPVOL

SMVREF_B

SCKE_B2

SCKE_B3

Intel Springdale

CRITICAL

AE18

AG19

SCS_B0#

SCS_B1#

SCS_B2#

SCS_B3#

SRAS_B#

SCAS_B#

SWE_B#

SMAA_B0

SMAA_B1

SMAA_B2

SMAA_B3

SMAA_B4

SMAA_B5

SMAA_B6

SMAA_B7

SMAA_B8

SMAA_B9

SMAA_B10

SMAA_B11

SMAA_B12

SMAB_B1

SMAB_B2

SMAB_B3

SMAB_B4

SMAB_B5

SBA_B0

SBA_B1

SDM_B0

SDM_B1

SDM_B2

SDM_B3

SDM_B4

SDM_B5

SDM_B6

SDM_B7

SDQS_B0

SDQS_B1

SDQS_B2

SDQS_B3

SDQS_B4

SDQS_B5

SDQS_B6

SDQS_B7

MCKE_B[0..1] 9,10

U26

T29

V25

W25

W26

W31

W27

AG31

AJ31

AD27

AE24

AK27

AG25

AL25

AF21

AL23

AJ22

AF29

AL21

AJ20

AE27

AD26

AL29

AL27

AE23

Y25

AA25

AG11

AG15

AE21

AJ28

AC31

U31

M29

J31

AF15

AG13

AG21

AH27

AD29

U30

L27

J30

AG29

AG30

AF17

AG17

N27

N26

AJ30

AH29

AK15

AL15

N31

N30

AA33

R34

R33

AP9

MA_B0

MA_B1

MA_B2

MA_B3

MA_B4

MA_B5

MA_B6

MA_B7

MA_B8

MA_B9

MA_B10

MA_B11

MA_B12

1

.

1

.

1

.

1

.

1

.

1

.

1

.

1

.

YRCOMP

YCOMPH

YCOMPL

SMVREF_B

MCS_B#0 9,10

MCS_B#1 9,10

MRAS_B# 9,10

MCAS_B# 9,10

MWE_B# 9,10

TP49

TP51

TP53

TP55

TP57

SDQS_B0

SDQS_B1

SDQS_B2

SDQS_B3

SDQS_B4

SDQS_B5

SDQS_B6

SDQS_B7

TP59

TP61

TP63

R84 150RST

R85 150RST

MA_B[0..12] 9,10

MBA_B0 9,10

MBA_B1 9,10

SDMB0 9,10

SDMB1 9,10

SDMB2 9,10

SDMB3 9,10

SDMB4 9,10

SDMB5 9,10

SDMB6 9,10

SDMB7 9,10

SDQS_B[0..7] 9,10

MCLK_B0 9

MCLK_B#0 9

MCLK_B1 9

MCLK_B#1 9

MCLK_B2 9

MCLK_B#2 9

0.01u-0603C100

0.01u-0603C101

C104

0.1u-0603

MICRO-STAR INt ' L CO., LTD.

Title

Size Project Name Rev

A3

Date: Sheet of

Intel SpringDale DDR

MS-6765

1

R78

42.2RST

YRCOMP

R79

42.2RST

VCC_DDR_C2

R80

10KST

YCOMPH

R81

30.1KST

VCC_DDR_C2

MEM_STR

8

R82

30.1KST

YCOMPL

R83

10KST

Engineer

Shun Min Hsu

Drawn by

Shun Min Hsu

1.0

282003/05/07

5

4

3

2

1

MEM_STR

MEM_STR

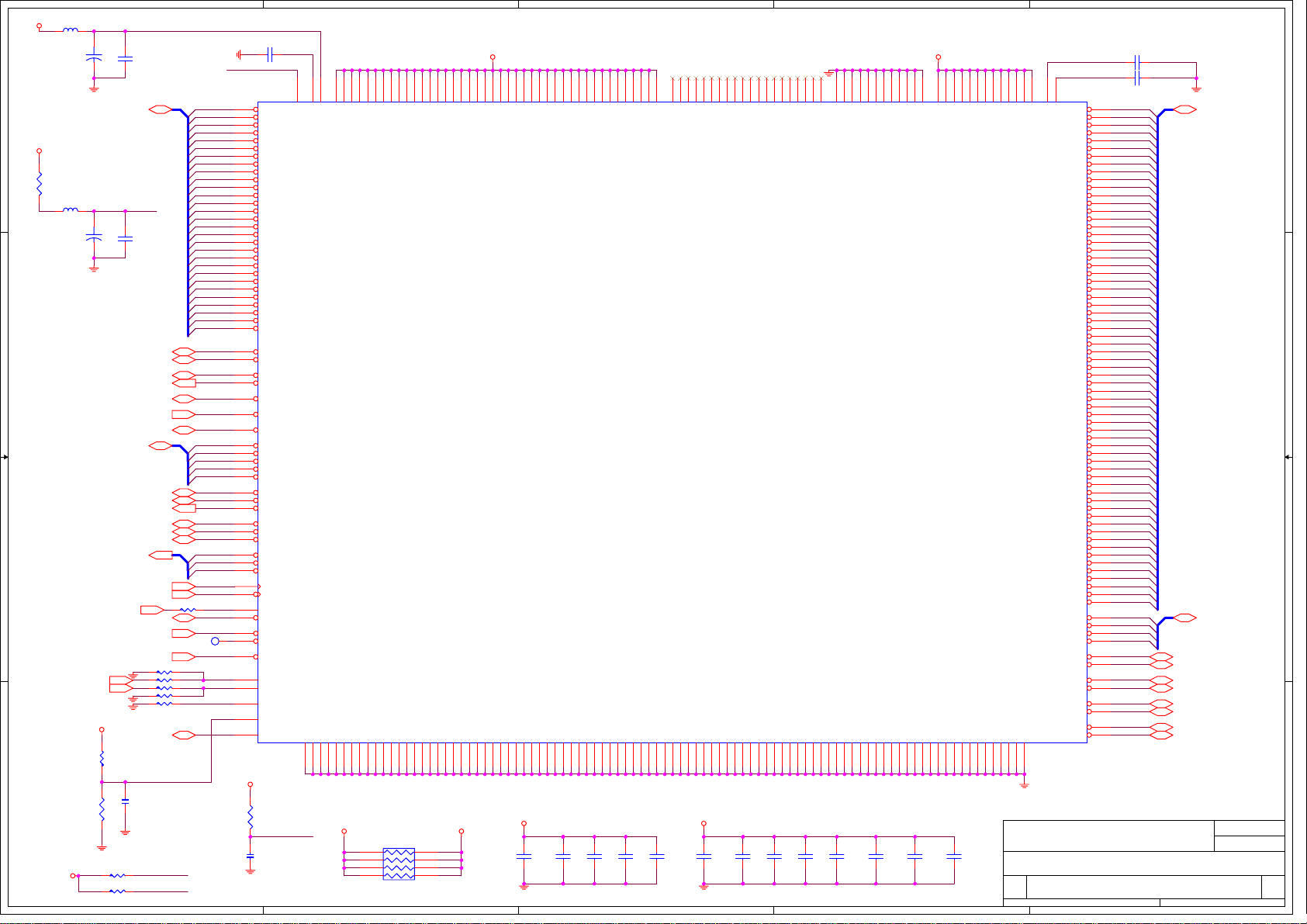

SYSTEM MEMORY

180

15

VDDQ13

VDDQ14

VDDQ15

CK1#(CK0#)

NC(RESET#)

VSS19

VSS20

VSS21

160

176

A3

82

VDDID

CS0#

CS1#

CS2#

CS3#

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

FETEN

A10_AP

SCL

SDA

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

CK0(DU)

CK0#(DU)

CK1(CK0)

CK2(DU)

CK2#(DU)

NC5

CKE0

CKE1

CAS#

RAS#

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

DDR2

N13-1840021

DDR2

A11

A12

A13

BA0

BA1

BA2

SA0

SA1

SA2

184

VDDSPD

157

158

71

163

5

14

25

36

56

67

78

86

47

167

48

A0

43

A1

41

A2

130

A3

37

A4

32

A5

125

A6

29

A7

122

A8

27

A9

141

118

115

103

59

52

113

92

91

181

182

183

44

45

49

51

134

135

142

144

16

17

137

138

76

75

173

10

21

111

65

154

97

107

119

129

149

159

169

177

140

SDQS_B0

SDQS_B1

SDQS_B2

SDQS_B3

SDQS_B4

SDQS_B5

SDQS_B6

SDQS_B7

MA_B0

MA_B1

MA_B2

MA_B3

MA_B4

MA_B5

MA_B6

MA_B7

MA_B8

MA_B9

MA_B10

MA_B11

MA_B12

SMBCLK

SMBDATA

MEM_STR

MCKE_B0

MCKE_B1

DDR DIMM1 & 2

MS-6765

MCS_B#0 8,10

MCS_B#1 8,10

MBA_B0 8,10

MBA_B1 8,10

MCLK_B1 8

MCLK_B#1 8

MCLK_B0 8

MCLK_B#0 8

MCLK_B2 8

MCLK_B#2 8

MCAS_B# 8,10

MRAS_B# 8,10

SDMB0 8,10

SDMB1 8,10

SDMB2 8,10

SDMB3 8,10

SDMB4 8,10

SDMB5 8,10

SDMB6 8,10

SDMB7 8,10

1

SDQS_B[0..7] 8,10

MA_B[0..12] 8,10

MCKE_B[0..1] 8,10

Engineer

Shun Min Hsu

Drawn by

Shun Min Hsu

9

1.0

282003/05/07

143

156

164

104

108

120

148

143

156

164

128

VDDQ7

116

136

VDDQ8

VSS14

124

VDDQ9

VSS15

132

VDDQ10

VDDQ11

VSS16

VSS17

139

4

172

VDDQ12

VSS18

145

152

104

108

120

148

168

94

95

98

99

12

13

19

20

105

106

109

110

23

24

28

31

114

117

121

123

33

35

39

40

126

127

131

133

53

55

57

60

146

147

150

151

61

64

68

69

153

155

161

162

72

73

79

80

165

166

170

171

83

84

87

88

174

175

178

179

90

63

101

102

2

4

6

8

1

9

VDD07VDD138VDD246VDD370VDD485VDD5

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

WP(NC)

WE#

VREF

NC2

NC3

NC4

D D

DDRMD_A[0..63]8,10

C C

B B

MWE_A#8,10

75RST

R94

DDR_VREF2

A A

X-0603-R

75RST

Keep the voltage divider within 1" of DIMM1.

Trace width 12 mil with 12 mil space.

MEM_STR

R93

R96

DDRMD_A0

DDRMD_A1

DDRMD_A2

DDRMD_A3

DDRMD_A4

DDRMD_A5

DDRMD_A6

DDRMD_A7

DDRMD_A8

DDRMD_A9

DDRMD_A10

DDRMD_A11

DDRMD_A12

DDRMD_A13

DDRMD_A14

DDRMD_A15

DDRMD_A16

DDRMD_A17

DDRMD_A18

DDRMD_A19

DDRMD_A20

DDRMD_A21

DDRMD_A22

DDRMD_A23

DDRMD_A24

DDRMD_A25

DDRMD_A26

DDRMD_A27

DDRMD_A28

DDRMD_A29

DDRMD_A30

DDRMD_A31

DDRMD_A32

DDRMD_A33

DDRMD_A34

DDRMD_A35

DDRMD_A36

DDRMD_A37

DDRMD_A38

DDRMD_A39

DDRMD_A40

DDRMD_A41

DDRMD_A42

DDRMD_A43

DDRMD_A44

DDRMD_A45

DDRMD_A46

DDRMD_A47

DDRMD_A48

DDRMD_A49

DDRMD_A50

DDRMD_A51

DDRMD_A52

DDRMD_A53

DDRMD_A54

DDRMD_A55

DDRMD_A56

DDRMD_A57

DDRMD_A58

DDRMD_A59

DDRMD_A60

DDRMD_A61

DDRMD_A62

DDRMD_A63

5

C122

0.1u-0603

DDR_VREF1

VDD6

VDD7

VDD8

VDDQ022VDDQ130VDDQ254VDDQ362VDDQ477VDDQ596VDDQ6

VSS03VSS111VSS218VSS326VSS434VSS542VSS650VSS758VSS866VSS974VSS1081VSS1189VSS1293VSS13

112

DDR DIMM SOCKET

100

184

180

15

82

VDDID

VDDQ13

VDDQ14

VDDQ15

VDDSPD

157

CS0#

158

CS1#

71

CS2#

163

CS3#

5

DQS0

14

DQS1

25

DQS2

36

DQS3

56

DQS4

67

DQS5

78

DQS6

86

DQS7

47

DQS8

167

FETEN

48

A0

43

A1

41

A2

130

A3

37

A4

32

A5

125

A6

29

A7

122

A8

27

A9

141

A10_AP

118

A11

115

A12

103

A13

59

BA0

52

BA1

113

BA2

SCL

SDA

SA0

SA1

SA2

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

CK0(DU)

CK0#(DU)

CK1(CK0)

CK1#(CK0#)

CK2(DU)

CK2#(DU)

NC5

NC(RESET#)

CKE0

CKE1

CAS#

RAS#

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

VSS19

VSS20

VSS21

DDR1

N13-1840021

160

176

DDR1

Close to North-Bridge

SMBCLK

92

SMBDATA

91

181

182

183

44

45

49

51

134

135

142

144

16

17

137

138

76

75

173

10

21

111

65

154

97

107

119

129

149

159

169

177

140

SDQS_A0

SDQS_A1

SDQS_A2

SDQS_A3

SDQS_A4

SDQS_A5

SDQS_A6

SDQS_A7

MA_A0

MA_A1

MA_A2

MA_A3

MA_A4

MA_A5

MA_A6

MA_A7

MA_A8

MA_A9

MA_A10

MA_A11

MA_A12

MCKE_A0

MCKE_A1

MCS_A#0 8,10

MCS_A#1 8,10

MA_A[0..12] 8,10

MBA_A0 8,10

MBA_A1 8,10

SMBCLK 14,17,20,22

SMBDATA 14,17,20,22

9Pcs doupling

caps place

between DDR1

and DDR2

MCLK_A1 8

MCLK_A#1 8

MCLK_A0 8

MCLK_A#0 8

MCLK_A2 8

MCLK_A#2 8

MCKE_A[0..1] 8,10

MCAS_A# 8,10

MRAS_A# 8,10

SDMA0 8,10

SDMA1 8,10

SDMA2 8,10

SDMA3 8,10

SDMA4 8,10

SDMA5 8,10

SDMA6 8,10

SDMA7 8,10

MEM_STR

DDRMD_B[0..63]8,10

SDQS_A[0..7] 8,10

MEM_STR

CB87

10u-0805

3

MWE_B#8,10

CB5

0.1u-0402

CB6

0.1u-0402

CB7

0.1u-0402

CB8

0.1u-0402

CB9

0.1u-0402

CB10

0.1u-0402

CB11

10u-0805

CB12

0.1u-0402

CB13

0.1u-0402

X-0603-R

X-0603-R

CB88

10u-0805

MEM_STR

R92

R95

DDRMD_B0

DDRMD_B1

DDRMD_B2

DDRMD_B3

DDRMD_B4

DDRMD_B5

DDRMD_B6

DDRMD_B7

DDRMD_B8

DDRMD_B9

DDRMD_B10

DDRMD_B11

DDRMD_B12

DDRMD_B13

DDRMD_B14

DDRMD_B15

DDRMD_B16

DDRMD_B17

DDRMD_B18

DDRMD_B19

DDRMD_B20

DDRMD_B21

DDRMD_B22

DDRMD_B23

DDRMD_B24

DDRMD_B25

DDRMD_B26

DDRMD_B27

DDRMD_B28

DDRMD_B29

DDRMD_B30

DDRMD_B31

DDRMD_B32

DDRMD_B33

DDRMD_B34

DDRMD_B35

DDRMD_B36

DDRMD_B37

DDRMD_B38

DDRMD_B39

DDRMD_B40

DDRMD_B41

DDRMD_B42

DDRMD_B43

DDRMD_B44

DDRMD_B45

DDRMD_B46

DDRMD_B47

DDRMD_B48

DDRMD_B49

DDRMD_B50

DDRMD_B51

DDRMD_B52

DDRMD_B53

DDRMD_B54

DDRMD_B55

DDRMD_B56

DDRMD_B57

DDRMD_B58

DDRMD_B59

DDRMD_B60

DDRMD_B61

DDRMD_B62

DDRMD_B63

DDR_VREF2

C121

0.1u-0603

94

95

98

99

12

13

19

20

105

106

109

110

23

24

28

31

114

117

121

123

33

35

39

40

126

127

131

133

53

55

57

60

146

147

150

151

61

64

68

69

153

155

161

162

72

73

79

80

165

166

170

171

83

84

87

88

174

175

178

179

90

63

101

102

2

4

6

8

1

9

VDD07VDD138VDD246VDD370VDD485VDD5

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

WP(NC)

WE#

VREF

NC2

NC3

NC4

168

VDD6

VDD7

VDD8

VDDQ022VDDQ130VDDQ254VDDQ362VDDQ477VDDQ596VDDQ6

VSS03VSS111VSS218VSS326VSS434VSS542VSS650VSS758VSS866VSS974VSS1081VSS1189VSS1293VSS13

2

112

DDR DIMM SOCKET

100

172

128

136

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VSS14

VSS15

VSS16

VSS17

VSS18

116

124

132

139

145

152

MICRO-STAR INt ' L CO., LTD.

Title

Size Project Name Rev

Date: Sheet of

Loading...

Loading...