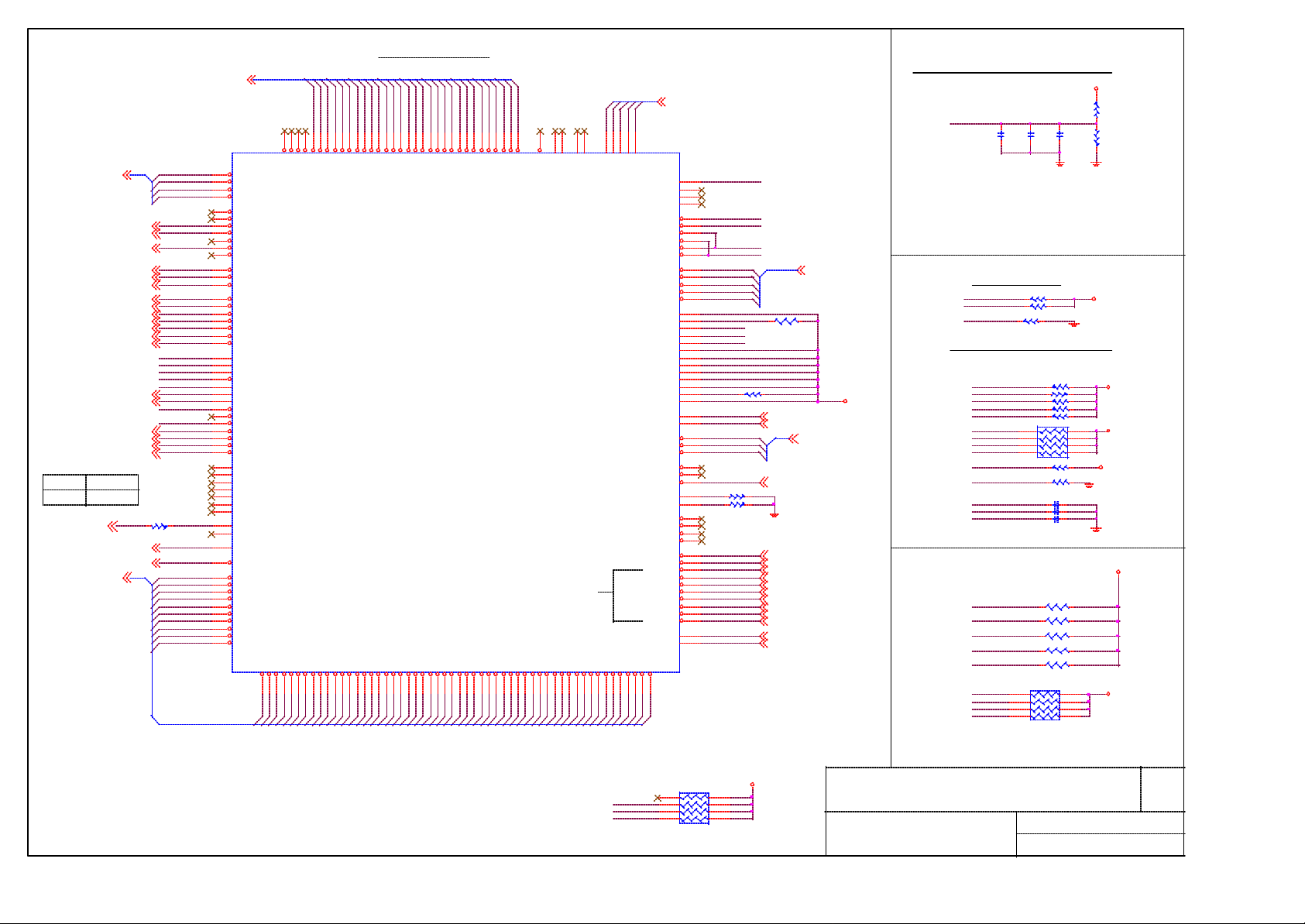

Cover Sheet

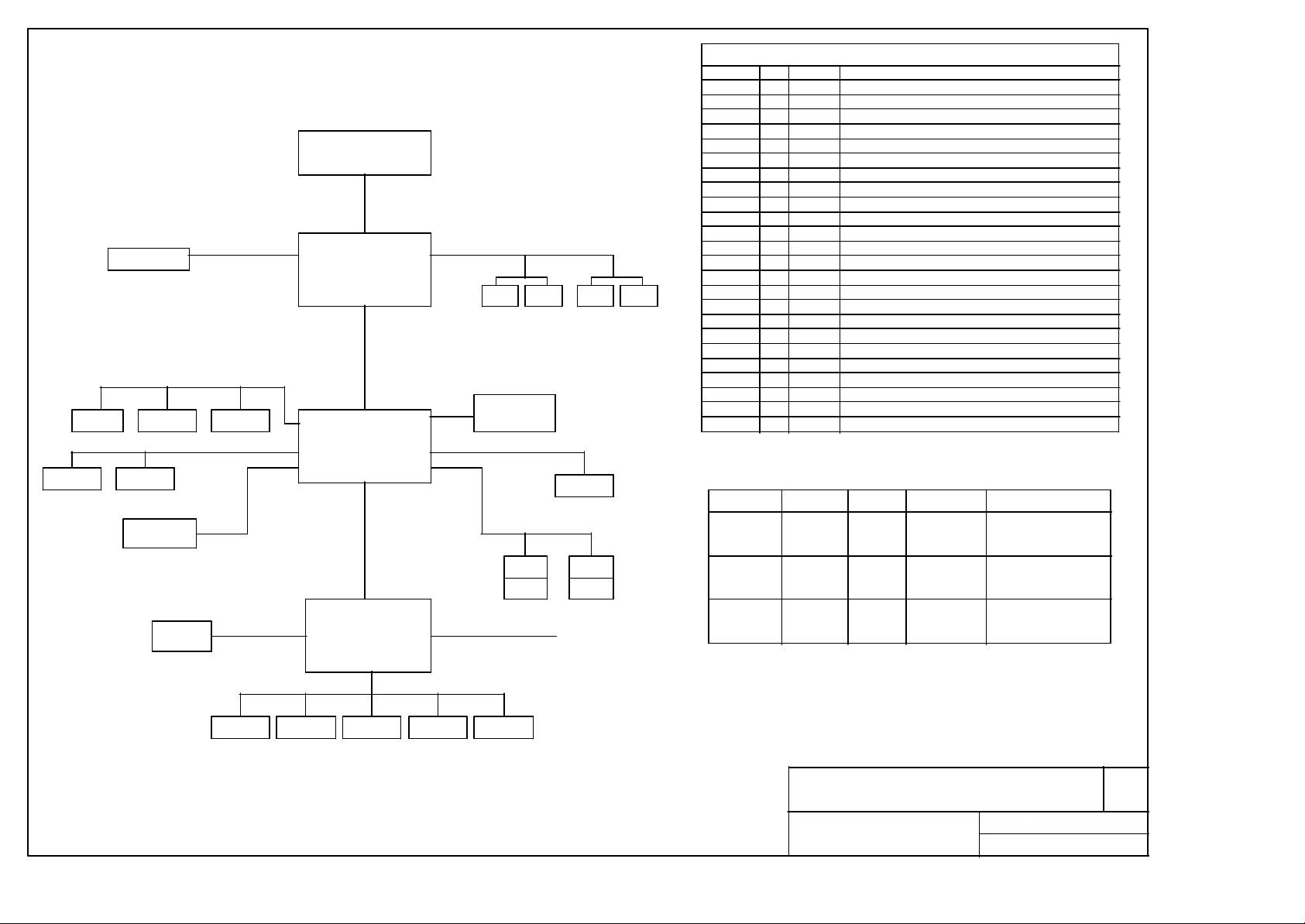

Block Diagram

1

MS6739

2

Rev:100

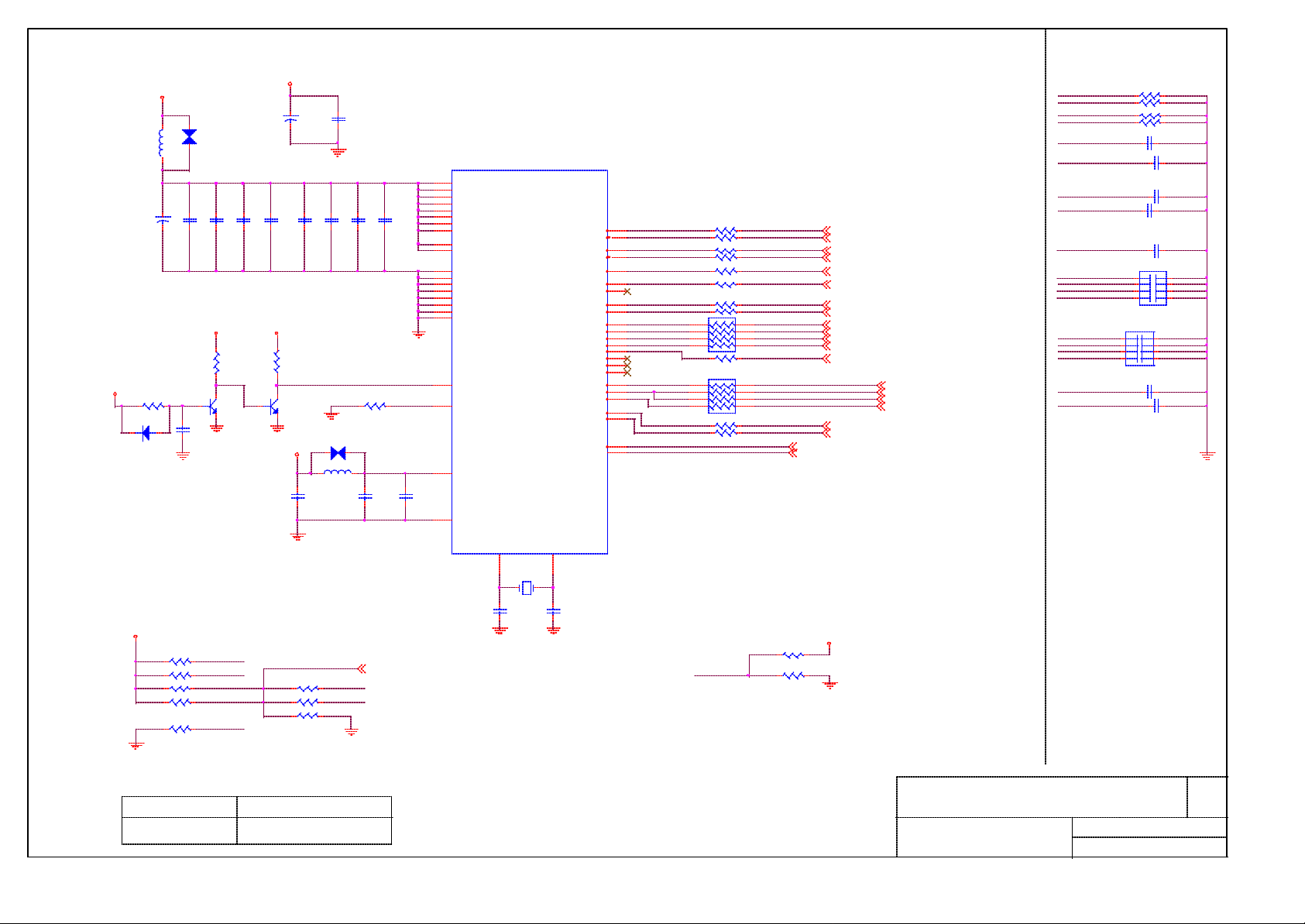

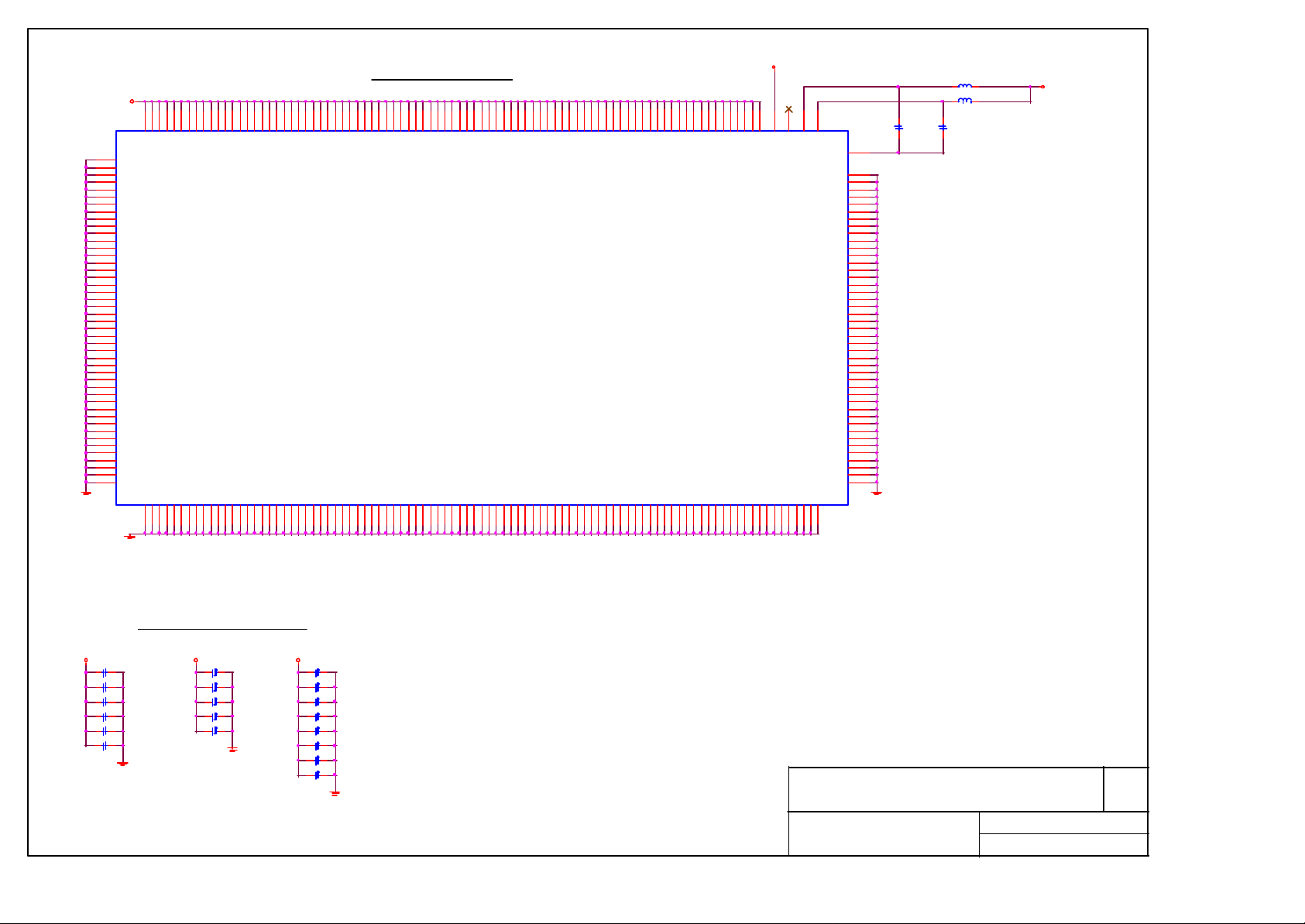

MAIN CLOCK GEN

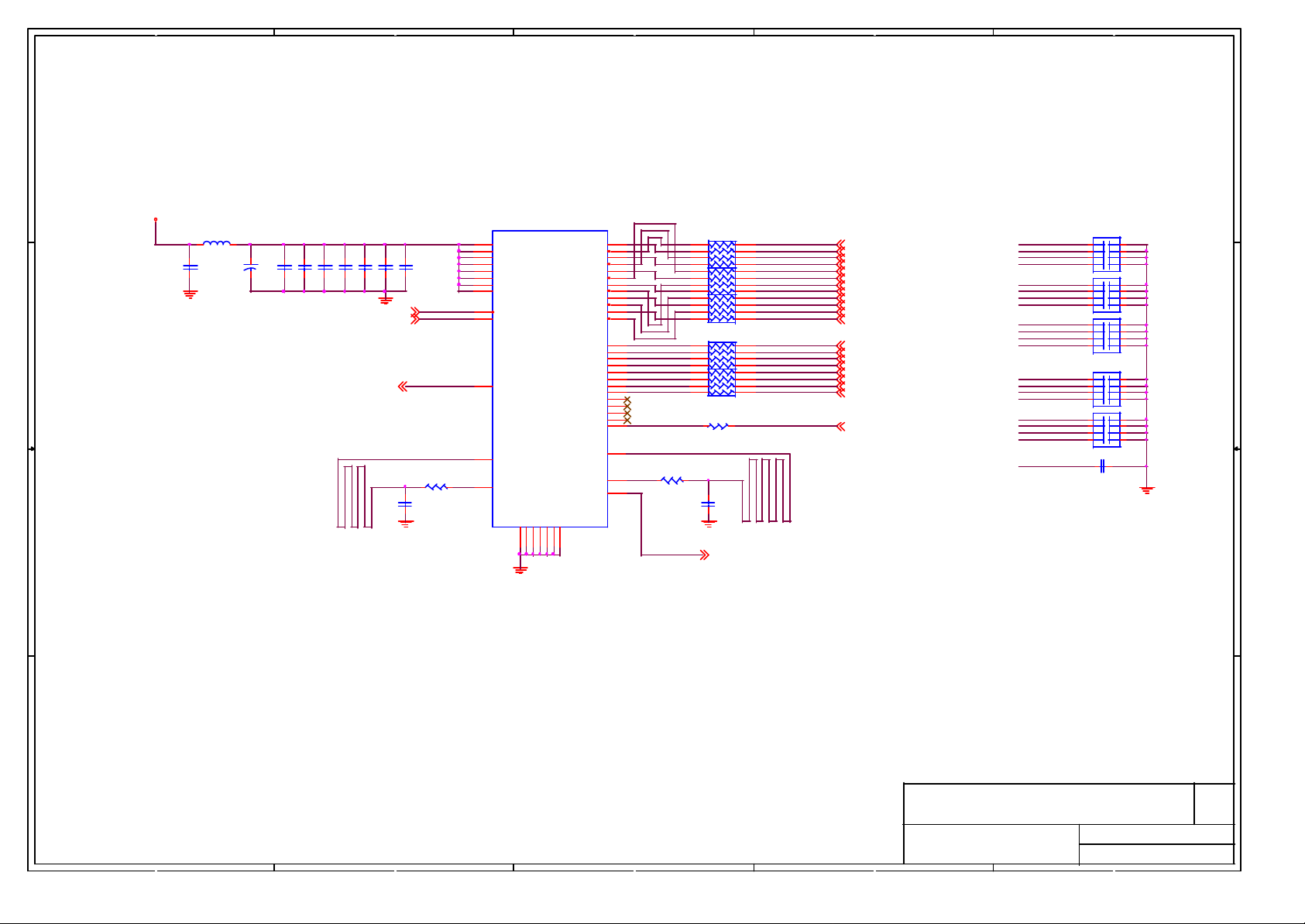

CLOCK BUFFER

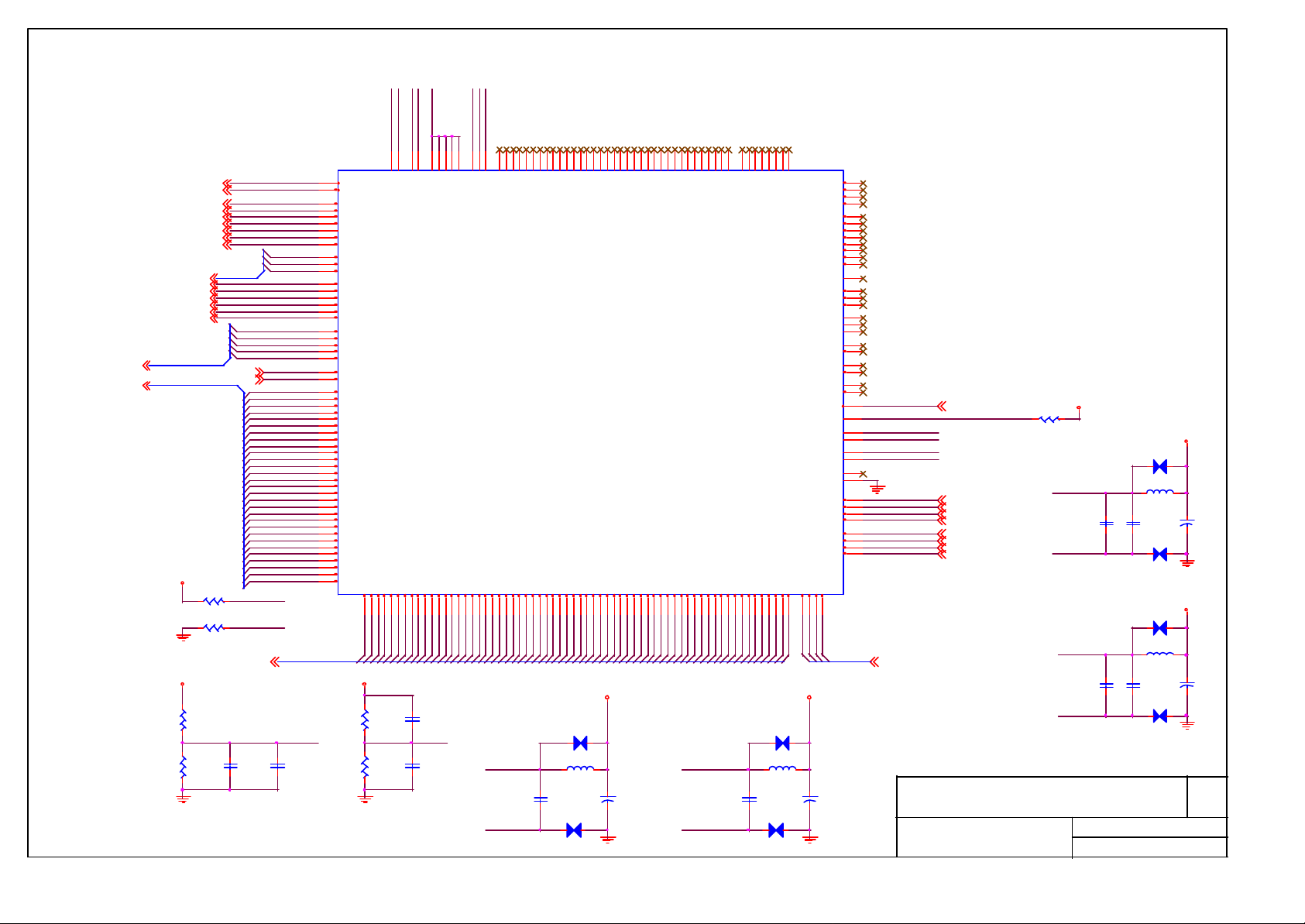

mPGA478-B INTEL CPU Sockets

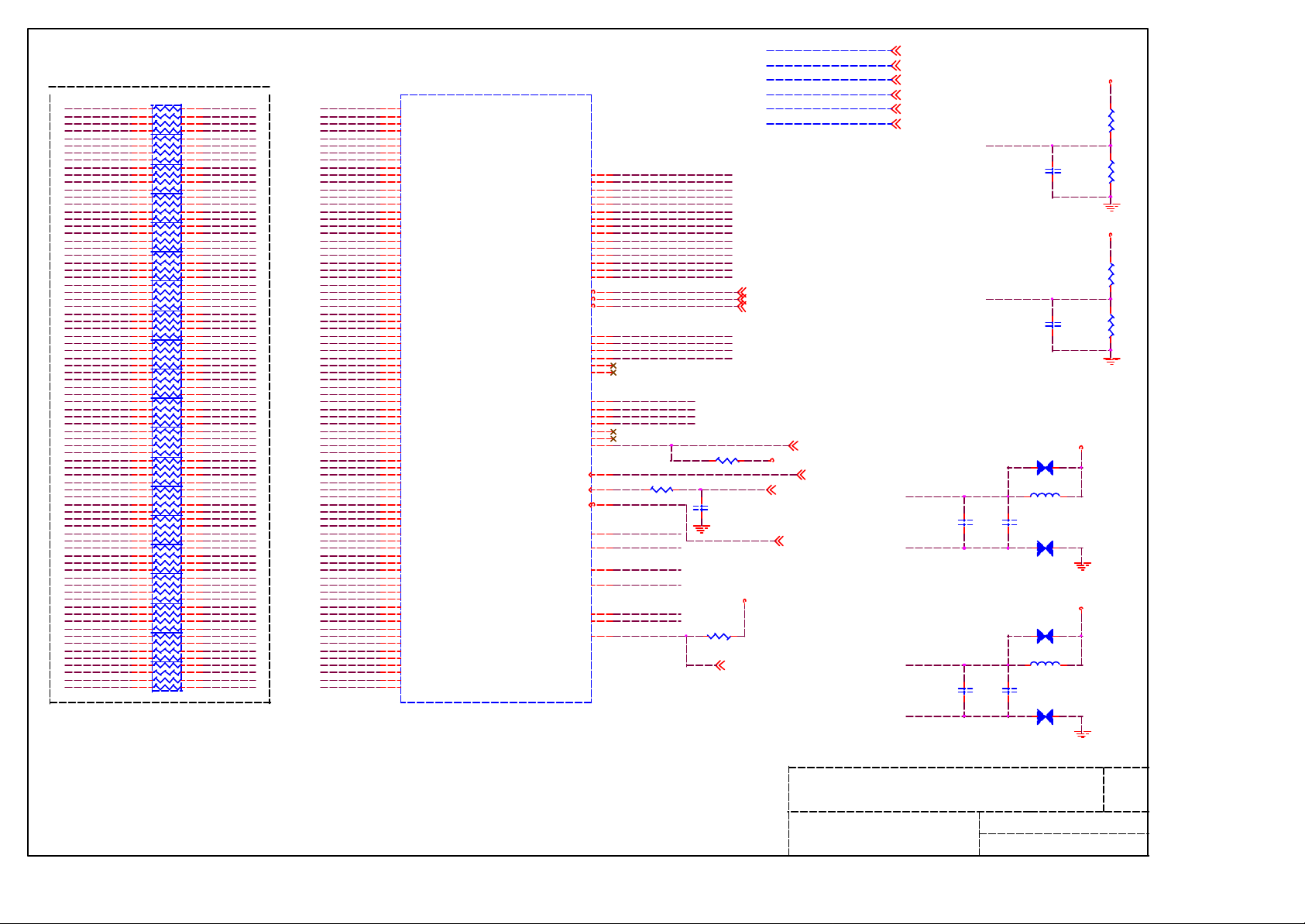

SIS 650GL NORTH BRIDGE

DDR DDR1 & DDR2

SDR DIMM1 & DIMM2

DDR Terminator

AUDIO CODEC

SIS 962L SOUTH BRIDGE

LAN CONTROLLER (RTL8201BL MII PHY)

PCI SLOTS ( PCI 1-3 )

KB/MS Connector & FAN Connector

IDE Connectors

USB Connector

ATX POWER Connector & VGA Connector

LPC I/O(W83697HF) & BIOS

PARALLEL & SERIAL PORTS

VRM 9.0 (INTERSIL HIP6302)

MS-5 ACPI CONTROLLER

3

4

5 - 6

7 - 10

11

12

13

14

15 - 17

18

19

20

21

22

23

24

25

26

27

SIS 650GL CHIPSET

Willamette/Northwood 478pin mPGA-B Processor Schematics

CPU:

Willamette/Northwood mPGA-478B Processor

System Brookdale Chipset:

SIS 650GL (North Bridge) + 962L (South Bridge)

On Board Chipset:

LPC Super I/O -- W83697HF

RTL8201BL MII PHY

Memory Slots:

DDR * 2

SDRAM * 2

Expansion Slots:

PCI2.2 SLOT* 3

AC'97 Codec :

Realtek ALC650

Decoupling Capacitor

FRONT PANEL

MANUAL PARTS

28

29

30

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

Micro Star Restricted Secret

COVER Sheet

MS-6739

Last Revision Date:

Sheet

Rev

1.0

Tuesday, December 17, 2002

1 30

of

VGA CON.

PCI slot 3 PCI slot 2 PCI slot 1

IDE 2 IDE 1

KEYBOA RD

/MOUSE

LEGACY

ROM

System Block Diagram

VGA CONNECTOR

PS/2

SOCKET 478

Host Bus

SIS 650GL

Hyper ZIP

SIS 962L

LPC BUS

LPC SUPER I/O

DDR DIMM

AC'97

AUDIO CODEC

H/W MONITOR

USB 0

USB 1

DDR2DDR1

SDRAM DIMM

Lan

USB 3

USB 4

GPIO_0

GPIO_1

GPIO_2

GPIO_3 EXTSMI#

GPIO_4 Pull-Down

GPIO_5

GPIO_6

GPIO_7 AUX

GPIO_8

GPIO_9

GPIO_10

GPIO_11

GPIO_12 I/O

GPIO_13

GPIO_14

DIMM2DIMM1

GPIO_15

GPIO_16

GPIO_17

GPIO_18

GPIO_19

GPIO_20

GPIO_21

GPIO_22

GPIO_23

GPIO_24 I

I/O

MAIN

I/O

MAIN

I/O

MAIN

I/O

MAIN

I/O

MAIN

I/O

MAIN

I/O

MAIN

I/O

AUX

I/O

AUX

I/O

AUX

I/O

I/O

AUX

AUX

I/O

AUX

I/O

AUX

I/O

AUX

I/O

AUX

I/O

AUX

I/O

AUX

I/O

AUX

I/O

AUX

I

AUX EESK

I

AUX

I

AUX

AUX

PCI Routing

DEVICES

PCI SLOT 2

PCI SLOT 3

PCI SLOT 1

INT#

INT#B

INT#C

INT#D

INT#A

INT#C

INT#D

INT#A

INT#B

INT#D

INT#A

INT#B

INT#C

Flash Rom protection H: Disable, L: Enable

Pull-Down

THERM#

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

Pull-Down(for SIS962L)

Pull-Up

RESERVED

Pull-Down

KBDAT

KBCLK

MSDAT

MSCLK

SMBCLK

SMBDAT

EEDI

DDEO

EECS

IDSEL

AD17

AD18

AD19

REQ#/GNT#

PREQ#0

PGNT#0

PREQ#1

PGNT#1

PREQ#2

PGNT#2

CLOCK

PCICLK0

PCICLK1

PCICLK2

GPIO Table on SIS962L

FLOPPYPRINTERCOMGAME/MIDIGPIOS

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

Micro Star Restricted Secret

BLOCK DIAGRAM

MS-6739

Last Revision Date:

Monday, December 16, 2002

Sheet

2 30

of

Rev

1.0

VCC3

L42

X_80_0805

C140

X_4.7U/0805

NPN-MBT3904LT1-S-SOT23

VCCP

R154

10K

D13

AC

X_1N4148-S-LL34-75V

CP35

X_COPPER

CB115

CB98

0.1u

X_0.1u

VCC3 VCC3

R155

10K

Q21

C130

X_10p

4.7U/0805

CB107

0.1u

VCC3

C124

CB102

0.1u

CB96

X_0.1u

CB99

CB100

0.1u

X_0.1u

R157

10K

Q20

NPN-MBT3904LT1-S-SOT23

VCC3

R170

CP37 X_COPPER

L43

X_80_0805

CB2

0.1u

CB103

0.1u

0.1u

CB101

CB116

0.1u

475

Main Clock Generato r

U13

ICS952004AF

1

VDDREF

11

VDDZ

13

VDDPCI

19

VDDPCI

28

VDD48

29

VDDAGP

42

VDDCPU

48

VDDSD

12

PCI_STOP#

45

CPU_STOP#

5

VSSREF

8

VSSZ

18

VSSPCI

24

VSSPCI

25

VSS48

32

VSSAGP

41

VSSCPU

46

VSSSD

33

PD#/VTT_PWRGD

38

IREF

36

VDDA

CB104

X_102P

37

VSSA

CPUCLK0

CPUCLK#0

CPUCLK1

CPUCLK#1

SDCLK

AGPCLK0

AGPCLK1

ZCLK0

ZCLK1

PCICLK_F0/FS3

PCICLK_F1/FS4

PCICLK0

PCICLK1

PCICLK2

PCICLK3

PCICLK4

PCICLK5

REF0/FS0

REF1/FS1

REF2/FS2

48M

24_48M/MULTISEL

SCLK

SDATA

40

39

44

43

47

31

30

9

10

FS3 96XPCLK

14

FS4 SIOPCLK

15

16

17

20

21

22

23

2

FS0

FS1

3

FS2

4

27

26

35

34

R186

R182

R184 33

R185

R183

R187 33

R218

R219 22

RN26 8P4R-33

R217

RN27 8P4R-33

R188

R189

7 8

5 6

3 4

1 2

7 8

5 6

3 4

1 2

33

33

33

22

22

33

22

22

SMBCLK

SMBDAT

CPUCLK1

CPUCLK-1

CPUCLK0

CPUCLK-0

SDCLK

AGPCLK0

ZCLK0

ZCLK1

PCICLK1

PCICLK2

UCLK48M

SIO48MMULTISEL

SMBCLK 4,11,12,16,27

SMBDAT 4,11,12,16,27

CPUCLK1 7

CPUCLK-1 7

CPUCLK0 5

CPUCLK-0 5

SDCLK 8

AGPCLK0 7

ZCLK0 9

ZCLK1 15

96XPCLK 15

SIOPCLK 24

PCICLK1 19

PCICLK2 19

PCICLK3 19

REFCLK0

REFCLK1

APICCLK

REFCLK2

UCLK48M 17

SIO48M 24

REFCLK0 9

REFCLK1 16

APICCLK 16

REFCLK2 14

CPUCLK0

CPUCLK-0

CPUCLK1

CPUCLK-1

SDCLK

AGPCLK0

ZCLK0

ZCLK1

PCICLK3

PCICLK2

PCICLK1

SIOPCLK

96XPCLK

REFCLK2

APICCLK

REFCLK1

REFCLK0

UCLK48M

SIO48M

R171

R172

R173 49.9

R174

C144 X_10p

C141 X_10p

C172 X_10p

C173 X_10p

C158 X_10p

CN9

1 2

3 4

5 6

7 8

X_8P4C_10p

CN10

1 2

3 4

5 6

7 8

8P4C_10p

C142 10p

C143 10p

49.9

49.9

49.9

FS0~FS4 internal Pull-Down 120K

VCC3

X_2.7K

FS0

FS1

FS3

R221 X_10K

R228 X_10K

R288 X_2.7K

100 100

100133

BSEL0 5

FS2

FS4

6666666633

R222 2.7K

R227 X_2.7K

R226

R290 X_10K

FS4 FS3 FS2 FS1 FS0 CPU SDRAM ZCLK AGP PCI

0 0 0 0

0 01111

XIN

6

14M-32pf-HC49S-D

27p

33

C155

XOUT

7

Y2

C150

27p

MULTISEL internal Pull-Up 120K

R291 X_10K

MULTISEL

R180 X_10KR298 X_2.7K

VCC3

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

Micro Star Restricted Secret

CLOCK GEN

MS-6739

Last Revision Date:

Sheet

Monday, January 06, 2003

3 30

of

Rev

1.0

5

D D

4

3

2

1

VCC3

L50

80_0805

CB48

0.1u

C C

B B

C243

4.7U/0805

CB151

0.1u

CB152

0.1u

CB153

0.1u

CB157

0.1u

CB155

CB156

CB159

0.1u

0.1u

0.1u

FWDSDCLKO

10p

SMBCLK

SMBDAT

SMBCLK3,11,12,16,27

SMBDAT3,11,12,16,27

FWDSDCLKO8

FB_SDR

R279

22C241

U7 ICS93725

1

VDD3.3/2.5

7

VDD3.3/2.5

14

VDD3.3/2.5

20

VDD3.3/2.5

27

VDD3.3/2.5

33

VDD3.3/2.5

39

VDD3.3/2.5

45

VDD3.3/2.5

26

SCLK

25

SDATA

10

BUFFER_IN

23

SDFB_IN

22

SDFB_OUT

GND

GND

GND

GND

GND

6131924283440

SDRAM10

SDRAM11

SDRAM12

DDRFB_IN

DDRFB_OUT

SEL_DDR

GND

GND

CLK0

CLK#0

CLK1

CLK#1

CLK2

CLK#2

CLK3

CLK#3

CLK4

CLK#4

CLK5

CLK#5

SDRAM0

SDRAM1

SDRAM2

SDRAM3

SDRAM4

SDRAM5

SDRAM6

SDRAM7

SDRAM8

SDRAM9

30

29

32

31

36

35

38

37

42

41

44

43

2

3

4

5

8

9

11

12

15

16

17

18

21

47

46

48

RN36

8P4R-0

RN39

8P4R-0

RN89

8P4R-0

RN90

8P4R-10

RN40

8P4R-10

R276 10

FB_DDR

R297

22

Low--SDR

Hi--DDR

C265

X_10p

SDRSEL#1 8,12

DDRCLK0-

12

DDRCLK0+

34

56

DDRCLK1DDRCLK1+

78

DDRCLK2-

12

DDRCLK2+

34

DDRCLK3-

56

78

DDRCLK3+

DDRCLK4-

12

DDRCLK4+

34

DDRCLK5-

56

DDRCLK5+

78

SDCLK0

12

SDCLK1

34

56

SDCLK2

SDCLK3

78

SDCLK4

12

SDCLK5

34

SDCLK6

56

78

SDCLK7

SDCLKI

for SDR memory read

DDRCLK0- 11

DDRCLK0+ 11

DDRCLK1- 11

DDRCLK1+ 11

DDRCLK2- 11

DDRCLK2+ 11

DDRCLK3- 11

DDRCLK3+ 11

DDRCLK4- 11

DDRCLK4+ 11

DDRCLK5- 11

DDRCLK5+ 11

SDCLK0 12

SDCLK1 12

SDCLK2 12

SDCLK3 12

SDCLK4 12

SDCLK5 12

SDCLK6 12

SDCLK7 12

SDCLKI 8

DDRCLK1+

DDRCLK1DDRCLK0+

DDRCLK0-

DDRCLK3+

DDRCLK3DDRCLK2+

DDRCLK2-

DDRCLK5+

DDRCLK5DDRCLK4+

DDRCLK4-

SDCLK3

SDCLK2

SDCLK1

SDCLK0

SDCLK7

SDCLK6

SDCLK5

SDCLK4

SDCLKI

CN13 X_8P4C_10p

1 2

3 4

5 6

7 8

CN18 X_8P4C_10p

1 2

3 4

5 6

7 8

CN19 X_8P4C_10p

1 2

3 4

5 6

7 8

CN20 X_8P4C_10p

1 2

3 4

5 6

7 8

CN17 X_8P4C_10p

1 2

3 4

5 6

7 8

C248 X_10p

A A

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

5

4

3

http://www.msi.com.tw

2

Micro Star Restricted Secret

CLOCK BUFFER

MS-6739

Last Revision Date:

Monday, December 16, 2002

Sheet

4 30

1

Rev

1.0

of

Trace : 10

mil width

10mil

space

BSEL0

0

1

HDBI#[0..3]7

BSEL03

HD#[0..63]7

STPCLK#16

HDRDY#7

HDEFER#7

CPU_TMPA24

VTIN_GND24

CPUSLP#16

FSB

100 MHz

133 MHz

CPU_GD7

CPURST#7

FERR#16

HINIT#16

HDBSY#7

HTRDY#7

HADS#7

HLOCK#7

HBNR#7

HITM#7

HBPRI#7

IGNNE#16

SMI#16

A20M#16

HIT#7

R220 X_0

HDBI#0

HDBI#1

HDBI#2

HDBI#3

ITP_TD I

ITP_TDO

ITP_TMS

ITP_TRST#

ITP_TC K

CPU_TMPA

THERMTRIP#

PROCHOT#

IGNNE#

SMI#

A20M#

CPUSLP#

CPU_GD

CPURST#

HD#63

HD#62

HD#61

HD#60

HD#59

HD#58

HD#57

HD#56

HD#55

HD#54

HA#[3..31]7

AF26

AB26

AE21

AF24

AF25

AB23

AB25

AA24

AA22

AA25

W25

W26

E21

G25

P26

V21

AC3

AA3

W5

AB2

G1

G4

G2

A22

AD2

AD3

AD6

AD5

Y21

Y24

Y23

Y26

V24

U4A

V6

B6

Y4

H5

H2

J6

F3

E3

D2

E2

C1

D5

F7

E6

D4

B3

C4

A2

C3

B2

B5

C6

A7

DBI0#

DBI1#

DBI2#

DBI3#

IERR#

MCERR#

FERR#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

SLP#

RESERVED0

RESERVED1

RESERVED2

RESERVED3

RESERVED4

RESERVED5

RESERVED6

BSEL0

BSEL1

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

D53#

V22

HD#53

CPU SIGNAL BLOCK

HA#29

T26

HD#44

HA#28

A29#

D44#

R24

HD#43

HA#27

A28#

D43#

R25

HD#42

HA#26

A27#

D42#

P24

HD#41

HA#25

A26#

D41#

R21

HD#40

HA#24

A25#

D40#

N25

HD#39

HA#23

A24#

D39#

N26

HD#38

A23#

D38#

HA#31

HA#30

AB1Y1W2V3U4T5W1R6V2T4U3P6U1T2R3P4P3R2T1N5N4N2M1N1M4M3L2M6L3K1L6K4K2

A35#

A34#

A33#

A32#

A31#

A30#

D52#

D51#

D50#

D49#

D48#

D47#

D46#

D45#

U21

V25

U23

U24

U26

T23

T22

T25

HD#50

HD#49

HD#52

HD#48

HD#45

HD#51

HD#47

HD#46

HA#22

M26

HD#37

HA#21

A22#

D37#

N23

HD#36

HA#20

A21#

D36#

M24

HD#35

HA#19

A20#

D35#

P21

HD#34

HA#18

A19#

D34#

N22

HD#33

HA#17

A18#

D33#

M23

HD#32

HA#16

A17#

D32#

H25

HD#31

A16#

D31#

HA#15

K23

HD#30

HA#14

A15#

D30#

J24

HD#29

HA#13

A14#

D29#

L22

HD#28

HA#12

A13#

D28#

M21

HD#27

HA#11

A12#

D27#

H24

HD#26

HA#10

A11#

D26#

G26

HD#25

HA#9

A10#

D25#

L21

HD#24

HA#8

A9#

D24#

D26

HD#23

HA#7

A8#

D23#

F26

HD#22

HA#6

A7#

D22#

E25

HD#21

HA#5

A6#

D21#

F24

HD#20

HA#4

A5#

D20#

F23

HD#19

HA#3

A4#

D19#

G23

HD#18

A3#

D18#

AE25A5A4

DBR#

Differential

Host Data

Strobes

D17#

D16#

D15#

D14#

E24

H22

D25

J21

D23

HD#17

HD#14

HD#13

HD#15

HD#16

AD26

AC26

ITP_CLK1

ITP_CLK0

VCC_SENSE

VSS_SENSE

D13#

D12#

D11#

D10#

D9#

C26

H21

G22

B25

C24

HD#9

HD#8

HD#10

HD#12

HD#11

D8#

C23

CPU GTL REFERNCE VOLTAGE BLOCK

VCCP

VID[0..4] 26

VID0

VID1

VID2

VID4

VID3

AE1

AE2

AE3

AE4

AE5

VID4#

VID3#

VID2#

VID1#

VID0#

GTLREF3

GTLREF2

GTLREF1

GTLREF0

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

BCLK1#

BCLK0#

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

COMP1

COMP0

DP3#

DP2#

DP1#

DP0#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

LINT1/NMI

LINT0/INTR

D7#

D6#

D5#

D4#

D3#

D2#

D1#

D0#

C21

HD#4

A25

HD#3

A23

HD#2

B22

HD#1

B21

HD#0

PGA-S478-A10

B24

D22

HD#6

HD#7

HD#5

AA21

AA6

F20

F6

AB4

AA5

Y6

AC4

AB5

AC6

H3

J3

J4

K5

J1

AD25

A6

Y3

W4

U6

AB22

AA20

AC23

AC24

AC20

AC21

AA2

AD24

AF23

AF22

F4

G5

F1

V5

AC1

H6

P1

L24

L25

K26

K25

J26

R5

L5

W23

P23

J23

F21

W22

R22

K22

E22

E5

D1

GTLREF1

BPM#5

BPM#4

BPM#1

BPM#0

HREQ#4

HREQ#3

HREQ#2

HREQ#1

HREQ#0

TESTHI11

TESTHI10

TESTHI9

TESTHI8

RS#2

RS#1

RS#0

R52 49.9

R55 49.9

R51 56

R32 1K

HREQ#[0..4] 7

CPUCLK-0 3

CPUCLK0 3

RS#[0..2] 7

HBR#0 7

* Short trace

HADSTB#1 7

HADSTB#0 7

HDSTBP#3 7

HDSTBP#2 7

HDSTBP#1 7

HDSTBP#0 7

HDSTBN#3 7

HDSTBN#2 7

HDSTBN#1 7

HDSTBN#0 7

NMI 16

INTR 16

VCCP

Length < 1.5inch.

GTLREF1

2/3*Vccp

C37 R39

C32

220p

220p

R38

49.9RST

C27

1u

100RST

Every pin put one 220pF cap near it.

Trace Width 15mils, Space 15mils.

Keep the voltage dividers within 1.5 inches of the

first GTLREF Pin

CPU ITP BLOCK

ITP_TMS

ITP_TDO

ITP_TC K

R41 39

R43 75

R49 27

VCCP

CPU STRAPPING RESISTORS

CLOSED TO SOCKET478

PROCHOT#

CPU_GD

HBR#0

CPURST#

THERMTRIP#

BPM#4

BPM#5

BPM#1

BPM#0

ITP_TDI

ITP_TRST#

CPU_GD

CPURST#

CPUSLP#

CLOSED TO SOCKET478

STPCLK#

CPUSLP#

SMI#

HINIT#

FERR#

IGNNE#

NMI

INTR

A20M#

R44 62

R29 62

R68 49.9

R35 49.9

R66 62

RN3 8P4R-56

7 8

5 6

3 4

1 2

R67 150

R45 680

X_102pC22

X_102pC24

X_0.022uC23

R42 X_56

R31 X_56

R33 X_56

R46 X_56

R40 X_62

RN7

7 8

5 6

3 4

1 2

X_8P4R-56

VCCP

VCCP

VCCP

VCCP

VCCP

TESTHI9

TESTHI8

TESTHI10

RN4

7 8

5 6

3 4

1 2

8P4R-56

VCCP

Title

Micro Star Restricted Secret

mPGA478-B Intel CPU Socket Part 1

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

MS-6739

Last Revision Date:

Sheet

Rev

1.0

Monday, December 16, 2002

5 30

of

AA11

AA13

AA15

AA17

AA19

AA23

AA26

AB10

AB12

AB14

AB16

AB18

AB20

AB21

AB24

AC11

AC13

AC15

AC17

AC19

AC22

AC25

VCC

VSS

F13

VCC

VSS

G21G6G24

F15

F17

VCC

VCC

VSS

VSS

G3H1H23

VCC

VSS

F19

F9

VCC

VSS

VCC_VID

AF4

VCC

VSS

VSS

H26H4J2

AF3

VCC-VID

VCC-VIDPRG

VSS

VSS

VSS

J22

AD20

AE23

VCC-IOPLL

VSS

VSS

VSS

J25J5K21

VSSA

VCCA

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

PGA-S478-A10

AD22

Y5

Y25

Y22

Y2

W6

W3

W24

W21

V4

V26

V23

V1

U5

U25

U22

U2

T6

T3

T24

T21

R4

R26

R23

R1

P5

P25

P22

P2

N6

N3

N24

N21

M5

M25

M22

M2

L4

L26

L23

L1

K6

K3

K24

C19

10u-1206

L9 4.7u-10%

L10 4.7u-10%

C20

10u-1206

VCCP

CPU VOLTAGE BLOCK

VCCP

A10

A12

A14

A16

A18

A20A8AA10

AA12

AA14

AA16

AA18

AA8

AB11

AB13

AB15

AB17

AB19

AB7

AB9

AC10

AC12

AC14

AC16

AC18

AC8

AD11

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

AE16

AE18

AE20

AE6

AE8

AF11

AF13

AF15

AF17

AF19

AF2

AF21

AF5

AF7

AF9

B11

B13

B15

B17

B19B7B9

C10

C12

C14

C16

C18

C20C8D11

D13

D15

D17

D19D7D9

E10

E12

E14

E16

E18

VCC

VSS

F12

VCC

VSS

F14

VCC

VSS

F16

VCC

VCC

VSS

VSS

F18F2F22

VCC

VSS

E20E8F11

VCC

VCC

VSS

VSS

F25F5F8

U4B

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

E19

VSS

E23

VSS

E26

VSS

E4

VSS

VSS

E7E9F10

VCC

VSS

D10

VSS

A11

VSS

A13

VSS

A15

VSS

A17

VSS

A19

VSS

A21

VSS

A24

VSS

A26

VSS

A3

VSS

A9

VSS

AA1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AA4

VSS

AA7

VSS

AA9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AB3

VSS

AB6

VSS

AB8

VSS

VSS

VSS

VSS

VSS

VSS

AC2

VSS

VSS

VSS

AC5

VSS

AC7

VSS

AC9

VSS

AD1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AD10

AD12

AD14

AD16

AD18

AD21

AD4

AD23

AD8

AE11

AE13

AE15

AE17

AE19

AE22

AE24

AE26

AE7

AE9

AF1

AF10

AF12

AF14

AF16

AF18

AF20

AF6

AF8

B10

B12

B14

B16

B18

B23

B20

B26B4B8

C11

C13

C15

C17C2C19

C22

C25C5C7C9D12

D14

D16

D18

D20

D21D3D24D6D8E1E11

E13

E15

E17

CPU DECOUPLING CAPACITORS

VCCP VCCPVCCP

CB41

X_10u-0805

CB5

10u-1206

CB40

X_10u-0805

CB39

X_10u-0805

CB4

10u-1206

CB38

X_10u-0805

PLACE CAPS WITHIN CPU CAVITY

CB8

10u-1206

CB18

10u-1206

CB7

10u-1206

CB16

X_10u-1206

CB6

10u-1206

CB21

X_10u-1206

CB20

10u-1206

CB19

X_10u-1206

CB30

10u-1206

CB29

X_10u-1206

CB28

10u-1206

CB27

X_10u-1206

CB22

10u-1206

Title

Micro Star Restricted Secret

mPGA478-B Intel CPU Socket Part 2

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

MS-6739

Last Revision Date:

Sheet

Rev

1.0

Monday, December 16, 2002

6 30

of

C1XAVSS

C1XAVDD

C4XAVSS

C4XAVDD

HVREF

HPCOMP

HNCOMP

HNCVREF

AC/BE#3

AC/BE#2

AC/BE#1

AC/BE#0

AREQ#

AGNT#

AFRAME#

AIRDY#

ATRDY#

ADEVSEL#

ASERR#

ASTOP#

APAR

RBF#

WBF#

PIPE#

AGP8XDET

ADBIH

ADBIL

SB_STB

SB_STB#

AD_STB0

AD_STB#0

AD_STB1

AD_STB#1

AGPCLK

AGPRCOMP

A1XAVDD

A1XAVSS

A4XAVDD

A4XAVSS

AGPVREF

AGPVSSREF

HDSTBN#3

HDSTBN#2

HDSTBN#1

HDSTBN#0

HDSTBP#3

HDSTBP#2

HDSTBP#1

HDSTBP#0

DBI#3

DBI#2

DBI#1

DBI#0

A27

H27

R25

HDBI#2

HDBI#1

HDBI#0

CT16

X_10u_0805

U8A

F6

F3

H4

K5

C9

A6

G2

G1

G3

G4

H5

H1

H3

E8

F8

D9

D10

B3

C4

B5

A4

K1

L1

C1

D1

B10

M1

B9

A9

B8

A8

M3

M2

F20

F23

K24

P24

F21

F24

L24

N25

SIS-SIS650GL

AGPCLK0

AGPRCOMP

A1XAVDD

A1XAVSS

A4XAVDD

A4XAVSS

HDSTBN#3

HDSTBN#2

HDSTBN#1

HDSTBN#0

HDSTBP#3

HDSTBP#2

HDSTBP#1

HDSTBP#0

HDBI#[0..3] 5

AGPCLK0 3

HDSTBN#3 5

HDSTBN#2 5

HDSTBN#1 5

HDSTBN#0 5

HDSTBP#3 5

HDSTBP#2 5

HDSTBP#1 5

HDSTBP#0 5

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

Micro Star Restricted Secret

SIS 650GL PART1

VDDQ

R140

60.4

A1XAVDD

A1XAVSS

A4XAVDD

A4XAVSS

MS-6739

Last Revision Date:

Sheet

VCC3

CP24

1 2

X_COPPER_0

L34

X_0

CP23

1 2

CP26

1 2

L35

X_80_0603

CP25

1 2

CT22

X_10u_0805

VCC3

CT23

4.7U/0805

CB77

X_103P

CB78

0.1u

CB75

0.1u

X_COPPER_0

X_COPPER_0

CB80

X_103P

X_COPPER_0

Rev

Monday, December 16, 2002

7 30

of

1.0

AH25

AJ25

AH27

AJ27

U21

T21

P21

N21

J17

B20

B19

A19A7F9B7M6M5M4L3L6L4K6L2K3J3K4J2J6J4J1H6F4F1G6E3F5E2E4E1D3D4C2F7C3E6B2D5D6A3D7C5A5C6D8

RS#2

RS#1

RS#0

HD#[0..63]

HVREF

CB65

0.1u

AJ26

AH26

U26

U24

C20

D19

U25

U29

U28

W26

W28

W29

W24

W25

AD24

AA24

AF26

AE25

AH28

AD26

AG29

AE26

AF28

AC24

AG28

AE29

AD28

AC25

AD27

AE28

AF27

AB24

AB26

AC28

AC26

AC29

AA26

AB28

AB27

AA25

AA29

AA28

V26

T27

T24

T26

V28

T28

V24

V27

Y27

Y26

Y24

Y28

CPUCLK

CPUCLK#

DEFER#

HLOCK#

HTRDY#

CPURST#

CPUPWRGD

BPRI#

BREQ0#

RS#2

RS#1

RS#0

ADS#

HITM#

HIT#

DRDY#

DBSY#

BNR#

HREQ#4

HREQ#3

HREQ#2

HREQ#1

HREQ#0

HASTB#1

HASTB#0

HA#31

HA#30

HA#29

HA#28

HA#27

HA#26

HA#25

HA#24

HA#23

HA#22

HA#21

HA#20

HA#19

HA#18

HA#17

HA#16

HA#15

HA#14

HA#13

HA#12

HA#11

HA#10

HA#9

HA#8

HA#7

HA#6

HA#5

HA#4

HA#3

HD#63

B21

HD#63

75

C1XAVSS

C1XAVDD

C4XAVSS

HOST

HD#62

HD#61

HD#60

HD#59

HD#58

HD#57

HD#56

F19

A21

E19

D22

D20

B22

C22

B23

HD#59

HD#58

HD#57

HD#62

HD#61

HD#55

HD#60

HD#56

R80

150

HNCVREF

R81

HVREF0

C4XAVDD

HD#55

HD#54

HD#53

A23

D21

HD#54

HD#53

CB57

X_0.1u

CB55

0.1u

HVREF1

HD#52

F22

HD#52

HVREF2

HD#51

D24

D23

HD#51

ST0

ST1

ST2

AAD0

AAD1

AAD2

AAD3

AAD4

AAD5

AAD6

AAD7

AAD8

AAD9

AAD10

AAD11

AAD12

AAD13

AAD14

HVREF3

HVREF4

HPCOMP

HNCOMP

HNCOMPVREF

AAD15

650GL-1

HD#50

HD#49

HD#48

HD#47

HD#46

HD#45

HD#44

HD#43

HD#42

HD#41

HD#40

HD#39

HD#38

HD#37

HD#36

HD#35

HD#34

HD#33

HD#32

HD#31

HD#30

HD#29

HD#28

HD#27

HD#26

HD#25

C24

B24

E25

E23

D25

A25

C26

B26

B27

D26

B28

E26

F28

G25

F27

F26

G24

H24

G29

J26

G26

J25

H26

G28

H28

J24

HD#32

HD#31

HD#30

HD#50

HD#49

HD#48

HD#47

HD#46

HD#44

HD#45

C1XAVDD

C1XAVSS

HD#43

HD#42

HD#41

HD#39

HD#40

HD#38

HD#37

HD#36

HD#33

HD#35

HD#34

CP8

1 2

X_COPPER_0

L19

X_0

CB45

0.1u

CP11

1 2

X_COPPER_0

HD#29

HD#28

HD#24

HD#27

HD#26

HD#25

CT15

X_10u_0805

AAD16

HD#24

K28

HD#23

AAD17

HD#23

J29

HD#22

AAD18

HD#22

K27

HD#21

AAD19

AAD20

HD#21

HD#20

J28

HD#20

AAD21

HD#19

M24

HD#19

AAD22

HD#18

L26

HD#18

AAD23

HD#17

K26

L25

HD#17

HD#16

C4XAVDD

C4XAVSS

AAD24

AAD25

HD#16

HD#15

L28

HD#15

AAD26

HD#14

M26

HD#14

AAD27

HD#13

P26

HD#13

L29

HD#12

AAD28

AAD29

AAD30

AAD31

AGP

HD#12

HD#11

HD#10

HD#9

HD#8

N24

N26

M27

N28

HD#9

HD#8

HD#11

HD#10

HLOCK#5

HTRDY#5

HBPRI#5

HBR#05

RS#[0..2]

HADSTB#15

HADSTB#05

R83

20

R78

110

CPUCLK1

CPUCLK-1

HDEFER#

HLOCK#

HTRDY#

CPURST#

CPU_GD

HBPRI#

HBR#0

HADS#

HITM#

HIT#

HDRDY#

HDBSY#

HBNR#

HREQ#4

HREQ#3

HREQ#2

HREQ#1

HREQ#0

HADSTB#1

HADSTB#0

HA#31

HA#30

HA#29

HA#28

HA#27

HA#26

HA#25

HA#24

HA#23

HA#22

HA#21

HA#20

HA#19

HA#18

HA#17

HA#16

HA#15

HA#14

HA#13

HA#12

HA#11

HA#10

HA#9

HA#8

HA#7

HA#6

HA#5

HA#4

HA#3

HNCOMP

Rds-on(n) = 10 ohm

HNCVERF = 1/3 VCCP

HPCOMP

Rds-on(p) = 56 ohm

HPCVERF = 2/3 VCCP

HD#[0..63]5

CB66

X_103P

place this capacitor

under 650 solder side

CPUCLK13

CPUCLK-13

HDEFER#5

CPURST#5

CPU_GD5

RS#[0..2]5

HADS#5

HITM#5

HIT#5

HDRDY#5

HDBSY#5

HBNR#5

HREQ#[0..4]5

HA#[3..31]5

HREQ#[0..4]

HA#[3..31]

VCCP

VCCP VCCP

R90

75

R89

150

P27

HD#7

SBA7

HD#7

N29

HD#6

SBA6

SBA5

SBA4

SBA3

HD#6

HD#5

HD#4

HD#3

R24

R28

M28

HD#3

HD#5

HD#4

1 2

X_COPPER_0

CB49

0.1u

CP9

1 2

X_COPPER_0

C7

SBA2

SBA1

SBA0

HD#2

HD#1

HD#0

P28

R26

R29

HD#2

HD#1

HD#0

CP7

L18

X_80_0603

E21

HDBI#3

VCC3VCC3

Rs place close to DIMM1

RMD1 MD1

RMD5 MD5

RMD4 MD4

RMD0 MD0

RMD6 MD6

RMD2 MD2

RDQM0 DQM0

RDQS0 DQS0

RMD9 MD9

RMD8 MD8

RMD7 MD7

RMD3 MD3

RMD11 MD11

RMD10 MD10

RMD15 MD15

RMD14 MD14

RDQM1 DQM1

RMD13 MD13

RDQS1 DQS1

RMD12 MD12

RMD21 MD21

RMD17 MD17

RMD16 MD16

RMD20 MD20

RMD22 MD22

RMD18 MD18

RDQM2 DQM2

RDQS2 DQS2

RMD28 MD28

RMD24 MD24

RMD23 MD23

RMD19 MD19

RMD31 MD31

RMD27 MD27

RMD30 MD30

RMD26 MD26

RDQM3 DQM3

RDQS3 DQS3

RMD25 MD25

RMD29 MD29

RMD37 MD37

RMD33 MD33

RMD36 MD36

RMD32 MD32

RMD38 MD38

RMD34 MD34

RDQM4 DQM4

RDQS4 DQS4

RMD44 MD44

RMD40 MD40

RMD35 MD35

RMD39 MD39

RDQS5 DQS5

RDQM5 DQM5

RMD41 MD41

RMD45 MD45

RMD47 MD47

RMD46 MD46

RMD43 MD43

RMD42 MD42

RMD55 MD55

RDQS6 DQS6

RMD54 MD54

RDQM6 DQM6

RMD53 MD53

RMD52 MD52

RMD49 MD49

RMD48 MD48

RMD56 MD56

RMD60 MD60

RMD51 MD51

RMD50 MD50

RMD62 MD62

RDQM7 DQM7

RMD57 MD57

RMD61 MD61

RMD59 MD59

RMD63 MD63

RMD58 MD58

RDQS7 DQS7

RN48

8P4R-10

RN47

8P4R-10

RN46

8P4R-10

RN45

8P4R-10

RN44

8P4R-10

RN43

8P4R-10

RN42

8P4R-10

RN41

8P4R-10

RN56

8P4R-10

RN55

8P4R-10

RN54

8P4R-10

RN53

8P4R-10

RN52

8P4R-10

RN51

8P4R-10

RN50

8P4R-10

RN49

8P4R-10

RN59

8P4R-10

RN58

8P4R-10

RN57

8P4R-10

RN60

8P4R-10

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

DQM0

DQS0

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

DQM1

DQS1

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

DQM2

DQS2

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

DQM3

DQS3

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

DQM4

DQS4

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

DQM5

DQS5

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

DQM6

DQS6

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

DQM7

DQS7

AJ23

AG22

AH21

AJ21

AD23

AE23

AF22

AF21

AD22

AH22

AD21

AG20

AE19

AF19

AE21

AD20

AD19

AH19

AF20

AH20

AF18

AG18

AH17

AD16

AD18

AD17

AF17

AJ17

AE17

AH18

AD14

AG14

AJ13

AE13

AJ15

AF14

AD13

AF13

AH13

AH14

AD10

AH10

AG10

AF10

AG4

AG6

AG2

AG1

AE9

AD8

AH9

AF9

AD9

AJ9

AH5

AE5

AH3

AF6

AF5

AF4

AH4

AJ3

AE4

AD6

AE2

AC5

AF3

AC6

AD4

AF2

AB6

AD3

AA6

AB3

AC4

AE1

AD2

AC1

AB4

AC2

U8B

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

DQM0

DQS0/CSB#0

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

DQM1

DQS1/CSB#1

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

DQM2

DQS2/CSB#2

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

DQM3

DQS3/CSB#3

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

DQM4

DQS4/CSB#4

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

DQM5

DQS5/CSB#5

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

DQM6

DQS6/CSB#6

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

DQM7

DQS7/CSB#7

SIS-SIS650GL

650GL-2

MA10

MA11

MA12

MA13

MA14

SRAS#

SCAS#

SWE#

CKE0

CKE1

CKE2

CKE3

CKE4

CKE5

S3AUXSW#

SDCLK

FWDSDCLKO

SDRCLKI

SDAVDD

SDAVSS

DDRAVDD

DDRAVSS

DDRVREFA

DDRVREFB

DRAM_SEL

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

CS#0

CS#1

CS#2

CS#3

CS#4

CS#5

AH11

AF12

AH12

AG12

AD12

AH15

AF15

AH16

AE15

AD15

AF11

AG8

AJ11

AG16

AF16

AH8

AJ7

AH7

AE7

AF7

AH6

AJ5

AF8

AD7

AB2

AA4

AB1

Y6

AA5

Y5

Y4

AA3

AD11

AE11

Y1

Y2

AA1

AA2

AJ19

AH2

W3

High for DDR

Low for SDR

R s place close to DIMM1

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

MA14

SRAS#

SCAS#

SWE#

CS#0

CS#1

CS#2

CS#3

CKE0

CKE1

CKE2

CKE3

R103 22

SDAVDD

DDRAVDD

DDRAVSS

DDRVREFA

DDRVREFB

SRAS# 11,12,13

SCAS# 11,12,13

SWE# 11,12,13

CKE: Open Drain

S3AUXSW#

R143 4.7K

FWDSDCLKO

C92

10p_0603

SDCLKI

VCC3SBY

R282

4.7K

SDRSEL#1 4,12

SDCLK

RMD[0..63]

RDQM[0..7]

RDQS[0..7]

MA[0..14]

CS#[0..3]

CKE[0..3]

S3AUXSW# 27

VCC3SBY

SDCLK 3

FWDSDCLKO 4

SDCLKI 4

RMD[0..63] 11,12,13

RDQM[0..7] 11,12,13

RDQS[0..7] 11,12,13

MA[0..14] 11,12,13

CS#[0..3] 11,12,13

CKE[0..3] 11,12

SDAVDD

SDAVSSSDAVSS

DDRAVDD

CB82

0.1u

DDRAVSS

CB81

0.1u

X_103P

DDRVREFA

DDRVREFB

CB90

CP33

1 2

X_COPPER_0

L40

X_80_0603

CB92

X_103P

CP32

1 2

X_COPPER_0

CP31

1 2

X_COPPER_0

L39

X_80_0603

CP29

1 2

X_COPPER_0

CB64

0.1u

CB79

0.1u

VCC3

VCC3

VCCM

VCCM

R86

150

R88

150

R129

150

R128

150

Title

Micro Star Restricted Secret

SIS 650GL PART2

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

MS-6739

Last Revision Date:

Sheet

Rev

1.0

Monday, December 16, 2002

8 30

of

VCC1_8

ZAD[0..15]15

VCC1_8

VCC3

VCC3

CP27

1 2

X_COPPER_0

L36

X_80_0603

R148

150

150

R150

CB91

0.1u

CP28

1 2

X_COPPER_0

L37

X_80_0603

CP30

1 2

X_COPPER_0

L38

X_80_0603

C118

0.1u

ZAD[0..15]

ZVREF

Z1XAVDD

C112

0.1u

Z1XAVSS

Z4XAVDD

C119

0.1u

Z4XAVSS

R142 56

R141 56

NOTE: This page is for universal PCB design( suitable for both 645 or 650)

N B Hardware Trap Table

VDDZCMP

ZCMP_N

ZCMP_P

VSSZCMP

DLLEN#

DRAM_SEL

TRAP0

TRAP1

CSYNC

RSYNC

LSYNC

ZCLK0

ZCLK03

ZUREQ15

ZDREQ15

ZUREQ

ZDREQ

ZSTB0

ZSTB015

ZSTB-0

ZSTB-015

ZSTB1

ZSTB115

ZSTB-1

ZSTB-115

ZAD0

ZAD1

ZAD2

ZAD3

ZAD4

ZAD5

ZAD6

ZAD7

ZAD8

ZAD9

ZAD10

ZAD11

ZAD12

ZAD13 VCOMP

ZAD14 VRSET

ZAD15

ZVREF

VDDZCMP

ZCMP_N

ZCMP_P

VSSZCMP

Z1XAVDD

Z1XAVSS

Z4XAVDD

Z4XAVSS

0

enable PLL disable PLL

SDR DDR

normal NB debug mode

TV selection, NTSC/PAL(0/1) 0

enable VB

e nable VGA interface

e nable panel link

U8C

SIS-SIS650GL

V3

ZCLK

U6

ZUREQ

U1

ZDREQ

T3

ZSTB0

T1

ZSTB#0

P1

ZSTB1

P3

ZSTB#1

T4

ZAD0

R3

ZAD1

T5

ZAD2

T6

ZAD3

R2

ZAD4

R6

ZAD5

R1

ZAD6

R4

ZAD7

P4

ZAD8

N3

ZAD9

P5

ZAD10

P6

ZAD11

N1

ZAD12

N6

ZAD13

N2

ZAD14

N4

ZAD15

U3

ZVREF

V5

VDDZCMP

U4

ZCMP_N

U2

ZCMP_P

V6

VSSZCMP

W1

Z1XAVDD

W2

Z1XAVSS

V2

Z4XAVDD

V1

Z4XAVSS

PCIRST1#24,27

PWRGD16,26,27

RSMRST#16,18,27

ENTEST

PWRGD

RSMRST#

PCIRST1#

PWRGD

RSMRST#

R122 4.7K

C125 X_0.1u

C122 0.1u

1

VGA

Stereo

Glass

HyperZip

650GL-3

PCIRST#

PWROK

AUXOK

TRAP1

TRAP0

Y3W4W6

D11

E10

Default

1(DDR)

TESTMODE2

TESTMODE1

TESTMODE0

A10

F11

C11

0

0

0

1

0

DLLEN#

E11

F10

ENTEST

ENTEST

e mbedded pull-low

(30~50K Ohm)

DCLKAVDD

DCLKAVSS

ECLKAVDD

ECLKAVSS

yes

yes

yes

VOSCI

ROUT

GOUT

BOUT

HSYNC

VSYNC

VGPIO0

VGPIO1

INT#A

CSYNC

RSYNC

LSYNC

VCOMP

VRSET

VVBWN

DACAVDD1

DACAVSS1

DACAVDD2

DACAVSS2

DCLKAVDD

DCLKAVSS

ECLKAVDD

ECLKAVSS

CB70

CB71

0.1u

0.1u

C15

A12

B13

A13

R96 15

F13

R92 15

E13

R93 100

D13

D12

R95

B11

E12

A11

F12

E14

D14

F14

B12

C12

C13

C14

B15

A15

B14

A14

CP15

1 2

X_COPPER_0

L25

CP16

1 2

X_COPPER_0

CP17

1 2

X_COPPER_0

L29 X_80_0603

CP18

1 2

X_COPPER_0

R114 X_0

R105 X_0

R97 X_0

X_80_0603

VCC3

VCC3

100

C76

X_10u_0805

C84

X_10u_0805

for 650 only

REFCLK0

HSYNC

VSYNC

DDC1CLK

DDC1DATA

INTA#

RSYNC

VVBWN

DACAVDD1

DACAVSS1

DACAVDD1

DACAVSS1

DCLKAVDD

DCLKAVSS

ECLKAVDD

ECLKAVSS

ROUT

GOUT

BOUT

Title

RSYNC

R118 4.7K

REFCLK0 3

HSYNC 23

VSYNC 23

DDC1CLK 23

DDC1DATA 23

INTA# 15,19

VVBWN

VCOMP

DACAVDD1

DACAVSS1

Micro Star Restricted Secret

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

VCC3

C94

C96

X_47p

X_47p

CB61

0.1u

CB59

0.1u

SIS 650GL PART3

MS-6739

Last Revision Date:

Sheet

ROUT 23

GOU T 23

BOUT 23

C91

X_47p

VRSET

VCC1_8

L31

80_0603

CB72

0.1u

CP22

1 2

X_COPPER_0

C100

X_10u_0805

L33X_80_0603

Monday, December 16, 2002

9 30

of

R91

130

Rev

1.0

Loading...

Loading...