1

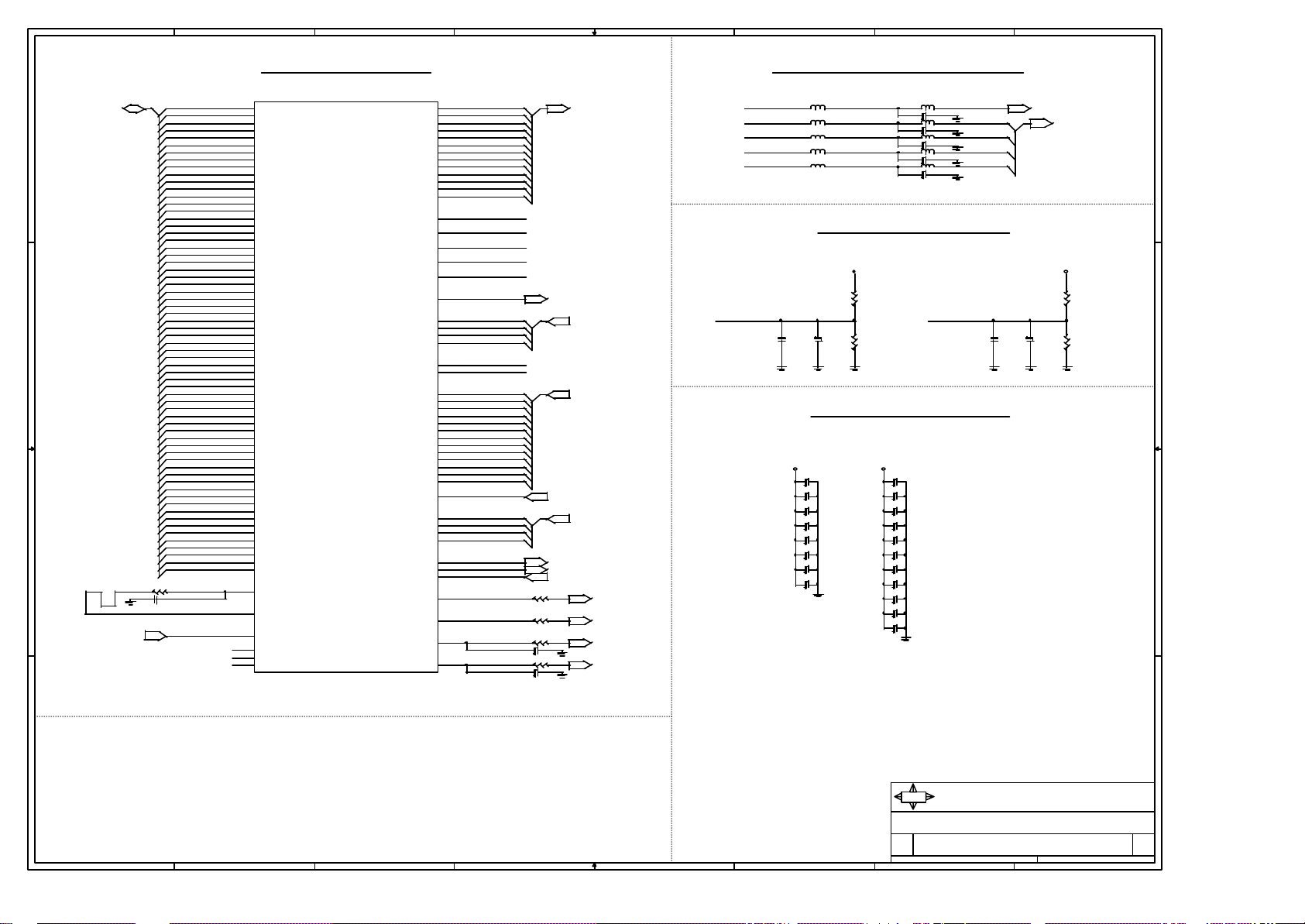

Cover Sheet 1

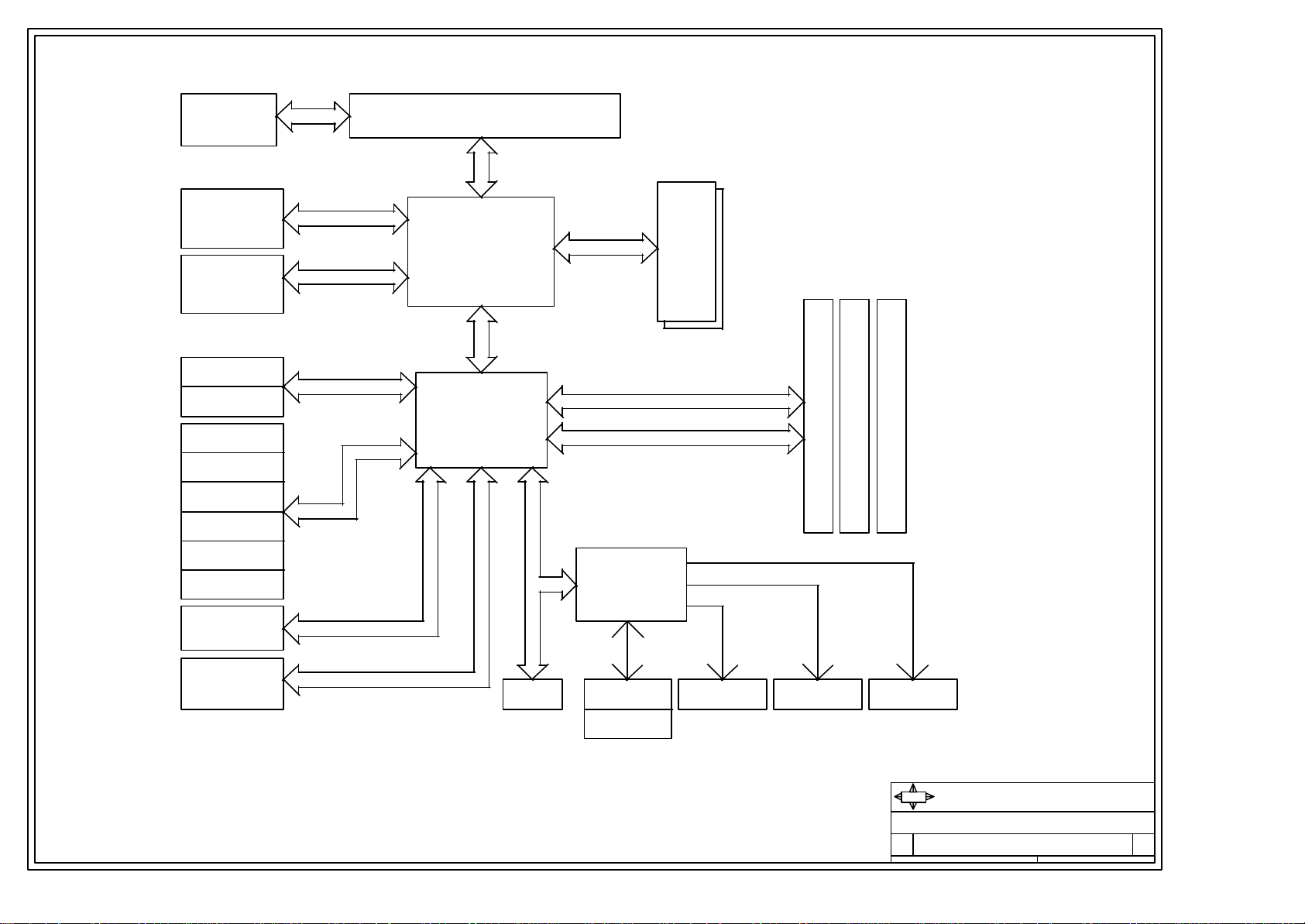

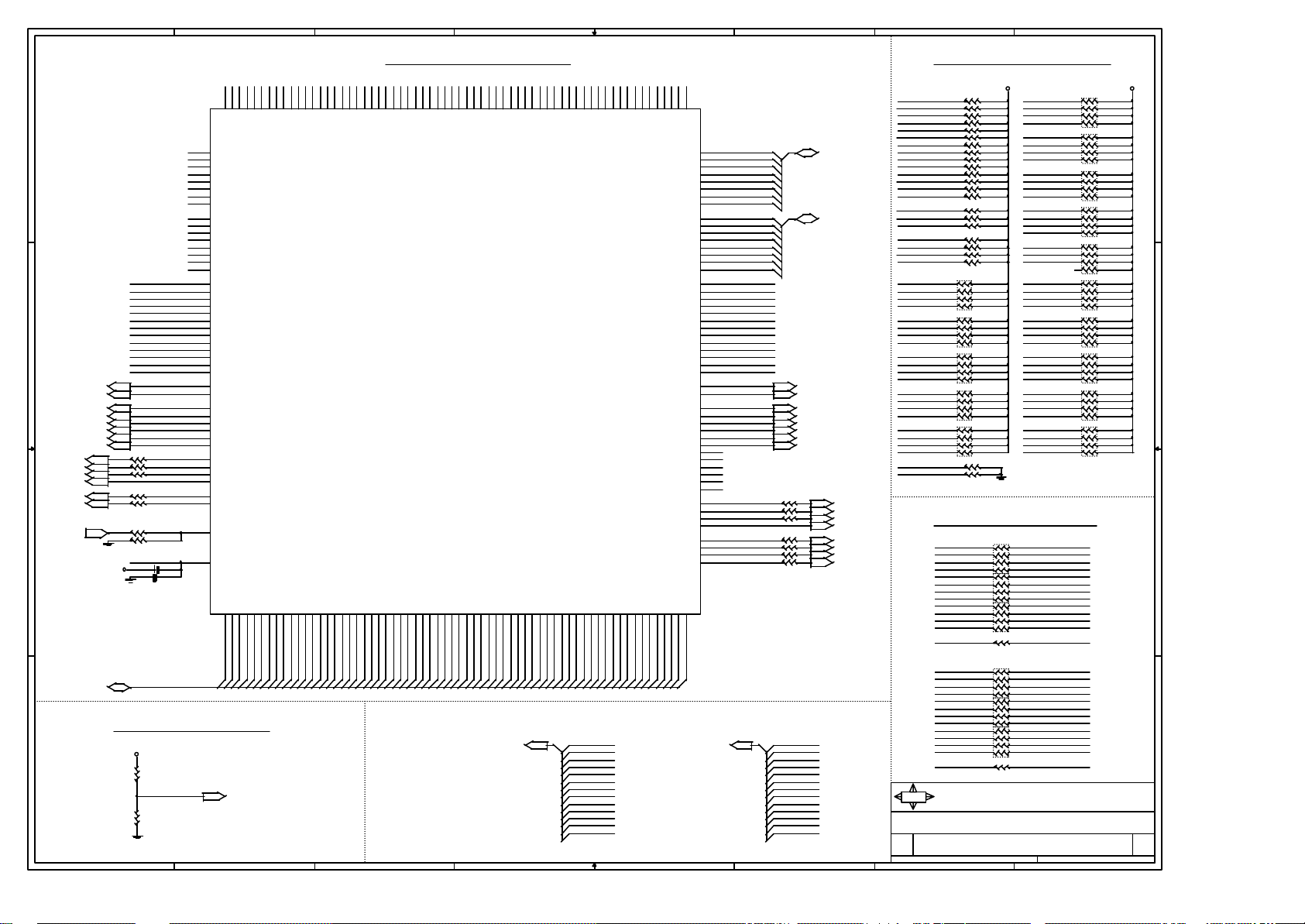

Block Diagram

2

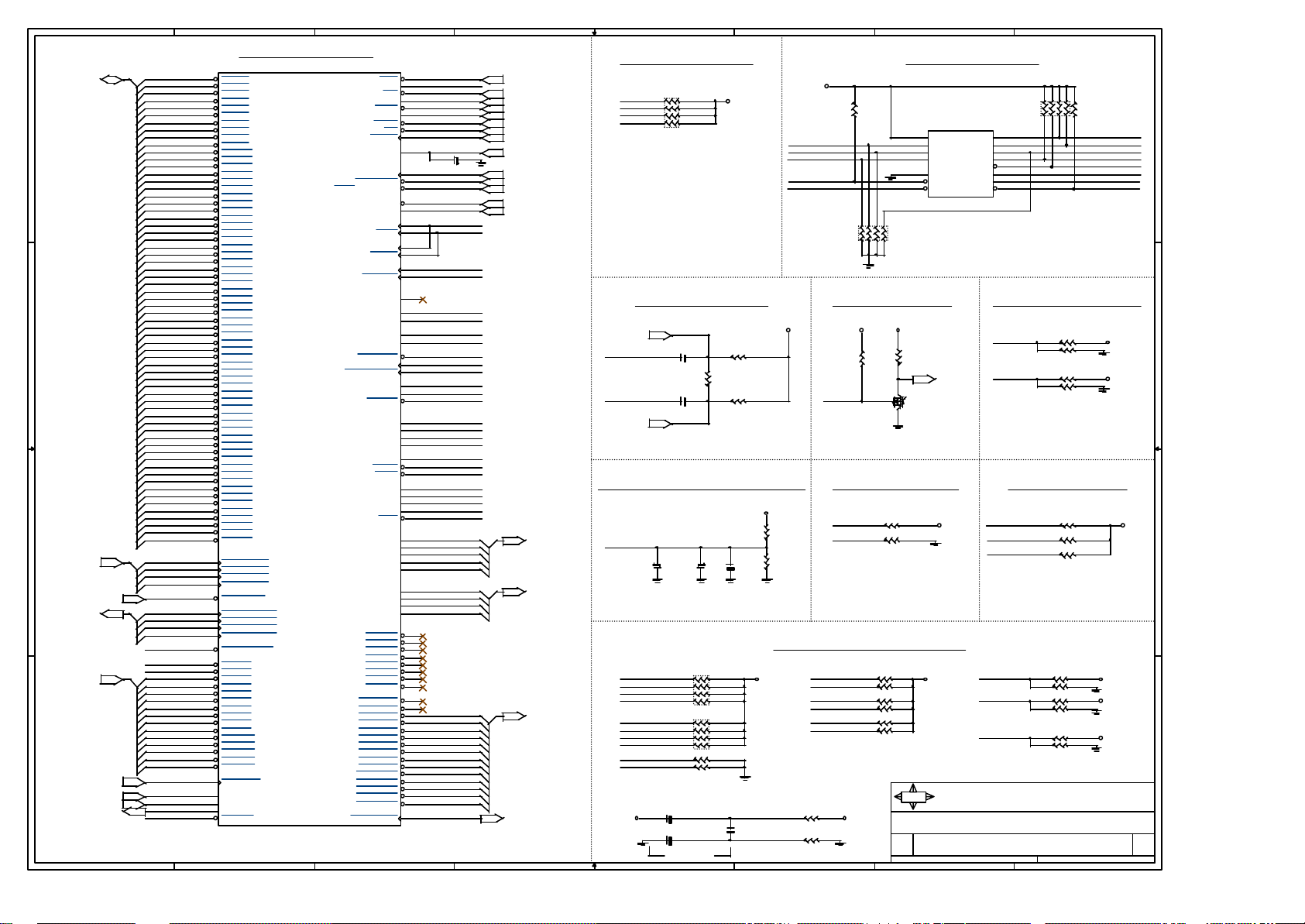

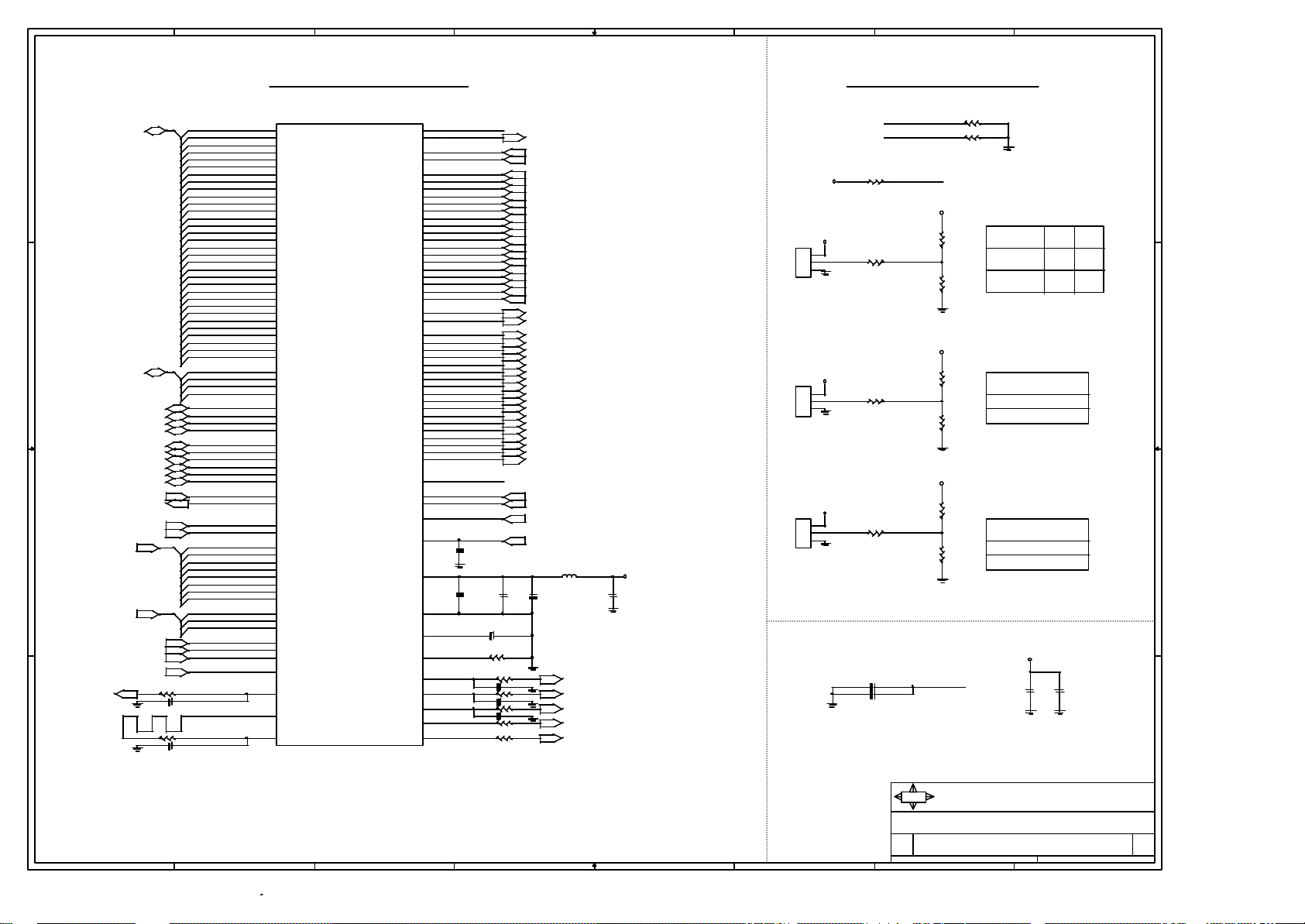

3AMD 462pins SocketA CPU - Signals

ZZTOP (MS-6553)

Nvidia (R) Crush11(nForce IGP 64) + MCP Chipset

Version 0CE0

11/19/2001 Update

AMD Althon/Duron/Palomino Socket 462 Processor

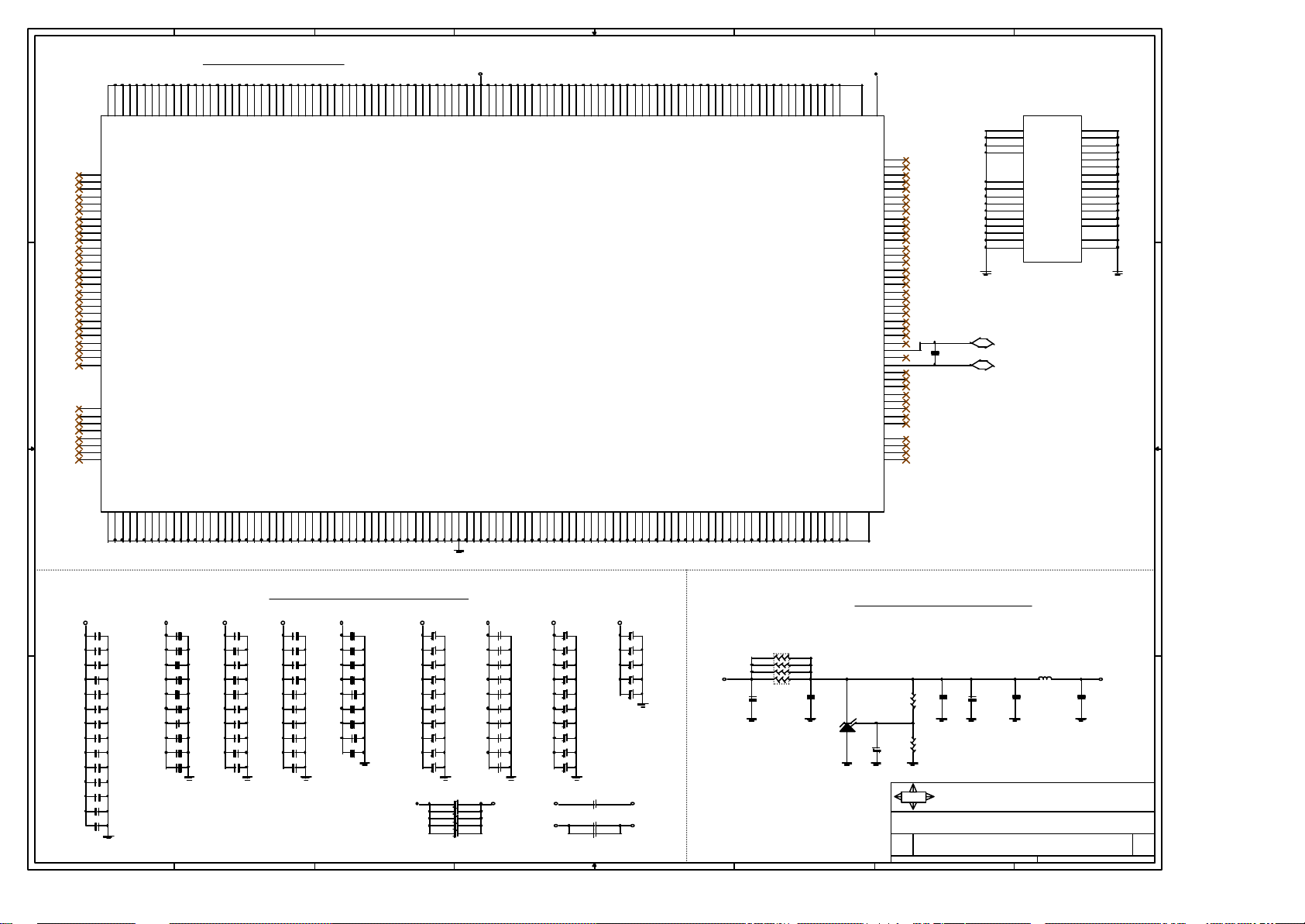

AMD 462pins SocketA CPU - Power 4

CRUSH11 - Host Signals 5

CRUSH11 - Memory Signals 6

CRUSH11 -AGP & LDT Signals 7

CRUSH11- Power & Manual

MCP - PCI & LDT Signals

MCP - CPU & IDE & LPC & MAC & USB Signals

LPC I/O - LPC47B367

AC97 Audio - AD1885

A A

LAN & LPC Flash EEPROM

8

9

10

11

12

13

CPU:

AMD Althon/Duron/Palomino Socket 462 Processor

System Chipset:

Nvidia nForce IGP 64 (North Bridge)

MCP Wep (South Bridge)

On Board Chipset:

BIOS -- LPC EEPROM

AC'97 Codec -- AD1885

LPC Super I/O -- LPC47B367

LAN -- ICS1893AF

DDR System Memory

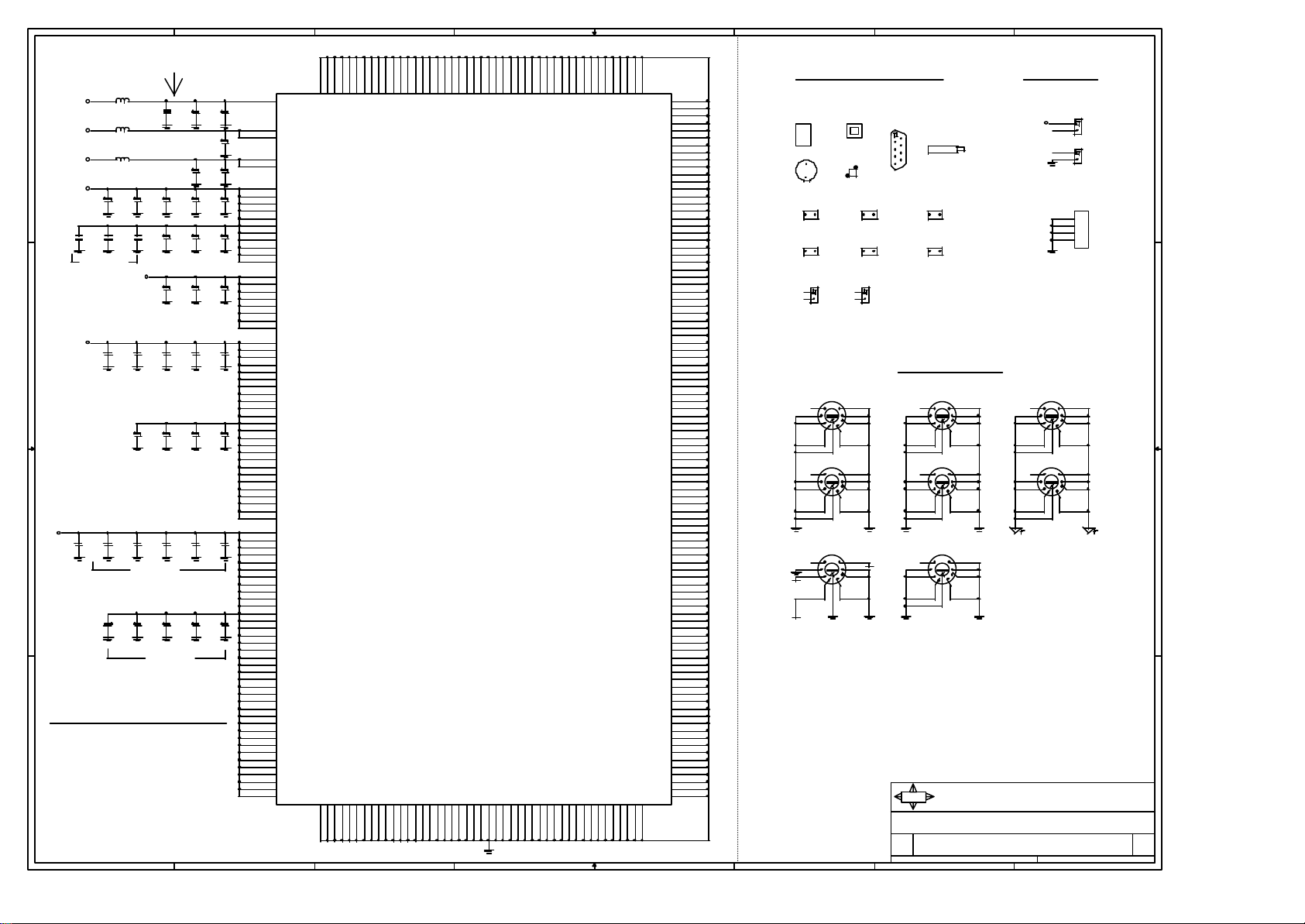

AGP 1.5V Slot & PCI Expansion Riser 15

PCI Slots

ATA33/66/100 IDE & Video Connectors 17

14

16

Expansion Slots:

AGP2.0 SLOT (1.5V) * 1

PCI2.2 SLOT * 3

H/W Monitor & FAN & USB Connectors

PLL Delay & VID Select

ATX & Front Panel

System & LDT & DDR Regulators

VRM 9.2 - Intersil 6301

GPIO

Revision History 1 - 2

18

19

20

21

22

23

24 - 25

Intersil PWM:

Controller: HIP6301

Driver: HIP6601 + HIP6602

Regulators

System : SC1544

DDR VTT: CM8500

LDT : IRU3037

1

MSI

Title

Size Document Number Rev

Date: Sheet of

MICRO-STAR INt'L CO., LTD.

H/W Project Leader : Andy Chen

H/W Project Engineer : Prudence Wang

COVER SHEET

ZZTOP (MS-6553)

1 25Monday, November 19, 2001

0CE0

1

VRM 9.2

Intersil 6301

3-Phase PWM

AGP 1.5V

Connector

Analog

Video

4X w/Fast Write

462-Pin Socket Processor

K7 FSB

CRUSH 11

64bit DDR

Block Diagram

2 DDR

DIMM

Modules

(1+1)

Out

LDT Link

IDE Primary

UltraDMA 33/66/100

PCI CNTRL

PCI Slot 1

PCI Slot 2

PCI Slot 3

IDE Secondary

MCP-1

A A

USB Port 0

PCI ADDR/DATA

USB Port 1

USB Port 2

USB

LPC Bus

USB Port 3

USB Port 4

LPC SIO

USB Port 5

AD1885

AC'97 Link

SMSC

LPC47B367

AC'97 Codec

10/100BaseT

PHY

ICS1893AF

MII

Flash

Keyboard

Mouse

1

Floopy Parallel Serial

MSI

Title

Size Document Number Rev

Date: Sheet of

MICRO-STAR INt'L CO., LTD.

H/W Project Leader : Andy Chen

H/W Project Engineer : Prudence Wang

BLOCK DIAGRAM

ZZTOP (MS-6553)

2 25Monday, November 19, 2001

0CE0

8

SDATA#[0..63](5)

D D

C C

B B

DICLK#[0..3](5)

DIVAL#(5)

DOCLK#[0..3](5)

AIN#[2..14](5)

A A

AICLK#(5)

CFWDRST(5)

CONNECT(5)

PROCRDY(5)

8

SDATA#0

SDATA#1

SDATA#2

SDATA#3

SDATA#4

SDATA#5

SDATA#6

SDATA#7

SDATA#8

SDATA#9

SDATA#10

SDATA#11

SDATA#12

SDATA#13

SDATA#14

SDATA#15

SDATA#16

SDATA#17

SDATA#18

SDATA#19

SDATA#20

SDATA#21

SDATA#22

SDATA#23

SDATA#24

SDATA#25

SDATA#26

SDATA#27

SDATA#28

SDATA#29

SDATA#30

SDATA#31

SDATA#32

SDATA#33

SDATA#34

SDATA#35

SDATA#36

SDATA#37

SDATA#38

SDATA#39

SDATA#40

SDATA#41

SDATA#42

SDATA#43

SDATA#44

SDATA#45

SDATA#46

SDATA#47

SDATA#48

SDATA#49

SDATA#50

SDATA#51

SDATA#52

SDATA#53

SDATA#54

SDATA#55

SDATA#56

SDATA#57

SDATA#58

SDATA#59

SDATA#60

SDATA#61

SDATA#62

SDATA#63

DICLK#0

DICLK#1

DICLK#2

DICLK#3

DOCLK#0

DOCLK#1

DOCLK#2

DOCLK#3

DOVAL#

AIN#0

AIN#1

AIN#2

AIN#3

AIN#4

AIN#5

AIN#6

AIN#7

AIN#8

AIN#9

AIN#10

AIN#11

AIN#12

AIN#13

AIN#14

FILVAL#

AG33

AG37

AG35

7

CPU SIGNAL BLOCK

U13A

AA35

SDATA0

W37

SDATA1

W35

SDATA2

Y35

SDATA3

U35

SDATA4

U33

SDATA5

S37

SDATA6

S33

SDATA7

AA33

SDATA8

AE37

SDATA9

AC33

SDATA10

AC37

SDATA11

Y37

SDATA12

AA37

SDATA13

AC35

SDATA14

S35

SDATA15

Q37

SDATA16

Q35

SDATA17

N37

SDATA18

J33

SDATA19

G33

SDATA20

G37

SDATA21

E37

SDATA22

G35

SDATA23

Q33

SDATA24

N33

SDATA25

L33

SDATA26

N35

SDATA27

L37

SDATA28

J37

SDATA29

A37

SDATA30

E35

SDATA31

E31

SDATA32

E29

SDATA33

A27

SDATA34

A25

SDATA35

E21

SDATA36

C23

SDATA37

C27

SDATA38

A23

SDATA39

A35

SDATA40

C35

SDATA41

C33

SDATA42

C31

SDATA43

A29

SDATA44

C29

SDATA45

E23

SDATA46

C25

SDATA47

E17

SDATA48

E13

SDATA49

E11

SDATA50

C15

SDATA51

E9

SDATA52

A13

SDATA53

C9

SDATA54

A9

SDATA55

C21

SDATA56

A21

SDATA57

E19

SDATA58

C19

SDATA59

C17

SDATA60

A11

SDATA61

A17

SDATA62

A15

SDATA63

W33

SDATAINCLK0

J35

SDATAINCLK1

E27

SDATAINCLK2

E15

SDATAINCLK3

AN33

SDATAINVAL

AE35

SDATAOUTCLK0

C37

SDATAOUTCLK1

A33

SDATAOUTCLK2

C11

SDATAOUTCLK3

AL31

SDTATOUTVAL

AJ29

SADDIN0

AL29

SADDIN1

SADDIN2

AJ37

SADDIN3

AL35

SADDIN4

AE33

SADDIN5

AJ35

SADDIN6

SADDIN7

AL33

SADDIN8

AN37

SADDIN9

AL37

SADDIN10

SADDIN11

AN29

SADDIN12

AN35

SADDIN13

AN31

SADDIN14

AJ33

SADDINCLK

AJ21

CLKFWDRST

AL23

CONNECT

AN23

PROCRDY

AJ31

SFILLVAL

N12-4620011-F02

**All CPU interface are 2.5V tolerant**

7

462-Pin Socket

6

A20M

FERR

INIT

INTR

IGNNE

NMI

RESET

SMI

STPCLK

PWROK

PICCLK

PICD0/BYPASSCLK

PICD1/BYPASSCLK

COREFB-

COREFB+

CLKIN

CLKIN

RSTCLK

RSTCLK

K7CLKOUT

K7CLKOUT

ANALOG

SYSVREFMODE

VREF_SYS

PLLBYPASS

PLLBYPASSCLK

PLLBYPASSCLK

PLLMON1

PLLMON2

PLLTEST

SCANCLK1

SCANCLK2

SCANINTEVAL

SCANSHIFTEN

Part 1

DBRDY

DBREQ

FLUSH

TCK

TDO

TMS

TRST

VID0

VID1

VID2

VID3

VID4

FID0

FID1

FID2

FID3

SCHECK0

SCHECK1

SCHECK2

SCHECK3

SCHECK4

SCHECK5

SCHECK6

SCHECK7

SADDOUT0

SADDOUT1

SADDOUT2

SADDOUT3

SADDOUT4

SADDOUT5

SADDOUT6

SADDOUT7

SADDOUT8

SADDOUT9

SADDOUT10

SADDOUT11

SADDOUT12

SADDOUT13

SADDOUT14

SADDOUTCLK

6

5

A20M#

AE1

FERR

AG1

CPUINIT#

AJ3

INTR

AL1

IGNNE#

AJ1

NMI

AN3

CPURST#

AG3

SMI#

AN5

STPCLK#

AC1

CPU_OK

AE3

C594 X_10p

APICCLK_CPU

N1

APICD0#

N3

APICD1#

N5

COREFB#

AG13

COREFB

AG11

CPUCLK_R

AN17

CPUCLK#_R

AL17

AN19

AL19

CLKOUT

AL21

CLKOUT#

AN21

AJ13

VREFMODE

AA5

VREF_SYS

W5

ZN

AC5

ZN

ZP

TDI

AE5

AJ25

AN15

AL15

AN13

AL13

AC3

S1

S5

S3

Q5

AA1

AA3

AL3

Q1

U1

U5

Q3

U3

L1

L3

L5

L7

J7

W1

W3

Y1

Y3

U37

Y33

L35

E33

E25

A31

C13

A19

J1

J3

C7

A7

E5

A5

E7

C1

C5

C3

G1

E1

A3

G5

G3

E3

ZP

PLLBP#

PLBYCLK

PLBYCLK#

PLLMON1

PLLMON2

PLLTEST#

SCANCLK1

SCANCLK2

SINTVAL

SSHIFTEN

DBRDY

DBREQ#

FLUSH#

CPU_TCK

CPU_TDI

CPU_TDO

CPU_TMS

CPU_TRST#

VIDA0

VIDA1

VIDA2

VIDA3

VIDA4

FID0

FID1

FID2

FID3

AOUT#2

AOUT#3

AOUT#4

AOUT#5

AOUT#6

AOUT#7

AOUT#8

AOUT#9

AOUT#10

AOUT#11

AOUT#12

AOUT#13

AOUT#14

A20M# (10)

CPUINIT# (10)

INTR (10)

IGNNE# (10)

NMI (10)

CPURST# (10)

SMI# (10)

STPCLK# (10)

CPU_OK (20)

APICCLK_CPU (5)

APICD0# (10)

APICD1# (10)

COREFB# (22)

COREFB (22)

VIDA[0..4] (19)

FID[0..3] (5)

AOUT#[2..14] (5)

AOCLK# (5)

5

CFID[3:0] => CPU Clock Multiplier

CPUCLK_R

CPUCLK#_R

CPUCLK#(5)

CPU SYSCLK REFERNCE BLOCK

VREF_SYS

VCORE

4

3

CPU Clock Multiplier

FID2

FID1

FID0

FID3

1 2

3 4

5 6

7 8

RN5

4.7K

VCORE

VCORE

SSHIFTEN

SINTVAL

SCANCLK2

CPURST#

R38

510

123456

78

CPU SYSCLK BLOCK CPU FERR BLOCK

VCORE

CPUCLK(5)

R87 X_60.4RST

680pC67

R89

X_301RST

R90 X_60.4RST

680pC82

CLOSE SOCKET462

VCORE

FERR

YFET-FDV301N SOT-23

Measure FERR# & IGNNE Delay Time

VCORE

R15

680

Q6

CPU ZN / ZP BLOCK

0.5 * VCORE

C50

0.1u

10u-0805

CLOSE SOCKET462

VCORE

R78

110RST

R77

C45C44

110RST0.047u

ZN

R69 40.2RST

ZP

R68 56.2RST

CLOSE SOCKET462

match the transmission line

Push-pull compensation circuit

CPU PULL-UP / DOWN BLOCK

NMI

INTR

SMI#

CPUINIT#

STPCLK#

A20M#

IGNNE#

CPURST#

FILVAL#

DOVAL#

R132 270

R126 270

X_4.7u-0805C543

X_4.7u-0805C545

Put in Solder

4

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

RN3

680

RN6

680

COREFB

X_4.7u-0805C544

COREFB#

VCORE

AIN#0

AIN#1

R72 10K

R76 0

3

PLLMON1

PLLMON2

FLUSH#

PLLBP#

R116 680

R117 680

R79 56

R74 56

R40 680

R113 680

VCORE

2

1

AMD HDT Debug Port

JTAG1

1 2

VCC TCK

3

SHIFT

5

INTEVAL

7

SC2

11

GND

13

DBREQ#

15 16

CPURST# TEST#

X_AMD HDT

RN16

270

TMS

SC1

TRST#

TDO

DBRDY

RN14

510

4

6

8

TDI

10

12

14

R33

510

1 2

3 4

5 6

7 8

CPU_TCK

CPU_TMS

SCANCLK1

CPU_TDI

CPU_TRST#

CPU_TDO

DBRDYDBREQ#

PLLTEST#

CPU K7CLKOUT BLOCK

CLKOUT

R100 100

CLKOUT#

R99 100

R96 100

R95 100

R24

150

FERR# (10)

* Trace lengths of CLKOUT and

CLKOUT# are between 2" and 3"

VCORE

VCORE

CPU APIC BLOCK

VCORE

VCORE

APICD0#

APICD1#

APICCLK_CPU

PLBYCLK

PLBYCLK#

VREFMODE

VREFMODE=Low=No voltage scaling

MSI

Title

Size Document Number Rev

Date: Sheet of

MICRO-STAR INt'L CO., LTD.

AMD Socket462 CPU (Signal)

ZZTOP (MS-6553)

2

R27 220

R29 220

R165 X_453RST

R84 100

R83 100

R81 100

R80 100

R62 X_1K

R61 56.2RST

H/W Project Leader : Andy Chen

H/W Project Engineer : Prudence Wang

3 25Monday, November 19, 2001

VCC2_5

VCORE

VCORE

VCORE

1

0CE0

8

7

6

5

4

3

2

1

CPU VOLTAGE BLOCK

H12

H16

H20

H24M8P30R8T30V8X30Z8AB30

D D

VCC_CORE1

VCC_CORE2

VCC_CORE3

VCC_CORE4

VCC_SRAM1

VCC_SRAM2

VCC_SRAM3

VCC_SRAM4

VCC_SRAM5

VCC_SRAM6

VCC_SRAM7

VCC_SRAM8

VCC_SRAM9

VCC_SRAM11

VCC_SRAM13

VCC_SRAM14

VCC_SRAM16

VCC_SRAM17

VCC_SRAM19

VCC_SRAM20

VCC_SRAM21

VCC_SRAM22

VCC_SRAM23

VCC_SRAM24

VCC_SRAM25

VCC_SRAM26

VCC_SRAM27

VCC_SRAM28

VCC_SRAM29

VCC_SRAM30

VCC_SRAM31

KEY4

KEY6

KEY8

KEY10

KEY12

KEY14

KEY16

KEY18

VSS1

VSS2

VSS3

VSS4

H14

H18

H22

H26

M30P8R30T8V30X8Z30

VCC_CORE5

VSS5

AD30

AD8

AF10

AF28

AF30

AF32

AF6

AF8

AH30

AH8

AJ9

AK8

AL9

AM8

F30

F8

H10

H28

H30

H32

H6

H8

K30

K8

C C

B B

AN7

G25

G17

AG7

AG15

AG29

AJ7

AL7

G9

N7

Y7

VCC_CORE6

VCC_CORE7

VCC_CORE8

VCC_CORE9

VSS6

VSS7

VSS8

VSS9

AF14

AF18

AF22

VCC_CORE10

VCC_CORE11

VCC_CORE12

VCC_CORE13

VCC_CORE14

VSS10

VSS11

VSS12

VSS13

VSS14

AB8

AF12

AF16

AF20

AF26

AM34

AK36

AK34

VCC_CORE15

VCC_CORE16

VCC_CORE17

VCC_CORE18

VCC_CORE19

VSS15

VSS16

VSS17

VSS18

VSS19

AF24

AM36

AK32

AK28

AK30

AK26

AK22

AK18

VCC_CORE20

VCC_CORE21

VCC_CORE22

VCC_CORE23

VSS20

VSS21

VSS22

VSS23

AK24

AK20

AK16

AK12

AK14

AK10

AL5

AH26

VCC_CORE24

VCC_CORE25

VCC_CORE26

VCC_CORE27

VSS25

VSS26

VSS27

VSS28

AK4

AK2

AH36

AM32

AM30

AH22

AH18

AH14

VCC_CORE28

VCC_CORE29

VCC_CORE30

VCC_CORE31

VSS29

VSS30

VSS31

VSS32

AH34

AH32

AH28

AH24

AH10

AH4

AH2

AF36

AF34

AD6

AM26

AD4

AD2

AB36

AB34

AB32Z6Z4Z2X36

X34

VCC_CORE32

VCC_CORE33

VCC_CORE34

VCC_CORE35

VCC_CORE36

VCC_CORE37

VCC_CORE38

VCC_CORE39

VCC_CORE40

VCC_CORE41

VCC_CORE42

VCC_CORE43

VCC_CORE44

VCC_CORE45

VCC_CORE46

VCC_CORE47

462-Pin Socket

Part 2

VSS33

VSS34

VSS35

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

AH20

AH16

AH12

AF4

AF2

AD36

AD34

AD32

AB6

AB4

AB2

Z36

Z34

VSS49

Z32X6AM28X4X2

AM22

X32V6V4V2T36

VCC_CORE48

VCC_CORE49

VCC_CORE50

VCC_CORE51

VCC_CORE52

VSS50

VSS51

VSS52

VSS53

VSS54

V36

V34

V32T6T4T2R36

T34

T32R6R4R2AM18

VCC_CORE53

VCC_CORE54

VCC_CORE55

VCC_CORE56

VCC_CORE57

VSS55

VSS56

VSS57

VSS58

VSS59

R34

AM24

P36

P34

VCC_CORE58

VCC_CORE59

VCC_CORE60

VCC_CORE61

VCC_CORE62

VSS60

VSS61

VSS62

VSS63

VSS64

R32P6P4P2M36

P32M4M6M2K36

VCC_CORE63

VCC_CORE64

VCC_CORE65

VCC_CORE66

VSS65

VSS66

VSS67

VSS68

M34

M32K6K4K2AM20

K34

K32H4H2

AM14

VCC_CORE67

VCC_CORE68

VCC_CORE69

VCC_CORE70

VCC_CORE71

VSS69

VSS70

VSS71

VSS72

VSS73

H36

H34

F26

F36

F34

F32

F28

VCC_CORE72

VCC_CORE73

VCC_CORE74

VCC_CORE75

VCC_CORE76

VSS74

VSS75

VSS76

VSS77

VSS78

F22

F18

F14

F10F6F4F2AM16

F24

F20

F16

F12

VCC_CORE77

VCC_CORE78

VCC_CORE79

VCC_CORE80

VSS79

VSS80

VSS81

VSS82

D32

D28

AM10

D24

VCC_CORE81

VCC_CORE82

VCC_CORE83

VCC_CORE84

VSS83

VSS84

VSS85

VSS86

D36

D34

D30

D26

D20

D16

D12D8D4D2B36

VCC_CORE85

VCC_CORE86

VCC_CORE87

VCC_CORE88

VSS87

VSS88

VSS89

VSS90

D22

D18

D14

D10D6B34

B32

AM2

VCC_CORE89

VCC_CORE90

VCC_CORE91

VCC_CORE92

VCC_CORE93

VSS91

VSS92

VSS93

VSS94

VSS95

AM12

B30

B26

B28

B24

B20

B16

VCC_CORE94

VCC_CORE95

VCC_CORE96

VSS96

VSS97

VSS98

B22

B18

B14

B10B6B2

B12B8B4

AJ5

VCC_CORE97

VCC_CORE98

VCC_CORE99

VCC_CORE100

VCC_CORE101

VSS99

VSS100

VSS101

VSS102

VSS103

AM4

AK6

AM6

VCCA_PLLVCORE

AC7

VCC_Z

NC10

NC11

NC12

NC13

NC15

NC16

NC17

NC18

NC19

NC20

NC21

NC22

NC23

NC24

NC25

NC27

NC28

NC29

NC30

NC31

NC32

NC33

NC34

NC35

NC36

NC37

NC42

NC43

NC44

NC45

BP0_CUT

BP1_CUT

BP2_CUT

BP3_CUT

VSS104

NC1

NC2

NC3

NC6

NC7

NC8

NC9

AE7

AJ23

VCC_A

VSS_Z

0 ~ 100 mA (50mA)

2.25 ~ 2.75 V

U13B

N12-4620011-F02

AA31

AC31

AE31

AG23

AG25

AG31

AG5

AJ11

AJ15

AJ17

AJ19

AJ27

AL11

AN11

AN9

G11

G13

G27

G29

G31

J31

J5

L31

N31

Q31

S31

S7

U31

U7

W31

W7

Y31

Y5

AG19

G21

AG21

G19

AN27

AL27

AN25

AL25

C20

1000p

VCCA_PLL trace length from the regulator to

the PGA must less be 0.75"

Place all filters close to the PGA

Keep all power and signal trace away from

the regulator

Place a cut in GND plane around the

VCCA_PLL regulator circuit

U13C

AO1

GND

AO2

AO3

AO4

YY1

YY2

YY3

YY4

YY5

YY6

YY7

YY8

YY9

YY10

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

N12-4620011-F02

For 1.5GHz CPU Fan Holes

THERMDP# (18)

THERMDN# (18)

YY24

YY23

YY22

YY21

YY20

YY19

YY18

YY17

YY16

YY15

YY14

YY13

YY12

YY11

XX1

XX2

CPU DECOUPLING CAPACITORS

VCORE VCORE VCORE VCOREVCORE VCORE VCORE

C74

39p

C75

39p

C149

39p

C27

39p

C73

39p

C125

39p

C141

39p

C162

39p

C35

A A

39p

C155

39p

C157

39p

C166

39p

C86

39p

C132

39p

C532

39p

C533

39p

C534

39p

C535

39p

C536

39p

C537

39p

C538

39p

C539

39p

C540

39p

C541

39p

Put around inside plane of SocketA

on Bottom side

EMI Decoupling

C542

39p

C546

39p

C547

39p

C548

39p

C549

39p

C550

39p

C551

39p

C552

39p

C553

39p

C554

39p

C555

39p

C556

39p

C557

39p

C558

39p

C559

39p

C560

39p

C561

39p

C562

39p

C563

39p

C564

39p

VCORE

C604

56p

C605

56p

C606

56p

C607

56p

C608

56p

C609

56p

C610

56p

C611

56p

C612

56p

VCC5 VCC3

C99

0.22u

C123

0.22u

C54

0.22u

C77

0.22u

C61

0.22u

C130

0.22u

C118

0.22u

C95

0.22u

C47

0.22u

C78

0.22u

C9 0.1u

C220 0.1u

C7 0.1u

C494 0.1u

C10 0.1u

C46

0.22u

C119

0.22u

C49

0.22u

C103

0.22u

C121

0.22u

C68

0.22u

C72

0.22u

C122

0.22u

C56

0.22u

C48

0.22u

VCC3 VCORE

VCC5 VCORE

C80

0.22u

C128

0.22u

C124

0.22u

C57

0.22u

C120

0.22u

C84

0.22u

C76

0.22u

C41

0.22u

C79

0.22u

C94

0.22u

C40 0.1u

C144 0.1u

C204 0.1u

VCC2_5

C3

0.1u

C24

0.1u

C15

0.1u

C37

0.1u

C23

0.1u

VCC5

C104

1 2

3 4

5 6

7 8

RN18

100

2.50V Reference

VR1

SC431CSK

Put inside SocketA

8

7

6

5

4

3

CPU PLL VOLTAGE BLOCK

(40mils trace / 60 mils space)

VCC_PLL

C126

39p

2

3 1

R108

039p

VR1_2

R111

C617

X_0

0.1u

Used when spec changed

MSI

Title

Size Document Number Rev

Date: Sheet of

2.5V

Max 150 mA

Design for 100 mA

L16 0-0805

EC5

4.7u-0805

C109

39p

H/W Project Leader : Andy Chen

H/W Project Engineer : Prudence Wang

C114

1000p

MICRO-STAR INt'L CO., LTD.

AMD Socket462 CPU (Power)

ZZTOP (MS-6553)

2

4 25Monday, November 19, 2001

1

C101

39p

VCCA_PLL

0CE0

8

7

6

5

4

3

2

1

SYSTEM DATA-IN-CLK NOISE L/C BLOCKCRUSH 11 HOST SIGNALS

SDATA#[0..63](3)

D D

C C

B B

R179 10RST

C241 10p

CPURST#(10)

SDATA#0

SDATA#1

SDATA#2

SDATA#3

SDATA#4

SDATA#5

SDATA#6

SDATA#7

SDATA#8

SDATA#9

SDATA#10

SDATA#11

SDATA#12

SDATA#13

SDATA#14

SDATA#15

SDATA#16

SDATA#17

SDATA#18

SDATA#19

SDATA#20

SDATA#21

SDATA#22

SDATA#23

SDATA#24

SDATA#25

SDATA#26

SDATA#27

SDATA#28

SDATA#29

SDATA#30

SDATA#31

SDATA#32

SDATA#33

SDATA#34

SDATA#35

SDATA#36

SDATA#37

SDATA#38

SDATA#39

SDATA#40

SDATA#41

SDATA#42

SDATA#43

SDATA#44

SDATA#45

SDATA#46

SDATA#47

SDATA#48

SDATA#49

SDATA#50

SDATA#51

SDATA#52

SDATA#53

SDATA#54

SDATA#55

SDATA#56

SDATA#57

SDATA#58

SDATA#59

SDATA#60

SDATA#61

SDATA#62

SDATA#63

CPU_FBO

CPU_FBI

AA3

AA2

AA6

AA4

AC5

AB3

AB2

AG2

AG3

AF3

AH5

W6

Y3

W2

W4

V4

V6

Y5

Y4

U6

W5

U4

V2

R6

T2

P6

R3

R2

U5

T6

T5

T4

V3

U3

N2

P4

N4

M6

M3

L6

H4

H5

K6

J2

N3

P3

P5

N5

M2

M4

J4

J6

G4

D1

E3

D3

C1

E2

A1

C2

J3

H6

G5

G2

G3

D2

F3

F5

K2

L3

U10A

SDATA0#

SDATA1#

SDATA2#

SDATA3#

SDATA4#

SDATA5#

SDATA6#

SDATA7#

SDATA8#

HOST INTERFACE

SDATA9#

SDATA10#

SDATA11#

SDATA12#

SDATA13#

SDATA14#

SDATA15#

SDATA16#

SDATA17#

SDATA18#

SDATA19#

SDATA20#

SDATA21#

SDATA22#

SDATA23#

SDATA24#

SDATA25#

SDATA26#

SDATA27#

SDATA28#

SDATA29#

SDATA30#

SDATA31#

SDATA32#

SDATA33#

SDATA34#

SDATA35#

SDATA36#

SDATA37#

SDATA38#

SDATA39#

SDATA40#

SDATA41#

SDATA42#

SDATA43#

SDATA44#

SDATA45#

SDATA46#

SDATA47#

SDATA48#

SDATA49#

SDATA50#

SDATA51#

SDATA52#

SDATA53#

SDATA54#

SDATA55#

SDATA56#

SDATA57#

SDATA58#

SDATA59#

SDATA60#

SDATA61#

SDATA62#

SDATA63#

CPUCLKFB_OUT

CPUCLKFB_IN

CPU_RST#

NC

NC

NC

CRUSH 11

CRUSH11

PART 1

SADDIN2#

SADDIN3#

SADDIN4#

SADDIN5#

SADDIN6#

SADDIN7#

SADDIN8#

SADDIN9#

SADDIN10#

SADDIN11#

SADDIN12#

SADDIN13#

SADDIN14#

SADDINCLK#

SDATAINCLK0#

SDATAINCLK1#

SDATAINCLK2#

SDATAINCLK3#

SDATAINVAL#

CPUFID0

CPUFID1

CPUFID2

CPUFID3

CPU_VREF1

CPU_VREF2

SADDOUT2#

SADDOUT3#

SADDOUT4#

SADDOUT5#

SADDOUT6#

SADDOUT7#

SADDOUT8#

SADDOUT9#

SADDOUT10#

SADDOUT11#

SADDOUT12#

SADDOUT13#

SADDOUT14#

SADDOUTCLK#

SDATAOUTCLK0#

SDATAOUTCLK1#

SDATAOUTCLK2#

SDATAOUTCLK3#

CPU_CLKFWDRST

CPU_CONNECT

CPU_PROCRDY

APICCLK_CPU

APICCLK_MCP

SYSCLK

SYSCLK#

AD2

AB6

AD4

AD3

AC4

AB5

AD6

AE5

AC6

AB4

AF4

AE4

AG4

AC3

W3

R4

K3

F2

AE6

L5

K5

K4

L4

H3

AF5

B2

A2

C4

B4

F4

C6

B3

A5

C7

D6

B5

A4

D7

C5

Y6

T3

N6

G6

AG6

AF6

AG5

AH2

AH4

AE3

AE2

AIN#2

AIN#3

AIN#4

AIN#5

AIN#6

AIN#7

AIN#8

AIN#9

AIN#10

AIN#11

AIN#12

AIN#13

AIN#14

SAICLK#

SDICLK#0

SDICLK#1

SDICLK#2

SDICLK#3

FID0

FID1

FID2

FID3

CPUREF1_NB

CPUREF_NB

AOUT#2

AOUT#3

AOUT#4

AOUT#5

AOUT#6

AOUT#7

AOUT#8

AOUT#9

AOUT#10

AOUT#11

AOUT#12

AOUT#13

AOUT#14

DOCLK#0

DOCLK#1

DOCLK#2

DOCLK#3

ACLK_CPU

ACLK_MCP

CCLK

CCLK#

DIVAL# (3)

AOCLK# (3)

CFWDRST (3)

CONNECT (3)

PROCRDY (3)

R180 10RST

R185 10RST

R173 10RST

C233 15p

R170 10RST

C230 15p

AIN#[2..14] (3)

FID[0..3] (3)

AOUT#[2..14] (3)

DOCLK#[0..3] (3)

APICCLK_CPU (3)

APICCLK_MCP (10)

CPUCLK (3)

CPUCLK# (3)

SAICLK#

SDICLK#0

SDICLK#1

SDICLK#2

SDICLK#3

CPUREF1_NB

L27 10nH L25 10nH

L24 10nH L22 10nH

L23 10nH L19 10nH

L21 10nH L18 10nH

L20 10nH L17 10nH

SICLK#

SICLK#0

SICLK#1

SICLK#2

REFERNCE VOLTAGE BLOCK

Set PO_VREF to

50% of VCORE

C169

C168

0.1u1000p

R150

110RST

R151

110RST

Crush 11 Decoupling Capacitors

VDDQ MEM_STR

C379

0.1u

C345

0.1u

C344

0.1u

C380

0.1u

C343

0.1u

C288

0.1u

C342

0.1u

C381

0.1u

C205 5p

C190 5p

C172 5p

C167 5p

C163 5p

C218

0.1u

C231

0.1u

C207

0.1u

C139

0.1u

C106

0.1u

C289

0.1u

C191

0.1u

C171

0.1u

C199

0.1u

C270

0.1u

C300

0.1u

CPUREF_NB

DICLK#0

DICLK#1

DICLK#2

DICLK#3SICLK#3

Set PO_VREF to

50% of VCORE

C222

1000p

AICLK# (3)

DICLK#[0..3] (3)

VCOREVCORE

C236

0.1u

R174

110RST

R176

110RST

BELONG TO CLKFWD GROUP[SADDIN] MATCH W/IN +/-10MILS OF GROUP 5/15, CLK:10/30

A A

BELONG TO CLKFWD GROUP[SADDOUT] MATCH W/IN +/-10MILS OF GROUP 5/15, CLK:10/30

BELONG TO CLKFWD GROUP;MATCHED TO INDIVIDUAL CLKFWD GROUP

RESPECTIVELY.[SDATA0], [SDATA1], [SDATA2],[SDATA3] W/IN+/-10MILS OF GROUP

8

7

6

MSI

Title

Size Document Number Rev

5

4

3

Date: Sheet of

MICRO-STAR INt'L CO., LTD.

H/W Project Leader : Andy Chen

H/W Project Engineer : Prudence Wang

Crush11 Host Signals

ZZTOP (MS-6553)

2

5 25Monday, November 19, 2001

0CE0

1

8

7

6

5

4

3

2

1

CRUSH 11 MEMORY SIGNALS

B7C9B11

C13C8B8

C11

C12

B13

B14

D19

B20

C14

C16

D17

D18

C21

C22

C24

C26

C19

B22

C25

B25

B26

B28

B31

A31

C27

C28

B30

C33

D33

F33

G32

K33

E33

F32

J33

J32

L32

N32

U32

V32

K32

M32

V33

W33

W32

AA33

AE33

AF32

Y32

AA32

AD32

AE32

AH33

AL34

AP34

AL32

AG33

AG32

AN34

AN33

MDQ_A0

MDQ_A1

MDQ_A2

MDQ_A3

MDQ_A4

MDQ_A5

MDQ_A6

MDQ_A7

MDQ_A8

MDQ_B3

MDQ_B4

MDQ_B5

MDQ_B6

D10

D11

MDQ_A9

MDQ_B7

MDQ_B8

MDQ_B9

F11

D12

MDQ_A10

MDQ_A11

MDQ_B10

MDQ_B11

F14

D15

E12

MDQ_A12

MDQ_A13

MDQ_A14

MDQ_B12

MDQ_B13

MDQ_B14

F12

D14

E14

MDQ_A15

MDQ_A16

MDQ_A17

MDQ_A18

MDQ_A19

MDQ_A20

MDQ_A21

MDQ_A22

MDQ_A23

MDQ_A24

MDQ_A25

MDQ_A26

MDQ_A27

MDQ_A28

CRUSH11

PART 2

SYSTEM MEMORY

MDQ_B15

MDQ_B16

MDQ_B17

MDQ_B18

MDQ_B19

MDQ_B20

MDQ_B21

MDQ_B22

MDQ_B23

MDQ_B24

MDQ_B25

MDQ_B26

MDQ_B27

F16

F17

D22

E24

F15

F18

E23

MDQ_B28

F25

F26

E27

E32

F31

D27

D29

MDQ_A29

MDQ_A30

MDQ_A31

MDQ_B29

MDQ_B30

MDQ_B31

J31

J30

M29

MDQ_A32

MDQ_A33

MDQ_A34

MDQ_B32

MDQ_B33

MDQ_B34

P29

P31

T29

MDQ_A35

MDQ_A36

MDQ_A37

MDQ_B35

MDQ_B36

MDQ_B37

M30

N31

R31

MDQ_A38

MDQ_A39

MDQ_A40

MDQ_B38

MDQ_B39

MDQ_B40

R29

V31

V30

MDQ_A41

MDQ_A42

MDQ_A43

MDQ_B41

MDQ_B42

MDQ_B43

AA29

AB29

U29

MDQ_A44

MDQ_A45

MDQ_A46

MDQ_B44

MDQ_B45

MDQ_B46

V29

AA30

AC31

MDQ_A47

MDQ_A48

MDQ_A49

MDQ_B47

MDQ_B48

MDQ_B49

AC29

AC30

AF29

MDQ_A50

MDQ_A51

MDQ_A52

MDQ_B50

MDQ_B51

MDQ_B52

AG31

AD31

AD29

MDQ_A53

MDQ_A54

MDQ_A55

MDQ_B53

MDQ_B54

MDQ_B55

AD30

AE29

AG29

MDQ_A56

MDQ_A57

MDQ_A58

MDQ_B56

MDQ_B57

MDQ_B58

AG30

AJ30

AK31

MDQ_A59

MDQ_A60

MDQ_A61

MDQM_B0

MDQM_B1

MDQM_B2

MDQM_B3

MDQM_B4

MDQM_B5

MDQM_B6

MDQM_B7

MDQS_B0

MDQS_B1

MDQS_B2

MDQS_B3

MDQS_B4

MDQS_B5

MDQS_B6

MDQS_B7

MA_B0

MA_B1

MA_B2

MA_B3

MA_B4

MA_B5

MA_B6

MA_B7

MA_B8

MA_B9

MA_B10

MA_B11

MA_B12

MBA_B0

MBA_B1

MCLK_B0

MCLK_B0#

MCLK_B1

MCLK_B1#

MCLK_B2

MCLK_B2#

MCLK_B3

MCLK_B3#

MCLK_B4

MCLK_B4#

MCLK_B5

MCLK_B5#

MRAS_B#

MWE_B#

MCKE_B

MCS_B0#

MCS_B1#

MCS_B2#

MCS_B3#

MDQ_B59

MDQ_B60

MDQ_B61

AF30

AH31

AJ31

MDQ_A62

MDQ_A63

MDQ_B62

MDQ_B63

AJ29

D9

F13

F20

H31

P30

Y30

AE31

AH29

F9

D13

F19

D28

N29

AA31

AF31

AK32

K31

H30

H29

C31

F28

D26

D25

F22

F23

D21

L31

D20

E17

R30

L29

C34

D34

B17

C18

AH32

AJ32

B33

B34

B19

C20

AK34

AK33

U31

U30

E15

Y29

AB31

W31

Y31

U10B

CRUSH 11

MDQM_B0

MDQM_B1

MDQM_B2

MDQM_B3

MDQM_B4

MDQM_B5

MDQM_B6

MDQM_B7

MDQS_B0

MDQS_B1

MDQS_B2

MDQS_B3

MDQS_B4

MDQS_B5

MDQS_B6

MDQS_B7

MA_RB0

MA_RB1

MA_RB2

MA_RB3

MA_RB4

MA_RB5

MA_RB6

MA_RB7

MA_RB8

MA_RB9

MA_RB10

MA_RB11

MA_RB12

CAS_B#

RAS_B#

WE_B#

CS_B#0

CS_B#1

CS_B#2

CS_B#3

R265 0

R245 0

R248 0

R267 0

R273 0

R258 0

R264 0

MDQM_B[0..7] (14)

MDQS_B[0..7] (14)

MBA_B0 (14)

MBA_B1 (14)

MCLK_B0 (14)

MCLK_B#0 (14)

MCLK_B1 (14)

MCLK_B#1 (14)

MCLK_B2 (14)

MCLK_B#2 (14)

MCAS_B# (14)

MRAS_B# (14)

MWE_B# (14)

MCKE_B (14)

MCS_B#0 (14)

MCS_B#1 (14)

MCS_B#2 (14)

MCS_B#3 (14)

D D

MA_RA0

MA_RA1

MA_RA2

MA_RA3

MA_RA4

MA_RA5

MA_RA6

MA_RA7

MA_RA8

C C

MBA_A0(14)

MBA_A1(14)

MCLK_A0(14)

MCLK_A#0(14)

MCLK_A1(14)

MCLK_A#1(14)

MCLK_A2(14)

MCLK_A#2(14)

MCAS_A#(14)

MRAS_A#(14)

MWE_A#(14)

MCKE_A(14)

MCS_B#2(14)

MCS_B#3(14)

PCIRST#1(9)

B B

MEM_STR

MA_RA9

MA_RA10

MA_RA11

MA_RA12

R244 0

R233 0

R243 0

R251 X_0

R260 X_0

R197 2K

R194 10K

DDR2_VREF

Put in Solder

C10

MDQM_A0

D16

MDQM_A1

B23

MDQM_A2

B29

MDQM_A3

H32

MDQM_A4

T32

MDQM_A5

AC32

MDQM_A6

AL33

MDQM_A7

B10

MDQS_A0

C15

MDQS_A1

C23

MDQS_A2

C29

MDQS_A3

G33

MDQS_A4

T33

MDQS_A5

AD33

MDQS_A6

AM33

MDQS_A7

J29

MA_A0

G31

MA_A1

D32

MA_A2

C30

MA_A3

F27

MA_A4

F24

MA_A5

E26

MA_A6

D23

MA_A7

D24

MA_A8

F21

MA_A9

K29

MA_A10

E21

MA_A11

E18

MA_A12

T31

MBA_A0

L30

MBA_A1

A32

MCLK_A0

B32

MCLK_A0#

B16

MCLK_A1

C17

MCLK_A1#

AB33

MCLK_A2

AB32

CAS_A#

RAS_A#

WE_A#

CS_A#0

CS_A#1

PRST#1

0.1uC573

0.1uC572

MCLK_A2#

R33

MCAS_A#

M33

MRAS_A#

N33

MWE_A#

E20

MCKE_A

P32

MCS_A0#

R32 W29

MCS_A1# MCAS_B#

C32

STR_EN#

M31

MEM_VREF

MDQ_B0

MDQ_B1

MDQ_B2

D8E9F10

E11E8F8

DDR Terminational Resisitors

MDQ_B16

R94 100

MDQ_B17

R97 100

MDQ_B18

R112 100

MDQ_B19

R127 100

MDQ_B20

R91 100

MDQ_B21

R103 100

MDQ_B22

R114 100

MDQ_B23

R124 100

MDQ_B41

R202 100

MDQ_B42

R221 100

MDQ_B45

R196 100

MDQ_B46

R224 100

MDQ_B52

R252 100

MDQ_B53

R249 100

MDQS_B2

R102 100

MDQS_B3

R134 100

MDQS_B5

R215 100

MDQM_B1

R70 100

MDQM_B2

R107 100

MDQM_B3

R136 100

MDQM_B5

R210 100

MDQ_B24

1 2

MDQ_B28

MDQ_B29

MDQ_B25

MDQ_B30

MDQ_B26

MDQ_B27

MDQ_B31

MDQ_B32

MDQ_B36

MDQ_B33

MDQ_B37

MDQS_B4

MDQ_B34

MDQM_B4

MDQ_B38

MDQ_B39

MDQ_B35

MDQ_B40

MDQ_B44

MCKE_A

MCKE_B

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

R101 100

R98 100

RN20

100

RN22

100

RN31

100

RN34

100

RN37

100

DDR Dampping Resisitors

MA_B0

7 8

MA_A0

MA_A10

MA_B10

MA_A2

MA_B2

MA_A1

MA_B1

MA_B6

MA_B5

MA_A6

MA_A5

5 6

3 4

1 2

7 8

5 6

3 4

1 2

7 8

5 6

3 4

1 2

R160 0

RN40

0

RN39

0

RN35

0

MDQ_B14

MDQ_B15

MDQ_B10

MDQ_B11

MDQ_B0

MDQ_B4

MDQ_B1

MDQS_B0

MDQ_B5

MDQ_B6

MDQM_B0

MDQ_B2

MDQ_B7

MDQ_B3

MDQ_B8

MDQ_B9

MDQS_B1

MDQ_B13

MDQ_B12

MDQ_B43

MDQ_B47

MDQ_B48

MDQ_B49

MDQ_B55

MDQM_B6

MDQ_B54

MDQS_B6

MDQ_B61

MDQ_B60

MDQ_B50

MDQM_B7

MDQ_B51

MDQ_B63

MDQ_B62

MDQ_B56

MDQ_B57

MDQ_B58

MDQS_B7

MDQ_B59

MA_RB0

MA_RA0

MA_RA10

MA_RB10

MA_RA2

MA_RB2

MA_RA1

MA_RB1

MA_RB6

MA_RB5

MA_RA6

MA_RA5

MA_RA12MA_A12

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

R82

100

RN7

100

RN10

100

RN12

100

RN13

100

RN41

100

RN44

100

RN45

100

RN47

100

RN48

100

VTT_DDR2VTT_DDR2

MA_B4 MA_RB4

MDQ_B61

MDQ_B59

MDQ_B10

MDQ_B13

MDQ_B16

MDQ_B22

MDQ_B12

MDQ_B0

MDQ_B3

MDQ_B1

MDQ_B2

MDQ_B4

MDQ_B[0..63](14)

MDQ_B11

MDQ_B7

MDQ_B5

MDQ_B6

MDQ_B8

MDQ_B9

MDQ_B20

MDQ_B14

MDQ_B21

MDQ_B19

MDQ_B17

MDQ_B18

MDQ_B15

MDQ_B25

MDQ_B23

MDQ_B24

MDQ_B29

MDQ_B34

MDQ_B28

MDQ_B26

MDQ_B27

MDQ_B36

MDQ_B31

MDQ_B30

MDQ_B33

MDQ_B32

MDQ_B35

MDQ_B43

MDQ_B37

MDQ_B41

MDQ_B39

MDQ_B42

MDQ_B38

MDQ_B40

MDQ_B49

MDQ_B47

MDQ_B45

MDQ_B48

MDQ_B46

MDQ_B44

MDQ_B56

MDQ_B57

MDQ_B51

MDQ_B53

MDQ_B52

MDQ_B50

MDQ_B60

MDQ_B55

MDQ_B54

MDQ_B62

MDQ_B58

MDQ_B63

DDR REFENCE VOLTAGE

MA_B[0..12](14)

A A

R43

110RST

R42

110RST

MEM_STR

DDR2_VREF

Put near DIMM

DDR2_VREF (14)

30mils Trace/45mils Space

8

7

6

5

MA_B0

MA_B1

MA_B2

MA_B3

MA_B4

MA_B5

MA_B6

MA_B7

MA_B8

MA_B9

MA_B10

MA_B11

MA_B12

MA_A[0..12](14)

4

MA_A0

MA_A1

MA_A2

MA_A3

MA_A4

MA_A5

MA_A6

MA_A7

MA_A8

MA_A9

MA_A10

MA_A11

MA_A12

MSI

Title

Size Document Number Rev

3

Date: Sheet of

7 8

MA_A3

5 6

MA_A4

3 4

MA_B3

1 2

MA_B7

7 8

MA_B8

5 6

MA_A7

3 4

MA_A8

1 2

MA_B11

7 8

MA_A11

5 6

MA_B9

3 4

MA_A9

1 2

MA_RB12

R158 0

MICRO-STAR INt'L CO., LTD.

MA_RA3

RN36

MA_RA4

0

MA_RB3

MA_RB7

MA_RB8

RN33

MA_RA7

0

MA_RA8

MA_RB11

MA_RA11

RN30

MA_RB9

0

MA_RA9

MA_B12

H/W Project Leader : Andy Chen

H/W Project Engineer : Prudence Wang

Crush11 Memory Signals

ZZTOP (MS-6553)

2

6 25Monday, November 19, 2001

1

0CE0

8

7

6

5

4

3

2

1

CRUSH 11 AGP & LDT SIGNALS

AL19

AJ19

AL18

AM19

AN19

AJ18

AL17

AK18

AL16

AM17

AJ16

AL15

AN17

AJ15

AK15

AM16

AL13

AN13

AJ13

AL12

AM12

AM11

AJ12

AK12

AK11

AJ11

AN10

AM9

AL10

AN8

AM8

AK10

AM18

AN16

AM13

AL11

AK17

AJ17

AM10

AN11

AN14

AM14

AK14

AJ14

AM15

AL14

AM5

AM4

AK8

AM7

AN7

AK9

AM3

AK6

AN5

AK7

AP5

AM6

AN20

AP4

AN4

AL8

AL7

AL6

AJ8

AJ9

AL9

AL3

U10C

CRUSH 11

AGP_AD0

AGP_AD1

CRUSH11

AGP_AD2

AGP_AD3

AGP_AD4

AGP_AD5

AGP_AD6

AGP_AD7

AGP_AD8

AGP_AD9

AGP_AD10

AGP_AD11

AGP_AD12

AGP_AD13

AGP_AD14

AGP_AD15

AGP_AD16

AGP_AD17

AGP_AD18

AGP_AD19

AGP_AD20

AGP_AD21

AGP_AD22

AGP_AD23

AGP_AD24

AGP_AD25

AGP_AD26

AGP_AD27

AGP_AD28

AGP_AD29

AGP_AD30

AGP_AD31

AGP_CBE0#

AGP_CBE1#

AGP_CBE2#

AGP_CBE3#

AGP_ADSTB0

AGP_ADSTB0#

AGP_ADSTB1

AGP_ADSTB1#

AGP_FRAME#

AGP_DEVESEL#

AGP_IRDY#

AGP_TRDY#

AGP_STOP#

AGP_PAR

AGP_REQ#

AGP_GNT#

AGP_SBSTB

AGP_SBSTB#

AGP_SBA0

AGP_SBA1

AGP_SBA2

AGP_SBA3

AGP_SBA4

AGP_SBA5

AGP_SBA6

AGP_SBA7

AGP_ST0

AGP_ST1

AGP_ST2

AGP_PIPE#

AGP_RBF#

AGP_WBF#

AGP_VREF

AGP_CLK

AGP_CLK_FB_IN

AGP_CLK_FB_OUT

PART 3

AGP 4X,

VIDEO,

INTERFACE

AND

LDT

LDT_RSET

LDT_RST#

LDT_RX_CLK

LDT_RX_CLK#

LDT_RXD0

LTD_RXD0#

LDT_RXD1

LTD_RXD1#

LDT_RXD2

LTD_RXD2#

LDT_RXD3

LTD_RXD3#

LDT_RXD4

LTD_RXD4#

LDT_RXD5

LTD_RXD5#

LDT_RXD6

LTD_RXD6#

LDT_RXD7

LTD_RXD7#

LDT_RXD8

LTD_RXD8#

LDT_TX_CLK

LDT_TX_CLK#

LDT_TXD0

LDT_TXD0#

LDT_TXD1

LDT_TXD1#

LDT_TXD2

LDT_TXD2#

LDT_TXD3

LDT_TXD3#

LDT_TXD4

LDT_TXD4#

LDT_TXD5

LDT_TXD5#

LDT_TXD6

LDT_TXD6#

LDT_TXD7

LDT_TXD7#

LDT_TXD8

LDT_TXD8#

TEST

INTR_OUT#

PCI_RST#

CLK14318IN

VDD_PLL

VDD_DAC

DACGND

DACVREF

DACRSET

RED

GREEN

BLUE

HSYNC

VSYNC

AM28

AJ3

AN23

AM24

AJ21

AK21

AN22

AM23

AL23

AK24

AM25

AN25

AL21

AM22

AL22

AK23

AJ22

AJ23

AL24

AL25

AL26

AM26

AM30

AL29

AN32

AP32

AP31

AN31

AM29

AN28

AK26

AL27

AN30

AN29

AL28

AK27

AJ27

AJ26

AJ25

AJ24

AM27

AN26

AK3

AK2

AN3

AJ4

AK1

AP3

AM1

AL1

AP2

AN2

AP1

AN1

AL2

AM2

LDT_RSET

TEST

VDD_DAC

DVREF

RSET

R

G

B

HSYNC

VSYNC

C239

1000p

C262

1000p

C255 0.01u

R205 124RST

R536 0

R537 0

R538 0

R204 33

R207 33

LDT_RST# (9)

LDT_RX_CLK (9)

LDT_RX_CLK# (9)

LDT_RXD0 (9)

LDT_RXD#0 (9)

LDT_RXD1 (9)

LDT_RXD#1 (9)

LDT_RXD2 (9)

LDT_RXD#2 (9)

LDT_RXD3 (9)

LDT_RXD#3 (9)

LDT_RXD4 (9)

LDT_RXD#4 (9)

LDT_RXD5 (9)

LDT_RXD#5 (9)

LDT_RXD6 (9)

LDT_RXD#6 (9)

LDT_RXD7 (9)

LDT_RXD#7 (9)

LDT_RXD8 (9)

LDT_RXD#8 (9)

LDT_TX_CLK (9)

LDT_TX_CLK# (9)

LDT_TXD0 (9)

LDT_TXD#0 (9)

LDT_TXD1 (9)

LDT_TXD#1 (9)

LDT_TXD2 (9)

LDT_TXD#2 (9)

LDT_TXD3 (9)

LDT_TXD#3 (9)

LDT_TXD4 (9)

LDT_TXD#4 (9)

LDT_TXD5 (9)

LDT_TXD#5 (9)

LDT_TXD6 (9)

LDT_TXD#6 (9)

LDT_TXD7 (9)

LDT_TXD#7 (9)

LDT_TXD8 (9)

LDT_TXD#8 (9)

PIRQ#E (15,16)

PCIRST#1 (9)

CLK14M (19)

VDD_PLL_C12 (19)

C268

0.1u

L37 80-0805

C273

4.7u-0805

C275

0.1u

VCC3

AM1 "rounted GND"

Connect each routed GND to GND plane at

one point only(one via)

Use surface mount caps, and placed closed as possibleto

power pins with short, wide direct connections.

X_10pC614

X_10pC615

X_10pC616

CRT_R (17)

CRT_G (17)

CRT_B (17)

CRT_HSYNC (17)

CRT_VSYNC (17)

SW1

1

2

3

X_YJ103

SW2

1

2

3

X_YJ103

SW3

1

2

3

YJ103

X_10pC278

10pC266

GAD0

GAD1

GAD2

GAD3

GAD4

GAD5

GAD6

GAD7

GAD8

GAD9

GAD10

GAD11

GAD12

GAD13

GAD14

GAD15

GAD16

GAD17

GAD18

GAD19

GAD20

GAD21

GAD22

GAD23

GAD24

GAD25

GAD26

GAD27

GAD28

GAD29

GAD30

GAD31

GC_BE#0

GC_BE#1

GC_BE#2

GC_BE#3

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

ST0

ST1

ST2

GCLK

GCLK_FBI

GCLK_FBO

D D

C C

B B

A A

GAD[0..31](15)

GC_BE#[0..3](15)

AD_STB0(15)

AD_STB#0(15)

AD_STB1(15)

AD_STB#1(15)

GFRAME#(15)

GDEVSEL#(15)

GIRDY#(15)

GTRDY#(15)

GSTOP#(15)

GPAR(15)

GREQ#(15)

GGNT#(15)

SB_STB(15)

SB_STB#(15)

SBA[0..7](15)

ST[0..2](15)

PIPE#(15)

RBF#(15)

WBF#(15)

VREF4X_IN(15)

AGPCLK(15)

R234 22

R213 22

CRUSH 11 Strapping Resistors

LDT_RSET

TEST

R347 8.2K

VDDQ

VDDQ

SW1_2

R284 X_8.2K

VDDQ

SW2_2

R287 X_8.2K

VDDQ

SW3_2 SBA3

R288 8.2K

C299 1u-0805

SBA0

SBA1

SBA2

VREF4X_IN

0.1uC293

R277 51RST

R181 10K

VDDQ

R542

8.2K

R543

X_8.2K

VDDQ

R226

8.2K

R230

X_8.2K

VDDQ

R227

X_8.2K

R232

X_8.2K

Host Freq.

100MHz

133MHz

0 = Use values stored in ROM tables.

1 = AUTO detect by reading SBA[1:0]

SBA0SBA1

0 1

1 1

FSB Set. SBA2

ROM

AUTO

0 = "SAFE" mode table

1 = USER defined table

0

1

FSB Mode1SBA3

SAFE 0

AUTO

VDD

C301

C369

0.1u

0.1u

MSI

Title

Size Document Number Rev

8

7

6

5

4

3

Date: Sheet of

MICRO-STAR INt'L CO., LTD.

H/W Project Leader : Andy Chen

H/W Project Engineer : Prudence Wang

Crush11 AGP & LDT Signals

ZZTOP (MS-6553)

2

7 25Monday, November 19, 2001

0CE0

1

8

7

6

5

4

3

2

1

30 mils Trace / 40 mils Space

V21

V22

W13

W14

W15

W16

W17

W18

W19

W20

W21

W22

Y14

Y15

Y16

Y17

Y18

Y19

Y20

Y21

AA14

AA15

AA16

AA17

AA18

AA19

AA20

AA21

AB16

GND

GND

U19

GND

GND

U20

GND

GND

AB17

AB19

AB18

AC33

AC34

AE30

AG34

AH30

AJ33

AJ34

V18

V17

V16

V15

AJ1AJ2

AK22

GND

AK25

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

N16

U21

U22

V13

V14

AJ6

V19

5

GND

N17

N18

N19

P14

P15

P16

P17

GND

GND

GND

GND

GND

GND

GND

GNDGND

AK30

GND

AL31

GND

AN27

GND

AP22

GND

AP25

GND

AP27

GND

AP30

GND

AJ7

GND

AJ10

GND

AK5

GND

AK13

GND

AK16

GND

AK19

GND

AL4

GND

AL5

GND

AN9

GND

AN15

GND

AP7

GND

AP9

GND

AP13

GND

AP15

GND

AP19

GND

B1

GND

C3

GND

D4

GND

D5

GND

E1

GND

E4

GND

E5

GND

E6

GND

E7

GND

F6

GND

F7

GND

J1

GND

J5

GND

L1

GND

L2

GND

M5

GND

R1

GND

R5

GND

U1

GND

U2

GND

V5

GND

AA1

GND

AA5

GND

AC1

GND

AC2

GND

AD5

GND

AG1

GND

AH6

GND

A6

GND

A9

GND

A13

GND

A15

GND

A19

GND

A21

GND

A25

GND

A27

GND

A30

GND

A34

GND

B6

GND

B9

GND

B15

GND

B21

GND

B27

GND

D30

GND

D31

GND

E10

GND

E13

GND

E16

GND

E19

GND

E22

GND

E25

GND

E28

GND

E29

GND

E30

GND

E31

GND

E34

GND

F29

GND

F30

GND

G29

GND

G30

GND

J34

GND

K30

GND

L33

GND

L34

GND

N30

GND

R34

GND

T30

GND

U33

GND

U34

GND

W30

GND

AA34

GND

AB30

GND

GND

GND

GND

GND

P18

P19

P20

P21

4

V20

U10D

AH3

VDD_2P5

AJ5

VDD_3P30

AK4

VDD_3P31

AF1

VDD_CLK

AF2

VDD_CLK

A3

VTT_CPU

F1

VTT_CPU

H1

VTT_CPU

H2

VTT_CPU

M1

VTT_CPU

P1

VTT_CPU

P2

VTT_CPU

V1

VTT_CPU

Y1

VTT_CPU

Y2

VTT_CPU

AD1

VTT_CPU

AN6

VDDQ

AN12

VDDQ

AN18

VDDQ

AP6

VDDQ

AP10

VDDQ

AP12

VDDQ

AP16

VDDQ

AP18

VDDQ

A7

VDD_MEM

A10

VDD_MEM

A12

VDD_MEM

A16

VDD_MEM

A18

VDD_MEM

A22

VDD_MEM

A24

VDD_MEM

A28

VDD_MEM

A33

VDD_MEM

B12

VDD_MEM

B18

VDD_MEM

B24

VDD_MEM

F34

VDD_MEM

H33

VDD_MEM

H34

VDD_MEM

M34

VDD_MEM

P33

VDD_MEM

P34

VDD_MEM

V34

VDD_MEM

Y33

VDD_MEM

Y34

VDD_MEM

AD34

VDD_MEM

AF33

VDD_MEM

AF34

VDD_MEM

AM34

VDD_MEM

AJ20

VDD

AJ28

VDD

AK20

VDD

AK28

VDD

AK29

VDD

AL20

VDD

AL30

VDD

AM20

VDD

AM21

VDD

AM31

VDD

AM32

VDD

AN21

VDD

AN24

VDD

AP21

VDD

AP24

VDD

AP28

VDD

AP33

VDD

N13

VDD

N14

VDD

N15

VDD

N20

VDD

N21

VDD

N22

VDD

P13

VDD

P22

VDD

R13

VDD

R22

VDD

Y13

VDD

Y22

VDD

AA13

VDD

AA22

VDD

AB13

VDD

AB14

VDD

AB15

VDD

AB20

VDD

AB21

VDD

AB22

VDD

CRUSH 11

7

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

CRUSH11

PART 4

Power and GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

R14

R15

R16

R17

GND

R18

R19

R20

R21

T15

T16

T17

T18

T19

T20

T13

T14

6

T21

GND

T22

U13

U14

U15

U16

U17

U18

FB2 0-0805

VCC2_5

VCC3

D D

VCORE

VCORE

C206

0.1u

C565

C566

39p

39p

Put in Solder

MEM_STR

C C

B B

VDD

C313

0.1u

C198

0.1u

C574

0.1u

C577

0.1u

FB4 80-0805

L28 80-0805

C228

0.1u

C569

39p

VDDQ

C210

0.1u

C282

0.1u

C567

0.1u

Put in Solder

C575

0.1u

C225

39p

C219

0.1u

C212

0.1u

C284

0.1u

C227

0.1u

C298

0.1u

C571

0.1u

C570

0.1u

Put in Solder

C245

0.1u

C235

0.1u

C196

0.1u

C188

0.1u

C276

0.1u

C238

0.1u

C302

0.1u

C295

0.1u

C576

0.1u

FB2

C246

0.1u

FB4

C243

0.1u

L28

C215

0.1u

C178

0.1u

C184

0.1u

C271

0.1u

C267

0.1u

C291

0.1u

C568

0.1u

C578

0.1u

CRUSH 11 POWER SIGNALS

A A

8

Auto-BOM Manual Parts Simulation

+

U10_X21

U27_X1

U10_X1

SW3(2-3)

FAN_SEL2(1-2)

U10_X22

COM1

AGP_X1

AGP

JBAT1(1-2)

JCMOS1(1-2)

VCC5

SIM1

SIM2

PCB1

PCB

BAT1_X1

SW1(2-3)

FAN_SEL1(1-2)

Mounting Holes

MH4

1

5

2

6

3

7

4

8

9

MH3

1

5

2

6

3

7

4

8

9

MH7

1

5

2

6

3

7

4

8

9

3

MH5

1

5

2

6

3

7

4

8

9

MH6

1

5

2

6

3

7

4

8

9

MH2

1

5

2

6

3

7

4

8

9

MSI

Title

Size Document Number Rev

Date: Sheet of

MICRO-STAR INt'L CO., LTD.

2

MH1

1

2

3

4

8

9

MH8

1

2

3

4

8

9

H/W Project Leader : Andy Chen

H/W Project Engineer : Prudence Wang

Crush11 Power Signals

ZZTOP (MS-6553)

U31

1

1

2

2

3

3

4

4

X_HS_C12

5

6

7

5

6

7

8 25Monday, November 19, 2001

J4

J3

0CE0

1

Loading...

Loading...