8

7

6

5

4

3

2

1

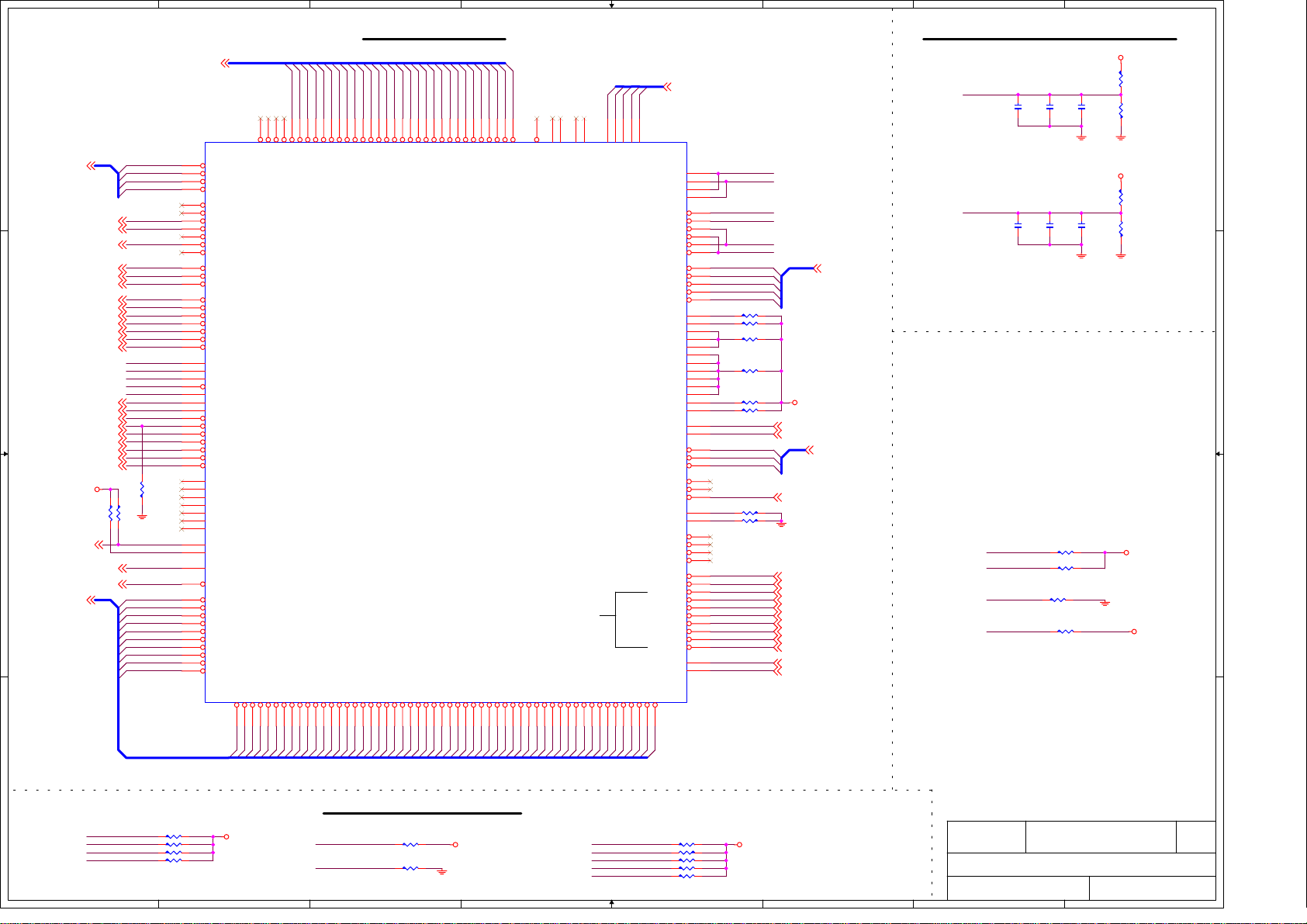

Cover Sheet

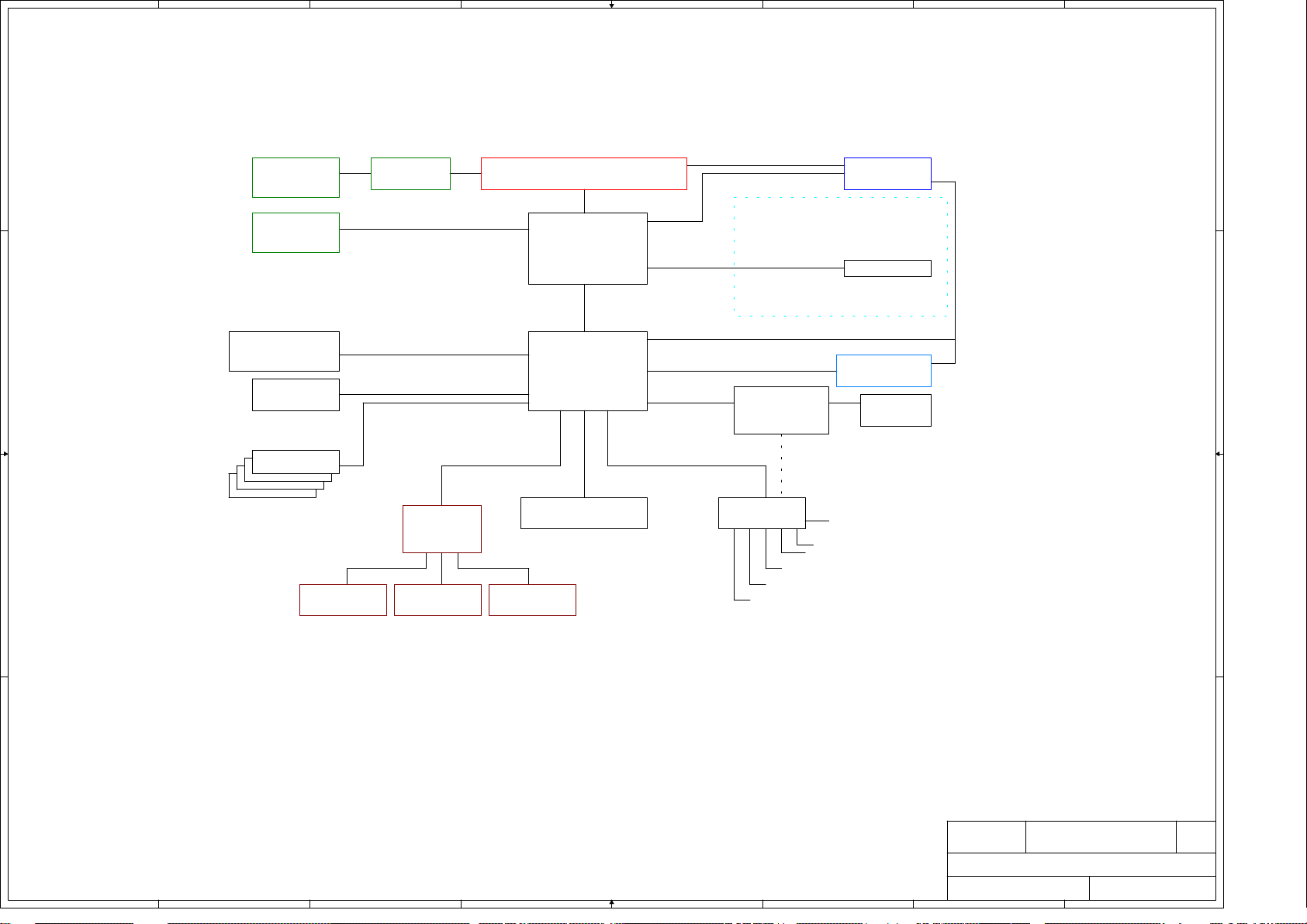

Block Diagram

1

2

MS-6507

Version 5.0

11/20/2001 Update

INTEL (R) Brookdale Chipset

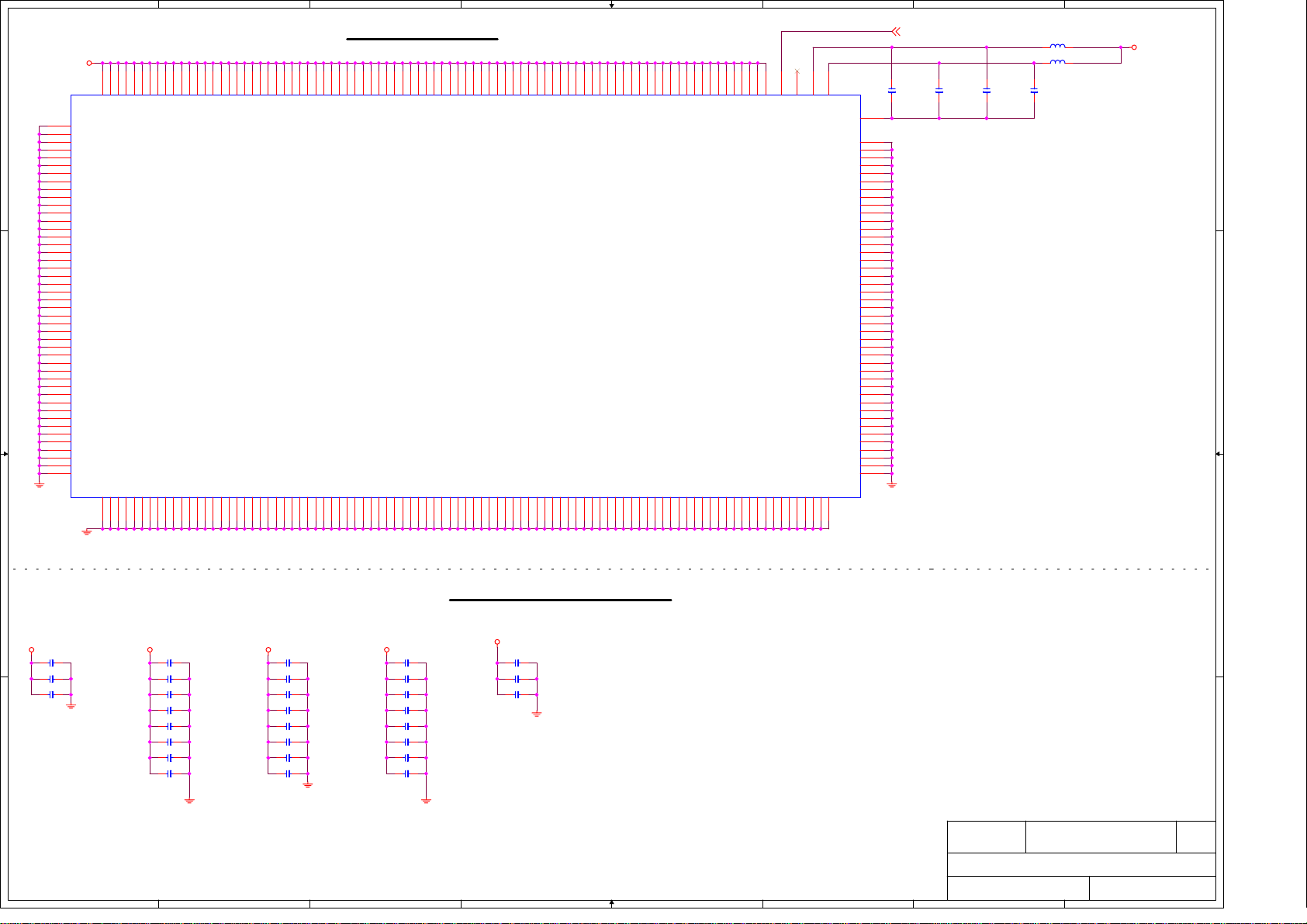

Power Delivery Map

D D

GPIO Spec.

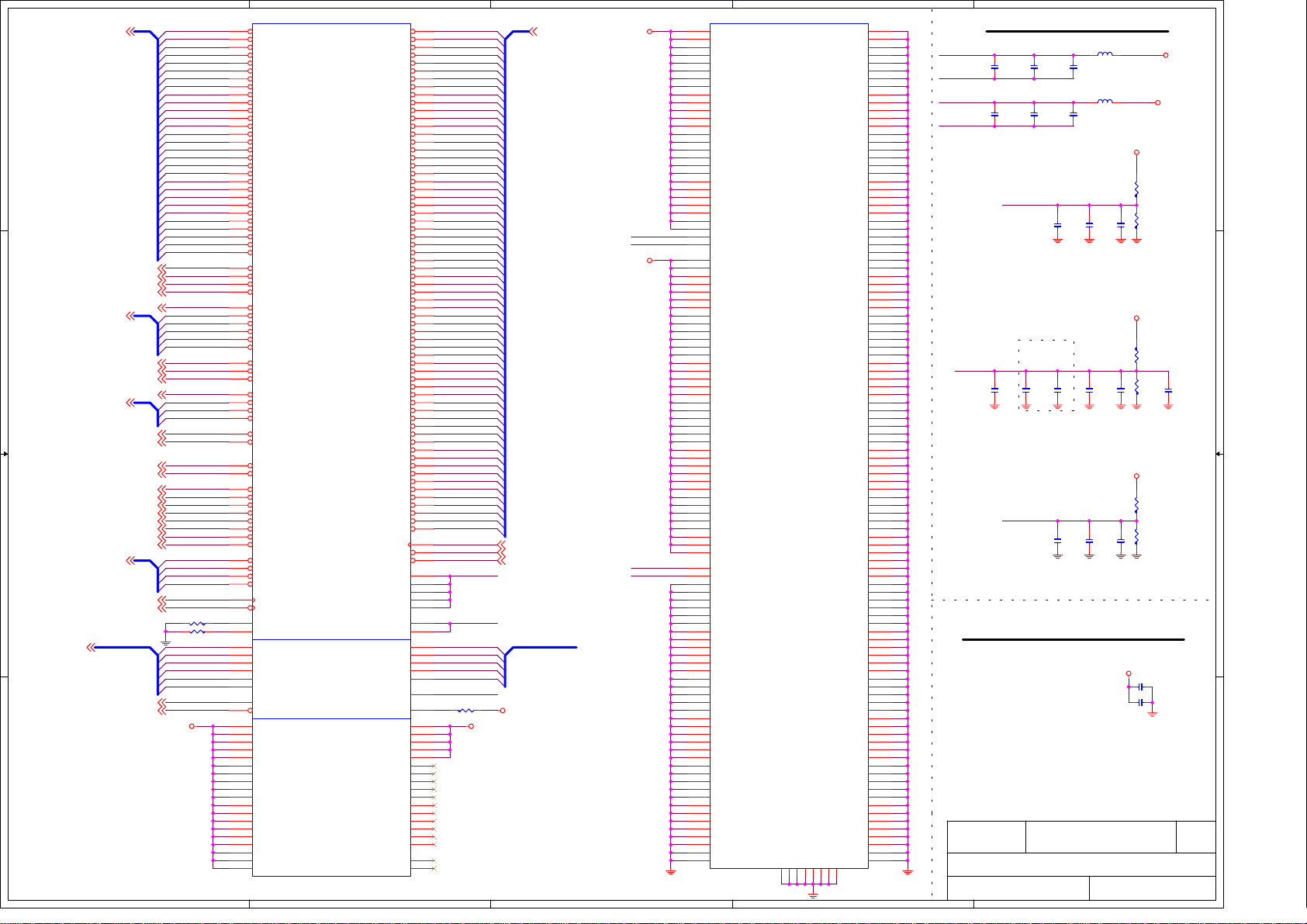

Clock ICS950213AF & ATA100 IDE CONNECTORS

mPGA478-B INTEL CPU Sockets

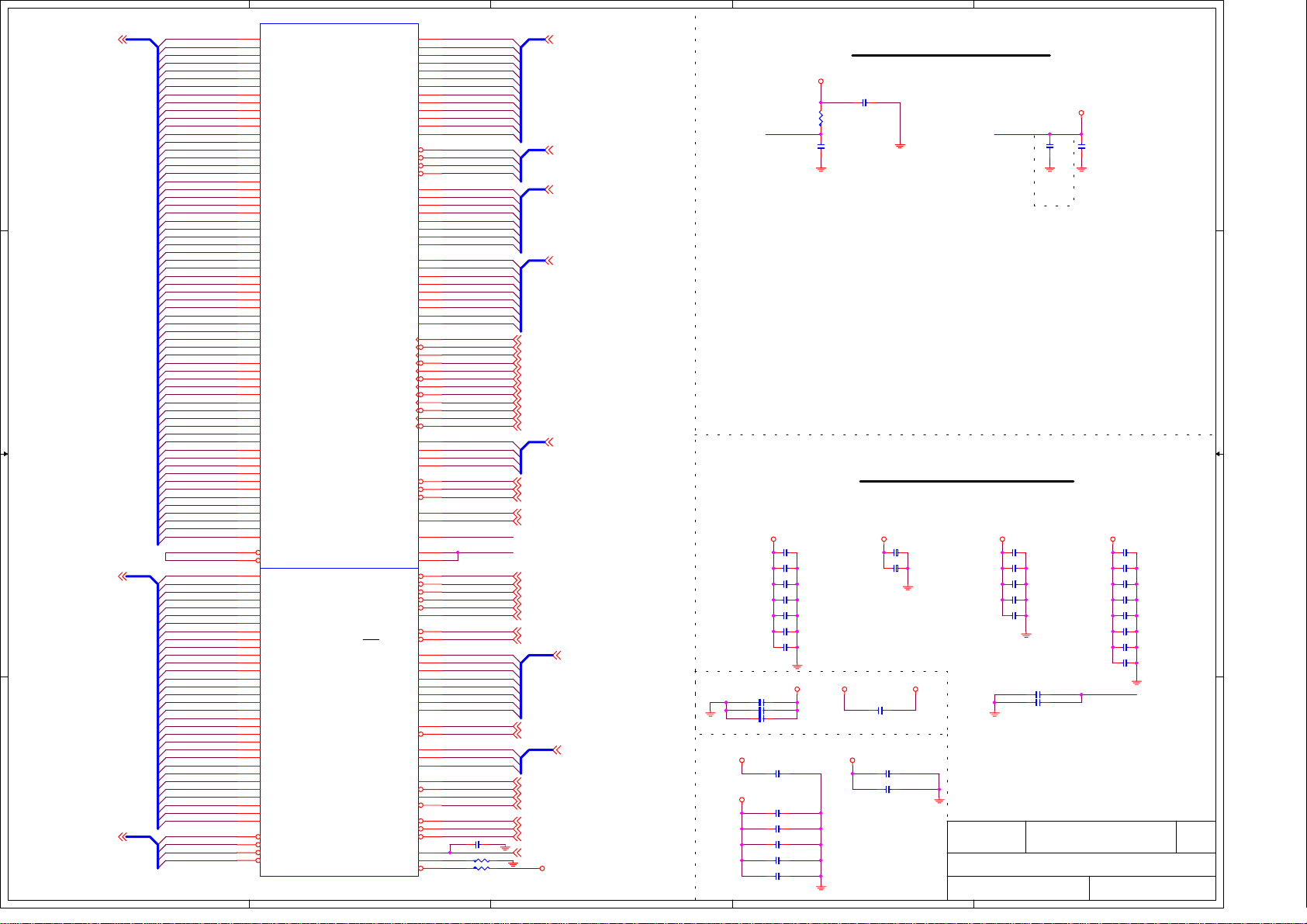

INTEL Brookdale-E MCH -- North Bridge

DDR DIMMM1,2

DDR Damping & DDR Termination

INTEL ICH4 -- South Bridge

C C

Ac'97 Codec and Audio Connector & Game Port

3

4

5

6 - 7

8 - 9

10

11

12-13

14

Willamette/Northwood 478pin mPGA-B Processor Schematics

CPU:

Willamette/Northwood mPGA-478B Processor

System Brookdale Chipset:

INTEL MCH (North Bridge) +

AGP 4X SLOT (1.5V)

PCI SLOT 1 & 2 & 3

Realtek RTL8100(L) LAN

LPC I/O W83627HF

15

16

17

18

INTEL ICH2 (South Bridge)

On Board Chipset:

BIOS -- FWH

LPC Super I/O -- W83627HF

FWH & CNR Connector

USB & FAN Connectors

B B

Front Panel & Connectors

ACPI Controller

L6719B CPU Power ( PWM )-VRM9.0

19

20

21

22

23

Expansion Slots:

Clock Generation -- ICS950213AF

AC'97 Codec -- AvanceLogic

AC201A/AC202A

AGP2.0 SLOT * 1

PCI2.2 SLOT * 3

IO Connectors

JUMPER SETTING

LAYOUT GUIDE

A A

8

7

6

5

24

25

26-30

CNR 2.2 SLOT * 1

Title

Micro-Star

Document Number

Last Revision Date:

4

3

Friday, December 21, 2001

2

MS-6507

Cover Sheet

Sheet of

Rev

5.0

130

1

8

D D

AGP

4X(1.5V)

AGP CONN

7

Power

Supply

CONN

AGP 4X

(1.5V)

6

VRM

9.0

4X (66MHz) AGP

(593PINS/FCBGA)

5

(478PINS)

Willamette/Northwood

Socket (mPGA478-B)

(400/533MHz)

Scalable Bus

MCH: Memory

Controller HUB

4

(100/133MHz)

(100/133MHz)

Scalable Bus/2

(200/266MHz)

3

CK408 Clock

DDR DIMM 1:2

2

1

( 66MHz X 4 )

C C

Heceta Hardware

Monitor

IDE CONN 1&2

USB Port 0:3

SM Bus

(360PINS/EBGA)

(48MHz)

LPC Bus AC Link

Controller HUB

FWH: Firmware HUB

SIO

B B

PS2 Mouse &

Keyboard

Parallel (1)

Serial (2)

Floppy Disk

Drive CONN

HUB Interface

ICH4: I/O

(33MHz)

(33MHz)

(14.318MHz)

PCI (33MHz)

PCI Lan /

RealTek

8100BL

AC '97 Audio

Codec

Audio In

Line In

CD-ROM

PCI Slots 1:3

Line Out

Telephone In

MIC In

RJ-45

Connector

A A

Title

Micro-Star

Document Number

Last Revision Date:

8

7

6

5

4

3

Friday, December 21, 2001

2

MS-6507

Block Diagram

Sheet of

Rev

5.0

230

1

8

7

6

5

4

3

2

1

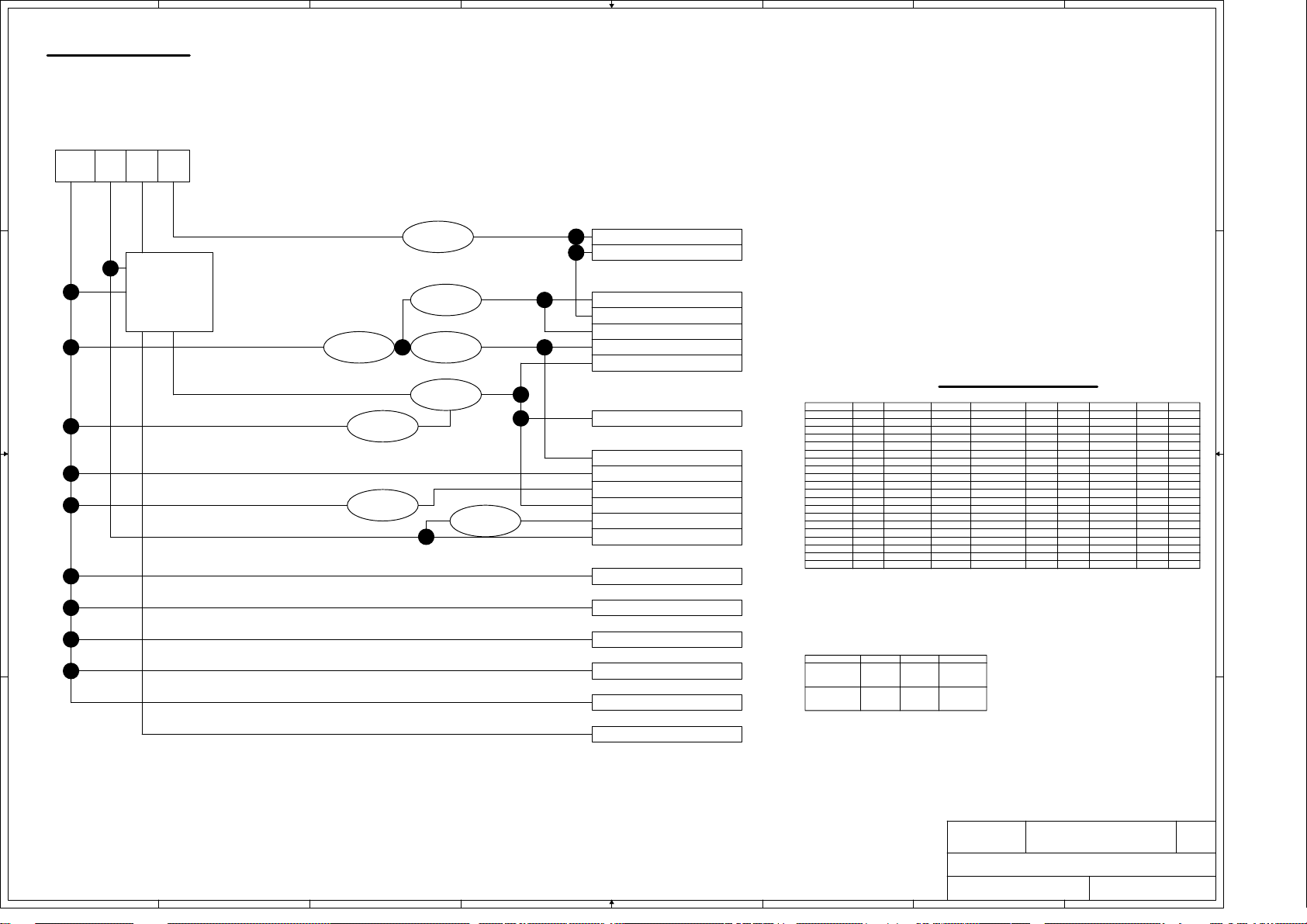

Power Delivery Map

D D

ATX 12V POWER Supply

3.3V 5V 5VSB1A12V

VRM9.2

Processor Core

Processor Vtt

Power

Translator

ACPI IC

1.5V VREG

MCH Core 1.5V

MCH Vtt

MCH AGP

C C

OP

1.8V VREG

MCH HUB Interface 1.8V

MCH Memory DDR 2.5V

3.3V

DUAL

3.3V VREG

FET

DDR System Memory 2.5V

ICH2 Core 1.8V

ICH2 I/O 3.3V

ICH2 Resume 3.3V

1.8V VREG

5V TO 3.3V

RESISTOR

B B

ICH2 Resume I/O 1.8V

ICH2 RTC 3.3V

ICH2 5V

FWH 3.3V

LPC Super I/O 3.3V

CLOCK GEN 3.3V

HARDWARE AUDIO 3.3V

PCI LAN 3.3V/2.5V

5VDual For USB and K/B

CPU

PMCH

ICH2

CY28324

AD1885

FWH -SST

W83627HF

HIP6301

HIP6602A

HIP6601A

DIMM

AGP

PCI

USB

USB HUB

FAN

TTL

AMPLIFIER

OTHER

NOTE1 --- MCH

VCC_AGP

NOTE2 --- DIMM

S0 STATE --- 2.0A * 3 = 6.0A ---> VCC3

S1/S3 STATE --- 200mA * 3 = 600mA ---> VCC3_SB

VCC3_SB --> 600mA*3.3V/5V=396mA --> VCC5_SB

NOTE3 --- ICH2

1.8V

1.8V_LAN 36mA

VCC1_8SB

VCC3

VCC3+562ET

VCC3_SB

VCC3_SB

VCC1_8SB

VCC5_SB

VCCP VCC_AGP

69.0A NOTE40

2.4A NOTE1

0

0

0

0

0

0

0

0

0

000 0

0

0

0

0

0

00000 0

= VCC1_5 (1.5A) VCC_AGP (0.37A)+

S0Power S3/S4/S5

300mA

45mA

410mA

230mA

25mA

=

=

= VCC3_SB VCC1_8SB+

POWER CONSUMPTION

VCC1_8

0

0

0

0

0

0

0

0

0

0SC1547

0

0

0

0

0

S1

100mA

28mA

30mA

5mA

210mA

0.6mA

VCC3_DIMM VCC3 VCC5

0

0.2A

NOTE3 NOTE3 NOTE3

0

0

0

0

0

0

0

0

0

0

0

0

0

0

00

0

2.0A 0 0

0

0

0

0

0

0

0

0

0

NOTE2

0

0

0

0

0

0

N/A

N/A

7mA

N/A

N/A

N/A

0

0

0

0

0

0

0

0

0

6.0A 1.0A8.0A 2.0A

0

0

0

VCC5_SB

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

NOTE2

?

0

0

0

0

+12V

-12V

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

A A

Title

Micro-Star

Document Number

Last Revision Date:

8

7

6

5

4

3

Friday, December 21, 2001

2

MS-6507

Power Delivery Map

Sheet of

Rev

330

1

5

4

3

2

1

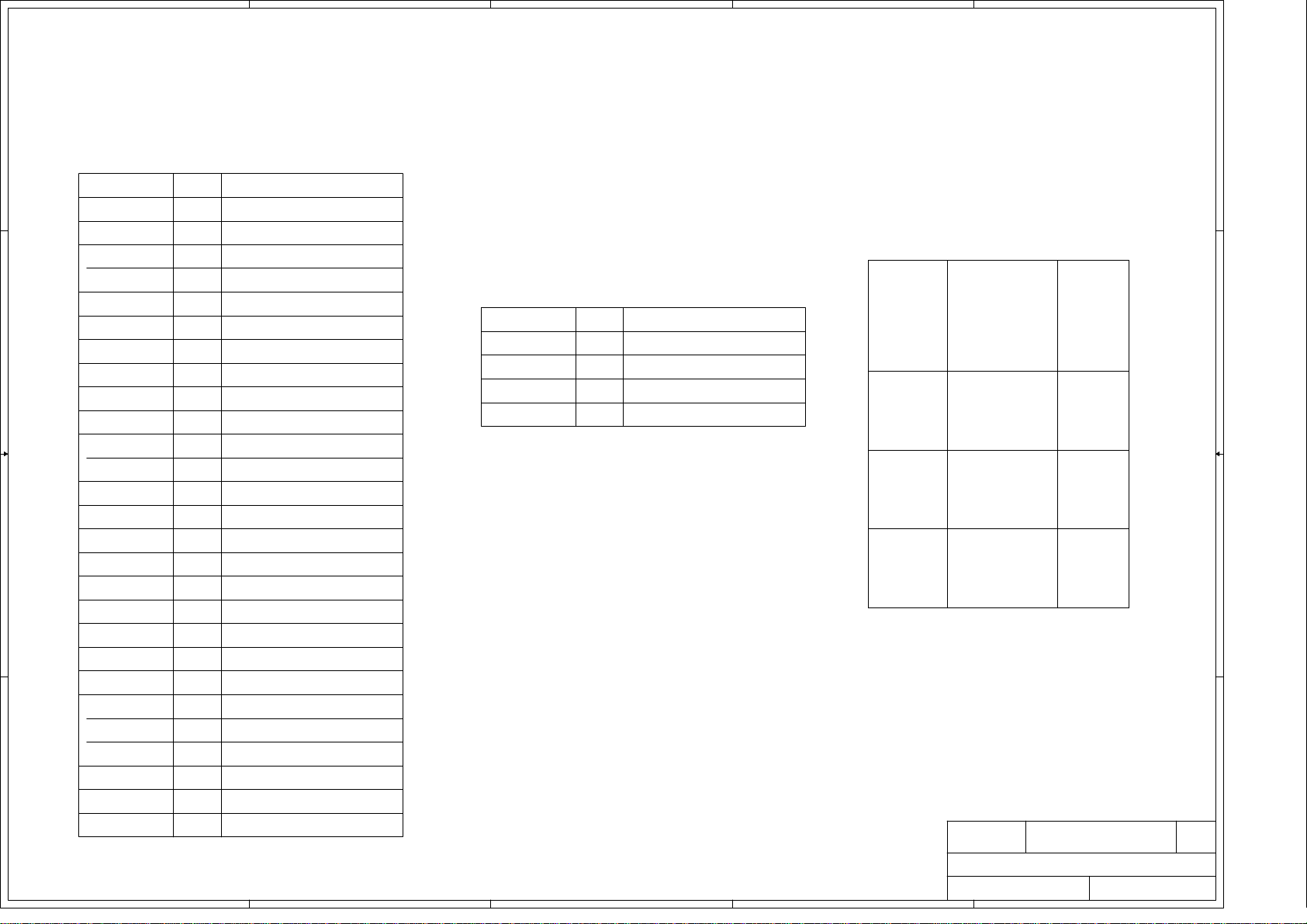

General Purpose I/O Spec.

D D

ICH4

FunctionTypeGPIO Pin

Non Connect

GPIO 0

GPIO 1

GPIO 2~4

GPIO 5

GPIO 6

C C

GPIO 7

GPIO 8

GPIO 9

GPIO 10

GPIO 11

GPIO 12

GPIO 13

GPIO 14~15

GPIO 16

GPIO 17

B B

GPIO 18

GPIO 19

GPIO 20

GPIO 21

GPIO 22

GPIO 23

GPIO 24

GPIO 25

GPIO 26

A A

GPIO 27

GPIO 28

GPIO 29~31

5

I

I

I

I

I

I

I

I

I

I

I

I

I

O

O

O

O

O Non

O

O

OD

O

O

O

I/O

I/O

I/O

Non Connect

Not Implemented

Non Connect

AC97 Enabled/Disabled

None

LAN Wake Up

AC'97 Serial Data In

Non Connect

Non Connect

External SMI

LPC PME

Not Implemented

Non Connect

Non Connect

Not Implemented

Not Implemented

Not Implemented

Non

BIOS Locked/Unlocked

Non

Non

Non

Non

Non

Not Implemented

IDSEL

AD16

AD17

FWH

GPIO Pin Type Function

GPI 0

GPI 1

GPI 2

GPI 3

ATA IDE 1 Detect

I

ATA IDE 2 Detect

I

Reserved

I

Reserved

I

DEVICE

PCI Slot 1

ICH INT Pin

INTA#

INTB#

INTC#

INTD#

PCI Slot 2 INTB#

INTC#

INTD#

INTA#

PCI Slot 3

INTC#

AD18

INTD#

INTA#

INTB#

Title

AD29

MS-6507

GPIO Spec.

Sheet of

1

Rev

5.0

430

PCI Lan INTC#/INTF#

Micro-Star

Document Number

Last Revision Date:

4

3

2

Friday, December 21, 2001

8

for good filtering from 10K~1M

CP1 X_COPPER

VCC3

D D

VCC3

*Put GND copper under Clock Gen.

connect to every GND pin

* 40 mils Trace on Layer 4

with GND copper around it

* put close to every power pin

C C

Trace Width 7mils.

*

Same Group spacing 15mils

*

Different Group spacing 30mils

*

Different mode spacing 7mils on itself

*

VCC3

VCCP

VCC3

SKTOCC#{6}

B B

ST1{9,15}

A A

FB1

CB1

104P

for good filtering from 10K~1M

CP2 X_COPPER

FB2 X_0/0805

CB6

104P

R30

10K

R36 220

R39

X

VCC_AGP

A C

R51

6.8K

Q3

2N3904S

E C

8

X_0/0805

Rubycon

Rubycon

Q1

2N3904S

R46

1K

D1

1N4148S

B

+

X_ELS10U/16V-B

+

X_ELS10U/16V-B

Q2

X_2N3904S

R47

8.2K

R52

R/0603

R56

R/0603

CT1

CT2

BSEL0 {6}

VCC3_C

SMBCLK{10,18,19,22}

SMBDATA{10,18,19,22}

CB2

105P

CB7

105P

R9

X_0

FS1

7

VCC3V

VCC3_C

SMBCLK

SMBDATAVTT_GD#

R34 X_1K

7

6

5

4

3

*Trace less 0.5"

CLOCK GENERATOR BLOCK Shut Source Termination Resistors

PDD[0..7]{13}

VCC5

CB3

104P

CB4

104P

CB5

104P

CB8

104P

CB9

104P

CB10

104P

CB11

104P

CB12

104P

VTT_GD#

HD_RST#{22}

PDIORDY{13}

PDDACK#{13}

39

36

46

43

29

9

5

18

13

24

21

2

47

34

33

26

25

19

PDDREQ{13}

PDIOW#{13}

PDIOR#{13}

IRQ14{12}

PDA1{13}

PDA0{13}

PDCS#1{13}

PD_LED{21}

R55 8.2K

U1

CPU_VDD

CPU_GND

MREF_VDD

MREF_GND

3V66_GND

PCI_VDD

PCI_GND

PCI_VDD

PCI_GND

48_VDD

48_GND

REF_VDD

REF_GND

CORE_VDD

CORE_GND

SCLK

SDATA

VTT_GD#

ICS950213AF

CPU0

CPU0#

CPU1

CPU1#

3VMREF/CPU_STP#

3VMREF#/PCI_STP#

3V66_03V66_VDD

3V66_1

3V66_2

3V66_3

FS2/PCI_F0

FS3/PCI_F1

MODE/PCI_F2

FS4/PCI0

PCI1

PCI2

PCI3

PCI4

PCI5

PCI6

FS0/48MHz

FS1/24_48MHz

MUL0/REF0

MUL1/REF1

IREF

RST#

PWR_DN#

41

40

38

37

45

44

3132

30

28

27

6

7

8

10

11

12

14

15

16

17

22

23

48

1

3

X1

4

X2

35

20

42

R3 33

R5 33

R7 47

R8 47

C_STP

P_STP

1 2

RN1

3 4

8P4R-33

5 6

FS2

FS3

MODE

FS4

FS0

FS1

MUL0

MUL1

X1 14.318MHZ/32PF

7 8

RN2

8P4R-33

R14 33

7 8

RN3

5 6

8P4R-33

3 4

1 2

R19 33

R20 33

R22 33

R24 33

R29 475RST

R32 X_0

R35 4.7K

PRIMARY IDE BLOCK

R41 4.7K

HD_RST#

R43 33

PDD7

PDD6 PDD9

PDD5

PDD4

PDD3

PDD2

PDD1

PDD0

R49 33

C11

47P

6

VCC3

IDE2

YJ220-CB-1

1

3 4

5 6

7 8

91110

13 14

17 18

19

21

23

25

27

29

31

33

35

37

R53

10K

VCC3

CB13

104P

2

12

1615

22

24

26

R45 470

28

30

32

34

36

38

4039

C12

X_473P

CB14

104P

CB15

104P

7 8

5 6

3 4

1 2

18PC6

18PC7

CPUCLK

CPUCLK#

MCHCLK

MCHCLK#

MCH_66

ICH_66

AGPCLK

ICH_PCLK

FWH_PCLK

SIO_PCLK

PCICLK5

PCICLK0

PCICLK1

PCICLK2

PCICLK3

ICH_48

SIO_48

ICH_14

AUDIO_14

FP_RST#CRST#

VCC3V

CPUCLK {6}

CPUCLK# {6}

MCHCLK {8}

MCHCLK# {8}

MCH_66 {8}

ICH_66 {13}

AGPCLK {15}

ICH_PCLK {12}

FWH_PCLK {19}

SIO_PCLK {18}

PCICLK5 {16}

PCICLK0 {16}

PCICLK1 {16}

PCICLK2 {16}

PCICLK3 {17}

ICH_48 {13}

SIO_48 {18}

ICH_14 {13}

AUDIO_14 {14}

FP_RST# {13,21,22}

VCC3V

CLOCK STRAPPING RESISTORS

MUL0=0 MUL0=1

Ioh=6*Iref

Voh=0.71V

ATA100 IDE CONNECTORS

PDD8

PDD10

PDD11

PDD12

PDD13

PDD14

PDD15

CB16

104P

5

PDD[8..15] {13}

PD_DET {19}

PDA2 {13}

PDCS#3 {13}

4

SDD[0..7]{13}

SDIORDY{13}

SDDACK#{13}

VCC5

CPUCLK

CPUCLK#

MCHCLK

MCHCLK#

Trace less 0.2"

49.9ohm for 50ohm M/B impedance

FS1

SDDREQ{13}

SDIOW#{13}

SDIOR#{13}

IRQ15{12}

SDA1{13}

SDA0{13}

SDCS#1{13}

SD_LED{21}

R1 49.9RST

R2 49.9RST

R4 49.9RST

R6 49.9RST

FS4

FS3

FS1

FS0

FS2

MODE

MUL0

MUL1

CRST# VCC3V

SMBCLK

SMBDATA

C_STP

P_STP

R10 10K

R11 10K

R12 10K

R13 X_10K

R15 10K

R16 X_10K

R17 10K

R18 X_10K

R21 X_10K

R23 X_10K

R25 10K

R26 10K

R27 X_10K

R28 10K

R31 1K

R33 1K

R37 X_1K

R38 X_1K

SECONDARY IDE BLOCK

R40 4.7K

HD_RST#

SDD7

SDD6

SDD5

SDD4

SDD3

SDD2

SDD1

SDD0

R54 8.2K

R48 33

3

R42 33

C9

47P

2

VCC3V

VCC3V

VCC3V

VCC3V

VCC3V

VCC3V

VCC3V

VCC3

VCC3V

IDE1

YJ220-CW-1

1

2

3 4

5 6

7 8

91110

12

13 14

1615

17 18

19

22

21

24

23

26

25

28

27

30

29

32

31

34

33

36

35

38

37

4039

R50

10K

VCC3

Micro-Star

Document Number

Last Revision Date:

Friday, December 21, 2001

2

Pull-Down Capacitors

CN1

MCH_66

ICH_66

AGPCLK

SIO_PCLK

FWH_PCLK

ICH_PCLK

PCICLK0

PCICLK1

PCICLK2

PCICLK3

PCICLK4

PCICLK5

AUDIO_14

ICH_48

SIO_48

ICH_14

X_8P4C-10P

1

3

5

7

CN2

X_8P4C-10P

8

6

4

2

CN3

X_8P4C-10P

7

5

3

1

10PC2

10PC3

X_10PC4

10PC5

10PC8

used only for EMI issue

Trace less 0.2"

SDD8

SDD9

SDD10

SDD11

SDD12

SDD13

SDD14

SDD15

R44 470

SD_DET {19}

SDA2 {13}

SDCS#3 {13}

C10

X_473P

Title

MS-6507

Clock CY28323/4 & ATA100 IDE

Sheet of

1

2

4

6

8

7

5

3

1

8

6

4

2

X_10PC1

SDD[8..15] {13}

Rev

5.0

530

1

8

7

6

5

4

3

2

1

CPU GTL REFERNCE VOLTAGE BLOCKCPU SIGNAL BLOCK

C15

105P

C18

X_105P

VCCP

VCCP

R57

49.9RST

R58

100RST

R59

X_49.9RST

R60

X_100RST

VCCP

VCCP

HA#[3..31]{8}

C13

220P

C16

220P

R72 39

R73 75

R74 27

R75 300

2/3*Vccp

C14

220P

2/3*Vccp

C17

220P

VID[0..4] {18,23}

HA#8

HA#22

HA#25

HA#23

HA#26

HA#27

HA#24

HA#28

HA#30

HA#29

D D

U2A

HDBI#[0..3]{8}

STPCLK#{12}

HDBSY#{8}

HDRDY#{8}

HTRDY#{8}

HLOCK#{8}

C C

B B

HDEFER#{8}

Trace : 10

mil width

10mil space

CPU_TMPA{18}

VTIN_GND{18}

THERMTRIP#{12}

SKTOCC#{5}

PROCHOT#{13}

VCC3

BSEL0{5}

CPURST#{8}

HD#[0..63]{8}

R68

X_1K

CPU_GD{13}

HDBI#0

HDBI#1

HDBI#2

HDBI#3

FERR#{12}

HINIT#

HINIT#{12,19}

HADS#{8}

HBNR#{8}

HIT#{8}

HITM#{8}

HBPRI#{8}

ITP_TDI

ITP_TDO

ITP_TMS

ITP_TRST#

ITP_TCK

THERMTRIP#

IGNNE#{12}

HSMI#{12}

A20M#{12}

SLP#{12}

R69

1K

CPU_GD

CPURST#

HD#63

HD#62

HD#61

HD#60

HD#59

HD#58

HD#57

HD#56

HD#55

HD#54

R67

E21

DBI0#

G25

DBI1#

P26

DBI2#

V21

DBI3#

AC3

IERR#

V6

MCERR#

B6

FERR#

Y4

STPCLK#

AA3

BINIT#

W5

INIT#

AB2

RSP#

H5

DBSY#

H2

DRDY#

J6

TRDY#

G1

ADS#

G4

LOCK#

G2

BNR#

F3

HIT#

E3

HITM#

D2

BPRI#

E2

DEFER#

C1

TDI

D5

TDO

F7

TMS

E6

TRST#

D4

TCK

B3

THERMDA

C4

THERMDC

A2

THERMTRIP#

AF26

GND/SKTOCC#

C3

PROCHOT#

B2

IGNNE#

B5

SMI#

C6

A20M#

AB26

SLP#

A22

RESERVED0

A7

RESERVED1

AD2

AD3

AE21

AF24

AF25

AD6

AD5

AB23

AB25

AA24

AA22

AA25

W25

W26

Y21

Y24

Y23

Y26

V24

RESERVED2

RESERVED3

RESERVED4

RESERVED5

RESERVED6

BSEL0

BSEL1

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

V22

D53#

U21

X_0

HA#31

AB1Y1W2V3U4T5W1R6V2T4U3P6U1T2R3P4P3R2T1N5N4N2M1N1M4M3L2M6L3K1L6K4K2

A35#

A34#

A33#

A32#

A31#

A30#

A29#

A28#

A27#

A26#

A25#

D52#

D51#

D50#

D49#

D48#

D47#

D46#

D45#

D44#

D43#

D42#

D41#

D40#

V25

U23

U24

U26

T23

T22

T25

T26

R24

R25

P24

R21

N25

A24#

D39#

N26

A23#

D38#

M26

HA#21

A22#

D37#

N23

A21#

D36#

HA#20

HA#19

A20#

D35#

M24

P21

A19#

D34#

HA#18

HA#17

A18#

D33#

N22

M23

A17#

D32#

HA#15

HA#16

A16#

D31#

H25

K23

HA#14

A15#

D30#

J24

A14#

D29#

HA#13

HA#12

A13#

D28#

L22

M21

A12#

D27#

HA#10

HA#11

A11#

D26#

H24

G26

A10#

D25#

HA#9

A9#

D24#

L21

D26

A8#

D23#

HA#7

A7#

D22#

F26

HA#6

A6#

D21#

E25

HA#5

A5#

D20#

F24

HA#4

A4#

D19#

F23

HA#3

AE25A5A4

A3#

DBR#

Differential

Host Data

Strobes

D18#

D17#

D16#

D15#

G23

E24

H22

D25

VCC_SENSE

D14#

D13#

J21

D23

C26

AD26

AC26

ITP_CLK1

ITP_CLK0

VSS_SENSE

D12#

D11#

D10#

D9#

H21

G22

B25

C24

D8#

C23

D7#

VID4

AE1

B24

VID3

AE2

VID4#

D6#

D22

VID2

AE3

VID3#

D5#

C21

VID1

AE4

VID2#

D4#

A25

VID0

AE5

VID1#

VID0#

TESTHI12

TESTHI11

TESTHI10

LINT1/NMI

LINT0/INTR

D3#

D2#

A23

B22

GTLREF3

GTLREF2

GTLREF1

GTLREF0

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

BCLK1#

BCLK0#

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

COMP1

COMP0

DP3#

DP2#

DP1#

DP0#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

D1#

D0#

B21

AA21

AA6

F20

F6

AB4

AA5

Y6

AC4

AB5

AC6

H3

J3

J4

K5

J1

AD25

A6

Y3

W4

U6

AB22

AA20

AC23

AC24

AC20

AC21

AA2

AD24

AF23

AF22

F4

G5

F1

V5

AC1

H6

P1

L24

L25

K26

K25

J26

R5

L5

W23

P23

J23

F21

W22

R22

K22

E22

E5

D1

SOCKET478

GTLREF1

GTLREF2

BPM#5

BPM#4

BPM#1

BPM#0

HREQ#4

HREQ#3

HREQ#2

HREQ#1

HREQ#0

R61 56.2RST

R62 56.2RST

R63 4.7K

R64 4.7K

R65 4.7K

R66 4.7K

HRS#2

HRS#1

HRS#0

R70 49.9RST

R71 49.9RST

HREQ#[0..4] {8}

VCCP

CPUCLK# {5}

CPUCLK {5}

HRS#[0..2] {8}

HBR#0 {8}

* Short trace

HADSTB#1 {8}

HADSTB#0 {8}

HDSTBP#3 {8}

HDSTBP#2 {8}

HDSTBP#1 {8}

HDSTBP#0 {8}

HDSTBN#3 {8}

HDSTBN#2 {8}

HDSTBN#1 {8}

HDSTBN#0 {8}

NMI {12}

INTR {12}

GTLREF1

GTLREF2

Every pin put one 220pF cap near it.

Trace Width 15mils, Space 15mils.

Keep the voltage dividers within 1.5 inches of the

first GTLREF Pin

ITP_TMS

ITP_TDO

ITP_TCK

HINIT#

HD#5

HD#4

HD#3

HD#2

HD#0

HD#1

R79 62

R83 49.9RST

R85 49.9RST

R86 62

Title

Micro-Star

Document Number

Last Revision Date:

4

3

Friday, December 21, 2001

2

MS-6507

INTEL mPGA478-B CPU1

Sheet of

Rev

5.0

630

1

HD#8

HD#7

HD#9

HD#53

HD#48

HD#47

HD#51

HD#50

HD#49

HD#52

A A

HD#46

HD#45

HD#44

HD#43

HD#41

HD#42

HD#39

HD#40

HD#37

HD#38

HD#35

HD#36

HD#34

HD#33

HD#32

HD#31

HD#29

HD#30

HD#28

HD#27

HD#26

HD#25

HD#23

HD#24

HD#22

HD#21

HD#19

HD#20

HD#18

HD#17

HD#16

HD#15

HD#14

HD#13

HD#12

CPU STRAPPING RESISTORS

BPM#0

BPM#4

BPM#5

8

R76 49.9RST

R77 49.9RST

R80 49.9RST R81 300

R82 49.9RST

VCCP

7

ITP_TDI

ITP_TRST# CPURST#

R78 150

R84 680

6

VCCP VCCP

5

HD#6

HD#10

HD#11

ALL COMPONENTS CLOSE TO CPU

PROCHOT#BPM#1

CPU_GD

HBR#0

THERMTRIP#

8

7

6

5

4

3

2

1

AD22

Y5

Y25

Y22

Y2

W6

W3

W24

W21

V4

V26

V23

V1

U5

U25

U22

U2

T6

T3

T24

T21

R4

R26

R23

R1

P5

P25

P22

P2

N6

N3

N24

N21

M5

M25

M22

M2

L4

L26

L23

L1

K6

K3

K24

VCC_VID {22}

C19

106P/1206

C20

106P/1206

C21

X_226P/1206

L1 4.7UH/100MA

L2 4.7UH/100MA

C22

X_226P/1206

VCCP

CPU VOLTAGE BLOCK

VCCP

A10

A12

A14

A16

A18

A20A8AA10

AA12

AA14

AA16

AA18

AA8

AB11

AB13

AB15

AB17

AB19

AB7

AB9

AC10

AC12

AC14

AC16

AC18

AC8

AD11

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

AE16

AE18

AE20

AE6

AE8

AF11

AF13

AF15

AF17

AF19

AF2

AF21

AF5

AF7

AF9

B11

B13

B15

B17

B19B7B9

C10

C12

C14

C16

C18

C20C8D11

D13

D15

D17

D19D7D9

E10

E12

E14

E16

E18

E20E8F11

F13

F15

F17

F19

AF4

VCC

VSS

VCC

VSS

VCC

VSS

G21G6G24

VCC

VCC

VCC

VSS

VSS

VSS

G3H1H23

F9

VCC

VSS

VSS

H26H4J2

U2B

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

D D

C C

AA11

AA13

AA15

AA17

AA19

AA23

AA26

AB10

AB12

AB14

AB16

AB18

AB20

AB21

AB24

AC11

AC13

AC15

AC17

AC19

AC22

AC25

D10

A11

A13

A15

A17

A19

A21

A24

A26

AA1

AA4

AA7

AA9

AB3

AB6

AB8

AC2

AC5

AC7

AC9

AD1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

A3

VSS

A9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AD10

AD12

AD14

AD16

AD18

AD21

AD4

AD23

AD8

AE11

AE13

AE15

AE17

AE19

AE22

AE24

AE26

AE7

AE9

AF1

AF10

AF12

AF14

AF16

AF18

AF20

AF6

AF8

B10

B12

B14

B16

B18

B23

B20

B26B4B8

C11

C13

C15

C17C2C19

C22

C25C5C7C9D12

D14

D16

D18

D20

D21D3D24D6D8E1E11

E13

E15

E17

E19

E23

E7E9F10

F12

E4

E26

VCC

VSS

VSS

VSS

VSS

VSS

VSS

F14

F16

F18F2F22

F25F5F8

AF3

VCC-VID

VCC-VIDPRG

VSS

VSS

VSS

AE23

VCC-IOPLL

VSS

VSS

J22

J25J5K21

AD20

VCCA

VSSA

VSS

VSS

SOCKET478

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

B B

CPU DECOUPLING CAPACITORS

VCCP VCCP VCCPVCCP

CB17

106P/1206

CB22

106P/1206

CB27

106P/1206

A A

CB18

X_106P/1206

CB23

X_106P/1206

CB28

X_106P/1206

CB32

106P/1206

CB35

106P/1206

CB38

106P/1206

CB41

106P/1206

CB44

X_106P/1206

CB19

106P/1206

CB24

106P/1206

CB29

X_106P/1206

CB33

106P/1206

CB36

X_106P/1206

CB39

106P/1206

CB42

106P/1206

CB45

106P/1206

CB20

106P/1206

CB25

106P/1206

CB30

106P/1206

CB34

106P/1206

CB37

106P/1206

CB40

106P/1206

CB43

106P/1206

CB46

106P/1206

PLACE CAPS WITHIN CPU CAVITY

8

7

6

VCCP

CB21

106P/1206

CB26

106P/1206

CB31

106P/1206

5

Title

Micro-Star

Document Number

Last Revision Date:

4

3

Friday, December 21, 2001

2

MS-6507

INTEL mPGA478-B CPU2

Sheet of

Rev

5.0

730

1

5

AD4

AD3

AE6

AE7

AE11

AD11

AC15

AC16

AD5

AG4

AH9

AD15

AC2

AC13

P25

P24

N27

P23

M26

M25

N25

N24

AA9

AB8

AB18

AB20

AC19

AD18

AD20

AE19

AE21

AF18

AF20

AG19

AG21

AG23

AJ19

AJ21

AJ23

M4

M3

M5

G2

M6

W3

W5

W2

W7

W6

M8

U3A

T4

HA3#

T5

HA4#

T3

HA5#

U3

HA6#

R3

HA7#

P7

HA8#

R2

HA9#

P4

HA10#

R6

HA11#

P5

HA12#

P3

HA13#

N2

HA14#

N7

HA15#

N3

HA16#

K4

HA17#

HA18#

HA19#

L3

HA20#

L5

HA21#

K3

HA22#

J2

HA23#

HA24#

J3

HA25#

L2

HA26#

H4

HA27#

N5

HA28#

HA29#

HA30#

L7

HA31#

V7

BR0#

BNR#

Y7

BPRI#

HLOCK#

V3

ADS#

U6

HREQ0#

T7

HREQ1#

R7

HREQ2#

U5

HREQ3#

U2

HREQ4#

Y5

HIT#

Y3

HITM#

Y4

DEFER#

U7

HTRDY#

RS0#

RS1#

RS2#

V5

DBSY#

V4

DRDY#

R5

HAD_STB0#

N6

HAD_STB1#

HD_STBN0#

HD_STBP0#

HD_STBN1#

HD_STBP1#

HD_STBN2#

HD_STBP2#

HD_STBN3#

HD_STBP3#

DBI0#

DBI1#

DBI2#

DBI3#

J8

BCLK

K8

BCLK#

H_RCOMP0

H_RCOMP1

HI0

HI1

HI2

HI3

HI4

HI5

HI_STB

HI_STB#

VTT

U8

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

845MCH-DDR

HOST

HUB LINK

POWER

HIT#{6}

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HRS#0

HRS#1

HRS#2

HDBI#0

HDBI#1

HDBI#2

HDBI#3

R93 24.9RST

R94

24.9RST

HL0

HL1

HL2

HL3

HL4

HL5

VCCP

HA#[3..31]{6}

D D

HBR#0{6}

HBNR#{6}

HBPRI#{6}

HLOCK#{6}

HREQ#[0..4]{6}

C C

HRS#[0..2]{6}

B B

HL[0..10]{12}

A A

HADS#{6}

HITM#{6}

HDEFER#{6}

HTRDY#{6}

HDBSY#{6}

HDRDY#{6}

HADSTB#0{6}

HADSTB#1{6}

HDSTBN#0{6}

HDSTBP#0{6}

HDSTBN#1{6}

HDSTBP#1{6}

HDSTBN#2{6}

HDSTBP#2{6}

HDSTBN#3{6}

HDSTBP#3{6}

HDBI#[0..3]{6}

MCHCLK{5}

MCHCLK#{5}

HL[0..10]

HL_STB{12}

HL_STB#{12}

5

4

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

66IN

RSTIN#

CPURST#

H_VREF0

H_VREF1

H_VREF2

H_VREF3

H_VREF4

H_SWNG0

H_SWNG1

HI10

HI_REF

HL_RCOMP

VCC1_8

VCC1_8

VCC1_8

VCC1_8

VCC1_8

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD7

RSVD8

RSVD9

NC0

NC1

4

3

HD#0

AA2

HD#1

AB5

HD#2

AA5

HD#3

AB3

HD#4

AB4

HD#5

AC5

HD#6

AA3

HD#7

AA6

HD#8

AE3

HD#9

AB7

HD#10

AD7

HD#11

AC7

HD#12

AC6

HD#13

AC3

HD#14

AC8

HD#15

AE2

HD#16

AG5

HD#17

AG2

HD#18

AE8

HD#19

AF6

HD#20

AH2

HD#21

AF3

HD#22

AG3

HD#23

AE5

HD#24

AH7

HD#25

AH3

HD#26

AF4

HD#27

AG8

HD#28

AG7

HD#29

AG6

HD#30

AF8

HD#31

AH5

HD#32

AC11

HD#33

AC12

HD#34

AE9

HD#35

AC9

HD#36

AE10

HD#37

AD9

HD#38

AG9

HD#39

AC10

HD#40

AE12

HD#41

AF10

HD#42

AG11

HD#43

AG10

HD#44

AH11

HD#45

AG12

HD#46

AE13

HD#47

AF12

HD#48

AG13

HD#49

AH13

HD#50

AC14

HD#51

AF14

HD#52

AG14

HD#53

AE14

HD#54

AG15

HD#55

AG16

HD#56

AG17

HD#57

AH15

HD#58

AC17

HD#59

AF16

HD#60

AE15

HD#61

AH17

HD#62

AD17

HD#63

AE16

P22

J27

AE17

HVREF

M7

R8

Y8

AB11

AB17

HSWNG

AA7

AD13

HL6

L28

HI6

HI7

HI8

HI9

L27

M27

N28

M24

P26

P27

L25

L29

M22

N23

N26

G9

G10

H6

J25

J23

G16

G17

H7

H27

K23

K25

AD26

AD27

HL7

HL8

HL9

HL10

HUB_MREF

R95 40.2RST

VCC1_8

HD#[0..63] {6}

MCH_66 {5}

PCIRST#1 {17,18,19,22}

CPURST# {6}

HL[0..10]

VCC1_8

VCC_AGP

VCC_DIMM

3

VTT1

VTT2

VTT_GND1

VTT_GND2

R22

R29

U22

U26

W22

W29

AA22

AA26

AB21

AC29

AD21

AD23

AE26

AF23

AG29

AJ25

N14

N16

P13

P15

P17

R14

R16

T15

U14

U16

T13

T17

A13

A17

A21

A25

C29

D11

D15

D19

D23

D25

F10

F14

F18

F22

G29

H10

H12

H14

H16

H18

H20

H22

H24

K22

K24

K26

L23

U13

U17

AD12

AD14

AD16

AD19

AD22

AE1

AE4

AE18

AE20

AE29

AF5

AF7

AF9

AF11

AF13

AF15

AF17

AF19

AF21

AF25

AG1

AG18

AG20

AG22

AH19

AH21

AH23

AJ3

AJ5

AJ7

AJ9

AJ11

AJ13

AJ15

AJ17

AJ27

A5

A9

C1

D7

F6

G1

G4

H8

K6

U3C

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

J5

VCCSM

J7

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

845MCH-DDR

POWER

X1X2X3X4X5X6X7

X1X2X3X4X5X6X7

2

A3

GND

A7

GND

A11

GND

A15

GND

A19

GND

A23

GND

A27

GND

D5

GND

D9

GND

D13

GND

D17

GND

D21

GND

E1

GND

E4

GND

E26

GND

E29

GND

F8

GND

F12

GND

F16

GND

F20

GND

F24

GND

G26

GND

H9

GND

H11

GND

H13

GND

H15

GND

H17

GND

H19

GND

H21

GND

J1

GND

J4

GND

J6

GND

J22

GND

J26

GND

J29

GND

K5

GND

K7

GND

K27

GND

L1

GND

L4

GND

L6

GND

L8

GND

L22

GND

L24

GND

L26

GND

M23

GND

N1

GND

N4

GND

N8

GND

N13

GND

N15

GND

N17

GND

N22

GND

N29

GND

P6

GND

P8

GND

P14

GND

P16

GND

R1

GND

R4

GND

R13

GND

R15

GND

R17

GND

R26

GND

T6

GND

T8

GND

T14

GND

T16

GND

T22

GND

U1

GND

U4

GND

U15

GND

U29

GND

V6

GND

V8

GND

V22

GND

W1

GND

W4

GND

W8

GND

W26

GND

Y6

GND

Y22

GND

AA1

GND

AA4

GND

AA8

GND

AA29

GND

AB6

GND

AB9

GND

AB10

GND

AB12

GND

AB13

GND

AB14

GND

AB15

GND

AB16

GND

AB19

GND

AB22

GND

AC1

GND

AC4

GND

AC18

GND

AC20

GND

AC21

GND

AC23

GND

AC26

GND

AD6

GND

AD8

GND

AD10

GND

X8

X8

2

VTT1

VTT_GND1

VTT2

VTT_GND2

MCH REFERENCE BLOCK

C23

CB47

X_226P/1206

104P

CB48

C25

104P

106P/1206

HSWNG

C27

104P

Place 1 Cap. as Close as possible to

every pin of MCH

Trace width use 15 mils and 15mils space

BACK

HVREF

C30

103P

Place 1 Cap. as Close as possible to

every pin of MCH

Trace width use 15 mils and 15mils space

C31

X_103P

C32

X_103P

HUB_MREF

C36

X_103P

Place 0.01uF Cap. as Close as possible to MCH

Trace width use 15 mils and 15mils space

MCH Trace Decoupling Capacitors

11/21 modify

to ddr

chipset

Title

Micro-Star

Document Number

Last Revision Date:

Friday, December 21, 2001

1

L3 4.7UH/1206

C24

106P/1206

L4 4.7UH/1206

C26

X_226P/1206

VCCP

C28

C29

X_103P

X_103P

VCCP

C34

C33

103P

X_103P

VCC1_8

C37

C38

104P

X_104P

VCC1_8

MCH & ICH2

MS-6507

Brookdale MCH1

Sheet of

1

VCC_AGP

VCC_AGP

R87

301RST

R88

150RST

R89

49.9RST

R90

C35

104P

100RST

R91

150RST

R92

150RST

CB49

104P

CB50

104P

Rev

5.0

830

5

U3B

MD[0..63]{11}

D D

C C

B B

A A

1" trace

GAD[0..31]{15}

GC_BE#[0..3]{15}

5

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

GAD0

GAD1

GAD2

GAD3

GAD4

GAD5

GAD6

GAD7

GAD8

GAD9

GAD10

GAD11

GAD12

GAD13

GAD14

GAD15

GAD16

GAD17

GAD18

GAD19

GAD20

GAD21

GAD22

GAD23

GAD24

GAD25

GAD26

GAD27

GAD28

GAD29

GAD30

GAD31

GC_BE#0

GC_BE#1

GC_BE#2

GC_BE#3

G28

C28

E28

H25

G27

C25

B27

D27

E23

E21

C24

D22

B21

D18

C20

E19

E17

C13

C11

D10

E10

R27

R28

R25

U27

U28

V26

V27

U23

U24

U25

V24

Y27

Y26

AA28

AB25

AB27

AA27

AB26

Y23

AB23

AA24

AA25

AB24

AC25

AC24

AC22

AD24

V25

V23

Y25

AA23

F27

F25

B28

E27

C27

B25

D26

E25

D24

C22

B23

C21

D20

C19

C18

E13

C12

B11

C10

B13

E11

T25

T26

T27

T23

T24

G5

G3

SDQ0

SDQ1

SDQ2

SDQ3

SDQ4

SDQ5

SDQ6

SDQ7

SDQ8

SDQ9

SDQ10

SDQ11

SDQ12

SDQ13

SDQ14

SDQ15

SDQ16

SDQ17

SDQ18

SDQ19

SDQ20

SDQ21

SDQ22

SDQ23

SDQ24

SDQ25

SDQ26

SDQ27

SDQ28

SDQ29

SDQ30

SDQ31

SDQ32

SDQ33

SDQ34

SDQ35

SDQ36

SDQ37

SDQ38

SDQ39

SDQ40

C9

SDQ41

D8

SDQ42

E8

SDQ43

SDQ44

B9

SDQ45

B7

SDQ46

C7

SDQ47

C6

SDQ48

D6

SDQ49

D4

SDQ50

B3

SDQ51

E6

SDQ52

B5

SDQ53

C4

SDQ54

E5

SDQ55

C3

SDQ56

D3

SDQ57

F4

SDQ58

F3

SDQ59

B2

SDQ60

C2

SDQ61

E2

SDQ62

SDQ63

RCVENIN#

H3

RCVENOUT#

G_AD0

G_AD1

G_AD2

G_AD3

G_AD4

G_AD5

G_AD6

G_AD7

G_AD8

G_AD9

G_AD10

G_AD11

G_AD12

G_AD13

G_AD14

G_AD15

G_AD16

G_AD17

G_AD18

G_AD19

G_AD20

G_AD21

G_AD22

G_AD23

G_AD24

G_AD25

G_AD26

G_AD27

G_AD28

G_AD29

G_AD30

G_AD31

G_C/BE0#

G_C/BE1#

G_C/BE2#

G_C/BE3#

845MCH-DDR

AGP

Tri-Stated

during

RSTIN#

assertion

DDR

4

SMA0

SMA1

SMA2

SMA3

SMA4

SMA5

SMA6

SMA7

SMA8

SMA9

SMA10

SMA11

SMA12

SCS#0

SCS#1

SCS#2

SCS#3

SDQS0

SDQS1

SDQS2

SDQS3

SDQS4

SDQS5

SDQS6

SDQS7

SDQS8

SCK#0

SCK#1

SCK#2

SCK#3

SCK#4

SCK#5

SCKE0

SCKE1

SCKE2

SCKE3

SRAS#

SCAS#

SWE#

SM_RCOMP

SD_REF0

SD_REF1

G_FRAME#

G_IRDY#

G_TRDY#

G_DEVSEL#

G_STOP#

G_PAR

G_REQ#

G_GNT#

SB_STB

SB_STB#

AD_STB0

AD_STB0#

AD_STB1

AD_STB1#

PIPE#

WBF#

AGPREF

G_RCOMP

TESTIN#

4

SCB0

SCB1

SCB2

SCB3

SCB4

SCB5

SCB6

SCB7

SCK0

SCK1

SCK2

SCK3

SCK4

SCK5

SBS0

SBS1

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

ST0

ST1

ST2

RBF#

E12

F17

E16

G18

G19

E18

F19

G21

G20

F21

F13

E20

G22

E9

F7

F9

E7

C16

D16

B15

C14

B17

C17

C15

D14

F26

C26

C23

B19

D12

C8

C5

E3

E15

E14

F15

J24

G25

G6

G7

G15

G14

E24

G24

H5

F5

G23

E22

H23

F23

F11

G8

G11

G12

G13

J28

J9

J21

Y24

W27

W24

W28

W23

W25

AG24

AH25

AH28

AH27

AG28

AG27

AE28

AE27

AE24

AE25

AF27

AF26

AG25

AF24

AG26

R24

R23

AC27

AC28

AF22

AE22

AE23

AA21

AD25

H26

DDRMA0

DDRMA1

DDRMA2

DDRMA3

DDRMA4

DDRMA5

DDRMA6

DDRMA7

DDRMA8

DDRMA9

DDRMA10

DDRMA11

DDRMA12

CS#0

CS#1

CS#2

CS#3

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

SDQS0

SDQS1

SDQS2

SDQS3

SDQS4

SDQS5

SDQS6

SDQS7

SDQS8

DCLK0

DCLK#0

DCLK1

DCLK#1

DCLK2

DCLK#2

DCLK3

DCLK#3

DCLK4

DCLK#4

DCLK5

DCLK#5

DDRCKE0

DDRCKE1

DDRCKE2

DDRCKE3

RASA#

CASA#

WEA#

BS0

BS1

MRCOMP

DIMMREF

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

ST0

ST1

ST2

CB77 X_104P

R97 40.2RST

R98 X_4.7K

DDRMA[0..12] {10,11}

CS#[0..3] {10,11}

CB[0..7] {11}

SDQS[0..8] {11}

DCLK0 {10}

DCLK#0 {10}

DCLK1 {10}

DCLK#1 {10}

DCLK2 {10}

DCLK#2 {10}

DCLK3 {10}

DCLK#3 {10}

DCLK4 {10}

DCLK#4 {10}

DCLK5 {10}

DCLK#5 {10}

DDRCKE[0..3] {10,11}

RASA# {10,11}

CASA# {10,11}

WEA# {10,11}

BS0 {10,11}

BS1 {10,11}

GFRAME# {15}

GIRDY# {15}

GTRDY# {15}

GDEVSEL# {15}

GSTOP# {15}

GPAR {15}

GREQ# {15}

GGNT# {15}

SBA[0..7] {15}

SB_STB {15}

SB_STB# {15}

ST[0..2] {5,15}

GAD_STB0 {15}

GAD_STB#0 {15}

GAD_STB1 {15}

GAD_STB#1 {15}

PIPE# {15}

RBF# {15}

WBF# {15}

AGPREF {15}

VCC1_8

3

2

1

MCH REFERENCE VOLTAGE

DDR_VTT

C39 X_104P

X_104P

DIMMREF

C41

C42

104P

MRCOMP

104P

C40

R96

33RST

DIMMREF

BACK

MCH DECOUPLING CAPACITOR

VCC1_8 VCC_DIMMVCCP VCC_AGP

C48

X_104P

X_104P/0805

X_104P/0805

CB73

CB74

CB52

105P

CB56

104P

Micro-Star

Document Number

Last Revision Date:

Friday, December 21, 2001

C46 X_105P

11/21 modify

to ddr

chipset

CB53

104P

CB57

104P

CB60

104P

CB63

104P

CB66

104P

Title

104PC44

AGPREF

MS-6507

Brookdale MCH 2

Sheet of

1

CB54

104P

CB58

104P

CB61

104P

CB64

104P

CB67

104P

CB69

104P

CB71

104P

C43

104P

Rev

5.0

930

CB51

105P

CB55

104P

CB59

104P

CB62

104P

CB65

103P

CB68

X_106P/1206

CB70

X_106P/1206

EMI

VCC5

VCC_DIMM VCC5

X_104PC45

X_104PC47

X_104PC49

BACK

VCCP

VCC_AGP

3

CB72

X_104P

CB75

X_104P

CB76

X_104P

CB78

X_104P

CB79

X_104P

CB80

X_104P

VCC_DIMM

2

Loading...

Loading...