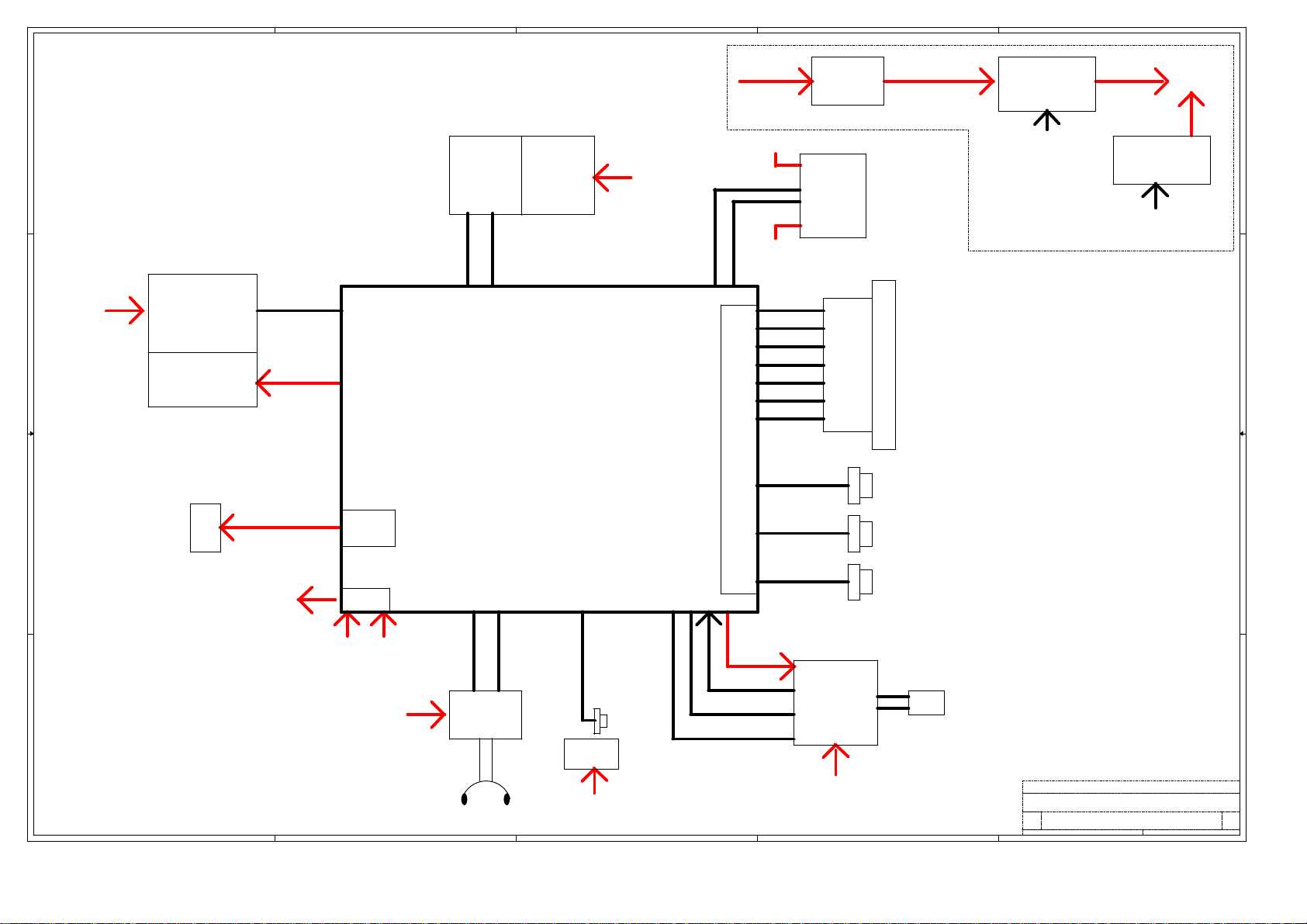

MSI MS-55591 Schematic 10

5

4

3

2

1

MS-55591-1.0 BLOCK DIAGRAM(2006/08)

D D

FLASH

FLASH

VDDIO_P

VBAT

VBUS(5V)

D+

3.3V

LDO

VDDIO

3.3V

POWER

SWITCH

VDDD

1.8V

VDDIO_P

REGULATOR

USB

D-

A

D

GND

USB_5V

1.8"

VDDIO_P

C C

TFT

LCD

Power/Play/Pause

B

Menu

VOL +

Back Light

PWM

U

T

VOL Forward

Reward

OK

Main Chip

T

STMP3507

O

REC

B B

450mA

Li-ON

VBAT

Charger

N

HOLD

S

RESET

1.8V

A A

LDO

Li-lon

VDDIO_P

VBUS(5V)

ORVBAT

Line

IN/OUT

Audio 24MHz

Switch

1.8V

RTC

I2S

I2C

STFM

1000

MIC

VDDIO_P

MIC_BIAS

5

4

3

2

Title

MS-55591

Size Document Number Rev

_ 0A

Custom

Date: Sheet of

1

1 9Thursday, August 31, 2006

5

4

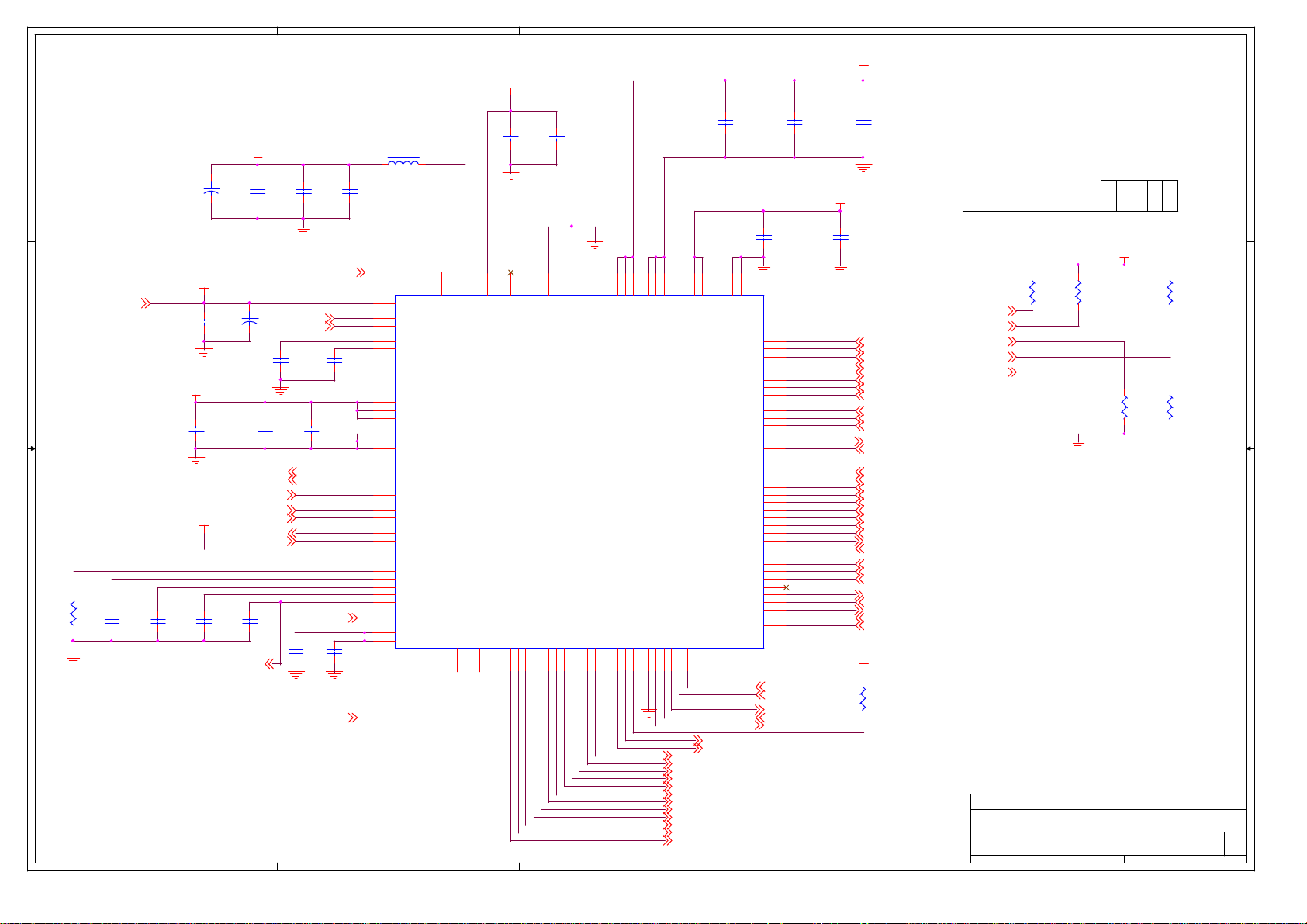

STMP3507 100-Pin TQFP - 1 CHANNEL BUCK MODE

VDD_BAT

3

One cap for each pin (39, 11, 86)

+1.8V

VDDD

2

1

C7

29

28

96

VddIO1

VssIO1

VddIO2

GP55 / SM_WPn

GP54 / SM_WEn

GP51 / CF_IOWRn

GP52 / CF_IORDn

GP42 / CF_A10

GP35 / CF_A3

GP34 / CF_A2

GP33 / CF_A1

GP32 / CF_A0

GP43 / CF_REGn

GP50 / CF-RESETn

GP44 / CF_CE1n

GP49 / CF_BVD1

GP48 / CF_WPn

GP47_CF_READY

GP46 / CF_CDn

I2C_SDA

I2C_SCL

uSD_CLK

uSD_DATA_OUT

uSD_DATA_IN

SW_LIN_IN 7

LCD_D0 5

0.1uF

97

GND

VssIO2

L1

C15

0.1uF

C24

4pF

SDR-31-4R7M

IND_SDR31_100M

1 2

C6

1uF

U1

61

Vdd5V

80

USB_DP

81

USB_DM

67

Vag

66

Vbg

64

VddHP

73

VddA1

76

VddPLL

63

VssHP

72

VssA1

78

VssPLL

65

HPR

62

HPL

55

MIC

59

LINE1R / HP_COMMON

57

LINE1L / HP_SENSE

58

LRADC1 / MIC_BIAS

60

LRADC2 / TEMP_SENSE / MIC_BIAS

56

BATT

70

REF_RES

71

REFp

68

ADCL

69

ADCR

77

VddXTAL

75

XTALi

74

XTALo

4

79

PSWITCH

465251

49

DCDC_Batt

ONCE_DSI

ONCE_DSO

ONCE_DSK

D D

USB_5V3,5

C C

VDDD

GND

B B

R6

620

C19

0.1uF

C20

1000pF

5

1%

GND

A A

+

USB_5V

GND

C16

0.1uF

VDD_BAT

C3

68uF

C13

0.1uF

C21

1000pF

VDD_XTAL6,8

VDDD

LINE_OUT_R7

LINE_OUT_L7

+

LINE_IN_R7

LINE_IN_L7

MIC_BIAS7

LRADC29

C4

0.01uFC50.1uF

GND

C12

USB_D+5

1uF

USB_D-5

C14

1uF

GND

C17

0.1uF

LINE_OUT_R

LINE_OUT_L

MIC

MIC7

LINE_IN_R

LINE_IN_L

C22

0.1uF

GND GND

C23

4pF

PSWITCH8

USB_D+

USB_D-

C18

0.1uF

XTAL_OUT6

XTAL_IN6

GND

484750

DCDC_VddD

DCDC_VddIO

GP7 / I2S_DataO2

ONCE_DRn

8889909192939495828385

53

C1

0.01uFC20.1uF

54

DCDC_Gnd

STMP3507

GP6 / I2S_DataO1

GP5 / I2S_DataO0

GP4 / I2S_BCLK

GP3 / I2S_WCLK

GP2 / I2S_DataI2

GP1 / I2S_DataI1

GP0 / I2S_DataI0

GND

DCDC_Mode2

GP11

GP9

GP10

GP8

84

86

87

11

10

39

38

VddD3

VssD3

VddD2

VssD2

VddD1

VssD1

GP56 / SM_READY / CF_WAITn

GP45 / SM_CE1n / CF_CE0n

TESTMODE

GP19 / TIO1

GP18 / TIO0

GP15 / SPI-SSn

GP14 / SPI_MOSI / SM_WP2n

GP13 / SPI_MISO

6

98

99

1001234

GND

SW_LIN_IN

LCD_D0

LCD_CS#

LCD_WR#

PWM

LCD_RS

I2S_DATA

LCD_D1

LCD_D2

I2S_WCLK

I2S_BCLK

LCD_D5

LCD_D6

LCD_D7

3

One cap for each pin (29, 96)

GP31 / SM_D7 / CF_D7

GP30 / SM_D6 / CF_D6

GP29 / SM_D5 / CF_D5

GP28 / SM_D4 / CF_D4

GP27 / SM_D3 / CF_D3

GP26 / SM_D2 / CF_D2

GP25 / SM_D1 / CF_D1

GP24 / SM_D0 / CF_D0

GP41 / SM_ALE / CF_A9

GP40 / SM_CLE / CF_A8

GP39 / SM_SEn / CF_A7

GP38 / SM_CE0n / CF_A6

GP37 / SM_CE2n / CF_A5

GP36 / SM_CE3n / CF_A4

GP53 / SM_REn / CF_OEn

GP12 / SPI_SCK

GP16 / I2C_SCL

GP17 / I2C_SDA

5

LCD_CS# 5

LCD_WR# 5

PWM 3

LCD_RS 5

I2S_DATA 6

LCD_D1 5

LCD_D2 5

I2S_WCLK 6

I2S_BCLK 6

LCD_D5 5

LCD_D6 5

LCD_D7 5

C8

0.1uF

C10

0.1uF

37

36

35

34

33

32

31

30

WP#

27

WE#

26

FLASH_RDY

25

LCD_D4

9

VOLUP

8

OK

22

ALE

21

CLE

20

FORWARD

19

CE0#

18

CE2#

17

CE3#

16

HOLD

15

PLAY_SWMIC_BIAS

14

LCD_D3

13

uSD_DETECT

12

CE1#

24

RE#

23

MENU

44

43

LCD_RESET

7

REC

45

SW_LIN_OUT

42

VOLDN

41

REWARD

40

I2C_SDA 6

I2C_SCL 6

uSD_CLK 4

uSD_DATA_OUT 4

uSD_DATA_IN 4

C9

0.1uF

STMP35XX BOOT MODE SELECT

GND

VDDIO

C11

0.1uF

GND

IO7

IO6

IO5

IO4

IO3

IO2

IO1

IO0

IO7 4

IO6 4

IO5 4

IO4 4

IO3 4

IO2 4

IO1 4

IO0 4

WP# 4

WE# 4

FLASH_RDY 4

LCD_D4 5

VOLUP 8

OK 8

ALE 4

CLE 4

FORWARD 8

CE0# 4

CE2# 4

CE3# 4

HOLD 8

PLAY_SW 8

LCD_D3 5

uSD_DETECT 4

CE1# 4

RE# 4

MENU 8

LCD_RESET 5

REC 8

SW_LIN_OUT 7

VOLDN 8

REWARD 8

VDDIO_P

R7

47K

2

BOOT MODE 02

3.3V NAND w/Play Recovery

R1

2.2K

I2S_DATA5

LCD_D15

LCD_D25

I2S_WCLK5

LCD_CS#5

GND

Title

MS-55591

Size Document Number Rev

_ 0A

Custom

Date: Sheet of

00

1 1

VDDIO_P

R2

47K

GPIO

01 03

1

0

R4

47K

1

08

0

R3

2.2K

R5

47K

2 9Thursday, August 31, 2006

5

4

3

2

1

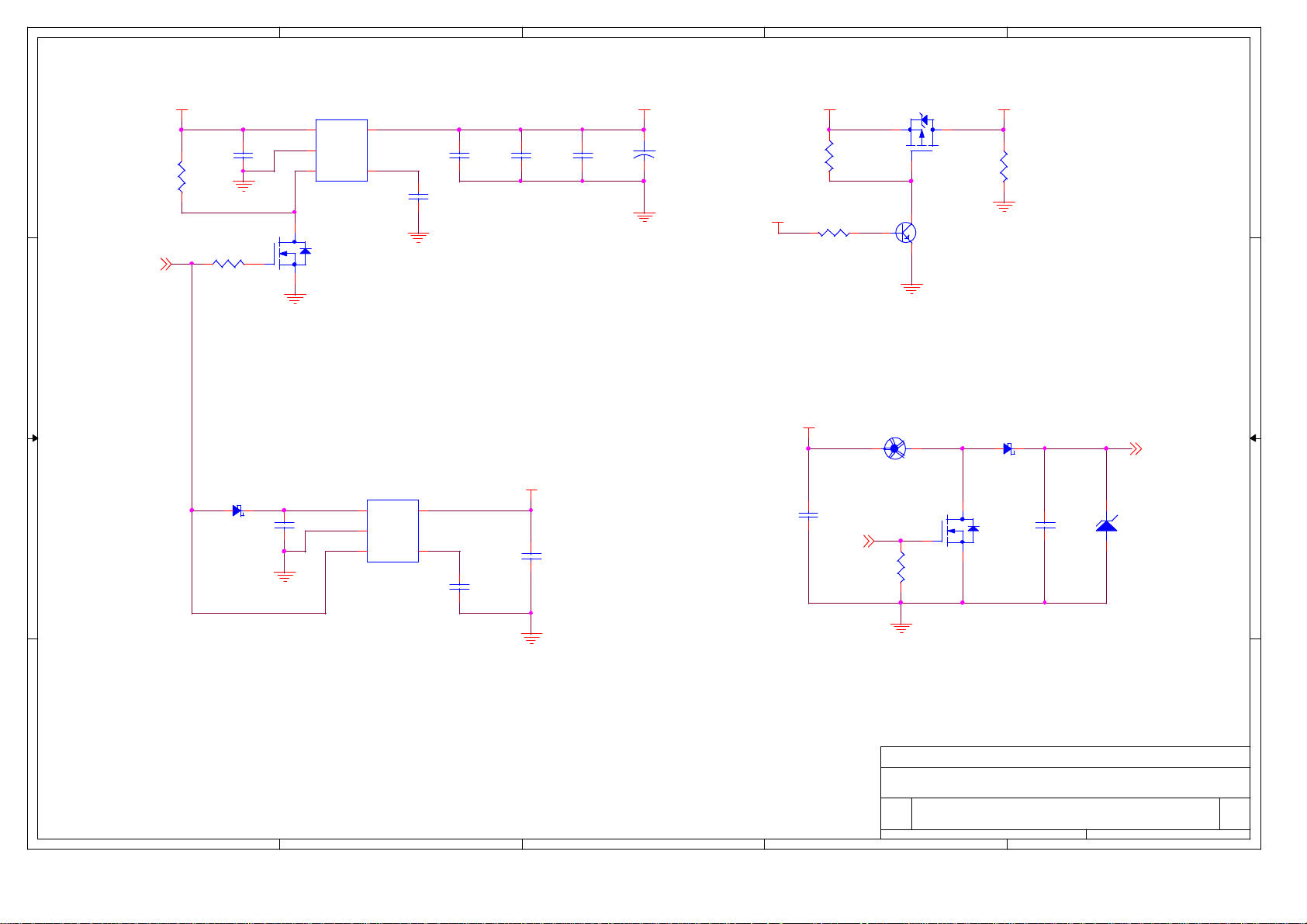

POWER

VDD_BAT

D D

C26

1uF

R10

1M

GND

Q3

2N7002

USB_5V2,5

C C

R12 1K

VDDIO REGULATOR

U2

1

2

GND

3

ENINByP

RT9167A33PB_500mA

GND

OUT

5

4

GND

C30

10000pF

C27

0.01uF

3.3V

C28

0.1uF

C29

1uF

VDDIO

+

GND

C25

22uF

VDDD

VDDIO_P Power Switch

Q1

IRLML6401

R8

100K R9

R11

100K

B

GND

CE

Q2

N-MMBT3904_SOT23

VDDIO_PVDDIO

100K

GND

LCD BACKLIGHT

VDDIO_P

CHOKE1

VDDIO_P REGULATOR

100uH

PWM2

R13

47K

C35

22nF

VDDIO_P

C32

1uF

C33

1uF

RB551V-30-S-SOD-323

CA

C31

D2

B B

1uF

GND

U3

1

2

GND

3

ENINByP

RT9193-30PU5_300mA

OUT

5

4

RB551V-30-S-SOD-323

Q4

AO3400

CA

D1

C34

2.2uF

VLED+ 5

D3

BZT52C15-ZENER-15V

A C

GND

A A

5

4

3

GND

Title

MS-55591

Size Document Number Rev

Date: Sheet of

2

_ 0A

Custom

3 9Thursday, August 31, 2006

1

Loading...

Loading...