Motorola MC68HC908AZ60CFU, MC68HC908AZ60MFU, MC68HC908AZ60VFU Datasheet

MC68HC908AZ60/D

MC68HC908AZ60

Rev 2.0

HCMOS Microcontroller Unit

TECHNICAL DATA

MC68HC908AZ60 — Rev 2.0

MOTOROLA List of Sections 1

List of Sections

List of Sections

List of Sections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Table of Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

RAM. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

FLASH-1 Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

FLASH-2 Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

EEPROM-1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

EEPROM-2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Central Processor Unit (CPU) . . . . . . . . . . . . . . . . . . . . . 87

System Integration Module (SIM). . . . . . . . . . . . . . . . . 105

Clock Generator Module (CGM). . . . . . . . . . . . . . . . . 127

Configuration Register (CONFIG-1) . . . . . . . . . . . . . . . 155

Configuration Register (CONFIG-2) . . . . . . . . . . . . . . . 159

Break Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

© Motorola, Inc., 1999

List of Sections

MC68HC908AZ60 — Rev 2.0

2 List of Sections MOTOROLA

Monitor ROM (MON) . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

Computer Operating Properly Module (COP) . . . . . . 179

Low-Voltage Inhibit (LVI) . . . . . . . . . . . . . . . . . . . . . . . 185

External Interrupt Module (IRQ) . . . . . . . . . . . . . . . . . . 191

Serial Communications Interface Module (SCI). . . . . 199

Serial Peripheral Interface Module (SPI) . . . . . . . . . . . 237

Timer Interface Module B (TIMB) . . . . . . . . . . . . . . . . . 269

Programmable Interrupt Timer (PIT) . . . . . . . . . . . . . . . 295

I/O Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 305

MSCAN Controller (MSCAN08). . . . . . . . . . . . . . . . . . . 331

Keyboard Module (KBD). . . . . . . . . . . . . . . . . . . . . . . . 381

Timer Interface Module A (TIMA-6) . . . . . . . . . . . . . . . 389

Analog-to-Digital Converter (ADC-15) . . . . . . . . . . . . 421

Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 433

Appendix A: Future EEPROM Registers . . . . . . . . . . . . 449

Glossary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 453

Literature Updates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 465

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 469

MC68HC908AZ60 — Rev 2.0

MOTOROLA Table of Contents 3

Table of Contents

Table of Contents

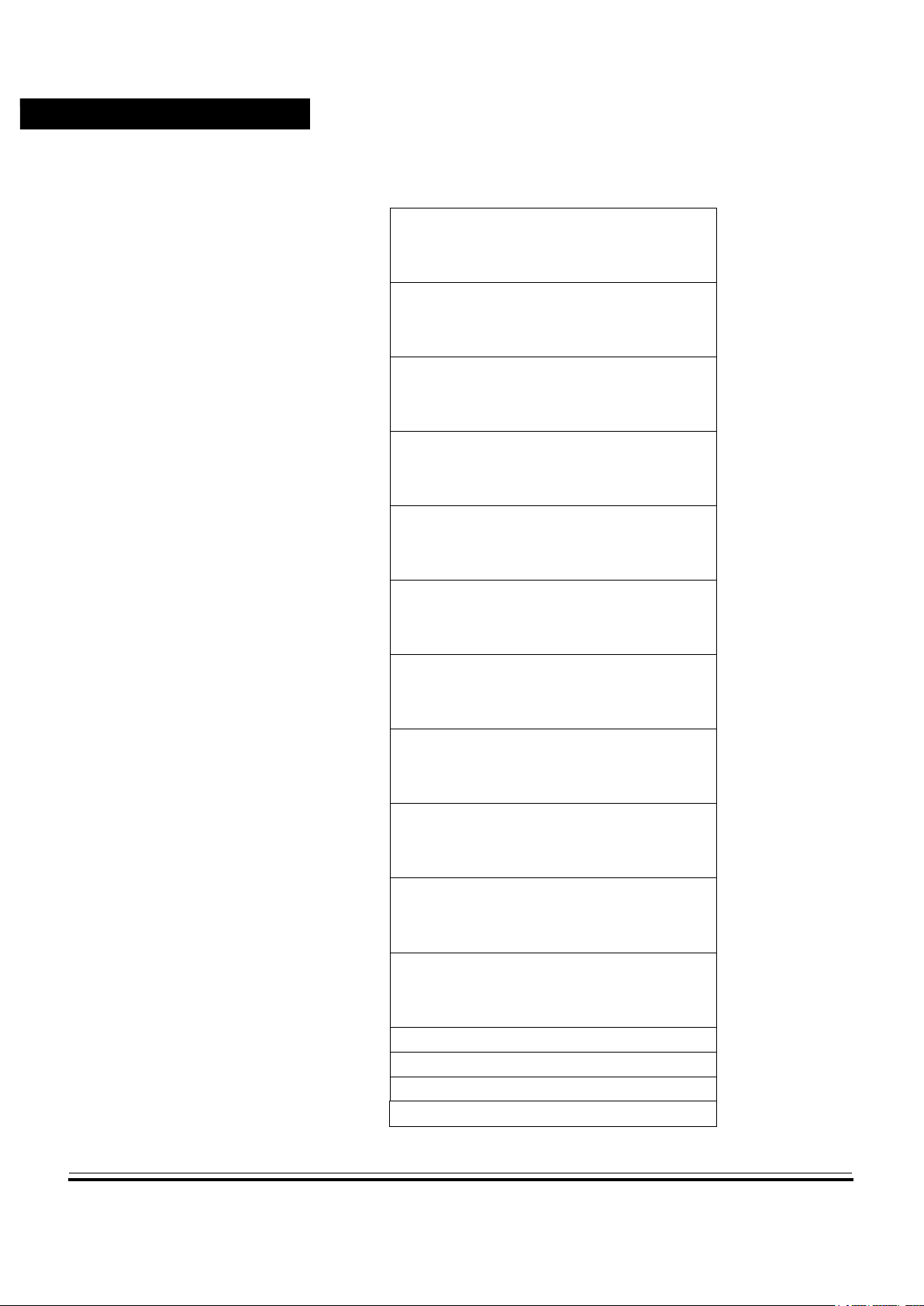

List of Sections

Table of Contents

General Description Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12

MCU Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

Memory Map Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

I/O Section . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

RAM Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

FLASH-1 Memory Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

Future FLASH Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .38

FLASH-1 Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

FLASH Charge Pump Frequency Control . . . . . . . . . . . . . . . . . . . . .41

FLASH Erase Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

FLASH Program/Margin Read Operation . . . . . . . . . . . . . . . . . . . . . .43

FLASH Block Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .46

FLASH-1 Block Protect Register . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

FLASH-2 Block Protect Register . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

FLASH-2 Memory Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

Future FLASH Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

Table of Contents

MC68HC908AZ60 — Rev 2.0

4 Table of Contents MOTOROLA

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52

FLASH Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53

FLASH Charge Pump Frequency Control . . . . . . . . . . . . . . . . . . . . .55

FLASH Erase Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .55

FLASH Program/Margin Read Operation . . . . . . . . . . . . . . . . . . . . . .57

FLASH Block Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .60

FLASH Block Protect Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .60

Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .61

EEPROM-1 Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63

Future EEPROM Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .64

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .64

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .65

Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .74

EEPROM-2 Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .75

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .75

Future EEPROM Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .76

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .76

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .77

Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .86

Central Processor

Unit (CPU)

Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .87

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .87

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .88

CPU registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .89

Arithmetic/logic unit (ALU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .94

Low-power modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .94

CPU during break interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .95

Instruction Set Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .96

Opcode Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .103

System Integration

Module (SIM)

Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .105

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .106

SIM Bus Clock Control and Generation . . . . . . . . . . . . . . . . . . . . . .109

Reset and System Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . .110

SIM Counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .115

Program Exception Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .116

Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .120

SIM Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123

Table of Contents

MC68HC908AZ60 — Rev 2.0

MOTOROLA Table of Contents 5

Clock Generator

Module (CGM)

Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

I/O Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

CGM Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

CGM During Break Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

Acquisition/Lock Time Specifications . . . . . . . . . . . . . . . . . . . . . . . 149

Configuration

Register

(CONFIG-1)

Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

Configuration

Register

(CONFIG-2)

Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

Break Module Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

Break Module Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165

Monitor ROM

(MON)

Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

Computer

Operating

Properly Module

(COP)

Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 179

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 179

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 180

I/O Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 181

COP Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 183

Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 183

Monitor Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 183

Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 184

COP Module During Break Interrupts . . . . . . . . . . . . . . . . . . . . . . . 184

Table of Contents

MC68HC908AZ60 — Rev 2.0

6 Table of Contents MOTOROLA

Low-Voltage

Inhibit (LVI)

Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .185

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .186

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .186

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .186

LVI Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .189

LVI Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .190

Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .190

External Interrupt

Module (IRQ)

Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .191

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .191

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .191

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .192

IRQ

Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .195

IRQ Module During Break Interrupts . . . . . . . . . . . . . . . . . . . . . . . .196

IRQ Status and Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . .197

Serial

Communications

Interface Module

(SCI)

Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .199

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .200

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .200

Pin Name Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .201

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .201

Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .218

SCI During Break Module Interrupts . . . . . . . . . . . . . . . . . . . . . . . . .219

I/O Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .219

I/O Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .220

Serial Peripheral

Interface Module

(SPI)

Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .237

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .238

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .238

Pin Name and Register Name Conventions . . . . . . . . . . . . . . . . . . .239

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .240

Transmission Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .244

Error Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .249

Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .253

Queuing Transmission Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .255

Resetting the SPI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .256

Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .257

SPI During Break Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .258

I/O Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .259

I/O Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .262

Table of Contents

MC68HC908AZ60 — Rev 2.0

MOTOROLA Table of Contents 7

Timer Interface

Module B (TIMB)

Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 269

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 270

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 270

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 273

Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 280

Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 281

TIMB During Break Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 282

I/O Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 283

I/O Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 284

Programmable

Interrupt Timer (PIT)

Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 295

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 295

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 296

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 296

PIT Counter Prescaler . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 298

Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 298

PIT During Break Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 299

I/O Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 300

I/O Ports Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 305

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 306

Port A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 307

Port B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 309

Port C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 312

Port D . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 315

Port E . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 318

Port F . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 322

Port G . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 325

Port H . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 327

MSCAN Controller

(MSCAN08)

Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 331

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 332

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 333

External Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 334

Message Storage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 335

Identifier Acceptance Filter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 340

Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 344

Protocol Violation Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 346

Low Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 346

Timer Link . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 350

Clock System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 351

Table of Contents

MC68HC908AZ60 — Rev 2.0

8 Table of Contents MOTOROLA

Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .355

Programmer’s Model of Message Storage . . . . . . . . . . . . . . . . . . . .355

Programmer’s Model of Control Registers . . . . . . . . . . . . . . . . . . . .360

Keyboard Module

(KBD)

Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .381

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .381

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .382

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .382

Keyboard Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .385

Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .386

Keyboard Module During Break Interrupts . . . . . . . . . . . . . . . . . . . .386

I/O Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .387

Timer Interface

Module A (TIMA-6)

Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .389

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .390

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .390

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .393

Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .402

Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .403

TIMA During Break Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .404

I/O Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .405

I/O Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .406

Analog-to-Digital

Converter (ADC-15)

Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .421

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .421

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .422

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .422

Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .425

Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .425

I/O Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .426

I/O Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .427

Specifications Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .433

Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .434

Mechanical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .447

Appendix A: Future

EEPROM Registers

EEPROM Timebase Divider Control Registers . . . . . . . . . . . . . . . .449

EEDIVH and EEDIVL Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . .450

EEDIV Non-volatile Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .451

Table of Contents

MC68HC908AZ60 — Rev 2.0

MOTOROLA Table of Contents 9

Glossary

Literature Updates Literature Distribution Centers . . . . . . . . . . . . . . . . . . . . . . . . . . . . 465

Customer Focus Center . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 466

Microcontroller Division’s Web Site . . . . . . . . . . . . . . . . . . . . . . . . . 466

Revision History Major Changes Between Revision 2.0 and Revision 1.0 . . . . . . . . 469

Table of Contents

MC68HC908AZ60 — Rev 2.0

10 Table of Contents MOTOROLA

MC68HC908AZ60 — Rev 2.0

MOTOROLA General Description 11

General Description

General Description

Contents

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

MCU Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

Power Supply Pins (VDD and VSS) . . . . . . . . . . . . . . . . . . . . . . . .16

Oscillator Pins (OSC1 and OSC2) . . . . . . . . . . . . . . . . . . . . . . . . .16

External Reset Pin (RST) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

External Interrupt Pin (IRQ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Analog Power Supply Pin (VDDA) . . . . . . . . . . . . . . . . . . . . . . . . .17

Analog Ground Pin (VSSA). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

External Filter Capacitor Pin (CGMXFC) . . . . . . . . . . . . . . . . . . . .17

Port A Input/Output (I/O) Pins (PTA7–PTA0) . . . . . . . . . . . . . . . . .17

Port B I/O Pins (PTB7/ATD7–PTB0/ATD0) . . . . . . . . . . . . . . . . . . 17

Port C I/O Pins (PTC5–PTC0) . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

Port D I/O Pins (PTD7–PTD0/ATD8) . . . . . . . . . . . . . . . . . . . . . . .18

Port E I/O Pins (PTE7/SPSCK–PTE0/TxD) . . . . . . . . . . . . . . . . . .18

Port F I/O Pins (PTF6–PTF0/TACH2). . . . . . . . . . . . . . . . . . . . . . .18

Port G I/O Pins (PTG2/KBD2–PTG0/KBD0). . . . . . . . . . . . . . . . . .18

Port H I/O Pins (PTH1/KBD4–PTH0/KBD3) . . . . . . . . . . . . . . . . . . 18

CAN Transmit Pin (CANTx) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

CAN Receive Pin (CANRx). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

Ordering Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

MC Order Numbers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

Introduction

The MC68HC908AZ60 is a member of the low-cost, high-performance

M68HC08 Family of 8-bit microcontroller units (MCUs). The M68HC08

Family is based on the customer-specified integrated circuit (CSIC)

design strategy. All MCUs in the family use the enhanced M68HC08

1-gen

General Description

MC68HC908AZ60 — Rev 2.0

12 General Description MOTOROLA

central processor unit (CPU08) and are available with a variety of

modules, memory sizes and types, and package types.

This part is designed to emulate the MC68HC08AZxx automotive family.

In AZxx mode the MC68HC908AZ60 offers extra features which are not

available on the MC68HC08AZ32 device. It is the user’s responsibility to

ensure compatibility between the features used on the

MC68HC908AZ60 and those which are available on the device which

will ultimately be used in the application.

Features

Features of the MC68HC908AZ60 include:

• High-Performance M68HC08 Architecture

• Fully Upward-Compatible Object Code with M6805, M146805,

and M68HC05 Families

• 8.4 MHz Internal Bus Frequency

• 60 Kbytes of FLASH Electrically Erasable Read-Only Memory

(FLASH)

• FLASH Data Security

• 1 Kbyte of On-Chip Electrically Erasable Programmable

Read-Only Memory with Security Option (EEPROM)

• 2 Kbyte of On-Chip RAM

• Clock Generator Module (CGM)

• Serial Peripheral Interface Module (SPI)

• Serial Communications Interface Module (SCI)

• 8-Bit, 15-Channel Analog-to-Digital Converter (ADC-15)

• 16-Bit, 6-Channel Timer Interface Module (TIMA-6)

• Programmable Interrupt Timer (PIT)

• System Protection Features

2-gen

General Description

MCU Block Diagram

MC68HC908AZ60 — Rev 2.0

MOTOROLA General Description 13

– Computer Operating Properly (COP) with Optional Reset

– Low-Voltage Detection with Optional Reset

– Illegal Opcode Detection with Optional Reset

– Illegal Address Detection with Optional Reset

• Low-Power Design (Fully Static with Stop and Wait Modes)

• Master Reset Pin and Power-On Reset

• 16-Bit, 2-Channel Timer Interface Module (TIMB)

• 5-Bit Keyboard Interrupt Module

• MSCAN Controller (Motorola Scalable CAN) implements CAN

2.0b Protocol as Defined in BOSCH Specification September

1991

Features of the CPU08 include:

• Enhanced HC05 Programming Model

• Extensive Loop Control Functions

• 16 Addressing Modes (Eight More Than the HC05)

• 16-Bit Index Register and Stack Pointer

• Memory-to-Memory Data Transfers

• Fast 8 × 8 Multiply Instruction

• Fast 16/8 Divide Instruction

• Binary-Coded Decimal (BCD) Instructions

• Optimization for Controller Applications

• C Language Support

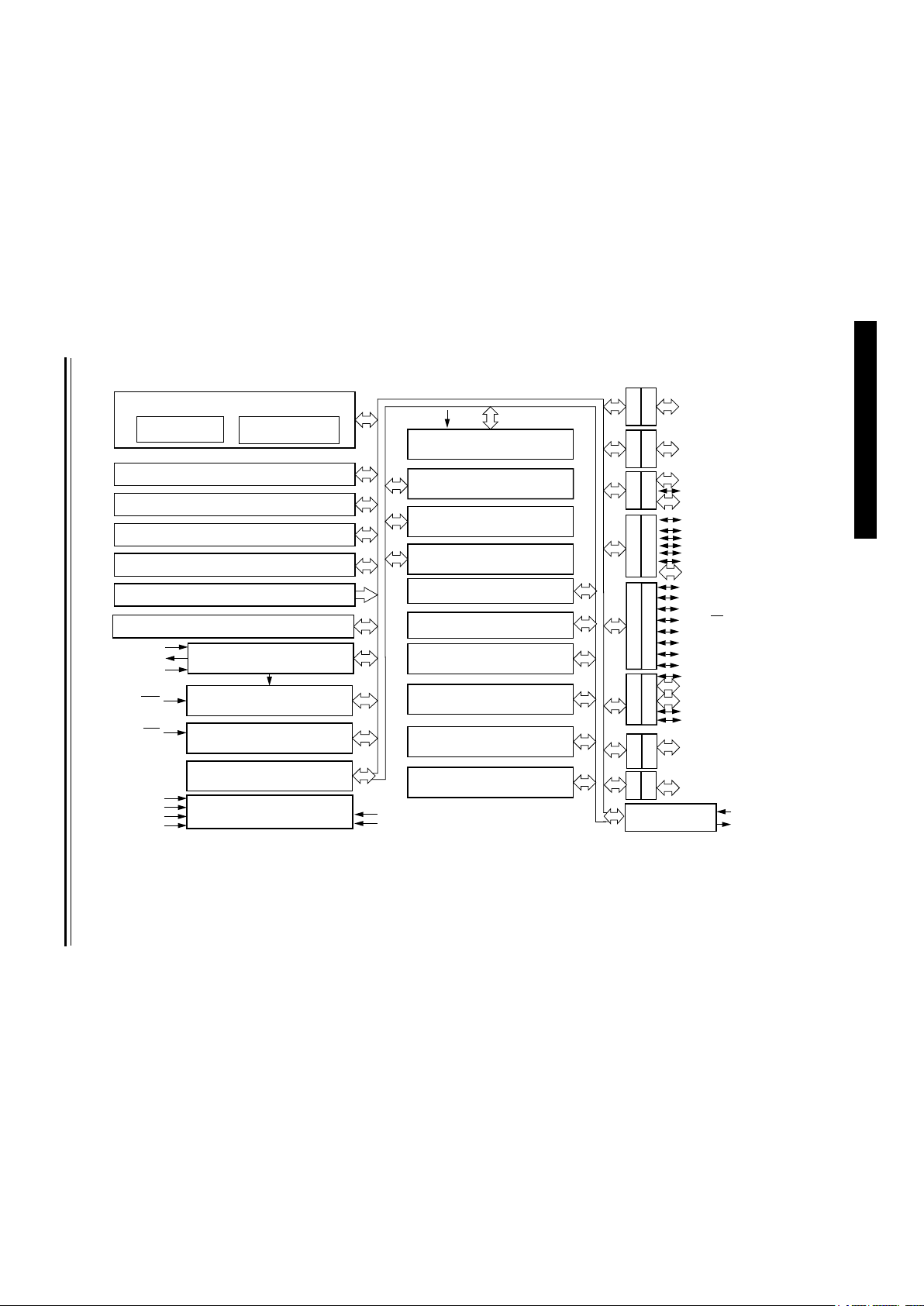

MCU Block Diagram

Figure 1 shows the structure of the MC68HC908AZ60.

3-gen

General Description

MC68HC908AZ60 — Rev 2.0

14 General Description MOTOROLA

BREAK MODULE

CLOCK GENERATOR

MODULE

SYSTEM INTEGRATION

MODULE

ANALOG-TO-DIGITAL

MODULE

SERIAL COMMUNICATIONS

INTERFACE MODULE

SERIAL PERIPHERAL

INTERFACE MODULE

TIMER A 6 CHANNEL

INTERFACE MODULE

LOW-VOLTAGE INHIBIT

MODULE

POWER-ON RESET

MODULE

COMPUTER OPERATING

PROPERLY MODULE

ARITHMETIC/LOGIC

UNIT (ALU)

CPU

REGISTERS

M68HC08 CPU

CONTROL AND STATUS REGISTERS — 62 BYTES

USER FLASH — 60 kBYTES

USER RAM — 2048BYTES

USER EEPROM — 1024 BYTES

MONITOR ROM — 224 BYTES

IRQ MODULE

DDRD

PTD

DDRE

PTE

PTG

DDRG

OSC1

OSC2

CGMXFC

RST

IRQ

V

DD

V

DDA

V

SSA

PTE7/SPSCK

PTE6/MOSI

PTE5/MISO

PTE4/SS

PTE3/TACH1

PTE2/TACH0

PTE1/RxD

PTE0/TxD

PTF5/TBCH1–PTF4/TBCH0

PTF3/TACH5-PTF2/TACH4

PTF

DDRF

PTG2/KBD2–PTG0/KBD0

POWER

PTF1/TACH3

PTF0/TACH2

PTA

DDRA

DDRB

PTB

DDRC

PTC

PTA7–PTA0

PTB7/ATD7–PTB0/ATD0

PTC5–PTC3

PTC2/MCLK

PTC1–PTC0

V

REFH

MSCAN MODULE

TIMER B INTERFACE

MODULE

CANRx

CANTx

PTH

DDRH

PTH1/KBD4–PTH0/KBD3

KEYBOARD INTERRUPT

MODULE

V

SS

USER FLASH VECTOR SPACE — 52 BYTES

PTF6

V

DDAREF

AVSS/V

REFL

Figure 1. MCU Block Diagram for the MC68HC908AZ60 (64-Pin QFP)

PTD1/ATD9–PTD0/ATD8

PTD2/ATD10

PTD6/ATD14/TACLK

PTD5/ATD13

PTD3/ATD11

PTD4/ATD12/TBCLK

PTD7

PROGRAMMABLE INTERRUPT

TIMER (PIT) MODULE

4-gen

General Description

Pin Assignments

MC68HC908AZ60 — Rev 2.0

MOTOROLA General Description 15

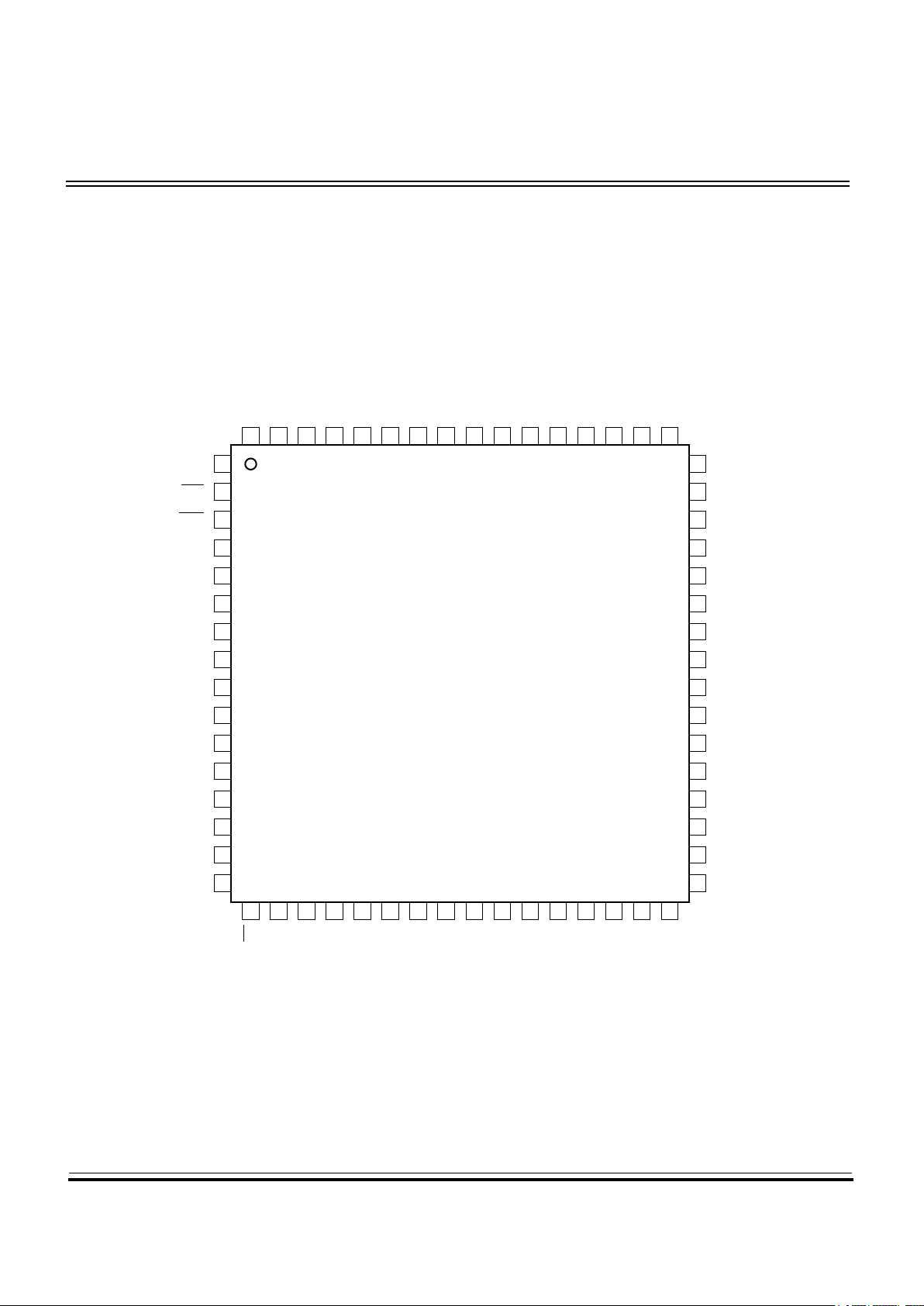

Pin Assignments

Figure 2 shows the MC68HC908AZ60 pin assignments.

Figure 2. MC68HC908AZ60 (64-Pin QFP)

NOTE:

The following pin descriptions are just a quick reference. For a more

detailed representation, see

I/O Ports

on page 305

.

PTF4/TBCH0

CGMXFC

PTB7/ATD7

PTF3/TACH5

PTF2/TACH4

PTF1/TACH3

PTF0/TACH2

RST

IRQ

PTC4

CANRx

CANTx

PTF5/TBCH1

PTE0/TxD

PTE1/RxD

PTE2/TACH0

PTE3/TACH1

PTH0/KBD3

PTD3/ATD11

PTD2/ATD10

AV

SS /VREFL

V

DDAREF

PTD1/ATD9

PTD0/ATD8

PTB6/ATD6

PTB5/ATD5

PTB4/ATD4

PTB3/ATD3

PTB2/ATD2

PTB1/ATD1

PTB0/ATD0

PTA7

V

SSAVDDA

V

REFH

PTD7

PTD6/ATD14/TACLK

PTD5/ATD13

PTD4/ATD12/TBCLK

PTH1/KBD4

PTC5

PTC3

PTC2/MCLK

PTC1

PTC0

OSC1

OSC2

PTE6/MOSI

PTE4/SS

PTE5/MISO

PTE7/SPSCK

V

SS

V

DD

PTG0/KBD0

PTG1/KBD1

PTG2/KBD2

PTA0

PTA1

PTA2

PTA3

PTA4

PTA5

PTA6

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

PTF6

48

49

5-gen

General Description

MC68HC908AZ60 — Rev 2.0

16 General Description MOTOROLA

Power Supply Pins

(V

DD

and V

SS

)

V

DD

and V

SS

are the power supply and ground pins. The MCU operates

from a single power supply.

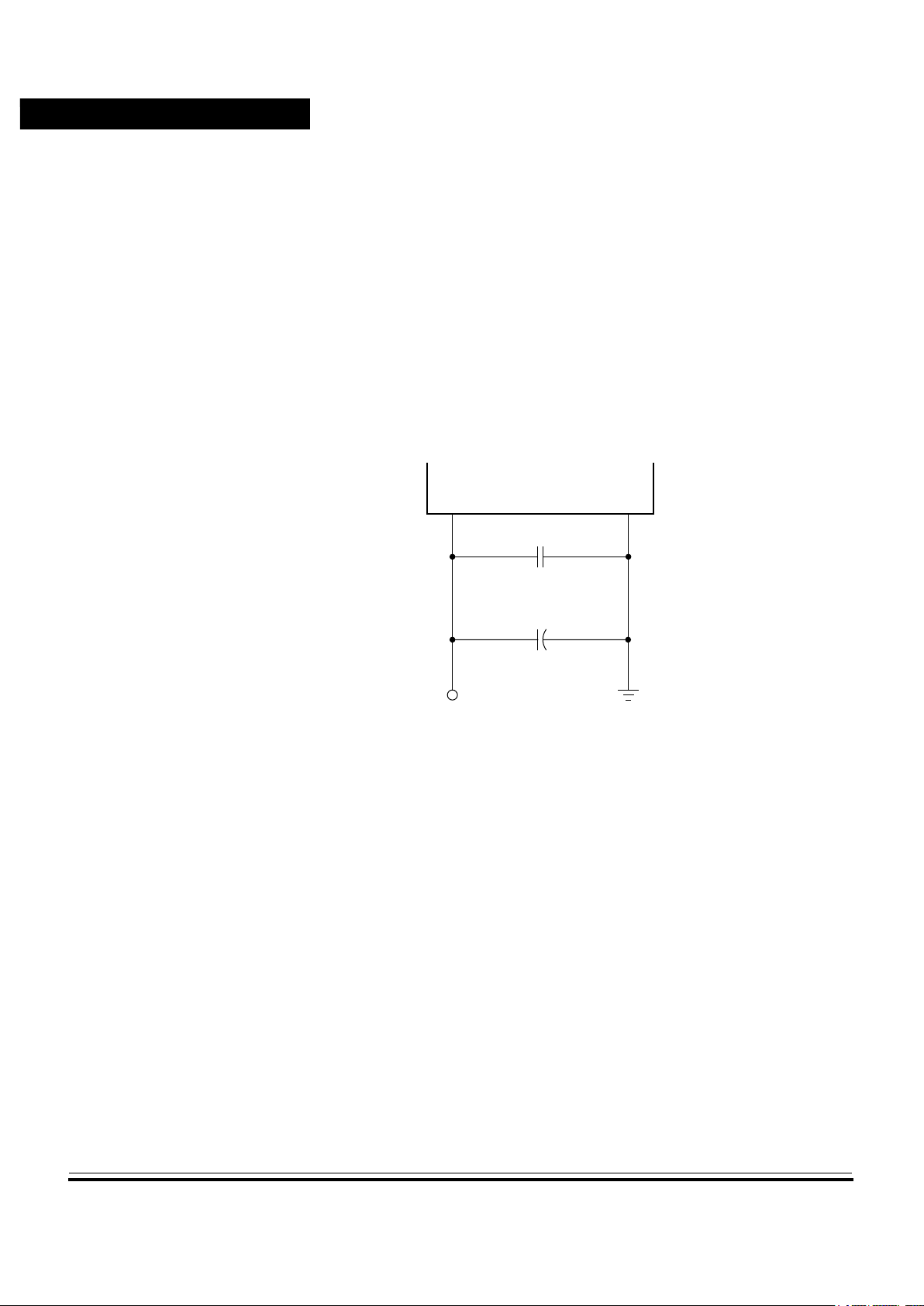

Fast signal transitions on MCU pins place high, short-duration current

demands on the power supply. To prevent noise problems, take special

care to provide power supply bypassing at the MCU as shown in Figure

3 . Place the C1 bypass capacitor as close to the MCU as possible. Use

a high-frequency response ceramic capacitor for C1. C2 is an optional

bulk current bypass capacitor for use in applications that require the port

pins to source high current levels.

V

SS

is also the ground for the port output buffers and the ground return

for the serial clock in the serial peripheral interface module (SPI). See

Serial Peripheral Interface Module (SPI) on page 237.

NOTE:

V

SS

must be grounded for proper MCU operation.

Oscillator Pins

(OSC1 and OSC2)

The OSC1 and OSC2 pins are the connections for the on-chip oscillator

circuit. See Clock Generator Module (CGM) on page 127.

Figure 3. Power supply bypassing

MCU

V

DD

C2

C1

0.1 µF

V

SS

V

DD

+

NOTE: Component values shown represent typical applications.

6-gen

General Description

Pin Assignments

MC68HC908AZ60 — Rev 2.0

MOTOROLA General Description 17

External Reset Pin

(RST

)

A logic 0 on the RST

pin forces the MCU to a known startup state. RST

is bidirectional, allowing a reset of the entire system. It is driven low when

any internal reset source is asserted. See

System Integration Module (SIM) on page 105 for more information.

External Interrupt

Pin (IRQ

)

IRQ

is an asynchronous external interrupt pin. See

External Interrupt Module (IRQ) on page 191.

Analog Power

Supply Pin (V

DDA

)

V

DDA

is the power supply pin for the analog portion of the chip. This pin

will supply the clock generator module (CGM). See

Clock Generator Module (CGM) on page 127.

Analog Ground

Pin (V

SSA

)

The V

SSA

analog ground pin is used only for the ground connections for

the analog sections of the circuit and should be decoupled as per the

V

SS

digital ground pin. The analog sections consist of a clock generator

module (CGM). See Clock Generator Module (CGM) on page 127.

External Filter

Capacitor Pin

(CGMXFC)

CGMXFC is an external filter capacitor connection for the CGM. See

Clock Generator Module (CGM) on page 127

Port A

Input/Output (I/O)

Pins (PTA7

–

PTA0)

PTA7–PTA0 are general-purpose bidirectional I/O port pins. See I/O

Ports on page 305.

Port B I/O Pins

(PTB7/ATD7ÐPTB0/

ATD0)

Port B is an 8-bit special function port that shares all eight pins with the

analog-to-digital converter (ADC). See

Analog-to-Digital Converter (ADC-15) on page 421 and I/O Ports on

page 305.

Port C I/O Pins

(PTC5ÐPTC0)

PTC5–PTC3 and PTC1–PTC0 are general-purpose bidirectional I/O

port pins. PTC2/MCLK is a special function port that shares its pin with

7-gen

General Description

MC68HC908AZ60 — Rev 2.0

18 General Description MOTOROLA

the system clock which has a frequency equivalent to the system clock.

See I/O Ports on page 305.

Port D I/O Pins

(PTD7ÐPTD0/ATD8)

Port D is an 8-bit special-function port that shares seven of its pins with

the analog-to-digital converter module (ADC-15), one of its pins with the

timer interface module (TIMA), and one more of its pins with the timer

interface module (TIMB). See Timer Interface Module A (TIMA-6) on

page 389, Analog-to-Digital Converter (ADC-15) on page 421 and I/O

Ports on page 305.

Port E I/O Pins

(PTE7/SPSCKÐPTE0/

TxD)

Port E is an 8-bit special function port that shares two of its pins with the

timer interface module (TIMA), four of its pins with the serial peripheral

interface module (SPI), and two of its pins with the serial communication

interface module (SCI). See

Serial Communications Interface Module (SCI) on page 199,

Serial Peripheral Interface Module (SPI) on page 237,

Timer Interface Module A (TIMA-6) on page 389, and I/O Ports on

page 305.

Port F I/O Pins

(PTF6ÐPTF0/TACH2)

Port F is a 7-bit special function port that shares its pins with the timer

interface module (TIMB). Six of its pins are shared with the timer

interface module (TIMA-6). See Timer Interface Module A (TIMA-6) on

page 389, Timer Interface Module B (TIMB) on page 269, and I/O

Ports on page 305.

Port G I/O Pins

(PTG2/KBD2ÐPTG0

/KBD0)

Port G is a 3-bit special function port that shares all of its pins with the

keyboard interrupt module (KBD). See Keyboard Module (KBD) on

page 381 and I/O Ports on page 305.

Port H I/O Pins

(PTH1/KBD4ÐPTH0/

KBD3)

Port H is a 2-bit special-function port that shares all of its pins with the

keyboard interrupt module (KBD). See Keyboard Module (KBD) on

page 381 and I/O Ports on page 305.

8-gen

General Description

Pin Assignments

MC68HC908AZ60 — Rev 2.0

MOTOROLA General Description 19

CAN Transmit Pin

(CANTx)

This pin is the digital output from the CAN module (CANTx). See

MSCAN Controller (MSCAN08) on page 331.

CAN Receive Pin

(CANRx)

This pin is the digital input to the CAN module (CANRx). See MSCAN

Controller (MSCAN08) on page 331.

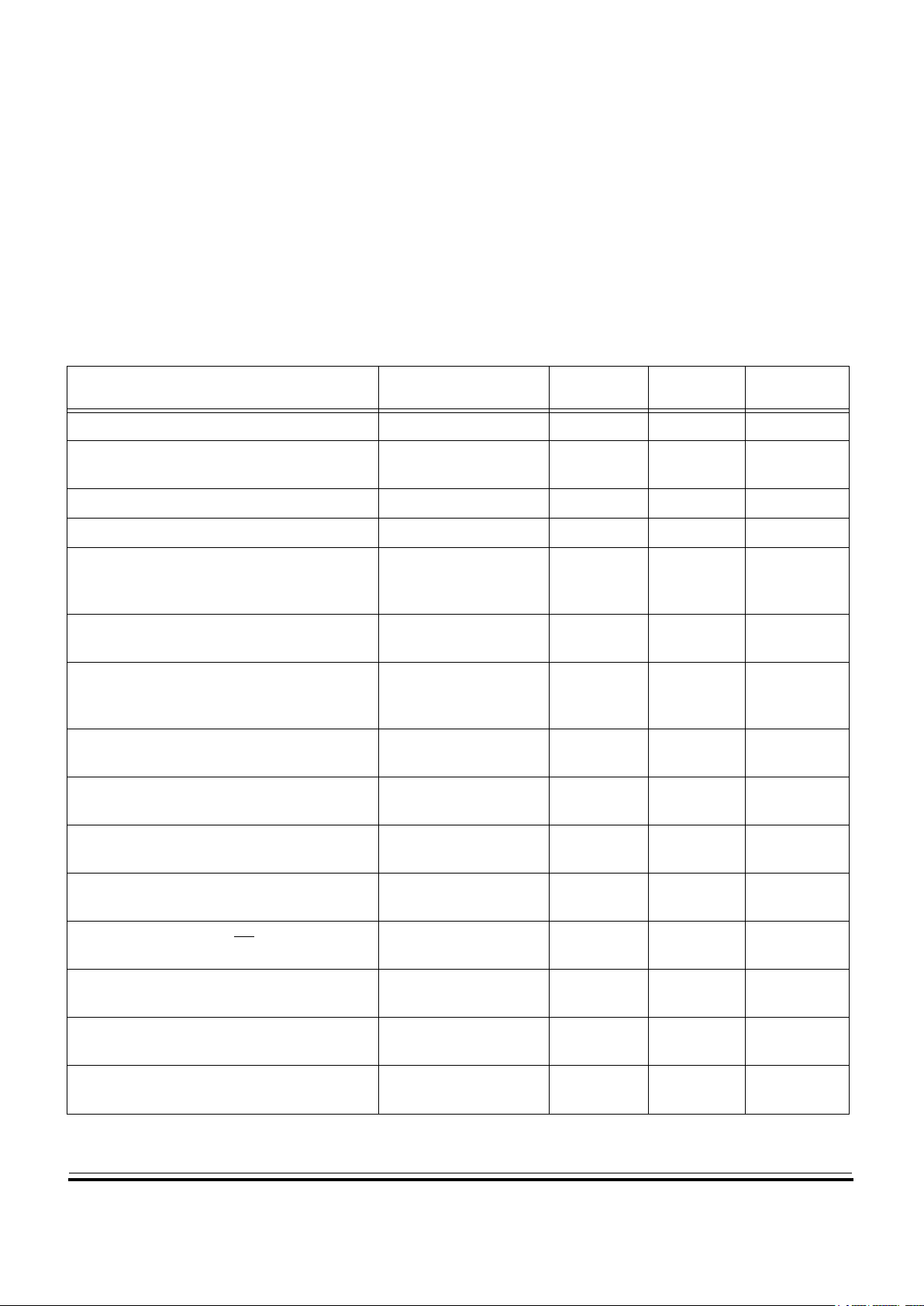

Table 1. External Pins Summary

Pin Name Function

Driver

Type

Hysteresis

(note 1)

Reset State

PTA7–PTA0 General-Purpose I/O Dual State No Input Hi-Z

PTB7/ATD7–PTB0/ATD0

General-Purpose I/O

ADC Channel

Dual State No Input Hi-Z

PTC5–PTC0 General-Purpose I/O Dual State No Input Hi-Z

PTD7 General Purpose I/O/ Dual State No Input Hi-Z

PTD6/ATD14/TACLK ADC Channel

General-Purpose I/O

ADC Channel/Timer

External Input Clock

Dual State No Input Hi-Z

PTD5/ATD13 ADC Channel General-Purpose I/O

ADC Channel

Dual State No Input Hi-Z

PTD4/ATD12/TBCLK ADC Channel

General-Purpose I/O

ADC Channel/Timer

External Input Clock

Dual State No

Input Hi-Z

PTD3/ATD11–PTD0/A TD8 ADC Channels

General-Purpose I/O

ADC Channel

Dual State

No

Input Hi-Z

PTE7/SPSCK

General-Purpose I/O

SPI Clock

Dual State

Open Drain

Yes Input Hi-Z

PTE6/MOSI

General-Purpose I/O

SPI Data Path

Dual State

Open Drain

Yes Input Hi-Z

PTE5/MISO

General-Purpose I/O

SPI Data Path

Dual State

Open Drain

Yes Input Hi-Z

PTE4/SS

General-Purpose I/O

SPI Slave Select

Dual State Yes Input Hi-Z

PTE3/TACH1

General-Purpose I/O

Timer Channel 1

Dual State Yes Input Hi-Z

PTE2/TACH0

General-Purpose I/O

Timer Channel 0

Dual State Yes Input Hi-Z

PTE1/RxD

General-Purpose I/O

SCI Receive Data

Dual State Yes Input Hi-Z

9-gen

General Description

MC68HC908AZ60 — Rev 2.0

20 General Description MOTOROLA

PTE0/TxD

General-Purpose I/O

SCI Transmit Data

Dual State No Input Hi-Z

PTF6 General-Purpose I/O Dual State No Input Hi-Z

PTF5/TBCH1–PTF4/TBCH0

General-Purpose

I/O/Timer B Channel

Dual State Yes Input Hi-Z

PTF3/TACH5

General-Purpose I/O

Timer A Channel 5

Dual State Yes Input Hi-Z

PTF2/TACH4

General-Purpose I/O

Timer A Channel 4

Dual State Yes Input Hi-Z

PTF1/TACH3

General-Purpose I/O

Timer A Channel 3

Dual State Yes Input Hi-Z

PTF0/TACH2

General-Purpose I/O

Timer A Channel 2

Dual State Yes Input Hi-Z

PTG2/KBD2–PTG0/KBD0

General-Purpose I/O/

Keyboard W ak eup Pin

Dual State Yes Input Hi-Z

PTH1/KBD4 –PTH0/KBD3

General-Purpose I/O/

Keyboard W ak eup Pin

Dual State Yes Input Hi-Z

V

DD

Chip Power Supply N/A N/A N/A

V

SS

Chip Ground N/A N/A N/A

V

DDAREF

ADC Power Supply/

ADC Reference

Voltage

N/A N/A N/A

A

VSS/VREFL

ADC Ground/ADC

Reference V oltage

N/A N/A N/A

V

REFH

A/D Reference

Voltage

N/A N/A N/A

OSC1 External Clock In N/A N/A Input Hi-Z

OSC2 External Clock Out N/A N/A Output

CGMXFC PLL Loop Filter Cap N/A N/A N/A

IRQ

External Interrupt

Request

N/A N/A Input Hi-Z

RST Reset N/A N/A Output Low

CANRx CAN Serial Input N/A Yes Input Hi-Z

CANTx CAN Serial Output Output No Output

Table 1. External Pins Summary (Continued)

Pin Name Function

Driver

Type

Hysteresis

(note 1)

Reset State

10-gen

General Description

Pin Assignments

MC68HC908AZ60 — Rev 2.0

MOTOROLA General Description 21

Note 1: Hysteresis is not 100% tested but is typically a minimum of

300mV

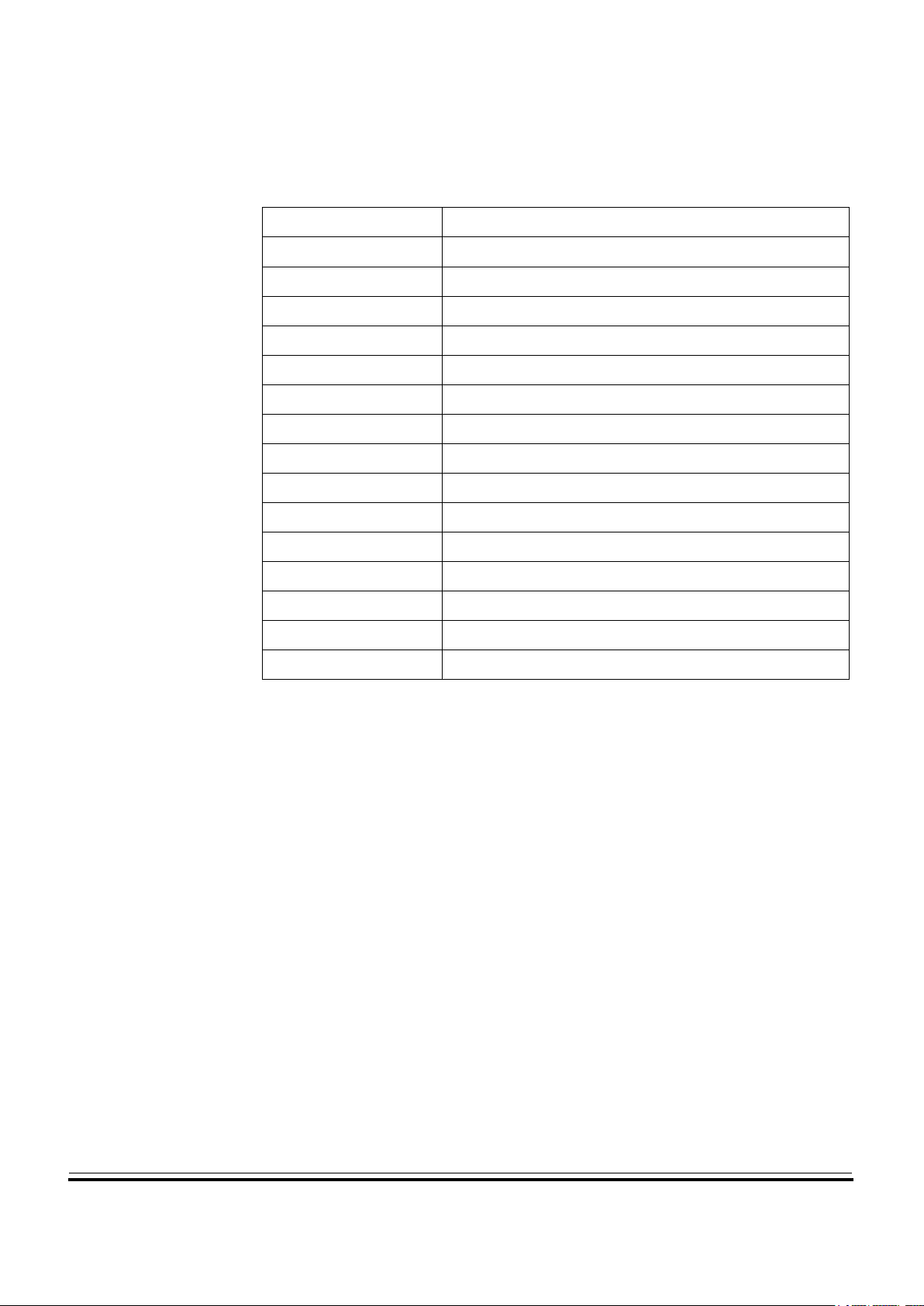

Table 2. Clock Source Summary

Module Clock Source

ADC CGMXCLK or Bus Clock

CAN CGMXCLK or CGMOUT

COP CGMXCLK

CPU Bus Clock

EEPROM RC OSC or Bus Clock

SPI Bus Clock/SPSCK

SCI CGMXCLK

TIMA-6 Bus Clock or PTD6/ATD14/TACLK

TIMB Bus Clock or PTD4/TBCLK

PIT Bus Clock

SIM CGMOUT and CGMXCLK

IRQ Bus Clock

BRK Bus Clock

LVI Bus Clock

CGM OSC1 and OSC2

11-gen

General Description

MC68HC908AZ60 — Rev 2.0

22 General Description MOTOROLA

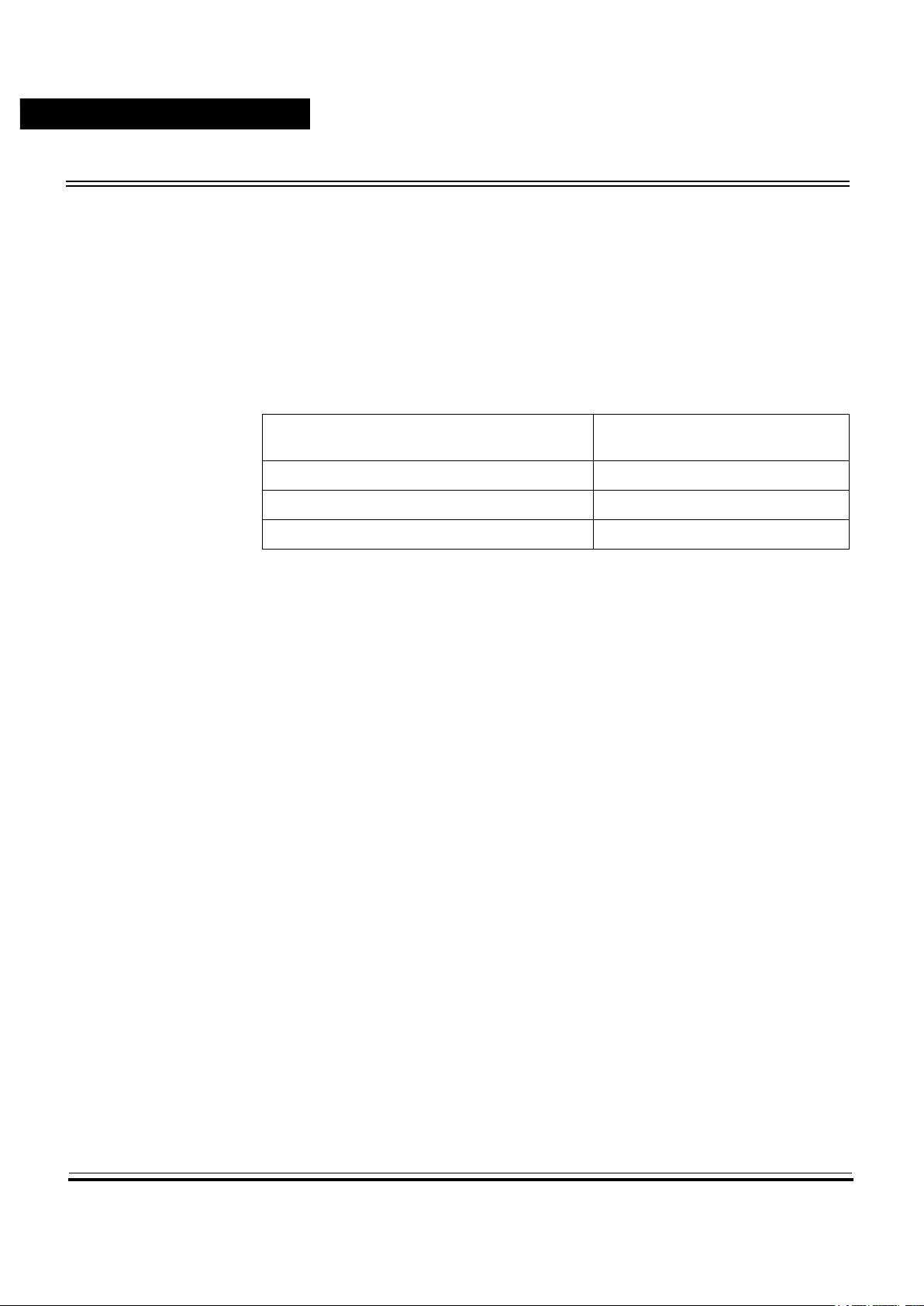

Ordering Information

This section contains instructions for ordering the MC68HC908AZ60.

MC Order

Numbers

Table 3. MC Order Numbers

MC Order Number

Operating

Temperature Range

MC68HC908AZ60CFU –40 °C to + 85°C

MC68HC908AZ60VFU –40

°C to + 105 °C

MC68HC908AZ60MFU –40 °C to + 125 °C

12-gen

MC68HC908AZ60 — Rev 2.0

MOTOROLA Memory Map 23

Memory Map

Memory Map

Contents

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

I/O Section . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

Introduction

The CPU08 can address 64 Kbytes of memory space. The memory

map, shown in Figure 1, includes:

• 60 Kbytes of FLASH EEPROM

• 2048 Bytes of RAM

• 1024 Bytes of EEPROM with Protect Option

• 52 Bytes of User-Defined Vectors

• 224 Bytes of Monitor ROM

The following definitions apply to the memory map representation of

reserved and unimplemented locations.

• Reserved — Accessing a reserved location can have

unpredictable effects on MCU operation.

• Unimplemented — Accessing an unimplemented location

causes an illegal address reset if illegal address resets are

enabled.

1-mem

Memory Map

MC68HC908AZ60 — Rev 2.0

24 Memory Map MOTOROLA

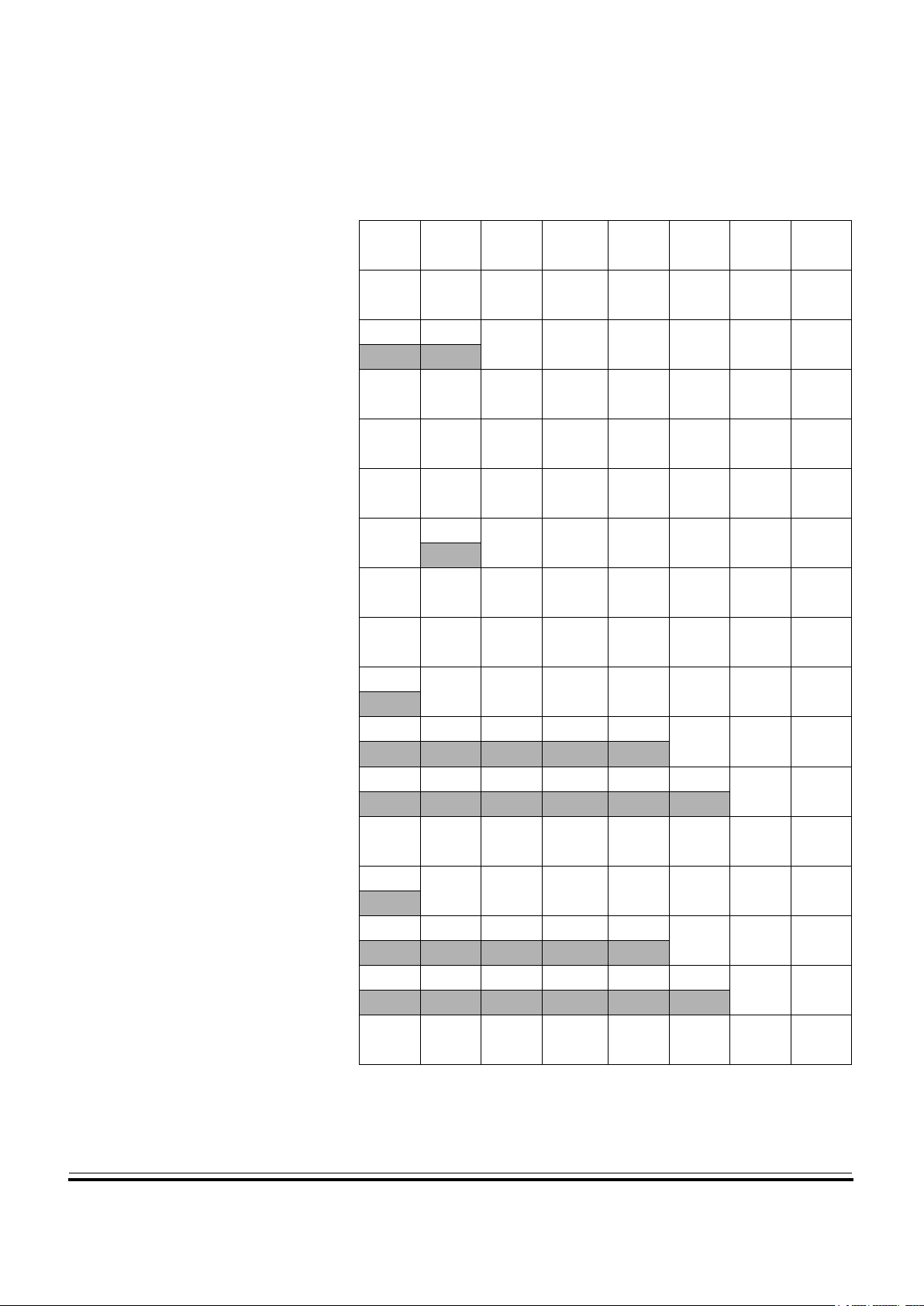

Figure 1. Memory Map

$0000

I/O REGISTERS (64 BYTES)

$0000

↓↓

$003F $003F

$0040

I/O REGISTERS, 16 BYTES

$0040

↓↓

$004F $004F

$0050

RAM-1, 1024 BYTES

$0050

↓↓

$044F $044F

$0450

FLASH-2, 176 BYTES

$0450

↓↓

$04FF $04FF

$0500

CAN CONTROL AND MESSAGE

BUFFERS, 128 BYTES

$0500

↓↓

$057F $057F

$0580

FLASH-2, 128 BYTES

$0580

↓↓

$05FF $05FF

$0600

EEPROM-2, 512 BYTES

$0600

↓↓

$07FF $07FF

$0800

EEPROM-1, 512 BYTES

$0800

↓↓

$09FF $09FF

$0A00

RAM-2 , 1024 BYTES

$0A00

↓↓

$0DFF $0DFF

$0E00

FLASH-2, 29,184 BYTES

$0E00

↓↓

$7FFF $7FFF

$8000

FLASH-1, 32,256BYTES

$8000

↓↓

$FDFF $FDFF

$FE00 SIM BREAK STATUS REGISTER (SBSR) $FE00

$FE01 SIM RESET STATUS REGISTER (SRSR) $FE01

$FE02 RESERVED $FE02

$FE03 SIM BREAK FLAG CONTROL REGISTER (SBFCR) $FE03

2-mem

Memory Map

Introduction

MC68HC908AZ60 — Rev 2.0

MOTOROLA Memory Map 25

$FE04 RESERVED $FE04

$FE05 RESERVED $FE05

$FE06 UNIMPLEMENTED $FE06

$FE07 RESERVED $FE07

$FE08 RESERVED $FE08

$FE09

CONFIGURA TION WRITE-ONCE REGISER

(CONFIG-2)

$FE09

$FE0A RESER VED $FE0A

$FE0B FLASH CONTROL REGISTER (FLCR1) $FE0B

$FE0C BREAK ADDRESS REGISTER HIGH (BRKH) $FE0C

$FE0D BREAK ADDRESS REGISTER LOW (BRKL) $FE0D

$FE0E BREAK STATUS AND CONTROL REGISTER (BSCR) $FE0E

$FE0F LVI STATUS REGISTER (LVISR) $FE0F

$FE10 RESERVED $FE10

$FE11 FLASH CONTROL REGISTER (FLCR2) $FE11

$FE12

UNIMPLEMENTED (5BYTES)

$FE12

↓↓

$FE17 $FE17

$FE18 EEPROM NON-VOLATILE REGISTER (EENVR2) $FE18

$FE19 EEPROM CONTROL REGISTER (EECR2) $FE19

$FE1A RESERVED $FE1A

$FE1B EEPROM ARRAY CONFIGURATION (EEACR2) $FE1B

$FE1C EEPROM NON-VOLATILE REGISTER (EENVR1) $FE1C

$FE1D EEPROM CONTROL REGISTER (EECR1) $FE1D

$FE1E RESERVED $FE1E

$FE1F EEPROM ARRAY CONFIGURATION (EEACR1) $FE1F

$FE20

MONITOR ROM (224 BYTES)

$FE20

↓↓

$FEFF $FEFF

$FF00

↓

$FF7F

UNIMPLEMENTED (128 BYTES)

$FF00

↓

$FF7F

$FF80 FLASH BLOCK PROTECT REGISTER (FLBPR1) $FF80

$FF81 FLASH BLOCK PROTECT REGISTER (FLBPR2) $FF81

$FF82

RESERVED (75 BYTES)

$FF82

↓↓

$FFCB $FFCB

Figure 1. Memory Map (Continued)

3-mem

Memory Map

MC68HC908AZ60 — Rev 2.0

26 Memory Map MOTOROLA

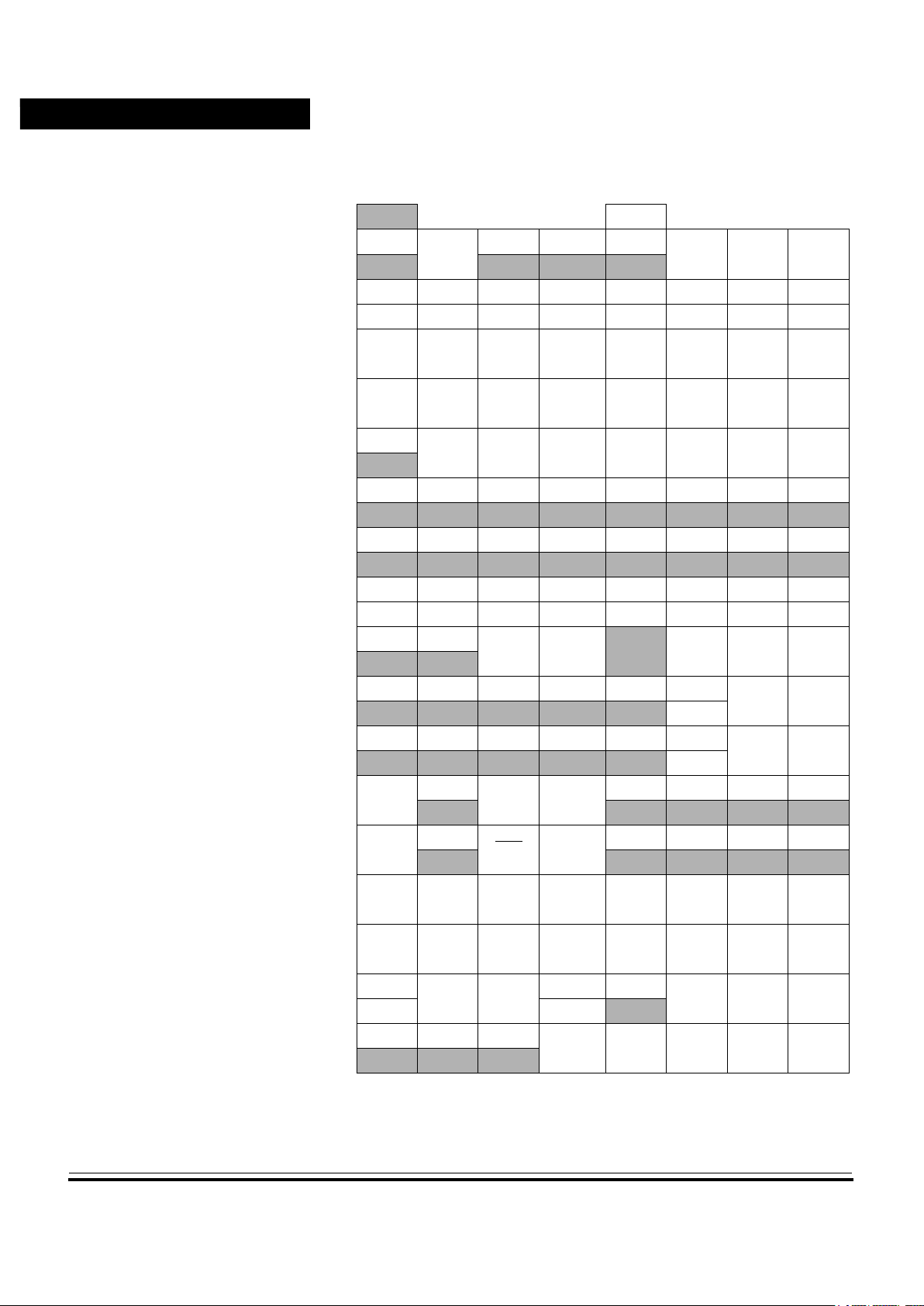

I/O Section

Addresses $0000–$003F, shown in Figure 2, contain most of the

control, status, and data registers. Additional I/O registers have these

addresses:

• $FE00 (SIM break status register, SBSR)

• $FE01 (SIM reset status register, SRSR)

• $FE03 (SIM break flag control register, SBFCR)

• $FE09 (configuration write-once register, CONFIG-2)

• $FE0B (FLASH control register, FLCR1)

• $FE0C and $FE0D (break address registers, BRKH and BRKL)

• $FE0E (break status and control register, BRKSCR)

• $FE0F (LVI status register, LVISR)

• $FE11 (FLASH control register, FLCR2)

• $FE18 (EEPROM non-volatile register, EENVR2)

• $FE19 (EEPROM control register, EECR2)

• $FE1B (EEPROM array configuration register, EEACR2)

• $FE1C (EEPROM non-volatile register, EENVR1)

• $FE1D (EEPROM control register, EECR1)

• $FE1F (EEPROM array configuration register, EEACR1)

• $FF80 (FLASH block protect register, FLBPR1)

• $FF81 (FLASH block protect register, FLBPR2)

• $FFFF (COP control register, COPCTL)

Table 1 is a list of vector locations.

$FFCC

VECTORS (52BYTES)

$FFCC

↓↓

$FFFF $FFFF

Figure 1. Memory Map (Continued)

4-mem

Memory Map

I/O Section

MC68HC908AZ60 — Rev 2.0

MOTOROLA Memory Map 27

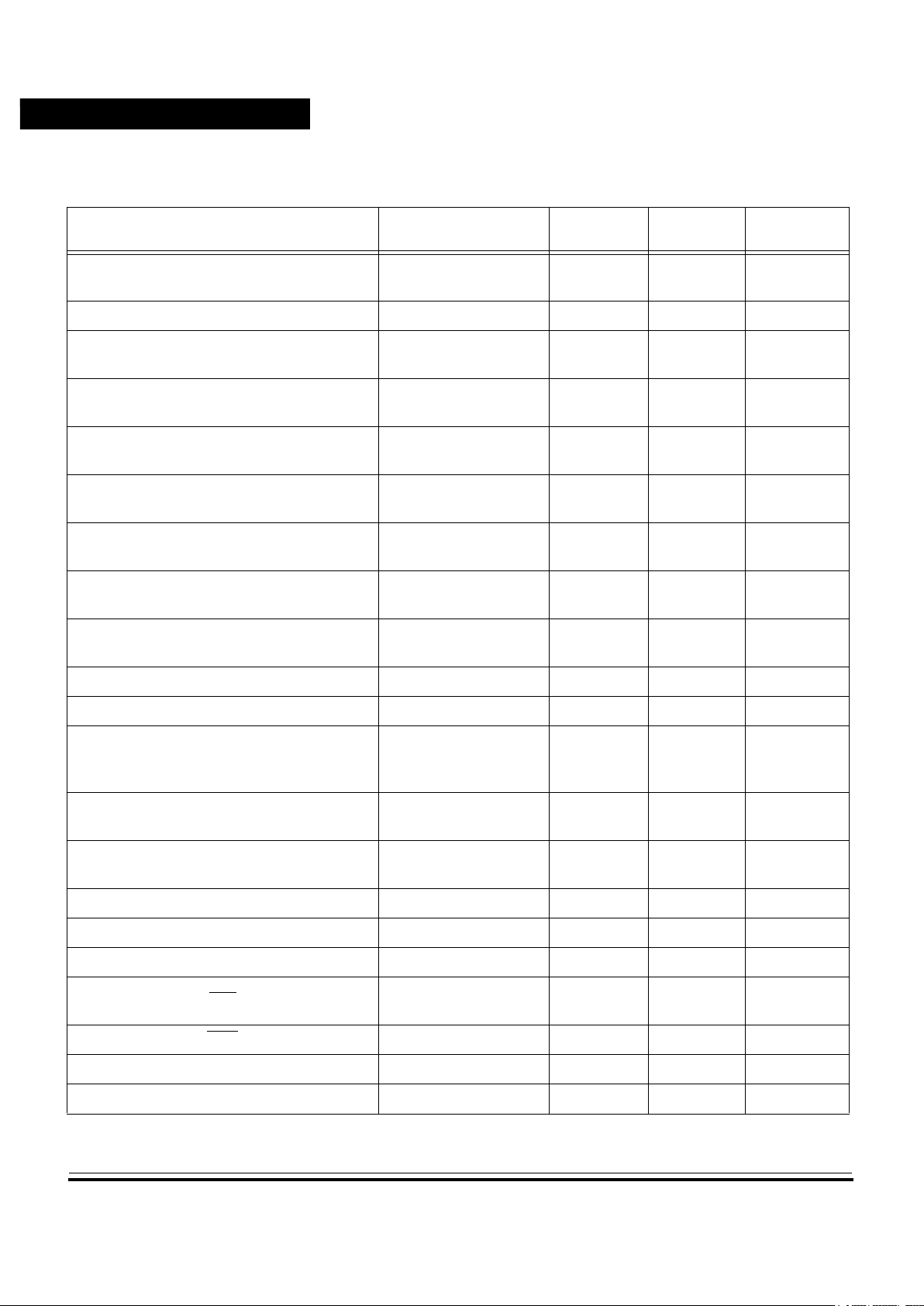

Addr. Register Name Bit 7 6 5 4 3 2 1 Bit 0

$0000 Port A Data Register (PTA)

Read:

PTA7 PTA6 PTA5 PTA4 PTA3 PTA2 PTA1 PTA0

Write:

$0001 Port B Data Register (PTB)

Read:

PTB7 PTB6 PTB5 PTB4 PTB3 PTB2 PTB1 PTB0

Write:

$0002 Port C Data Register (PTC)

Read: 0 0

PTC5 PTC4 PTC3 PTC2 PTC1 PTC0

Write:

$0003 Port D Data Register (PTD)

Read:

PTD7 PTD6 PTD5 PTD4 PTD3 PTD2 PTD1 PTD0

Write:

$0004

Data Direction Register A

(DDRA)

Read:

DDRA7 DDRA6 DDRA5 DDRA4 DDRA3 DDRA2 DDRA1 DDRA0

Write:

$0005

Data Direction Register B

(DDRB)

Read:

DDRB7 DDRB6 DDRB5 DDRB4 DDRB3 DDRB2 DDRB1 DDRB0

Write:

$0006

Data Direction Register C

(DDRC)

Read:

MCLKEN

0

DDRC5 DDRC4 DDRC3 DDRC2 DDRC1 DDRC0

Write:

$0007

Data Direction Register D

(DDRD)

Read:

DDRD7 DDRD6 DDRD5 DDRD4 DDRD3 DDR2 DDRD1 DDRD0

Write:

$0008 Port E Data Register (PTE)

Read:

PTE7 PTE6 PTE5 PTE4 PTE3 PTE2 PTE1 PTE0

Write:

$0009 Port F Data Register (PTF)

Read: 0

PTF6 PTF5 PTF4 PTF3 PTF2 PTF1 PTF0

Write:

$000A Port G Data Register (PTG)

Read: 0 0 0 0 0

PTG2 PTG1 PTG0

Write:

$000B Port H Data Register (PTH)

Read: 0 0 0 0 0 0

PTH1 PTH0

Write:

$000C

Data Direction Register E

(DDRE)

Read:

DDRE7 DDRE6 DDRE5 DDRE4 DDRE3 DDRE2 DDRE1 DDRE0

Write:

$000D

Data Direction Register F

(DDRF)

Read: 0

DDRF6 DDRF5 DDRF4 DDRF3 DDRF2 DDRF1 DDRF0

Write:

$000E

Data Direction Register G

(DDRG)

Read: 0 0 0 0 0

DDRG2 DDRG1 DDRG0

Write:

$000F

Data Direction Register H

(DDRH)

Read: 0 0 0 0 0 0

DDRH1 DDRH0

Write:

$0010 SPI Control Register (SPCR)

Read:

SPRIE R SPMSTR CPOL CPHA SPWOM SPE SPTIE

Write:

Figure 2. Control, Status, and Data Registers (Sheet 1 of 6)

5-mem

Memory Map

MC68HC908AZ60 — Rev 2.0

28 Memory Map MOTOROLA

= Unimplemented R = Reserved

$0011

SPI Status and Control

Register (SPSCR)

Read: SPRF

ERRIE

OVRF MODF SPTE

MODFE

N

SPR1 SPR0

Write:

$0012 SPI Data Register (SPDR)

Read: R7 R6 R5 R4 R3 R2 R1 R0

Write: T7 T6 T5 T4 T3 T2 T1 T0

$0013 SCI Control Register 1 (SCC1)

Read:

LOOPS ENSCI TXINV M WAKE ILTY PEN PTY

Write:

$0014 SCI Control Register 2 (SCC2)

Read:

SCTIE TCIE SCRIE ILIE TE RE RWU SBK

Write:

$0015 SCI Control Register 3 (SCC3)

Read: R8

T8 R R ORIE NEIE FEIE PEIE

Write:

$0016 SCI Status Register 1 (SCS1)

Read: SCTE TC SCRF IDLE OR NF FE PE

Write:

$0017 SCI Status Register 2 (SCS2)

Read: 0 0 0 0 0 0 BKF RPF

Write:

$0018 SCI Data Register (SCDR)

Read: R7 R6 R5 R4 R3 R2 R1 R0

Write: T7 T6 T5 T4 T3 T2 T1 T0

$0019 SCI Baud Rate Register (SCBR)

Read: 0 0

SCP1 SCP0 SCR2 SCR1 SCR0

Write:

$001A

IRQ Status and Control

Register (ISCR)

Read: 0 0 0 0 IRQF 0

IMASK1 MODE1

Write: ACK1

$001B

Keyboard Status and Control

Register (KBSCR)

Read: 0 0 0 0 KEYF 0

IMASKK MODEK

Write: ACKK

$001C PLL Control Register (PCTL)

Read:

PLLIE

PLLF

PLLON BCS

1111

Write:

$001D

PLL Bandwidth Control

Register (PBWC)

Read:

AUTO

LOCK

ACQ XLD

0000

Write:

$001E

PLL Programming Register

(PPG)

Read:

MUL7 MUL6 MUL5 MUL4 VRS7 VRS6 VRS5 VRS4

Write:

$001F

Configuration Write-Once

Register (CONFIG-1)

Read:

LVISTOP R LVIRST LVIPWR SSREC COPL STOP COPD

Write:

$0020

Timer A Status and Control

Register (TASC)

Read: TOF

TOIE TSTOP

00

PS2 PS1 PS0

Write: 0 TRST

$0021

Keyboard Interrupt Enable Register

(KBIE)

Read: 0 0 0

KBIE4 KBIE3 KBIE2 KBIE1 KBIE0

Write:

Addr. Register Name Bit 7 6 5 4 3 2 1 Bit 0

Figure 2. Control, Status, and Data Registers (Sheet 2 of 6)

6-mem

Loading...

Loading...