Motorola MC14538BCP, MC14538BDW, MC14538BCL Datasheet

MOTOROLA CMOS LOGIC DATA

1

MC14538B

The MC14538B is a dual, retriggerable, resettable monostable multivibrator. It may be triggered from either edge of an input pulse, and produces an

accurate output pulse over a wide range of widths, the duration and accuracy

of which are determined by the external timing components, CX and RX.

• Unlimited Rise and Fall Time Allowed on the A Trigger Input

• Pulse Width Range = 10 µs to 10 s

• Latched Trigger Inputs

• Separate Latched Reset Inputs

• 3.0 Vdc to 18 Vdc Operational Limits

• Triggerable from Positive (A Input) or Negative–Going Edge (B–Input)

• Capable of Driving Two Low–power TTL Loads or One Low–power

Schottky TTL Load Over the Rated Temperature Range

• Pin–for–pin Compatible with MC14528B and CD4528B (CD4098)

• Use the MC54/74HC4538A for Pulse Widths Less Than 10 µs with

Supplies Up to 6 V.

MAXIMUM RATINGS* (Voltages Referenced to V

SS

)

Symbol

Parameter

Value

Unit

V

DD

DC Supply Voltage

– 0.5 to + 18.0

V

Vin, V

out

Input or Output Voltage (DC or Transient)

– 0.5 to VDD + 0.5

V

Iin, I

out

Input or Output Current (DC or Transient),

per Pin

± 10

mA

P

D

Power Dissipation, per Package†

500

mW

T

stg

Storage Temperature

– 65 to + 150

_

C

T

L

Lead Temperature (8–Second Soldering)

260

_

C

*Maximum Ratings are those values beyond which damage to the device may occur.

†Temperature Derating:

Plastic “P and D/DW” Packages: – 7.0 mW/_C From 65_C To 125_C

Ceramic “L” Packages: – 12 mW/_C From 100_C To 125_C

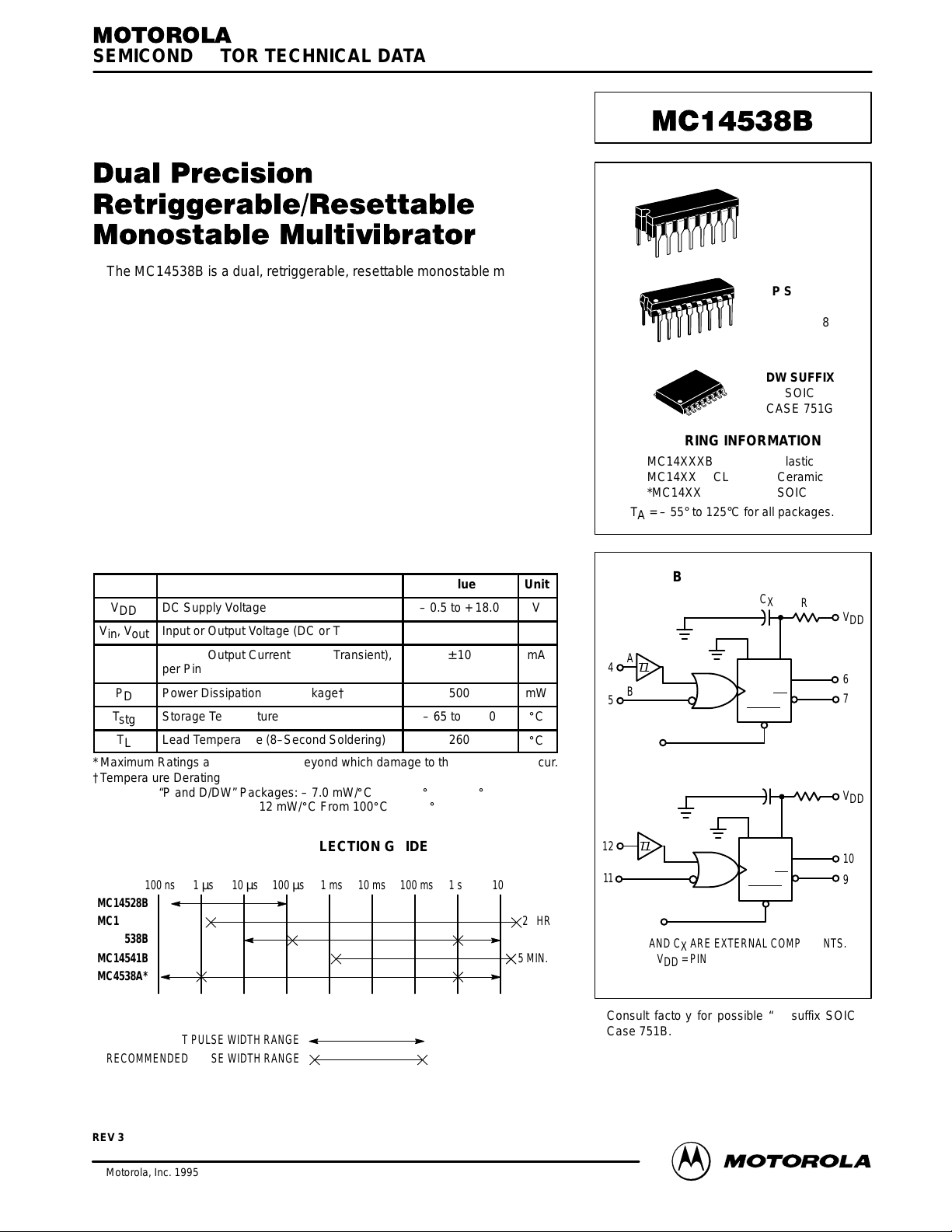

ONE–SHOT SELECTION GUIDE

100 ns

MC14528B

MC14536B

MC14538B

MC14541B

MC4538A*

1 µs 10 µs 100 µs 1 ms 10 ms 100 ms 1 s 10 s

*LIMITED OPERATING VOLTAGE (2 – 6 V)

TOTAL OUTPUT PULSE WIDTH RANGE

RECOMMENDED PULSE WIDTH RANGE

23 HR

5 MIN.

SEMICONDUCTOR TECHNICAL DATA

Motorola, Inc. 1995

REV 3

1/94

L SUFFIX

CERAMIC

CASE 620

ORDERING INFORMATION

MC14XXXBCP Plastic

MC14XXXBCL Ceramic

*MC14XXXBDW SOIC

TA = – 55° to 125°C for all packages.

P SUFFIX

PLASTIC

CASE 648

DW SUFFIX

SOIC

CASE 751G

BLOCK DIAGRAM

*Consult factory for possible “D” suffix SOIC

Case 751B.

V

DD

V

DD

6

7

10

9

12

11

5

4

A

B

C

X

R

X

1 2

Q1

Q1

RESET

3

C

X

R

X

15 14

Q2

Q2

RESET

13

A

B

RX AND CX ARE EXTERNAL COMPONENTS.

VDD = PIN 16

VSS = PIN 8, PIN 1, PIN 15

MOTOROLA CMOS LOGIC DATAMC14538B

2

ELECTRICAL CHARACTERISTICS (Voltages Referenced to V

SS

)

V

DD

– 55_C 25_C 125_C

Characteristic

Symbol

DD

Vdc

Min Max Min Typ # Max Min Max

Unit

Output Voltage “0” Level

Vin = VDD or 0

V

OL

5.0

10

15

—

—

—

0.05

0.05

0.05

—

—

—

0

0

0

0.05

0.05

0.05

—

—

—

0.05

0.05

0.05

Vdc

“1” Level

Vin = 0 or V

DD

V

OH

5.0

10

15

4.95

9.95

14.95

—

—

—

4.95

9.95

14.95

5.0

10

15

—

—

—

4.95

9.95

14.95

—

—

—

Vdc

Input Voltage “0” Level

(VO = 4.5 or 0.5 Vdc)

(VO = 9.0 or 1.0 Vdc)

(VO = 13.5 or 1.5 Vdc)

V

IL

5.0

10

15

—

—

—

1.5

3.0

4.0

—

—

—

2.25

4.50

6.75

1.5

3.0

4.0

—

—

—

1.5

3.0

4.0

Vdc

“1” Level

(VO = 0.5 or 4.5 Vdc)

(VO = 1.0 or 9.0 Vdc)

(VO = 1.5 or 13.5 Vdc)

V

IH

5.0

10

15

3.5

7.0

11

—

—

—

3.5

7.0

11

2.75

5.50

8.25

—

—

—

3.5

7.0

11

—

—

—

Vdc

Output Drive Current

(VOH = 2.5 Vdc) Source

(VOH = 4.6 Vdc)

(VOH = 9.5 Vdc)

(VOH = 13.5 Vdc)

I

OH

5.0

5.0

10

15

– 3.0

– 0.64

– 1.6

– 4.2

—

—

—

—

– 2.4

– 0.51

– 1.3

– 3.4

– 4.2

– 0.88

– 2.25

– 8.8

—

—

—

—

– 1.7

– 0.36

– 0.9

– 2.4

—

—

—

—

mAdc

(VOL = 0.4 Vdc) Sink

(VOL = 0.5 Vdc)

(VOL = 1.5 Vdc)

I

OL

5.0

10

15

0.64

1.6

4.2

—

—

—

0.51

1.3

3.4

0.88

2.25

8.8

—

—

—

0.36

0.9

2.4

—

—

—

mAdc

Input Current, Pin 2 or 14 I

in

15 — ±0.05 — ±0.00001 ±0.05 — ±0.5 µAdc

Input Current, Other Inputs I

in

15 — ±0.1 — ±0.00001 ±0.1 — ±1.0 µAdc

Input Capacitance, Pin 2 or 14 C

in

— — — — 25 — — — pF

Input Capacitance, Other Inputs

(Vin = 0)

C

in

— — — — 5.0 7.5 — — pF

Quiescent Current

(Per Package)

Q = Low, Q = High

I

DD

5.0

10

15

—

—

—

5.0

10

20

—

—

—

0.005

0.010

0.015

5.0

10

20

—

—

—

150

300

600

µAdc

Quiescent Current, Active State

(Both) (Per Package)

Q = High, Q = Low

I

DD

5.0

10

15

—

—

—

2.0

2.0

2.0

—

—

—

0.04

0.08

0.13

0.20

0.45

0.70

—

—

—

2.0

2.0

2.0

mAdc

**Total Supply Current at an

external load capacitance (CL) and

at external timing network (RX, CX)

I

T

5.0

10

IT = (3.5 x 10–2) RXCXf + 4CXf + 1 x 10–5 CLf

IT = (8.0 x 10–2) RXCXf + 9CXf + 2 x 10–5 CLf

IT = (1.25 x 10–1) RXCXf + 12CXf + 3 x 10–5 CLf

where: IT in µA (one monostable switching only),

where: CX in µF, CL in pF, RX in k ohms, and

where: f in Hz is the input frequency.

µAdc

#Data labelled “Typ” is not to be used for design purposes but is intended as an indication of the IC’s potential performance.

**The formulas given are for the typical characteristics only at 25_C.

This device contains protection circuitry to guard against damage due to high static voltages or electric fields. However,

precautions must be taken to avoid applications of any voltage higher than maximum rated voltages to this high-impedance

circuit. For proper operation, Vin and V

out

should be constrained to the range VSS ≤ (Vin or V

out

) ≤ VDD.

Unused inputs must always be tied to an appropriate logic voltage level (e.g., either VSS or VDD). Unused outputs must

be left open.

MOTOROLA CMOS LOGIC DATA

3

MC14538B

SWITCHING CHARACTERISTICS* (C

L

= 50 pF, TA = 25_C)

V

All Types

Characteristic

Symbol

V

DD

Vdc

Min Typ # Max

Unit

Output Rise Time

t

TLH

= (1.35 ns/pF) CL + 33 ns

t

TLH

= (0.60 ns/pF) CL + 20 ns

t

TLH

= (0.40 ns/pF) CL + 20 ns

t

TLH

5.0

10

15

—

—

—

100

50

40

200

100

80

ns

Output Fall Time

t

THL

= (1.35 ns/pF) CL + 33 ns

t

THL

= (0.60 ns/pF) CL + 20 ns

t

THL

= (0.40 ns/pF) CL + 20 ns

t

THL

5.0

10

15

—

—

—

100

50

40

200

100

80

ns

Propagation Delay Time

A or B to Q or Q

t

PLH

, t

PHL

= (0.90 ns/pF) CL + 255 ns

t

PLH

, t

PHL

= (0.36 ns/pF) CL + 132 ns

t

PLH

, t

PHL

= (0.26 ns/pF) CL + 87 ns

5.0

10

15

—

—

—

300

150

100

600

300

220

ns

Reset to Q or Q

t

PLH

, t

PHL

= (0.90 ns/pF) CL + 205 ns

t

PLH

, t

PHL

= (0.36 ns/pF) CL + 107 ns

t

PLH

, t

PHL

= (0.26 ns/pF) CL + 82 ns

5.0

10

15

—

—

—

250

125

95

500

250

190

ns

Input Rise and Fall Times

Reset

5

10

15

—

—

—

—

—

—

15

5

4

µs

B Input 5

10

15

—

—

—

300

1.2

0.4

1.0

0.1

0.05

ms

A Input 5

10

15

No Limit

—

Input Pulse Width

A, B, or Reset

tWH,

t

WL

5.0

10

15

170

90

80

85

45

40

—

—

—

ns

Retrigger Time t

rr

5.0

10

15

0

0

0

—

—

—

—

—

—

ns

Output Pulse Width — Q or Q

Refer to Figures 8 and 9

CX = 0.002 µF, RX = 100 kΩ

5.0

10

15

198

200

202

210

212

214

230

232

234

µs

CX = 0.1 µF, RX = 100 kΩ 5.0

10

15

9.3

9.4

9.5

9.86

10

10.14

10.5

10.6

10.7

ms

CX = 10 µF, RX = 100 kΩ 5.0

10

15

0.91

0.92

0.93

0.965

0.98

0.99

1.03

1.04

1.06

s

Pulse Width Match between circuits in

the same package.

CX = 0.1 µF, RX = 100 kΩ

100

[(T1 – T2)/T1]

5.0

10

15

—

—

—

± 1.0

± 1.0

± 1.0

± 5.0

± 5.0

± 5.0

%

*The formulas given are for the typical characteristics only at 25_C.

#Data labelled “Typ” is not to be used for design purposes but is intended as an indication of the IC’s potential performance.

OPERATING CONDITIONS

External Timing Resistance R

X

— 5.0 — kΩ

External Timing Capacitance C

X

— 0 — No

Limit†

µF

*The maximum usable resistance RX is a function of the leakage of the capacitor CX, leakage of the MC14538B, and leakage due to board layout

and surface resistance. Susceptibility to externally induced noise signals may occur for RX > 1 MΩ..

†If CX > 15 µF, use discharge protection diode per Fig. 11.

t

,

PLH

t

PHL

tr, t

f

T

Loading...

Loading...