Marantz TMP86FH47BUG Service Manual

8 Bit Microcontroller

TLCS-870/C Series

TMP86FH47BUG

© 2011 TOSHIBA CORPORATION

All Rights Reserved

TMP86FH47BUG

Difference among product (TMP86xx46 Series)

|

86C846 |

86CH46 |

86CM46 |

86PH46 |

|

86PM46 |

|

86FH46 |

|

86FH46A |

|

86CH46A |

86CM46A |

|

86PM46A |

|

|

86FH46B |

|||

|

|

|

|

|

|

|

||||

ROM |

8192bytes |

16384bytes |

32768bytes |

16384bytes |

|

32768bytes |

|

|

16384bytes |

|

(MASK) |

(MASK) |

(MASK) |

(OTP) |

|

(OTP) |

|

|

(FLASH) |

||

|

|

|

|

|||||||

RAM |

512bytes |

512bytes |

1024bytes |

512bytes |

|

1024bytes |

|

512bytes |

|

512bytes |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

128bytes (Flash con- |

DBR(note1) |

|

|

|

- |

|

|

|

|

|

trol register con- |

|

|

|

|

|

|

|

|

|

|

tained) |

I/O |

|

|

|

|

33pins |

|

|

|

||

|

|

|

|

|

|

|

|

|

||

Large current out- |

|

|

|

|

19pins |

|

|

|

||

put |

|

|

|

(LED direct drive) |

|

|

|

|||

Interrupt |

|

|

|

18interrupt sources |

|

|

|

|||

|

|

|

(External : 6 Internal : 12) |

|

|

|

||||

|

|

|

|

|

|

|

||||

Timer counter |

|

|

|

16-bit timer counter : 1ch |

|

|

|

|||

|

|

|

8-bit timer counter : 2ch |

|

|

|

||||

|

|

|

|

|

|

|

||||

UART |

|

|

|

8-bit UART : 1ch |

|

|

|

|||

|

|

|

|

|

|

|

|

|||

SIO |

|

|

|

High-Speed SIO : 1ch |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

Key-on wakeup |

|

|

|

|

|

4ch |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

10-bit AD convert- |

|

|

|

Analog-input : 8ch |

|

|

|

|||

er |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

86FH46A |

|

|

||

|

|

|

|

|

|

VDD |

|

|

|

|

|

|

|

|

R |

|

|

|

|

|

|

without protect diode |

VDD |

without pull |

|

|

|

||

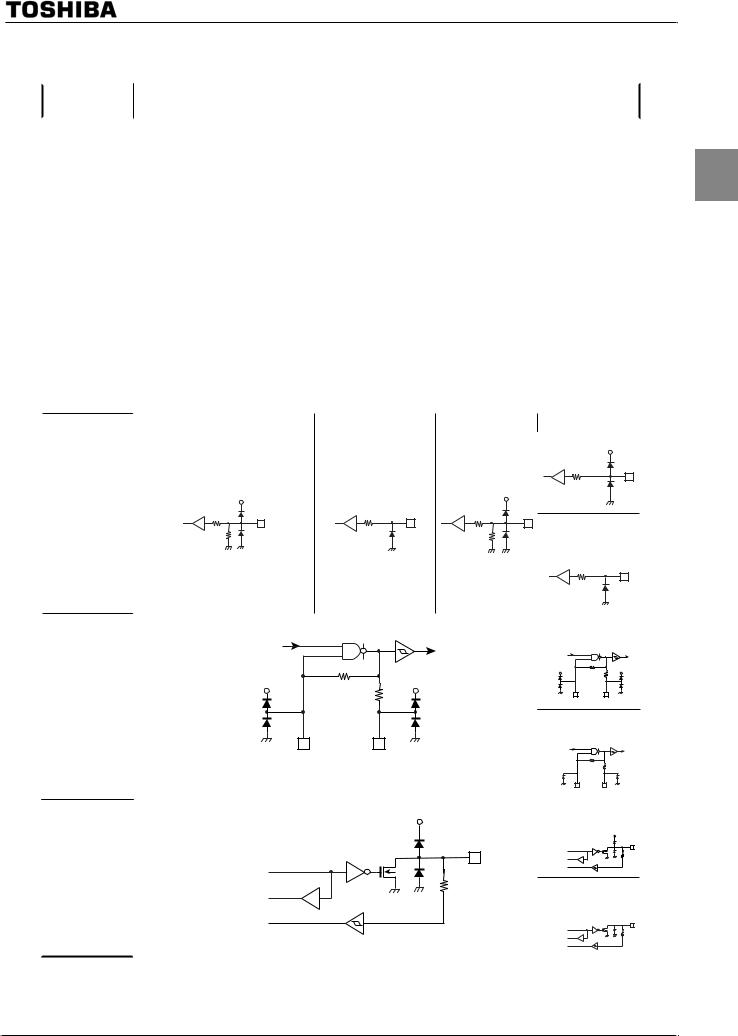

Structure |

VDD |

down resister |

|

|

|

||||

|

on the VDD side |

|

|

|

|

||||

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

of TEST pin |

R |

|

R |

R |

86FH46B |

|

|

||

|

|

|

|

|

|

||||

|

RIN |

|

|

R |

|

|

|

|

|

|

|

without pull |

IN |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

down resister |

|

without protect diode |

|||||

|

|

|

|

|

|||||

|

|

|

|

|

on the VDD side |

||||

|

|

|

|

|

R |

|

|

|

|

|

|

|

|

|

without pull |

|

|

|

|

|

|

|

|

|

down resister |

|

|

|

|

|

|

|

|

|

86FH46A |

|

|

||

|

|

|

XTEN |

|

|

|

|

|

|

|

Osc. enable |

|

fs |

|

|

XTEN |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

Osc. enable |

|

|

|

|

|

|

|

|

|

|

|

|

|

fs |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VDD |

Rf |

|

|

VDD |

|

|

|

|

|

|

|

RO |

|

|

|

|

|

|

|

|

|

|

|

|

|

VDD |

Rf |

VDD |

|

|

|

|

|

|

|

|

RO |

|

|

|

|

|

|

|

Structure |

|

|

|

XTIN |

XTOUT |

|

|||

|

|

|

|

|

|

|

|

|

|

of XTIN,XTOUT |

|

|

|

|

86FH46B |

|

|

||

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

XTEN |

|

|

|

|

|

|

|

|

Osc. enable |

|

|

|

fs |

|

|

|

|

|

|

|

|

|

|

|

XTIN |

|

XTOUT |

|

|

|

|

|

|

|

|

|

|

|

|

Rf |

RO |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

XTIN |

XTOUT |

|

||

|

|

|

|

|

86FH46A |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Structure |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

of P2 port |

|

|

|

|

86FH46B |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Initial "High-Z" |

|

|

|

|

|

|

|

|

|

Data output |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Input from |

|

|

|

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

output latch |

|

|

|

|

|

|

|

|

|

Pin input |

|

|

|

|

TMP86FH47BUG

|

86C846 |

86CH46 |

86CM46 |

86PH46 |

|

86PM46 |

86FH46 |

86FH46A |

|

86CH46A |

86CM46A |

|

86PM46A |

86FH46B |

|||

|

|

|

|

|

||||

Number of guaran- |

|

|

|

|

|

|

|

(a)86FH46A |

|

|

|

|

|

|

|

100 Times |

|

teed writes to |

|

- |

|

|

- |

100 Times |

||

|

|

|

(b)86FH46B |

|||||

flash memory |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1000 Times |

|

|

|

|

|

|

|

|

|

|

Terminal for SERI- |

|

|

|

|

|

|

BOOT1/RXD(P10) |

BOOT/RXD(P02) |

AL PROM MODE |

|

|

- |

|

|

|

||

|

|

|

|

|

BOOT2/TXD(P11) |

TXD(P03) |

||

(note2) |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(a)86FH46A |

|

|

|

|

|

|

|

|

Read protect |

Flash Security |

|

|

N.A. |

|

|

|

Read protect |

(b)86FH46B |

|

|

|

|

|

|

|

|

Read / Write |

|

|

|

|

|

|

|

|

protect |

Emulation Chip |

|

|

|

TMP86C947XB |

|

|

||

|

|

|

|

|

|

|

||

Package |

|

|

|

SDIP42-P-600-1.78 |

|

|

||

Note 1: The products with Flash memory (86FH46,86FH46A,86FH46B) contain the Flash control register (FLSCR) at 0FFFH in the DBR area. The products with mask ROM or OTP and the emulation chip do not have the FLSCR register. In these devices,therefore, a program that accesses the FLSCR register cannot function properly (executes differently as in the case of a Flash product).

Note 2: The TXD and RXD pins to be used in Serial PROM mode differ between the 86FH46 and the 86FH46A,86FH46B. Take this into consideration in your board design when you replace the product. Details of the function refer to the chapter of the 86FH46,86FH46A,86FH46B data sheet.

Note 3: P21,P22 combine XTIN,XTOUT and port.

TMP86FH47BUG

Difference among product (TMP86xx47 Series)

|

86C847 |

86CH47 |

86CM47 |

86PH47 |

|

86PM47 |

|

86FH47 |

|

86FH47A |

|

86CH47A |

86CM47A |

|

86PM47A |

|

|

86FH47B |

|||

|

|

|

|

|

|

|

||||

ROM |

8192bytes |

16384bytes |

32768bytes |

16384bytes |

|

32768bytes |

|

|

16384bytes |

|

(MASK) |

(MASK) |

(MASK) |

(OTP) |

|

(OTP) |

|

|

(FLASH) |

||

|

|

|

|

|||||||

RAM |

512bytes |

512bytes |

1024bytes |

512bytes |

|

1024bytes |

|

512bytes |

|

512bytes |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

128bytes (Flash con- |

DBR(note1) |

|

|

|

- |

|

|

|

|

|

trol register con- |

|

|

|

|

|

|

|

|

|

|

tained) |

I/O |

|

|

|

|

35pins |

|

|

|

||

|

|

|

|

|

|

|

|

|

||

Large current out- |

|

|

|

|

19pins |

|

|

|

||

put |

|

|

|

(LED direct drive) |

|

|

|

|||

Interrupt |

|

|

|

18interrupt sources |

|

|

|

|||

|

|

|

(External : 6 Internal : 12) |

|

|

|

||||

|

|

|

|

|

|

|

||||

Timer counter |

|

|

|

16-bit timer counter : 1ch |

|

|

|

|||

|

|

|

8-bit timer counter : 2ch |

|

|

|

||||

|

|

|

|

|

|

|

||||

UART |

|

|

|

8-bit UART : 1ch |

|

|

|

|||

|

|

|

|

|

|

|

|

|||

SIO |

|

|

|

High-Speed SIO : 1ch |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

Key-on wakeup |

|

|

|

|

|

4ch |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

10-bit AD convert- |

|

|

|

Analog-input : 8ch |

|

|

|

|||

er |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

86FH47A |

|

|

||

|

|

|

|

|

|

|

|

VDD |

|

|

|

|

|

|

|

|

|

|

R |

|

|

|

|

|

|

VDD |

without protect diode |

|

without pull |

|

|

|

|||

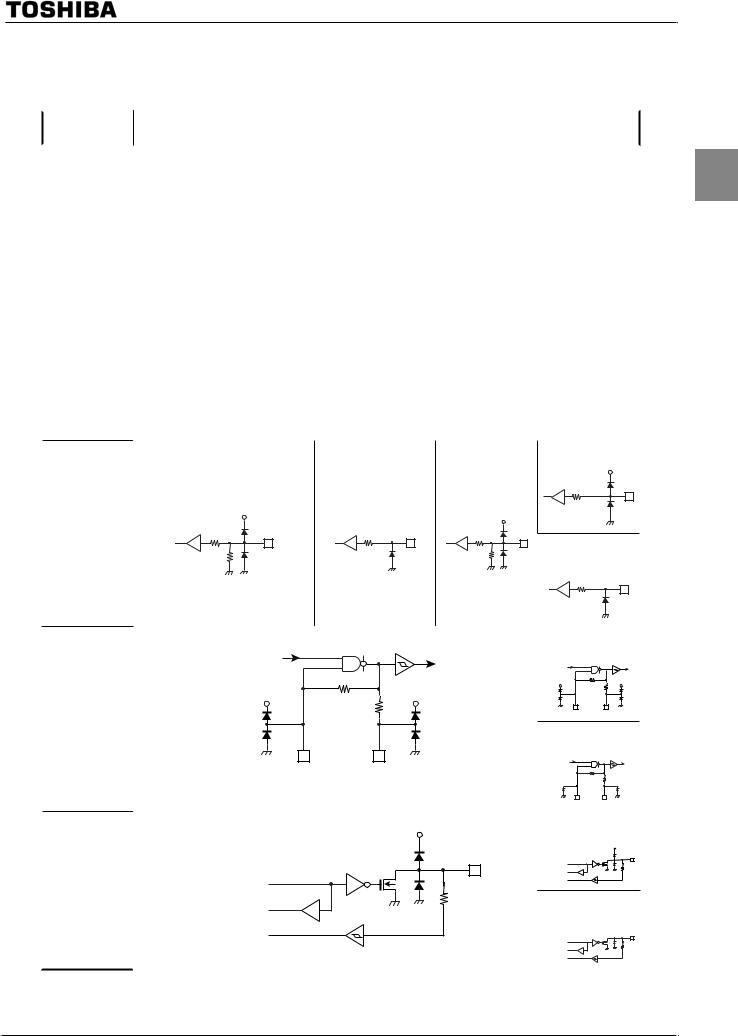

Structure |

|

VDD |

down resister |

|

|

|

|||||

|

|

|

on the VDD side |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

||

R |

|

|

|

|

|

|

|

|

|

|

|

of TEST pin |

|

|

R |

R |

|

86FH47B |

|

|

|||

|

|

|

|

|

|

|

|

||||

|

R |

IN |

without pull |

RIN |

|

|

|

|

|

|

|

|

|

|

|

without protect diode |

|||||||

|

|

|

down resister |

|

|||||||

|

|

|

|

|

on the VDD side |

||||||

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

R |

|

|

|

|

|

|

|

|

|

|

without pull |

|

|

|

||

|

|

|

|

|

|

down resister |

|

|

|

||

|

|

|

|

|

|

|

86FH47A |

|

|

||

|

|

|

|

XTEN |

|

|

|

|

|

|

|

|

|

Osc. enable |

|

|

fs |

|

|

XTEN |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

Osc. enable |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

fs |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VDD |

|

Rf |

|

|

VDD |

|

|

|

|

|

|

|

|

|

RO |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VDD |

Rf |

VDD |

|

|

|

|

|

|

|

|

|

|

RO |

|

|

|

|

|

|

|

|

Structure |

|

|

|

|

|

XTIN |

XTOUT |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

of XTIN,XTOUT |

|

|

|

|

|

|

86FH47B |

|

|

||

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

XTEN |

|

|

|

|

|

|

|

|

|

Osc. enable |

|

|

|

|

fs |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

XTIN |

|

XTOUT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Rf |

RO |

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

XTIN |

XTOUT |

|

||

|

|

|

|

|

|

|

86FH47A |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Structure |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

of P2 port |

|

|

|

|

|

86FH47B |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Initial "High-Z" |

|

|

|

|

|

|

|

|

|

|

|

Data output |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Input from |

|

|

|

|

R |

|

|

|

|

|

|

output latch |

|

|

|

|

|

|

|

|

|

|

|

Pin input |

|

|

|

|

|

TMP86FH47BUG

|

86C847 |

86CH47 |

86CM47 |

86PH47 |

|

86PM47 |

86FH47 |

86FH47A |

|

86CH47A |

86CM47A |

|

86PM47A |

86FH47B |

|||

|

|

|

|

|

||||

Number of guaran- |

|

|

|

|

|

|

|

(a)86FH47A |

|

|

|

|

|

|

|

100 Times |

|

teed writes to |

|

- |

|

|

- |

100 Times |

||

|

|

|

(b)86FH47B |

|||||

flash memory |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1000 Times |

|

|

|

|

|

|

|

|

|

|

Terminal for SERI- |

|

|

|

|

|

|

BOOT1/RXD(P10) |

BOOT/RXD(P02) |

AL PROM MODE |

|

|

- |

|

|

|

||

|

|

|

|

|

BOOT2/TXD(P11) |

TXD(P03) |

||

(note2) |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(a)86FH47A |

|

|

|

|

|

|

|

|

Read protect |

Flash Security |

|

|

N.A. |

|

|

|

Read protect |

(b)86FH47B |

|

|

|

|

|

|

|

|

Read / Write |

|

|

|

|

|

|

|

|

protect |

Emulation Chip |

|

|

|

TMP86C947XB |

|

|

||

|

|

|

|

|

|

|

|

|

Package |

|

Available |

|

|

|

|

|

|

(LQFP44- |

Available |

Available |

N.A. |

|

Available |

Available |

N.A. |

|

(86CH47) |

|

|||||||

P-1010-0.80A) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Package |

|

Available |

|

|

|

|

|

|

(LQFP44- |

N.A. |

N.A. |

Available |

|

N.A. |

N.A. |

Available |

|

(86CH47A) |

|

|||||||

P-1010-0.80B) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Note 1: The products with Flash memory (86FH47,86FH47A,86FH47B) contain the Flash control register (FLSCR) at 0FFFH in the DBR area. The products with mask ROM or OTP and the emulation chip do not have the FLSCR register. In these devices,therefore, a program that accesses the FLSCR register cannot function properly (executes differently as in the case of a Flash product).

Note 2: The TXD and RXD pins to be used in Serial PROM mode differ between the 86FH47 and the 86FH47A,86FH47B.

Take this into consideration in your board design when you replace the product. Details of the function refer to the chapter of the 86FH47,86FH47A,86FH47B data sheet.

Note 3: P21,P22 combine XTIN,XTOUT and port.

TMP86FH47BUG

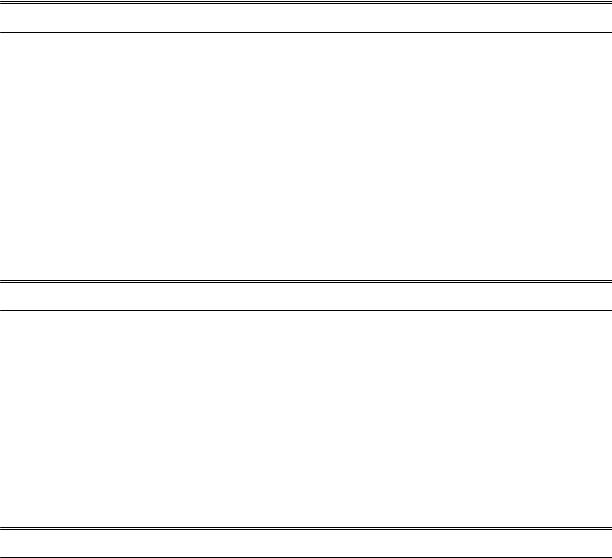

Differences in Electrical Characteristics (TMP86xx46 Series)

Read/

Fetch

Operating condition

(MCU

mode)

Erase/

Program

Operating condition

(Serial PROM mode)

Supply voltage

(Absolute Maximum Ratings)

Operating current

86C846 / 86CH46 / 86CM46 |

|

|

|

|

|

86PH46 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

86FH46A |

|

|

|

||||||||||||||||

|

|

|

|

86CM46A |

|

|

|

|

|

|

|

|

|

|

86FH46 |

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

86CH46A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

86FH46B |

|

|

|

||||||||||||||||||

|

|

|

|

86PM46 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

[V] |

|

|

|

|

|

|

|

|

|

[V] |

|

|

|

|

|

|

|

|

|

[V] |

|

|

|

|

|

|

|

|

|

|

|

|

[V] |

|

|

|

|

|

|

|

|

|

||

5.5 |

|

|

|

|

|

|

|

|

|

5.5 |

|

|

|

|

|

|

|

|

|

5.5 |

|

|

|

|

|

|

|

|

|

|

|

|

5.5 |

|

|

|

|

|

|

|

|

|

|

|

4.5 |

|

|

|

|

|

|

|

|

|

4.5 |

|

|

|

|

|

|

|

|

|

4.5 |

|

|

|

|

|

|

|

|

|

|

|

(a) |

4.5 |

|

|

|

|

|

|

|

|

|

(a) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(a) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(a) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3.0 |

|

|

|

|

|

|

|

|

|

(b) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

2.7 |

|

|

|

|

|

|

|

|

|

2.7 |

|

|

|

|

|

|

|

|

|

2.7 |

|

|

|

|

|

|

|

|

|

|

|

|

2.7 |

|

|

|

|

|

|

|

|

(Note2) |

||

|

|

|

|

|

|

|

|

|

|

2.0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(b) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1.8 |

|

|

|

|

|

|

|

|

|

1.8 |

|

|

|

|

|

|

|

(Note1) |

1.8 |

|

|

|

|

|

|

|

|

|

|

|

|

1.8 |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| <![if ! IE]> <![endif]>0.030 |

<![if ! IE]> <![endif]>0.034 |

1 4.2 8 16 [MHz] |

<![if ! IE]> <![endif]>0.030 |

<![if ! IE]> <![endif]>0.034 |

1 4.2 8 16 [MHz] |

<![if ! IE]> <![endif]>0.030 |

<![if ! IE]> <![endif]>0.034 |

1 |

4.2 |

8 |

16 |

[MHz] |

<![if ! IE]> <![endif]>0.030 |

<![if ! IE]> <![endif]>0.034 |

1 |

4.2 8 |

16 |

[MHz] |

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TMP86FH46A |

|

|

|

||||

(a) 1.8V to 5.5V (-40 to 85 °C) |

(a) 2.0V to 5.5V (-40 to 85 °C) |

(a) 2.7V to 5.5V (-40 to 85 °C) |

(a) 3.0V to 5.5V (-40 to 85 °C) |

|||||||||||||||||||||||||||||||||||||||||

(b) 2.7V to 3.0V (-20 to 85 °C) |

||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

(b) 1.8V to 2.0V (-20 to 85 °C) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TMP86FH46B |

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(a) 2.7V to 5.5V (-40 to 85 °C) |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

[V] |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

5.5 |

|

|

|

|

|

|

|

|

|

(a) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

- |

|

|

|

|

|

|

|

- |

|

|

|

|

|

|

|

|

- |

|

|

|

|

|

|

4.5 |

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2.7 |

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1.8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

<![if ! IE]> <![endif]>0.030 |

<![if ! IE]> <![endif]>0.034 |

1 |

4.2 8 |

16 |

[MHz] |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(a) 4.5V to 5.5V (-10 to 40 °C) |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

[V] |

|

|

|

|

|

|

|

|

|

|

|

|

[V] |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

5.5 |

|

|

|

|

|

|

|

|

|

|

|

(a) |

5.5 |

|

|

|

|

|

|

|

|

|

(a) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

- |

|

|

|

|

|

|

|

- |

|

|

|

4.5 |

|

|

|

|

|

|

|

|

|

|

|

|

4.5 |

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2.7 |

|

|

|

|

|

|

|

|

|

|

|

|

2.7 |

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1.8 |

|

|

|

|

|

|

|

|

|

|

|

|

1.8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

<![if ! IE]> <![endif]>0.030 |

<![if ! IE]> <![endif]>0.034 |

2 |

4 |

8 |

16 |

[MHz] |

<![if ! IE]> <![endif]>0.030 |

<![if ! IE]> <![endif]>0.034 |

2 |

4.2 8 |

16 |

[MHz] |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(a) 4.5V to 5.5V (20 to 30 °C) |

(a) 4.5V to 5.5V (-10 to 40 °C) |

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

86FH46A |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

−0.3 ~ 6.5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(a)−0.3 ~ 6.5 |

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

86FH46B |

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(a)−0.3 ~ 6.0 |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Operating current varies with each product. For details, refer to the datacheet (electrical chracteristics) of each product.(Note4)

(Note3)

Note 1: With The 86CH46A,PH46 the operating temperature (Topr) is -20 °C to 85 °C when the supply voltage VDD is less than 2.0V.

Note 2: With The 86FH46A, the operating temperature (Topr) is -20 °C to 85 °C when the supply voltage VDD is less than 3.0V.

Note 3: With The 86FH46A,86FH46B when a program is executing in the Flash memory or when data is being read from the

Flash memory, the Flash memory operates in an intermittent manner causing peak currents in the Flash memory momentarily, as shown in Figure. in this case, the supply current IDD(in NORMAL1,NORMAL2 and SLOW1 mode) is defined as the sum of the average peak current and MCU current.

Note 4: About the measurement condition of supply current, VIN level of TEST pin is deffrent between 86FH46B and the other 86xx46 series MCUs. The supply current is defined as follows; VIN of TEST pin: VIN ≤ 0.1V(86FH46B), VIN ≤ 0.2V(others) It is described in the section "Electrical characteristics" of TMP86FH46B in detail.

TMP86FH47BUG

1 machine cycle (4/fc or 4/fs)

Program counter (PC) |

n |

n+1 |

n+2 |

n+3 |

|

|

|

|

|

Momentary Flash current |

|

IDDP-P |

|

|

|

|

|

[mA] |

|

|

|

|

|

|

|

|

|

Max. current |

Sum of average momentary |

|

|

|

|

Typ. current |

Flash current and MCU current |

|

|

|

|

MCU current |

|

Intermittent Operation of Flash Memory

TMP86FH47BUG

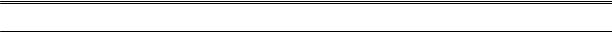

Differences in Electrical Characteristics (TMP86xx47 Series)

Read/

Fetch

Operating condition

(MCU

mode)

Erase/

Program

Operating condition

(Serial PROM mode)

Supply voltage

(Absolute Maximum Ratings)

Operating current

86C847 / 86CH47 / 86CM47 |

|

|

|

|

|

86PH47 |

|

|

|

|

|

|

|

|

|

|

|

|

|

86FH47A |

|

|

|

|||||||||||||||

|

|

|

|

86CM47A |

|

|

|

|

|

|

|

|

|

|

86FH47 |

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

86CH47A |

|

|

|

|

|

|

|

|

|

86FH47B |

|

|

|

|||||||||||||||||

|

|

|

|

86PM47 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

[V] |

|

|

|

|

|

|

|

|

|

[V] |

|

|

|

|

|

|

|

|

|

[V] |

|

|

|

|

|

|

|

|

[V] |

|

|

|

|

|

|

|

|

|

5.5 |

|

|

|

|

|

|

|

|

|

5.5 |

|

|

|

|

|

|

|

|

|

5.5 |

|

|

|

|

|

|

|

|

5.5 |

|

|

|

|

|

|

|

|

|

4.5 |

|

|

|

|

|

|

|

|

|

4.5 |

|

|

|

|

|

|

|

|

|

4.5 |

|

|

|

|

|

|

|

(a) |

4.5 |

|

|

|

|

|

|

|

|

(a) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(a) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(a) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3.0 |

|

|

|

|

|

|

|

|

(b) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2.7 |

|

|

|

|

|

|

|

|

|

2.7 |

|

|

|

|

|

|

|

|

|

2.7 |

|

|

|

|

|

|

|

|

2.7 |

|

|

|

|

|

|

|

(Note2) |

|

|

|

|

|

|

|

|

|

|

|

2.0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(b) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1.8 |

|

|

|

|

|

|

|

|

|

1.8 |

|

|

|

|

|

|

|

(Note1) |

1.8 |

|

|

|

|

|

|

|

|

1.8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| <![if ! IE]> <![endif]>0.030 |

<![if ! IE]> <![endif]>0.034 |

1 4.2 8 16 [MHz] |

<![if ! IE]> <![endif]>0.030 |

<![if ! IE]> <![endif]>0.034 |

1 4.2 8 16 [MHz] |

<![if ! IE]> <![endif]>0.030 |

<![if ! IE]> <![endif]>0.034 |

1 4.2 8 16 [MHz] |

<![if ! IE]> <![endif]>0.030 |

<![if ! IE]> <![endif]>0.034 |

1 4.2 8 |

16 [MHz] |

||||||||||||||||||||||||||

86FH47A

(a) 2.0V to 5.5V (-40 to 85 °C)

(a) 3.0V to 5.5V (-40 to 85 °C)

(a) 1.8V to 5.5V (-40 to 85 °C) (a) 2.7V to 5.5V (-40 to 85 °C) (b) 2.7V to 3.0V (-20 to 85 °C)

(b) 1.8V to 2.0V (-20 to 85 °C)

86FH47B

(a) 2.7V to 5.5V (-40 to 85 °C)

[V]

5.5

(a)

4.5

- |

- |

|

|

|

- |

|

|

|

2.7 |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

1.8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

<![if ! IE]> <![endif]>0.030 |

<![if ! IE]> <![endif]>0.034 |

1 |

4.2 |

8 |

16 |

[MHz] |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

(a) 4.5V to 5.5V (-10 to 40 °C) |

||||||||||

|

|

[V] |

|

|

|

|

|

|

|

|

[V] |

|

|

|

|

|

|

|

|

|

|

|

|

5.5 |

|

|

|

|

|

|

|

(a) |

5.5 |

|

|

|

|

|

|

|

|

|

(a) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

- |

- |

4.5 |

|

|

|

|

|

|

|

|

4.5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

2.7 |

|

|

|

|

|

|

|

|

2.7 |

|

|

|

|

|

|

|

|

|

|

||

|

|

1.8 |

|

|

|

|

|

|

|

|

1.8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

<![if ! IE]> <![endif]>0.030 |

<![if ! IE]> <![endif]>0.034 |

2 4 8 16 [MHz] |

<![if ! IE]> <![endif]>0.030 |

<![if ! IE]> <![endif]>0.034 |

2 |

4.2 |

8 |

16 |

[MHz] |

||||||||||

|

|

|

|

|

|

|

|

||||||||||||||

|

|

(a) 4.5V to 5.5V (20 to 30 °C) |

(a) 4.5V to 5.5V (-10 to 40 °C) |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

86FH47A |

|

|

|

|

||

|

−0.3 ~ 6.5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

(a)−0.3 ~ 6.5 |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

86FH47B |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(a)−0.3 ~ 6.0 |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Operating current varies with each product. For details, refer to the datacheet (electrical chracteristics) of each product.(Note4)

(Note3)

Note 1: With The 86CH47A, PH47 the operating temperature (Topr) is -20 °C to 85 °C when the supply voltage VDD is less than 2.0V.

Note 2: With The 86FH47A, the operating temperature (Topr) is -20 °C to 85 °C when the supply voltage VDD is less than 3.0V.

Note 3: With The 86FH47A,86FH47B when a program is executing in the Flash memory or when data is being read from the

Flash memory, the Flash memory operates in an intermittent manner causing peak currents in the Flash memory momentarily, as shown in Figure. in this case, the supply current IDD(in NORMAL1,NORMAL2 and SLOW1 mode) is defined as the sum of the average peak current and MCU current.

Note 4: About the measurement condition of supply current, VIN level of TEST pin is deffrent between 86FH47B and the other 86xx47 series MCUs. The supply current is defined as follows; VIN of TEST pin: VIN ≤ 0.1V(86FH47B), VIN ≤ 0.2V(others) It is described in the section "Electrical characteristics" of TMP86FH47B in detail.

TMP86FH47BUG

1 machine cycle (4/fc or 4/fs)

Program counter (PC) |

n |

n+1 |

n+2 |

n+3 |

|

|

|

|

|

Momentary Flash current |

|

IDDP-P |

|

|

|

|

|

[mA] |

|

|

|

|

|

|

|

|

|

Max. current |

Sum of average momentary |

|

|

|

|

Typ. current |

Flash current and MCU current |

|

|

|

|

MCU current |

|

Intermittent Operation of Flash Memory

Revision History

Date |

Revision |

Comment |

|

|

|

2010/7/23 |

Tentative 1 |

1st Release of Tentative |

|

|

|

2010/10/6 |

1 |

First Release |

|

|

|

2011/5/10 |

2 |

Contents Revised |

|

|

|

Table of Contents

Difference among product (TMP86xx46 Series)

TMP86FH47BUG

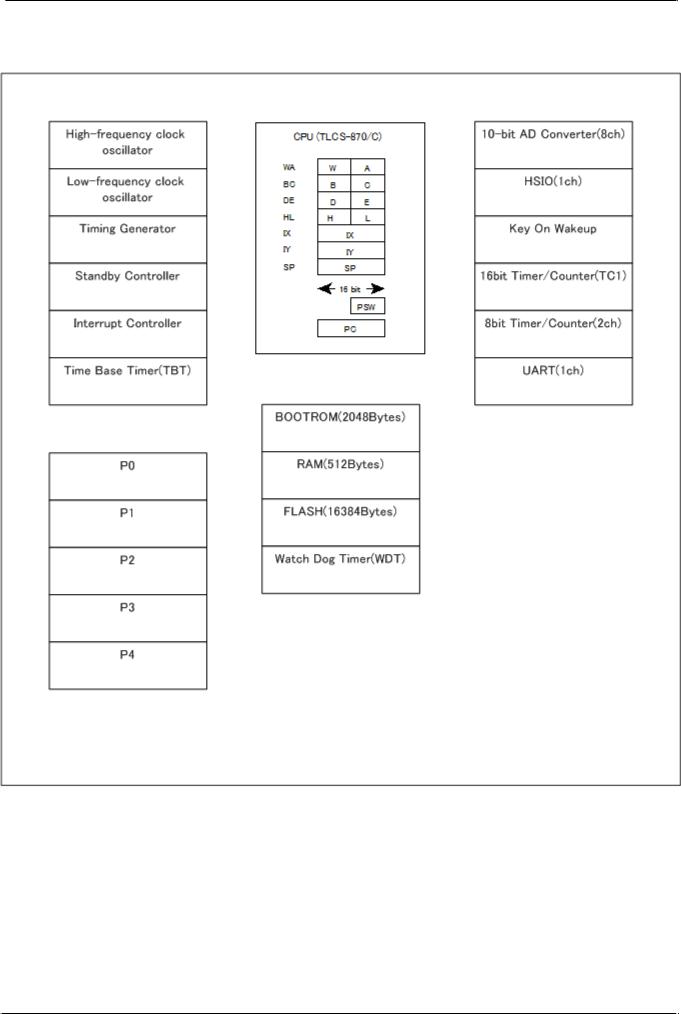

1.1 |

Features...................................................................................................................................... |

1 |

1.2 |

Pin Assignment.......................................................................................................................... |

3 |

1.3 |

Block Diagram........................................................................................................................... |

4 |

1.4 |

Pin Names and Functions.......................................................................................................... |

5 |

2. Operational Description

2.1 |

CPU Core Functions ................................................................................................................ |

7 |

|

2.1.1 |

Memory Address Map ....................................................................................................................................................... |

7 |

|

2.1.2 |

Program Memory (Flash) ................................................................................................................................................... |

7 |

|

2.1.3 |

Data Memory (RAM) ......................................................................................................................................................... |

7 |

|

2.2 |

System Clock Controller .......................................................................................................... |

8 |

|

2.2.1 |

Clock Generator ................................................................................................................................................................. |

8 |

|

2.2.2 |

Timing Generator ............................................................................................................................................................. |

10 |

|

2.2.2.1Configuration of timing generator

2.2.2.2Machine cycle

2.2.3 |

Operation Mode Control Circuit ...................................................................................................................................... |

11 |

|

2.2.3.1 Single-clock mode |

|

||

2.2.3.2 |

Dual-clock mode |

|

|

2.2.3.3 |

STOP mode |

|

|

2.2.4 |

Operating Mode Control .................................................................................................................................................. |

16 |

|

2.2.4.1STOP mode

2.2.4.2IDLE1/2 mode and SLEEP1/2 mode

2.2.4.3IDLE0 and SLEEP0 modes (IDLE0, SLEEP0)

2.2.4.4SLOW mode

2.3 Reset Circuit ........................................................................................................................... |

29 |

|

2.3.1 |

External Reset Input ......................................................................................................................................................... |

29 |

2.3.2 |

Address trap reset ............................................................................................................................................................. |

30 |

2.3.3 |

Watchdog timer reset ....................................................................................................................................................... |

30 |

2.3.4 |

System clock reset ............................................................................................................................................................ |

30 |

3. Interrupt Control Circuit

3.1 |

Interrupt latches (IL15 to IL2) ............................................................................................... |

31 |

3.2 |

Interrupt enable register (EIR) ............................................................................................... |

32 |

3.2.1 Interrupt master enable flag (IMF) .................................................................................................................................. |

32 |

|

3.2.2 Individual interrupt enable flags (EF15 to EF4) ............................................................................................................. |

32 |

|

3.3 |

Interrupt Source Selector (INTSEL)....................................................................................... |

35 |

3.4 |

Interrupt Sequence ................................................................................................................ |

35 |

3.4.1 Interrupt acceptance processing is packaged as follows. ................................................................................................ |

35 |

|

3.4.2 Saving/restoring general-purpose registers ...................................................................................................................... |

36 |

|

3.4.2.1Using PUSH and POP instructions

3.4.2.2Using data transfer instructions

3.4.3 |

Interrupt return ................................................................................................................................................................. |

38 |

i

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3.5 |

..................................................................................................Software Interrupt (INTSW) |

39 |

||||||

3.5.1 |

Address error detection .................................................................................................................................................... |

39 |

||||||

3.5.2 |

Debugging ........................................................................................................................................................................ |

39 |

||||||

3.6 |

Undefined Instruction Interrupt (INTUNDEF) ...................................................................... |

39 |

||||||

3.7 |

Address Trap Interrupt (INTATRAP) ................................................................................... |

39 |

||||||

3.8 |

External Interrupts .................................................................................................................. |

39 |

||||||

4. Special Function Register (SFR)

4.1 |

SFR.......................................................................................................................................... |

43 |

4.2 |

DBR......................................................................................................................................... |

45 |

5. Time Base Timer (TBT)

|

5.1 |

Time Base Timer..................................................................................................................... |

47 |

|

|

5.1.1 |

Configuration..................................................................................................................................................................... |

47 |

|

|

5.1.2 |

Control............................................................................................................................................................................... |

47 |

|

|

5.1.3 |

Function............................................................................................................................................................................. |

48 |

|

|

5.2 |

Divider Output (DVO)............................................................................................................ |

49 |

|

|

5.2.1 |

Configuration..................................................................................................................................................................... |

49 |

|

|

5.2.2 |

Control............................................................................................................................................................................... |

49 |

|

|

|

|

||

|

|

|

||

6. |

Watchdog Timer (WDT) |

|

||

|

6.1 |

Watchdog Timer Configuration ............................................................................................. |

51 |

|

|

6.2 |

Watchdog Timer Control ....................................................................................................... |

52 |

|

|

6.2.1 Malfunction Detection Methods Using the Watchdog Timer ......................................................................................... |

52 |

||

|

6.2.2 |

Watchdog Timer Enable .................................................................................................................................................. |

53 |

|

|

6.2.3 |

Watchdog Timer Disable ................................................................................................................................................. |

54 |

|

|

6.2.4 Watchdog Timer Interrupt (INTWDT) ............................................................................................................................ |

54 |

||

|

6.2.5 |

Watchdog Timer Reset ..................................................................................................................................................... |

55 |

|

|

6.3 |

Address Trap .......................................................................................................................... |

56 |

|

|

6.3.1 Selection of Address Trap in Internal RAM (ATAS) ..................................................................................................... |

56 |

||

|

6.3.2 Selection of Operation at Address Trap (ATOUT) ......................................................................................................... |

56 |

||

|

6.3.3 Address Trap Interrupt (INTATRAP)............................................................................................................................... |

56 |

||

|

6.3.4 |

Address Trap Reset........................................................................................................................................................... |

57 |

|

|

|

|

||

|

|

|

||

7. |

I/O Ports |

|

||

|

7.1 |

Port P0 (P07 to P00)............................................................................................................... |

60 |

|

|

7.2 |

Port P1 (P17 to P10)............................................................................................................... |

61 |

|

|

7.3 |

Port P2 (P22 to P20)............................................................................................................... |

62 |

|

|

7.4 |

Port P3 (P37 to P30)............................................................................................................... |

63 |

|

|

7.5 |

Port P4 (P47 to P40)............................................................................................................... |

65 |

|

|

|

|||

|

|

|||

8. 16-Bit Timer/Counter 1 (TC1) |

|

|||

|

8.1 |

Configuration........................................................................................................................... |

67 |

|

|

8.2 |

Timer/Counter Control............................................................................................................ |

68 |

|

ii

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

...................................................................................................................................8.3 Function |

70 |

|||||

8.3.1 |

Timer mode........................................................................................................................................................................ |

70 |

|||||

|

8.3.2 External Trigger Timer Mode........................................................................................................................................... |

72 |

|||||

8.3.3 |

Event Counter Mode......................................................................................................................................................... |

74 |

|||||

8.3.4 |

Window Mode................................................................................................................................................................... |

75 |

|||||

|

8.3.5 Pulse Width Measurement Mode...................................................................................................................................... |

76 |

|||||

|

8.3.6 Programmable Pulse Generate (PPG) Output Mode........................................................................................................ |

79 |

|||||

9. 8-Bit TimerCounter (TC3, TC4)

9.1 |

Configuration .......................................................................................................................... |

83 |

9.2 |

TimerCounter Control............................................................................................................. |

84 |

9.3 |

Function................................................................................................................................... |

89 |

9.3.1 8-Bit Timer Mode (TC3 and 4)........................................................................................................................................ |

89 |

9.3.2 8-Bit Event Counter Mode (TC3, 4)................................................................................................................................. |

90 |

9.3.3 8-Bit Programmable Divider Output (PDO) Mode (TC3, 4)........................................................................................... |

90 |

9.3.4 8-Bit Pulse Width Modulation (PWM) Output Mode (TC3, 4)...................................................................................... |

93 |

9.3.5 16-Bit Timer Mode (TC3 and 4)...................................................................................................................................... |

95 |

9.3.6 16-Bit Event Counter Mode (TC3 and 4)......................................................................................................................... |

96 |

9.3.7 16-Bit Pulse Width Modulation (PWM) Output Mode (TC3 and 4).............................................................................. |

96 |

9.3.8 16-Bit Programmable Pulse Generate (PPG) Output Mode (TC3 and 4)....................................................................... |

99 |

9.3.9 Warm-Up Counter Mode................................................................................................................................................. |

101 |

9.3.9.1Low-Frequency Warm-up Counter Mode

(NORMAL1 → NORMAL2 → SLOW2 → SLOW1)

9.3.9.2High-Frequency Warm-Up Counter Mode

(SLOW1 → SLOW2 → NORMAL2 → NORMAL1)

10. Synchronous Serial Interface (SIO)

10.1 |

Configuration ...................................................................................................................... |

103 |

10.2 |

Control................................................................................................................................. |

104 |

10.3 |

Function............................................................................................................................... |

106 |

10.3.1 |

Serial clock.................................................................................................................................................................... |

106 |

|

10.3.1.1 |

Clock source |

|

|

10.3.1.2 |

Shift edge |

|

|