Service

SA17S1 /F1N/L1G/N1G/S1G

SA-17S1

Manual

POWER

Super Audio CD Player

PHONES

PAUSE

STOP

LEVEL

MIN MAX

PLAY

OPEN/CLOSE

ON/OFF

SUPER AUDIO CD PLAYER SA-17S1

TIME

SOUND MODE

PHANTOM-C

DISPLAY

TABLE OF CONTENTS

SECTION PAGE

1. TECHNICAL SPECIFICATIONS ...................................................................................................1

2. SERVICE MODE...........................................................................................................................2

3. TAKING THE DISC OUT OF EMERGENCY................................................................................. 3

4. CAUTION Optical pick up and Servo Board.................................................................................. 4

5. BLOCK DIAGRAM ........................................................................................................................ 5

6. SCHEMATIC DIAGRAM................................................................................................................ 7

7. PARTS LOCATION...................................................................................................................... 20

8. MICROPROCESSOR AND IC DATA........................................................................................... 27

9. EXPLODED VIEW AND PARTS LIST......................................................................................... 45

10. MECHA LOADER ASS'Y ............................................................................................................ 48

11. ELECTRICAL PARTS LIST.........................................................................................................49

Please use this service manual with referring to the user guide ( D.F.U. ) without fail.

R

SA-17S1

08AK855010 MIT

First Issue 2002.12

MARANTZ DESIGN AND SERVICE

Using superior design and selected high grade components,

Only original

MARANTZ

parts can insure that your

MARANTZ

MARANTZ

product will continue to perform to the specifi cations for which

company has created the ultimate in stereo sound.

it is famous.

Parts for your

MARANTZ

ORDERING PARTS :

equipment are generally available to our National Marantz Subsidiary or Agent.

Parts can be ordered either by mail or by Fax.. In both cases, the correct part number has to be specifi ed.

The following information must be supplied to eliminate delays in processing your order :

1. Complete address

2. Complete part numbers and quantities required

3. Description of parts

4. Model number for which part is required

5. Way of shipment

6. Signature : any order form or Fax. must be signed, otherwise such part order will be considered as null and void.

USA

MARANTZ AMERICA, INC

1100 MAPLEWOOD DRIVE

ITASCA, IL. 60143

USA

PHONE : 630 - 741 - 0300

FAX : 630 - 741 - 0301

AMERICAS

SUPERSCOPE TECHNOLOGIES, INC.

MARANTZ PROFESSIONAL PRODUCTS

2640 WHITE OAK CIRCLE, SUITE A

AURORA, ILLINOIS 60504 USA

PHONE : 630 - 820 - 4800

FAX : 630 - 820 - 8103

EUROPE / TRADING

MARANTZ EUROPE B.V.

P. O. BOX 8744, BUILDING SILVERPOINT

BEEMDSTRAAT 11, 5653 MA EINDHOVEN

THE NETHERLANDS

PHONE : +31 - 40 - 2507844

FAX : +31 - 40 - 2507860

AUSTRALIA

TECHNICAL AUDIO GROUP PTY, LTD

558 DARLING STREET,

BALMAIN, NSW 2041,

AUSTRALIA

PHONE : 61 - 2 - 9810 - 5300

FAX : 61 - 2 - 9810 - 5355

CANADA

LENBROOK INDUSTRIES LIMITED

633 GRANITE COURT,

PICKERING, ONTARIO L1W 3K1

CANADA

PHONE : 905 - 831 - 6333

FAX : 905 - 831 - 6936

HONG KONG

Jolly ProAudio Broadcast Engineering Ltd.

UNIT 2, 10F, WAH HUNG CENTRE,

41 HUNG TO ROAD, KWUN TONG, KLN.,

HONG KONG

PHONE : 852 - 21913660

FAX : 852 - 21913990

AUSTRALIA

QualiFi Pty Ltd,

24 LIONEL ROAD,

MT. WAVERLEY VIC 3149

AUSTRALIA

PHONE : +61 - (0)3 - 9543 - 1522

FAX : +61 - (0)3 - 9543 - 3677

NEW ZEALAND

WILDASH AUDIO SYSTEMS NZ

14 MALVERN ROAD MT ALBERT

AUCKLAND NEW ZEALAND

PHONE : +64 - 9 - 8451958

FAX : +64 - 9 - 8463554

JAPAN

MARANTZ JAPAN, INC.

35- 1, 7- CHOME, SAGAMIONO

SAGAMIHARA - SHI, KANAGAWA

JAPAN 228-8505

PHONE : +81 42 748 1013

FAX : +81 42 741 9190

Technical

THAILAND

MRZ STANDARD CO., LTD

746 - 754 MAHACHAI ROAD.,

WANGBURAPAPIROM, PHRANAKORN,

BANGKOK, 10200 THAILAND

PHONE : +66 - 2 - 222 9181

FAX : +66 - 2 - 224 6795

TAIWAN

PAI- YUING CO., LTD.

6 TH FL NO, 148 SUNG KIANG ROAD,

TAIPEI, 10429, TAIWAN R.O.C.

PHONE : +886 - 2 - 25221304

FAX : +886 - 2 - 25630415

SHOCK, FIRE HAZARD SERVICE TEST :

SINGAPORE

WO KEE HONG DISTRIBUTION PTE LTD

130 JOO SENG ROAD

#03-02 OLIVINE BUILDING

SINGAPORE 368357

PHONE : +65 6858 5535 / +65 6381 8621

FAX : +65 6858 6078

MALAYSIA

WO KEE HONG ELECTRONICS SDN. BHD.

2ND FLOOR BANGUNAN INFINITE CENTRE

LOT 1, JALAN 13/6, 46200 PETALING JAYA

SELANGOR DARUL EHSAN, MALAYSIA

PHONE : +60 - 3 - 7954 8088

FAX : +60 - 3 - 7954 7088

KOREA

MK ENTERPRISES LTD.

ROOM 604/605, ELECTRO-OFFICETEL, 16-58,

3GA, HANGANG-RO, YONGSAN-KU, SEOUL

KOREA

PHONE : +822 - 3232 - 155

FAX : +822 - 3232 - 154

CAUTION : After servicing this appliance and prior to returning to customer, measure the resistance between either primary AC

cord connector pins ( with unit NOT connected to AC mains and its Power switch ON ), and the face or Front Panel of product

and controls and chassis bottom.

Any resistance measurement less than 1 Megohms should cause unit to be repaired or corrected before AC power is applied,

and verifi ed before it is return to the user/customer.

Ref. UL Standard No. 1492.

In case of diffi culties, do not hesitate to contact the Technical

Department at above mentioned address.

020816MIT

1. TECHNICAL SPECIFICATIONS

Super Audio CD CD

Audio Characteristics

Analog output

Channels 6channels (Max.) 2channels

Frequency range 2Hz — 100kHz 2Hz — 20kHz

Frequency characteristics 2Hz — 50kHz (-3dB) 2Hz — 20kHz

Dynamic range 114dB 100dB

THD (1kHz) 0.0008% 0.0020%

Wow & Flutter Precision of quartz Precision of quartz

Output level 2.2V 2.2V

Digital output

Output level (Cinch JACK) — 0.5Vp-p (75Ω)

Output level (Optical) — -19dBm

Headphone output level 0.5W / 32Ω (max, Vol.) 0.5mW / 32Ω (max, Vol.)

Optical Readout System

Laser AlGaAs AlGaAs

Wave length 650nm 780nm

Signal format 1-bit DSD 16-bit linear PCM

Sampling frequency 2.8224MHz 44.1kHz

Power Supply

Input Voltage, Frequency (/F).................................................................... AC 100V 50/60Hz

(/L)......................................................................... AC 110V 60Hz

(/N/S)..................................................................... AC 230V 50Hz

Power Consumption....................................................................................................... 24W

Cabinet, etc.

Dimensions ...............................................................................................

Net weight...................................................................................................................11.5kg

Operating temperatures.................................................................................. +5°C ~ +35°C

Operating humidity............................................................................. 5 ~ 90% (without dew)

Accessories

• Remote control unit (RC-17SAS1) ....................................................................................1

Dimensions (Width × Height × Depth)....................................................

Net weight (without Batteries) .....................................................................................189g

• AAA (R03) Batteries ..........................................................................................................2

• AC Power cord...................................................................................................................1

• Audio cable...............................................................................................................3 pairs

• Remote connection Cable ................................................................................................1

• User’s Guide......................................................................................................................1

458 × 110 × 394mm

44 × 17.5 × 239mm

1

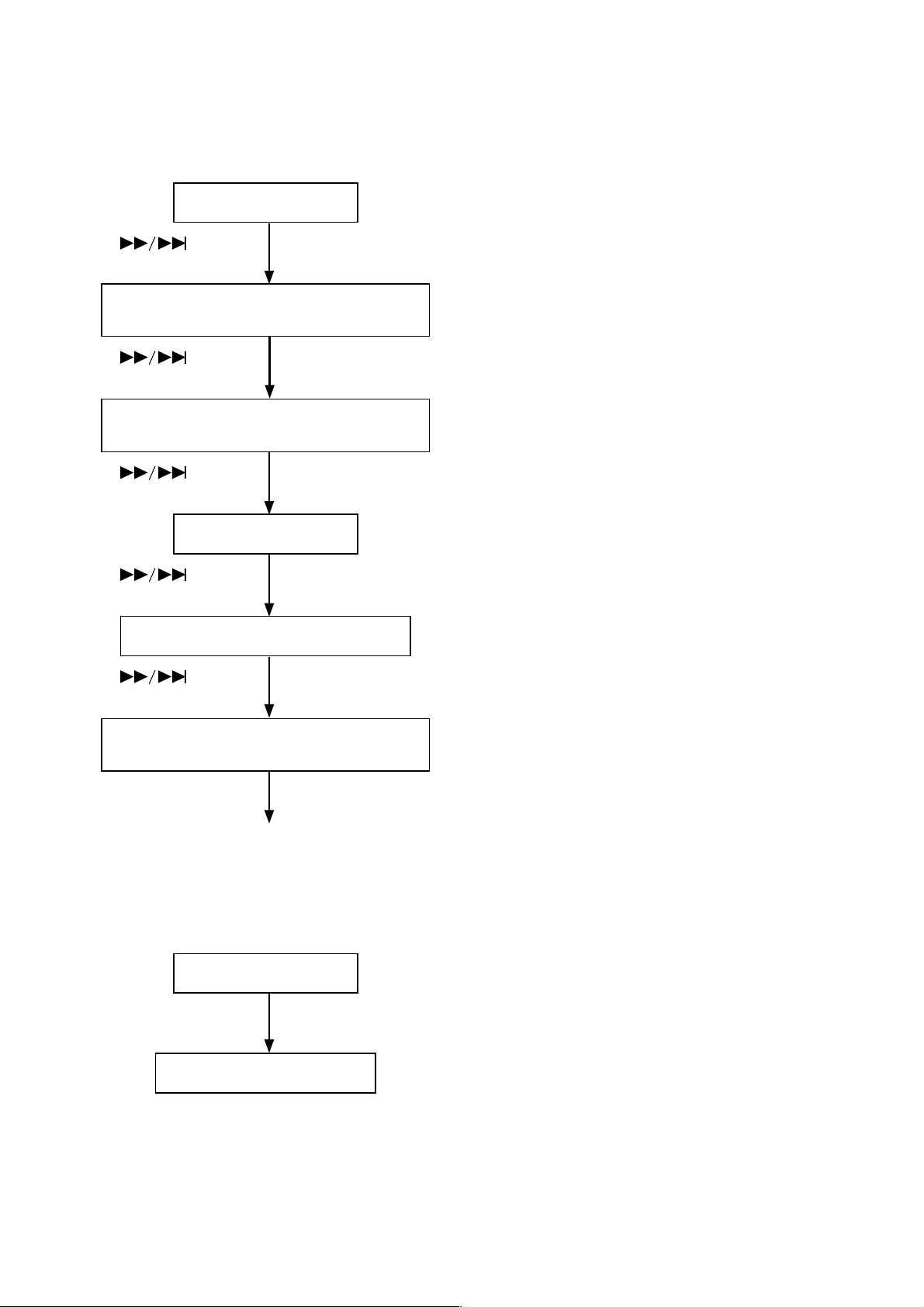

2. SERVICE MODE

2-1. Factory mode

While pressing <OPEN/CLOSE>and<NEXT>plug in the Mains cord.

Press<

Press<

Press<

Press<

"SA-17S1" is displayed

>

Version of Backend(QF01) u-COM is displayed

"Ver : X.XX" is displayed

>

Version of Frontend(Q125) µ-COM is displayed

"DrvVer : XX.XX" is displayed

>

All parts of FTD is turned on

>

Each Segment is displayed one by one

Press<

Turn off Power to quit Service Mode.

2-2. Reset the unit to the default settings

While pressing <OPEN/CLOSE>and<NEXT>plug in the Mains cord.

Press <PHANTOM-C>

All the setting are restored to the default setting.

When key is depressed,key name is displayed

>

Check of key

"SA-17S1" is displayed

"EEPROM Clear" is displayed

2

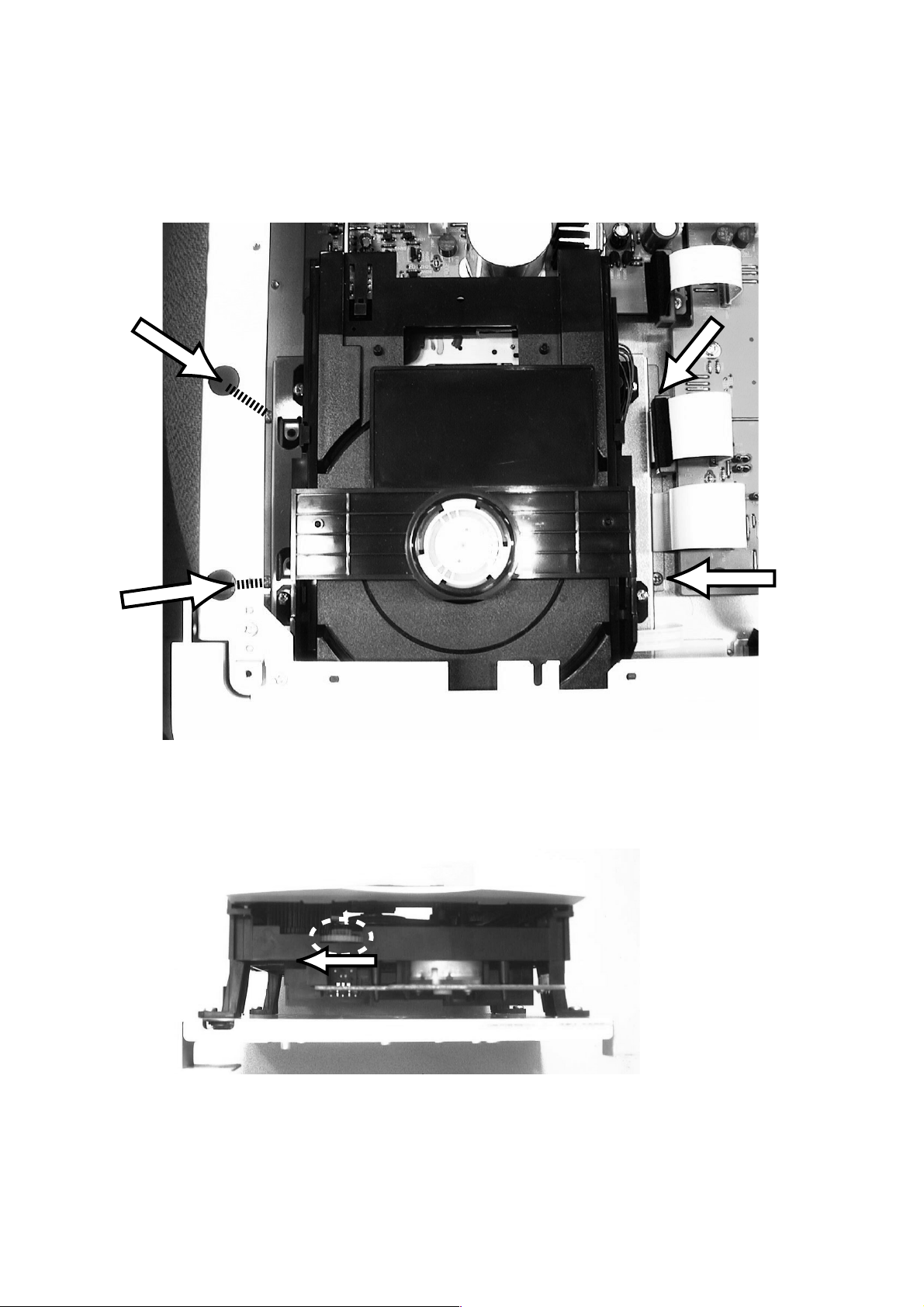

3. TAKING THE DISC OUT OF EMERGENCY

1. Remove 8 screws on the top cover and remove the top cover.

2. Remove 6 screws on the side panel and remove the side panel.

3. Remove Power SW. Link.

4. Remove 4 screws pointed with the arrows.

5. Disconnect all the wires at the right.

6. Remove the Mecha. component.

7. Turn the gear to the direction shown with your fi nger and disc tray will opened.

3

4. CAUTION Optical pick up and Servo Board

When removing the fl at wire between Optical pick up and Servo Board (PV16),

Solder the four lands pointed by arrows to short the circuit.

Otherwise the LASER DIODE may be damaged by static electricity.

4

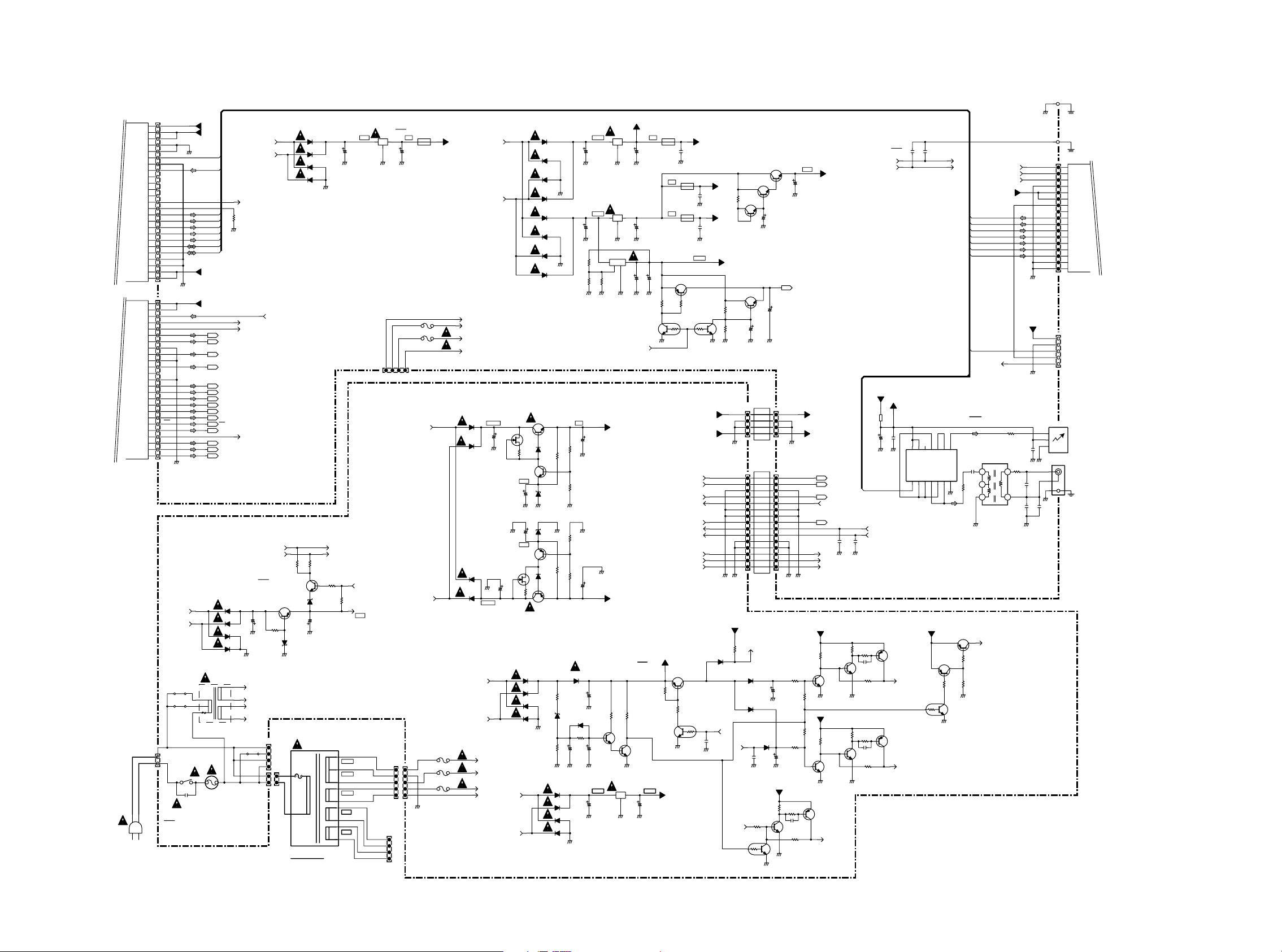

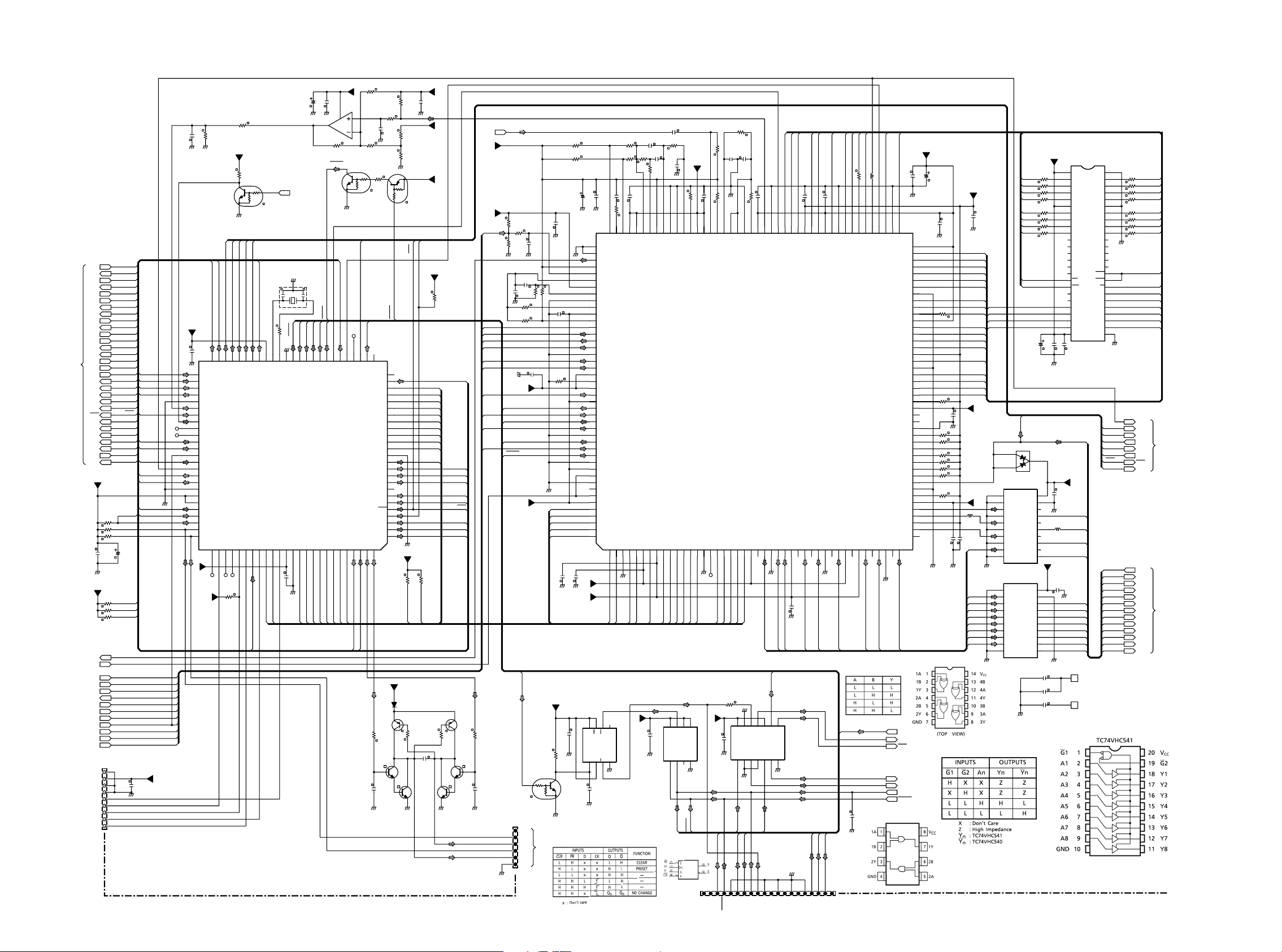

5. BLOCK DIAGRAM

SACD UNIT BLOCK

TURNTABLE

photo

Laser

control

CD and DVD

FOC,RAD,SLDG

3-AXICAL ACTUATOR

CLV MOTOR

BA5981FP

MOTOR DRIVER

LASER and MONITOR

SERVO SIGNAL

FOC

RAD

M11L1616SA-45

CXD1881R

RF-AMP, AGC, EQ

LASER POWER CONTROL

RF-DC

AMP

CXD3068Q

RF-AC

EFM AMP

33.8688MHz DSARS

RFACO

Control data bus line

CD DECODER

and

D-RAM(16M)

CXD1882R

DSD DECODER

WATER MARK

RF-AMP

SYSTEM CLK SYCL

WARFI

Control data bus line

DIGITAL SERVO

CLV

SLEDG

SERVO CONTOROL MPU

CXP97100

PCM data bus line

MPU data bus line

AT24C04N

EM636165TS-7

LEVEL SHIFT

DIG out

SDRAM(16M)

CXD2752R/

CXD2753R

PSP DECORD

and

DSD MULTI-

CHANNL

DECODER

DIVIDER

SYCLSW

MB90F553A

FEATUR MPU

EEROM

DISPLAY and

KEYS

RC-5

for front block

m odule power in

+8V

DAPC

DARD

DACL

LRCK

DSAC

DSALS

DSALF

SACD/CD

DATA SWITCH

MODE

CONTROL

+5B

+5A

DIG

out

GND

DAC PWB

DAPC/DARD

DACL/LRCK

SYCL

CONTROL

and

DAC CONTROL

PCM/DSD DATA

DSAC/DSALF

DACL/LRCK

SYCL

CONTROL

DSALS/DSARS

DACL/LRCK

SYCL

CONTROL

CS4397

FRONT-CH DAC

CS4397

WOOFER/

CENTER-CH

DAC

CS4397

REAR-CH DAC

L.ch

HDAM

L.ch

Diffrencial AMP

R.ch

&

2nd-LPF

HDAM

Rch

Diffrencial AMP

&

2nd-LPF

CENTER

WOOFER WOOFER

S-Lch S-Lch

HDAM x 2

Diffrencial AMP

&

2nd-LPF

HDAM x 2

CENTER

Diffrencial AMP

S-Rch

&

2nd-LPF

S-Rch

HDAM

SUM

HDAM

SUM

AMP

AMP

PTMDRV

SW

PTMDRV

PTMDRV

HDAM

2nd-LPF &

Current AMP

HDAM

2nd-LPF &

Current AMP

HDAM

2nd-LPF &

Current AMP

HDAM

2nd-LPF &

Current AMP

L ch

FRONT

R ch

CENTRER

WOOFER

L ch

SURROUND

R ch

FRONT UNIT BLOCK

IR sensor

RC-5

LC7512NE

FTD DRIVER

PLAY/STOP/PAUSE/NEXT/PREVI/etc

KEYS

DISPLAY

and

KEYS/

RC-5

SUB TRANS

for FL

MAIN TRANS

-VFT

FILMENT

FILMENT

+5V

+5.6V

+8V

+5V

POWER SUPLLY AND MUTING

+12V

-12V

from module

for module

DIGITAL I/O

buffer

from IR

sensor

for DAC

CENTER ON/OFF

CAOX

OPT

RC-5

I/O

IN/OUT

SW

LPF SW

phantom

SW

DIGITAL OUT

5 6

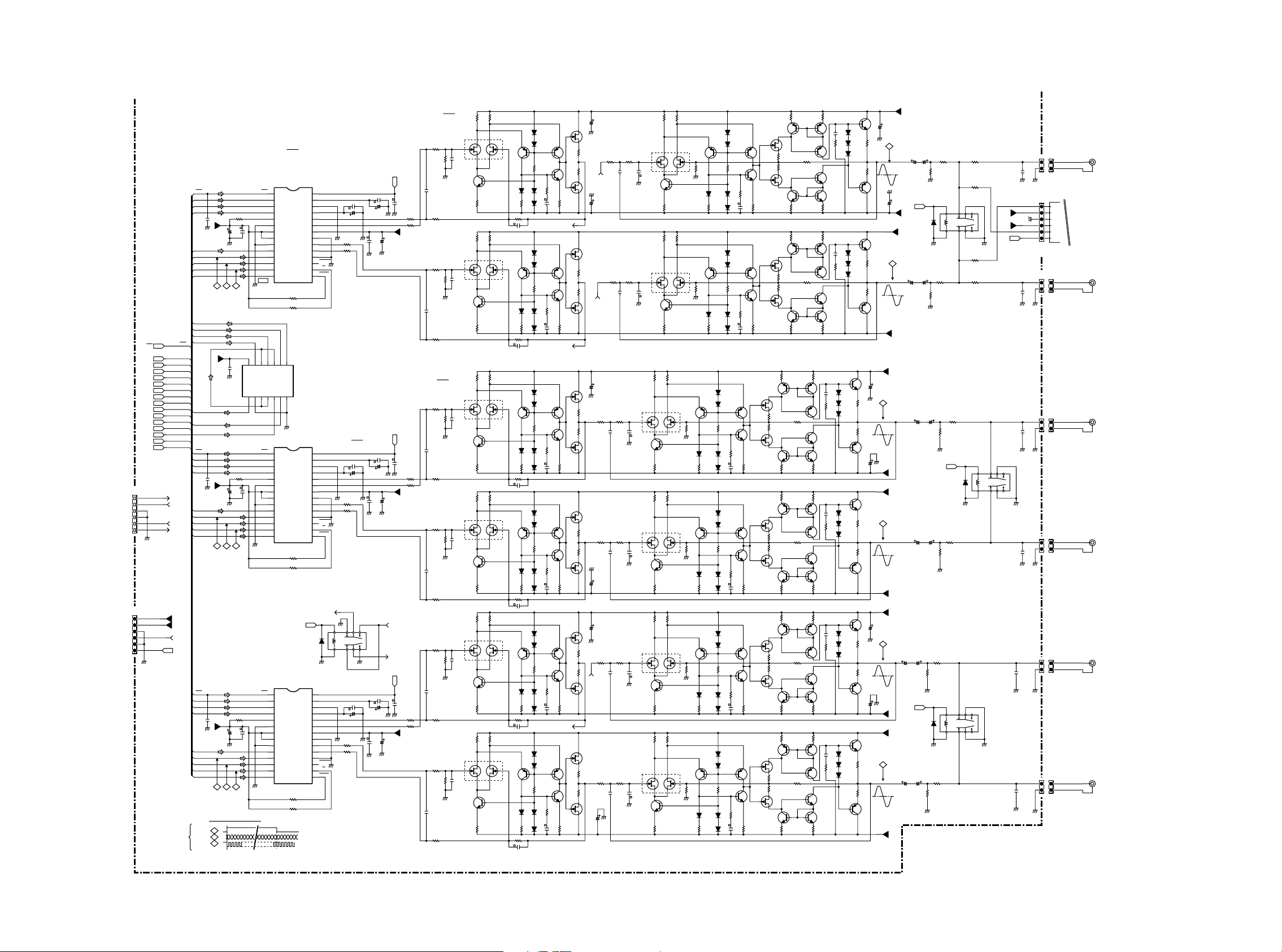

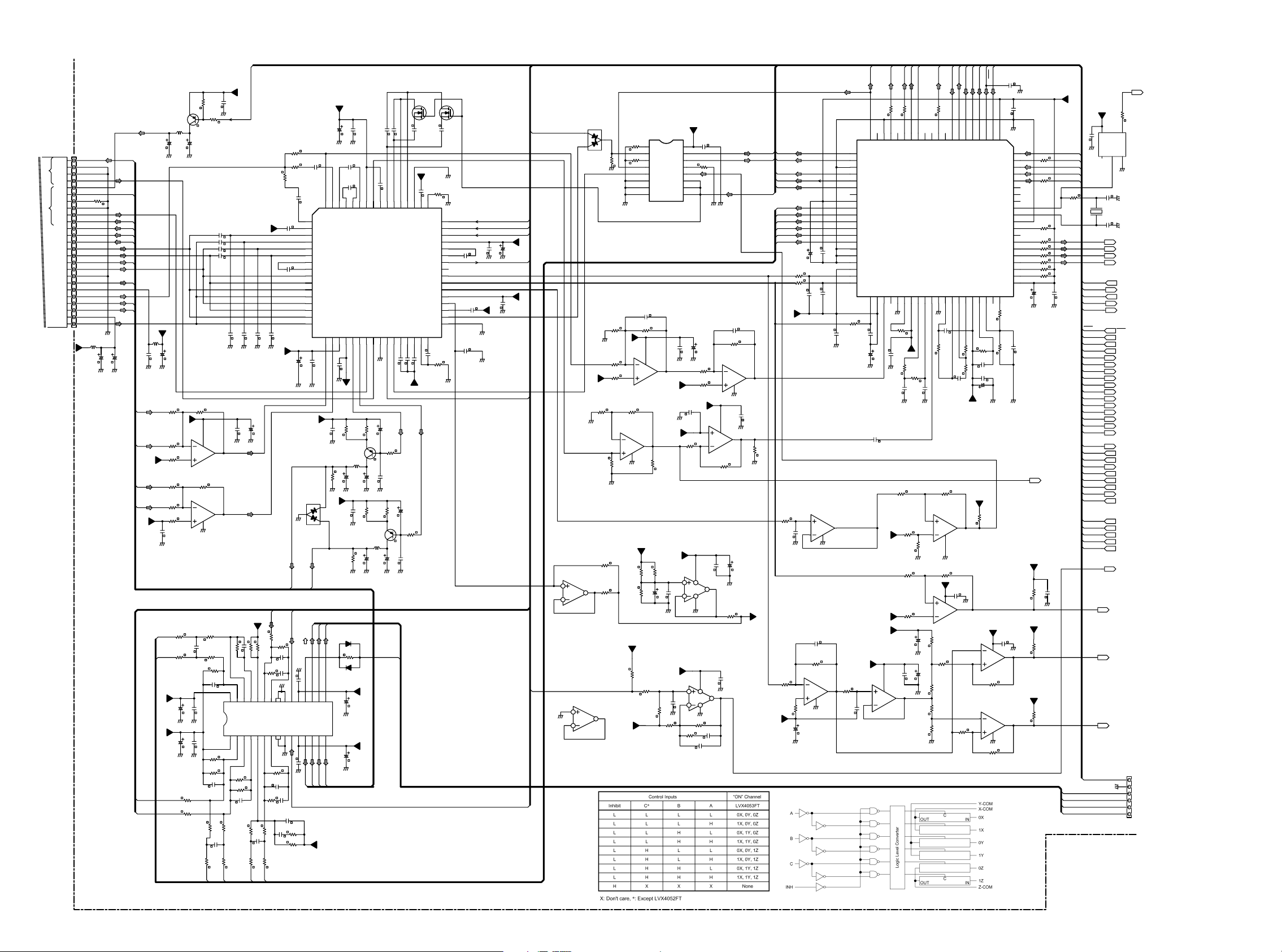

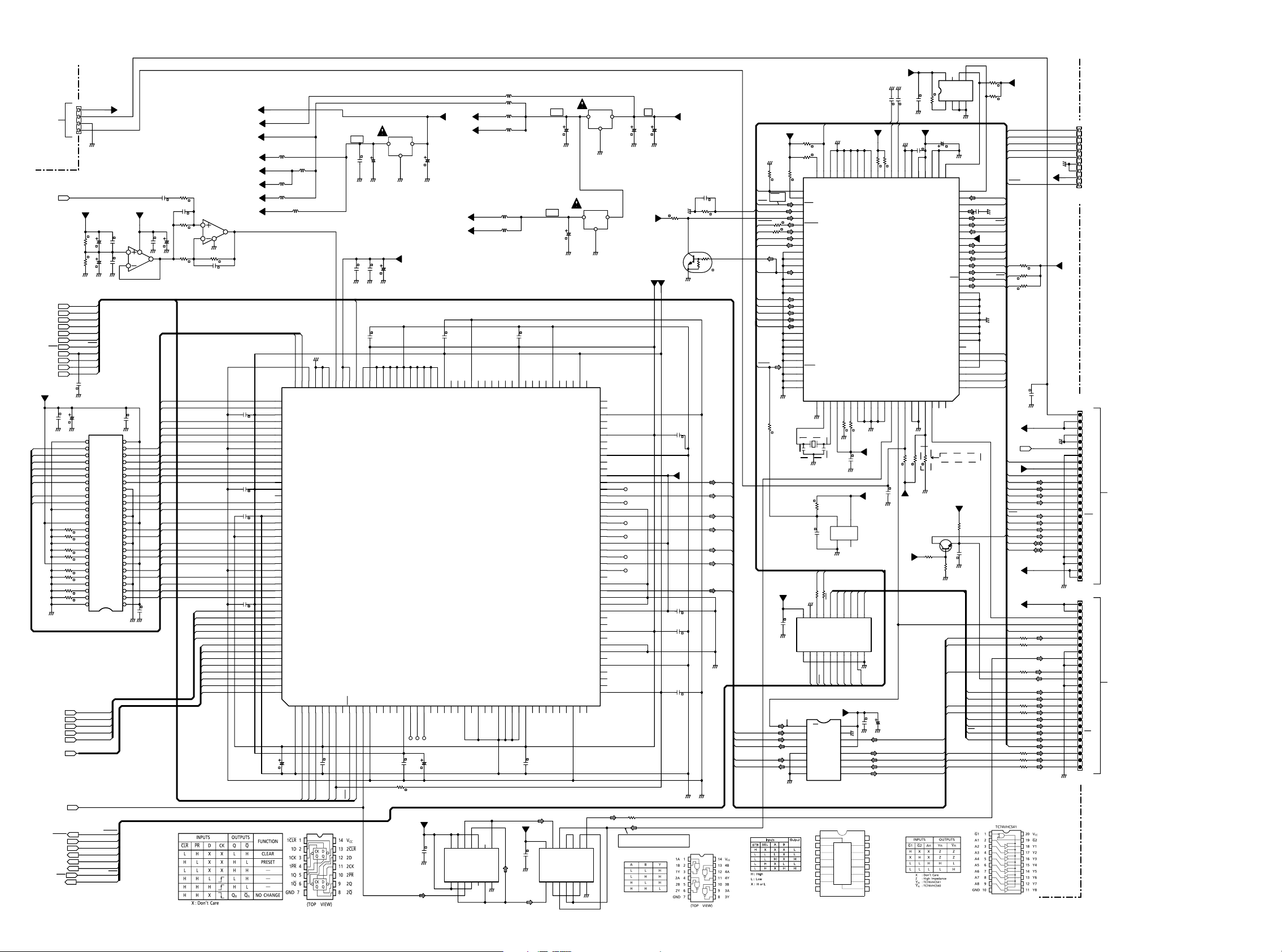

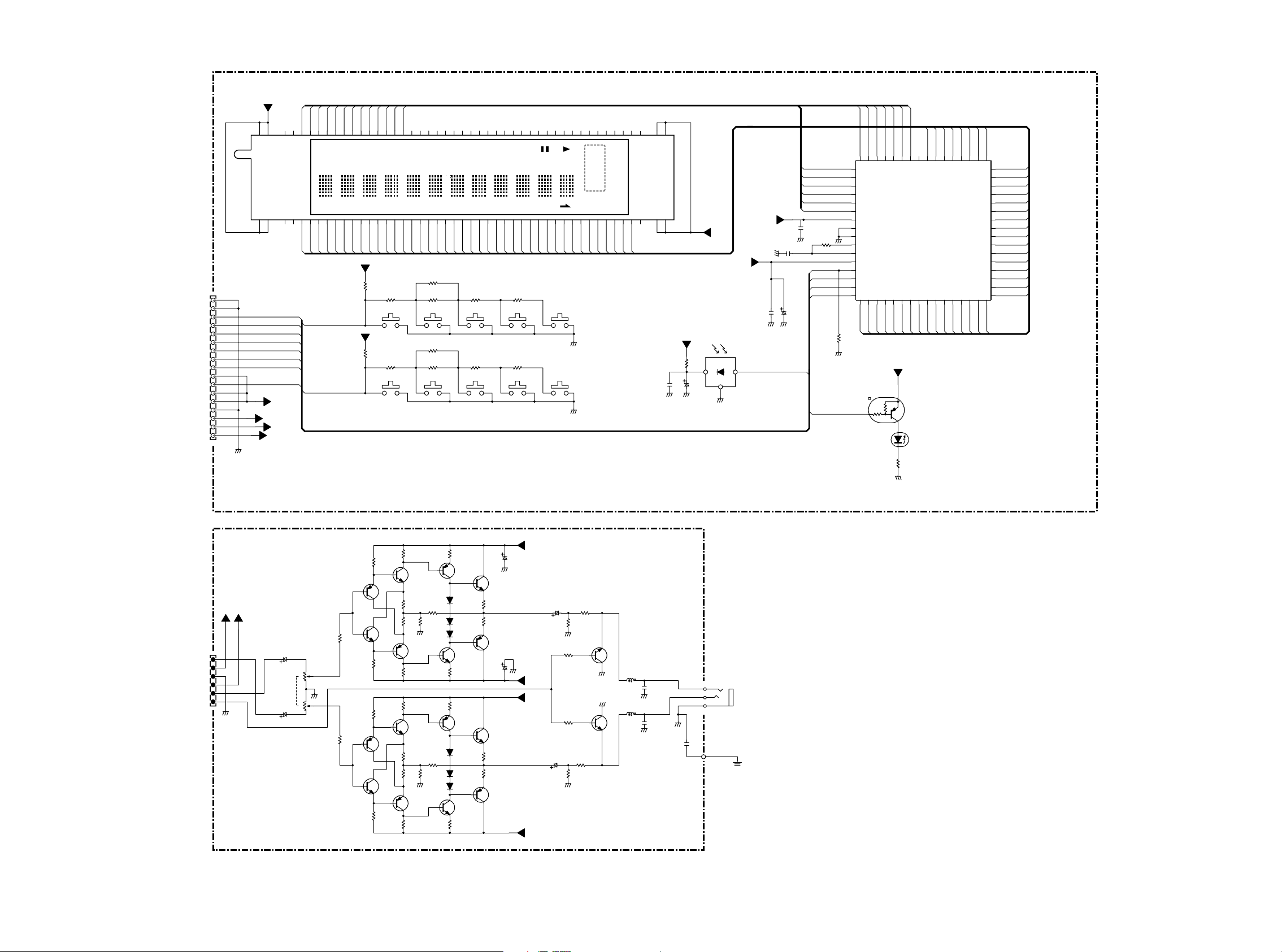

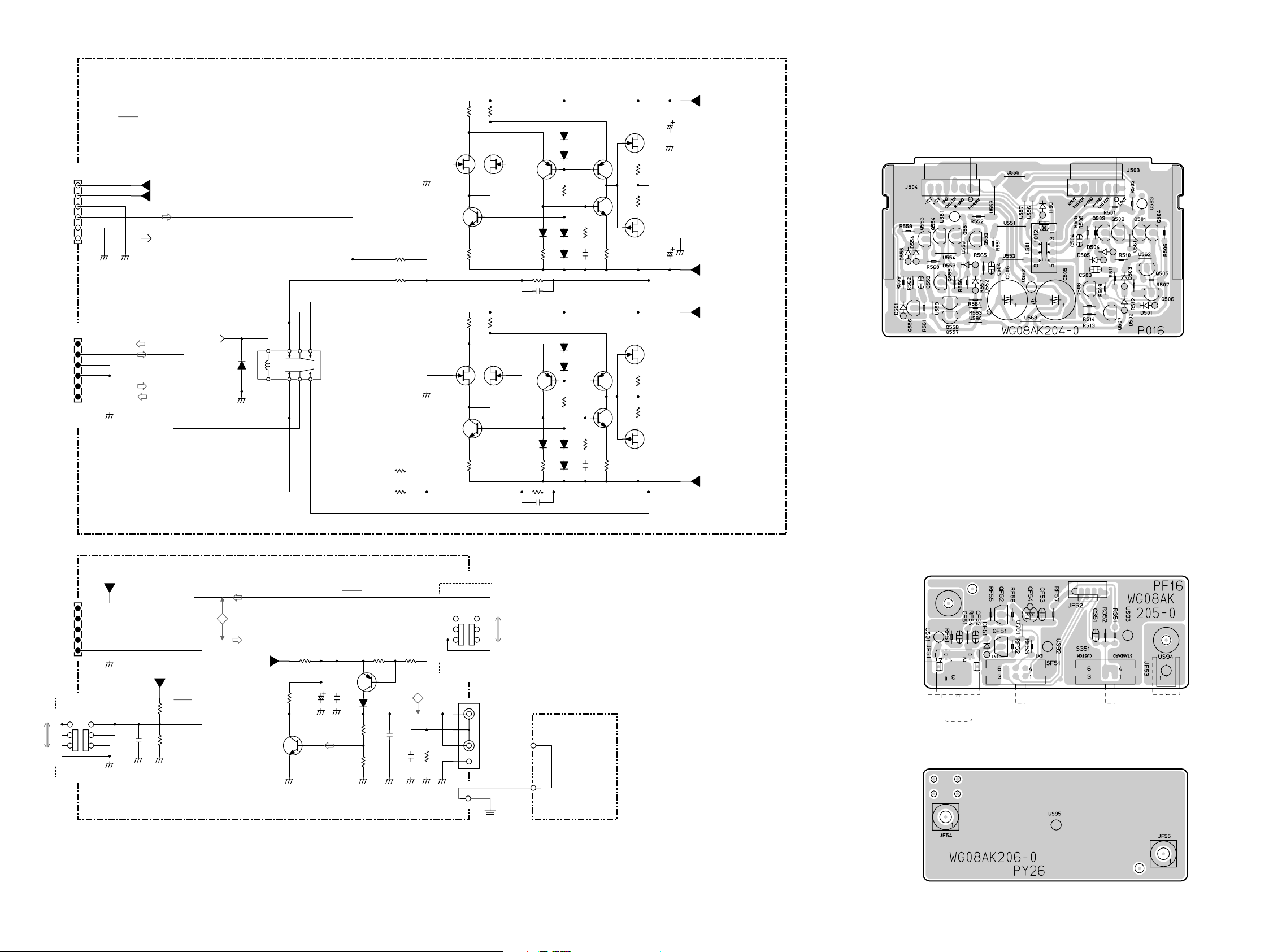

6. SCHEMATIC DIAGRAM

JF01

25P

WF04

+5A

25

P8M

24

P8M

23

MGN

22

MGN

21

DIGO

20

GND

19

RC5S

18

BK5V

17

STBSW

16

CDLED

15

SALED

14

SRLED

13

STBLED

12

DISPLED

11

TO SERVO PCB(PV16)

DSD DATA IN AND POWER OUT

TO SERVO PCB(PV16)

DSD DATA IN AND POWER OUT

W001

FRES

10

FCEN

9

FCLK

8

FDAT

7

KEY1

6

KEY0

5

GND

4

GND

3

+5A

2

+5A

1

JF02

25P

WF05

+5B

25

+5B

24

LPFSW

23

MODE1

22

MUT1

21

DAPC

20

DARD

19

GND

18

SYCL

17

GND

16

DACL

15

M0

14

GND

13

M41

12

M42

11

DSALS

10

DSARS

9

M2

8

M3

7

RST

6

M43

5

MUT2

4

DALR

3

DSALF

2

DSAC

1

for F,N,S

JH01

2

1

LPT

M-GND

GND

GND

AP1

AP2

12

UH01

12

UH02

for L

SH01

12

GH01

0.1

AC250V

5

3

1

+5VD

P8M+5A

DIGO

RC5S

DISPLED

FRES

FCEN

FCLK

FDAT

KEY1

KEY0

+5B

DAPC

DARD

SYCL

DACL

M41

M42

DSALS

DSARS

M2

M3

RST

M43

DALR

DSALF

DSAC

TO DAC_PCB

LH01

FH01

L 250V

T1.25A

JUMPER (F only)

DY52

11EQS10

DY51

11EQS10

DY54

11EQS10

DY53

11EQS10

JL02

EARTHGND

JL01

EARTH

WF07

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

17P_1MM

JF03

JF50

1

+5VD

2

GND

3

RC5S

4

RC5F

5

LPFSW

JT03

321

OPT

DIG OUT

JT02

GNDGND

1

CAOX

2

47p

3

GND

0.1

CT04

COMMAND INTERFACE

TO FRONT PCB(PY16)

TO RC5 PCB(PF16)

KEY0

KEY1

FDAT

FCLK

FCEN

FRES

DISPLED

3

2

FOR DAC

(BUS LINE)

H2

H2

-VFT

-VFT

H1

H1

+5F

GND

+5VD2

LPFSW

GND

RT01

100

0.1

LT01

DSOF

CT06

4

RT03

75

CT02

51

CT03

2200p

GND

LPS

D822

3AC9

4AC9

PTMON

1k

RY17

GND

11EQS10

D821

11EQS10

D824

11EQS10

D823

11EQS10

M-GND

M-GND

Q821

NJM7808F

+12V

OUTIN

13

2

C822

COM

4700 16V

M-GND M-GND

POWER AND D/A CONVERTOR

PA16 MAIN PCB

TO RC_PCB

LPFSW

MODE1

MUT1

J802

432

MUT2

ACXXX

QY62

47

RY59

Y,GR

2SC2458

VF-GND

ACXXX

1

3

L001

H1

H2

47

RY60

C

2

B

E

4.7V

DY11

-VFT

CY52

100 50V

DSOF

RY57

10k

47k

RY58

-VFT

-26V

PURPLE

AC12V

BLACK

AC12V

WHITE

ORANGE

AC17V

YERROW

GREEN

AC8V

BLUE

BROWN

AC9V

RED

1

2

3

4

5

1

2

3

4

H1

H2

LLM

QY61

Y.GR.

2SA1048

ETC

123

E

C

CY51

VF-GND

VF-GND

AP1

10

AP2

9

H2

7

H1

6

UH04

for F,N,S

B

220 50V

RY51

4.7k

27V

DY61

VF-GND

JH02

for L

1

12

2

for L

3

4

1

212

JH02

FOR F:N:S

TO SERVO

L821

+8V +5V

C823

470 16V

T1.25A L 250V

T800mA L 250V

1

J801

1

2

3

4

5

A-GND

12

F801

F821

1AC12

3AC12

T800mA L 250V

T800mA L 250V

T800mA L 250V

P8M

F852

F851

F831

1AC8

2AC8

1AC8

2AC8

3AC9

4AC9

D854

11EQS10

+15.5V 11V

D853

C851

11EQS10

11EQS10

11EQS10

4700 35V

A-GND

D852

D851

A-GND

C852

-15.5V

4AC17

5AC17

1AC12

3AC12

4AC17

5AC17

D803

11EQS10

D802

11EQS10

D804

11EQS10

D801

11EQS10

GND

D807

11EQS10

D806

11EQS10

D808

11EQS10

GND

D805

11EQS10

Q852

2SD1415A

231

CBE

S

2

G

Q851

2SK246

1

GR

D

3

D858

2.7k

100

R851

C

1

Q853

2SC2240

GR,BL

E

3

6.2V

ARS

C855

47 16V

ARS

A-GND A-GND A-GND

C856

47 16V

6.2V

E

3

GR,BL

Q857

2SA970

1

C

Q855

2SK246

S

GR

2

G

1

D

3

B

100

4700 35V

R852

C

231

Q856

2SB1020A

DN02

11EQS10

DN01

11EQS10

DN04

11EQS10

DN03

11EQS10

GND

4AC17

5AC17

R853

A-GND

3.3k

R858

2

B

3.3k

R854

D856

HZ6L-3

A-GNDA-GNDA-GND

D857

HZ6L-3

R856

3.3k

2

B

R857

3.3k

D859

2.7k

R855

E

DN05

11EQS10

CN01

RN01

100 50V

1k

DN06

4.7V

DN07

RN03

2.2M

RN02

CN02

18k

1 100V

GND

GND

D832

11EQS10

D831

11EQS10

D834

11EQS10

D833

11EQS10

GND

+7.6V

C801

6800 16V

GND GND

+7.6V

C805

6800 16V

GND GND

2.2k

R801

2.2k

R802

GNDGND

TO AUDIO

C857C858

470 16V470 16V

A-GND

TO AUDIO

GND

2SC2458

Y,GR

CN03

4.7 50V

GND

+24V

C831

470 35V

GND

+5VD

Q801

BA05T

13

2

COM

Q802

BA05T

13

2

COM

Q803

PQ15RW11

12

3

4

33k

R803

GND

+12V

-12V

RN04

47k

QN01

C

1

2

B

E

3

2

B

Q831

MJN7812F

2

COM

GND

OUTIN

OUTIN

RN05

10K

C

1

E

3

GND

OUTIN

13

L801

12

C802

3300 6.3V

GND

+5V

+5V

C806C809

3300 6.3V3300 6.3V

GND

C810

470 16V

GND

GND

4.7k

RD22

1

3

QD21

DTC114TS

GND GND GND GND

MODE1

MODE1

24VMT

LMU

E

4.7k

RN07

RN08

QN02

2SC2458

Y,GR

+12V

+12VR

C832

10 63V

GND

POWER AND MUTING

PP16 POWER PCB

TO SERVO

+5A

0.1

C803

GND

TO SERVO

L802

E

4.7k

1

3

GND

DTC114TS

12

L803

12

QD23

2SA970

B

RD23

2

123

C

QN04

B

2SA1048

QN06

+5B

C807

1k

TO FRONT

0.1 0.1

C808

Y.GR

H:MUTE ON

L:MUTE OFF

CN04

NC

GND

TO DAC

1

3

+12V-12V

DN14

NC

)

+5F

5.6VA

GND

MUT1

H:PHANTOM ON

L:NORMAL

RD27

1.5k3.9k

RD24RD25

J851 J852

A-GND GND

JN01 JN02

VF-GND GNDVF-GND

-12V

NC

RN28

MUT2

PTMON

GND

GND

+5.6V

Y,GR

123

C

1k

2

QD22

DTC114TS

LMUT1

LMUT2

PTMDRV

PTMON

TMUT1

MUT2

MUT1

H2

-VFT -VFT

H1

(

2

2SC2458

QD25

2SC2458

Y,GR

123

C

QD24

2SC2878

123

CBE

TMUT1

DN11

DN12

2

QN05

DTC114TS

QD27

2SC2458

123

CBE

QD26

Y,GR

123

CBE

E

B

CD25

47 25V

GND

CD22

100 10V

CD21

10 63V

GND

W851

+12V

1

GND

2

GND

3

-12V

4

WF03

1

LMUT1

LMUT2

2

R-GND

3

PTMDRV

4

PTMON

5

GND

6

GND

7

TMUT1

8

9

MUT2

MUT1

10

VF-GND

11

VF-GND

12

H1

13

-VFT

14

H2

15

CN22

2.2 50V

GND

DN13

CN05

NC

GND

GND

+12VR

RN45

100k

C

RN44

4.7k

2

B

E

1

3

GND

GND

Y,GR

GND

VREF

TO DAC(5.5/3.5V)

1

2

3

4

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

RN22

47k

RN21

22k

RN31

22k

RN32

47k

CN32

2.2 50V

RN46

22k

1

QN42

2SC2458

Y,GR

3

RN47

220k

LLM

CY60

CY61

0.022

0.022

ACXXX

ACXXX

DIG OUT

14 8910111213

NC

1234567

24VMT

QY64

2SA1048

E

QY63

DTC114TS

2

GND

H2

H1

RC5S

LTD

QT01

74HC04

CT01

0.1

33

RT02

GND

GND

QY65

2SA1048

Y.GR

123

E

C

B

RY62

Y.GR

10K

123

C

B

RY61

RY63

10K

10K

GND

1

3

CN11

NC

QN22

2SC2458

Y,GR

QN32

2SC2458

Y,GR

H2

H1

+5VD

+5VD2

LT02

0.1

CT10

CT05

100 25V

GND

GND

DIGO

MUT2

MUT1

3

E

RN26

22k

2

QN23

2SA1048

B

Y.GR

1

C

CN21

NC

LMUT1

RN27

220k

3

E

RN36

22k

2

QN33

2SA1048

B

Y.GR

1

C

CN31

NC

LMUT2

RN37

220k

TO DAC

3.3V

3VDA

CD26

220 25V

+12V-12V

LMUT1

LMUT2

PTMDRV

PTMON

TMUT1

CN12

NC

H2

GNDGND

H1

+12VR

RN25

100k

RN23

22k

C

1

2

B

C

1

E

3

RN33

22k

1

3

PTMDRV

QN21

2SC2458

Y,GR

QN31

2SC2458

Y,GR

3

GND

RN35

100k

C

1

2

B

E

3

GND

2

B

E

GND

+12VR

C

2

B

E

GND

E

3

QN43

2

2SA1048

B

Y.GR

1

C

CN41

NC

87

270

D606

R628

270

D656

R678

3

E

1

C

560

3

E

1

C

560

D707

D708

2

B

R729

D709

D710

D757

D758

2

B

R779

D759

D760

D407

D408

2

B

R429

D409

D410

D457

D458

2

B

R479

D459

D460

D607D610

D608

2

B

2SC2240

33k

R629

D609

D657

D658

2

B

2SC2240

33k

R679

D659

D660

Q713

2SA970

GR,BL

Q714

2SC2240

33k

GR,BL

47

R730

33p

C711

Q763

GR,BL

Q764

2SC2240

33k

GR,BL

47

R780

33p

C761

Q413

2SA970

GR,BL

Q414

2SC2240

33k

GR,BL

47

R430

33p

C411

Q463

2SA970

GR,BL

Q464

2SC2240

33k

GR,BL

47

R480

33p

C461

CURRENT LPF

Q615

2SK170

Q613

2SA970

3

E

GR,BL

2

B

1

C

Q614

1

C

Q616

2SJ74

GR,BL

2

B

3

E

47

R630

33p

560

C611

R631

Q665

2SK170

Q663

2SA970

3

E

GR,BL

2

B

1

C

Q664

1

C

Q666

2SJ74

GR,BL

2

B

3

E

47

R680

33p

560

C661

R681

2SA970

GR,BL

Q715

2SK170

V

1

3

E

G

2

B

1

C

1

C

Q716

2SJ74

2

V

B

G

3

1

E

2SC2240

GR,BL

560

R731

2SA970

GR,BL

Q765

2SK170

V

1

3

E

G

2

B

1

C

1

C

Q766

2SJ74

2

V

B

G

3

1

E

2SC2240

GR,BL

560

R781

2SA970

GR,BL

Q415

2SK170

V

1

3

E

G

2

B

1

C

1

C

Q416

2SJ74

2

V

B

G

3

1

E

2SC2240

GR,BL

560

R431

2SA970

GR,BL

Q465

2SK170

V

1

3

E

G

2

B

1

C

1

C

Q466

2SJ74

2

V

B

G

3

1

E

2SC2240 2SC2240

GR,BL

560

R481

Q618

270

R634

2SA970

E

E

3

GR,BL

Q617

2SA970

GR,BL

D

3

V

1

G

2

S

S

2

V

G

1

3

D

Q620 Q621

2SC2240 2SC2240

GR,BL G R,BL

Q667

2SA970

GR,BL

D

3

V

1

G

2

S

S

V

2

G

1

3

D

Q670

2SC2240

GR,BL

270

R734

3

Q717

1

D

3

2

S

100

R732

100

R733

S

2

3

D

1

Q720

3

270

R736

270

R784

3

Q767

1

D

3

2

S

100

R782

100

R783

S

2

3

D

1

Q770

3

270

R786

270

R434

3

Q417

1

D

3

2

S

100

R432

100

R433

S

2

3

D

1

Q420

3

270

R436

270

R484

3

Q467

1

D

3

2

S

100

R482

100

R483

S

2

3

D

1

Q470

3

270

R486

2

2

B

B

1

C

C

Q619

E

2SA970

GR,BL

2

B

R641

100

120

1

3

270

270

3

1

3

270

2

B

2

2

B

2

2

B

2

2

B

2

C

E

E

C

E

2SA970

B

2SA970

B

2SA970

B

2SA970

B

C

GR,BL

GR,BL

GR,BL

GR,BL

C

C

2

B

E

C

2

2

B

B

E

Q668

2SA970

E

GR,BL

2

2

B

B

C

Q669

E

2SA970

GR,BL

2

B

R691

120

C

C

2

B

E

C

2

2

B

B

E

Q718

270

R735

2SA970

E

3

GR,BL

2

B

1

C

Q719

3

E

2

B

R741

1

120

C

1

C

2

2SC2240

B

GR,BL

3

E

C

1

2

2SC2240

B

GR,BL

3

E

270

R737

Q768

270

R785

2SA970

E

3

GR,BL

2

B

1

C

Q769

3

E

2

B

R791

1

120

C

1

C

2

2SC2240

B

GR,BL

3

E

C

1

2

2SC2240

B

GR,BL

3

E

270

R787

Q418

270

R435

2SA970

E

3

GR,BL

2

B

1

C

Q419

3

E

2

B

R441

1

120

C

1

C

2

2SC2240

B

GR,BL

3

E

C

1

2

2SC2240

B

GR,BL

3

E

270

R437

Q468

270

R485

2SA970

E

3

GR,BL

2

B

1

C

Q469

3

E

2

B

R491

1

120

C

1

C

2

2SC2240

B

GR,BL

3

E

C

1

2

B

GR,BL

3

E

270

R487

R632

100

R633

R636

R684

100

R682

100

R683

R686

E

C

C

E

E

C

C

E

E

C

C

E

E

C

C

E

Q623

2SC2240

1

270

R635

3

1

3

1

1

2SC2240

GR,BL

3

1

3

270

R637

270

R685

3

1

3

1

1

2SC2240

GR,BL

3

1

2SC2240

GR,BL

3

270

R687

C712

R738

Q722

Q721

C762

R788

Q772

Q771

C412

R438

Q422

Q421

C462

R488

Q472

Q471

C

GR,BL

2

B

3

E

D611D612D613

680p

C612

47

R638

C662

R688

2SC2240

GR,BL

2SC2240

GR,BL

2SC2240

GR,BL

2SC2240

GR,BL

Q723

2SA970

GR,BL

Q773

2SA970

GR,BL

Q423

2SA970

GR,BL

Q473

2SA970

GR,BL

2SC2240

680p

47

D711

D712D763

D713

Q724

D761

D762

Q774

D411

D412

D413

Q424

D461

D462

D463

Q474

2

B

2

B

2

B

2

B

2

B

2

B

2

B

2

B

2SA970

GR,BL

Q673

GR,BL

2SA970

GR,BL

0

Q624

3

E

2

B

1

C

1

C

2

B

3

E

D661

D662

D663

0

Q674

3

E

2

B

1

C

1

C

3

E

GND

33

R739

0

33

R740

3

E

ARA

1

C

C714

470 16V

1

C

3

E

33

R789

0

33

R790

3

E

1

C

1

C

3

E

GND

R439

0

33

R440

3

E

ARA

1

C

C414

470 16V

1

C

3

E

33

R489

0

33 33

R490

3

E

1

C

Q622

Q672

Q671

680p

47

680p

47

680p

47

680p

47

+12V

ARA

C613

470 16V

GND

3333

66

R639

R640

GND

C614

470 16V

33 33

R690 R689

ARA

C713

470 16V

66

GND

66

ARA

C413

470 16V

66

GND

66

C617

0

(JUMPER)

C616

220 16V

R643

GND

ARA

LMUT1

-12V

D691

+12V

GND

66

C667

0

R694

(JUMPER)

C666

220 16V

ARS

R693

GND

-12V

+12V

C717

0

(JUMPER)

C716

220 16V

ARS

GND

-12V

+12V-12V

+12V

-12V

+12V

-12V

C416

220 16V

ARS

C466

220 16V

LMUT2

C767

0

(JUMPER)

C766

220 16V

ARS

GND

C417

0

R495

(JUMPWE)

56

10k

R443

GND

LMUT2

D491

GND

C467

0

R494

(JUMPER)

56

ARS

10k

R493

GND

R644

56

10k

12 10

56

10k

12 10

R645

0

(JUMPER)

R646

100

54

3

1

+

-

98

L601

R793

10k

GND

R696

100

R695

0

(JUMPER)

R744

56

+

D791

-

12 10

L701

R794

56

R743

10k

549813

+

TMUT1

549813

J606

W601

1

1

2

2

NC

C618

GND

GND

W901

1

R.CH

GNDGND

GND

GND

J605

NC

C668

GND GNDGND

J706

C718

NC

GND

J705

NC

C768

GND GND

J405

NC

C418

2

-12V

3

GND

4

+12V

5

L.CH

6

TMUT1

J901

PH6P

W602

1

1

2

2

W701

1

1

2

2

GND

W702

1

1

2

2

W401

1

1

2

2

GND

-12V

+12V

J607

1

2

TO FRONT PHONES PWB

J608

1

2

J707

1

2

J708

1

2

J407

1

2

FRONT

L.CH

(WHT)

FRONT

R.CH

(RED)

SURROUND

L.CH

(WHT)

SURROUND

R.CH

(RED)

CENTER

(BLK)

-

L401

GND

SUB

J406

1

1

2

2

NC

C468

GND

GND

J408

W402

1

WOOFER

2

(BLK)

POWR & DAC PCB

PA16

FROM 2/5 PAGE

(DAC BUS)

RST

M41

M3

M2

CD82

NC

3VDA

GND

CD61

100 16V

384/192fs

GND

SYCL

DACL

DALR

DAPCO

DARDO

1514

DARDO

DARD

DAPCO

DAPC

RST

RST

M2

M3

M41

M42

M43

SYCL

DACL

DALR

DARD

DAPC

DSALS

DSARS

DSAC

DSALF

PTMON

J502

6

5

4

3

2

1

GND

J501

6

5

4

3

2

1

GND

ROUT

LOUT

RIN

LIN

DSALS

DSARS

DSALF

PTMON

-12V

+12V

CMIXIN

PTMDRV

M2

M3

M41

M42

M43

SYCL

DACL

DALR

DARD

DAPC

3VDA

PTMON

DSACO

RST

M42

M3

M2

CD80

1000p

3VDA

GND

384/192fs

SYCL

DACL

DALR

DSALS

DSARS

14

RST

M43

M3

M2

CD81

1000p

3VDA

GND

384/192fs

SYCL

DACL

DALR

DSACO

DSALF

14

DAC DATA INPUT FIG

DACK 15

DAD1,3,5 16

SCLK 14

CD60

GND

CD71

100 16V

GND

15

CD41

100 16V

GND

15

6-CHANNEL DAC/LPF (AUDIO)

LDA

1CH/2CH

QD61

CS4397

128

RST VREF

RD62

22k

0.1

CD62

16

14 8910111213

0.1

1234567

RD72

22k

0.1

CD72

16

RD42

22k

0.1

CD42

16

GND

GND

GND

L,CH

2

M4/ADD

3

M3/AD1

4

M2/SC1

5

M0/SDA

6

DGND

7

VD

8

VD

9

DGND

10

MCLK

11

SCLK

12

CMOD

13

SDAT

14

M1

CD=H

128

RST VREF

2

M4/ADD

3

M3/AD1

4

M2/SC1

5

M0/SDA

6

DGND

7

VD

8

VD

9

DGND

10

MCLK

11

SCLK

12

CMOD

13

SDAT

14

M1

128

RST VREF

2

M4/ADD

3

M3/AD1

4

M2/SC1

5

M0/SDA

6

DGND

7

VD

8

VD

9

DGND

10

MCLK

11

SCLK

12

CMOD

13

SDAT

14

M1

M

L

RD64

22k

RD65

22k

QD60

TC74VHC86F

GND

QD71

CS4397

RD74

22k

RD75

22k

PTMDRV

5CH/6CH

QD41

CS4397

RD44

22k

RD45

22k

R,CH

27

FILT+

26

FILT-

25

CMOUT

24

-LO

23

+LO

22

VA

21

GND

20

+RD

19

-RD

18

GND

17

MUTEC

16

C/H

15

MUTE

3CH/4CH

27

FILT+

26

FILT-

25

CMOUT

24

-LO

23

+LO

22

VA

21

GND

20

+RD

19

-RD

18

GND

17

MUTEC

16

C/H

15

MUTE

CMIXIN

D421

GND GND

27

FILT+

26

FILT-

25

CMOUT

24

-LO

23

+LO

22

VA

21

GND

20

+RD

19

-RD

18

GND

17

MUTEC

16

C/H

15

MUTE

GND

GND

12 10

GND

VREF

VREF

0.1

CD68

CD66

0.1

10 25V

CD65

R652

GNDGND

1.2k

R651

GND

1.2k

LDA

CD78

0.1

CD76

10 25V

CD75

R752

1.2k

GND

GND

R751

GND

1.2k

GND

549813

+

CD67

100 10V

CD77

100 10V

0.1

CD69

R601

1.2k

GNDGND

R602

1.2k

5.6VA

0.1

CD64

CD63

100 16V

GND

VREF

0.1

0.1

CD79

R701

1.2k

GND

GND

R702

1.2k

5.6VA

0.1

CD74

CD73

100 16V

GND

CIN

-

L402

CD46

10 25V

CD45

R452

1.2k

GND

R451

1.2k

COUT

VREF

0.1

CD48

0.1

GND

GND

CD47

100 10V

CD43

0.1

CD49

R401

1.2k

GND

GND

R402

1.2k

5.6VA

0.1

CD44

100 16V

GND

LFB

2SK369 GR,BL

R603

560

1.8k

R604

C602

GND

C601

1800p

R605

3.9k

2SK369 GR,BL

R653

560

1.8k

C652

R654

GND

C651

1800p

R655

3.9k

LFB

2SK369 GR,BL

R703

560

1.8k

C702

R704

GND

C701

1800p

R705

3.9k

2SK369 GR,BL

R753

560

R754

1.8k

C752

GND

C751

1800p

R755

3.9k

2SK369 GR,BL

R403

560

C402

1.8k

R404

GND

C401

1800p

R405

3.9k

2SK369 GR,BL

R453

560

C452

R454

1.8k

GND

C451

1800p

R455

3.9k

120

R606

R607

Q601

D

D

7

1

+-

2

G

5

3

S

S

330p

1

C

Q603

2

2SC2240

B

GR,BL

3

E

68

R608

120

R657

R656

Q651

D

D

7

1

+

2

G

5

3

S

S

330p

1

C

Q653

2

2SC2240

B

GR,BL

3 1

E

68

R658

120

R706

R707

Q701

D

D

7

1

+

2

G

5

3

S

S

330p

1

C

Q703

2

2SC2240

B

GR,BL

3

E

68

R708

120

R757

R756

Q751

D

D

7

1

+

2

G

5

3

S

S

330p

1

C

Q753

2

2SC2240

B

GR,BL

3

E

68

R758

120

R407

R406

Q401

D

D

7

1

+

2

G

5

3

S

S

330p

1

C

Q403

2

2SC2240

B

GR,BL

3

E

68

R408

120

R457

R456

Q451

D

D

7

1

+

2

G

5

3

S

S

330p

1

C

Q453

2

2SC2240

B

GR,BL

3

E

68

R458

120

6

G

120

6

G

120

6

G

120

6

G

120

6

G

120

6

G

-

-

-

-

-

2SA970

2SA970

2SA970

2SA970

2SA970

2SA970

GR,BL

GR,BL

GR,BL

GR,BL

GR,BL

GR,BL

Q604

R615

C604

Q654

R665

C654

Q704

R715

C704

Q754

R765

C754

Q404

R415

C404

Q454

R465

C454

DIFFERENCIAL

3

E

2

B

1

C

D601

D604D605

560

R609

5.1k

120p

3

E

2

B

1

C

D651

D654

560

R659

D655

5.1k

120p

3

E

2

B

1

C

D704

D701

560

D705

R709

5.1k

120p

3

E

2

B

1

C

D751

D754

560

D755

R759

5.1k

120p

3

E

2

B

1

C

D404

D401

560

R409

D405

5.1k

120p

3

E

2

B

1

C

D451

D454

560

D455

R459

5.1k

120p

C605

470 16V

Q607

Q608

LIN

Q657

Q658

2SJ74

RIN

Q707

Q708

2SJ74

Q757

Q758

2SJ74

Q407

Q408

2SJ74

CIN

Q457

2SK170

Q458

2SJ74

ARA

3

D

V

1

GND

G

2

S

R622

2.2k

33 33

R614 R613

S

G

1

D

V

D

V

1

G

S

33

R663

33

R664

S

G

1

D

V

D

V

1

G

S

33

R713

33

R714

S

G

1

D

V

D

V

1

G

S

33

R763

33

R764

S

G

1

D

V

D

V

1

G

S

33

R413

33

R414

2

S

G

1

D

V

D

V

1

G

S

33

R463

33

R464

2

S

G

1

D

V

C609

2

LOUT

GND

3

C606

470 16V

ARA

3

2

R672

2.2k

C659

2

ROUT

3

C705

470 16V

3

ARA

GND

2

R723

R722

3.3k

2.2k

C709

1200p

2

3

3

2

R772

R773

3.3k

2.2k

C759

1200p

2

GND

3

C706

470 16V

ARA

C405

470 16V

3

ARA

GND

2

R423

R422

2.2k

3.3k

C409

1200p

COUT

3

3

2

R472

R473

2.2k

3.3k

C459

1200p

ARA

3

GND

C406

470 16V

R623

3.3k

560p

C610

1200p

GND

R673

3.3k

560p

C660

1200p

Q709

2SK389

GR,BL

+

560p

C710

Q711

2SC2240

GND

GR,BL

Q759

2SK389

GR,BL

+

560p

C760

Q761

2SC2240

GND

GR,BL

Q409

2SK389

GR,BL

+

560p

C410

Q411

2SC2240

GND

GR,BL

Q459

2SK389

GR,BL

+

560p

C460

Q461

2SC2240

GND

GR,BL

Q609

2SK389

GR,BL

+-

Q611

2SC2240

GR,BL

Q659

2SK389

GR,BL

+

Q661

2SC2240

GR,BL

R724

2

G

R774

2

G

R424

2

G

R474

2

G

2SK170

Q605

2SA970

GR,BL

3

E

D603 D602

2

B

1

C

Q606

2SC2240

GR,BL

1

C

33k

R610

2

B

3

E

R611

100

2SJ74

47p

560

C603

R612

2SK170

D652

Q655

2SA970

GR,BL

3

E

D653

2

B

1

C

Q656

2SC2240

GR,BL

1

C

33k

R660

2

B

3

E

R661

100

47p

560

C653

R662

2SK170

D702D703

Q705

2SA970

GR,BL

3

E

2

B

1

C

Q706

2SC2240

GR,BL

1

C

33k

R710

2

B

3

E

100

R711

47p

560

C703

R712

2SK170

D752

Q755

2SA970

GR,BL

3

E

D753

2

B

1

C

Q756

2SC2240

GR,BL

1

C

33k

R760

2

B

3

E

100

R761

47p

560

C753

R762

2SK170

D402

Q405

2SA970

GR,BL

3

E

D403

2

B

1

C

Q406

2SC2240

GR,BL

1

C

33k

R410

2

B

3

E

R411

100

47p

560

C403

R412

D452

Q455

2SA970

GR,BL

3

E

D453

2

B

1

C

Q456

2SC2240

GR,BL

1

C

33k

R460

2

B

3

E

100

R461

47p

560

C453

R462

120

R624

D

2

G

S

1

C

3

E

120

R674

D

2

G

S

1

C

3

E

120

D

1

7

3

5

S

1

C

2

B

3

E

68

R726

120

D

1

7

3

5

S

1

C

2

B

3

E

68

R776

120

D

1

7

3

5

S

1

C

2

B

3

E

68

R426

120

D

1

7

3

5

S

1

C

2

B

3

E

68

R476

120

R625

D

7

1

6

G

5

3

S

2

B

68

R626

120

R675

D

1

7

-

6

G

3

5

S

2

B

68

R676

120

R725

Q712

2SA970

GR,BL

D

-

6

G

S

R727

GND

120

R775

Q762

2SA970 2SA970

GR,BL

D

-

6

G

S

R777

GND

120

R425

Q412

2SA970

GR,BL

D

-

6

G

S

R427

GND

120

R475

Q462

2SA970

GR,BL

D

-

6

G

S

R477

GND

2SA970

GND

2SA970

GR,BL

GND

270

D706

R728

270

D756

R778

270

D406

R428

270

D456

R478

GR,BL

Q662

Q612

R627

R677

3

E

1

C

560

3

E

1

C

560

3

E

1

C

560

3

E

1

C

560

9 10

RF AMP AND ACTUTOR CONTROL

J101

25P 1MM

LD

25

LD

LDGND

24

LDGND

VR

23

VR

780n650n

FROM OPTICAL UNIT

PD

VMOD

LD

VR

LDGND

PD

TRK+

TRK-

FCS-

FCS+

A

D

E

C

GND

H

VC

RF

F

G

VCC

B

PD

22

VMOD

21

LD

20

VR

19

LDGND

18

PD

17

TRK+

16

TRK-

15

FCS-

14

FCS+

13

A

12

D

11

E

10

C

9

GND

8

H

7

VC

6

RF

5

F

4

G

3

VCC

2

B

1

A5V

COUT

CF

NJM2115V

R197

DVss0

REDC

8

GRSCOR

100

WDCK

ADIO

GND

VC16

VC16

A3.3DV

Q113

SCOR

100

R196

C4M

SCOR

IGFN

AVssO

GND

R174

33k

1u

A3.3CD

C143

10k

R175

0.01

C186

GND GND

R145

R150

1

C2PO

GFSDSP

GFS

C2PO

CXD3068Q

ASY0

AVddO

R176

100k

0.47

C187

3k

R146

GND GND

3K

C175

22 6.3V

GND

0.1

C173

C174

GND

C183

0.8V-P-P

1.5V-P-PRFAC

R155

330k

MIRR

MIRR

DFCT

21

FOK

22

PWMI

23

LOCK

24

MDP

25

SSTP

26

FSTO

27

DVdd1

28

SFDR

29

SRDR

30

TFDR

31

TRDR

32

FFDR

33

FRDR

34

DVss1

35

TEST

36

TES1

37

VC

38

FE

39

SE

40

TE

R173

10k

0.1

470p

C182

C185

22 6.3V

GND

C164

0.047

A5V

3

2

0.1

C172

XMODON

A5V

0.1

1k

C107

R110

Q103

3

2SB798

2

L103

1

47

VMODE

C109

C108

10 16V

LV_CD

LV_DVD

R119

100

TRK+

TRK-

FCS-

FCS+

E

H

2.5V

F

G

1u

C120

GND GND

H

G

F

E

FJUP_U

FJUP_D

VC25

L102

FB

C121

47 6.3V

H

G

VC25

F

E

VC25

0.1

C122

GND

SRDR

SFDR

GND

L101

FB

C101

C102

22 6.3V

4.7 10V

GNDGND

GND

PD-CD

PD-DVD

P8V

VC16

R103

22k

R104

11k

R107

22k

R108

11k

R224

1k

R225

1k

C220

1016V

GND GND

C201

1016V

10 16V

GND

C126

C127

C128

A

D

C

B

R102R101

22k22k

A5V

2

3

NJM2115V

R106R105

22k22k

NJM2115V

6

5

GND

2200p

C217

0.1

C219

0.1

C202

GNDGND

R202

33k

R207

33k

XMODON

GND

R109

470

0.6V-P-P

2200p

2200p

2200p

C129

2200p

22p

22p

22p

C132

C131

C130

0.1

C103

10 16V

C104

GND GND

8

1

Q102

Q102

7

4

R222

150k

R223

150k

R226

22k

C218

0.068

MN

R245

R201

5.6k

C203

560P

R203

1.8kk

C204

470p

R204

R206

2.2k

FRDR

CD-F

CD-E

VC16

0.068

C216

22k

27k

R221

R219

OPOUT4

OPIN4-

BAIASIN

OPIN1+

OPIN1-

OPOUT1

12345678910111213

R244

MN

R208

5.6k

C205

560p

1.8k

R205

56k

R209

C206

2200p

R210

2.2k

FFDR

TRDR

OPIN3+

OPIN2+

1k

R120

NC

R126

0

0

R121

C125

1000p

VC25

C134

330p

22p

C133

GNDGNDGNDGND

A5V

C135

22 6.3V

GND

1SS300,DAP202U

LV_DVD

SPO

SLMUT

R218

27k

R217

47k

47k

C215

0.01u

R220

C363R378

GND

0.1u

68k

GND

21

22232425262728

GND

FIN

MUTE2

POWVcc

OPOUT3

OPIN3-

OPIN2-

OPOUT2

FIN

GND

MUTE1

POWVcc

GND

0.1

C211

GND

R215

56k

C209

220p

R216

C210

47k

0.1u

C207

220p

56k

R211

R214C208

47k0.1u

R213

56k

1k

R212

TFDR

A5V

226.3V

0.1

C156

C155

GND GND

C153C157

3300p0.1

C154

3300p

1000p

C124

ATON

AT0P

RFDC

1 48

RFSIN

DVDRFP SDFN

2

DVDRFN

3

A2

4

B2

5

C2

6

D2

7

CP

8

CN

9

D

10

C

11

B

12

A

13

CD-D

14

CD-C

15

CD-B

16

CD-A

VC

VPB

CD-E

CD-F

0.1

C136

0.1

C123

GND

VC25

GNDGND

A5V

33

R113

C110

0.1

GND

2SB798

33k

R114

GND GNDGND

A5V

C115

13

SL-

SL+

1617181920

VO4-

VO1-

VO1+ VO4+

14 15

FCS+

FCS-

Q117

BA5981FP

0.1

GND

D107

NC

R234

0

D108

NC

GND

GND

2

D104

LV_CD

SP-

0.1

C214

VO3+

VO3-

VO2-

VO2+

TRK+

TRK-

Q104

L104

C114

DVDLD

47

10 16V

C213C212

1500p

C151

BYP

VPAAPAIN

RFAC

Q101

CXD1881R

VNB

PD-CD

PD-DVD

CDLD

GND

33

R112

3

2

1

C113

10 16V

GND

33

33

R116

R117

Q105

3

2SB798

L105

1

47

33k

R118

C119

10 16V

GND

P8VP8V

47 16V47 16V

MOTOR DRIVER

VC16

Q108

2SK3019

D

D

1

1

3

S

1500p

C148

C150

A5V

0.01

0.1

C152

C147

VNA

ENN

ENP

DIP

DIN

MLPF

MBMPMIRR

LDON

0.033

0.033

150p

C139

C138

C137

A5V

C111

33 10V

DVDLD

CDLD

R111

470

1000p

C112

C116

33 10

R115

470

2

1000p

C118

C117

10 16

GNDGNDGND

SP+

2

2

G

G

3

S

Q107

2SK3019

0.1

0.1

C149

GND

R125

12k 1%

4932

505152535455565758596061626364

RXMEVO

MFV

SDATA

SCKK

Y33

LCP

LON

MNTR

CE

FE

TF

PI

V25

V125

TPH

DFT

KINK

MIN

313029282726252423222120191817

0.047

C140

R123

10M

L=SA, H=CD

GND

AMPSEN

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

GND

AMPSDT

AMPSCK

0.1

C145

GND GND

0.1

C144

AMPMNT

C141

0.1

A5V

GND

GND

C177

0.1

GND

C146C142

AMPMNT

AMPSEN

AMPSDT

AMPSCK

47 6.3V0.1

LDON

A3.3V

A3.3V

FSJP

RFDCO

RFACO

MDPCD

FTMUT

D105

1SS301,DAN202U

2

31

10k

R167

GND

R130

36k

GND

R128

22k

0.3V-P-P

R131

8.2k

VC16

R136 R137

51 51

GND

0.7V-P-P

51

R135

GND

R257

NC

Q118

NJM3414AV

5

6

GND

R260

7

NC

Q106

NJM3414AV

3

1

2

R168

R169

GND

A5V

2

3

Q110

AD8062

6

5

4

GND

VC16

R371

10k

VC16

Q115

TC74LVX4053FT

4.7k

4.7k

87654321

C158

1p

R129

22k

8

Q109

NJM2137V

7

1k

R138

VC16(Refrence)

A3.3DV

R258

NC

1.7

15k 15k

C167

R256 R255

10 16V

R372

100k

R377

220k

1

0.1

C166

CD CLV

R375

GND

NC

0.1

C159

VC16

GND

VC25

A5V

Q118

NJM3414AV

3

2

A5V

Q106

NJM3414AV

C357

100p

D3.3DV

161514131211109

C160

C163

0.1

R139

5

6

R374

C179

0.1

4.7k

R170

FOK_DVD

GNDGND

C161

1p

R133

47k

22 6.3V

GNDGND

2k

GNDGND

GND

R373

NC

C358

Q109

R132

NJM2137V

22k

6

R134

15k

5

4

GND

A5V

GND

8

3

1

2

Q110

AD8062

R140

2k

0.1

C258

C257

8

4

8

4

C359

22 6.3

GND

1

1.70V

R259

0 OHM

0.1

C360

GND

7

68k

NC

NC

7

C162

CD/XDVD

0.1

GND

DFCT

DFCT

FOK

FOK

LOCK

MDPCD

MDPCD

XLIM

SFDR

SRDR

TFDR

TRDR

FFDR

FRDR

C362

4.7U 10V

R171

12k

R172

47k

VC16

RFDC

1k

R141

FOK_DVD

R142

10k

330p

C165

GND

VC16

R152

10k

VC16

GND

Q115

1u

C184

0.047

C181

270p

C180

GND

0.6V-P-P

CD_RFAC

Q111

NJM2115V

5

7

4

6

GND

C170

150p

R153

10k

Q113

NJM2115V

6

7

5

4

4.7k

GND

R154

C171

10 16V

TC74LVX4053FT

XPCK

ASY1

22k

SENS

WFCK

SNSCK

100

R195

SCLK

ATSK

XUGF

WFCK

Q116

FIL0

CLTV

Vss1

RFAC

GND

C188

1500p

10k

R177

C189

0.047

R144R143

330k3.3k

Q112

NJM2903V

3

1

4

2

R149R148

330k3.3k

A5V

C168

0.1

8

5

7

6

Q112

NJM2903V

10k

R156

R160

10k

22 6.3V

R157R158R159

1.5k1.5k10k

R163

GND

XRST

AMUT

DSPSDT

DSPSCK

DSPXLAT

SENS

FILL

R178

10k

XRST

XLAT

SCOK

DATA

MUTE

V16M

VCTL

BLAS

AVDD1

PC0

R179

R180

470k

C190

3.3k 3.3k

220p

C191

C347

22u/10v

A3.3CD GND GND

D3.3DV

4.7k

R147

FOK_DVD

GND

A5V

6

8

5

Q114

NJM2903V

R161

1M

Q114

NJM2903V

2

3

4

GND

R164

1M

C178

0.1

GND

BCK

PCMD

LRCK

DIGO

EXCK

SUBDT

SCSY

SQCK

SQSO

XRST

AMUT

DSPSDT

DSPXLAT

DSPSCK

SENS

SNSCK

WFCK

GFSDSP

C2PO

SCOR

GRSCOR

MIRR

DFCT

FOK

LOCK

XLIM

XMODON

CD/XDVD

FSJP

AMPSEN

AMPSDT

AMPSCK

AMPMNT

LDON

FTMUT

SLMUT

SPO

FJUP_U

FJUP_D

MDPC

J102

6P PH

GND

GND GND

6

5

4

3

2

1

R193

100

Q119

TC7SHU04F

LIMITSW

LIMITSW

SLED-

SLED+

SPINDLE-

SPINDLE+

768FS

GND

0.1

C196

GND

1234567891011121314151617181920

DVdd0

EXCK

80

SBSO

79

SCSY

78

SQCK

77

SQSO

76

XOLT

75

SOCK

74

SOUT

73

XTAO

72

XTAI

71

DVss2

70

R189

XTSL

69

EMPH

68

R188

BCK

67

R187

PCMD

66

R186

LRCK

65

R185

DOUT

64

R184

MD2

63

R183

ASYE

62

DVdd2

61

VPCO

6059585756555453525150494847464544434241

GND

0.1

1M 470k

C192

R181 R182

1u

RFAC

FOR DSD RF AMP

D3.3DV

TZC

A3.3DV

C176

0.1

GND

XFCMP_L

7

A3.3DV

R165 R162

XFCMP_H

1

D3.3CD

D3.3CD

C169

0.1

54

EXCK

1u

C193

XFCMP_L

XFCMP_H

SL-

SL+

SP-

SP+

SUBDT

R192

220

BCK

PCMD

LRCK

DIGO

SQCK

SCSY

SQSO

GND

123

C195

7p

X101

33.8688MHz

C194

10p

TO J105 (6PIN)

EXCK

SUBDT

SCSY

SQCK

SQSO

XRST

AMUT

DSPSDT

DSPXLAT

DSPSCK

SENS

SNSCK

WFCK

GFSDSP

C2PO

SCOR

GRSCOR

MIRR

DFCT

FOK

LOCK

XLIM

XMODON

CD/XDVD

FSJP

AMPSEN

AMPSDT

AMPSCK

AMPMNT

LDON

FTMUT

SLMUT

SPO

FJUP_U

FJUP_D

TZC

TZC

XFCMP_L

XFCMP_H

XLIM

SL-

SL+

SP-

SP+

R191

100

R190

100

10k

100

100

100

100

10k

10k

C197

22 6.3V

GND

RFAC

0.1

4.7k

C200

R151

GND

10k 10k

PV16 SERVO (1/3)

1211

DVD DECORD CONTROL MPU

DECMNT2 DECMNT2

JIT5V

GND

TZC

R274

R275

R276

0.1

GND

R251

R252

R253

SPO

J103

9P (MP-WRITE)

GND

GND

GND

FOK

DSPXLAT

DSPSDT

DSPSCK

SENS

SQSO

SNSCK

SQCK

AMPMNT

SCSY

GFSDSP

MIRR

FJUP_D

FJUP_U

XFCMP_L

XFCMP_H

XLIM

SENS

XMODON

SQSO

LDON

SNSCK

FTMUT

SQCK

SLMUT

FSJP

AMPMNT

XRST

CD/XDVD

LOCK

AMPSDT

SCSY

AMPSCK

GFSDSP

AMPSEN

TZC

MIRR

AMUT

FJUP_D

FJUP_U

XFCMP_L

XLIM

XFCMP_H

10k

10k

10k

C270

22 6.3V

FTMUT

10k

SLMUT

10k

AMUT

10k

9

8

7

6

5

4

3

2

1

M3.3V

0.1

C313

GND

768FS

MDPC

DFCT

GRSCOR

EXCK

SUBDT

SCOR

WFCK

C2PO

PCMD

LRCK

M3.3V

GND

P17

PJ0

GND

SPO

BCK

FOK

DSPXLAT

DSPSDT

DSPSCK

SENS

SQSO

SNSCK

SQCK

AMPMNT

SCSY

GFSDSP

MIRR

FJUP_D

FJUP_U

XFCMP_L

XFCMP_H

BUS LINE

(A TO A)

XLIM

XMODON

LDON

FTMUT

SLMUT

FSJP

XRST

CD/XDVD

LOCK

AMPSDT

AMPSCK

AMPSEN

AMUT

M3.3V

C269

M3.3V

768FS

MDPC

DFCT

GRSCOR

EXCK

SUBDT

SCOR

WFCK

C2PO

BCK

PCMD

LRCK

M3.3V

MPR1

MPR2

PCRXD

(CONNECTOR)

TO FEATUR UP

MPR3

PCTXD

PV16 SERVO (2/3)

R271

4.7k

9.1k

NC

R272

C223

GND

M3.3V

22K

R282

1

2

-ATT

3

Q138

DTC144EUA

GND

MSCK

MSDTI

MSDTO

XMSLAT

MSRADY

DSPSDT

DSPSCK

0.1

C268

MSCK

MSDT0

MSDT1

XMSLAT

MSDEDY

DSPDT0

DSPSCK

SENS

51525354555657585960616263646566676869707172737475

SQSO

SNSCK

SQCK

VSS

JITIN

AMPMNT

-ATT

P17

PJ0

PJ1

GFSDSP

C2PO

MIRR

DECMNT2

EJUP_D

EJUP_U

AVss

AVref

AVdd

XFCMP_L

XFCMP_H

XLIM

XTCLS

XTOPN

EDCERR

BUEEMP

EPDA

EPCL

PCRXD

PCTXD

7677787980818283848586878889909192939495969798

M3.3V

EDCERR

M3.3V

XTOPN

XTCLS

FSJP

EPCL

EPDA

R277

10k

FSJP

DSPXLAT

DSPXLAT

SYNCERR

XDECWR

Vgg

XDECWR

XDECRD

0

R273

GND

XTAL

EXTAL

CXPQ71000

XDECRDNCVDD

C271

GND

Vss

Q125

GND

X103

20MHZ

3

12

XRESET

DRVIRQ

DRVCLK

DRVRDY1

DRVCLK

DRVIRQ

XRESET

XDRVRDY

VSSA0A1A2A3A4A5A6A7

0.1

DECA0

DECA1

DECA2

C264

22 6.3V

DRVTX

DRVTXD

DECA3

GNDGND

XRESET

DRVRX

DECA4

C263

1

Q111

NJM2115V

R267

XRESET

DRVRXD

DECA5

0.1

8

22k

GFSDEC

FOK

DECA6

1

FOK

3

GND

DECMNT1

DECA7

A5V

3

2

Q129

DTC144EUA

REQST

SFPG

SPEG

HDRQ/REQST

XMODON

LDON

XMODON

LDON

R263

1k

R266

6.8k

2

SEEK

26272829303132333435363738394041424344454647484950

SEEK

XRDCINT

XDECINT

XDECSEL

MBHLD(NC)

CD/XDVD

EJCT-

99

100

0.1

C262

GND

R283

10k

PE4

TZCIN

AMPSEN

AMPSCK

AMPSDT

LOCK

XRST

SMUT

AMUT

SLMUT

FTMUT

EJCT+

R261

33k

GND

1

2

DRVRST

PE3

D7

D6

D5

D4

D3

D2

D1

D0

VSS

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25

GND

M3.3V

R278

1k22k1k

R262R264R265

3

DTA144EUA

4.7k

XINT0

VC16

C261

0.1

GND

A5V

Q128

D3.3DI

XRST

SMUT

M3.3V

47k

R254

XINT1

XINT0

DECD7

DECD6

DECD5

DECD4

DECD3

DECD2

DECD1

DECD0

XDECSEL

4.7k

R279

XINT1

AMPSEN

AMPSCK

AMPSDT

LOCK

CD/XDVD

AMUT

SLMUT

FTMUT

FROM Q110

(RF AMP)

RFAC

VC16

A3.3DV

MDPC

R311

47K

22k 22k

R310 R309

C301

1000p

GNDGND

C303

0.47

0.047

C302

GND

R314

8.2k

22k

R315

DFCT

GRSCOR

EXCK

SUBDT

SCOR

WFCK

GND

DBCK

DDAT

DLRC

XRESET

C297

0.1

D5VDV

D3.3DV

TZC

C2PO

BCK

PCMD

LRCK

XRST

RFAC

R308

NC

R307

100

C291

C348

22u/10v

GND

0.1

C296

GND

1k

1M

R312

R313

C304

R316

GND

DECD0

DECD1

DECD2

DECD3

DECD4

133

134

GND

135

136

137

138

139

140

141

142

143

0.1

144

145

146

147

148

149

150

151

152

10k

153

154

155

156

157

158

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173

174

175

176

0.1

0.1

C198

C199

GND

GND

D3.3DVD5VDV

1u

C290

0

GND

R317

132

131

FDO

PDHVC0

GNDA2

GNDA1

SP0

VC2

MDIN2

MDIN1

VCCA1

CLVS

VSS

MDSOUT

VDD

MDPOUT

DFCT/LINK

GSCOR

EXCK

SBIN

VSS

SCOR

WFCK

VDD5

XRCI

VDDS

C2PO

VDD

DBCK

BCLK

DDAT

MDAT

VSS

DLRC

LRCK

XRST

IFS0

IFS1

XTAI

VSS

XLT2

XLT1

Vdd

D0

D1

D2

D3

D4

D5D6VssD7A0

123456789

GND

DECD5

DECD6

R306

470k

0.01

130

129

PDO

VCCA2

DECD7

C287

4700p

C288

R302

NC

10k

C289

R304R305

0.01

10k150k

R303

0.1

C293

128

127

126

LPF1

LPF2

VCCA3

VddA1Vdd5VA2A3A4A5A6A7

DECA0

DECA1

A3.3DV

220p

C292

2.2k

GND

5.6k

R301

125

124

123

122

121

120

VC1

119

LPF5

GNDA3

GNDA4

VCOIN

VCOR1

VCCA4

1011121314151617181920212223242526272829303132

GND GND GND

DECA2

DECA3

DECA4

DECA5

DECA6

DECA7

118

VCCA5

VSS

XWAIT

R295

100k

4.3k

C284

C285

0.01

0.47

0.1

NC

GND

R298 R297

C286

117

116

115

114

113

112

RFIN

AFS2

AFS1

RFDCC

DASY1

XWAIT

XRQ

XWR

XCS

XINT0

XDECRD

XDECWR

XDECSEL

XINT0

XINT1

R296

111

GNDA5

CXD1882R

XINT1

10k

DASYO

Q124

VDD

110

VDD

XHRS/(NC)

0.1

C283

109

108

APEO

HDB7/DAT7

VDT07

MD15

0.1

C280

107

106

105

104

103

102

MDBF

HDB6/DAT6

GND