Page 1

960L

Multi-Channel

Digital Effects System

Service

Manual

Page 2

960L Multi-Channel Digital Effects System Service Manual

Copyright © 1999 Lexicon, Inc.

All Rights Reserved

Lexicon Inc. ● 3 Oak Park ● Bedford, MA 01730-1441 ● Tel (781) 280-0300 ● Customer Service Fax (781) 280-0499

Lexicon Part # 070-14826 Rev 0

Printed in the United States of America

Page 3

960L Multi-Channel Digital Effects System Service Manual

Page 4

960L Multi-Channel Digital Effects System Service Manual

Page 5

Lexicon

Table of Contents

Chapter 1 Reference Documents, Required Equipment............................. 1-1

Reference Documents............................................................................................................................. 1-1

Required Equipment................................................................................................................................ 1-1

Tools .................................................................................................................................................... 1-1

Test Equipment.................................................................................................................................... 1-1

Chapter 2 General Information ................................................................... 2-1

Periodic Maintenance .............................................................................................................................. 2-1

Ordering Parts ......................................................................................................................................... 2-1

Returning Units to Lexicon for Service .................................................................................................... 2-1

Chapter 3 Specifications............................................................................. 3-1

960L Mainframe....................................................................................................................................... 3-1

LARC2 User Interface ............................................................................................................................. 3-3

Chapter 4 Performance Verification............................................................ 4-1

Initial Inspection and checkout: ............................................................................................................... 4-1

960L Mainframe: .................................................................................................................................. 4-1

LARC2 controller:................................................................................................................................. 4-1

Cables:................................................................................................................................................. 4-1

Power Supplies: ................................................................................................................................... 4-1

Audio/Functional Tests Setup*: ............................................................................................................... 4-5

I/O Gain Tests ......................................................................................................................................... 4-6

Analog In to Analog Out Audio Gain Test: ........................................................................................... 4-6

Analog In To Digital Out Audio Gain Test: ........................................................................................... 4-6

Digital Input to Analog Output Gain Test:............................................................................................. 4-6

Frequency Response: ............................................................................................................................. 4-6

Analog In to Analog Out Frequency Response Test:........................................................................... 4-6

Analog In To Digital Out Frequency Response Test:........................................................................... 4-6

Digital In To Analog Out Frequency Response Test:........................................................................... 4-7

THD+N Measurement:............................................................................................................................. 4-7

Analog In to Analog Out THD+N Test:................................................................................................. 4-7

Analog In to Digital Out THD+N Test: .................................................................................................. 4-7

Digital In to Analog Out THD+N Test: .................................................................................................. 4-7

Crosstalk Tests:....................................................................................................................................... 4-8

Analog In to Digital Out Crosstalk Test: ............................................................................................... 4-8

Digital In to Analog Out Crosstalk Test: ............................................................................................... 4-8

Dynamic Range Tests: ............................................................................................................................ 4-8

Analog In to Analog Out Dynamic Range Test: ................................................................................... 4-8

Analog In to Digital Out Dynamic Range Test:..................................................................................... 4-8

Digital In To Analog Out Dynamic Range Test: ................................................................................... 4-8

Functional Tests: ..................................................................................................................................... 4-9

Midi Tests:............................................................................................................................................ 4-9

Listening Test:...................................................................................................................................... 4-9

Lexicon Audio Precision ATE Summary ............................................................................................ 4-11

Chapter 5 Service Notes............................................................................. 5-1

Motherboard - lithium battery................................................................................................................... 5-1

Power Supplies........................................................................................................................................ 5-1

Symptoms of possible power supply failures ....................................................................................... 5-1

Larc2 Meter Display LED Handling ......................................................................................................... 5-1

Removal and Replacement of Larc2 Piezo Transducer .......................................................................... 5-1

For units with the transducer soldered (Rev 5 PCB and up):............................................................... 5-1

For units with the transducer epoxied (Rev 4 PCB and below):........................................................... 5-1

Female RS-422 Wraparound Plug: ......................................................................................................... 5-3

Male RS-422 Wraparound Plug............................................................................................................... 5-4

Page 6

960L Multi-Channel Digital Effects System Service Manual

Chapter 6 Troubleshooting ......................................................................... 6-1

Diagnostics...............................................................................................................................................6-1

Overview...............................................................................................................................................6-1

960L Diagnostics: .................................................................................................................................6-1

960L Diagnostic User Interface: ...........................................................................................................6-2

Audio I/O Algorithm (8 In - 8 Out): ........................................................................................................6-3

Functional Diagnostic Test Scripts .......................................................................................................6-3

960L Setup for Functional Diagnostic Tests .........................................................................................6-4

960L Power On Diagnostic Descriptions: .............................................................................................6-4

960L Functional Diagnostic Descriptions:.............................................................................................6-5

960L Troubleshooting Tools: ..............................................................................................................6-16

Global Commands: .............................................................................................................................6-17

LISTING of RESIDENT SCRIPTS ......................................................................................................6-18

LARC2 DIAGNOSTICS ..........................................................................................................................6-24

Debug Port:.........................................................................................................................................6-25

POWER ON DIAGNOSTICS:.................................................................................................................6-26

Power On Diagnostics Sequence: ......................................................................................................6-26

Power On Self Tests:..........................................................................................................................6-28

INTERACTIVE DIAGNOSTICS:.............................................................................................................6-33

Self Test:.............................................................................................................................................6-34

LCD Test:............................................................................................................................................6-35

Key Test:.............................................................................................................................................6-35

LED Test:............................................................................................................................................6-36

Joystick Test: ......................................................................................................................................6-38

Fader/Motor Test: ...............................................................................................................................6-39

Lexicon Test: ......................................................................................................................................6-39

Memory Test:......................................................................................................................................6-40

Repetitive Test:...................................................................................................................................6-40

Diagnostics Suite: ...............................................................................................................................6-41

OPTION BOARD Menu:.........................................................................................................................6-42

MISCELLANEOUS TESTS:................................................................................................................6-44

Program Flash Data Checking:...........................................................................................................6-46

Chapter 7 Theory of Operation ................................................................... 7-1

NLX Backplane.........................................................................................................................................7-1

Overview...............................................................................................................................................7-1

Circuit Description.................................................................................................................................7-1

NLX Interface (Sheet1) .........................................................................................................................7-2

PCI Interface (Sheets 2, 3, 4) ...............................................................................................................7-2

IO Connectors (Sheet 5).......................................................................................................................7-2

Miscellaneous Connectors (Sheet 6)....................................................................................................7-2

IOBUS & Power Connectors (Sheet 7).................................................................................................7-2

DSPBUS Connectors (Sheet 8, 9)........................................................................................................7-3

I/O Backplane...........................................................................................................................................7-4

Introduction ...........................................................................................................................................7-4

Overview...............................................................................................................................................7-4

Circuit Description.................................................................................................................................7-5

I/O Clock card - Input/Output and Clock Generator card..........................................................................7-7

Midi Interface ........................................................................................................................................7-7

Ttl Wordclock Interface .........................................................................................................................7-7

Larc2 Interface......................................................................................................................................7-8

CPLD Logic...........................................................................................................................................7-8

Control Interface .................................................................................................................................7-10

Register Descriptions..........................................................................................................................7-10

Access ................................................................................................................................................7-10

Description .............................................................................................................................................7-10

Page 7

Lexicon

Board ID ................................................................................................................................................ 7-10

Interface revision ................................................................................................................................... 7-10

Preview Word Clock Select ................................................................................................................... 7-10

Clock Bus Interface............................................................................................................................ 7-10

Clock Selection .................................................................................................................................. 7-11

PLL Support ....................................................................................................................................... 7-11

Phase-Locked Loop ........................................................................................................................... 7-11

PLL Detailed Description ................................................................................................................... 7-12

Power Supply..................................................................................................................................... 7-14

Analog Input card .................................................................................................................................. 7-15

Overview. ........................................................................................................................................... 7-15

Input Buffer ........................................................................................................................................ 7-15

Common Mode Performance............................................................................................................. 7-15

A/D Converter .................................................................................................................................... 7-16

Signal Polarity .................................................................................................................................... 7-16

System Interface Logic ...................................................................................................................... 7-16

Control Interface ................................................................................................................................ 7-16

Register Descriptions......................................................................................................................... 7-16

Clock Interface ................................................................................................................................... 7-17

Digital Audio Interface........................................................................................................................ 7-17

Pin Descriptions ................................................................................................................................. 7-18

Power Supply..................................................................................................................................... 7-20

Analog Output card................................................................................................................................ 7-21

Overview............................................................................................................................................ 7-21

Circuit Description.............................................................................................................................. 7-21

D/A Converter .................................................................................................................................... 7-21

Filter................................................................................................................................................... 7-22

Output Driver...................................................................................................................................... 7-22

Mute Relay......................................................................................................................................... 7-22

Signal Polarity .................................................................................................................................... 7-23

System Interface Logic ...................................................................................................................... 7-23

Control Interface ................................................................................................................................ 7-23

Register Descriptions......................................................................................................................... 7-23

Clock Interface ................................................................................................................................... 7-23

Digital Audio Interface........................................................................................................................ 7-24

Power Supply..................................................................................................................................... 7-26

AES card ............................................................................................................................................... 7-28

Introduction ........................................................................................................................................ 7-28

Overview............................................................................................................................................ 7-28

Circuit Description.............................................................................................................................. 7-29

Startup Sequence .............................................................................................................................. 7-29

AES card Memory Map...................................................................................................................... 7-29

FPGA Control Register ...................................................................................................................... 7-30

FPGA Lock Register .......................................................................................................................... 7-30

Locking to the AES Input Word Clock................................................................................................ 7-31

Octal Select Register ......................................................................................................................... 7-31

Local Loopback Mode:....................................................................................................................... 7-32

Reverb card ........................................................................................................................................... 7-32

Introduction ........................................................................................................................................ 7-32

Overview............................................................................................................................................ 7-32

Circuit Description.............................................................................................................................. 7-33

Startup Sequence .............................................................................................................................. 7-36

DSP 56301 Expansion Port Memory Map ......................................................................................... 7-37

Larc2...................................................................................................................................................... 7-39

General Description ........................................................................................................................... 7-39

Central Processor (sheet 1) ............................................................................................................... 7-40

Page 8

960L Multi-Channel Digital Effects System Service Manual

Main Memory (sheet 2).......................................................................................................................7-41

Peripheral I/O Subsystems .................................................................................................................7-44

Power Supply......................................................................................................................................7-49

Register Summary ..............................................................................................................................7-50

Meter Bridge Module ..........................................................................................................................7-53

Chapter 8 - Parts List.................................................................................. 8-1

CHASSIS/MECHANICAL .........................................................................................................................8-1

I/O BPL ASSY,960L .................................................................................................................................8-2

I/O CLK BD ASSY,960L ...........................................................................................................................8-3

AIN BD ASSY,960L..................................................................................................................................8-4

AOUT BD ASSY,960L..............................................................................................................................8-5

AES BD ASSY,960L.................................................................................................................................8-7

RVB BD ASSY,960L ................................................................................................................................8-8

NLX CPU BD ASSY .................................................................................................................................8-9

NLX BPL EXT BD ASSY,960L .................................................................................................................8-9

I/O BPL EXT BD ASSY,960L ...................................................................................................................8-9

LARC2:...................................................................................................................................................8-10

CHASSIS/MECHANICAL: ..................................................................................................................8-10

SHIP MAT’L/PACKAGING/MISCELLANEOUS ..................................................................................8-14

POWER CORDS....................................................................................................................................8-14

SHIP MAT’L/PACKAGING/MISCELLANEOUS......................................................................................8-14

Spare Assemblies ..................................................................................................................................8-15

Chapter 9 Schematics and Drawings ......................................................... 9-1

Schematics:..............................................................................................................................................9-1

Drawings: .................................................................................................................................................9-1

Page 9

Lexicon

Chapter 1 Refe rence Documents, Required Equipment

Reference Documents

960L Owner's Manual - Lexicon P/N 070-14353 or latest revision

Software Release Notice, 960L - Lexicon P/N 070-14354 or latest revision

Required Equipment

Tools

The following is a minimum suggested technician's tool kit required for performing disassembly, assembly

and repairs:

• Clean, antistatic, well lit work area.

• (1) #1 Phillips tip screwdriver

• (1) #2 Phillips tip screwdriver

• Small pair chain nose pliers

• Solder: 63/37 - Tin/Lead Alloy composition, low residue, no-clean solder.

• Magnification glasses and lamps

• SMT Soldering / Desoldering bench-top repair station

Test Equipment

The following is a minimum suggested equipment list required for performing the proof of performance and

diagnostic tests.

• Digital Multi-Meter ( DMM )

• Amplifier with speakers or headphones.

• Cables: (dependent on your signal source)

• low distortion analog oscillator

• analog distortion analyzer and level meter with Audio Band-Pass filter

• 100 MHz oscilloscope

• digital distortion analyzer & digital function generator (e.g. Stanford Research Systems Model DS360 or

Audio Precision System 1 with DSP Option/System 2).

• Variable AC Power Supply with voltage and current meters,(known as a Variac), adjustable from 0 -

140VAC, and 0-2Amps.BK Precision 1653 or equivalent.

• 100/120 to 220/240 VAC step-up transformer

• LARC2 to 960L Interface Cable, Lexicon P/N 680-03525.

• (2) Male D9 RS422 Wraparound Connectors (see Chapter 5 for spec/drawing)

• (2) audio cables XLR male on one end with appropriate connectors on the opposite end for connection

to the low distortion oscillator.

• (2) audio cables XLR female on one end with appropriate connectors on the opposite end for

connection to a headphone amplifier.

• Stereo Headphones

• XLR male to XLR female audio cables, maximum length 1 meter.

• XLR male to XLR female audio cables, maximum length 2 meters.

• BNC to BNC Cables, maximum length 5 meters.

• XLR male to XLR female 110 ohm AES digital audio cables, maximum length 1 meter.

• (8) XLR male to XLR female 110 ohm AES digital audio cables, maximum length 2 meters.

• (2) 5 Pin DIN to 5 Pin DIN Cables, maximum length 3 meters, (MIDI Cables), Hosa Technology P/N

MID-305 or equivalent.

• Lexicon 960L PCI Extender cards P/N 023-14297

• Lexicon 960L I/O Extender cards P/N 023-14426

• 960L 120V Power Cord, Lexicon P/N 680-09149

1-1

Page 10

960L Multi-Channel Digital Effects System Service Manual

• IBM compatible personal computer capable of running Windows 95/98, minimum 200mHz Pentium

Processor, 128MB memory, 4GB Hard Disk Drive, SVGA Monitor, Video card w/ 4MB memory, Mouse,

17” monitor, Windows 95 Keyboard, CD-ROM Drive, 3.5" High Density Floppy Disk Drive, and Windows

95/98 Operating System.

• 6' DE-9 Female to DE-9 Female RS-232 Serial Cable.

• DE-9 Male to DE-9 Male RS-232 Null-Modem Adapter

• Female RS-422 Wraparound Plug (see Chapter 5 for spec/drawing)

• PS/2 Keyboard (or IBM 102/104-key keyboard with PS/2 adapter)

• Optional:

• High Current Continuity Tester, 10A, 100 milliohm. Associated Research 5030DT or

equivalent.

• (1) 15” Computer Monitor

• (1) PS/2 Mouse

• LARC2 Option Board (Rev.1), Lexicon P/N 023-14310.

• 32MB PCMCIA FLASH Memory Card, PCMCIA 2.1 Compliant, 5 Volt, (LINEAR Flash

PC Card, Centennial P/N FL32M-20-11736-J5).

• External Power Supply, 12VDC @ 3A, 5.5 mm O.D., 2.5 mm I.D. barrel connector, with

the positive voltage on center contact. PowDec Model WI60-12V or equivalent.

Page 11

Lexicon

Chapter 2 Gene ral Information

Periodic Maintenance

Under normal conditions the 960L system requires minimal maintenance. Use a soft, lint-free cloth slightly

dampened with warm water and mild detergent to clean the exterior surfaces.

Do not use alcohol, benzene or acetone-based cleaners or any strong commercial cleaners. Avoid

using abrasive materials such as steel wool or metal polish. It the unit is exposed to a dusty environment, a

vacuum or low-pressure blower may be used to remove dust from the unit's exterior.

The 960L's cooling fan, located on the right side of the mainframe (facing the front) has a removable filter. It

should be cleaned periodically with water and mild detergent, rinsed thoroughly, dried and reinstalled.

Ordering Parts

When ordering parts, identify each part by type, price and Lexicon Part Number. Replacement parts can be

ordered from:

LEXICON, INC.

3 Oak Park

Bedford, MA 01730-1441

Telephone: 781-280-0300; Fax: 781-280-0499; email: csupport@lexicon.com

ATTN: Customer Service

Returning Units to Lexicon for Service

Before returning a unit for warranty or non-warranty service, consult with Lexicon Customer

Service to determine the extent of the problem and to obtain Return Authorization. No equipment

will be accepted without Return Authorization from Lexicon.

If Lexicon recommends that a 960L be returned for repair and you choose to return the unit to Lexicon for

service, Lexicon assumes no responsibility for the unit in shipment from the customer to the factory,

whether the unit is in or out of warranty. All shipments must be well packed (using the original packing

materials if possible), properly insured and consigned, prepaid, to a reliable shipping agent.

When returning a unit for service, please include the following information:

• Name

• Company Name

• Street Address

• City, State, Zip Code, Country

• Telephone number (including area code and country code where applicable)

• Serial Number of the unit

• Description of the problem

• Preferred method of return shipment

• Return Authorization #, on both the inside and outside of the package

Please enclose a brief note describing any conversations with Lexicon personnel (indicate the name of the

person at Lexicon) and give the name and telephone daytime number of the person directly responsible for

maintaining the unit.

Do not include accessories such as manuals, audio cables, footswitches, etc. with the unit, unless

specifically requested to do so by Lexicon Customer Service personnel.

2-1

Page 12

Page 13

Chapter 3 Spec ifications

960L Mainframe

Analog Input

Connectors Eight, Female XLR

Impedance 50Kohm, balanced

Level (for 0 dbFS) +24dBu

Freq Response @48K 20Hz-20KHz, ±1db

Freq Response @96K 20Hz-40KHz, ±1db

A/D Conversion 24 bits

128x oversampled

A/D Dyn Range >110 dB (20-20kHz)

THD <.002%

CMRR >50db

Crosstalk @ 1Khz < -100dB

Analog Output

Connectors Eight, Male XLR

Impedance 50 Ohm, balanced

Level (at 0 dbFS) +24dBu

Freq Response @48K 20Hz-20Khz, ±1db

Freq Response @96K 20Hz-40Khz, ±1db

D/A Conversion 24 bits

8x oversampled @ 44.1/48Khz

4x oversampled @ 88.2/96Khz

Lexicon

D/A Dyn Range >110 dB (20-20kHz)

THD <.002%

Crosstalk @ 1Khz < -100dB

A/A Performance

Freq Response @48K 20Hz-20Khz, ±1db

Freq Response @96K 20Hz-40Khz, ±1db

Dyn Range >107 dB (20-20kHz)

THD <.002%

Digital Audio IO

Connectors Four Male XLR Outputs

Four Female XLR Inputs

Format AES/EBU

Word Size 24 bits

Sample Rates

Internal 44.1/48/88.2/96KHz

Accuracy within ±10ppm

External 44.1/48/88.2/96KHz

Lock Range ±1%

Group Delays (milliseconds)

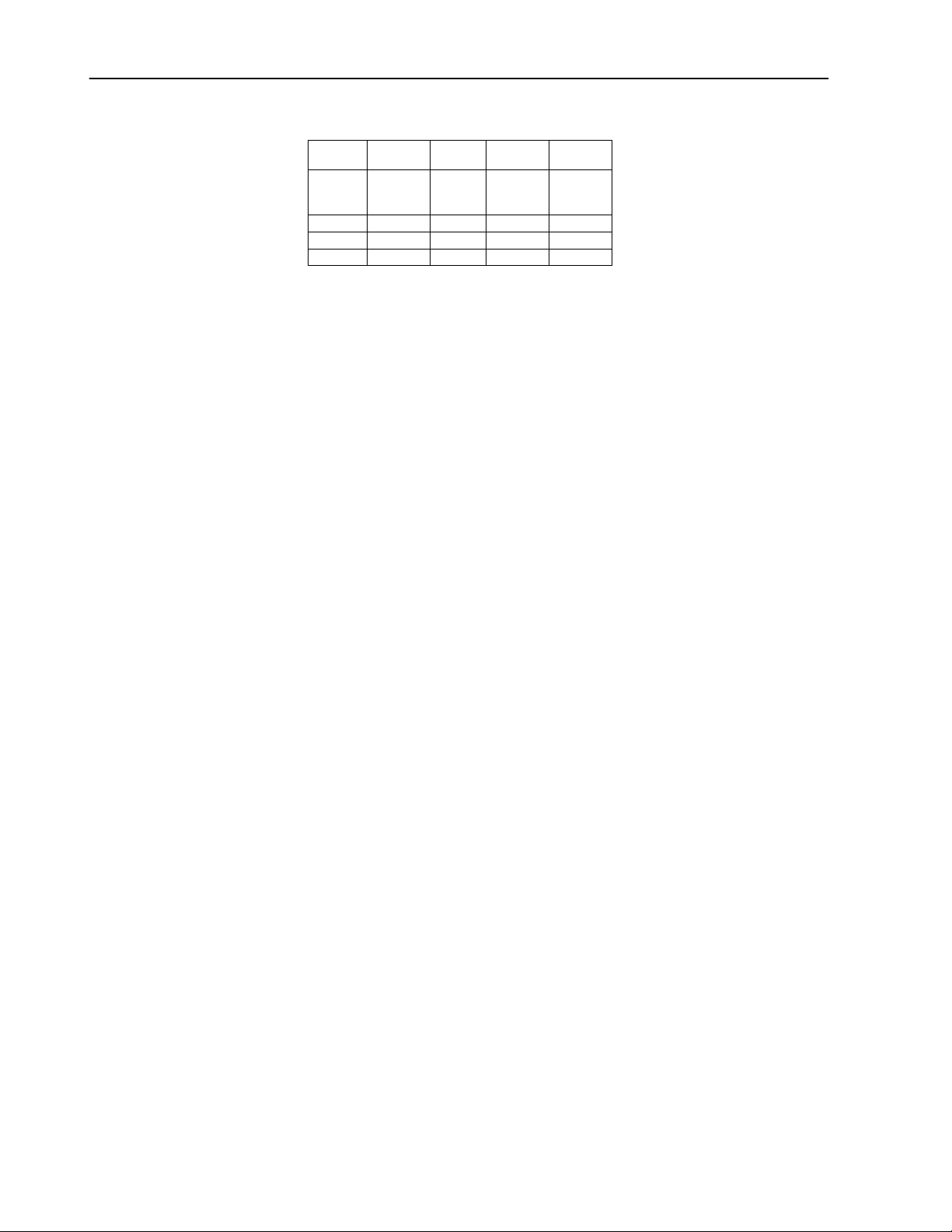

3-1

Page 14

960L Multi-Channel Digital Effects System Service Manual

A/D

A/A 2.42 2.23 1.80 1.66

D/A 1.54 1.42 1.35 1.25

D/D 0.54 0.50 0.36 0.33

Synchronization

TTL Word Clock Input *

75 Ohm, BNC

self-terminating loopthru

TTL Word Clock Output * Low Z, BNC

(* Falling edge marks start of frame)

Clock Jitter

Intrinsic Exceeds AES3 Amendment 1

Jitter Gain Exceeds AES3 Amendment 1

Control Interfaces

LARC2 Ports 2

MIDI ** In/Out/Thru

(**supports program change)

Algorithms

Ambience (48K Stereo & Surround)

Chamber (48K Stereo & Surround)

Plate (48K Stereo & Surround)

Reverse (48K Stereo & Surround)

Random Hall

(48/96K Stereo & 48K Surround)

Ambient Chamber (48K Surround)

44.1

Khz

1.44 1.33 0.81 0.74

48

Khz

88.2

Khz

96

Khz

Standard Hardware Configuration

DSP/CPU Card Compartment

One System CPU Card

One Reverb DSP Card

Two Spare DSP card slots

One MIDI Card

IO Card Compartment

One Analog Input Card

One Analog Output Card

One AES/EBU Digital IO Card

One IO/Clock Card

One Spare IO Card slot

Storage Media

Hard Disk

3.5” Floppy Disk Drive

CD-ROM Drive

Reverb Card Configurations

48K

Page 15

Stereo Machines Four

2in x 5out Machines Two

5in x 5out Machines Two

96K

Stereo Machines Two

2in x 5out Machines One

5in x 5out Machines One

Internal Hard Disk Storage

Factory Programs 240

User Registers 1000

Removable 3.5” Floppy Disk Storage

User Registers 100

Power

Requirements***

100-120 / 220-240 VAC

50-60Hz, 300W max

(some mainframes will have a mains voltage selection

switch; if there is no selector switch, it will operate

on mains voltages from 100-240 VAC)

Connector 3-pin IEC

Lexicon

Dimensions

Rack Units 4U

Size 19.0" L x 7.0" W x 17.4" H

(483mm x 178mm x 442mm)

Weight

Regulatory Approvals

FCC Class A

CE EN55103-1, EN55103-2

UL UL1419

cUL C22.2

TUV EN60065

Environment

Operating 10 to 40 °C

Storage -30 to 70 °C

Humidity 95% max, non-condensing

LARC2 User Interface

Display

Type Passive Matrix LCD

Resolution 640x240

Colors 256

Backlight Fluorescent

Contrast HW controlled (rear panel)

Brightness SW controlled

35 lbs

LED Meter Bridge

Configuration 8 channels x 3 levels

Levels

-60dBFS (Signal)

3-3

Page 16

960L Multi-Channel Digital Effects System Service Manual

-6dBFS

-0.5dBFS (Overload)

Control Surface

Faders 8

60mm throw, motorized, touch sensitive

Joystick Two axis

Dedicated Function Keys 29 (12 backlit)

Soft Buttons 8

Connectors

960L 9-pin D-sub

Aux. PS/2 Keyboard 6-pin Mini-DIN

Ext. Power concentric, 2.5mm

Operating Distance

With power from 960L up to100 feet

With Ext. Power up to1000 feet

Power

Requirements 12 VDC, 3 A (max)

Dimensions

Size 12.7” L x 8.25” W x 5.0” H

(323mm x 210mm x 127mm)

Weight 4 lbs

Regulatory Approvals

FCC Class A

CE EN55103-1, EN55103-2

TUV EN60065

Environment

Operating 5 to 40 °C

Storage -30 to 70 °C

Humidity 95% max, non-condensing

Page 17

Lexicon

Chapter 4 Perfo rmance Verification

This section describes the tests and procedures for verification of the operation of the 960L with LARC2

and the integrity of its analog and digital audio signal paths.

Initial Inspection and checkout:

Note: Please refer to the chassis assembly drawing in the Schematics and Drawings section later in this

manual.

960L Mainframe:

1. Remove the top and bottom covers of the 960L

2. Inspect the entire unit for obvious signs of physical damage.

3. Unscrew the front panel screws and fold down the front panel.

4. Verify that the main processor board, midi card, and reverb cards are seated properly and are held

down with screws. Also verify that all cable connections to the midi card, main processor board, and

backplanes are in place.

5. At the back of the unit, in the power supply section, verify that all connections are firmly seated to the

backplane. Verify all ribbon cables are firmly seated to the I/O backplane and that Pin 1 of all ribbon

cables (identified by a red stripe) are at the top of the connectors.

6. Carefully turn the unit over.

7. Verify that all of the drives are properly secured in place. Verify all ribbon cables and power cables to

these devices are firmly seated.

8. Verify all ribbon cables to both the NLX and I/O backplanes are firmly seated.

9. On the back panel of the 960L make sure all cards are tightly screwed in place. Inspect all connectors

for wear or breaks that might cause intermittent operation.

LARC2 controller:

1. Inspect the entire unit for obvious signs of physical damage such as cracked or broken plastic

housings.

2. Verify display is not cracked or shattered.

3. Verify all sliders move up and down smoothly and do not bind.

4. Verify the joystick also has a smooth, fluid movement.

5. Depress all the buttons to insure non-stick operation.

Cables:

Inspect both the 960L power cable and LARC cable for physical damage or excessive wear.

Power Supplies:

Note: It is important that the power supply be tested while fully connected in the 960L mainframe

to insure proper voltage readings.

System Current Draw Tests:

1. For 100/120V operation, verify that the voltage selection switch* on the back of the 960L is set to the

115 Volt setting.

2. Set the voltage level on the Variable AC power supply down to 0 volts then turn it ON.

3. Plug the 960L into the variable AC power supply and switch the main power switch on the rear panel to

the ON position.

4. Slowly bring the variable AC power supply voltage up to 120 Volts. The current draw will vary from

between approximately 0.5A and 1.5A.

5. At 120V verify that the current draw is approximately 0.75 A and that the Green Power On LED above

the Front Panel power switch is on.

6. Power off.

4-1

Page 18

960L Multi-Channel Digital Effects System Service Manual

7. For 220/240V operation, verify that the voltage selection switch* on the back of the 960L is set to the

230 Volt setting.

8. Follow steps 2 through 6 above. Note - the current draw should be approximately one-half of that listed

in the steps above dependant upon the accuracy of the current meter. It should not be higher.

*Note: Different manufacturer's power supplies have been specified for the 960L. There are some slight

mechanical differences in some of these power supplies. Some units will have a power supply with a

voltage setting switch as noted above. Some units will have a power supply that does not have a voltage

selection switch. The AC voltage input will be automatically sensed by the supply. Be sure to inspect the

unit in case of the need to "switch" for the appropriate AC input voltage.

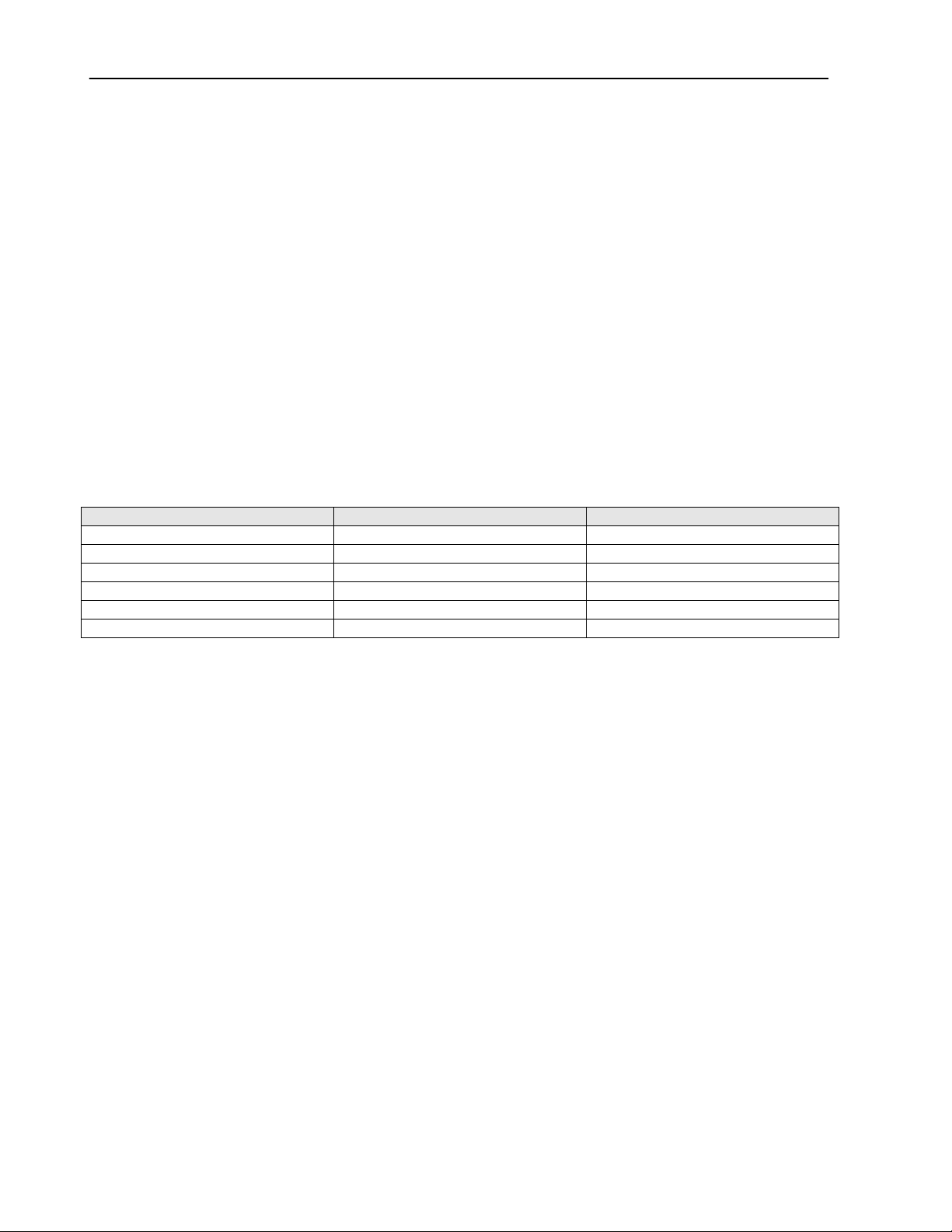

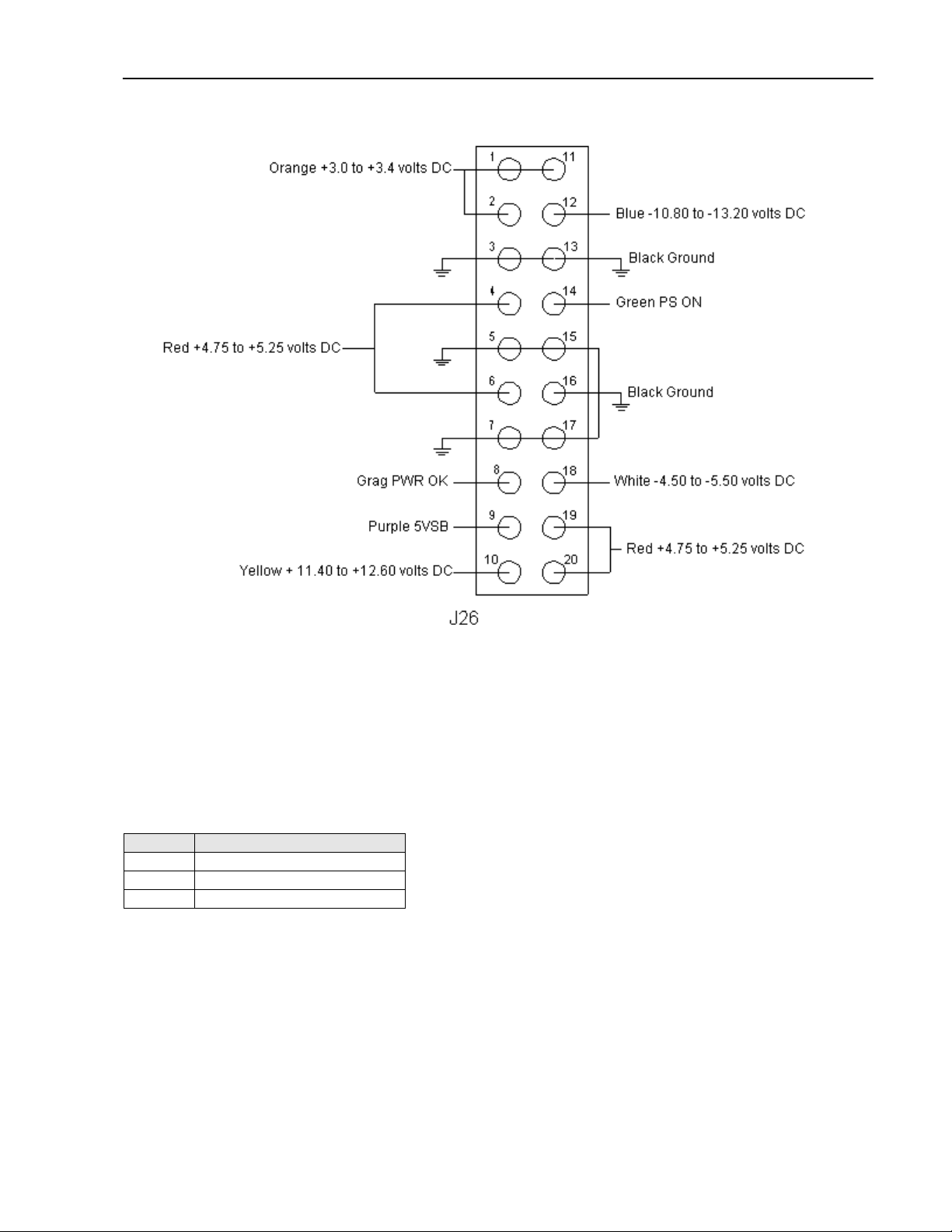

Main Power Supply Connector J26 Voltage Level Tests:

1. Remove the top and bottom covers of the 960L.

2. Remove all DSP cards and the Midi card from the card cage in the front section of the 960L and place

them in static shielding bags.

3. With the front of the 960L facing you, locate the solder side of connector J26 on the Left side of the NLX

backplane.

4. Clip the ground lead of the DMM meter to the chassis for ground reference.

5. Take the Plus lead and using the table below verify the voltage levels indicated on J26.

Pin # Wire Color Voltage Range

1 Orange + 3 volts DC +.4/-0

4 Red + 5 volts DC ±.25

10 Yellow + 12. volts DC ±.6

12 Blue -12 volts DC ±1.2

13 Black Ground

18 White - 5 volts DC ±.5

4-2

Page 19

Lexicon

NOTE: The following voltage tests are to insure that the connectors are plugged into the NLX

backplane and that power is being properly distributed to the other devices. This may also help in

determining whether or not the devices themselves are defective.

To gain easier access to the test points called out in the following tests, you will want to turn over the

mainframe of the 960L so the bottom faces up or rest it on its side.

All power connections to the backplane, Hard Drive, CD ROM Drive and 3.5" Floppy Drive have the same

colored wiring code.

Color Voltage Range

Yellow + 12. volts DC ±.6

Black Ground

Red + 5 volts DC ±.25

NLX Backplane Connector J9 Voltage Level Test:

1. Locate the power connector J9 on the rear backplane.

2. Measure the voltages on the connector with your DMM leads.

3. Place the DMM ground lead on the Black wire connector and the DMM plus lead on the Yellow wire

connector and verify the voltage is +12 VDC (± .6 VDC).

4. Place the DMM ground lead on the Black wire connector and the DMM plus lead on the Red wire

connector and verify the voltage is + 5 VDC (± .25 VDC).

3.5" Floppy Drive Connector:

1. Locate the power connector on the back of 3.5” Floppy Drive.

2. With your DMM leads measure the voltages on the connector.

4-3

Page 20

960L Multi-Channel Digital Effects System Service Manual

3. Place the DMM ground lead on the Black wire connector and the DMM plus lead on the Yellow wire

connector and verify the is +12 VDC (± .6 VDC).

4. Place the DMM ground lead on the Black wire connector and the DMM plus lead on the Red wire

connector and verify the voltage is +5 VDC (± .25 VDC).

CD-ROM Drive Connector:

1. Locate the power connector on the back of CD-ROM drive.

2. With your DMM leads measure the voltages on the connector.

3. Place the DMM ground lead on the Black wire connector and the DMM plus lead on the Yellow wire

connector and verify the voltage is +12 VDC (± .6 VDC).

4. Place the DMM ground lead on the Black wire connector and the DMM plus lead on the Red wire

connector and verify the voltage is +5 VDC (± .25 VDC).

Hard Drive Connector:

1. Locate the power connector on the back of Hard Drive.

2. With your DMM leads measure the voltages on the connector.

3. Place the DMM ground lead on the Black wire connector and the DMM plus lead on the Yellow wire

connector and verify the voltage is +12 VDC (± .6 VDC).

4. Place the DMM ground lead on the Black wire connector and the DMM plus lead on the Red wire

connector and verify the voltage is +5 VDC (± .25 VDC).

For the following voltage tests, an I/O extender card (part # 023-14426) will be needed to bring the cards

out of the mainframe in order to gain access to the test points called out in the following tests.

Analog Output Card Voltage Test:

The supplies being tested on this card will be the +/-12 VSUP, and the +5VD provided by the main supply

via the backplane and voltages +5VD, 6.6V, +/-18V, 24V, and 36V created on the card.

1. Before powering on the 960L for this test, remove the Analog Output card from the rear of the chassis.

2. Insert the I/O extender card and install the Analog Output card into the extender card.

3. Power on the 960L.

4. For your ground reference locate test point marked GND to the Left of U3.

5. At the back right hand corner of the card locate the –12V-test point just below FB2. Verify the voltage is

-12VDC ±1.2VDC.

6. Next locate in the test point marked +12V just below FB3. Verify the voltage is +12VDC ±.6VDC.

7. Locate the +5VD voltage test point left side of the card just above U6. Verify the voltage is +5VDC

±.25VDC.

8. Locate the +5 VA voltage test point just below U3 between D8 and D9. Verify the voltage is +5VDC

±.25VDC.

9. Locate the + VB voltage test point on the right side of the card just to the left of C15. Verify the voltage

is between + 6.27 and + 6.93 VDC.

10. Locate the +/- VCC voltage test points on the right side of the card. +VCC is just to the right of C206

and –VCC is just to the right of that under FB54. Verify the voltage to be +17.50VCC and -17.50VCC

+/- 1.0 volt each.

Analog Input Card Voltage Test:

The supplies being tested on this card will be the +/- 12 VSUP provided by the main supply via the

backplane and the +5VD, and +5VA created on the card.

1. Before powering on the 960L for this test, remove the Analog Input card from the rear of the chassis.

2. Insert the I/O extender card and install the Analog Input card into the extender card.

3. Power on the 960L.

4. For your ground reference, locate test point marked GNDA just above D7.

4-4

Page 21

Lexicon

5. At the back right hand corner of the card locate the FB1. Measure the +12 volts here and verify the

voltage is +12VDC ± .6VDC.

6. Next locate FB2. Measure the -12 volts here and verify the voltage is -12VDC ± 1.2VDC.

7. Using the same ground reference measure pin 3 of U3 (+ 5 VA). Verify the voltage is +5VDC ± .25VDC.

8. Locate the + 5 VD test point on the left side of the card just to the left of U1. Using the ground reference

marked GNDD2 just to the right of the + 5 VD verify the voltage is +5VDC ± .25VDC.

AES Input /Output Card Voltage Test:

The supply being tested on this card will be the +5VD provided by the main supply via the backplane.

1. Before powering on the 960L remove the AES Input/Output card from the rear of the chassis.

2. Insert the I/O extender card and install the AES Input/Output card into the extender card.

3. Power on the 960L.

4. Locate the ground reference test point marked GND1 just above U3.

5. Locate test point marked + 5 V to the right of the GND1 test point.

6. With the DMM verify the voltage is +5VDC ± .25VDC.

Input/Output Clock Generator Card Voltage Test:

The supplies being tested on this card will be the +/-12 VSUP and the +5VD provided by the main supply

via the backplane.

1. Before powering on the 960L remove the Input/Output Clock card from the rear of the chassis.

2. Insert the I/O extender card and install the Input/Output Clock card into the extender card.

3. Power on the 960L.

4. For a ground reference locate test point marked GND2 on the right side of the card.

5. Locate the ferrite bead FB3 at the back of the card just to the right of the connector and measure the

+12 volts. Verify the voltage is +12VDC ± .6VDC.

6. FB4 is next to FB3. Measure the -12 volts here. Verify the voltage -12VDC ± 1.2VDC.

7. Locate the ground reference test point marked GND1 on the left side of the card just to the left of U1.

8. Locate test point marked + 5 V just below U1.

9. With the DMM verify the voltage is +5VDC ± .25VDC.

Audio/Functional Tests Setup*:

1. Power on the 960L with the main power switch and wait for the Power on diagnostics cycle to finish.

2. On the Larc2, press the Control Button. The Control Mode screen will appear at this time.

3. Press the #1 button to set the clock source to Internal. Note: for any "Digital In" tests, you will need to

return to this screen and select Source #3, AES/EBU.

4. Press the Right arrow button to jump to the Rate page.

5. Press the #2 button to select a 48kHz sample rate.

6. Press the Soft button labeled CONFIG under the display.

7. Press the #4 button. This will highlight the 1-8in/8out setup for Diagnostics.

8. Press the Edit button, the screen will then display the Edit Mode page

9. Press the Soft button labeled Algorithm, the display will then read Algorithms Options Enabled.

10. Press the Soft button labeled Select, a small box will open with 1-OctalThru stated.

11. Press the #1 button, then the Enter button this will load the Diagnostic 1-8in/8out setup.

12. Press Control and then the ►key to highlight Inputs.

13. Press the + key to toggle the state to AN (Analog). Note: for any "Digital In" tests, you will need to

return to this screen and toggle the state to AES (Digital).

14. Set the distortion analyzer to measure VRMS.

*Note: The following tests should also be performed at the 44.1kHz and 96kHz sample rates. Prior to

performing the following tests at each sample rate, you must perform the previous set-up procedure

substituting the indicated sample rate in step 5.

4-5

Page 22

960L Multi-Channel Digital Effects System Service Manual

I/O Gain Tests

Analog In to Analog Out Audio Gain Test:

1. Connect a balanced XLR audio cable between the low distortion oscillator and the 960L # 1 Audio

Input.

2. Connect a balanced XLR audio cable between the 960L # 1 Audio Output and the distortion analyzer.

3. Apply a 1kHz sinewave @ 9.75 VRMS.

4. Verify the output level to be 10 VRMS ±1.5V.

5. Repeat the test on the remaining Input /Outputs 2-8.

Analog In To Digital Out Audio Gain Test:

1. Connect a balanced XLR audio cable between the low distortion oscillator and the 960L # 1 Audio

Input.

2. Connect a balanced XLR audio cable between the 960L # 1-2 AES Output and the digital distortion

analyzer.

3. Apply a 1kHz sinewave @ 10.94 VRMS.

4. Verify the output level to be -1 dBFS ± 1dBFS.

5. Move the audio input cable to the # 2 Input and repeat the test.

6. Repeat the test on the remaining Input /Outputs pairs 3-4, 5-6, and 7-8.

Digital Input to Analog Output Gain Test:

Note: Change the Clock Source and Inputs to AES - see Audio/Functional Tests Setup.

1. Connect a balanced XLR audio cable between the digital function generator and the 960L # 1-2 AES

Input.

2. Connect a balanced XLR audio cable between the 960L # 1 Audio Output and the distortion analyzer.

3. Apply a 1kHz sinewave @ -1 dBFS.

4. Verify the output level to be 11.5 VRMS ±1.5V.

5. Move the audio output cable to the # 2 Output and repeat the test.

6. Repeat the test on the remaining Input /Outputs pairs 3-4, 5-6, and 7-8.

Frequency Response:

Analog In to Analog Out Frequency Response Test:

Note: Change the Clock Source to Internal and Inputs to Analog - see Audio/Functional Tests Setup.

1. Disable all filters on the distortion analyzer.

2. Connect a balanced XLR audio cable between the low distortion oscillator and the 960L # 1 Audio

Input.

3. Connect a balanced XLR audio cable between the 960L # 1 Audio Output and the distortion analyzer.

4. Apply a 1kHz sinewave @ 2.45 VRMS.

5. Set the Analyzer for a 0dB reference (@1khz)

6. Sweep the oscillator from 20Hz to 20kHz and verify the level is +/- 1dBr throughout the sweep.

7. Repeat the test on the remaining Input /Outputs 2-8.

Analog In To Digital Out Frequency Response Test:

1. Disable all filters on the digital distortion analyzer.

2. Connect a balanced XLR audio cable between the low distortion oscillator and the 960L # 1 Audio

Input.

3. Connect a balanced XLR audio cable between the 960L # 1-2 AES Output and the digital distortion

analyzer.

4. Apply a 1kHz sinewave @ 6.90 VRMS.

5. Set the Analyzer for a 0dB reference (@1khz)

6. Sweep the oscillator from 20Hz to 20kHz and verify the level is +/- 1dBr throughout the sweep.

4-6

Page 23

Lexicon

7. Move the Audio Input cable to Audio Input #2 and repeat the test.

8. Repeat the test on the remaining Input /Outputs pairs 3-4,5-6, and 7-8.

Digital In To Analog Out Frequency Response Test:

Note: Change the Clock Source and Inputs to AES - see Audio/Functional Tests Setup.

1. Disable all Filters on the distortion analyzer

2. Connect a balanced XLR audio cable between the digital function generator and the 960L # 1-2 AES

Input.

3. Connect a balanced XLR audio cable between the 960L # 1 Audio Output and the distortion analyzer.

4. Apply a 1kHz sinewave @ -1 dBFS.

5. Set the Analyzer for a 0dB reference (@1khz)

6. Sweep the oscillator from 20Hz to 20kHz and verify the level is +/- 1dBr throughout the sweep.

7. Move the audio output cable to the # 2 Output and repeat the test.

8. Repeat the test for the remaining Input /Outputs pairs 3-4,5-6, and 7-8.

THD+N Measurement:

Analog In to Analog Out THD+N Test:

Note: Change the Clock Source to Internal and Inputs to Analog - see Audio/Functional Tests Setup.

1. Connect a balanced XLR audio cable between the low distortion oscillator and the 960L # 1 Audio

Input.

2. Connect a balanced XLR audio cable between the 960L # 1 Audio Output and the distortion analyzer.

3. Apply a 997Hz sinewave @ 9.75 VRMS.

4. Set the distortion analyzer to measure THD+N.

5. Enable the Audio Band Pass filter on the distortion analyzer.

6. Verify the output THD+N on the Analyzer is < 0.002%.

7. Repeat the rest for the remaining Input /Outputs 2-8.

Analog In to Digital Out THD+N Test:

1. Connect a balanced XLR audio cable between the low distortion oscillator and the 960L # 1 Audio

Input.

2. Connect a balanced XLR audio cable between the 960L # 1-2 AES Output and the digital distortion

analyzer.

3. Apply a 997Hz sinewave @ 10.94 VRMS.

4. Set the distortion analyzer to measure THD+N.

5. Enable the Audio Band Pass filter on the distortion analyzer.

6. Verify the output THD+N on the Analyzer is < -94 dBFS.

7. Move the audio input cable to the # 2 Input and repeat the test.

8. Repeat the test for the remaining Input /Outputs pairs 3-4,5-6, and 7-8.

Digital In to Analog Out THD+N Test:

Note: Change the Clock Source and Inputs to AES - see Audio/Functional Tests Setup.

1. Connect a balanced XLR audio cable between the digital function generator and the 960L # 1-2 AES

Input.

2. Connect a balanced XLR audio cable between the 960L # 1 Audio Output and the distortion analyzer.

3. Apply a 997Hz sinewave @ -1 dBFS.

4. Set the distortion analyzer to measure THD+N.

5. Enable the Audio Band Pass filter on the distortion analyzer.

6. Verify the output THD+N on the Analyzer is < -94 dBFS.

7. Move the audio output cable to the # 2 Output and repeat the test.

8. Repeat the test for the remaining Input /Outputs pairs 3-4,5-6, and 7-8.

4-7

Page 24

960L Multi-Channel Digital Effects System Service Manual

Crosstalk Tests:

Analog In to Digital Out Crosstalk Test:

1. Connect a balanced XLR audio cable between the low distortion oscillator and the 960L # 1 Audio

Input.

2. Connect a balanced XLR audio cable between the 960L # 1-2 AES Output and the digital distortion

analyzer.

3. Apply a 997Hz sinewave @ 10.94 VRMS.

4. Enable the Audio Band Pass filter on the distortion analyzer.

5. Verify the level on AES Output #2 to be < -100 dB throughout the sweep.

6. Move the Input cable to the # 2 Input and repeat the test for AES Output #1.

7. Repeat the test for the remaining Input /Outputs pairs 3-4, 5-6, and 7-8.

Digital In to Analog Out Crosstalk Test:

Note: Change the Clock Source and Inputs to AES - see Audio/Functional Tests Setup.

1. Connect a balanced XLR audio cable between the digital function generator and the 960L # 1-2 AES

Input.

2. Connect a balanced XLR audio cable between the 960L # 2 Audio Output and the distortion analyzer.

3. Apply a 997Hz sinewave @ -1 dBFS.

4. Enable the Audio Band Pass filter on the distortion analyzer.

5. Verify the level on Output #2 to be < -100 dB throughout the sweep.

6. Move the audio output cable to the # 1 Output and repeat the test.

7. Repeat the test for the remaining Input /Outputs pairs 3-4,5-6, and 7-8.

Dynamic Range Tests:

Analog In to Analog Out Dynamic Range Test:

Note: Change the Clock Source to Internal and Inputs to Analog - see Audio/Functional Tests Setup.

1. Connect a balanced XLR audio cable between the low distortion oscillator and the 960L # 1 Audio

Input.

2. Connect a balanced XLR audio cable between the 960L # 1 Audio Output and the distortion analyzer.

3. Apply a 997Hz sinewave @ 24dBu.

4. Set the distortion analyzer for a 0dB reference.

5. Enable the Audio Band Pass filters on the distortion analyzer.

6. Lower the input by 60dB to -36dBu.

7. Verify the THD+N at the # 1 output to be <-110 dBr.

8. Repeat the test for the remaining Input/Outputs 2-8.

Analog In to Digital Out Dynamic Range Test:

1. Connect a balanced XLR audio cable between the low distortion oscillator and the 960L # 1 Audio

Input.

2. Connect a balanced XLR audio cable between the 960L # 1-2 AES Output and the digital distortion

analyzer.

3. Apply a 997Hz sinewave @ 24dBu.

4. Set the distortion analyzer for a 0dB reference.

5. Lower the input by 60 dB to -36dBu.

6. Verify the THD+N level at the # 1-2 AES Output to be <-110 dBFS.

7. Move the audio input cable to the # 2 Input and repeat the test.

8. Repeat the test for the remaining Input /Outputs pairs 3-4, 5-6, and 7-8.

Digital In To Analog Out Dynamic Range Test:

Note: Change the Clock Source and Inputs to AES - see Audio/Functional Tests Setup.

4-8

Page 25

Lexicon

1. Connect a balanced XLR audio cable between the digital function generator and the 960L # 1-2 AES

Input.

2. Connect a balanced XLR audio cable between the 960L # 1 Audio Output and the distortion analyzer.

3. Apply a 997Hz sinewave @ -1 dBFS.

4. Set the distortion analyzer for a 0dB reference.

5. Enable the Audio Band Pass filter on the distortion analyzer.

6. Lower the input by 60dB to -61dBFS.

7. Verify the THD+N at the # 1 output to be < -110 dB.

8. Move the audio output cable to the # 2 Output and repeat the test.

9. Repeat the test for the remaining Input /Outputs pairs 3-4, 5-6, and 7-8.

Functional Tests:

Midi Tests:

Setup

1. This test will require 1 Midi cable. The cable is connected to the Midi In and Out connector on the back

of the 960L creating a loop that the internal diagnostics requires to perform the test.

2. The 960L must first be placed into Diagnostic mode. This is done by powering on the 960L's main

power switch on the rear panel, then immediately pressing and holding down the Program and Machine

buttons on the LARC2 for 2 seconds. When the LARC2 displays "Requesting Menu Mode …", the

buttons can be released. The display will take about two minutes, then it should state the following:

960L Boot Menu - Version ### Speed ### BIOS date ##/##/##

[Note: ### are placeholders for actual values which may vary]

1) Run 960L

2) Update 960L Software

3) Update LARC2 Boot ROM

4) Update LARC2

5) 960L Diagnostics

Can’t lock CD Drive: Access is denied

3. Press the # 5 button to enter the Diagnostics.

4. The display will scroll through some information then settle. At the bottom of the display it will read,

Press 0 for a list of tests.

5. Press the # 9 on the LARC2 then the Enter button.

6. If the Midi circuitry is good the display will read

MIDI Test : Passed

All test PASSED

If it fails then the display will read

MIDI Test : Failed : No data received

One or more tests failed

7. To exit Diagnostics, power off, then power on the unit.

Listening Test:

Setup:

1. Connect the two audio XLR male cables from the low distortion oscillator to Analog Inputs marked 1

and 2 on the back of the 960L.

2. Connect the two audio XLR female cables from the Headphones Amplifier to the Analog Outputs

marked 1 and 2 on the back of the 906L.

3. Set the oscillator to 220Hz @ 2.5VRMS.

4-9

Page 26

960L Multi-Channel Digital Effects System Service Manual

4. Turn the volume control on the Headphone Amplifier completely counter-clockwise, and plug in the

stereo headphones.

5. Power on the 960L.

6. Configure the 960L as follows. Control Mode to Stereo, Program load Bank 12 Halls, then load program

#1 Large Halls.

Verify Clean Audio:

1. Put on Headphones

2. Press the Edit button on the LARC2 make sure the Mix/Wet slider is set to Wet

3. Slowly increase the volume on the Headphone Amplifier unit it’s at a comfortable listening level.

4. Slowly sweep the oscillator across the audio frequency band and verify that no pops, clicks, static,

hash, and breakup in the audio.

5. Move the input and output cables to the next machine pair of the 960L (3,4) (5,6) and (7,8).

6. Repeat the test for each paired output.

Shock Test:

1. While still listening with the headphones. Lift each corner to the 960L a few inches off the workbench

and drop.

2. Verify there is no audio break up.

3. Inspect all components after to be sure nothing was loosened by this test.

4-10

Page 27

Lexicon Audio Precision ATE Summary

m

u

Lexicon

SOURCE ANALYZER 960L Setup

Analog or Digital Generator Bal/ Gnd/ Analog or Digital Analyzer Upper Lower Clock Sample Audio

Test Name Left Right Freq (hz) Z-out Unbal Float Level Measure Typ Read Limit Limit Filter Imp. Band. Configuration Algorithm Source Rate Source

Mute Test Analog Generator Analog Analyzer

Analog Generator Digital Analyzer

A-D 48 kHz Internal Sa

960lmute n/a n/a n/a n/a n/a n/a dBu Level -999 -100 -2000 n/a 100k <10 - >500k n/a n/a n/a n/a n/a

a-d 48k gain 23dBu 23dBu 997 40 Bal Gnd dBFS Level -1 0 -2 n/a n/a <10 - Fs/2 8 In 8 Out OctalThru Internal 48000 Analog

a-d 48k freq resp 19dBu 19dBu 20-20k 40 Bal Gnd dBr Level 0 1 -1 n/a n/a <10 - Fs/2 8 In 8 Out OctalThru Internal 48000 Analog

a-d 48k thd+n 23dBu 23dBu 20-20k 40 Bal Gnd dBFS THD+N -110 -94 -120 n/a n/a <10Hz->20kHz LP 8 In 8 Out OctalThru Internal 48000 Analog

A-D 44.1 kHz Internal Sample Rate Tests

A-D 96 kHz Internal Sample Rate Tests

a-d 44k gain 23dBu 23dBu 997 40 Bal Gnd dBFS Level -1 -0.5 -1.5 n/a n/a <10 - Fs/2 8 In 8 Out OctalThru Internal 44100 Analog

a-d 44k thd+n 23dBU 23dBu 20-20k 40 Bal Gnd dBFS Level -110 -94 -120 n/a n/a <10Hz->20kHz LP 8 In 8 Out OctalThru Internal 44100 Analog

a-d 44k dyn-rng -36dBu -36dBu 20-20k 40 Bal Gnd dBFS THD+N -113 -110 -130 n/a n/a <10Hz->20kHz LP 8 In 8 Out OctalThru Internal 44100 Analog

a-d 48k dyn-rng -36dBu -36dBu 20-20k 40 Bal Gnd dBFS THD+N -113 -110 -130 n/a n/a <10Hz->20kHz LP 8 In 8 Out OctalThru Internal 48000 Analog

a-d 48k cmrr 23dBu 23dBu 997 40 CMTST Gnd dBu Level -70 -50 -100 n/a n/a <10Hz->20kHz LP 8 In 8 Out OctalThru Internal 48000 Analog

a-d 48k xtalk 23dBu 23dBu 997 40 Bal Gnd dBu Level -140 -100 -150 n/a n/a <10 - Fs/2 8 In 8 Out OctalThru Internal 48000 Analog

a-d 96k gain 23dBu 23dBu 997 40 Bal Gnd dBFS Level -1 -0.5 -1.5 n/a n/a <10 - Fs/2 8 In 8 Out OctalThru Internal 96000 Analog

Digital Generator Analog Analyzer

D-A 48 kHz AES Sample

a-d 96k freq resp 19dBu 19dBu 20-40k 40 Bal Gnd dBr Level 0 1 -1 n/a n/a <10 - Fs/2 8 In 8 Out OctalThru Internal 96000 Analog

a-d 96k thd+n 23dBu 23dBu 20-20k 40 Bal Gnd dBFS THD+N -110 -94 -120 n/a n/a <10Hz->20kHz LP 8 In 8 Out OctalThru Internal 96000 Analog

a-d 96k dyn-rng -36dBu -36dBu 20-20k 40 Bal Gnd dBFS THD+N -113 -110 -130 n/a n/a <10Hz->20kHz LP 8 In 8 Out OctalThru Internal 96000 Analog

d-a 48k gain -1dBFS -1dBFS 997 n/a n/a n/a dBu Level 23.5 24.5 22.5 n/a 100k <10 - 22k 8 In 8 Out OctalThru AES 48000 AES

d-a 48k freq resp -1dBFS -1dBFS 20-20k n/a n/a n/a dBr Level 0 1 -1 n/a 100k <10 - >500k 8 In 8 Out OctalThru AES 48000 AES

D-A 44.1 kHz AES Sample Rate Tests

d-a 48k thd+n -1dBFS -1dBFS 20-20k n/a n/a n/a % THD+N 0.0004 0.002 0.0001 n/a 100k <10 - 22k 8 In 8 Out OctalThru AES 48000 AES

d-a 48k dyn-rng -60dBFS -60dBFS 20-20k n/a n/a n/a dBr THD+N -113 -110 -120 n/a 100k <10 - 22k 8 In 8 Out OctalThru AES 48000 AES

d-a 48k xtalk -1dBFS -1dBFS 997 n/a n/a n/a dB Level -140 -100 -150 n/a 100k <10 - 22k 8 In 8 Out OctalThru AES 48000 AES

D-A 96k AES Sample Rate Tests

d-a 44k gain -1dBFS -1dBFS 997 n/a n/a n/a dBu Level 23.5 24.5 22.5 n/a 100k <10 - 22k 8 In 8 Out OctalThru AES 44100 AES

d-a 44k thd+n -1dBFS -1dBFS 20-20k n/a n/a n/a % THD+N 0.0004 0.002 0.0001 n/a 100k <10 - 22k 8 In 8 Out OctalThru AES 44100 AES

d-a 44k dyn-rng -60dBFS -60dBFS 20-20k n/a n/a n/a dBr THD+N -113 -110 -120 n/a 100k <10 - 22k 8 In 8 Out OctalThru AES 44100 AES

d-a 96k gain -1dBFS -1dBFS 997 n/a n/a n/a dBu Level 23.5 24.5 22.5 n/a 100k <10 - 22k 8 In 8 Out OctalThru AES 96000 AES

d-a 96k freq resp -1dBFS -1dBFS 20-40k n/a n/a n/a dBr Level 0 1 -1 n/a 100k <10 - >500k 8 In 8 Out OctalThru AES 96000 AES

d-a 96k thd+n -1dBFS -1dBFS 20-20k n/a n/a n/a % THD+N 0.0006 0.002 0.0001 n/a 100k <10 - 22k 8 In 8 Out OctalThru AES 96000 AES

d-a 96k dyn-rng -60dBFS -60dBFS 20-20k n/a n/a n/a dBr THD+N -113 -110 -120 n/a 100k <10 - 22k 8 In 8 Out OctalThru AES 96000 AES

Digital Input/Output Analog Analyzer

Digital Generator Analog Analyzer

BNC Thru Tests

D-A BNC Word Clock O

word clk thru gain 2.500 Vpp 48000 n/a n/a n/a n/a Vpp Level 2.500 2.60 2.3 n/a n/a n/a 8 In 8 Out OctalThru BNC n/a n/a

word clk thru freq Output Sample Rate Sweep 100k-40k n/a Hz Freq 100k - 40k +50 -50 n/a n/a n/a 8 In 8 Out OctalThru BNC 100k - 40k n/a

Analog Generator Analog Analyzer

D-A BNC Word Clock In Sample Rate Tests

D-A BNC 96k Word Clock In/Out Sample Rate Tests

A-A Tests

d-a 48k word clk out thd+n -1dBFS -1dBFS 997 n/a n/a n/a % THD+N 0.0006 0.002 0.0001 Off 100k <10Hz-22kHz 8 In 8 Out OctalThru Internal 48000 AES

d-a 44k word clk out thd+n -1dBFS -1dBFS 997 n/a n/a n/a % THD+N 0.0006 0.002 0.0001 Off 100k <10Hz-22kHz 8 In 8 Out OctalThru Internal 44100 AES

d-a 48k word clk in thd+n -1dBFS -1dBFS 997 Sweep 48.495k to 47.505k % THD+N 0.0004 0.002 0.0001 Off 100k <10Hz-22kHz 8 In 8 Out OctalThru BNC 48 ,975-47,0250 AES

d-a 44k word clk in thd+n -1dBFS -1dBFS 997 Sweep 44554k to 43.646k % THD+N 0.0004 0.002 0.0001 Off 100k <10Hz-22kHz 8 In 8 Out OctalThru BNC 45,000-43,200 AES

d-a 96k word clk in thd+n -1dBFS -1dBFS 997 Sweep 96.989k to 95.011k % THD+N 0.0006 0.002 0.0001 Off 100k <10Hz-22kHz 8 In 8 Out OctalThru BNC 97,950-94,050 AES

d-a 96k word clk out thd+n -1dBFS -1dBFS 997 n/a n/a n/a % THD+N 0.0006 0.002 0.0001 Off 100k <10Hz-22kHz 8 In 8 Out OctalThru Internal 96000 AES

a-a gain 22dBu 22dBu 997 40 Bal Gnd dBu Level 22.5 23.5 21.5 n/a 100k <10Hz->500kHz 8 In 8 Out OctalThru Internal 48000 Analog

a-a freq resp 10dBu 10dBu 20-20k 40 Bal Gnd dBr Level 0 1 -1 n/a 100k <10Hz->500kHz 8 In 8 Out OctalThru Internal 48000 Analog

a-a thd+n 22dBu 22dBu 20-20k 40 Bal Gnd % THD+N 0.0006 0.002 0.0001 n/a 100k <10Hz-22kHz 8 In 8 Out OctalThru Internal 48000 Analog

Analog Generator Analog Analyzer

Listen Test

960 Listen 15dBu 15dBu 500 40 Bal Gnd n/a n/a n/a n/a n/a n/a n/a n/a Stereo Thru Random Hall Internal 48000 Analog

4-11

Page 28

960L Multi-Channel Digital Effects System Service Manual

4-12

Page 29

Lexicon

Chapter 5 Serv ice Notes

Motherboard - lithium battery

The motherboard has a lithium battery. This is not user replaceable. Only a qualified service technician

should replace it. Lithium batteries may be considered a hazardous substance should be disposed of in

accordance with any local, national or international laws or guidelines.

Power Supplies

Various manufacturer's power supplies have been specified for the 960L. There are some slight mechanical

differences in some of these power supplies. Some units will have a power supply with a voltage setting

switch as noted above. Some units will have a power supply that does not have a voltage selection switch

and the AC voltage input will be automatically sensed by the supply. Always be sure to inspect the rear

panel of the 960L for indication of proper AC voltage setup and in case of the need to "switch" for the

appropriate AC input voltage.

Symptoms of possible power supply failures

1. The fan mounted on the processor of the Main PC card and the fan mounted on the right side of the

chassis are spinning in slow motion or not spinning at all.

2. The Larc2 is indicating not seeing the 960L mainframe.

If supply problems are suspected, please test for proper voltage reading with a DMM meter as described in

the Troubleshooting section of this service manual.

Larc2 Meter Display LED Handling

Due to the special storage and handling procedures required for these dry packed moisture sensitive

devices and the sensitivity to temperature, Lexicon recommends that the Meter Board Assembly be

replaced in its entirety when service of the LEDs is required. Spare modules can be obtained from the

factory, Lexicon P/N 021-14511.

Removal and Replacement of Larc2 Piezo Transducer

For units with the transducer soldered (Rev 5 PCB and up):

Removal

1. Wick the solder from the transducer and the PCB solder pads.

2. Re-flow the remaining solder while gently lifting the transducer edge with an X-acto blade.

Replacement

1. Prep the PCB solder pads as needed

2. Assemble the transducer as outlined in the assembly notes on DWG # 080-14234, ASSY DWG, MECH,

MAIN BD, LARC 2

3. Solder the transducer to the six pads provided.

NOTE: Solder the pads alternately across from each other to minimize overheating of the transducer

For units with the transducer epoxied (Rev 4 PCB and below):

Removal

1. Gently insert the blade between the PCB and transducer to pry it loose from the 5-minute epoxy.

5-1

Page 30

960L Multi-Channel Digital Effects System Service Manual

Replacement

1. Assemble the transducer as outlined in the assembly notes on DWG # 080-14234, ASSY DWG, MECH,

MAIN BD, LARC 2

5-2

Page 31

Female RS-422 Wraparound Plug:

Lexicon

5-3

Page 32

960L Multi-Channel Digital Effects System Service Manual

Male RS-422 Wraparound Plug

5-4

Page 33

Lexicon

Chapter 6 Trou bleshooting

Check the Lexicon web site and Customer Support Knowledgebase for the latest software and information:

http://www.lexicon.com

http://www.lexicon.com/kbase/kbase.asp

Diagnostics

Overview

The purpose of this document is to describe the diagnostic tests in the 960L. The diagnostics in the 960L

are utilized to verify performance and functionality. The 960L and LARC2 are a high end, digital audio

effects system. The 960L and LARC2 system is a multi-channel digital audio effects processor that can also

be configured as a single channel processor. The LARC2 provides full control of 960L through a 50-foot, 9pin cable. The 960L and LARC2 system is composed of the following printed circuit assemblies

manufactured by Lexicon:

1. NLX backplane

2. I/O backplane

3. I/O Clock

4. Analog In

5. Analog Out

6. Reverb

7. AES

8. LARC2 Main

9. LARC2 Meter.

In addition there are 6 OEM devices:

1. NLX PC processor card (motherboard) with Celeron CPU Processor

2. NLX/ATX power supply

3. 3.5” floppy drive

4. CD-ROM

5. MIDI Card

6. Hard Disk Drive

960L Diagnostics:

The 960L has 3 sets of diagnostics, power on, functional, and troubleshooting. The power on diagnostics

are executed every time the 960L is powered on. The power on diagnostics verify basic reverb card

functionality, checks which cards are present in the I/O cage and communicates with the LARC2.

The functional diagnostics are used to verify the performance of the digital circuitry of the 960L. The

functional diagnostics test the following:

1. MIDI port

2. Serial 2 Port

3. Reverb Card, which includes

a. 56301 to Dual Port Ram

b. Z80 to Dual Port Ram

c. Z80 to DRAM

d. Z80 to SRAM

e. Lexichip3 WCS, (Writeable Control Storage)

f. Lexichip3 ADF, (Audio Data File)

g. TMIX

h. Serial Audio, (all the Octal Audio Data lines)

6-1

Page 34

960L Multi-Channel Digital Effects System Service Manual

4. I/O Cage Cards

The functional diagnostics test the hardware on the 960L that do not process audio, as well as the audio

processing circuitry. The non-audio processing sections include the MIDI, clock ports, and serial

communication on 960L. The audio processing is verified with functional diagnostics and a dry audioprocessing algorithm available in the normal operating mode called 8 In 8 Out. Diagnostic testing is

performed on the 960L prior to burn-in.

The troubleshooting diagnostics are those tests that are available to assist a technician, either in-house or

in another part of the world, to debug a 960L to the component level.

960L Diagnostic User Interface:

The primary user interface for the 960L diagnostics is the LARC2. The secondary user interface for the