Page 1

Intel

Xeon ® Processor E3-1200

Product Family and LGA 1155 Socket

Thermal/Mechanical Specifications and Design Guidelines

April 2011

®

Document Number: 324973-001

Page 2

Notice: This document contains information on products in the design phase of development. The information here is subject to change without

notice. Do not finalize a design with this information.

Legal Lines and Disclaimers

NFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED,

BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS

PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER,

AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING

LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY

PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving,

life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined.” Intel

reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future

changes to them.

The processor, chipset and LGA1155 socket may contain design defects or errors known as errata which may cause the product to

deviate from published specifications. Current characterized errata are available on request.Contact your local Intel sales office or

your distributor to obtain the latest specifications and before placing your product order.

Requires a system with Intel® Turbo Boost Technology capability. Consult your PC manufacturer. Performance varies depending

on hardware, software and system configuration. For more information, visit http://www.intel.com/technology/turboboost

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature may be obtained

by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Intel, Xeon and the Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States

and other countries.

*Other names and brands may be claimed as the property of others.

Copyright © 2011, Intel Corporation. All Rights Reserved.

2 Thermal/Mechanical Specifications and Design Guidelines

Page 3

Contents

1Introduction..............................................................................................................9

1.1 References ....................................................................................................... 10

1.2 Definition of Terms ............................................................................................ 10

2 Package Mechanical & Storage Specifications.......................................................... 13

2.1 Package Mechanical Specifications ....................................................................... 13

2.1.1 Package Mechanical Drawing.................................................................... 14

2.1.2 Processor Component Keep-Out Zones...................................................... 14

2.1.3 Package Loading Specifications ................................................................ 15

2.1.4 Package Handling Guidelines.................................................................... 15

2.1.5 Package Insertion Specifications............................................................... 15

2.1.6 Processor Mass Specification.................................................................... 15

2.1.7 Processor Materials................................................................................. 16

2.1.8 Processor Markings................................................................................. 16

2.1.9 Processor Land Coordinates ..................................................................... 17

2.2 Processor Storage Specifications ......................................................................... 18

3 LGA1155 Socket ...................................................................................................... 19

3.1 Board Layout .................................................................................................... 20

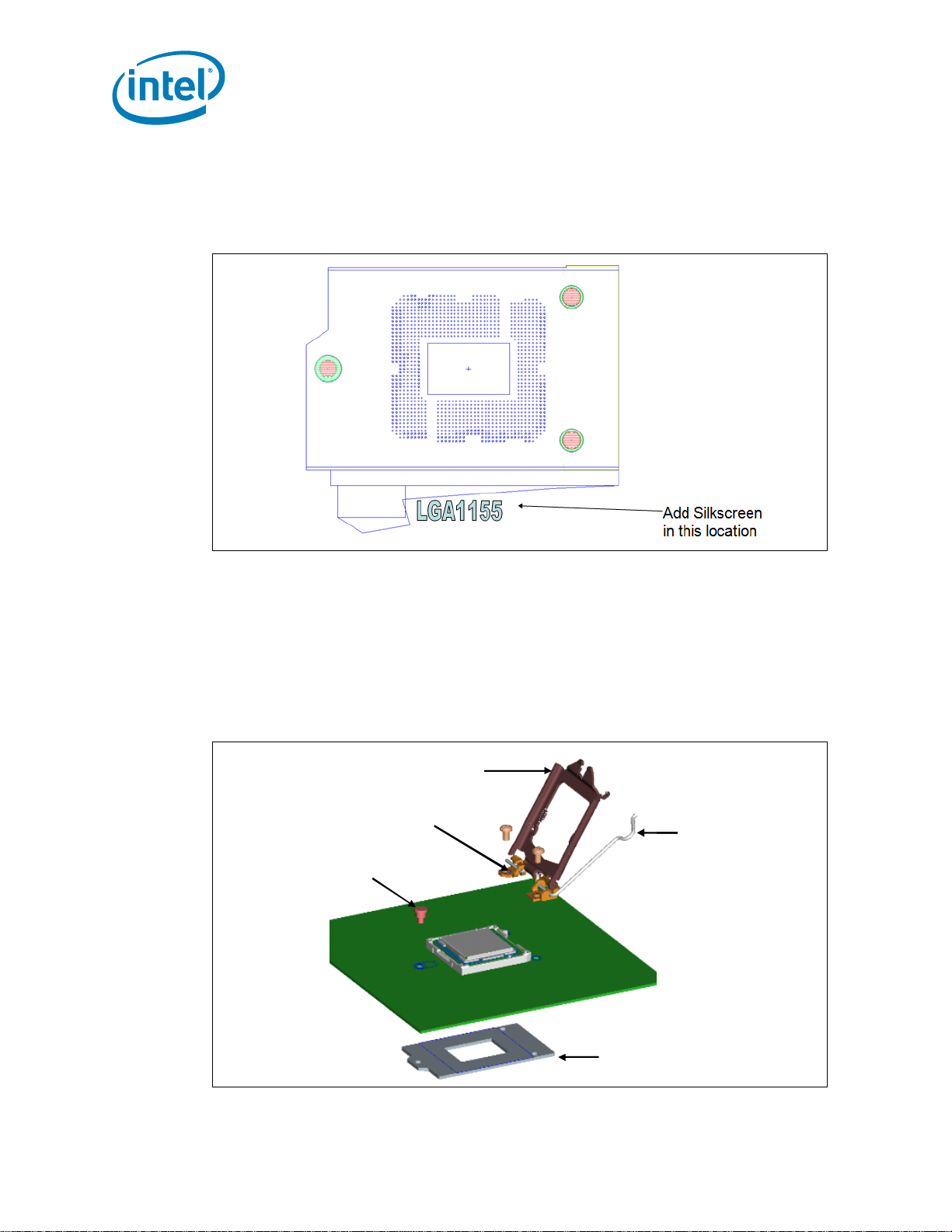

3.1.1 Suggested Silkscreen Marking for Socket Identification................................ 22

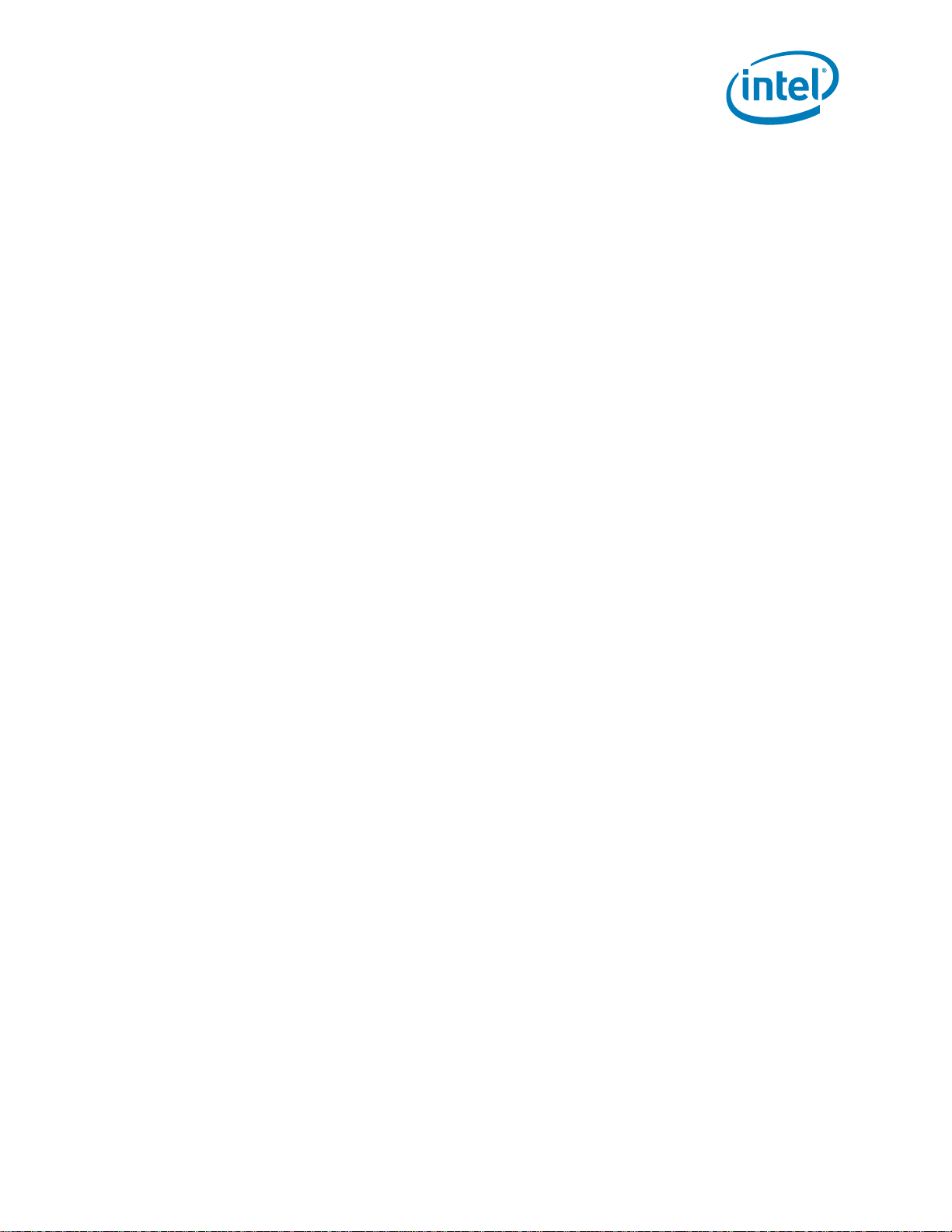

3.2 Attachment to Motherboard ................................................................................ 22

3.3 Socket Components........................................................................................... 23

3.3.1 Socket Body Housing .............................................................................. 23

3.3.2 Solder Balls ........................................................................................... 23

3.3.3 Contacts ............................................................................................... 23

3.3.4 Pick and Place Cover............................................................................... 23

3.4 Package Installation / Removal ........................................................................... 24

3.4.1 Socket Standoffs and Package Seating Plane.............................................. 25

3.5 Durability ......................................................................................................... 25

3.6 Markings .......................................................................................................... 25

3.7 Component Insertion Forces ............................................................................... 26

3.8 Socket Size ...................................................................................................... 26

4 Independent Loading Mechanism (ILM)................................................................... 27

4.1 Design Concept................................................................................................. 27

4.1.1 ILM Assembly Design Overview ................................................................ 27

4.1.2 ILM Back Plate Design Overview............................................................... 28

4.1.3 Shoulder Screw and Fasteners Design Overview ......................................... 29

4.2 Assembly of ILM to a Motherboard....................................................................... 30

4.3 ILM Interchangeability ....................................................................................... 32

4.4 Markings .......................................................................................................... 32

4.5 ILM Cover ........................................................................................................ 33

5 LGA1155 Socket and ILM Electrical, Mechanical and Environmental Specifications .. 37

5.1 Component Mass............................................................................................... 37

5.2 Package/Socket Stackup Height .......................................................................... 37

5.3 Loading Specifications........................................................................................ 38

5.4 Electrical Requirements...................................................................................... 38

5.5 Environmental Requirements .............................................................................. 39

6 Thermal Specifications ............................................................................................ 41

6.1 Thermal Specifications ....................................................................................... 41

6.1.1 Intel

6.1.2 Intel

6.1.3 Intel

®

Xeon® Processor E3-1280 (95W)Thermal Profile................................ 43

®

Xeon® Processor E3-1200 (80W) Thermal Profile............................... 44

®

Xeon® Processor E3-1260L (45W) Thermal Profile ............................. 46

Thermal/Mechanical Specifications and Design Guideline 3

Page 4

6.1.4 Intel® Xeon® Processor E3-1220L (20W) Thermal Profile..............................47

6.1.5 Intel® Xeon® Processor E3-1200 (95W) with Integrated

Graphics Thermal Profile..........................................................................48

6.1.6 Processor Specification for Operation Where Digital Thermal

Sensor Exceeds TCONTROL ......................................................................49

6.1.7 Thermal Metrology..................................................................................54

6.2 Processor Thermal Features ................................................................................54

6.2.1 Processor Temperature............................................................................54

6.2.2 Adaptive Thermal Monitor ........................................................................54

6.2.3 THERMTRIP# Signal................................................................................58

6.3 Intel® Turbo Boost Technology ............................................................................58

6.3.1 Intel

®

Turbo Boost Technology Frequency..................................................58

6.3.2 Intel® Turbo Boost Technology Graphics Frequency.....................................59

6.4 Thermal Considerations ......................................................................................59

6.4.1 Intel

®

Turbo Boost Technology Power Control and Reporting ........................60

6.4.2 Package Power Control ............................................................................61

6.4.3 Power Plane Control ................................................................................61

6.4.4 Turbo Time Parameter.............................................................................61

7 PECI Interface .........................................................................................................63

7.1 Platform Environment Control Interface (PECI) ......................................................63

7.1.1 Introduction...........................................................................................63

8 Sensor Based Thermal Specification Design Guidance ..............................................65

8.1 Sensor Based Specification Overview (DTS 1.0) .....................................................65

8.2 Sensor Based Thermal Specification .....................................................................67

8.2.1 TTV Thermal Profile.................................................................................67

8.2.2 Specification When DTS value is Greater than TCONTROL.............................68

8.3 Thermal Solution Design Process .........................................................................68

8.3.1 Boundary Condition Definition ..................................................................68

8.3.2 Thermal Design and Modelling ..................................................................69

8.3.3 Thermal Solution Validation......................................................................69

8.4 Fan Speed Control (FSC) Design Process...............................................................69

8.4.1 DTS 1.1 A New Fan Speed Control Algorithm without TAMBIENT Data............71

8.5 System Validation..............................................................................................73

9 1U Thermal Solution ................................................................................................75

9.1 Performance Targets ..........................................................................................75

9.2 1U Collaboration Heatsink...................................................................................75

9.2.1 Heatsink Performance .............................................................................75

9.2.2 Thermal Solution ....................................................................................78

9.2.3 Assembly...............................................................................................79

9.3 1U Reference Heatsink .......................................................................................80

9.3.1 Heatsink Performance .............................................................................80

9.3.2 Thermal Solution ....................................................................................80

9.3.3 Assembly...............................................................................................81

9.4 Geometric Envelope for 1U Thermal Mechanical Design ...........................................81

9.5 Thermal Interface Material ..................................................................................81

9.6 Heat Pipe Thermal Consideration .........................................................................81

10 Active Tower Thermal Solution ................................................................................83

10.1 Introduction......................................................................................................83

10.2 Mechanical Specifications....................................................................................84

10.2.1 Cooling Solution Dimensions ....................................................................84

10.2.2 Retention Mechanism and Heatsink Attach Clip Assembly .............................85

10.3 Electrical Requirements ......................................................................................85

10.3.1 Active Tower Heatsink Power Supply .........................................................85

10.4 Cooling Requirements ........................................................................................87

4 Thermal/Mechanical Specifications and Design Guideline

Page 5

11 Thermal Solution Quality and Reliability Requirements............................................ 89

11.1 Reference Heatsink Thermal Verification ............................................................... 89

11.2 Mechanical Environmental Testing ....................................................................... 89

11.2.1 Recommended Test Sequence.................................................................. 90

11.2.2 Post-Test Pass Criteria ............................................................................ 90

11.2.3 Recommended BIOS/Processor/Memory Test Procedures............................. 90

11.3 Material and Recycling Requirements ................................................................... 91

A Component Suppliers............................................................................................... 93

B Mechanical Drawings............................................................................................... 95

C Socket Mechanical Drawings ................................................................................. 115

D Package Mechanical Drawings............................................................................... 121

Figures

2-1 Processor Package Assembly Sketch .................................................................... 13

2-2 Package View ................................................................................................... 14

2-3 Processor Top-Side Markings .............................................................................. 16

2-4 Processor Package Lands Coordinates .................................................................. 17

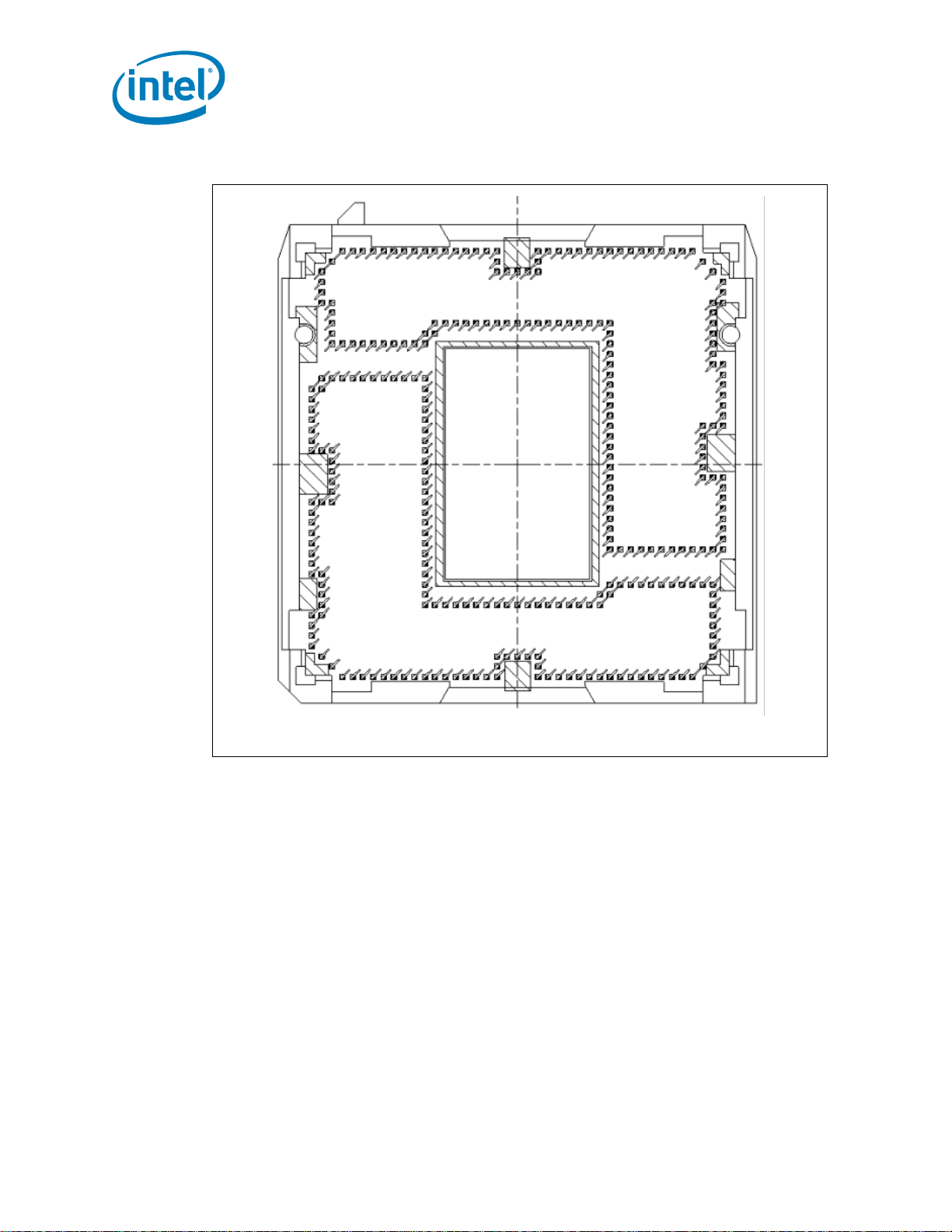

3-1 LGA1155 Socket with Pick and Place Cover ........................................................... 19

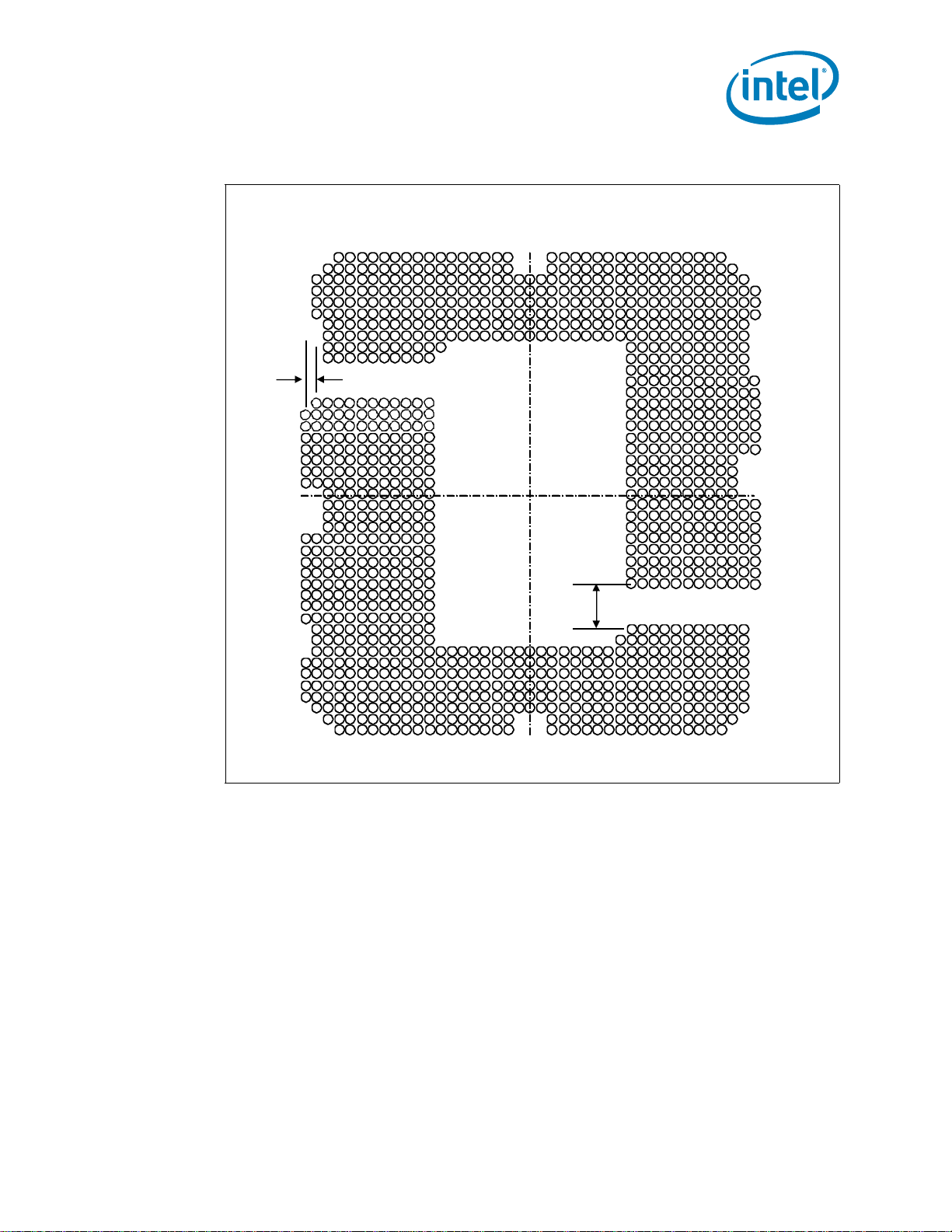

3-2 LGA1155 Socket Contact Numbering (Top View of Socket) ...................................... 20

3-3 LGA1155 Socket Land Pattern (Top View of Board) ................................................ 21

3-4 Suggested Board Marking................................................................................... 22

3-5 Attachment to Motherboard ................................................................................ 22

3-6 Pick and Place Cover.......................................................................................... 24

3-7 Package Installation / Removal Features............................................................... 25

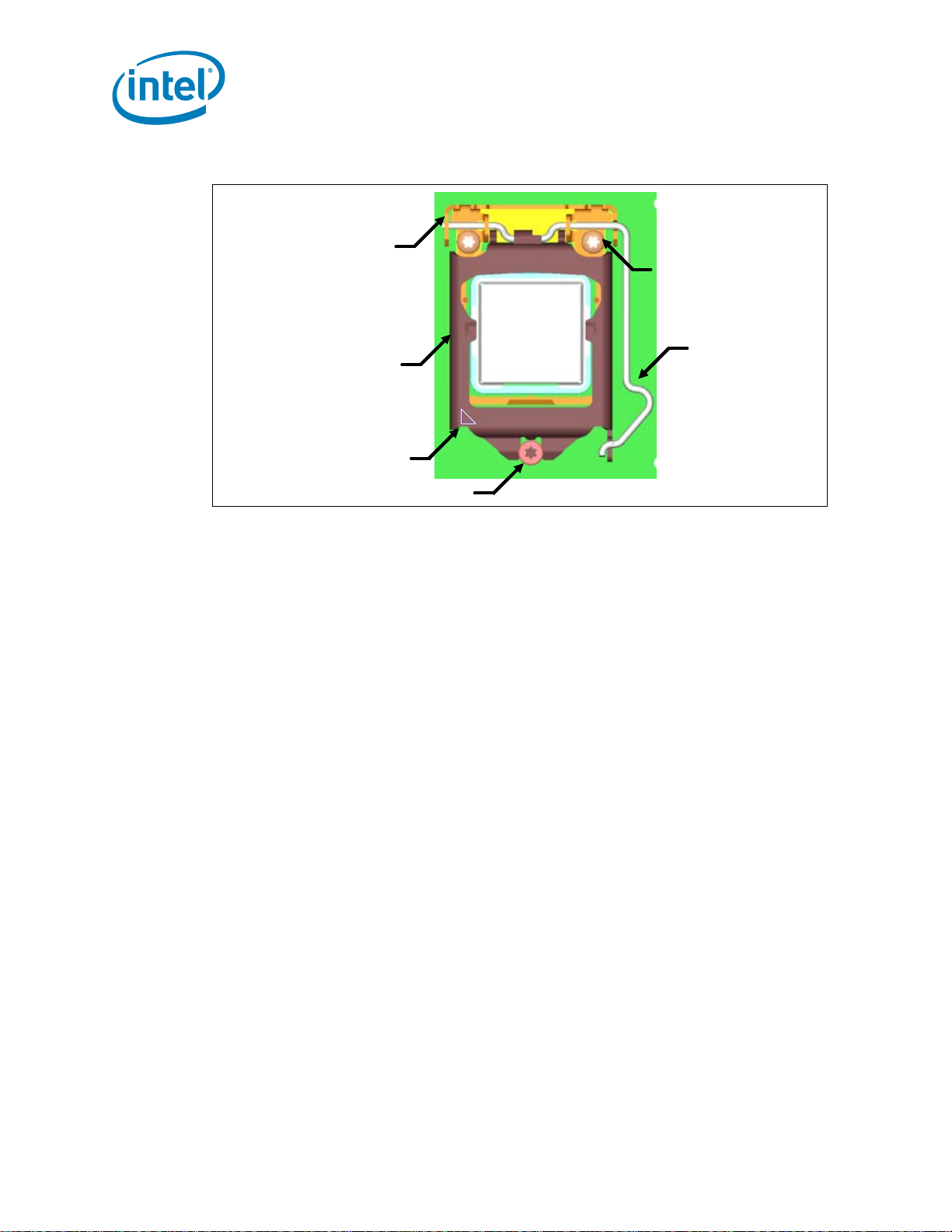

4-1 ILM Assembly with Installed Processor ................................................................. 28

4-2 Back Plate ........................................................................................................ 29

4-3 Shoulder Screw................................................................................................. 30

4-4 ILM Assembly ................................................................................................... 31

4-5 Pin1 and ILM Lever............................................................................................ 32

4-6 ILM Cover ........................................................................................................ 34

4-7 ILM Cover and PnP Cover Interference ................................................................. 35

5-1 Flow Chart of Knowledge-Based Reliability Evaluation Methodology .......................... 40

6-1 Thermal Test Vehicle Thermal Profile for Intel

6-2 Thermal Test Vehicle Thermal Profile for Intel

6-3 Thermal Test Vehicle Thermal Profile for Intel

6-4 Thermal Test Vehicle Thermal Profile for Intel

6-5 Thermal Test Vehicle Thermal Profile for

Intel® Xeon® Processor E3-1200 (95W) with Integrated Graphics ............................ 48

6-6 TTV Case Temperature (TCASE) Measurement Location .......................................... 54

6-7 Frequency and Voltage Ordering.......................................................................... 56

6-8 Package Power Control....................................................................................... 61

8-1 Comparison of Case Temperature vs. Sensor Based Specification............................. 66

8-2 Intel

®

Xeon® Processor E3-1280 (95W) TTV Thermal Profile ................................. 67

8-3 DTS 1.1 Definition Points.................................................................................... 72

9-1 1U Collaboration Heatsink Performance Curves...................................................... 76

9-2 1U Collaboration Heatsink Performance Curves...................................................... 77

9-3 1U Collaboration Heatsink Assembly .................................................................... 79

9-4 1U Reference Heatsink Performance Curves.......................................................... 80

9-5 KOZ 3-D Model (Top) in 1U Server ...................................................................... 81

9-6 TTV Die Size and Orientation .............................................................................. 82

®

Xeon® Processor E3-1280 (95W) ....... 43

®

Xeon® Processor E3-1200 (80W) ....... 44

®

Xeon® Processor E3-1260L (45W) ..... 46

®

Xeon® Processor E3-1220L (20W) .... 47

Thermal/Mechanical Specifications and Design Guideline 5

Page 6

10-1 Mechanical Representation of the Solution.............................................................83

10-2 Physical Space Requirements for the Solution (side view)........................................84

10-3 Physical Space Requirements for the Solution (top view).........................................85

10-4 Fan Power Cable Connector Description ...............................................................86

10-5 Baseboard Power Header Placement Relative to Processor Socket.............................86

10-6 Active Tower Heatsink Airspace Keepout Requirements (side view)...........................87

B-1 Socket / Heatsink / ILM Keepout Zone Primary Side for 1U (Top) .............................96

B-2 Socket / Heatsink / ILM Keepout Zone Secondary Side for 1U (Bottom) ....................97

B-3 Socket / Processor / ILM Keepout Zone Primary Side for 1U (Top)............................98

B-4 Socket / Processor / ILM Keepout Zone Secondary Side for 1U (Bottom) ...................99

B-5 1U Collaboration Heatsink Assembly................................................................... 100

B-6 1U Collaboration Heatsink.................................................................................101

B-7 1U Reference Heatsink Assembly ....................................................................... 102

B-8 1U Reference Heatsink .....................................................................................103

B-9 1U Heatsink Screw...........................................................................................104

B-10 Heatsink Compression Spring ............................................................................105

B-11 Heatsink Load Cup ...........................................................................................106

B-12 Heatsink Retaining Ring....................................................................................107

B-13 Heatsink Backplate Assembly ............................................................................108

B-14 Heatsink Backplate ..........................................................................................109

B-15 Heatsink Backplate Insulator .............................................................................110

B-16 Heatsink Backplate Stud ...................................................................................111

B-17 Thermocouple Attach Drawing ...........................................................................112

B-18 1U ILM Shoulder Screw ....................................................................................113

B-19 1U ILM Standard 6-32 Thread Fastener...............................................................114

C-1 Socket Mechanical Drawing (Sheet 1 of 4)...........................................................116

C-2 Socket Mechanical Drawing (Sheet 2 of 4)...........................................................117

C-3 Socket Mechanical Drawing (Sheet 3 of 4)...........................................................118

C-4 Socket Mechanical Drawing (Sheet 4 of 4)...........................................................119

D-1 Processor Package Drawing (Sheet 1 of 2) ..........................................................122

D-2 Processor Package Drawing (Sheet 2of 2) ...........................................................123

6 Thermal/Mechanical Specifications and Design Guideline

Page 7

Tables

1-1 Reference Documents ........................................................................................ 10

1-2 Terms and Descriptions...................................................................................... 10

2-1 Processor Loading Specifications ......................................................................... 15

2-2 Package Handling Guidelines............................................................................... 15

2-3 Processor Materials............................................................................................ 16

2-4 Storage Conditions ............................................................................................ 18

5-1 Socket Component Mass .................................................................................... 37

5-2 1155-land Package and LGA1155 Socket Stackup Height ........................................ 37

5-3 Socket & ILM Mechanical Specifications ................................................................ 38

5-4 Electrical Requirements for LGA1155 Socket ......................................................... 39

6-1 Processor Thermal Specifications......................................................................... 42

6-2 Thermal Test Vehicle Thermal Profile for Intel

6-3 Thermal Test Vehicle Thermal Profile for Intel

6-4 Thermal Test Vehicle Thermal Profile for Intel

6-5 Thermal Test Vehicle Thermal Profile for Intel

6-6 Thermal Test Vehicle Thermal Profile for

Intel

®

Xeon® Processor E3-1200 (95W) with Integrated Graphics ............................ 48

6-7 Thermal Solution Performance above TCONTROL for the

Intel® Xeon® Processor E3-1280 (95W) ............................................................... 49

6-8 Thermal Solution Performance above TCONTROL for the

6-9 Thermal Solution Performance above TCONTROL for the

Intel

Intel

®

Xeon® Processor E3-1200 (80W) .............................................................. 50

®

Xeon® Processor E3-1260L (45W).............................................................. 51

6-10 Thermal Solution Performance above TCONTROL for the

Intel® Xeon® Processor E3-1220L (20W) ............................................................. 52

6-11 Thermal Solution Performance above TCONTROL for the

Intel

®

Xeon® Processor E3-1200 (95W) with Integrated Graphics ............................ 53

8-1 DTS 1.1 Thermal Solution Performance above T

9-1 Boundary Conditions and Performance Targets ...................................................... 75

9-2 Comparison between TTV Thermal Profile and Thermal Solution Performance

for Intel

®

Xeon® Processor E3-1280 (95W) ......................................................... 77

10-1 Fan Power and Signal Specifications..................................................................... 86

11-1 Use Conditions (Board Level) .............................................................................. 89

A-1 Collaboration Heatsink Enabled Components-1U Server.......................................... 93

A-2 Reference Heatsink - Workstation........................................................................ 93

A-3 Reference Heatsink Components- Workstation....................................................... 93

A-4 LGA1155 Socket and ILM Components ................................................................. 93

A-5 Supplier Contact Information .............................................................................. 94

B-1 Mechanical Drawing List ..................................................................................... 95

C-1 Mechanical Drawing List ................................................................................... 115

D-1 Mechanical Drawing List ................................................................................... 121

®

Xeon® Processor E3-1280 (95W) ....... 43

®

Xeon® Processor E3-1200 (80W) ....... 45

®

Xeon® Processor E3-1260L (45W) ..... 46

®

Xeon® Processor E3-1220L (20W) .... 47

CONTROL

.......................................... 72

Thermal/Mechanical Specifications and Design Guideline 7

Page 8

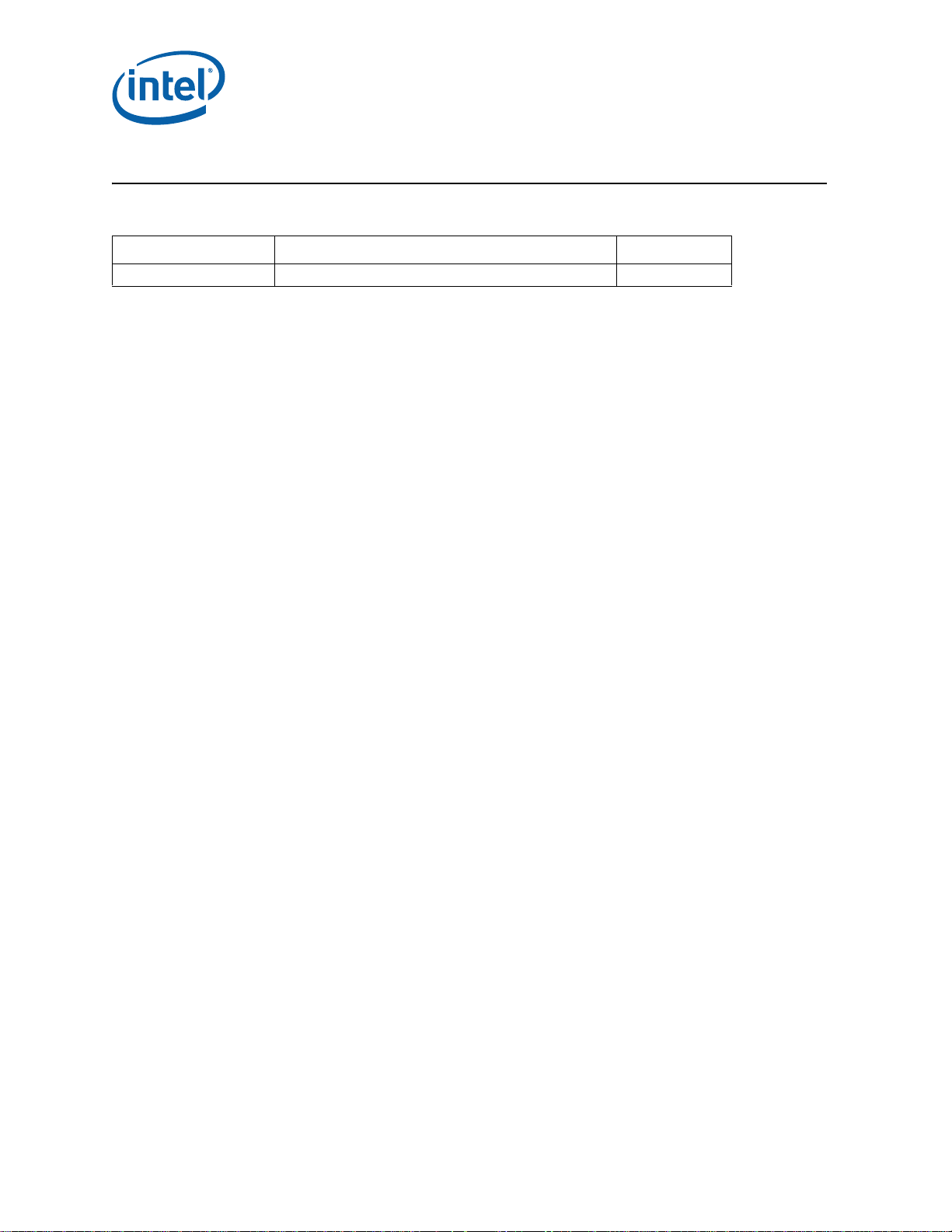

Revision History

Document Number Description Date

324973-001 • Initial release of the document. April 2011

§

8 Thermal/Mechanical Specifications and Design Guideline

Page 9

Introduction

1 Introduction

This document is intended to provide guidelines for design of thermal and mechanical

solution. Meanwhile thermal and mechanical specifications for the processor and

associated socket are included.

The components described in this document include:

• The thermal and mechanical specifications for the following Intel® server/

workstation processors:

—Intel® Xeon® processor E3-1200 product family

• The LGA1155 socket and the Independent Loading Mechanism (ILM) and back

plate.

• The collaboration/reference design thermal solution (heatsink) for the processors

and associated retention hardware.

®

The Intel

specifications. When required for clarity this document will use:

•Intel® Xeon® processor E3-1280 (95W)

•Intel® Xeon® processor E3-1200 (80W)

•Intel

•Intel® Xeon® processor E3-1260L (45W)

•Intel® Xeon® processor E3-1220L (20W)

Xeon® Processor E3-1200 product family has the different thermal

®

Xeon® processor E3-1200 series (95W) with integrated graphics

Note: When the information is applicable to all products the this document will use

“processor” or “processors” to simplify the document.

Thermal/Mechanical Specifications and Design Guidelines 9

Page 10

1.1 References

Material and concepts available in the following documents may be beneficial when

reading this document.

Table 1-1. Reference Documents

Intel® Xeon® Processor E3-1200 Family Data Sheet Volume One http://

Intel® Xeon® Processor E3-1200 Family Datasheet Volume Two http://

Intel® Xeon® Processor E3-1200 Family Specification Update http://

4-Wire Pulse Width Modulation (PWM) Controlled Fans

Introduction

Document Location Notes

www.intel.com/

Assets/PDF/

datasheet/

324970.pdf

www.intel.com/

Assets/PDF/

datasheet/

324971.pdf

www.intel.com/

Assets/PDF/

specupdate/

324972.pdf

Available at http://

www.formfactors.org/

1.2 Definition of Terms

Table 1-2. Terms and Descriptions (Sheet 1 of 2)

Term Description

Bypass Bypass is the area between a passive heatsink and any object that can act to form a duct. For this

CTE Coefficient of Thermal Expansion. The relative rate a material expands during a thermal event.

DTS Digital Thermal Sensor reports a relative die temperature as an offset from TCC activation temperature.

FSC Fan Speed Control

IHS Integrated Heat Spreader: a component of the processor package used to enhance the thermal

ILM Independent Loading Mechanism provides the force needed to seat the 1155-LGA land package onto the

PCH Platform Controller Hub. The PCH is connected to the processor via the Direct Media Interface (DMI) and

LGA1155 socket The processor mates with the system board through this surface mount, 1155-land socket.

PECI The Platform Environment Control Interface (PECI) is a one-wire interface that provides a communication

Ψ

CA

Ψ

CS

Ψ

SA

T

CASE or TC

example, it can be expressed as a dimension away from the outside dimension of the fins to the nearest

surface.

performance of the package. Component thermal solutions interface with the processor at the IHS surface.

socket contacts.

®

Flexible Display Interface (Intel® FDI).

Intel

channel between Intel processor and chipset components to external monitoring devices.

Case-to-ambient thermal characterization parameter (psi). A measure of thermal solution performance

using total package power. Defined as (T

be specified for Ψ measurements.

Case-to-sink thermal characterization parameter. A measure of thermal interface material performance

using total package power. Defined as (T

Sink-to-ambient thermal characterization parameter. A measure of heatsink thermal performance using

total package power. Defined as (T

The case temperature of the processor, measured at the geometric center of the topside of the TTV IHS.

– TLA) / Total Package Power.

S

– TLA) / Total Package Power. The heat source should always

CASE

– TS) / Total Package Power.

CASE

10 Thermal/Mechanical Specifications and Design Guidelines

Page 11

Introduction

Table 1-2. Terms and Descriptions (Sheet 2 of 2)

Term Description

T

CASE_MAX

TCC Thermal Control Circuit: Thermal monitor uses the TCC to reduce the die temperature by using clock

T

CONTROL

TDP Thermal Design Power: Thermal solution should be designed to dissipate this target power level. TDP is not

Thermal Monitor A power reduction feature designed to decrease temperature after the processor has reached its maximum

Thermal Profile Line that defines case temperature specification of the TTV at a given power level.

TIM Thermal Interface Material: The thermally conductive compound between the heatsink and the processor

TTV Thermal Test Vehicle. A mechanically equivalent package that contains a resistive heater in the die to

T

LA

T

SA

The maximum case temperature as specified in a component specification.

modulation and/or operating frequency and input voltage adjustment when the die temperature is very

near its operating limits.

Tcontrol is a static value that is below the TCC activation temperature and used as a trigger point for fan

speed control. When DTS > Tcontrol, the processor must comply to the TTV thermal profile.

the maximum power that the processor can dissipate.

operating temperature.

case. This material fills the air gaps and voids, and enhances the transfer of the heat from the processor

case to the heatsink.

evaluate thermal solutions.

The measured ambient temperature locally surrounding the processor. The ambient temperature should be

measured just upstream of a passive heatsink or at the fan inlet for an active heatsink.

The system ambient air temperature external to a system chassis. This temperature is usually measured

at the chassis air inlets.

§

Thermal/Mechanical Specifications and Design Guidelines 11

Page 12

Introduction

12 Thermal/Mechanical Specifications and Design Guidelines

Page 13

Package Mechanical & Storage Specifications

IHS

Substrate

System Board

Capacitors

Core (die)

TIM

LGA1155 Socket

2 Package Mechanical & Storage

Specifications

2.1 Package Mechanical Specifications

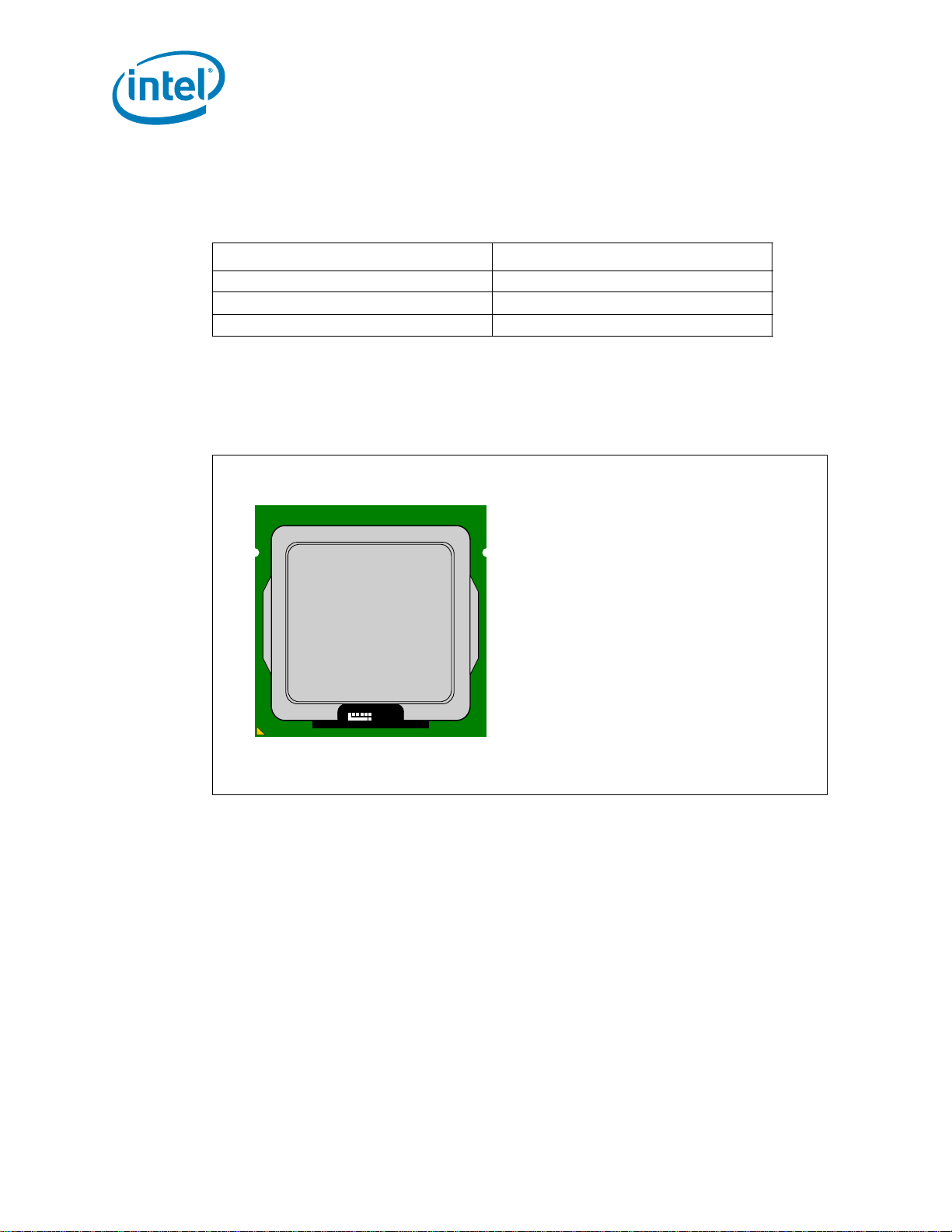

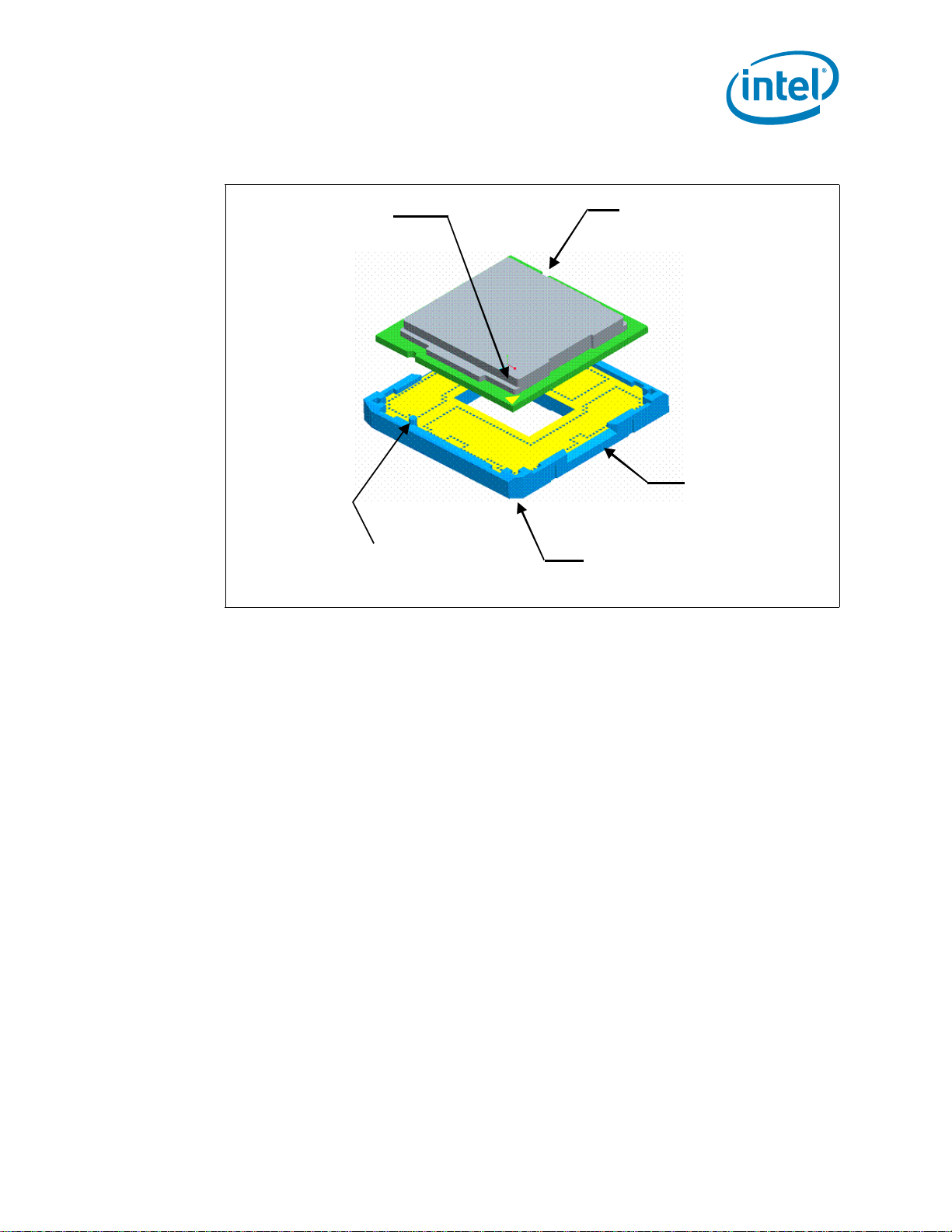

The processor is packaged in a Flip-Chip Land Grid Array package that interfaces with

the motherboard via the LGA1155 socket. The package consists of a processor

mounted on a substrate land-carrier. An integrated heat spreader (IHS) is attached to

the package substrate and core and serves as the mating surface for processor thermal

solutions, such as a heatsink. Figure 2-1 shows a sketch of the processor package

components and how they are assembled together. Refer to Chapter 3 and Chapter 4

for complete details on the LGA1155 socket.

The package components shown in Figure 2-1 include the following:

1. Integrated Heat Spreader (IHS)

2. Thermal Interface Material (TIM)

3. Processor core (die)

4. Package substrate

5. Capacitors

Figure 2-1. Processor Package Assembly Sketch

Note:

1. Socket and motherboard are included for reference and are not part of processor package.

2. For clarity the ILM not shown.

Thermal/Mechanical Specifications and Design Guidelines 13

Page 14

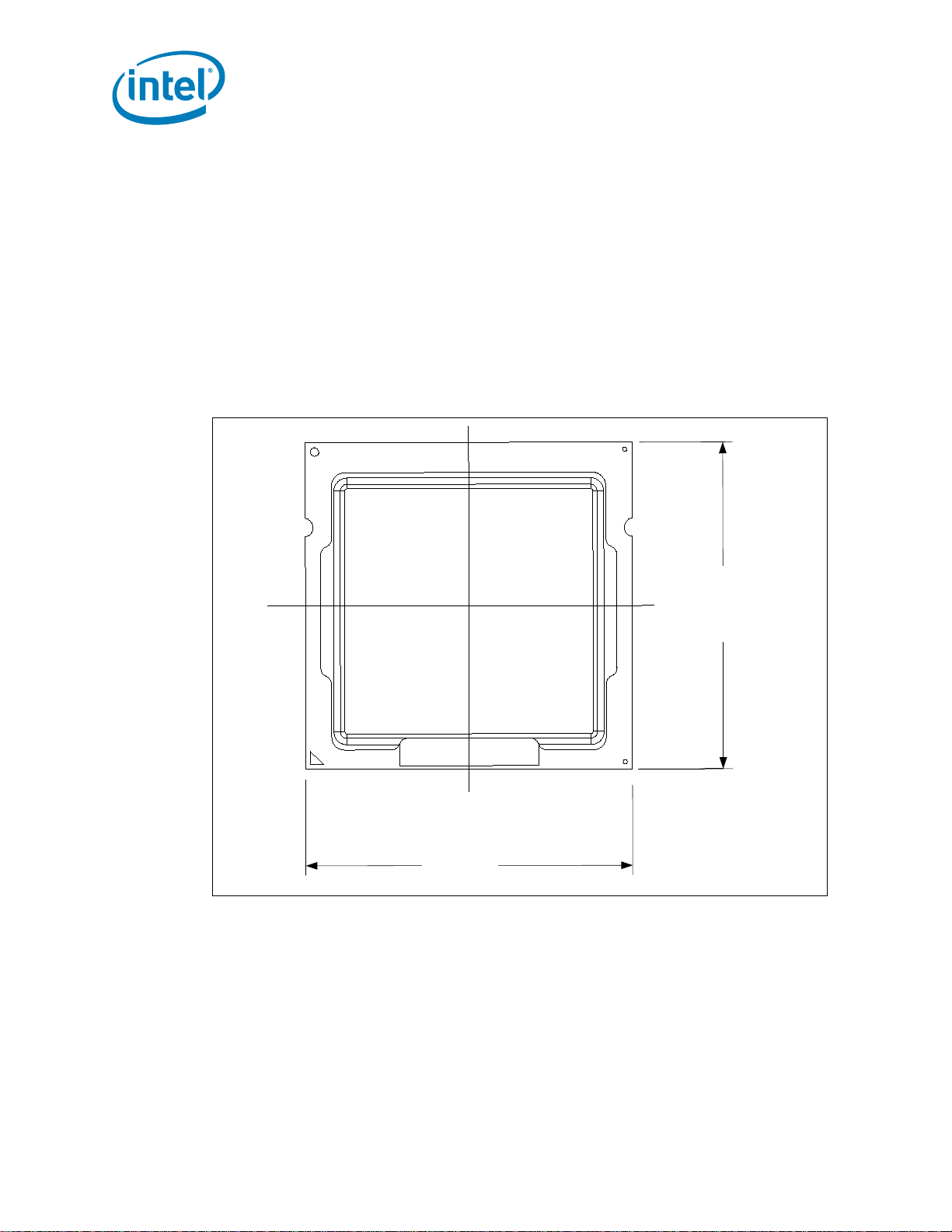

2.1.1 Package Mechanical Drawing

37.5

37.5

Figure 2-2 shows the basic package layout and dimensions. The detailed package

mechanical drawings are in Appendix D. The drawings include dimensions necessary to

design a thermal solution for the processor. These dimensions include:

1. Package reference with tolerances (total height, length, width, and so on)

2. IHS parallelism and tilt

3. Land dimensions

4. Top-side and back-side component keep-out dimensions

5. Reference datums

6. All drawing dimensions are in mm.

Figure 2-2. Package View

Package Mechanical & Storage Specifications

2.1.2 Processor Component Keep-Out Zones

The processor may contain components on the substrate that define component keepout zone requirements. A thermal and mechanical solution design must not intrude into

the required keep-out zones. Decoupling capacitors are typically mounted to either the

topside or land-side of the package substrate. See Figure B-3 and Figure B-4 for keepout zones. The location and quantity of package capacitors may change due to

manufacturing efficiencies but will remain within the component keep-in. This keep-in

zone includes solder paste and is a post reflow maximum height for the components.

14 Thermal/Mechanical Specifications and Design Guidelines

Page 15

Package Mechanical & Storage Specifications

2.1.3 Package Loading Specifications

Ta b le 2 - 1 provides dynamic and static load specifications for the processor package.

These mechanical maximum load limits should not be exceeded during heatsink

assembly, shipping conditions, or standard use condition. Also, any mechanical system

or component testing should not exceed the maximum limits. The processor package

substrate should not be used as a mechanical reference or load-bearing surface for

.

Table 2-1. Processor Loading Specifications

thermal and mechanical solution.

Parameter Minimum Maximum Notes

Static Compressive Load - 600 N [135 lbf] 1, 2, 3

Dynamic Compressive Load - 712 N [160 lbf ] 1, 3, 4

Notes:

1. These specifications apply to uniform compressive loading in a direction normal to the processor IHS.

2. This is the maximum static force that can be applied by the heatsink and retention solution to maintain the

heatsink and processor interface.

3. These specifications are based on limited testing for design characterization. Loading limits are for the

package only and do not include the limits of the processor socket.

4. Dynamic loading is defined as an 50g shock load, 2X Dynamic Acceleration Factor with a 500g maximum

thermal solution.

2.1.4 Package Handling Guidelines

Ta b le 2 - 2 includes a list of guidelines on package handling in terms of recommended

maximum loading on the processor IHS relative to a fixed substrate. These package

handling loads may be experienced during heatsink removal.

Table 2-2. Package Handling Guidelines

Parameter Maximum Recommended Notes

Shear 311 N [70 lbf] 1, 4

Tensile 111 N [25 lbf] 2, 4

Torque 3.95 N-m [35 lbf-in] 3, 4

Notes:

1. A shear load is defined as a load applied to the IHS in a direction parallel to the IHS top surface.

2. A tensile load is defined as a pulling load applied to the IHS in a direction normal to the IHS surface.

3. A torque load is defined as a twisting load applied to the IHS in an axis of rotation normal to the IHS top

surface.

4. These guidelines are based on limited testing for design characterization.

2.1.5 Package Insertion Specifications

The processor can be inserted into and removed from an LGA1155 socket 15 times. The

socket should meet the LGA1155 socket requirements detailed in Chapter 5.

2.1.6 Processor Mass Specification

The typical mass of the processor is 21.5 g (0.76 oz). This mass [weight] includes all

the components that are included in the package.

Thermal/Mechanical Specifications and Design Guidelines 15

Page 16

2.1.7 Processor Materials

Sample (QDF):

GRP1LINE1: i{M}{C}YY

GRP1LINE2: INTEL CONFIDENTIAL

GRP1LINE3: QDF ES SPEED

GRP1LINE4: COUNTRY OF ORIGIN

GRP1LINE5: {FPO} {e4}

Production (SSPEC):

GRP1LINE1: i{M}{C}YY

GRP1LINE2: BRAND PROC#

GRP1LINE3: SSPEC SPEED

GRP1LINE4: COUNTRY OF ORIGIN

GRP1LINE5: {FPO} {e4}

Package Mechanical & Storage Specifications

Tab l e 2- 3 lists some of the package components and associated materials.

Table 2-3. Processor Materials

Component Material

Integrated Heat Spreader (IHS) Nickel Plated Copper

Substrate Fiber Reinforced Resin

Substrate Lands Gold Plated Copper

2.1.8 Processor Markings

Figure 2-3 shows the topside markings on the processor. This diagram is to aid in the

identification of the processor.

Figure 2-3. Processor Top-Side Markings

GRP1LINE1

GRP1LINE2

GRP1LINE3

GRP1LINE4

GRP1LINE5

S/N

16 Thermal/Mechanical Specifications and Design Guidelines

Page 17

Package Mechanical & Storage Specifications

AY

AV

AT

AP

AM

AK

AH

AF

AD

AB

Y

V

T

P

M

K

H

F

D

B

AW

AU

AR

AN

AL

AJ

AG

AE

AC

AA

W

U

N

R

K

J

G

E

C

A

1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31

33 35 37 39

2 4 6 8 101214 1618202224 26283032

34 36 38 40

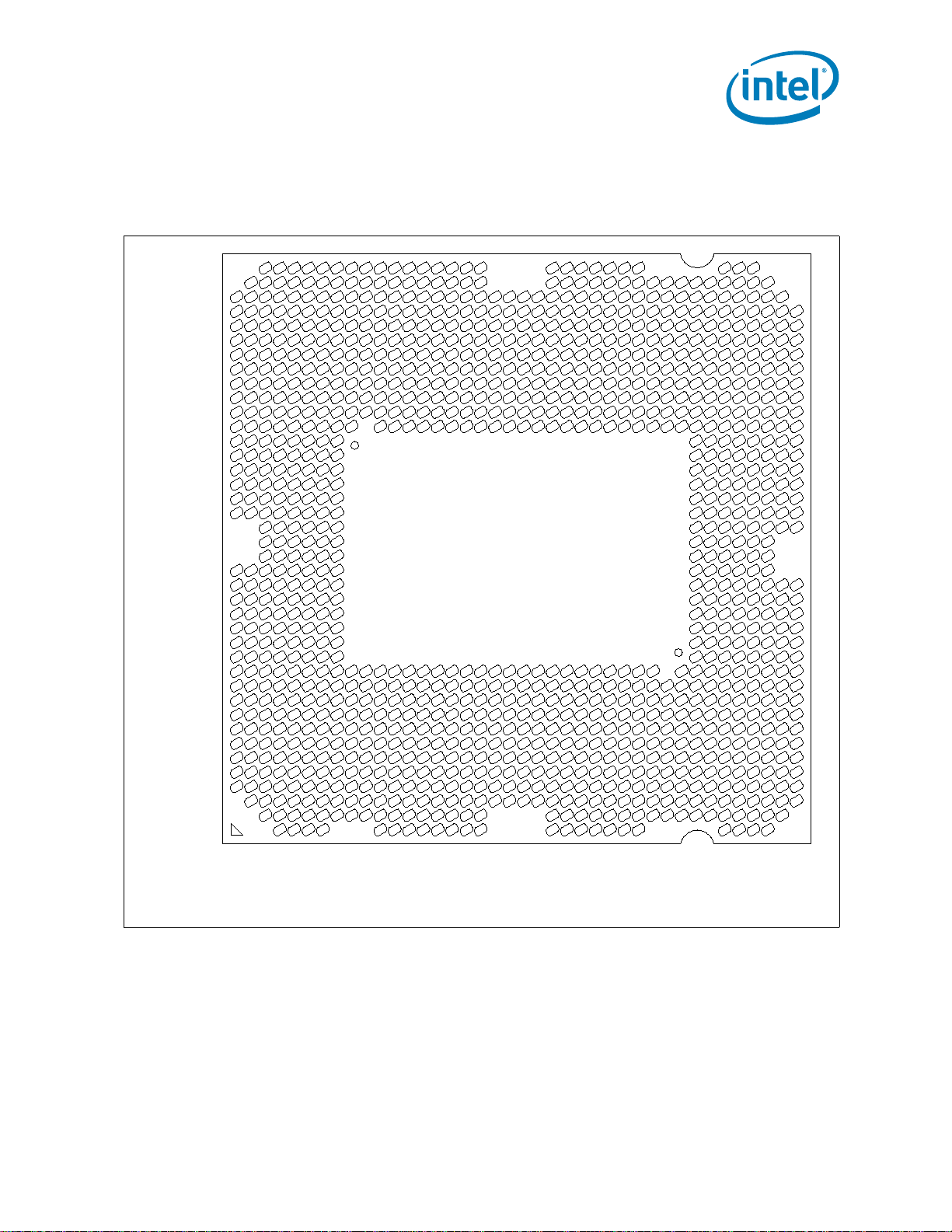

2.1.9 Processor Land Coordinates

.

Figure 2-4. Processor Package Lands Coordinates

Thermal/Mechanical Specifications and Design Guidelines 17

Figure 2-4 shows the bottom view of the processor package.

Page 18

Package Mechanical & Storage Specifications

2.2 Processor Storage Specifications

Tab l e 2- 4 includes a list of the specifications for device storage in terms of maximum

and minimum temperatures and relative humidity. These conditions should not be

.

Table 2-4. Storage Conditions

exceeded in storage or transportation.

Parameter Description Min Max Notes

T

ABSOLUTE STORAGE

T

SUSTAINED STORAGE

RH

SUSTAINED STORAGE

TIME

SUSTAINED STORAGE

Notes:

1. Refers to a component device that is not assembled in a board or socket that is not to be electrically

connected to a voltage reference or I/O signals.

2. Specified temperatures are based on data collected. Exceptions for surface mount reflow are specified in by

applicable JEDEC standard Non-adherence may affect processor reliability.

3. T

ABSOLUTE STORAGE

moisture barrier bags or desiccant.

4. Intel branded board products are certified to meet the following temperature and humidity limits that are

given as an example only (Non-Operating Temperature Limit: -40 °C to 70 °C, Humidity: 50% to 90%,

non-condensing with a maximum wet bulb of 28 °C). Post board attach storage temperature limits are not

specified for non-Intel branded boards.

5. The JEDEC, J-JSTD-020 moisture level rating and associated handling practices apply to all moisture

sensitive devices removed from the moisture barrier bag.

6. Nominal temperature and humidity conditions and durations are given and tested within the constraints

imposed by T

The non-operating device storage temperature.

Damage (latent or otherwise) may occur when

subjected to for any length of time.

The ambient storage temperature limit (in

shipping media) for a sustained period of time.

The maximum device storage relative humidity

for a sustained period of time.

A prolonged or extended period of time; typically

associated with customer shelf life.

applies to the unassembled component only and does not apply to the shipping media,

SUSTAINED STORAGE

and customer shelf life in applicable intel box and bags.

-55 °C 125 °C 1, 2, 3

-5 °C 40 °C 4, 5

60% @ 24 °C 5, 6

0

Months6 Months

6

§

18 Thermal/Mechanical Specifications and Design Guidelines

Page 19

LGA1155 Socket

3 LGA1155 Socket

This chapter describes a surface mount, LGA (Land Grid Array) socket intended for the

processors. The socket provides I/O, power and ground contacts. The socket contains

1155 contacts arrayed about a cavity in the center of the socket with lead-free solder

balls for surface mounting on the motherboard.

The contacts are arranged in two opposing L-shaped patterns within the grid array. The

grid array is 40 x 40 with 24 x 16 grid depopulation in the center of the array and

selective depopulation elsewhere.

The socket must be compatible with the package (processor) and the Independent

Loading Mechanism (ILM). The ILM design includes a back plate which is integral to

having a uniform load on the socket solder joints. Socket loading specifications are

listed in Chapter 5.

Figure 3-1. LGA1155 Socket with Pick and Place Cover

Thermal/Mechanical Specifications and Design Guidelines 19

Page 20

Figure 3-2. LGA1155 Socket Contact Numbering (Top View of Socket)

A C E G J L N R U W AA AC AE AG AJ AL AN AR AU AW

B D F H K M P T V Y AB AD AF AH AK AM AP AT AV AY

1

3

7

5

9

11

15

13

17

19

23

21

25

27

29

2

8

4

6

10

16

12

14

18

24

20

22

26

28

30

15

11

13

17

23

19

21

25

31

27

29

33

39

35

37

32

14

12

16

18

22

20

24

26

30

28

34

38

36

40

LGA1155 Socket

3.1 Board Layout

The land pattern for the LGA1155 socket is 36 mils X 36 mils (X by Y) within each of the

two L-shaped sections. Note that there is no round-off (conversion) error between

20 Thermal/Mechanical Specifications and Design Guidelines

socket pitch (0.9144 mm) and board pitch (36 mil) as these values are equivalent. The

two L-sections are offset by 0.9144 mm (36 mil) in the x direction and 3.114 mm

(122.6 mil) in the y direction, see Figure 3-3. This was to achieve a common package

land to PCB land offset which ensures a single PCB layout for socket designs from the

multiple vendors.

Page 21

LGA1155 Socket

A C E G J L N R U W AA AC AE AG AJ AL AN AR AU AW

B D F H K M P T V Y AB AD AF AH AK AM AP AT AV AY

1

3

7

5

9

11

15

13

17

19

23

21

25

27

29

2

8

4

6

10

16

12

14

18

24

20

22

26

28

30

32

15

11

14

12

13

16

17

23

19

18

22

20

21

24

25

31

27

26

30

28

29

33

39

35

34

38

36

37

40

B D F H K M P T V Y AB AD AF AH AK AM AP AT AV AY

A C E G J L N R U W AA AC AE AG AJ AL AN AR AU AW

122.6 mi l (3.1 144mm )

36mil (0.9144 mm )

Figure 3-3. LGA1155 Socket Land Pattern (Top View of Board)

Thermal/Mechanical Specifications and Design Guidelines 21

Page 22

LGA1155 Socket

Load plate

Frame

Load Lever

Back Plate

Shoulder

Screw

Load plate

Frame

Load Lever

Back Plate

Shoulder

Screw

3.1.1 Suggested Silkscreen Marking for Socket Identification

Intel is recommending that customers mark the socket name approximately where

shown in Figure 3-4.

Figure 3-4. Suggested Board Marking

3.2 Attachment to Motherboard

The socket is attached to the motherboard by 1155 solder balls. There are no additional

external methods (that is, screw, extra solder, adhesive, and so on) to attach the

socket.

As indicated in Figure 3-1, the Independent Loading Mechanism (ILM) is not present

during the attach (reflow) process.

Figure 3-5. Attachment to Motherboard

22 Thermal/Mechanical Specifications and Design Guidelines

Page 23

LGA1155 Socket

3.3 Socket Components

The socket has two main components, the socket body and Pick and Place (PnP) cover,

and is delivered as a single integral assembly. Refer to Appendix C for detailed

drawings.

3.3.1 Socket Body Housing

The housing material is thermoplastic or equivalent with UL 94 V-0 flame rating capable

of withstanding 260 °C for 40 seconds which is compatible with typical reflow/rework

profiles. The socket coefficient of thermal expansion (in the XY plane), and creep

properties, must be such that the integrity of the socket is maintained for the

conditions listed in Chapter 5.

The color of the housing will be dark as compared to the solder balls to provide the

contrast needed for pick and place vision systems.

3.3.2 Solder Balls

A total of 1155 solder balls corresponding to the contacts are on the bottom of the

socket for surface mounting with the motherboard. The socket solder ball has the

following characteristics:

• Lead free SAC (SnAgCu) 305 solder alloy with a silver (Ag) content between 3%

and 4% and a melting temperature of approximately 217 °C. The alloy is

compatible with immersion silver (ImAg) and Organic Solderability Protectant

(OSP) motherboard surface finishes and a SAC alloy solder paste.

• Solder ball diameter 0.6 mm ± 0.02 mm, before attaching to the socket lead.

The co-planarity (profile) and true position requirements are defined in Appendix C.

3.3.3 Contacts

Base material for the contacts is high strength copper alloy.

For the area on socket contacts where processor lands will mate, there is a 0.381 μm

[15 μinches] minimum gold plating over 1.27 μm [50 μinches] minimum nickel

underplate.

No contamination by solder in the contact area is allowed during solder reflow.

3.3.4 Pick and Place Cover

The cover provides a planar surface for vacuum pick up used to place components in

the Surface Mount Technology (SMT) manufacturing line. The cover remains on the

socket during reflow to help prevent contamination during reflow. The cover can

withstand 260 °C for 40 seconds (typical reflow/rework profile) and the conditions

listed in Chapter 5 without degrading.

As indicated in Figure 3-6, the cover remains on the socket during ILM installation, and

should remain on whenever possible to help prevent damage to the socket contacts.

Thermal/Mechanical Specifications and Design Guidelines 23

Page 24

Cover retention must be sufficient to support the socket weight during lifting,

Pick & Place Cover

Pin 1

ILM Installation

Pick & Place Cover

Pin 1

ILM Installation

translation, and placement (board manufacturing), and during board and system

shipping and handling. PnP Cover should only be removed with tools, to prevent the

cover from falling into the contacts.

The socket vendors have a common interface on the socket body where the PnP cover

attaches to the socket body. This should allow the PnP covers to be compatible between

socket suppliers.

As indicated in Figure 3-6, a Pin 1 indicator on the cover provides a visual reference for

proper orientation with the socket.

Figure 3-6. Pick and Place Cover

LGA1155 Socket

3.4 Package Installation / Removal

24 Thermal/Mechanical Specifications and Design Guidelines

As indicated in Figure 3-7, access is provided to facilitate manual installation and

removal of the package.

To assist in package orientation and alignment with the socket:

• The package Pin1 triangle and the socket Pin1 chamfer provide visual reference for

proper orientation.

• The package substrate has orientation notches along two opposing edges of the

package, offset from the centerline. The socket has two corresponding orientation

posts to physically prevent mis-orientation of the package. These orientation

features also provide initial rough alignment of package to socket.

• The socket has alignment walls at the four corners to provide final alignment of the

package.

Page 25

LGA1155 Socket

Pin 1

Chamfer

Package

Pin 1

Indicator

Alignment

Post

(2 Places)

Finger/Tool

Access

(2 Pla ces)

Orientation

Notch

(2 Place s)

.

Figure 3-7. Package Installation / Removal Features

3.4.1 Socket Standoffs and Package Seating Plane

Standoffs on the bottom of the socket base establish the minimum socket height after

solder reflow and are specified in Appendix C.

Similarly, a seating plane on the topside of the socket establishes the minimum

package height. See Section 5.2 for the calculated IHS height above the motherboard.

3.5 Durability

The socket must withstand 20 cycles of processor insertion and removal. The max

chain contact resistance from Tab l e 5- 4 must be met when mated in the 1st and

20th cycles.

The socket Pick and Place cover must withstand 15 cycles of insertion and removal.

3.6 Markings

There are three markings on the socket:

• LGA1155: Font type is Helvetica Bold - minimum 6 point (2.125 mm). This mark

will also appear on the pick and place cap.

• Manufacturer's insignia (font size at supplier's discretion).

• Lot identification code (allows traceability of manufacturing date and location).

Thermal/Mechanical Specifications and Design Guidelines 25

Page 26

All markings must withstand 260 °C for 40 seconds (typical reflow/rework profile)

without degrading, and must be visible after the socket is mounted on the

motherboard.

LGA1155 and the manufacturer's insignia are molded or laser marked on the side wall.

3.7 Component Insertion Forces

Any actuation must meet or exceed SEMI S8-95 Safety Guidelines for Ergonomics/

Human Factors Engineering of Semiconductor Manufacturing Equipment, example Table

R2-7 (Maximum Grip Forces). The socket must be designed so that it requires no force

to insert the package into the socket.

3.8 Socket Size

Socket information needed for motherboard design is given in Appendix C.

This information should be used in conjunction with the reference motherboard keepout drawings provided in Appendix B to ensure compatibility with the reference thermal

mechanical components.

LGA1155 Socket

§

26 Thermal/Mechanical Specifications and Design Guidelines

Page 27

Independent Loading Mechanism (ILM)

4 Independent Loading

Mechanism (ILM)

The ILM has two critical functions: deliver the force to seat the processor onto the

socket contacts and distribute the resulting compressive load evenly through the socket

solder joints.

The mechanical design of the ILM is integral to the overall functionality of the LGA1155

socket. Intel performs detailed studies on integration of processor package, socket and

ILM as a system. These studies directly impact the design of the ILM. The Intel

reference ILM will be “build to print” from Intel controlled drawings. Intel recommends

using the Intel Reference ILM. Custom non-Intel ILM designs do not benefit from Intel's

detailed studies and may not incorporate critical design parameters.

Note: There is a single ILM design for the LGA1155 socket and LGA1156 socket.

4.1 Design Concept

The ILM consists of two assemblies that will be procured as a set from the enabled

vendors. These two components are ILM assembly and back plate. To secure the two

assemblies, two types of fasteners are required a pair (2) of standard 6-32 thread

screws and a custom 6-32 thread shoulder screw. The reference design incorporates a

T-20 Torx head fastener. The Torx head fastener was chosen to ensure end users do not

inadvertently remove the ILM assembly and for consistency with the LGA1366 socket

ILM. The Torx head fastener is also less susceptible to driver slippage. Once assembled

the ILM is not required to be removed to install / remove the motherboard from a

chassis.

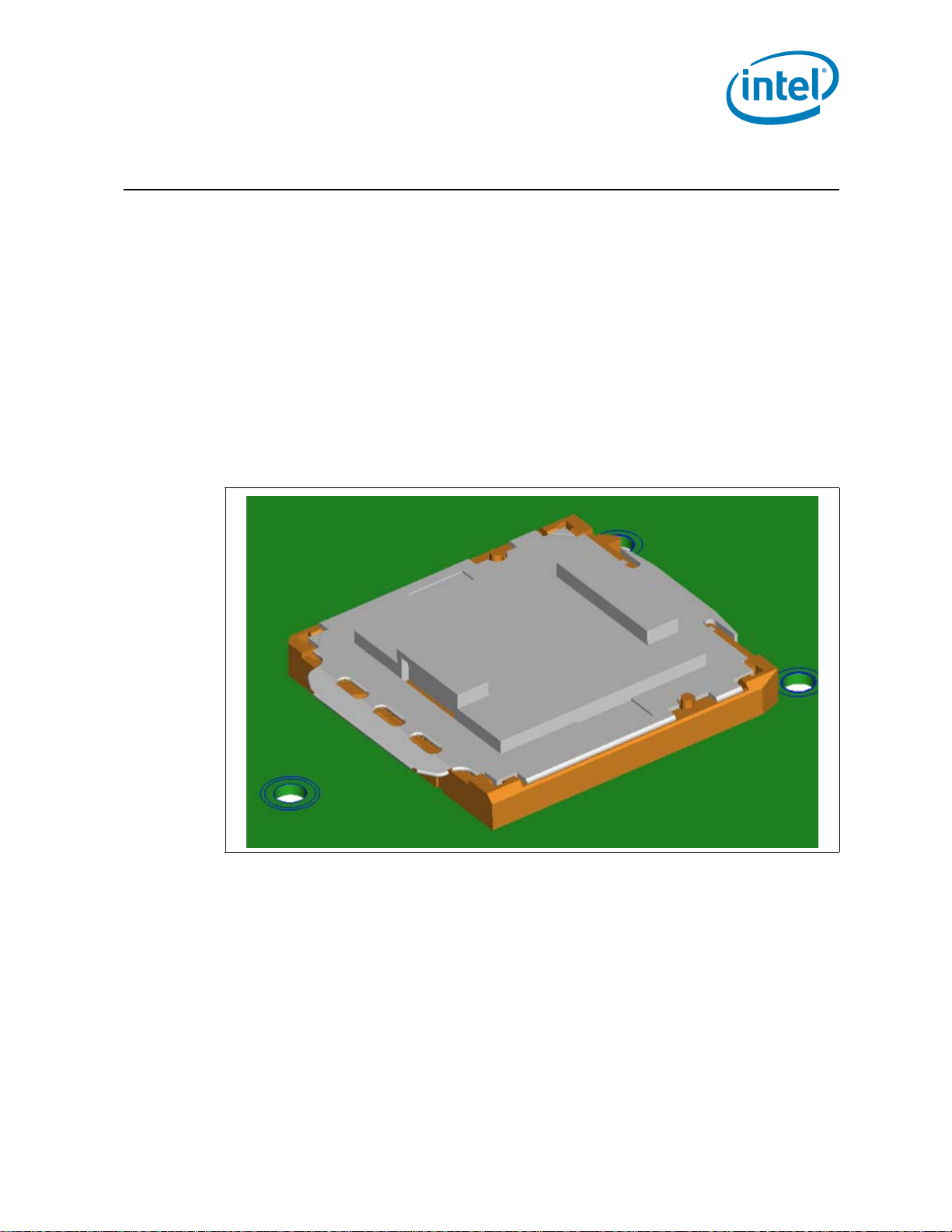

4.1.1 ILM Assembly Design Overview

The ILM assembly consists of 4 major pieces: ILM cover, load lever, load plate and the

hinge frame assembly.

All of the pieces in the ILM assembly except the hinge frame and the screws used to

attach the back plate are fabricated from stainless steel. The hinge frame is plated. The

frame provides the hinge locations for the load lever and load plate. An insulator is preapplied to the bottom surface of the hinge frame.

The ILM assembly design ensures that once assembled to the back plate the only

features touching the board are the shoulder screw and the insulated hinge frame

assembly. The nominal gap of the load plate to the board is ~1 mm.

When closed the load plate applies two point loads onto the IHS at the “dimpled”

features shown in Figure 4-1. The reaction force from closing the load plate is

transmitted to the hinge frame assembly and through the fasteners to the back plate.

Some of the load is passed through the socket body to the board inducing a slight

compression on the solder joints.

A pin 1 indicator will be marked on the ILM assembly.

Thermal/Mechanical Specifications and Design Guidelines 27

Page 28

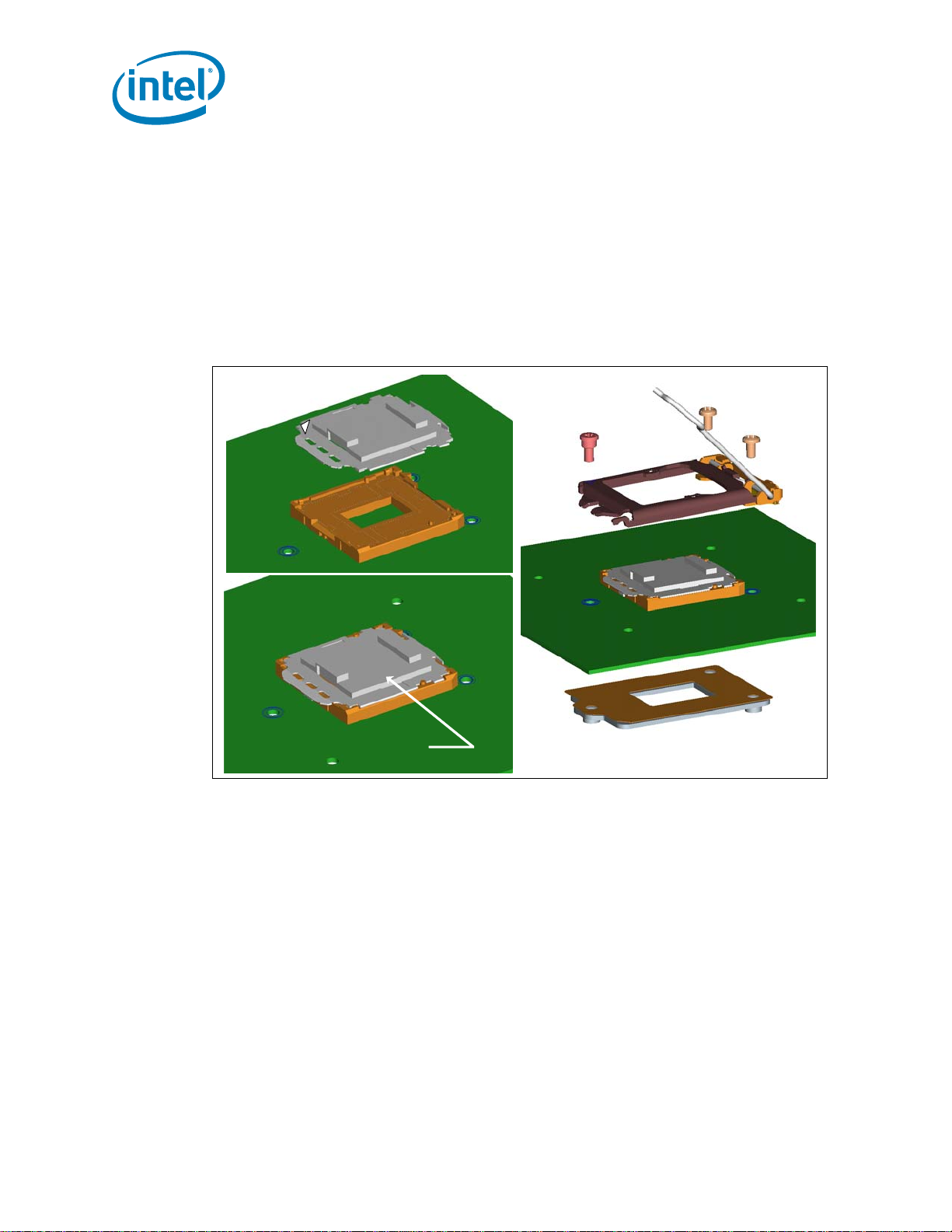

Figure 4-1. ILM Assembly with Installed Processor

Fasteners

Load

Lever

Load

Plate

Hinge /

Frame

Assy

Shoulder Screw

Pin 1 Indicator

Fasteners

Load

Lever

Load

Plate

Hinge /

Frame

Assy

Shoulder Screw

Pin 1 Indicator

Independent Loading Mechanism (ILM)

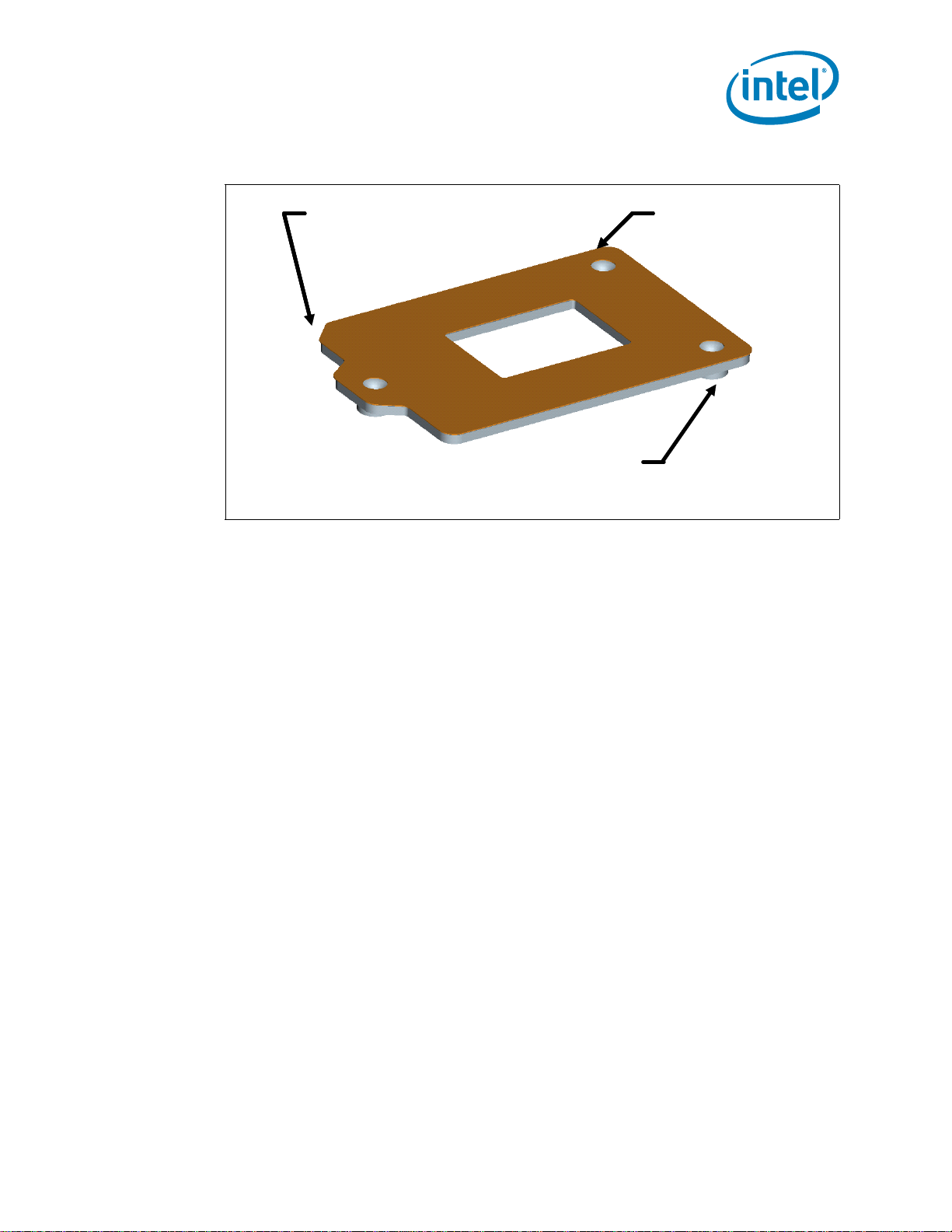

4.1.2 ILM Back Plate Design Overview

The back plate is a flat steel back plate with pierced and extruded features for ILM

attach. A clearance hole is located at the center of the plate to allow access to test

points and backside capacitors if required. An insulator is pre-applied. A notch is placed

in one corner to assist in orienting the back plate during assembly.

Note: The Server ILM back plate is different from the Desktop design. Since Server

secondary-side clearance of 3.0 mm [0.118 inch] is generally available for leads and

backside components, so Server ILM back plate is designed with 1.8 mm thickness and

2.2 mm entire height including punch protrusion length.

Caution: Intel does NOT recommend using the server back plate for high-volume desktop

applications at this time as the server back plate test conditions cover a limited

envelope. Back plates and screws are similar in appearance. To prevent mixing,

different levels of differentiation between server and desktop back plate and screws

have been implemented.

For ILM back plate, three levels of differentiation have been implemented:

• Unique part numbers, please refer to part numbers listed in Appendix A.

• Desktop ILM back plate to use black lettering for marking versus server ILM back

plate to use yellow lettering for marking.

• Desktop ILM back plate using marking “115XDBP” versus server ILM back plate

using marking “115XSBP”.

Note: When reworking a BGA component or the socket that the heatsink, battery, ILM and

ILM Back Plate are removed prior to rework. The ILM back plate should also be

removed when reworking through hole mounted components in a mini-wave or solder

pot). The maximum temperature for the pre-applied insulator on the ILM is

approximately 106 °C.

28 Thermal/Mechanical Specifications and Design Guidelines

Page 29

Independent Loading Mechanism (ILM)

Die Cut

Insulator

Pierced & Extruded

Thread Features

Assembly

Orientation

Feature

Die Cut

Insulator

Pierced & Extruded

Thread Features

Assembly

Orientation

Feature

Figure 4-2. Back Plate

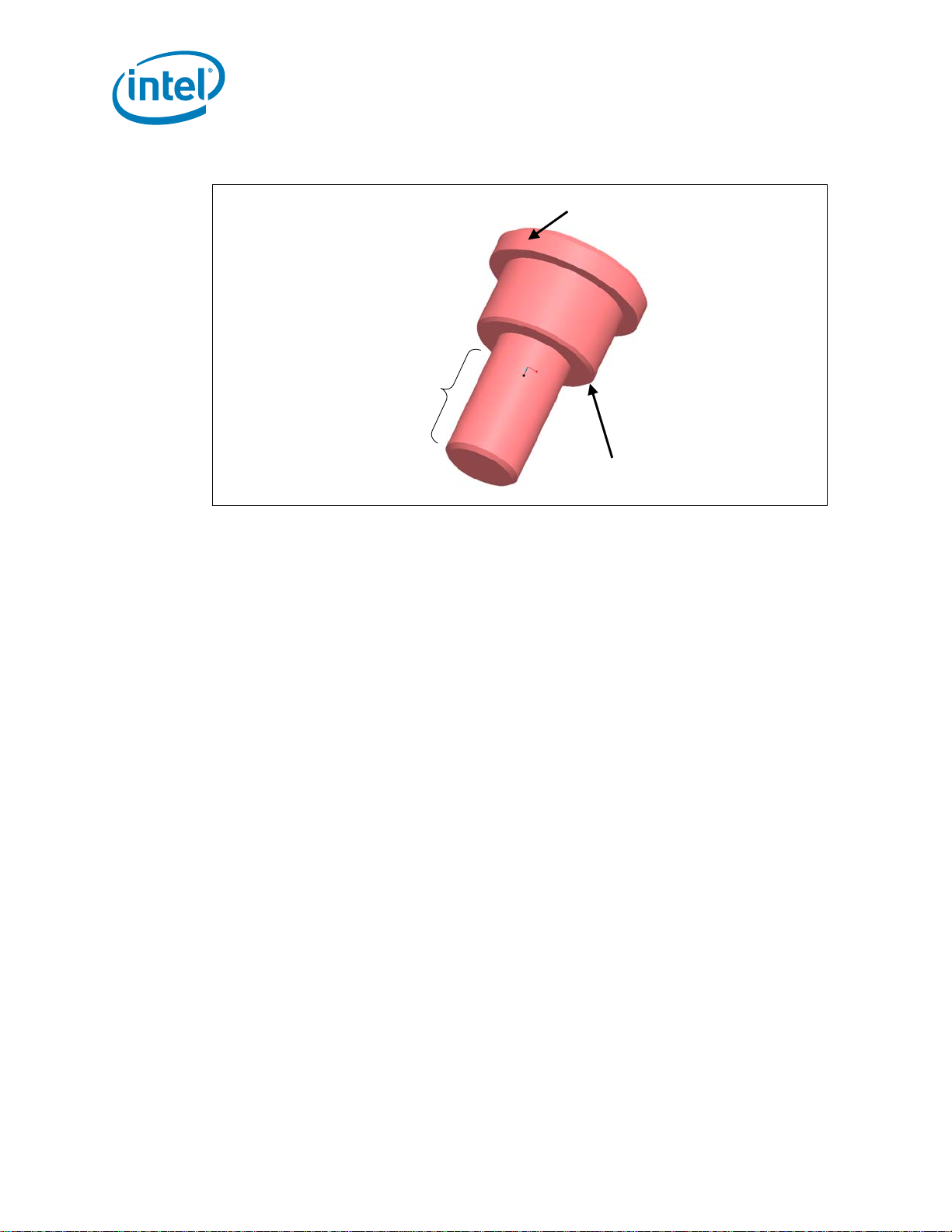

4.1.3 Shoulder Screw and Fasteners Design Overview

Note: The reference design incorporates a T-20 Torx head fastener. The Torx head fastener

The shoulder screw is fabricated from carbonized steel rod. The shoulder height and

diameter are integral to the mechanical performance of the ILM. The diameter provides

alignment of the load plate. The height of the shoulder ensures the proper loading of

the IHS to seat the processor on the socket contacts. The design assumes the shoulder

screw has a minimum yield strength of 235 MPa.

A dimensioned drawing of the shoulder screw is available for local sourcing of this

component. Please refer to Figure B-18 for the custom 6-32 thread shoulder screw

drawing.

The standard fasteners can be sourced locally. The design assumes this fastener has a

minimum yield strength of 235 MPa. Please refer to Figure B-19 for the standard 6-32

thread fasteners drawing.

The screws for Server ILM are different from Desktop design. The length of Server ILM

screws are shorter than the Desktop screw length to satisfy Server secondary-side

clearance limitation. Server ILM back plate to use black nickel plated screws, whereas

desktop ILM back plate to use clear plated screws. Unique part numbers, please refer

to Appendix A.

was chosen to ensure end users do not inadvertently remove the ILM assembly and for

consistency with the LGA1366 socket ILM.

Thermal/Mechanical Specifications and Design Guidelines 29

Page 30

Figure 4-3. Shoulder Screw

Shoulder

6-32 thread

Cap

Independent Loading Mechanism (ILM)

4.2 Assembly of ILM to a Motherboard

The ILM design allows a bottoms up assembly of the components to the board. See

Figure 4-4 for step by step assembly sequence.

1. Place the back plate in a fixture. The motherboard is aligned with the fixture.

2. Install the shoulder screw in the single hole near Pin 1 of the socket. Torque to a

minimum and recommended 8 inch-pounds, but not to exceed 10 inch-pounds.

3. Align and place the ILM assembly over the socket.

4. Install two (2) 6-32 fasteners. Torque to a minimum and recommended 8 inchpounds, but not to exceed 10 inch-pounds.

The thread length of the shoulder screw accommodates a nominal board thicknesses of

0.062”.

30 Thermal/Mechanical Specifications and Design Guidelines

Page 31

Independent Loading Mechanism (ILM)

Step 1 Step 2

Step 3

Step 4

Step 1 Step 2

Step 3

Step 4

Step 1 Step 2

Step 3

Step 4

.

Figure 4-4. ILM Assembly

Note: Here ILM assembly shown in figure is without ILM cover preinstalled.

As indicated in Figure 4-5, the shoulder screw, socket protrusion and ILM key features

Thermal/Mechanical Specifications and Design Guidelines 31

prevent 180 degree rotation of ILM cover assembly with respect to socket. The result is

a specific Pin 1 orientation with respect to ILM lever.

Page 32

Figure 4-5. Pin1 and ILM Lever

Alignment

Features

Load plate not

shown for

clarity

Pin 1

Shoulder

Screw

Load

Lever

Independent Loading Mechanism (ILM)

4.3 ILM Interchangeability

ILM assembly and ILM back plate built from the Intel controlled drawings are intended

to be interchangeable. Interchangeability is defined as an ILM from Vendor A will

demonstrate acceptable manufacturability and reliability with a socket body from

Vendor A, B or C. ILM assembly and ILM back plate from all vendors are also

interchangeable.

The ILM are an integral part of the socket validation testing. ILMs from each vendor will

be matrix tested with the socket bodies from each of the current vendors. The tests

would include: manufacturability, bake and thermal cycling.

See Appendix A for vendor part numbers that were tested.

Note: ILMs that are not compliant to the Intel controlled ILM drawings can not be assured to

be interchangeable.

4.4 Markings

There are four markings on the ILM:

• 115XLM: Font type is Helvetica Bold - minimum 6 point (2.125 mm).

• Manufacturer's insignia (font size at supplier's discretion).

• Lot identification code (allows traceability of manufacturing date and location).

• Pin 1 indicator on the load plate.

All markings must be visible after the ILM is assembled on the motherboard.

115XLM and the manufacturer's insignia can be ink stamped or laser marked on the

side wall.

32 Thermal/Mechanical Specifications and Design Guidelines

Page 33

Independent Loading Mechanism (ILM)

4.5 ILM Cover

Intel has developed an ILM Cover that will snap onto the ILM for the LGA115x socket

family. The ILM cover is intended to reduce the potential for socket contact damage

from operator and customer fingers being close to the socket contacts to remove or

install the pick and place cap. The ILM Cover concept is shown in Figure 4-6.

The ILM Cover is intended to be used in place of the pick and place cover once the ILM

is assembled to the motherboard. The ILM will be offered with the ILM Cover pre

assembled as well as offered as a discrete component.

ILM Cover features:

• Pre-assembled by the ILM vendors to the ILM load plate. It will also be offered as a

discrete component.

• The ILM cover will pop off if a processor is installed in the socket, and the ILM

Cover and ILM are from the same manufacturer.

• ILM Cover can be installed while the ILM is open.

• Maintain compatibility between validated ILM vendors for LGA115x socket, with the

exception noted below

• The ILM cover for the LGA115x socket will have a flammability rating of V-2 per UL

60950-1.

1

.

Note: The ILM Cover pop off feature is not supported if the ILM Covers are interchanged on

different vendor’s ILMs.

Thermal/Mechanical Specifications and Design Guidelines 33

Page 34

Figure 4-6. ILM Cover

Step 3: Close ILM

Step 1: PnP Cover installed

during ILM assembly

Step 2: Remove PnP Cover

Independent Loading Mechanism (ILM)

As indicated in Figure 4-6, the pick and place cover should remain installed during ILM

assembly to the motherboard. After assembly, the pick and place cover is removed,

and the ILM mechanism (with the ILM cover installed) closed to protect the contacts.

The ILM Cover is designed to pop off if the pick and place cover is accidentally left in

place and the ILM closed with the ILM Cover installed. This is shown in Figure 4-7.

34 Thermal/Mechanical Specifications and Design Guidelines

Page 35

Independent Loading Mechanism (ILM)

Figure 4-7. ILM Cover and PnP Cover Interference

As indicated in Figure 4-7, the pick and place cover cannot remain in place and used in

conjunction with the ILM Cover. The ILM Cover is designed to interfere and pop off if

the pick and place cover is unintentionally left in place. The ILM cover will also interfere

and pop off if the ILM is closed with a processor in place in the socket.

§

Thermal/Mechanical Specifications and Design Guidelines 35

Page 36

Independent Loading Mechanism (ILM)

36 Thermal/Mechanical Specifications and Design Guidelines

Page 37

LGA1155 Socket and ILM Electrical, Mechanical and Environmental Specifications

5 LGA1155 Socket and ILM

Electrical, Mechanical and

Environmental Specifications

This chapter describes the electrical, mechanical and environmental specifications for

the LGA1155 socket and the Independent Loading Mechanism.

5.1 Component Mass

Table 5-1. Socket Component Mass

Component Mass

Socket Body, Contacts and PnP Cover 10 g

ILM Cover 29 g

ILM Back Plate 38 g

5.2 Package/Socket Stackup Height

Ta b le 5 - 2 provides the stackup height of a processor in the 1155-land LGA package and

LGA1155 socket with the ILM closed and the processor fully seated in the socket.

Table 5-2. 1155-land Package and LGA1155 Socket Stackup Height

Component Stackup Height Note

Integrated Stackup Height

From Top of Board to Top of IHS

Socket Nominal Seating Plane Height 3.4 ± 0.2 mm 1

Package Nominal Thickness (lands to top of IHS) 4.381 ± 0.269 mm 1

Notes:

1. This data is provided for information only, and should be derived from: (a) the height of the socket seating

plane above the motherboard after reflow, given in Appendix C, (b) the height of the package, from the

package seating plane to the top of the IHS, and accounting for its nominal variation and tolerances that

are given in the corresponding processor data sheet.

2. The integrated stackup height value is a RSS calculation based on current and planned processors that will

use the ILM design.

(mm)

7.781 ± 0.335 mm 2

Thermal/Mechanical Specifications and Design Guidelines 37

Page 38

LGA1155 Socket and ILM Electrical, Mechanical and Environmental Specifications

5.3 Loading Specifications

The socket will be tested against the conditions listed in Chapter 11 with heatsink and

the ILM attached, under the loading conditions outlined in this section.

Tab l e 5- 3 provides load specifications for the LGA1155 socket with the ILM installed.

The maximum limits should not be exceeded during heatsink assembly, shipping

conditions, or standard use condition. Exceeding these limits during test may result in

component failure. The socket body should not be used as a mechanical reference or

load-bearing surface for thermal solutions.

Table 5-3. Socket & ILM Mechanical Specifications

Parameter Min Max Notes

ILM static compressive load on processor IHS 311 N [70 lbf] 600 N [135 lbf] 3, 4, 7, 8

Heatsink static compressive load 0 N [0 lbf] 222 N [50 lbf] 1, 2, 3

Total static compressive Load

(ILM plus Heatsink)

Dynamic Compressive Load

(with heatsink installed)

Pick & Place cover insertion force N/A 10.2 N [2.3 lbf] -

Pick & Place cover removal force 2.2N [0.5 lbf] 7.56 N [1.7 lbf] 9

Load lever actuation force N/A 20.9 N [4.7 lbf] in the

Maximum heatsink mass N/A 500g 10

311 N [70 lbf] 822 N [185 lbf] 3, 4, 7, 8

N/A 712 N [160 lbf ] 1, 3, 5, 6

vertical direction

10.2 N [2.3 lbf] in the

lateral direction.

-

Notes:

1. These specifications apply to uniform compressive loading in a direction perpendicular to the IHS top

surface.

2. This is the minimum and maximum static force that can be applied by the heatsink and it’s retention

solution to maintain the heatsink to IHS interface. This does not imply the Intel reference TIM is validated

to these limits.

3. Loading limits are for the LGA1155 socket.

4. This minimum limit defines the static compressive force required to electrically seat the processor onto the

socket contacts. The minimum load is a beginning of life load.

5. Dynamic loading is defined as a load a 4.3 m/s [170 in/s] minimum velocity change average load

superimposed on the static load requirement.

6. Test condition used a heatsink mass of 500 gm [1.102 lb.] with 50 g acceleration (table input) and an

assumed 2X Dynamic Acceleration Factor (DAF). The dynamic portion of this specification in the product

application can have flexibility in specific values. The ultimate product of mass times acceleration plus static

heatsink load should not exceed this limit.

7. The maximum BOL value and must not be exceeded at any point in the product life.

8. The minimum value is a beginning of life loading requirement based on load degradation over time.

9. The maximum removal force is the flick up removal upwards thumb force (measured at 45o), not

applicable to SMT operation for system assembly. Only the minimum removal force is applicable to vertical

removal in SMT operation for system assembly.

10. The maximum heatsink mass includes the heatsink, screws, springs, rings and cups. This mass limit is

evaluated using the heatsink attach to the PCB.

5.4 Electrical Requirements

LGA1155 socket electrical requirements are measured from the socket-seating plane of

the processor to the component side of the socket PCB to which it is attached. All

specifications are maximum values (unless otherwise stated) for a single socket

contact, but includes effects of adjacent contacts where indicated.

38 Thermal/Mechanical Specifications and Design Guidelines

Page 39

LGA1155 Socket and ILM Electrical, Mechanical and Environmental Specifications

Table 5-4. Electrical Requirements for LGA1155 Socket

Parameter Value Comment

The inductance calculated for two contacts,

Mated loop inductance, Loop <3.6 nH

Socket Average Contact Resistance

(EOL)

Max Individual Contact Resistance

(EOL)

Bulk Resistance Increase ≤

Dielectric Withstand Voltage 360 Volts RMS

Insulation Resistance 800 MΩ

19 mOhm

100 mOhm

3 mΩ

considering one forward conductor and one

return conductor. These values must be satisfied

at the worst-case height of the socket.

The socket average contact resistance target is

calculated from the following equation:

sum (Ni X LLCRi) / sum (Ni)

• LLCRi is the chain resistance defined as the

resistance of each chain minus resistance of

shorting bars divided by number of lands in

the daisy chain.

• Ni is the number of contacts within a chain.

• I is the number of daisy chain, ranging from

1 to 119 (total number of daisy chains).

The specification listed is at room temperature

and has to be satisfied at all time.

The specification listed is at room temperature

and has to be satisfied at all time.

Socket Contact Resistance:

the socket contact, solderball, and interface

resistance to the interposer land; gaps included.

The bulk resistance increase per contact from

25°C to 100°C.

The resistance of

5.5 Environmental Requirements

Design, including materials, shall be consistent with the manufacture of units that meet

the following environmental reference points.

The reliability targets in this section are based on the expected field use environment

for these products. The test sequence for new sockets will be developed using the

knowledge-based reliability evaluation methodology, which is acceleration factor

dependent. A simplified process flow of this methodology can be seen in Figure 5-1.

Thermal/Mechanical Specifications and Design Guidelines 39

Page 40

LGA1155 Socket and ILM Electrical, Mechanical and Environmental Specifications

Establish the

market/expected use

environment for the

technology

Develop Speculative

stress conditions based on

historical data, content

experts, and literature

search

Perform stressing to

validate accelerated

stressing assumptions and

determine acceleration

factors

Freeze stressing

requirements and perform

additional data turns

Figure 5-1. Flow Chart of Knowledge-Based Reliability Evaluation Methodology

A detailed description of this methodology can be found at: ftp://download.intel.com/

technology/itj/q32000/pdf/reliability.pdf.

§

40 Thermal/Mechanical Specifications and Design Guidelines

Page 41

Thermal Specifications

6 Thermal Specifications

The processor requires a thermal solution to maintain temperatures within its operating

limits. Any attempt to operate the processor outside these operating limits may result

in permanent damage to the processor and potentially other components within the

system. Maintaining the proper thermal environment is key to reliable, long-term

system operation.

A complete solution includes both component and system level thermal management

features. Component level thermal solutions can include active or passive heatsinks

attached to the processor integrated heat spreader (IHS).

This chapter provides data necessary for developing a complete thermal solution. For

more information on a thermal solution design, please refer to Chapter 9.

6.1 Thermal Specifications

To allow the optimal operation and long-term reliability of Intel processor-based

systems, the processor must remain within the minimum and maximum case

temperature (T

Thermal solutions not designed to provide this level of thermal capability may affect the

long-term reliability of the processor and system. For more details on thermal solution