Intel CORE I7-620 UE, CORE I7-620LE, CELERON PROCESSOR U3405, CORE I7-610E, CORE I7-660UE User Manual

...Page 1

Intel® Core

TM

i7-660UE, i7-620LE/

UE, i7-610E, i5-520E, i3-330E and

®

Intel

Celeron® Processor P4505,

U3405 Series

Datasheet Addendum

August 2010

Document Number: 323178-003

Page 2

Legal Lines and Disclaimers

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR

OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS

OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING

TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE,

MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for

use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the

presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel

or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “un defined.” Intel reserves these for

future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different

processor families. See http://www.intel.com/products/processor_number for details.

The Intel® CoreTM i7-620LE/UE, i7-610E and i5-520E Processor Series may contain design defects or errors known as errata which may cause the

product to deviate from published specifications. Current characterized errata are available on request.

Hyper-Threading Technology requires a computer system with an Intel® Pentium® 4 processor supporting HT Technology and a HT Technology enabled

chipset, BIOS and operating system. Performance will vary depending on the specific hardware and software you use. See http://www.intel.com/

products/ht/Hyperthreading_more.htm for additional information.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel lit erature may be obtained by calling

1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

BunnyPeople, Celeron, Celeron Inside, Centrino, Centrino logo, Core Inside, Dialogic, FlashFile, i960, InstantIP, Intel, Intel logo, Intel386, Intel486,

Intel740, IntelDX2, IntelDX4, IntelSX2, Intel Core, Intel Inside, Intel Inside logo, Intel. Leap ahead., Intel. Leap ahead. logo, Intel NetBurst, Intel

NetMerge, Intel NetStructure, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel Viiv, Intel vPro, Intel XScale, IPLink, Itanium, Itanium Inside,

MCS, MMX, Oplus, OverDrive, PDCharm, Pentium, Pentium Inside, skoool, Sound Mark, The Journey Inside, VTune, Xeon, and Xeon Inside are

trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

*Other names and brands may be claimed as the property of others.

Copyright © 2010, Intel Corporation. All Rights Reserved.

Intel® Core

Datasheet Addendum August 2010

2 Document Number: 323178-003

TM

i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel® Celeron® Processor P4505, U3405 Series

Page 3

Contents

1 Introduction and Features Summary .........................................................................8

1.1 Introduction .......................................................................................................8

1.2 Interfaces ........................................................................................................10

1.2.1 System Memory Support.........................................................................10

1.2.2 PCI Express*......................................................................................... 10

1.3 Package...........................................................................................................11

1.4 Terminology .....................................................................................................12

1.5 Related Documents ...........................................................................................13

2Interfaces................................................................................................................15

2.1 System Memory Interface ..................................................................................15

2.1.1 System Memory Technology Supported.....................................................15

2.1.2 System Memory Timing Support...................................... .. .. .....................16

2.1.3 System Memory Organization Modes.........................................................16

2.1.4 Rules for Populating Memory Slots............................................................18

2.1.5 Technology Enhancements of Intel

2.1.6 DRAM Clock Generation...........................................................................19

2.1.7 DDR3 On-Die Termination .......................................................................19

2.2 PCI Express* Interface....................................................................................... 19

2.2.1 PCI Express* Configuration Mechanism .....................................................19

2.2.2 PCI Express Port Bifurcation..................... .. .. .. ................................ .. .. ......20

3 Signal Description ...................................................................................................21

3.1 System Memory Interface ..................................................................................21

3.2 Reset and Miscellaneous Signals.......................................................................... 24

4 Electrical Specifications...........................................................................................25

4.1 Signal Groups.............................. ............................. .. .............................. ........25

4.2 DC Specifications ..............................................................................................25

4.2.1 Voltage and Current Specifications............................................................25

5 Processor Ball and Signal Information.....................................................................27

5.1 Processor Ball Assignments.................................................................................27

6 Processor Configuration Registers...........................................................................70

6.1 Register Terminology.........................................................................................70

6.1.1 DEVEN - Device Enable ...........................................................................72

6.1.2 ERRSTS - Error Status ............................................................................73

6.1.3 ERRCMD - Error Command ......................................................................74

6.1.4 SMICMD - SMI Command........................................................................76

6.1.5 C0WRDATACTRL - Channel 0 Write Data Control.........................................77

6.1.6 COECCERRLOG - Channel 0 ECC Error Log.................................................78

6.1.7 C1WRDATACTRL - Channel 1 Write Data Control.........................................80

6.1.8 C1ECCERRLOG - Channel 1 ECC Error Log .................................................80

6.2 PCI Device 6.....................................................................................................81

6.2.1 VID6 - Vendor Identification ....................................................................85

6.2.2 DID6 - Device Identification..................................................................... 85

6.2.3 PCICMD6 - PCI Command........................................................................86

6.2.4 PCISTS6 - PCI Status..............................................................................88

6.2.5 RID6 - Revision Identification...................................................................90

6.2.6 CC6 - Class Code ...................................................................................90

6.2.7 CL6 - Cache Line Size ............................................................................. 91

6.2.8 HDR6 - Header Type...............................................................................91

6.2.9 PBUSN6 - Primary Bus Number ................................................................92

®

Fast Memory Access (Intel® FMA)..........18

Intel® Core

August 2010 Datasheet Addendum

Document Number: 323178-003 3

TM

i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel® Celeron® Processor P4505, U3405 Series

Page 4

6.2.10 SBUSN6 - Secondary Bus Number.............................................................92

6.2.11 SUBUSN6 - Subordinate Bus Number ........................................................93

6.2.12 IOBASE6 - I/O Base Address....................................................................93

6.2.13 IOLIMIT6 - I/O Limit Address ...................................................................94

6.2.14 SSTS6 - Secondary Status.......................................................................95

6.2.15 MBASE6 - Memory Base Address...............................................................96

6.2.16 MLIMIT6 - Memory Limit Address..............................................................97

6.2.17 PMBASE6 - Prefetchable Memory Base Address...........................................98

6.2.18 PMLIMIT6 - Prefetchable Memory Limit Address........................................ ..99

6.2.19 PMBASEU6 - Prefetchable Memory Base Address Upper..............................100

6.2.20 PMLIMITU6 - Prefetchable Memory Limit Addres s Upper.............................101

6.2.21 CAPPTR6 - Capabilities Pointer................................................................102

6.2.22 INTRLINE6 - Interrupt Line ....................................................................102

6.2.23 INTRPIN6 - Interrupt Pin........................................................................103

6.2.24 BCTRL6 - Bridge Control........................................................................103

6.2.25 PM_CAPID6 - Power Management Capabilities ..........................................105

6.2.26 PM_CS6 - Power Management Control/Status...........................................106

6.2.27 SS_CAPID - Subsystem ID and Vendor ID Capabilities...............................108

6.2.28 SS - Subsystem ID and Subsystem Vendor ID ..........................................108

6.2.29 MSI_CAPID - Message Signaled Interrupts Capability ID ............................109

6.2.30 MC - Message Control............................................................................109

6.2.31 MA - Message Address...........................................................................111

6.2.32 MD - Message Data...............................................................................111

6.2.33 PEG_CAPL - PCI Express-G Capability List ................................................112

6.2.34 PEG_CAP - PCI Express-G Capabilities .....................................................112

6.2.35 DCAP - Device Capabilities .....................................................................113

6.2.36 DCTL - Device Control...........................................................................114

6.2.37 DSTS - Device Status............................................................................115

6.2.38 LCAP - Link Capabilities .........................................................................116

6.2.39 LCTL - Link Control ...............................................................................119

6.2.40 LSTS - Link Status................................................................................121

6.2.41 SLOTCAP - Slot Capabilities....................................................................123

6.2.42 SLOTCTL - Slot Control..........................................................................124

6.2.43 SLOTSTS - Slot Status................................................................. .. .. .. ....127

6.2.44 RCTL - Root Control ..............................................................................129

6.2.45 RSTS - Root Status...............................................................................130

6.2.46 LCTL2 - Link Control 2...........................................................................130

6.2.47 LSTS2 - Link Status 2............................................................................132

6.2.48 PEGLC - PCI Express-G Legacy Control ....................................................133

6.3 PCI Device 6 - Extended Configuration................................................................134

6.3.1 VCECH - Virtual Channel Enhanced Capability Header ................................134

6.3.2 PVCCAP1 - Port VC Capability Register 1..................................................134

6.3.3 PVCCAP2 - Port VC Capability Register 2..................................................135

6.3.4 PVCCTL - Port VC Control.......................................................................136

6.3.5 VC0RCAP - VC0 Resource Capability........................................................136

6.3.6 VC0RCTL - VC0 Resource Control............................................................137

6.3.7 VC0RSTS - VC0 Resource Status.............................................................138

Intel® Core

Datasheet Addendum August 2010

4 Document Number: 323178-003

TM

i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel® Celeron® Processor P4505, U3405 Series

Page 5

Figures

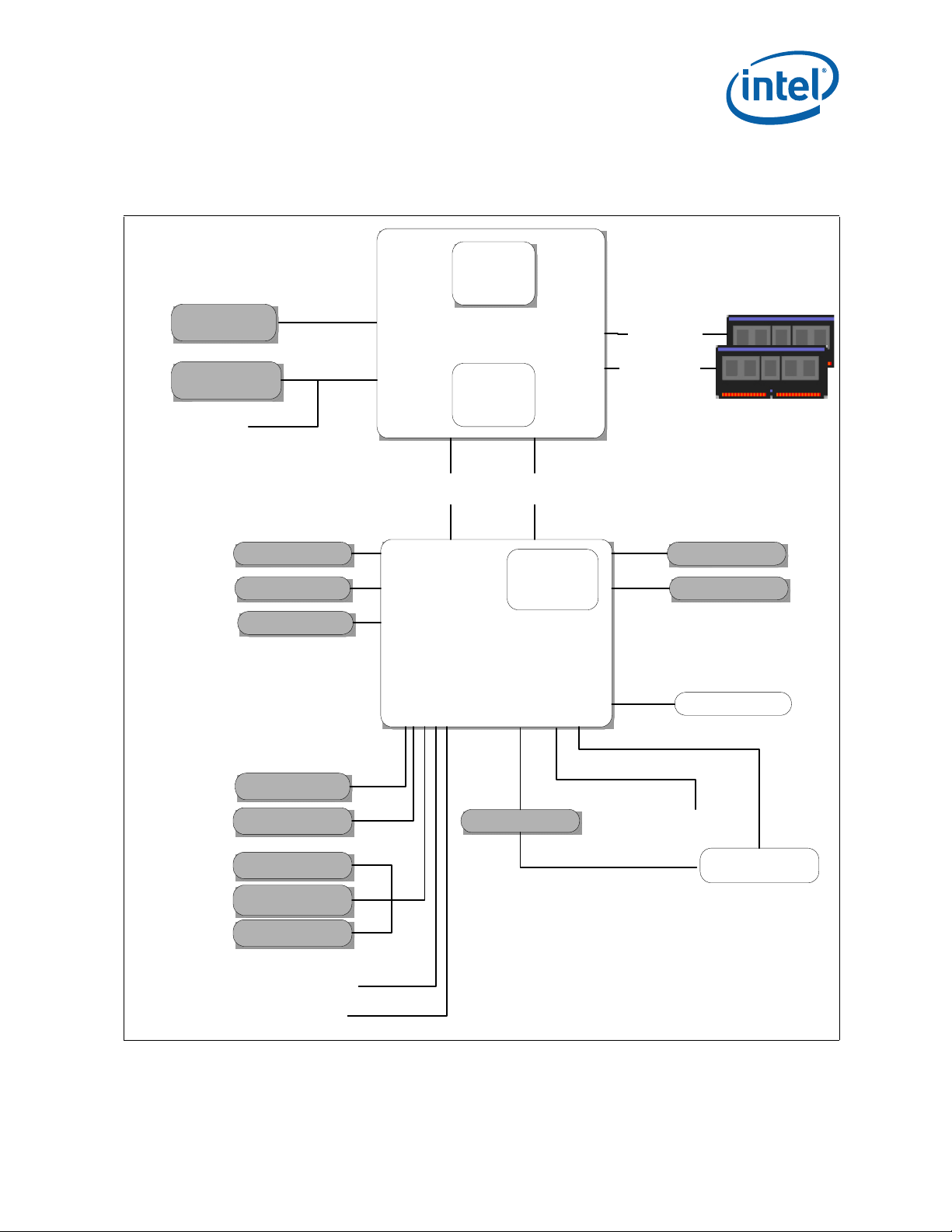

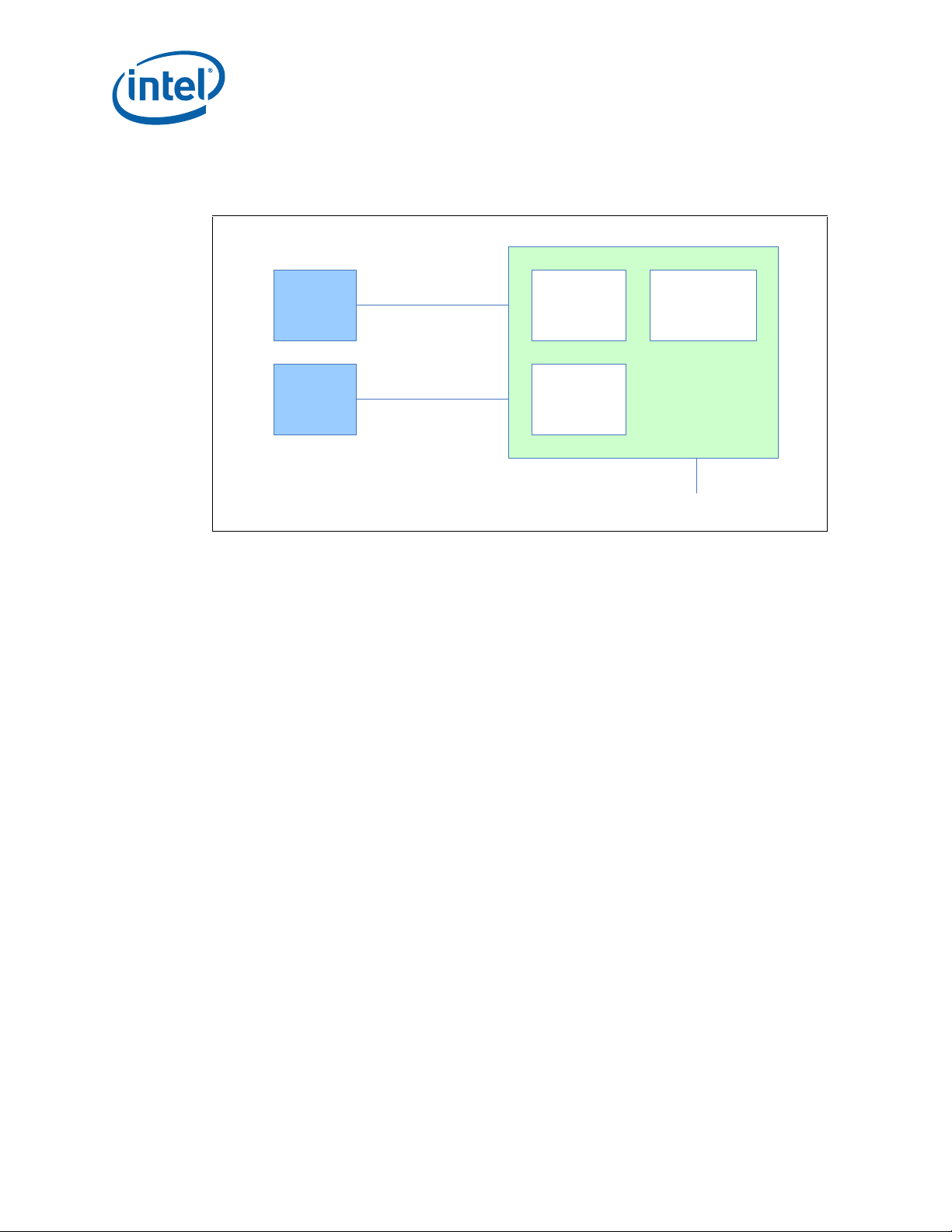

1Intel® CoreTM i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel® Celeron®

Processor P4505, U3405 Series on the Intel

low-power platform............................................................ .. ... ............................. .. ....9

2Intel

®

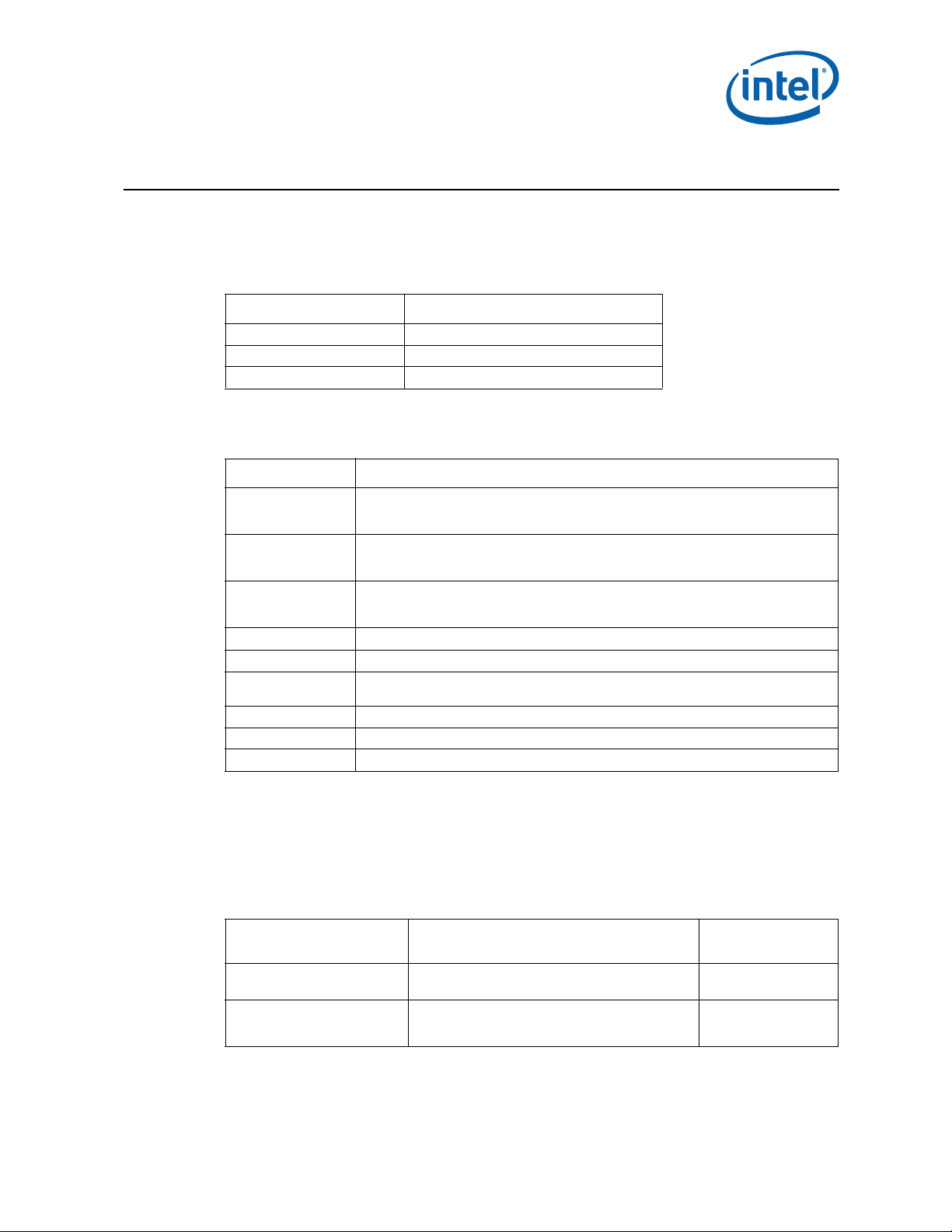

Flex Memory Technology Operation...................................................................17

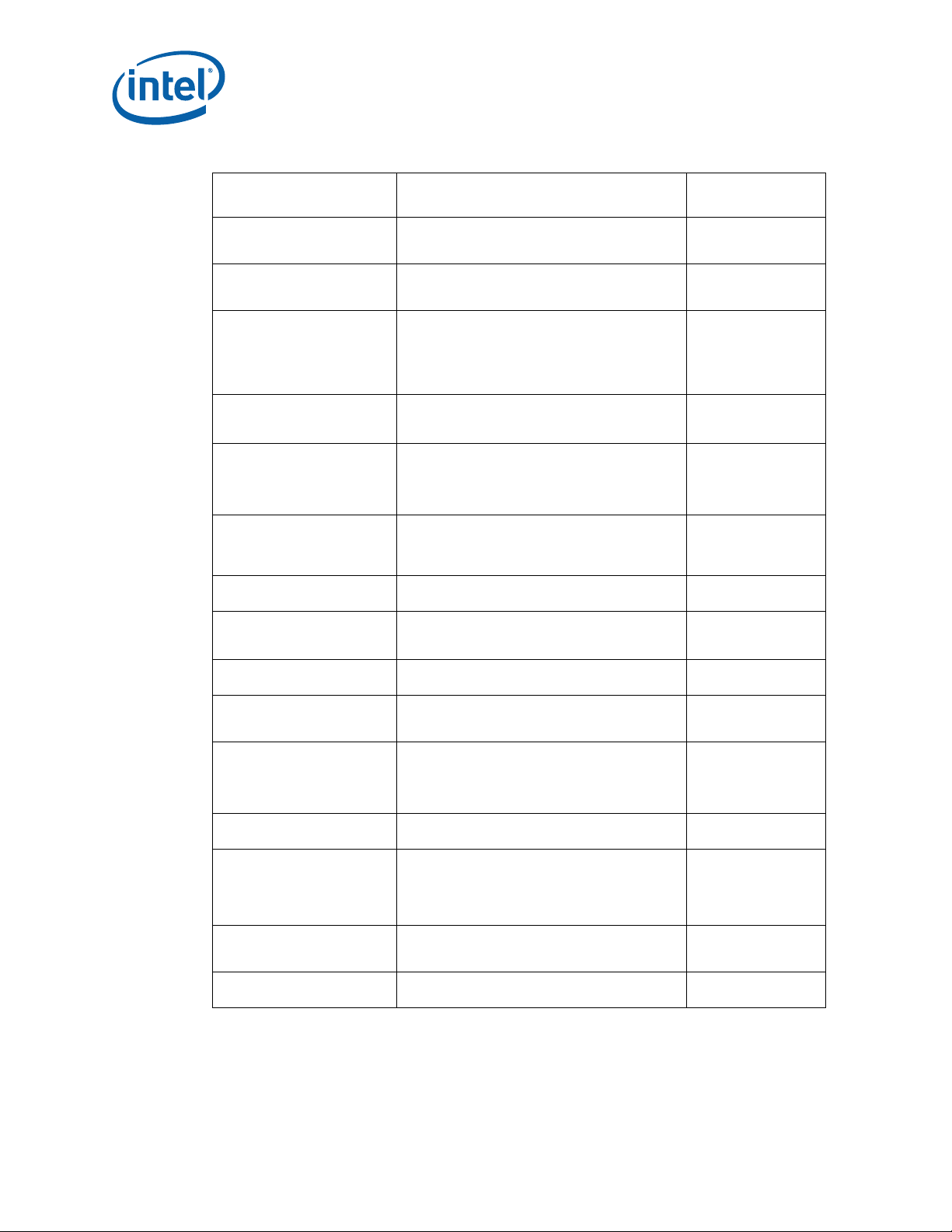

3 Dual-Channel Symmetric (Interleaved) and Dual-Channel Asymmetric Modes ..................18

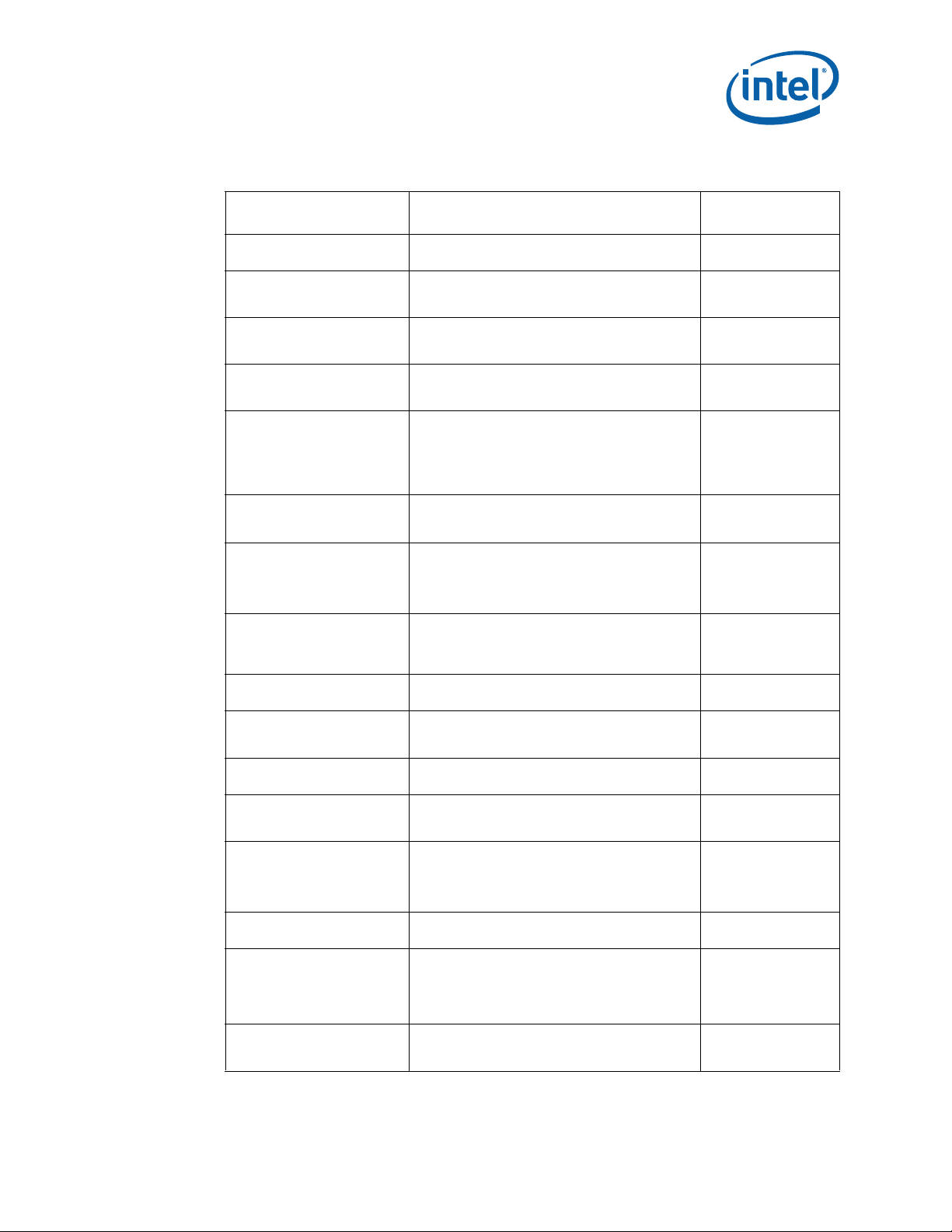

4 PCI Express* Related Register Structures in the Intel

i7-610E, i5-520E, i3-330E and Intel

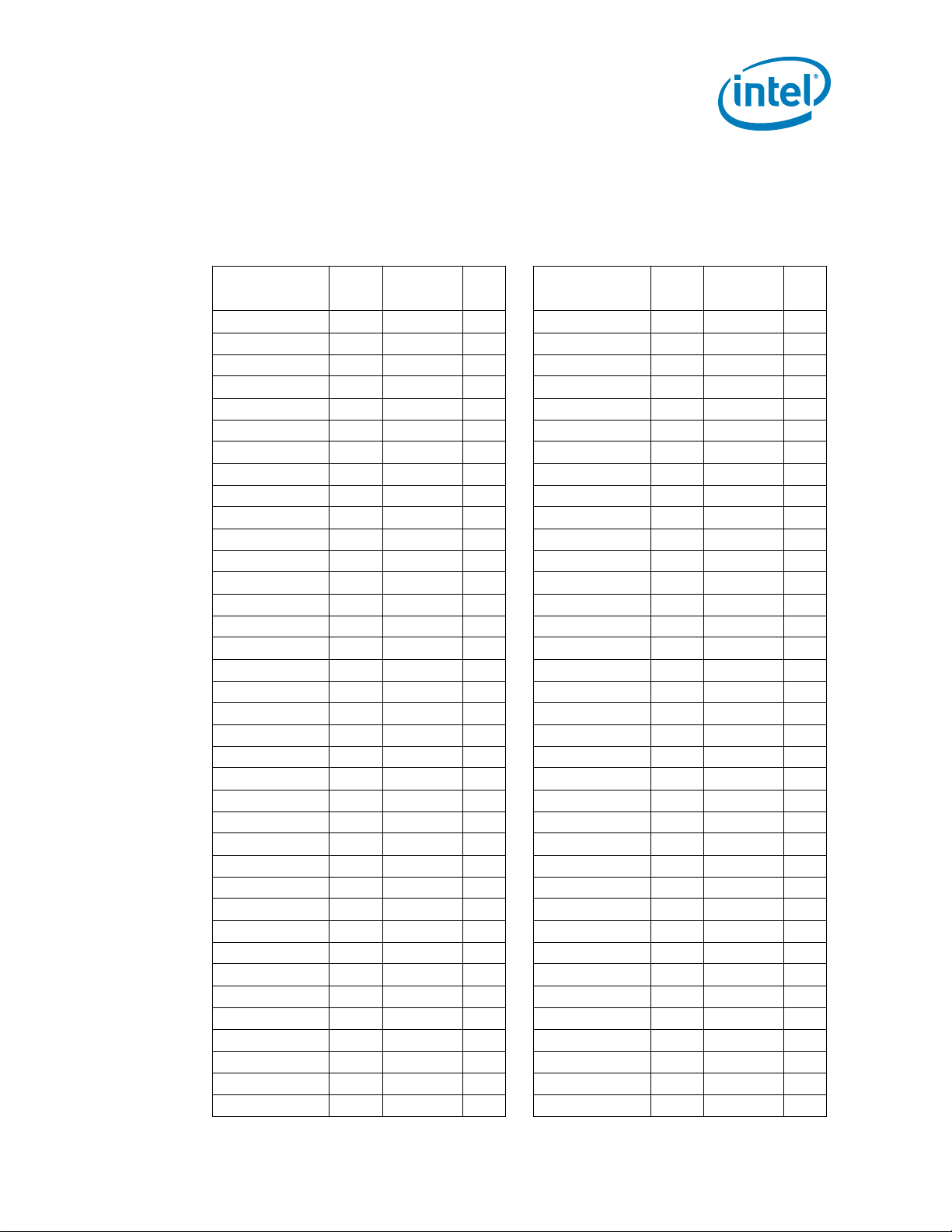

5Intel® Core

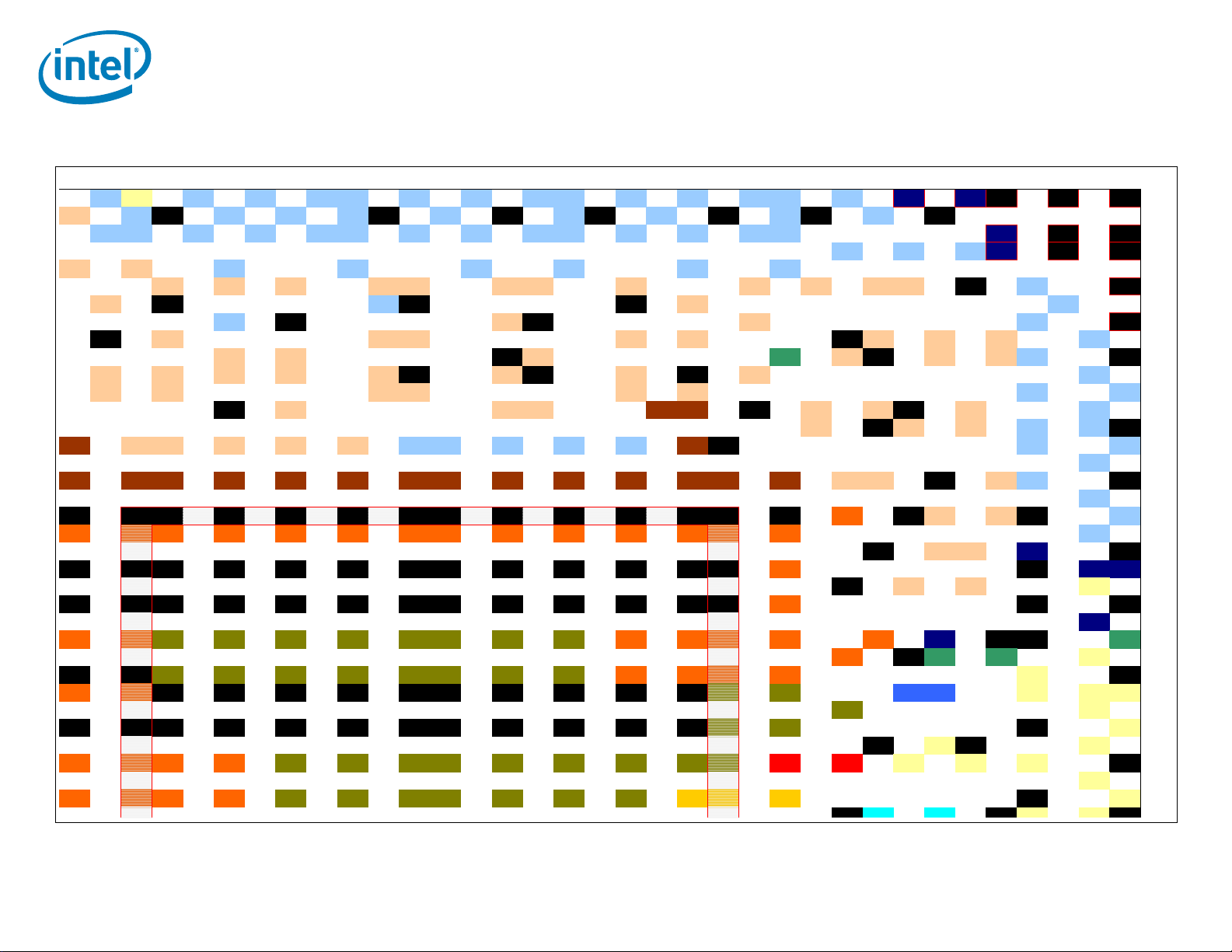

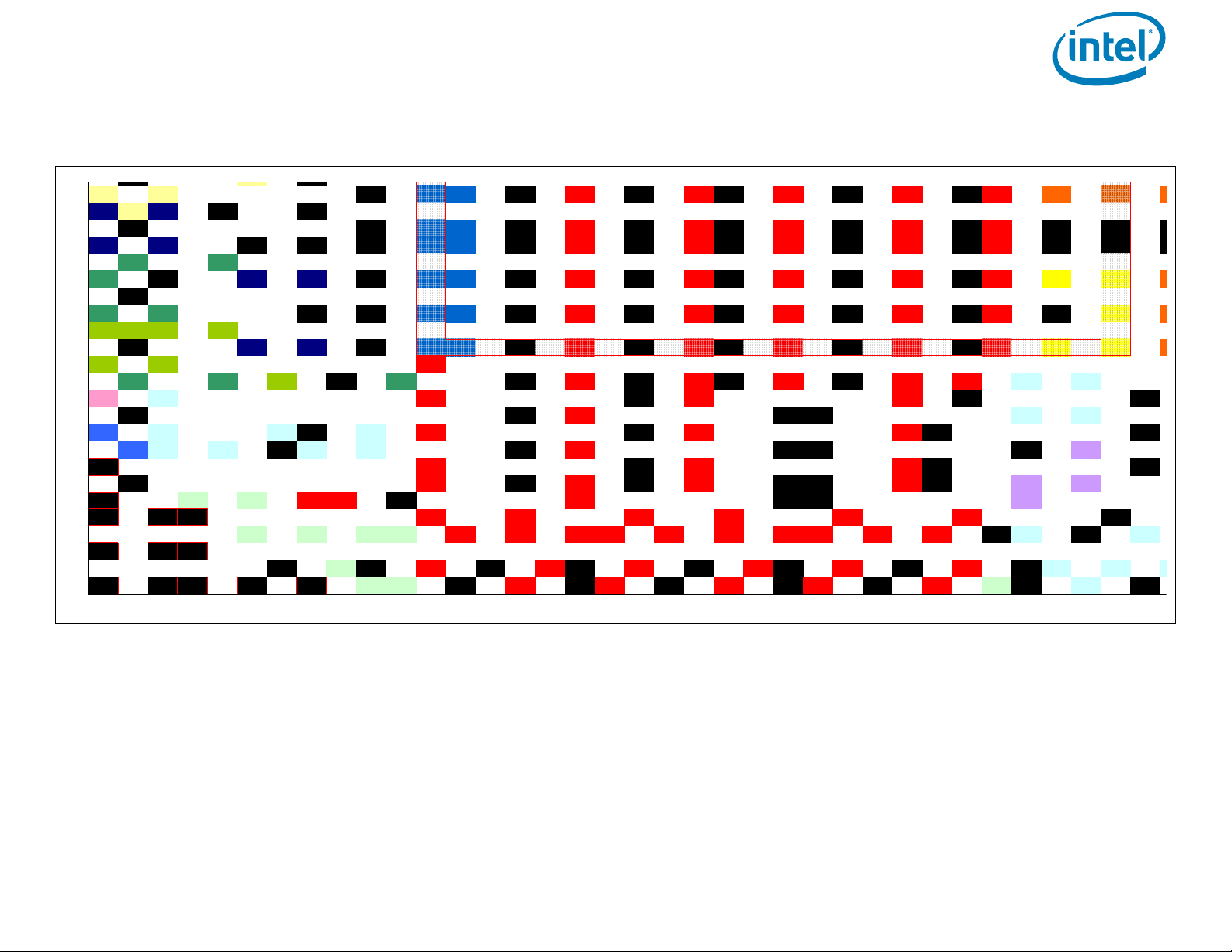

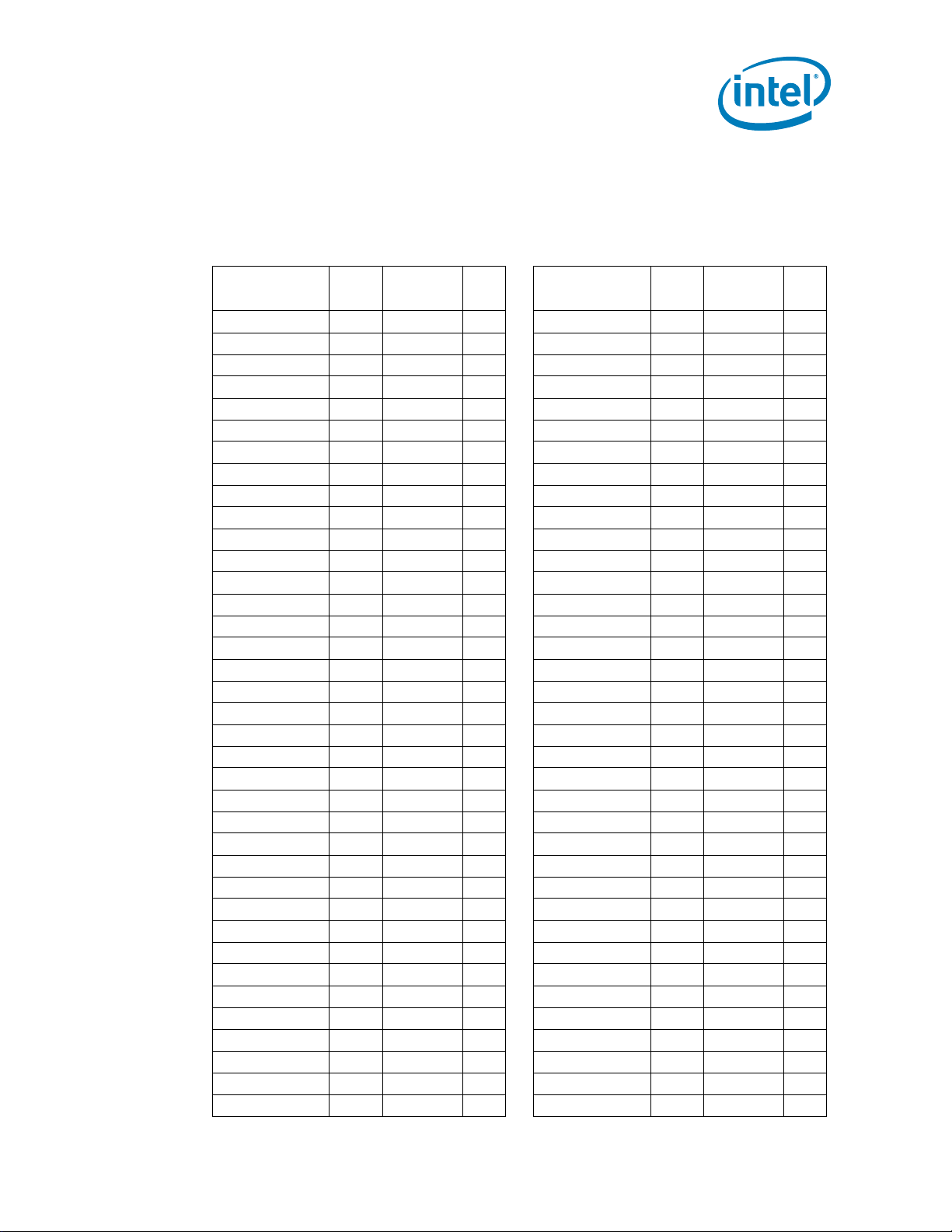

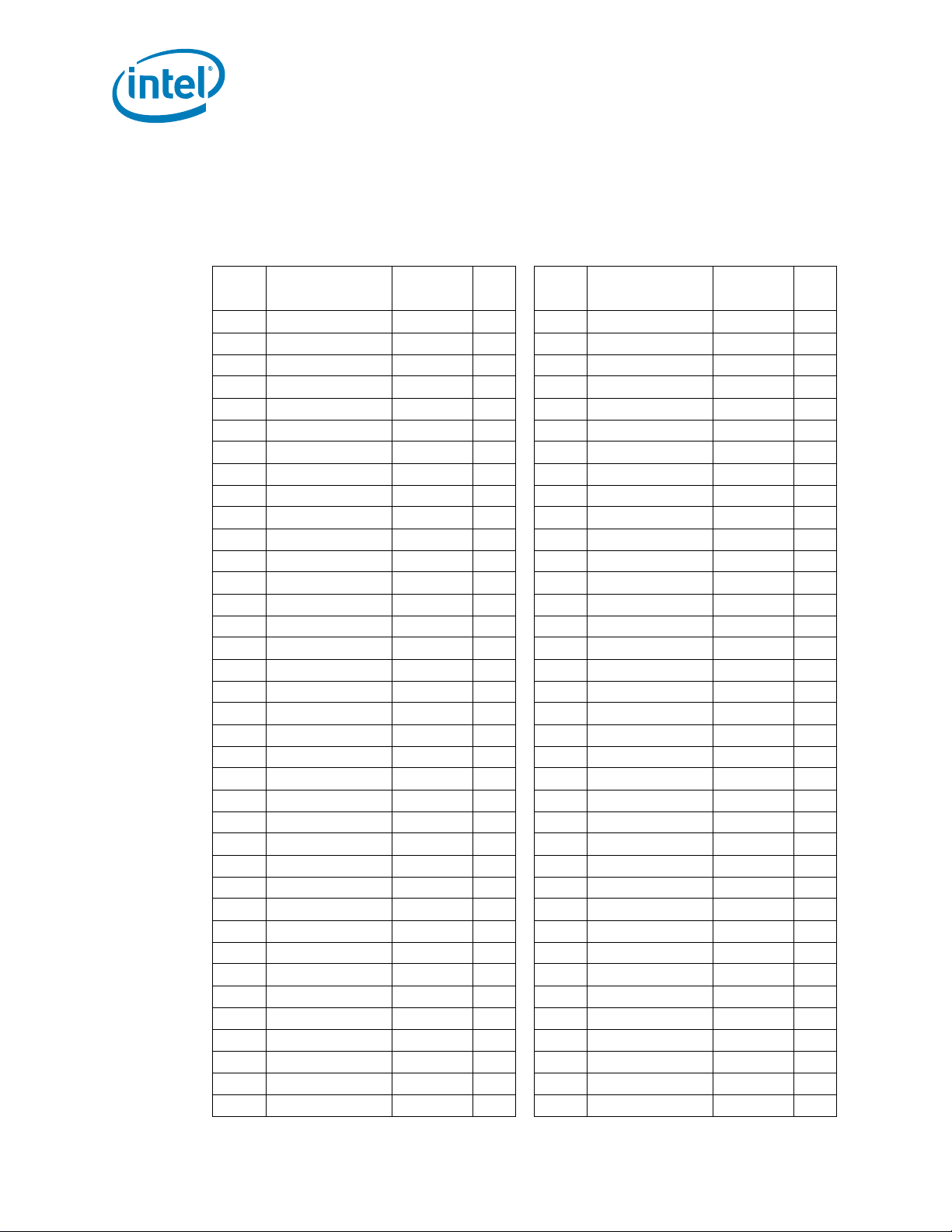

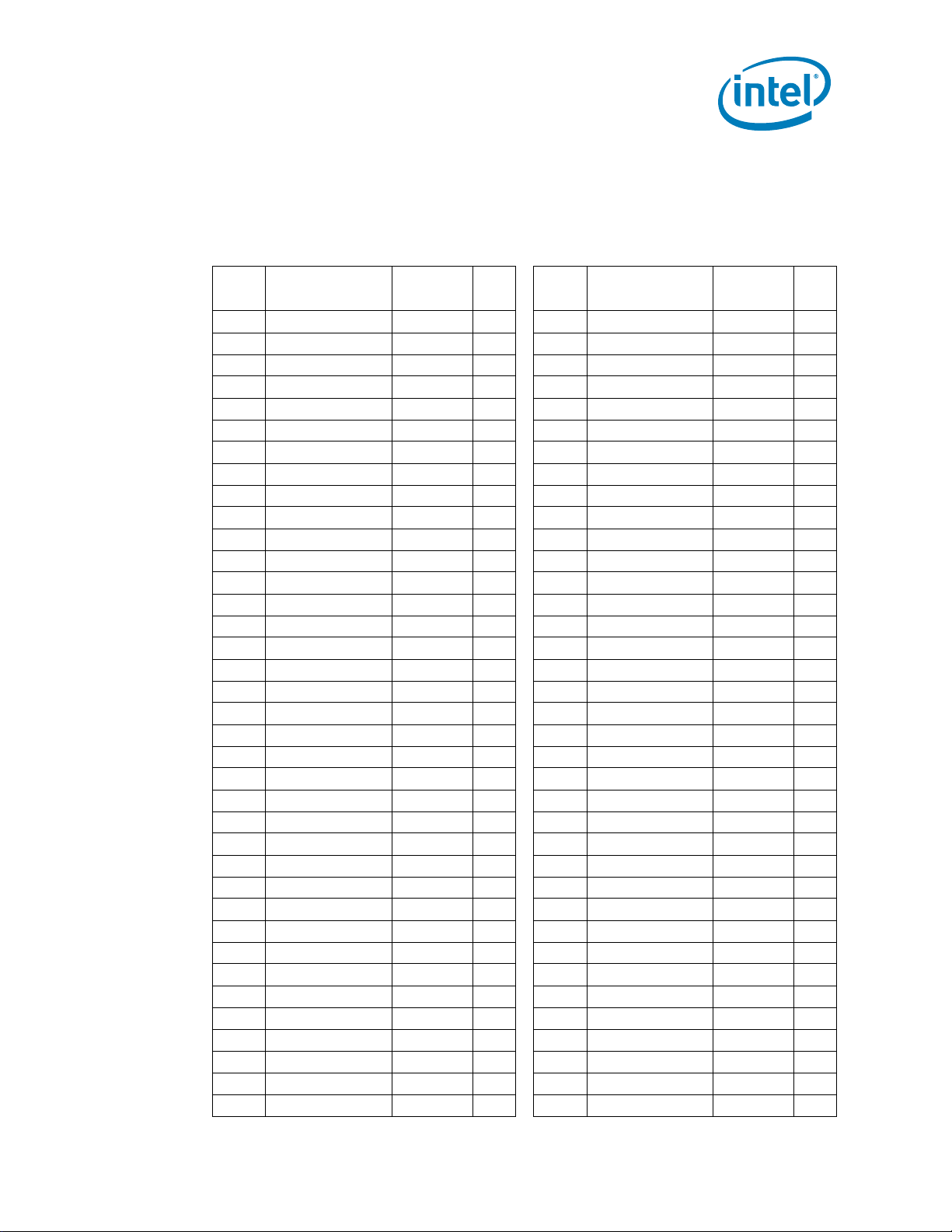

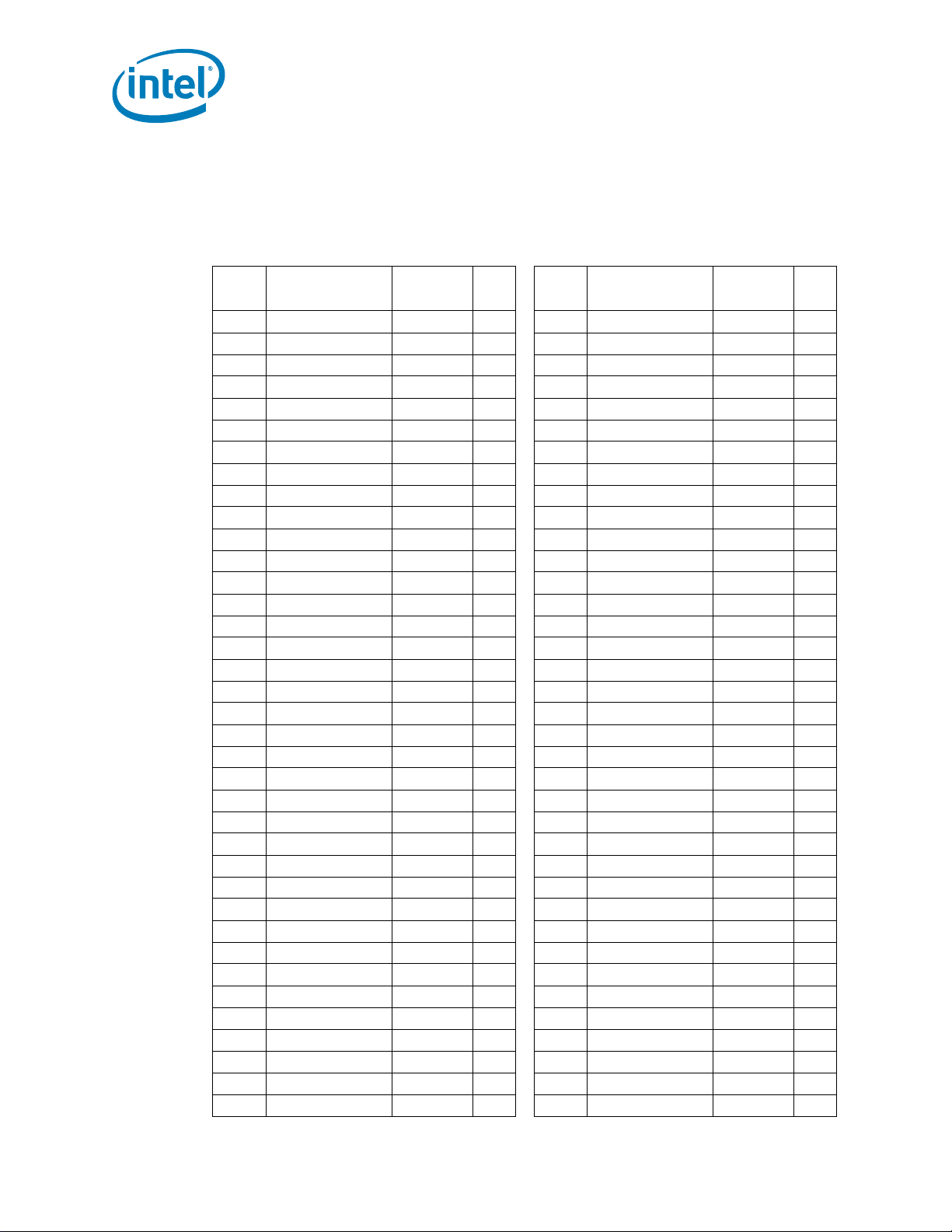

Processor P4505, U3405 Series Ballmap (Top View, Upper-Left Quadrant)....................... 28

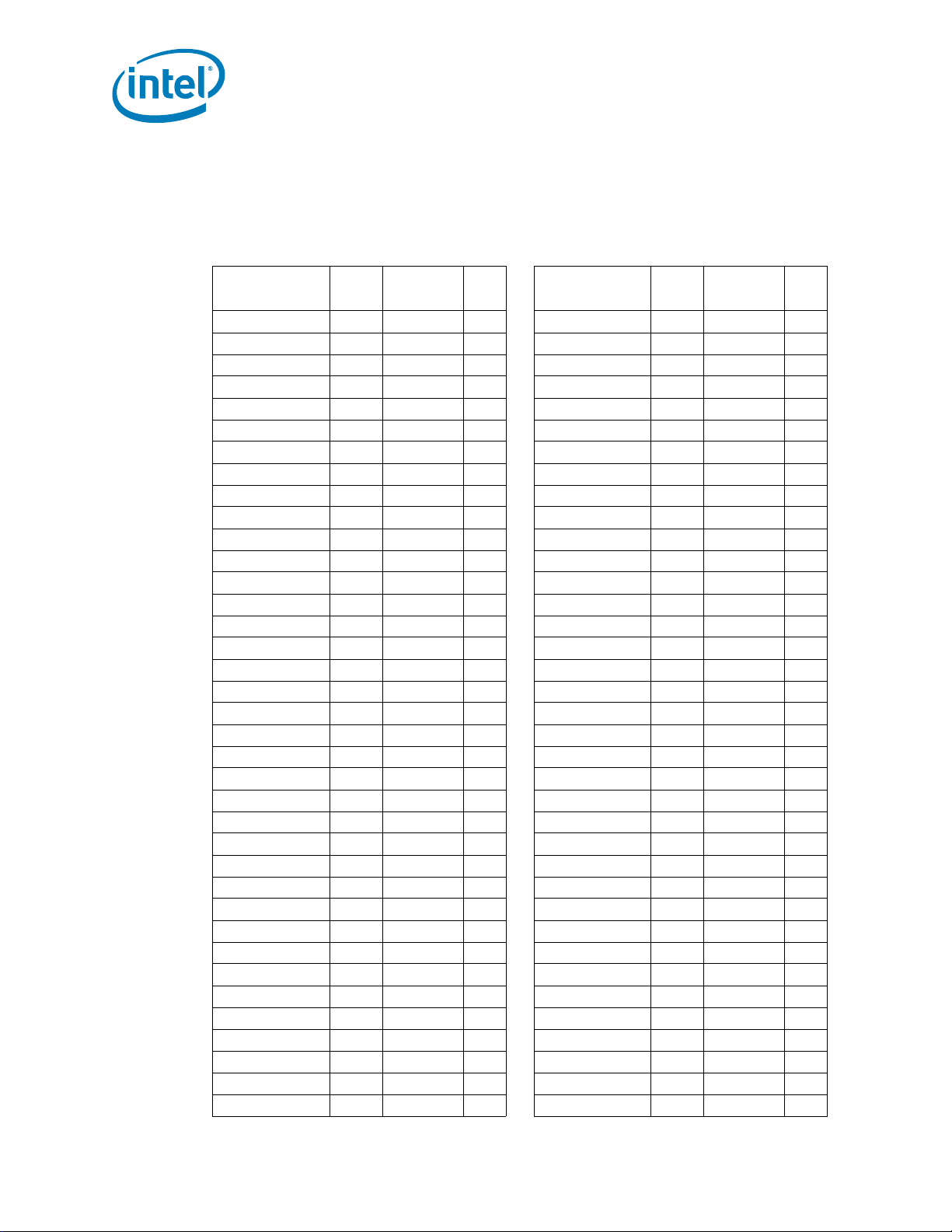

6Intel

7Intel

8Intel

®

Processor P4505, U3405 Series Ballmap (Top View, Upper-Right Quadrant)..................... 29

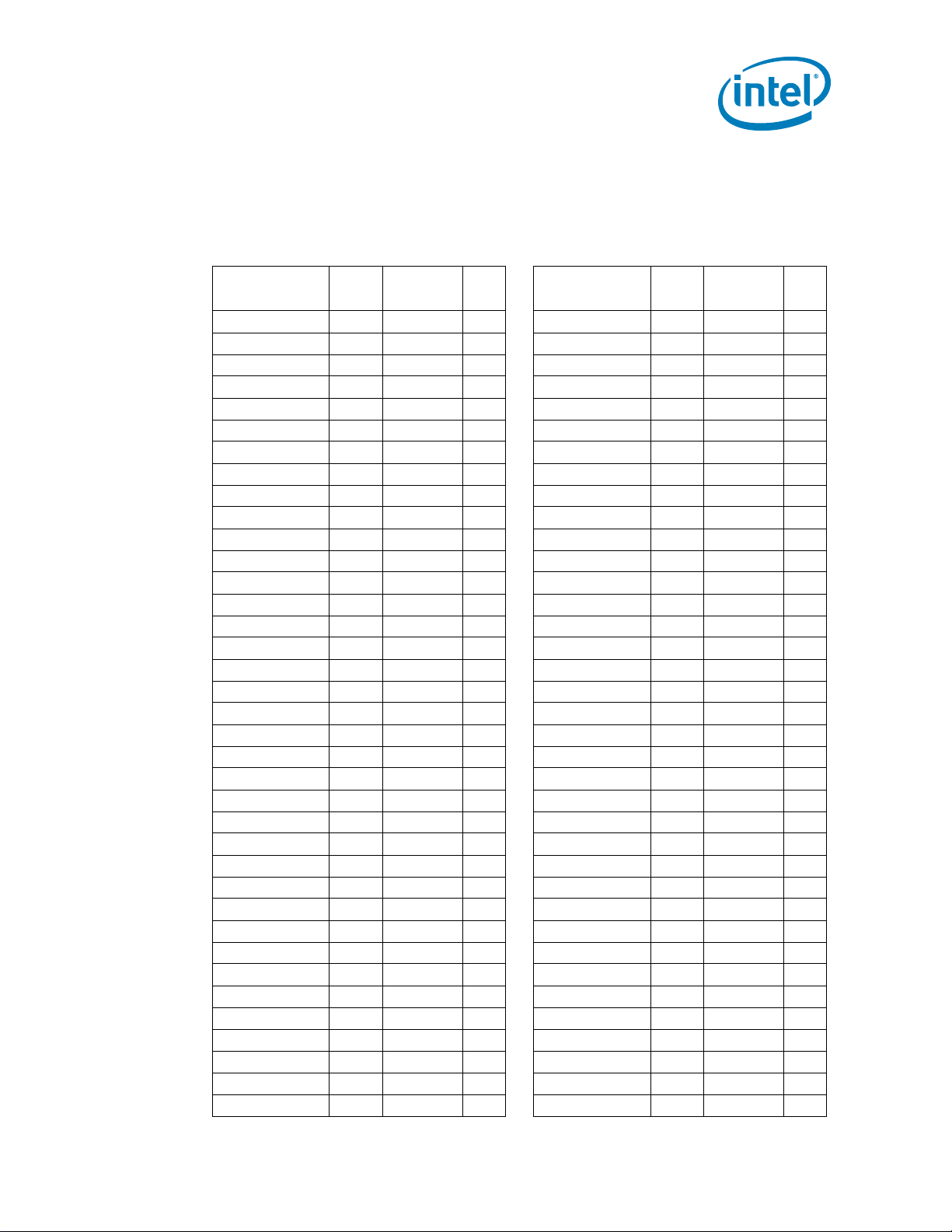

®

Processor P4505, U3405 Series Ballmap (Top View, Lower-Left Quadrant)....................... 30

®

Core

Core

Core

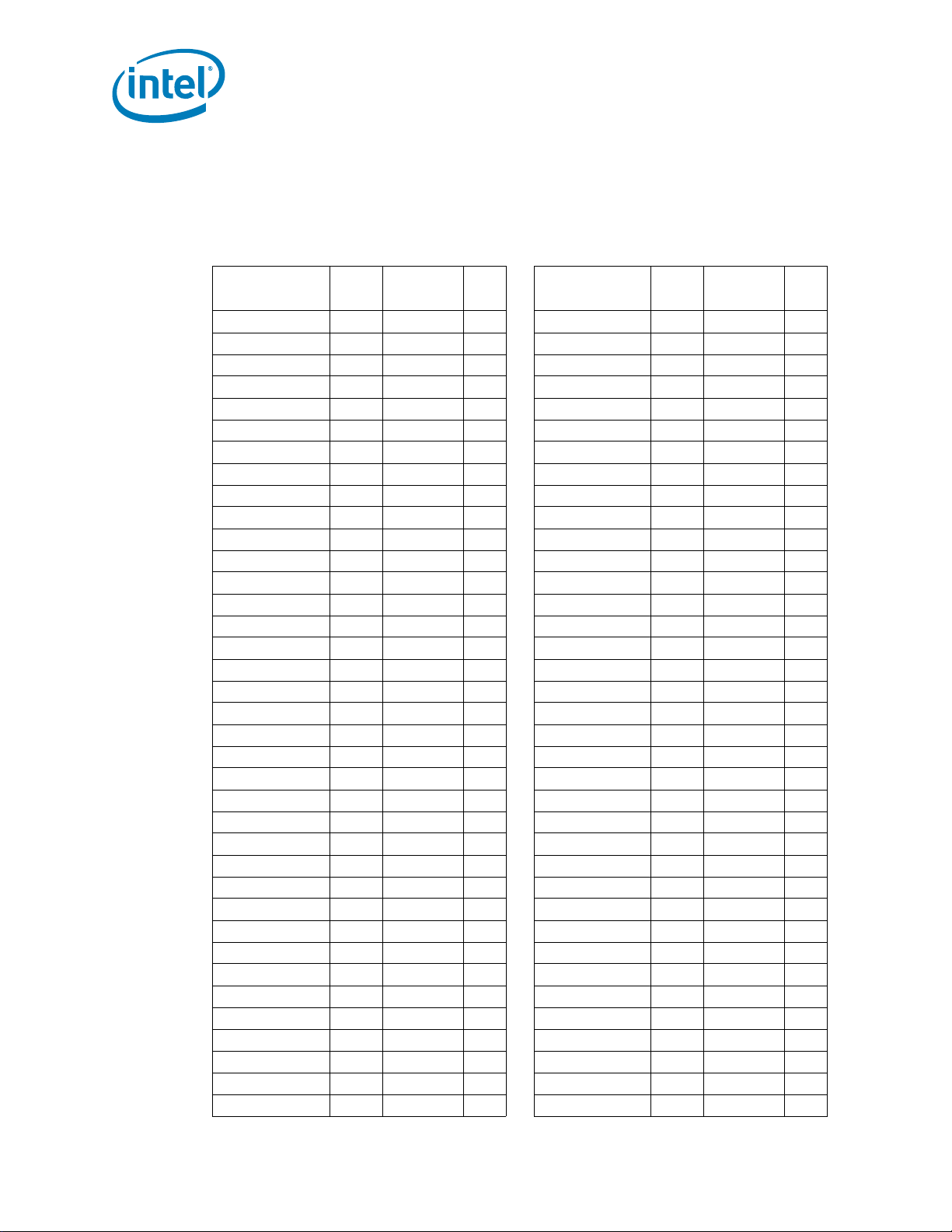

TM

i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel® Celeron®

TM

i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel® Celeron®

TM

i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel® Celeron®

TM

i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel® Celeron®

®

Processor P4505, U3405 Series Ballmap (Top View, Lower-Right Quadrant) ..................... 31

®

CoreTM i7 processor based

®

Core

TM

i7-660UE, i7-620LE/UE,

Celeron® Processor P4505, U3405 Series ............... 20

Tables

1 Processor Documents ........................................................... ... .. .. .............................13

2 PCH Documents.......................................... ......................................................... .... 14

3 Public Specifications............................................. .. ............................. .. .. .................14

4 Supported DIMM Module Configurations......................................................................15

5 DDR3 System Memory Timing Support........................................................................16

6 Signal Description Buffer Types........................................ .. ........................................21

7 Memory Channel A...................................................................................................21

8 Memory Channel B...................................................................................................23

9 Reset and Miscellaneous Signals ................................................................................24

10 Mobile Signal Groups1..............................................................................................25

11 DDR3 Signal Group DC Specifications .........................................................................25

12 Intel

13 Intel

14 Register Terminology................................................................................................70

15 DEVEN - Device Enable Register.................................................................................72

16 Error Status Register........................... ............................. .. .............................. .. .. .... 73

17 Error Command Registers ..................................... .. .. ............................. .. ... .. ............75

18 SMI Command Registers...........................................................................................76

19 Channel 0 Write Data Control Registers.......................................................................77

20 Channel 0 ECC Error Registers.................................................. .. .. .. ...........................78

21 Channel 1 Write Data Control Registers.......................................................................80

22 Channel 1 ECC Error Registers.................................................. .. .. .. ...........................81

23 PCI Device 6 Register........................................ ... ............................. .. .....................82

24 VID6 - Vendor Identification Register..........................................................................85

25 DID6 - Device Identification Register ..........................................................................85

26 PCICMD6 - PCI Command Register.............................................................................86

27 PCISTS6 - PCI Status Register...................................................................................88

28 RID6 - Revision Identification Register ........................................................................90

29 CC6 - Class Code Register........................................... .. .. ..........................................90

30 CL6 - Cache Line Size Register...................................................................................91

31 HDR6 - Header Type Register....................................................................................91

32 PBUSN6 - Primary Bus Number Register......................................................................92

33 SBUSN6 - Secondary Bus Number Register..................................................................92

34 SUBUSN6 - Subordinate Bus Number Register .............................................................93

35 IOBASE6 - I/O Base Address Register.........................................................................94

®

Processor P4505, U3405 Series Ball List by Ball Name...................................................32

®

Core

Core

TM

i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel® Celeron®

TM

i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel® Celeron®

Processor P4505, U3405 Series Ball List by Ball Number................................................49

Intel® Core

August 2010 Datasheet Addendum

Document Number: 323178-003 5

TM

i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel® Celeron® Processor P4505, U3405 Series

Page 6

36 IOLIMIT6 - I/O Limit Address Register.........................................................................94

37 SSTS6 - Secondary Status Register........................ ... ............................... ...................95

38 MBASE6 - Memory Base Address Register....................................................................96

39 MLIMIT6 - Memory Limit Address Register ...................................................................97

40 PMBASE6 - Prefetchable Memory Base Address Register ................................................98

41 PMLIMIT6 - Prefetchable Memory Limit Address Register................................................99

42 PMBASEU6 - Prefetchable Memory Base Address Upper Register...................................100

43 PMLIMITU6 - Prefetchable Memory Limit Address Upper Register ..................................101

44 CAPPTR6 - Capabilities Pointer Register .....................................................................102

45 INTRLINE6 - Interrupt Line Register..........................................................................102

46 INTRPIN6 - Interrupt Pin Register........................................... ..................................103

47 BCTRL6 - Bridge Control Register .............................................................................103

48 PM_CAPID6 - Power Management Capabilities Register................................................105

49 PM_CS6 - Power Management Control/Status Register ................................................106

50 SS_CAPID - Subsystem ID and Vendor ID Capabilities Register ....................................108

51 SS - Subsystem ID and Subsystem Vendor ID Register................................................108

52 MSI_CAPID - Message Signaled Interrupts Capability ID Register..................................109

53 MC - Message Control Register.................................................................................109

54 MA - Message Address Register................................................................................111

55 MD - Message Data Register ....................................................................................111

56 PEG_CAPL - PCI Express-G Capability List Register......................................................112

57 PEG_CAP - PCI Express-G Capabilities Register ...........................................................112

58 DCAP - Device Capabilities Register ..........................................................................113

59 DCTL - Device Control Register.................................................................................114

60 DSTS - Device Status Register .................................................................................115

61 LCAP - Link Capabilities Register...............................................................................116

62 LCTL - Link Control Register.....................................................................................119

63 LSTS - Link Status Register......................................................................................121

64 SLOTCAP - Slot Capabilities Register .........................................................................123

65 SLOTCTL - Slot Control Register ...............................................................................124

66 SLOTSTS - Slot Status Register................................................................................127

67 RCTL - Root Control Register....................................................................................129

68 RSTS - Root Status Register ....................................................................................130

69 LCTL2 - Link Control 2 Register ................................................................................130

70 LSTS2 - Link Status 2 Register.................................................................................132

71 PEGLC - PCI Express-G Legacy Control Register..........................................................133

72 PCI Device 6 - Extended Configuration ......................................................................134

73 VCECH - Virtual Channel Enhanced Capability Header..................................................134

74 PVCCAP1 - Port VC Capability Register 1 ....................................................................135

75 PVCCAP2 - Port VC Capability Register 2 ....................................................................136

76 PVCCTL - Port VC Control ........................................................................................136

77 VC0RCAP - VC0 Resource Capability..........................................................................136

78 VC0RCTL - VC0 Resource Control..............................................................................138

79 VC0RSTS - VC0 Resource Status ..............................................................................139

Intel® Core

Datasheet Addendum August 2010

6 Document Number: 323178-003

TM

i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel® Celeron® Processor P4505, U3405 Series

Page 7

Revision History

Date Revision Description

January 2010 001 • Initial release of this document.

April 2010 002

August 2010 003

• Added information for the Intel® Celeron® Processor P4500 and P4505 Series.

• Corrected first bullet in Section 2.1.1 to “No support for mixed ECC and non-ECC DIMM

configurations.”

®

• Added information for the Intel

• Removed all references to Celeron® Processor P4500 since it is a PGA package and does not

relate to this document (was included by error in last revision).

• CMD mode for DDR3 is restated to 1n instead of 1n and 2n

CoreTM i7-660UE, i3-330E and Celeron® Processor U3405

Intel® Core

August 2010 Datasheet Addendum

Document Number: 323178-003 7

TM

i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel® Celeron® Processor P4505, U3405 Series

Page 8

Introduction and Features Summary

1 Introduction and Features

Summary

1.1 Introduction

This Datasheet Addendum is a supplement to the Intel® CoreTM i7-600, i5-500 and i3-

300 Mobile Processor Series Datasheet. It contains the additional DC and AC electrical

specifications, signal integrity, differential signaling specifications, pinout and signal

definitions, interface functional descriptions, additional feature information and

configuration registers pertinent to the implementation and operation of the Intel

TM

Core

Processor P4505, U3405 Series on its respective platform.

Intel

Processor P4505, U3405 Series is the next generation of 64-bit, multi-core mobile

processor built on a 32- nanometer process technology. Throughout this document,

Intel

Processor P4505, U3405 Series may be referred to as simply the processor. The

processor is designed for a two-chip platform as opposed to the traditional three-chip

platforms (processor, GMCH, and ICH). The two-chip platform consists of a processor

and the Platform Controller Hub (PCH) and enables higher performance, lower cost,

easier validation, and improved x-y footprint. The PCH may also be referred to as

Mobile Intel® 5 Series Chipset (formerly Ibex Peak-M). Intel

620LE/UE, i7-610E, i5-520E, i3-330E and Intel

Series is designed for the Intel

offered in a BGA1288 package.

i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel® Celeron®

®

®

Core

Core

TM

i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel® Celeron®

TM

i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel® Celeron®

®

®

CoreTM i7 processor based low-power platform and is

Celeron® Processor P4505, U3405

®

Core

TM

i7-660UE, i7-

®

Included in this family of processors is an integrated graphics and memory controller

die on the same package as the processor core die. This two-chip solution of a

processor core die with an integrated graphics and memory controller die is known as a

multi-chip package (MCP) processor.

Note: Integrated graphics and memory controller die is built on 45-nanometer process

technology.

®

TM

Core

Intel

Datasheet Addendum August 2010

8 Document Number: 323178-003

i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel® Celeron® Processor P4505, U3405 Series

Page 9

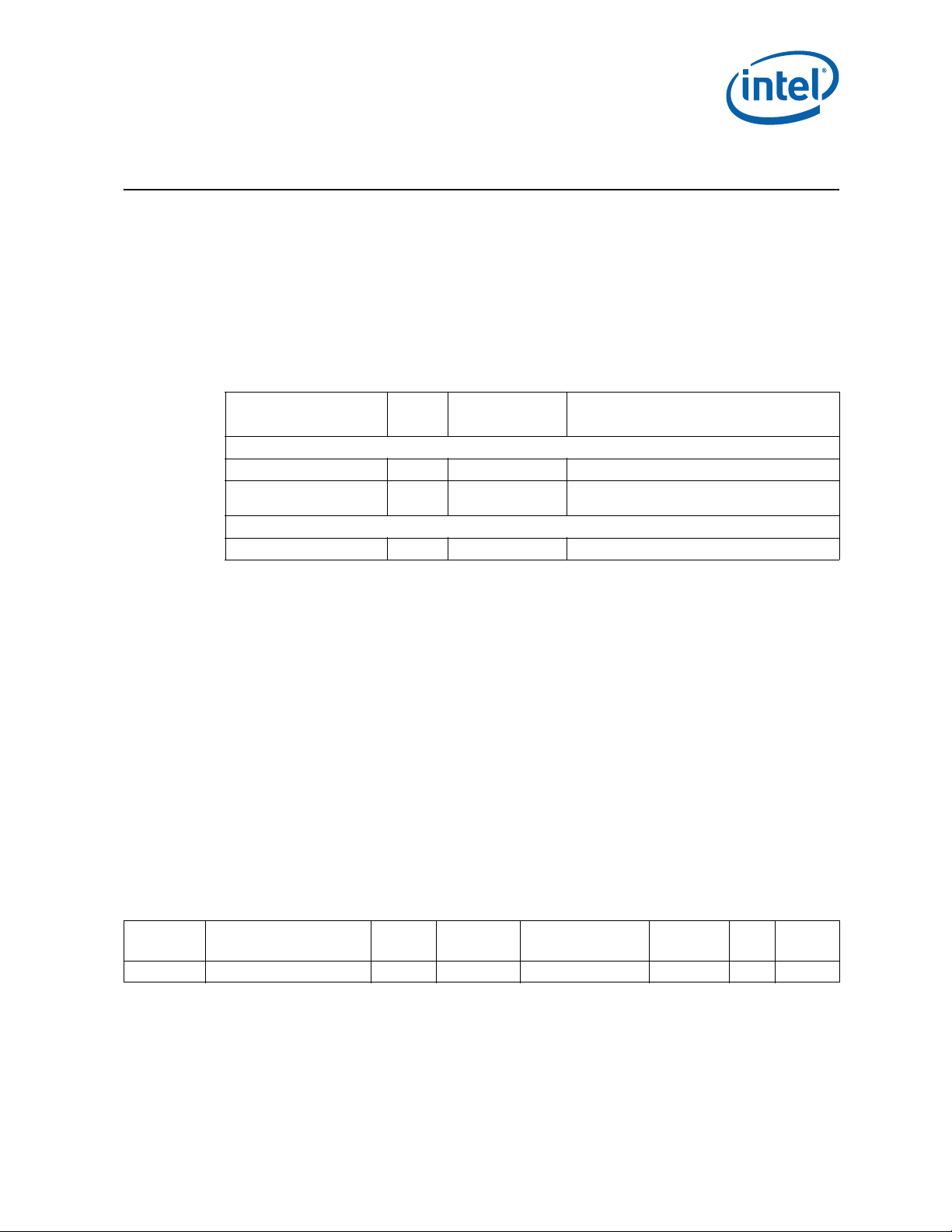

Introduction and Features Summary

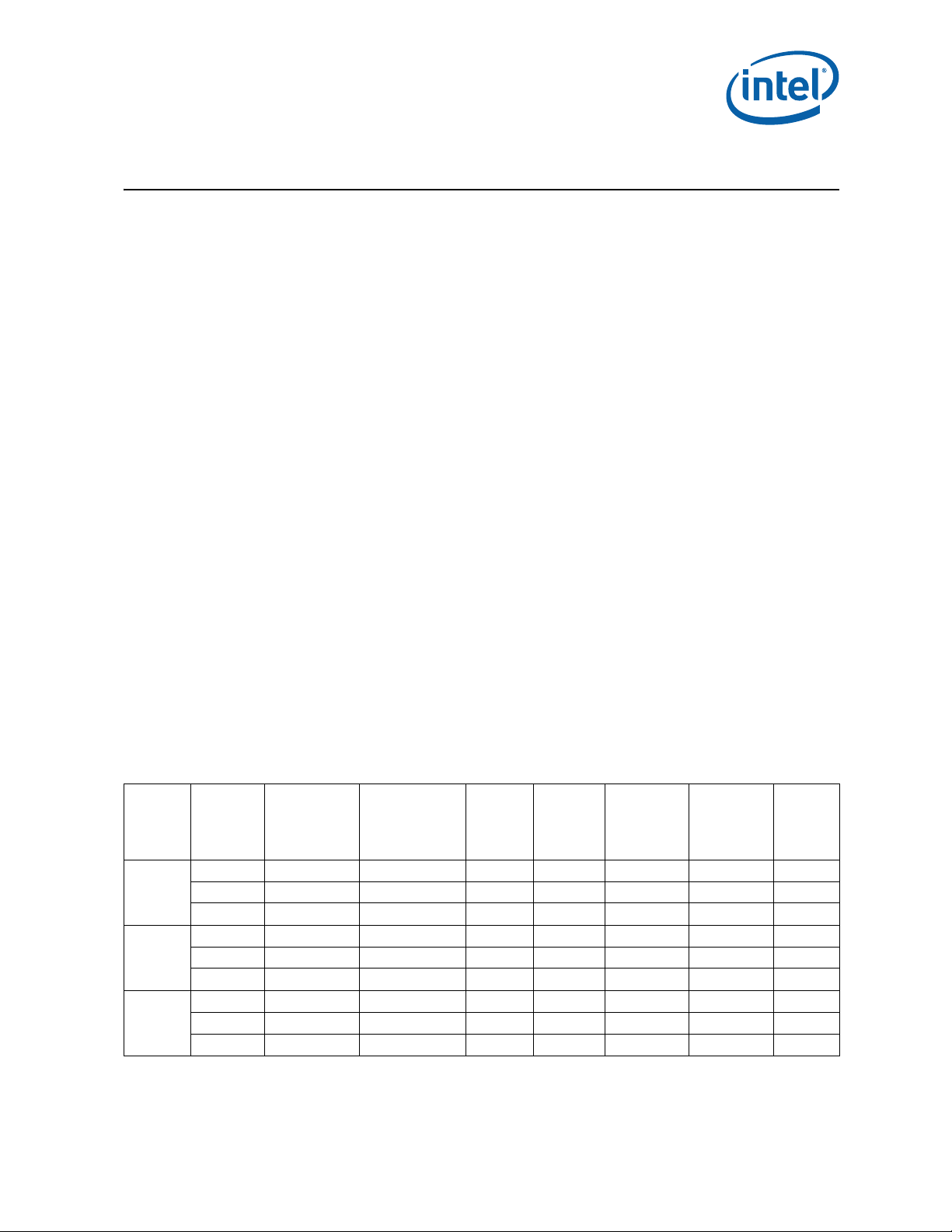

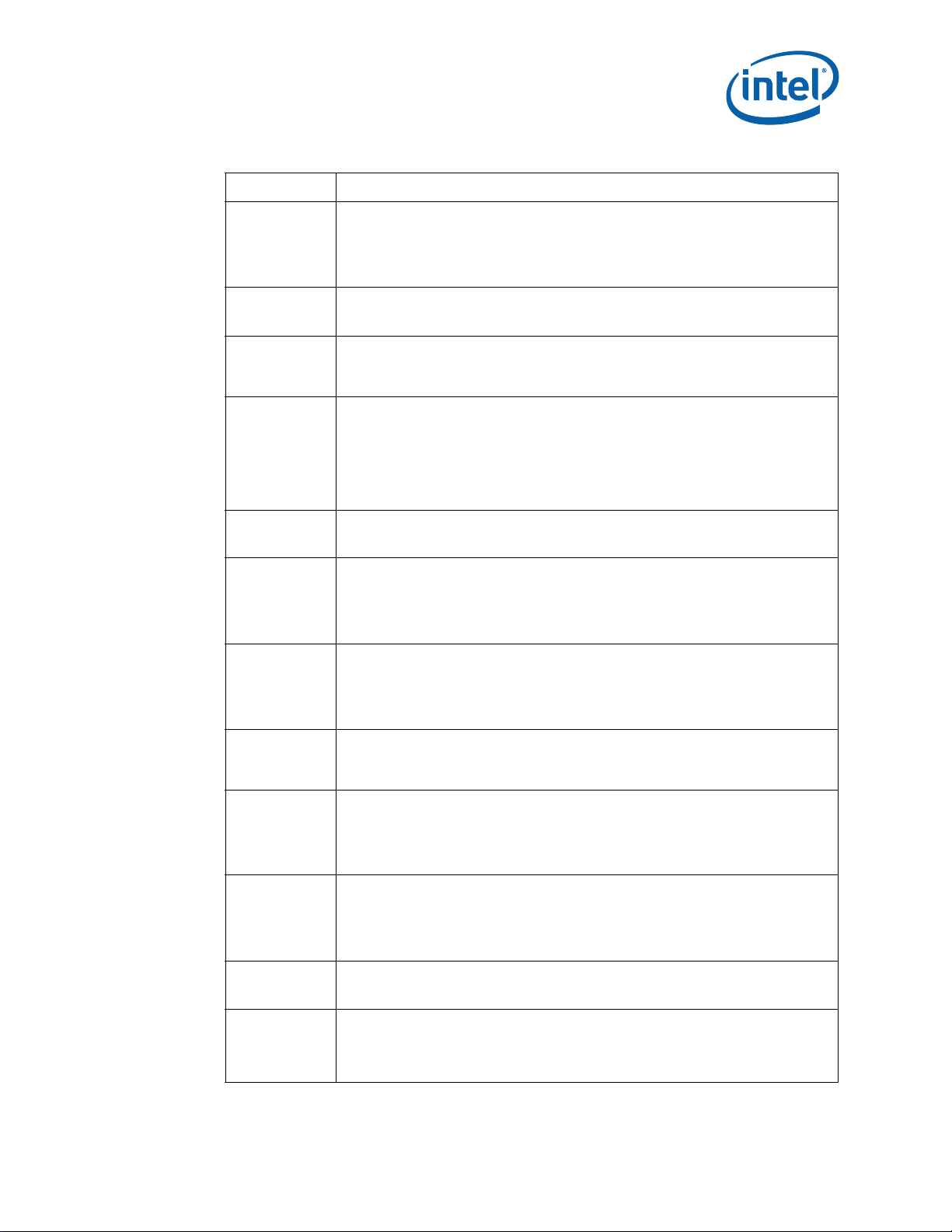

Intel CoreTM i7/i5/i3 and Celeron

Processor

(MCP Processor)

Discrete Graphics

(PEG)

Analog CRT

Gigabit

Network Connection

USB 2.0

Intel® HD Audio

FWH

TPM 1.2

Super I/O

PCI

Serial ATA

Mobile Intel 5 Series Chipset

PCH

DDR3 DIMMs

PCI Express* x16

14 Ports

PCI

6 Ports

3 Gb/s

SPI

Digital Display x 3

Intel® Flexible

Display Interface

SPI Flash

LPC

SMBUS 2.0

PECI

GPIO

OR

GPU, Memory

Controller

Dual-core

Processor

800/1066 MT/s

2 Channels

1 DIMM / Channel

DMI2

(x4)

LVDS Flat Panel

Intel®

Management

Engine

Embedded

DisplayPort* (eDP)

PCI Express x 1

PCI Express*

Controller Link 1

8 PCI Express* x1

Ports

(2.5 GT/s)

Figure 1. Intel® CoreTM i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel®

Celeron® Processor P4505, U3405 Series on the Intel

®

CoreTM i7 processor

based low-power platform

Intel® Core

August 2010 Datasheet Addendum

Document Number: 323178-003 9

TM

i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel® Celeron® Processor P4505, U3405 Series

Page 10

1.2 Interfaces

1.2.1 System Memory Support

• One or two channels of DDR3 memory with a maximum of one DIMM per channel

• Single- and dual-channel memory organization modes

• Data burst length of eight for all memory organization modes

• Memory DDR3 data transfer rates of 800 and 1066 MT/s

• 64-bit wide channels (72-bit wide including ECC)

• DDR3 I/O Voltage of 1.5 V

• Supports ECC and non-ECC, unbuffered DDR3 DIMMs

— Mixing of ECC and Non-ECC DIMMS is not supported

• Theoretical maximum memory bandwidth of:

— 12.8 GB/s in dual-channel mode assuming DDR3 800 MT/s

— 17.1 GB/s in dual-channel mode assuming DDR3 1066 MT/s

• 1-Gb, and 2-Gb DDR3 DRAM technologies for x8 and x16 devices

• Using 2-Gb device technologies, the largest memory capacity possible is 8 GB,

assuming dual-channel mode with two x8, dual-rank, un-buffered, DIMM memory

configuration.

• Up to 32 simultaneous open pages, 16 per channel (assuming 4 Ranks of 8 Bank

Devices)

• Memory organizations:

— Single-channel modes

— Dual-channel modes

Dual-channel symmetric (Interleaved)

Dual-channel asymmetric

®

Flex Memory Technology

Intel

• Command launch mode of 1n

• Partial Writes to memory using Data Mask (DM) signals

• On-Die T e rmination (ODT)

®

•Intel

Fast Memory Access (Intel® FMA):

— Just-in-Time Command Scheduling

—Command Overlap

— Out-of-Order Scheduling

Introduction and Features Summary

1.2.2 PCI Express*

• The processor PCI Express* port(s) are fully-compliant to the PCI Express Base

Specification, Revision 2.0 at 2.5GT/s.

• The processor supports:

— One 16-lane PCI Express port for graphics or I/O.

— Two 8-lane PCI Express ports for graphics or I/O.

• PCI Express Port 0 is mapped to PCI Device 1.

• PCI Express Port 1 is mapped to PCI Device 6.

®

TM

Core

Intel

Datasheet Addendum August 2010

10 Document Number: 323178-003

i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel® Celeron® Processor P4505, U3405 Series

Page 11

Introduction and Features Summary

1.3 Package

The Intel Core i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel Celeron

Processor P4505, U3405 Series are available on a 34 x 28 mm BGA package

(BGA1288).

Note: Although the BGA1288 package is shared with Intel

UM/LM, i5-540M, i5-520M/UM and i5-430M Processor Series they are not ball-out

compatible.

®

CoreTM i7-640UM/LM, i7-620M/

Intel® Core

August 2010 Datasheet Addendum

Document Number: 323178-003 11

TM

i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel® Celeron® Processor P4505, U3405 Series

Page 12

1.4 Terminology

Term Description

BLT Block Level Transfer

CRT Cathode Ray Tube

DDR3 Third generation Double Data Rate SDRAM memory technology

DP DisplayPort*

DMA Direct Memory Access

DMI Direct Media Interface

DTS Digital Thermal Sensor

ECC Error Correction Code

eDP* Embedded DisplayPort*

®

Intel

DPST Intel® Display Power Saving Technology

Enhanced Intel

SpeedStep

Execute Disable Bit

EU Execution Unit

(G)MCH Legacy component - Graphics Memory Controller Hub.

GPU Graphics Processing Unit

ICH

IMC Integrated Memory Controller

Intel

Intel

Intel

Intel

Technology

ITPM Integrated Trusted Platform Module

IOV I/O Virtualization

LCD Liquid Crystal Display

LVDS

MCP Multi-Chip Package

NCTF

PCH

PECI Platform Environment Control Interface

®

Technology

®

64 Technology 64-bit memory extensions to the IA-32 architecture.

®

FDI Intel® Flexible Display Interface.

®

TXT Intel® Trusted Execution Technology

®

Virtualization

Introduction and Features Summary

Technology that provides power management capabilities to laptops.

The Execute Disable bit allows memory to be marked as executable or nonexecutable, when combined with a supporting operating system. If code

attempts to run in non-executable memory the processor raises an error to the

operating system. This feature can prevent some classes of viruses or worms

that exploit buffer overrun vulnerabilities and can thus help improve the overall

security of the system. See the Intel® 64 and IA-32 Architectures Software

Developer's Manuals for more detailed information.

The legacy I/O Controller Hub component that contains the main PCI interface,

LPC interface, USB2, Serial ATA, and other I/O functions. It communicates with

the legacy (G)MCH over a proprietary interconnect called DMI.

Processor virtualization which when used in conjunction with Virtual Machine

Monitor software enables multiple, robust independent software environments

inside a single platform.

Low Voltage Differential Signaling

A high speed, low power data transmission standard used for display connections

to LCD panels.

Non-Critical to Function: NCTF locations are typically redundant ground or noncritical reserved, so the loss of the solder joint continuity at end of life co nditions

will not affect the overall product functionality.

Platform Controller Hub. The new 2009 chipset with centralized platform

capabilities including the main I/O interfaces along with display connectivity,

audio features, power management, manageability, security and storage

features. The PCH may also be referred to using the code name Ibex Peak.

®

TM

Core

Intel

Datasheet Addendum August 2010

12 Document Number: 323178-003

i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel® Celeron® Processor P4505, U3405 Series

Page 13

Introduction and Features Summary

Term Description

PEG

Processor The 64-bit, single-core or multi-core component (package)

Processor Core

Rank

SCI System Control Interrupt. Used in ACPI protocol.

Storage Conditions

TAC Thermal Averaging Constant

TDP Thermal Design Power

TOM Top of Memo ry

TTM Time-To-Market

V

CC

V

SS

V

AXG

V

TT

V

DDQ

VLD Variable Length Decoding

x1 Refers to a Link or Port with one Physical Lane

x4 Refers to a Link or Port with four Physical Lanes

x8 Refers to a Link or Port with eight Physical Lanes

x16 Refers to a Link or Port with sixteen Physical Lanes

PCI Express* Graphics. External Graphics using PCI Express Architecture. A

high-speed serial interface whose configuration is software compatible with the

existing PCI specifications.

The term “processor core” refers to Si die itself which can contain multiple

execution cores. Each execution core has an instruction cache, dat a cache, and

256-KB L2 cache. All execution cores share the L3 cache.

A unit of DRAM corresponding four to eight devices in parallel, ignoring ECC.

These devices are usually, but not always, mounted on a single side of a SODIMM.

A non-operational state. The processor may be installed in a platform, in a tray,

or loose. Processors may be sealed in packaging or exposed to free air. Under

these conditions, processor landings should not be connected to any supply

voltages, have any I/Os biased or receive any clocks. Upon exposur e to “free air”

(i.e., unsealed packaging or a device removed from packaging material) the

processor must be handled in accordance with moisture sensitivity labeling

(MSL) as indicated on the packaging material.

Processor core power supply

Processor ground

Graphics core power supply

L3 shared cache, memory controller, and processor I/O power rail

DDR3 power rail

1.5 Related Documents

Refer to the documents in Table 1 for additional information.

Table 1. Processor Documents

Document

Intel® CoreTM i7-600, i5-500 and i3-300 Mobile Processor Series Datasheet http://www.intel.com

®

Intel

Celeron

Update

Intel® Core

August 2010 Datasheet Addendum

Document Number: 323178-003 13

TM

i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel® Celeron® Processor P4505, U3405 Series

TM

Core

i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel®

®

Processor P4505, U3405 Series Datasheet Addendum Specification

Document Number/

Location

http://www.intel.com

Page 14

Table 2. PCH Documents

Introduction and Features Summary

Intel® 5 Series Chipset and Intel® 3400 Series Chipset Datasheet http://www.intel.com

Table 3. Public Specifications

Advanced Configuration and Power Interface Specification 3.0 http://www.acpi.info/

PCI Local Bus Specification 3.0

PCI Express Base Specification 2.0 http://www.pcisig.com

DDR3 SDRAM Specification http://www.jedec.org

DisplayPort Specification http://www.vesa.org

®

Intel

64 and IA-32 Architectures Software Developer's Manuals

Volume 1: Basic Architecture 253665

Volume 2A: Instruction Set Reference, A-M 253666

Volume 2B: Instruction Set Reference, N-Z 253667

Volume 3A: System Programming Guide 253668

Volume 3B: System Programming Guide 253669

Document

Document

Document Number/

Location

Document Number/

Location

http://www.pcisig.com/

specifications

http://www.intel.com/

products/processor/

manuals/index.htm

§ §

®

TM

Core

Intel

Datasheet Addendum August 2010

14 Document Number: 323178-003

i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel® Celeron® Processor P4505, U3405 Series

Page 15

Interfaces

2 Interfaces

This chapter describes the interfaces supported by the processor.

2.1 System Memory Interface

2.1.1 System Memory Technology Supported

The Integrated Memory Controller (IMC) supports DDR3 protocols with two,

independent, 64-bit wide channels each accessing one DIMM. It supports:

— ECC and non-ECC un-buffered DIMMs. No support for mixed ECC and non -ECC

DIMM configurations.

DDR3 Data Transfer Rates:

— 800 MT/s (PC3-6400), and 1066 MT/s (PC3-8500)

•DDR3 DIMM Modules:

— Raw Card A – single rank x8 unbuffered non-ECC

— Raw Card B – dual rank x8 unbuffered non-ECC

— Raw Card C – single rank x16 unbuffered non-ECC

— Raw Card D – single rank x8 unbuffered ECC

— Raw Card E – dual rank x8 unbuffered ECC

— Raw Card F - dual rank x16 unbuffered non-ECC

• DDR3 DRAM Device Technology:

— Standard 1-Gb, and 2-Gb technologies and addressing are supported for x16

and x8 devices. There is no support for memory modules with different

technologies or capacities on opposite sides of the same memory module. If

one side of a memory module is populated, the other side is either identical or

empty.

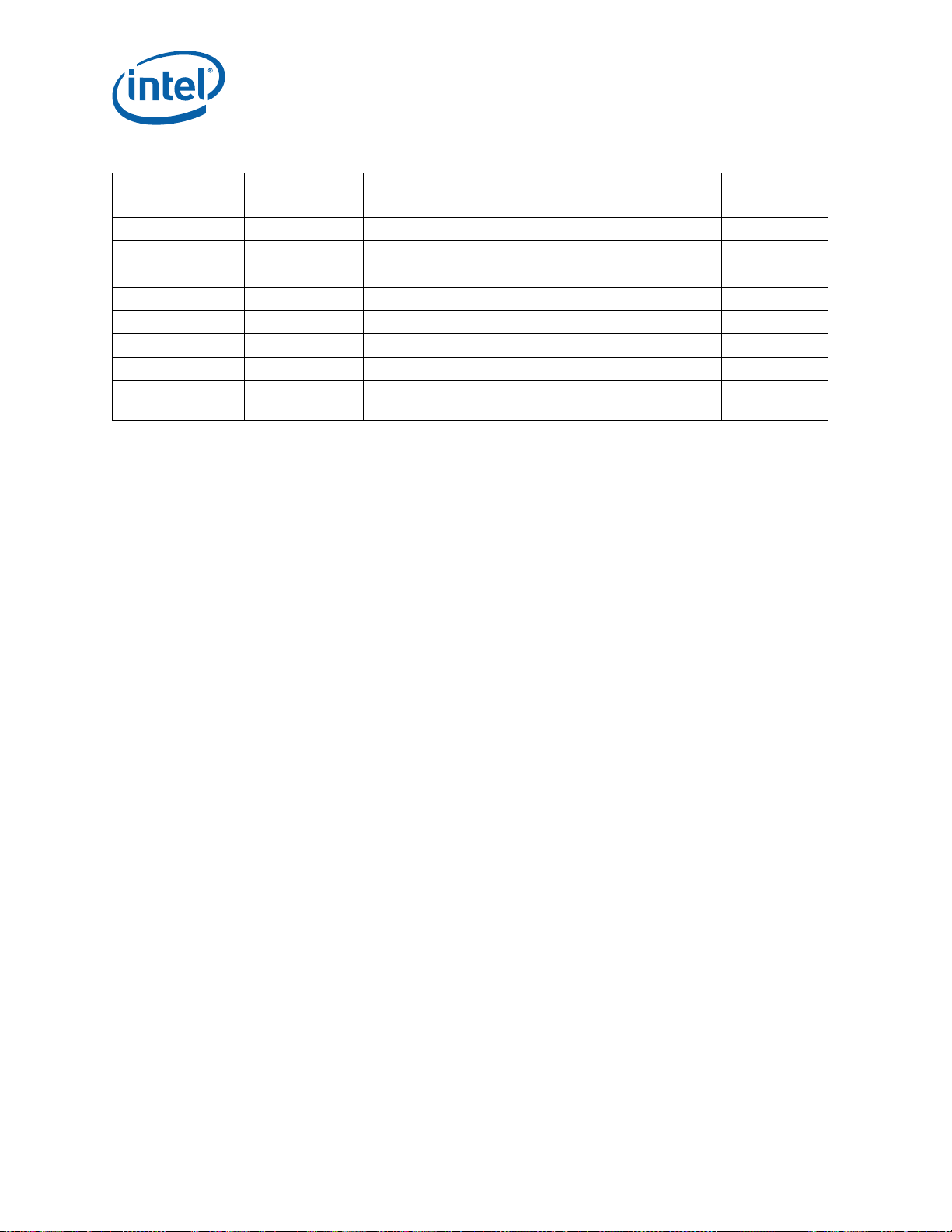

Table 4. Supported DIMM Module Configurations (Sheet 1 of 2)

Raw

Card

Version

A

B

C

Intel® Core

August 2010 Datasheet Addendum

Document Number: 323178-003 15

DIMM

Capacity

512 MB 512 Mb 64 M x 8 8 1 13/10 8 8K

1 GB 1 Gb 128 M x 8 8 1 14/10 8 8K

2 GB 2 Gb 256M x 8 8 1 15/10 8 8K

1 GB 512 Mb 64 M x 8 16 2 13/10 8 8K

2 GB 1 Gb 128 M x 8 16 2 14/10 8 8K

4 GB 2 Gb 256 M x 8 16 2 15/10 8 8K

256MB 512 Mb 32 M x 16 4 1 12/10 8 8K

512 MB 1 Gb 64 M x 8 4 1 13/10 8 8K

1 GB 2 Gb 128 M x 16 4 1 14/10 8 8K

TM

i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel® Celeron® Processor P4505, U3405 Series

DRAM

Device

Technology

DRAM

Organization

# of

DRAM

Devices

# of

Physical

Device

Ranks

# of Row/

Col

Address

Bits

# of

Banks

Inside

DRAM

Page

Size

Page 16

Table 4. Supported DIMM Module Configurations (Sheet 2 of 2)

Interfaces

Raw

Card

Version

D

E

F

DIMM

Capacity

512 MB 512 Mb 64 M x 8 9 1 13/10 8 8K

1 GB 1 Gb 128 M x 8 9 1 14/10 8 8K

2 GB 2 Gb 256 M x 8 9 1 15/10 8 8K

1 GB 512 Mb 64M x 8 18 2 13/10 8 8K

2 GB 1 Gb 128 M x 8 18 2 14/10 8 8K

4 GB 2 Gb 256 M x 8 18 2 15/10 8 8K

512 MB 512 Mb 32 M x 16 8 2 12/10 8 8K

1 GB 1 Gb 64 M x 16 8 2 13/10 8 8K

2 GB 2 Gb 128 M x 16 8 2 14/10 8 8K

DRAM

Device

Technology

DRAM

Organization

# of

DRAM

Devices

Physical

Device

2.1.2 System Memory Timing Support

The IMC supports the following DDR3 Speed Bin, CAS Write Latency (CWL), and

command signal mode timings on the main memory interface:

• tCL = CAS Latency

• tRCD = Activate Command to READ or WRITE Command delay

• tRP = PRECHARGE Command Period

• CWL = CAS Write Latency

• Command Signal modes = 1n indicates a new command may be issued every

clock. Command launch mode programming depends on the transfer rate and

memory configuration.

# of

Ranks

# of Row/

Col

Address

Bits

# of

Banks

Inside

DRAM

Page

Size

Table 5. DDR3 System Memory Timing Support

Transfer

Rate

(MT/s)

800 6 6 6 5 1n 1

1066

NOTES:

1. System Memory timing support is based on availability and is subject to change.

tCL

(tCK)

777

888

tRCD

(tCK)

tRP

(tCK)

CWL

(tCK)

CMD Mode Notes

61n 1

2.1.3 System Memory Organization Modes

The IMC supports two memory organization modes, single-channel and dual-channel.

Depending upon how the DIMM Modules are populated in each memory channel, a

number of different configurations can exist.

2.1.3.1 Single-Channel Mode

In this mode, all memory cycles are directed to a single-channel. Single-channel mode

is used when either Channel A or Channel B DIMM connectors are populated in any

order, but not both.

®

TM

Core

Intel

Datasheet Addendum August 2010

16 Document Number: 323178-003

i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel® Celeron® Processor P4505, U3405 Series

Page 17

Interfaces

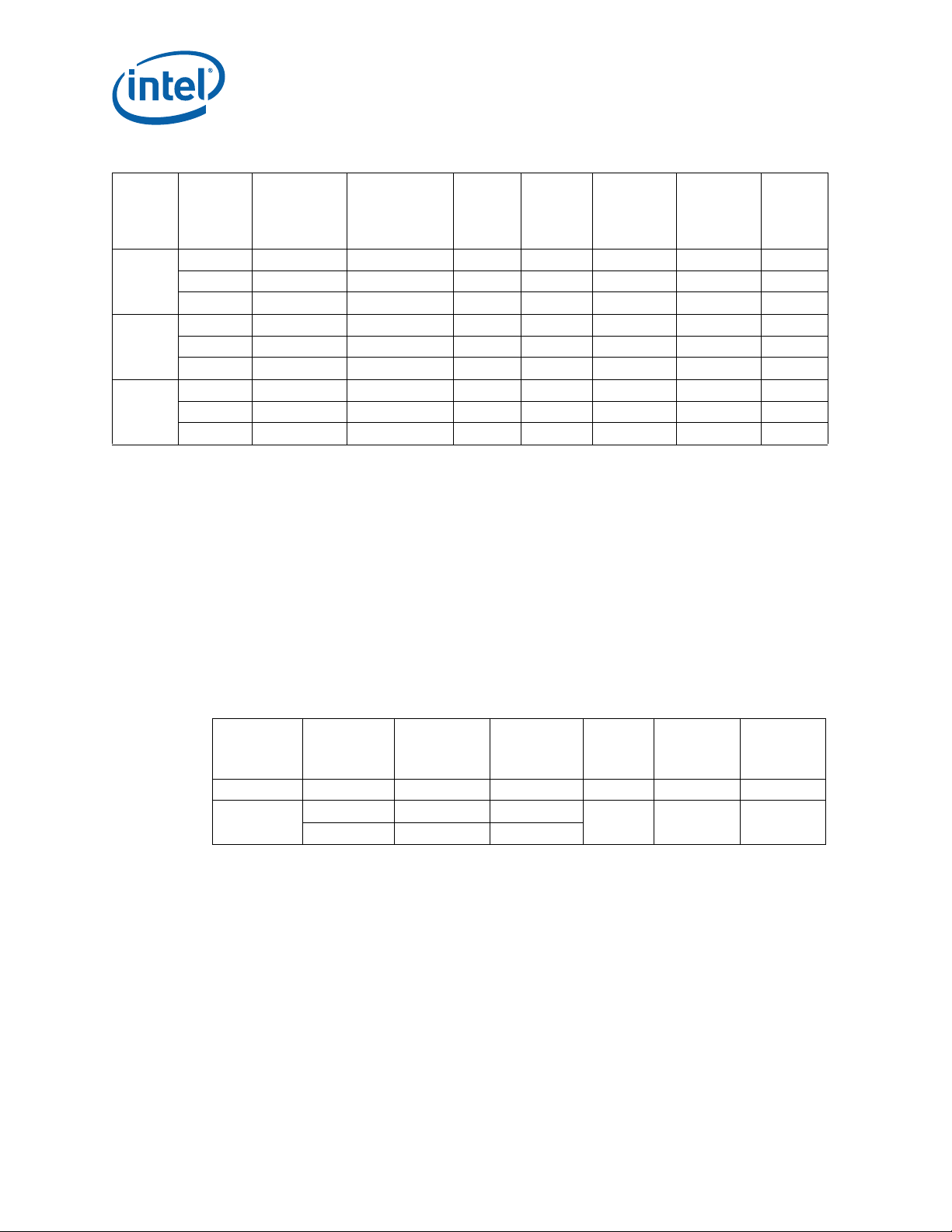

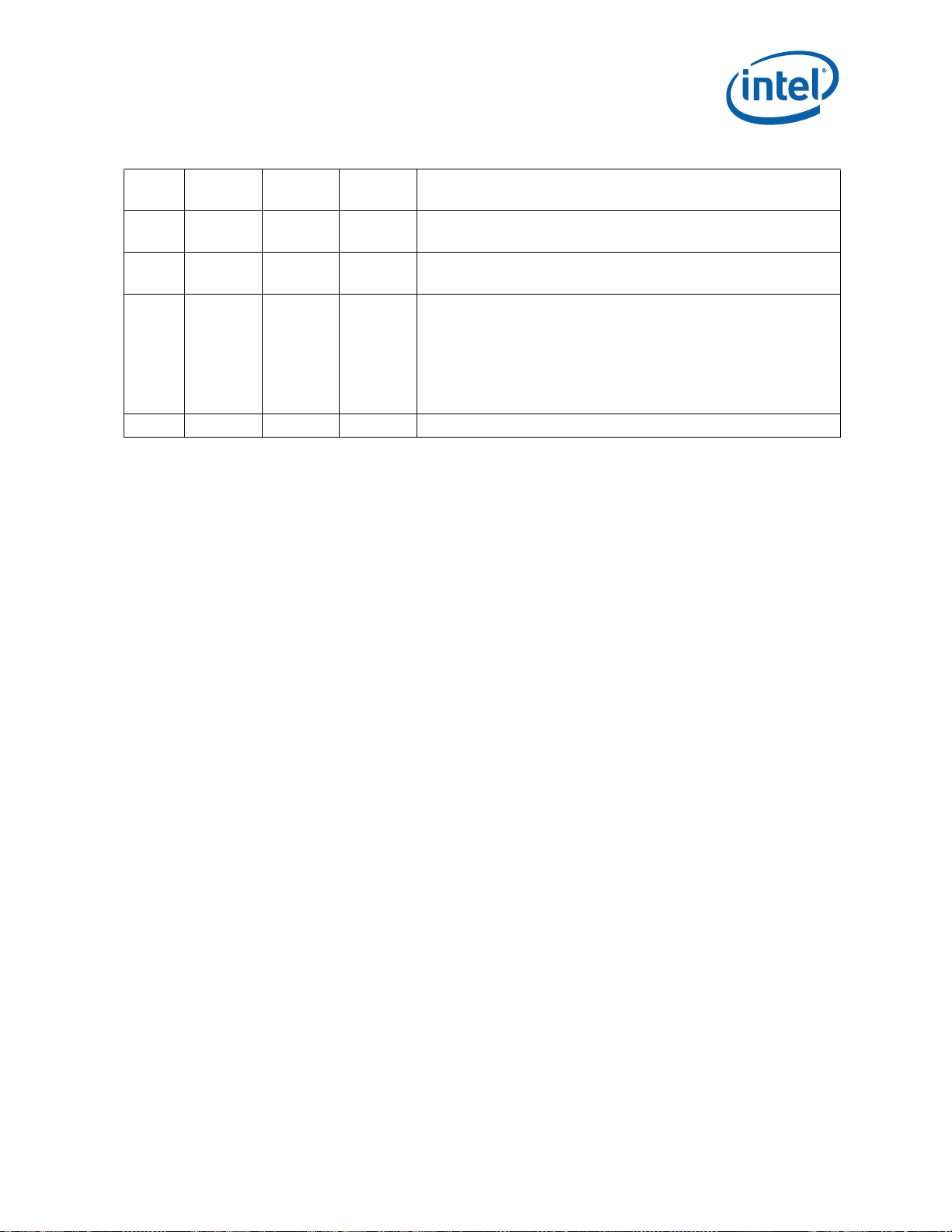

CH BCH A

CH BCH A

B B

C

BB

C

B

B

C

Non interleaved

access

Dual channel

interleaved access

TOM

B – The largest physical memory amount of the smaller size m em ory module

C – The remaining physical mem ory amount of the larger size m em ory module

2.1.3.2 Dual-Channel Mode - Intel® Flex Memory Technology Mode

The IMC supports Intel® Flex Memory Technology Mode. This mode combines the

advantages of the Dual-Channel Symmetric (Interleaved) and Dual-Channel

Asymmetric Modes. Memory is divided into a symmetric and a asymmetric zone. The

symmetric zone starts at the lowest address in each channel and is contiguous until the

asymmetric zone begins or until the top address of the channel with the smaller

capacity is reached. In this mode, the system runs with one zone of dual-channel mode

and one zone of single-channel mode, simultaneously, across the whole memory array.

Figure 2. Intel

®

Flex Memory Technology Operation

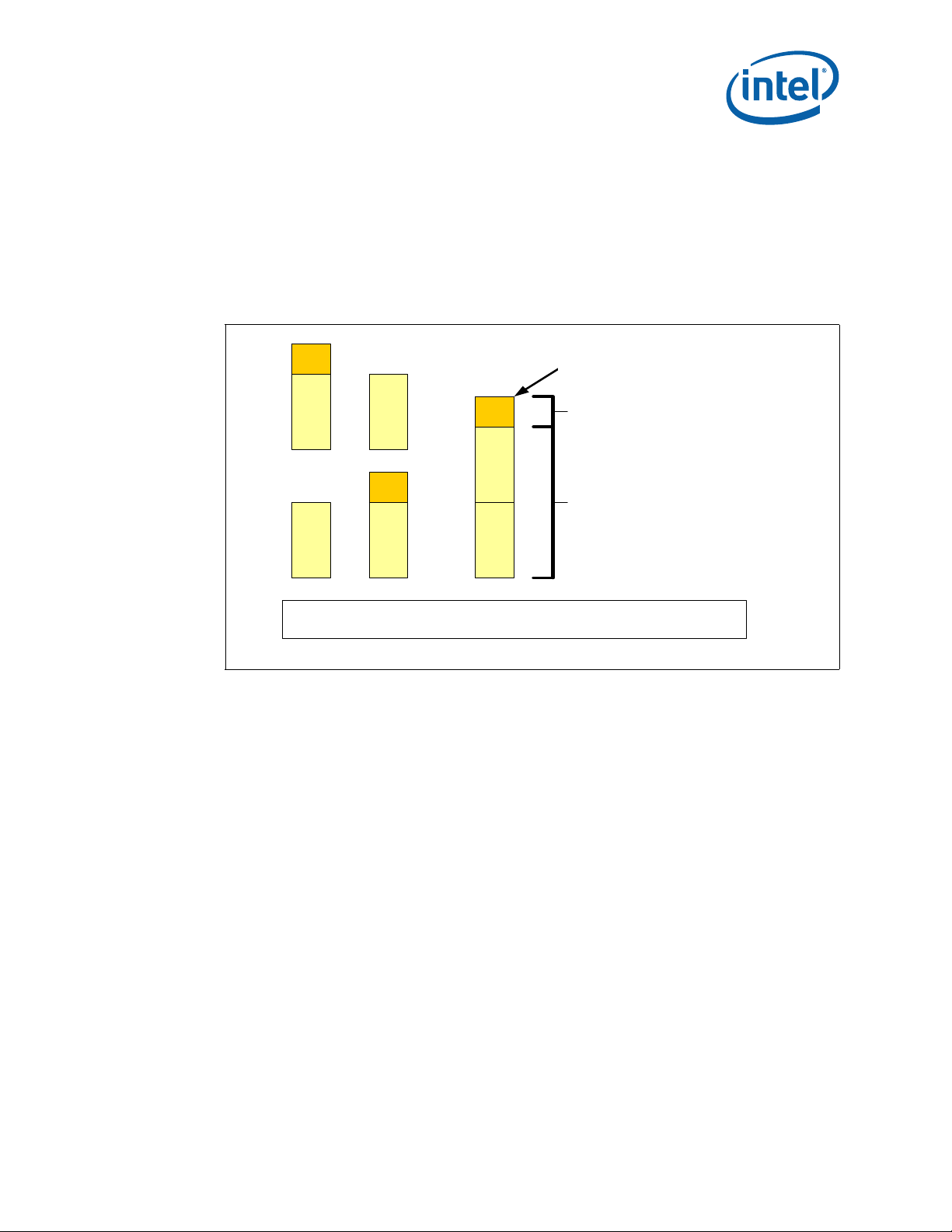

2.1.3.2.1 Dual-Channel Symmetric Mode

Dual-Channel Symmetric mode, also known as interleaved mode, provides maximum

performance on real world applications. Addresses are ping-ponged between the

channels after each cache line (64-byte boundary). If there are two requests, and the

second request is to an address on the opposite channel from the first, that request can

be sent before data from the first request has returned. If two consecutive cache lines

are requested, both may be retrieved simultaneously, since they are ensured to be on

opposite channels. Use Dual-Channel Symmetric mode when both Channel A and

Channel B DIMM connectors are populated in any order, with the total amount of

memory in each channel being the same.

When both channels are populated with the same memory capacity and the boundary

between the dual channel zone and the single channel zone is the top of memory, IMC

operates completely in Dual-Channel Symmetric mode.

Note: The DRAM device technology and width may vary from one channel to the other.

2.1.3.2.2 Dual-Channel Asymmetric Mode

This mode trades performance for system design flexibility. Unlike the previous mode,

addresses start at the bottom of Channel B and stay there until the end of the highest

Intel® Core

August 2010 Datasheet Addendum

Document Number: 323178-003 17

rank in Channel B, and then addresses continue from the bottom of Channel A to the

top. Real world applications are unlikely to make requests that alternate between

addresses that sit on opposite channels with this memory organization, so in most

cases, bandwidth is limited to a single channel.

TM

i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel® Celeron® Processor P4505, U3405 Series

Page 18

Interfaces

CH. B

CH. A

CH. B

CH. A

CH. B

CH. A

CL

0

Top of

Memory

CL

0

CH. A

CH. B

CH.B-top

DRB

Dual Channel Interleaved

(memory sizes must match)

Dual Channel Asymmetric

(memory sizes can differ)

Top of

Memory

This mode is used when Intel® Flex Memory Technology is disabled and both Channel A

and Channel B DIMM connectors are populated in any order with the total amount of

memory in each channel being different.

Figure 3. Dual-Channel Symmetric (Interleaved) and Dual-Channel Asymmetric Modes

2.1.4 Rules for Populating Memory Slots

2.1.5 Technology Enhancements of Intel® Fast Memory Access

2.1.5.1 Just-in-Time Command Scheduling

®

Core

Intel

Datasheet Addendum August 2010

18 Document Number: 323178-003

In all modes, the frequency of system memory is the lowest frequency of all memory

modules placed in the system, as determined through the SPD registers on the

memory modules. The system memory controller supports only one DIMM connector

per channel.For dual-channel modes both channels must have an DIMM connector

populated and for single-channel mode only a single-channel must have an DIMM

connector populated.

®

(Intel

The following sections describe the Just-in-Time Scheduling, Command Overlap, and

Out-of-Order Scheduling Intel

FMA)

®

FMA technology enhancements.

The memory controller has an advanced command scheduler where all pending

requests are examined simultaneously to determine the most efficient request to be

issued next. The most efficient request is picked from all pending requests and issued

to system memory Just-in-Time to make optimal use of Command Overlapping. Thus,

instead of having all memory access requests go individually through an arbitration

mechanism forcing requests to be executed one at a time, they can be started without

TM

i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel® Celeron® Processor P4505, U3405 Series

Page 19

Interfaces

interfering with the current request allowing for concurrent issuing of requests. This

allows for optimized bandwidth and reduced latency while maintaining appropriate

command spacing to meet system memory protocol.

2.1.5.2 Command Overlap

Command Overlap allows the insertion of the DRAM commands between the Activate,

Precharge, and Read/Write commands normally used, as long as the inserted

commands do not affect the currently executing command. Multiple commands can be

issued in an overlapping manner, increasing the efficiency of system memory protocol.

2.1.5.3 Out-of-Order Scheduling

While leveraging the Just-in-Time Scheduling and Command Overlap enhancements,

the IMC continuously monitors pending requests to system memory for the best use of

bandwidth and reduction of latency. If there are multiple requests to the same open

page, these requests would be launched in a back to back manner to make optimum

use of the open memory page. This ability to reorder requests on the fly allows the IMC

to further reduce latency and increase bandwidth efficiency.

2.1.6 DRAM Clock Generation

T wo differential clock pairs for every supported DIMM. There are total of four clock pairs

driven directly by the processor to two DIMMs.

2.1.7 DDR3 On-Die Termination

On-Die T ermination (OD T) is a feature that allows a DRAM device to turn on/off internal

termination resistance for each DQ, DQS/DQS#, and DM signal via the ODT control pin.

The ODT feature improves signal integrity of the memory channel by allowing the

DRAM controller to independently turn on or off the termination resistance for any or all

DRAM devices themselves instead of on the motherboard.

The IMC drives out the required ODT signals, based on the memory configuration and

which rank is being written to or read from, to the DRAM devices on a targeted DIMM

module rank to enable or disable their termination resistance.

2.2 PCI Express* Interface

This section describes the PCI Express* interface capabilities of the processor. See the

PCI Express Base Specification for further details on PCI Express.

The processor has two options for PCI Express controllers available:

• 1 x16 PCI Express Port

or

• 2 x8 PCI Express Ports

— Enabled with CFG[0] strapping, see Section 2.2.2 and Section 3.2

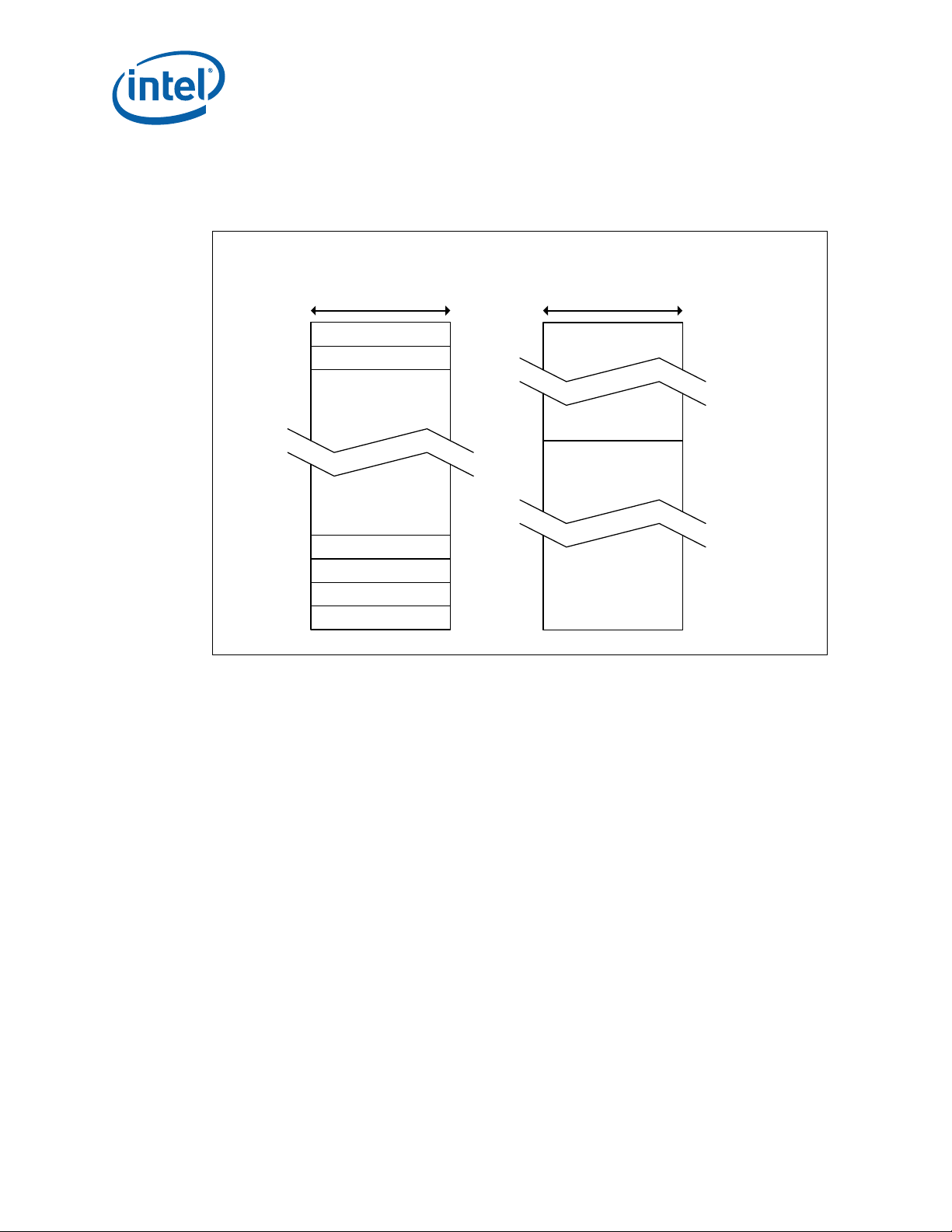

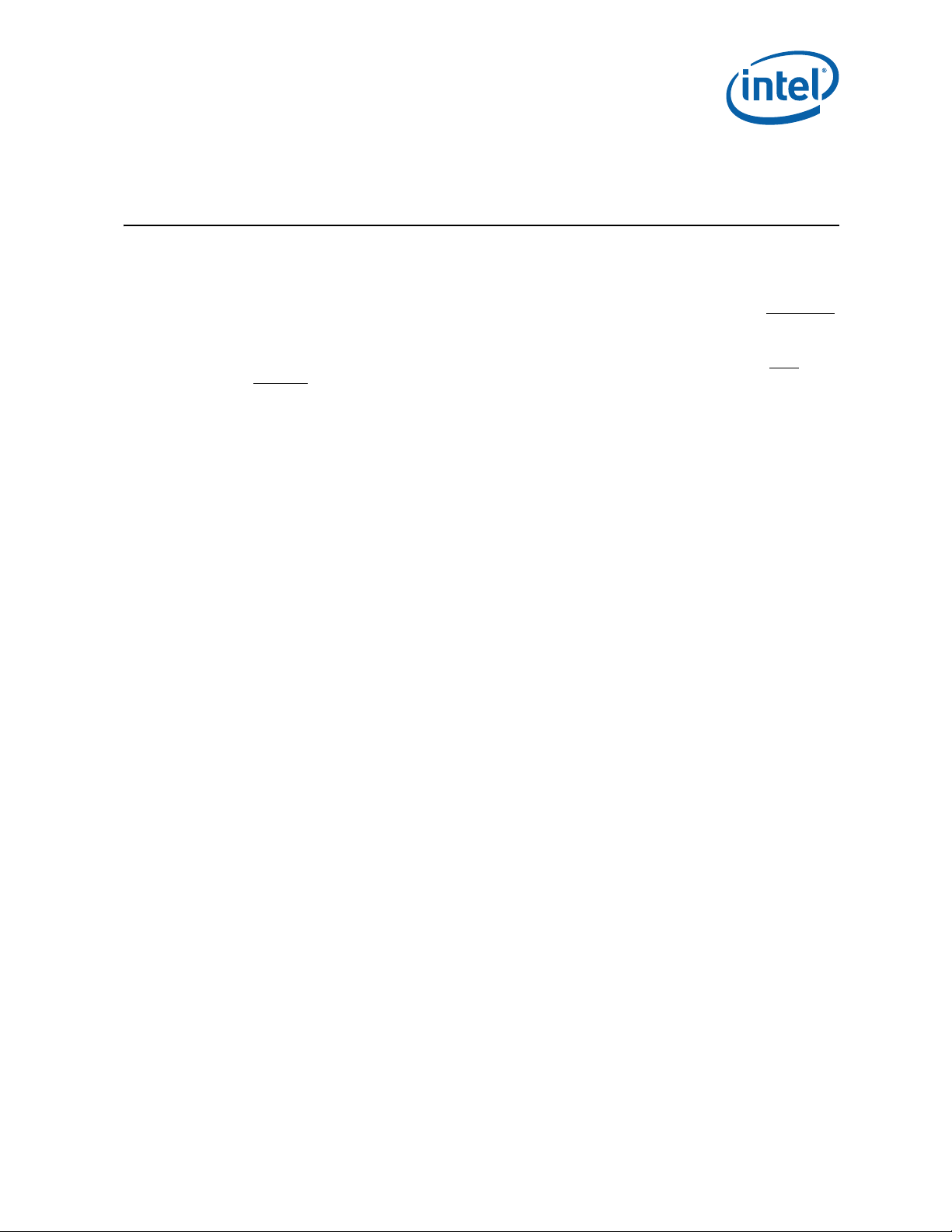

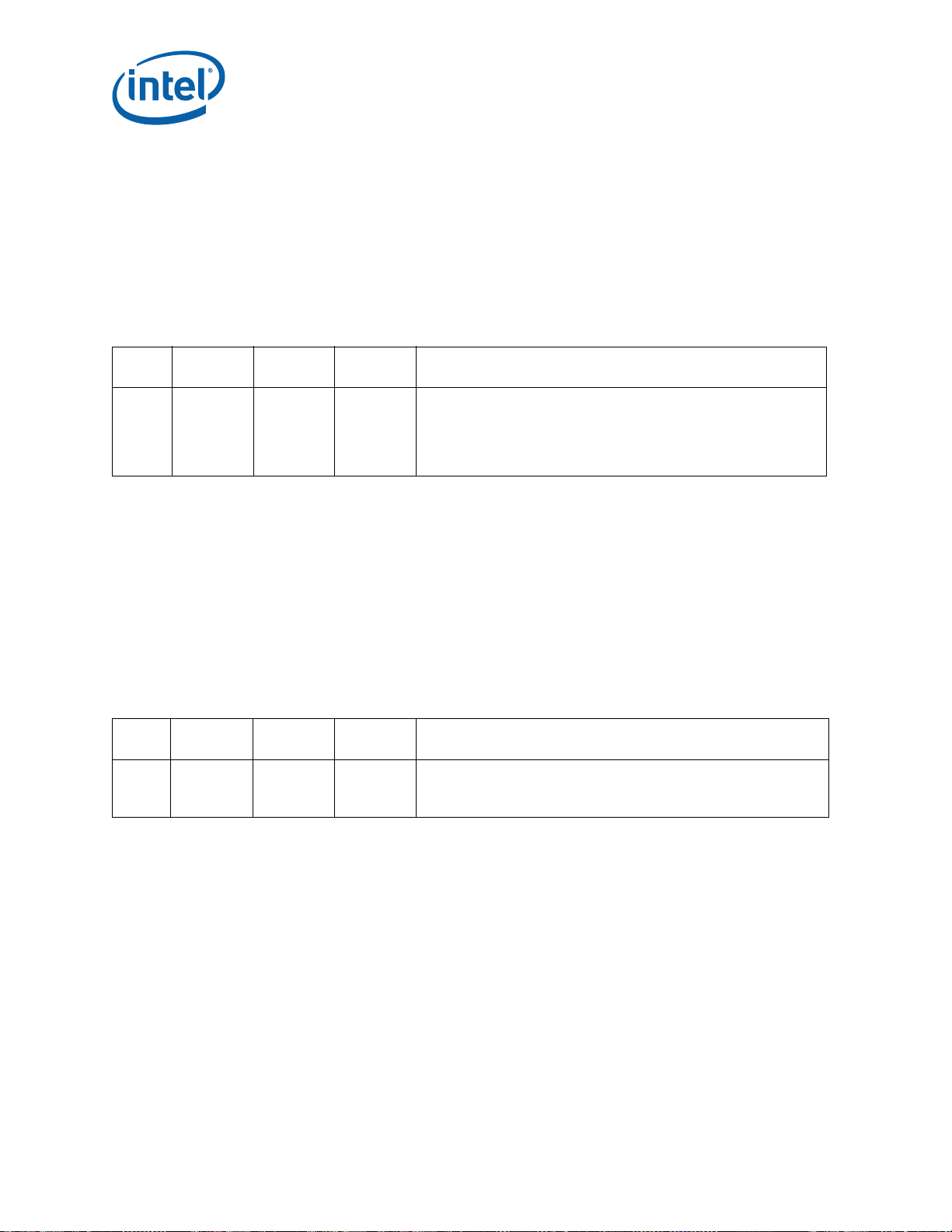

2.2.1 PCI Express* Configuration Mechanism

The PCI Express* link is mapped through a PCI-to-PCI bridge structure.

Intel® Core

August 2010 Datasheet Addendum

Document Number: 323178-003 19

TM

i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel® Celeron® Processor P4505, U3405 Series

Page 20

Interfaces

PCI-PCI Bridge

representing root

PCI Express port

(Device 1)

PCI-PCI Bridge

representing root

PCI Express port

(Device 6)

PCI Compatible

Host Bridge Device

(Device 0)

PCI Express

Device

PCI Express

Device

Port 0

Port 1

DMI

Figure 4. PCI Express* Related Register Structures in the

®

Intel

Celeron

TM

Core

®

i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel®

Processor P4505, U3405 Series

2.2.2 PCI Express Port Bifurcation

When bifurcated, the wires which had previously been assigned to lanes 15:8 of the

single x16 primary port (Port 0) are re ass i g ned to lanes 7:0 of the x8 secondary port

(Port 1). This assignment applies whether the lane numbering is reversed or not. The

controls for the secondary port (Port 1) and the associated virtual PCI-to-PCI bridge

can be found in PCI Device 6.

When the primary port is not bifurcated, Device 6 is hidden from the discovery

mechanism used in PCI enumeration, such that configuration of the device is neither

possible nor necessary.

®

TM

Core

Intel

Datasheet Addendum August 2010

20 Document Number: 323178-003

i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel® Celeron® Processor P4505, U3405 Series

Page 21

Signal Description

3 Signal Description

This chapter describes the processor signals. They are arranged in functional groups

according to their associated interface or category. Th e following notations are used to

describe the signal type:

Notations Signal Type

IInput Pin

OOutput Pin

I/O Bi-directional Input/Output Pin

The signal description also includes the type of buffer used for the particular signal:

Table 6. Signal Description Buffer Types

Signal Description

PCI Express*

FDI

DMI

CMOS CMOS buffers. 1.1-V tolerant

DDR3 DDR3 buffers: 1.5-V tolerant

A

GTL Gunning Transceiver Logic signaling technology.

Ref Voltage reference signal.

Asynchronous

1

PCI Express interface signals. These signals are compatible with PCI Express 2.0

Signalling Environment AC Specifications and are AC coupled. The buffers are not 3.3V tolerant. Refer to the PCIe specification.

Intel Flexible Display interface signals. These signals are compatible with PCI Express

2.0 Signaling Environment AC Specifications, but are DC co uple d. Th e b uffe rs ar e no t

3.3-V tolerant.

Direct Media Interface signals. These signals are compatible with PCI Express 2.0

Signaling Environment AC Specifications, but are DC coupled. The b uffers are not 3.3 V tolerant.

Analog reference or output. May be used as a threshold voltage or for buffer

compensation.

Signal has no timing relationship with any reference clock.

NOTES:

1. Qualifier for a buffer type.

3.1 System Memory Interface

Table 7. Memory Channel A (Sheet 1 of 2)

Signal Name Description

SA_BS[2:0]

SA_WE#

Intel® Core

August 2010 Datasheet Addendum

Document Number: 323178-003 21

TM

i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel® Celeron® Processor P4505, U3405 Series

Bank Select: These signals define which banks

are selected within each SDRAM rank.

Write Enable Control Signal: Used with

SA_RAS# and SA_CAS# (along with SA_CS#) to

define the SDRAM Commands.

Direction/Buffer

Type

O

DDR3

O

DDR3

Page 22

Table 7. Memory Channel A (Sheet 2 of 2)

Signal Description

Signal Name Description

SA_RAS#

SA_CAS#

SA_DM[7:0]

SA_DQS[8]

SA_DQS[7:0]

SA_DQS#[8]

SA_DQS#[7:0]

SA_DQ[71:64]

SA_DQ[63:0]

SA_MA[15:0]

SA_CK[1:0]

SA_CK#[1:0]

SA_CKE[1:0]

SA_CS#[1:0]

SA_ODT[1:0] On Die Termination: Active Termination Control.

RAS Control Signal: Used with SA_CAS# and

SA_WE# (along with SA_CS#) to define the SRAM

Commands.

CAS Control Signal: Used with SA_RAS# and

SA_WE# (along with SA_CS#) to define the SRAM

Commands.

Data Mask: These signals are used to mask

individual bytes of data in the case of a partial

write and to interrupt burst writes. When activated

during writes, the corresponding data groups in

the SDRAM are masked. There is one SA _DM[ 7:0]

for every data byte lane.

ECC Data Strobe: SA_DQS[8] is the data strobe

for the ECC check data bits SA_DQ[71:64]

Note: Not required for non-ECC mode

Data Strobes: SA_DQS[7:0] and its complement

signal group make up a differential stro be pair. The

data is captured at the crossing point of

SA_DQS[7:0] and its SA_DQS#[7:0] during read

and write transactions

ECC Data Strobe Complement: SA_DQS#[8] is

the complement strobe for the ECC check data bits

SA_DQ[71:64]

Note: Not required for non-ECC mode

Data Strobe Complements: These are the

complementary strobe signals.

ECC Check Data Bits: SA_DQ[71:64] are the ECC

check data bits for Channel A.

Note: Not required for non-ECC mode

Data Bus: Channel A data signal interface to the

SDRAM data bus.

Memory Address: These signals are used to

provide the multiplexed row and column address

to the SDRAM.

SDRAM Differential Clock: Channel A SDRAM

Differential clock signal pair. The crossing of the

positive edge of SA_CK and the negative edge of

its complement SA_CK# are used to sample the

command and control signals on the SDRAM.

SDRAM Inverted Differential Clock: Channel A

SDRAM Differential clock signal-pair complement.

Clock Enable: (1 per rank) Used to:

- Initialize the SDRAMs during power-up

- Power-down SDRAM ranks

- Place all SDRAM ranks into and out of self-refresh

during STR

Chip Select: (1 per rank) Used to select particular

SDRAM components during the active state. The re

is one Chip Select for each SDRAM rank.

Direction/Buffer

Type

O

DDR3

O

DDR3

O

DDR3

I/O

DDR3

I/O

DDR3

I/O

DDR3

I/O

DDR3

I/O

DDR3

I/O

DDR3

O

DDR3

O

DDR3

O

DDR3

O

DDR3

O

DDR3

O

DDR3

®

TM

Core

Intel

Datasheet Addendum August 2010

22 Document Number: 323178-003

i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel® Celeron® Processor P4505, U3405 Series

Page 23

Signal Description

Table 8. Memory Channel B (Sheet 1 of 2)

Signal Name Description

SB_BS[2:0]

SB_WE#

SB_RAS#

SB_CAS#

SB_DM[7:0]

SB_DQS[8]

SB_DQS[7:0]

SB_DQS#[8]

SB_DQS#[7:0]

SB_DQ[71:64]

SB_DQ[63:0]

SB_MA[15:0]

SB_CK[1:0]

SB_CK#[1:0]

SB_CKE[1:0]

SB_CS#[1:0]

Bank Select: These signals define which banks

are selected within each SDRAM rank.

Write Enable Control Signal: Used with

SB_RAS# and SB_CAS# (along with SB_CS#) to

define the SDRAM Commands.

RAS Control Signal: Used with SB_CAS# and

SB_WE# (along with SB_CS#) to define the SRAM

Commands.

CAS Control Signal: Used with SB_RAS# and

SB_WE# (along with SB_CS#) to define the SRAM

Commands.

Data Mask: These signals are used to mask

individual bytes of data in the case of a partial

write, and to interrupt burst writes. When

activated during writes, the corresponding data

groups in the SDRAM are masked. There is one

SB_DM[7:0] for every data byte lane.

ECC Data Strobe: SB_DQS[8] is the data strobe

for the ECC check data bits SB_DQ[71:64]

Note: Not required for non-ECC mode

Data Strobes: SB_DQS[7:0] and its complement

signal group make up a differential strobe pair. The

data is captured at the crossing point of

SB_DQS[7:0] and its SB_DQS#[7:0] during read

and write transactions.

ECC Data Strobe Complement: SB_DQS#[8] is

the complement strobe for the ECC check data bits

SB_DQ[71:64]

Note: Not required for non-ECC mode

Data Strobe Complements: These are the

complementary strobe signals.

ECC Check Data Bits: SB_DQ[71:64] are the ECC

check data bits for Channel B

Note: Not required for non-ECC mode

Data Bus: Channel B data signal interface to the

SDRAM data bus.

Memory Address: These signals are used to

provide the multiplexed row and column address

to the SDRAM.

SDRAM Differential Clock: Channel B SDRAM

Differential clock signal pair. The crossing of the

positive edge of SB_CK and the negative edge of

its complement SB_CK# are used to sample the

command and control signals on the SDRAM.

SDRAM Inverted Differential Clock:

SDRAM Differential clock signal-pair complement.

Clock Enable: (1 per rank) Used to:

- Initialize the SDRAMs during power-up.

- Power-down SDRAM ranks.

- Place all SDRAM ranks into and out of self-refresh

during STR.

Chip Select: (1 per rank) Used to select particular

SDRAM components during the active state. T here

is one Chip Select for each SDRAM rank.

Channel B

Direction/Buffer

Type

O

DDR3

O

DDR3

O

DDR3

O

DDR3

O

DDR3

I/O

DDR3

I/O

DDR3

I/O

DDR3

I/O

DDR3

I/O

DDR3

I/O

DDR3

O

DDR3

O

DDR3

O

DDR3

O

DDR3

O

DDR3

Intel® Core

August 2010 Datasheet Addendum

Document Number: 323178-003 23

TM

i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel® Celeron® Processor P4505, U3405 Series

Page 24

Table 8. Memory Channel B (Sheet 2 of 2)

Signal Description

Signal Name Description

SB_ODT[1:0] On Die Termination: Active Termination Control.

3.2 Reset and Miscellaneous Signals

Table 9. Reset and Miscellaneous Signals

Signal Name Description

SM_DRAMRST#

CFG[17:0]

DDR3 DRAM Reset: Reset signal from processor

to DRAM devices. One for all channels of DIMMs.

Configuration signals:

The CFG signals have a default value of 1 if not

terminated on the board. Refer to the Platform

Design Guide for pull-down recommendations

when logic low is desired.

• CFG[0]: PCI Express* Bifurcation:

— 1 = 1 x16 PCI Express I/O

— 0 = 2 x 8 PCI Express I/O

• CFG[1]: Reserved

• CFG[2]: Reserved configuration lands. A test

point may be placed on the board for this land.

• CFG[3]: PCI Express* Static Lane Numbering

Reversal. A test point may be placed on the

board for this land. Lane reversal will be

applied across all 16 lanes.

—1: No Reversal

—0: Reversal

In the case of Bifurcation with NO Lane Reversal

the physical lane mapping is as follows:

— Lanes 15:8 => Port 1 Lanes 7:0

— Lanes 7:0 => Port 0 Lanes 7:0

In the case of Bifurcation with WITH Lane Reversal

the physical lane mapping is as follows:

— Lanes 15:8 => Port 0 Lanes 0:7

— Lanes 7:0 => Port 1 Lanes 0:7

• CFG[4]: Embedded DisplayPort Detection:

This is used to detect the presence of a device

on the Embedded DisplayPort.

— 1: No Physical Display Port attached to

the Embedded Display Port

— 0: An external Display Port device is

connected to the Embedded Display Port

• CFG[17:5]: Reserved configuration lands.

Intel does not recommend a test point on the

board for these lands.

Direction/Buffer

Type

O

DDR3

Direction/Buffer

Type

O

DDR3

I

CMOS

§ §

®

TM

Core

Intel

Datasheet Addendum August 2010

24 Document Number: 323178-003

i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel® Celeron® Processor P4505, U3405 Series

Page 25

Electrical Specifications

4 Electrical Specifications

4.1 Signal Groups

Signals are grouped by buffer type and similar characteristics as listed in Table 10. The

buffer type indicates which signaling technology and specifications apply to the signals.

All the differential signals, and selected DDR3 and Control Sideband signals have OnDie Termination (ODT) resistors. There are some signals that do not have ODT and

need to be terminated on the board.

Table 10. Mobile Signal Groups

Signal Group

DDR3 Data Signals

Single ended (e) DDR3 Bi-directional SA_DQ[71:0], SB_DQ[71:0]

Differential (f) DDR3 Bi-directional

Power/Ground/Other

Single Ended (z) Other DBR#, PROC_DETECT, VCAP0, VCAP1, VCAP2

1

Alpha

Group

2

NOTES:

1. Refer to Chapter 3 for signal description details.

2. SA and SB refer to DDR3 Channel A and DDR3 Channel B.

All Control Sideband Asynchronous signals are required to be asserted/deasserted for

at least eight BCLKs in order for the processor to recognize the proper signal state. See

Section 4.2 for the DC specifications.

4.2 DC Specifications

The processor DC specifications in this section are defined at the processor

pins, unless noted otherwise. See Chapter 5 for the processor pin listings and

Chapter 3 for signal definitions.

The DC specifications for the DDR3 signals are listed in Table 11.

Type Signals

SA_DQS[8:0], SA_DQS#[8:0]

SB_DQS[8:0], SB_DQS#[8:0]

4.2.1 Voltage and Current Specifications

Table 11. DDR3 Signal Group DC Specifications (Sheet 1 of 2)

Symbol Parameter

V

IL

Input Low Voltage (e,f) 0.43*V

Alpha

Group

Min Typ Max Units Notes

DDQ

V2,4

NOTES:

1. Unless otherwise noted, all specifications in this table apply to all processor frequencies.

2. V

3. V

4. V

5. R

Intel® Core

August 2010 Datasheet Addendum

Document Number: 323178-003 25

is defined as the maximum voltage level at a receiving agent that will be interpreted as a logical low value.

IL

is defined as the minimum voltage level at a receiving agent that will be interpreted as a logical high value.

IH

and VOH may experience excursions above V

IH

specifications.

is the termination on the DIMM and in not controlled by the processor.

VTT_TERM

TM

i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel® Celeron® Processor P4505, U3405 Series

. However, input signal drivers must comply with the signal quality

DDQ

1,9

Page 26

Table 11. DDR3 Signal Group DC Specifications (Sheet 2 of 2)

Electrical Specifications

Symbol Parameter

V

IH

V

OL

V

OH

Input High Voltage (e,f) 0.57*V

Output Low Voltage (c,d,e,f)

Output High Voltage (c,d,e,f)

Alpha

Group

Min Typ Max Units Notes

DDQ

(V

/ 2)* (R

DDQ

(R

ON+RVTT_TERM

- ((V

V

DDQ

(R

(R

ON+RVTT_TERM

ON

DDQ

/

ON

))

/ 2)*

))

/

NOTES:

1. Unless otherwise noted, all specifications in this table apply to all processor frequencies.

2. V

3. V

4. V

5. R

is defined as the maximum voltage level at a receiving agent that will be interpreted as a logical low value.

IL

is defined as the minimum voltage level at a receiving agent that will be interpreted as a logical high value.

IH

and VOH may experience excursions above V

IH

specifications.

is the termination on the DIMM and in not controlled by the processor.

VTT_TERM

. However, input signal drivers must comply with the signal quality

DDQ

1,9

V3

5

V4,5

®

TM

Core

Intel

Datasheet Addendum August 2010

26 Document Number: 323178-003

i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel® Celeron® Processor P4505, U3405 Series

Page 27

Processor Ball and Signal Information

5 Processor Ball and Signal

Information

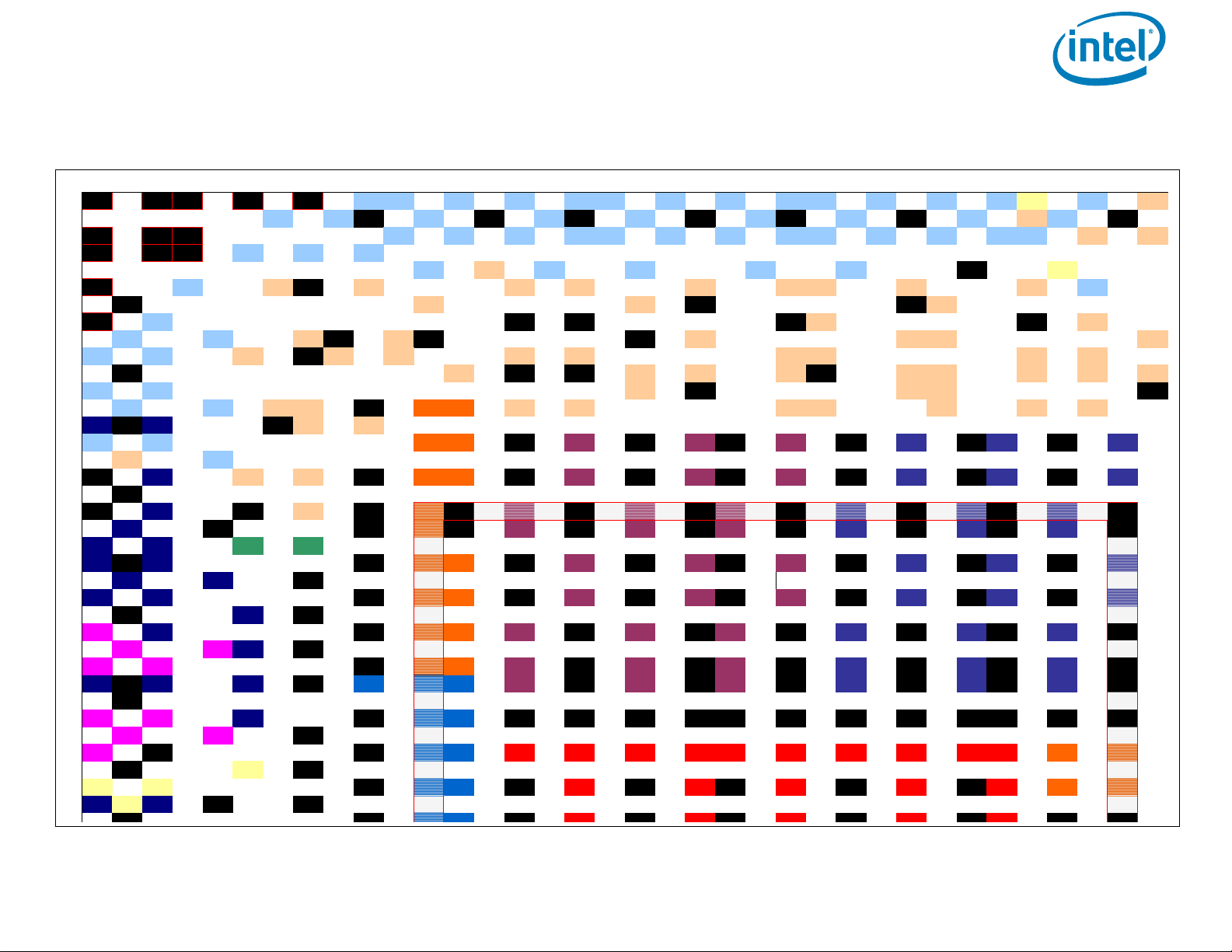

5.1 Processor Ball Assignments

• Table 12 provides a listing of all processor pins ordered alphabetically by ball name

for the Intel

Celeron

• Table 13 provides a listing of all processor pins ordered alphabetically by ball

number for the Intel® Core

and Intel

• Figure 5, Figure 6, Figure 7, and Figure 8 show the Top-Down view of the Intel

TM

Core

Processor P4505, U3405 Series ballmap

®

TM

Core

®

Processor P4505, U3405 Series package respectively.

®

Celeron® Processor P4505, U3405 Series package respectively.

i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel® Celeron®

i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel®

TM

i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E

®

Intel® Core

August 2010 Datasheet Addendum

Document Number: 323178-003 27

TM

i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel® Celeron® Processor P4505, U3405 Series

Page 28

Processor Ball and Signal Information

71 70 69 68 67 66 65 64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36

BV

DC_TES

T_BV71

DC_TES

T_BV69

DC_TES

T_BV68

VSS VSS

SB_DQS

[6]

SB_DQ[4

8]

SB_DQ[4

7]

SB_DM[5

]

SB_DQS

#[5]

SB_DQ[3

9]

SB_DQ[3

7]

SB_DQ[3

4]

SB_DQ[33]SB_DM[4

]

SB_ODT

[0]

SB_BS[1

]

SB_BS[0]SM_RCO

MP[2]

SB_CK[1

]

SA_MA[2

]

BU

SB_DM[6

]

SB_DQS

#[6]

VSS

SB_DQ[4

6]

VSS

SB_DQS

[5]

VSS

SB_DQ[4

1]

VSS

SB_ODT

[1]

VSS

SB_CAS

#

VSS

SB_MA[1

0]

SA_DQ[66]SB_CK#[

1]

VSS

BT

DC_TES

T_BT71

DC_TES

T_BT69

VSS

SB_DQ[5

3]

SB_DQ[4

2]

SB_DQ[4

3]

SB_DQ[44]SB_DQ[3

8]

SB_DQS

[4]

SB_DQS

#[4]

SB_DQ[32]SB_DQ[3

6]

SB_MA[1

3]

SB_CS#[

1]

SB_WE#

SB_RAS

#

SA_BS[0]

SA_MA[0

]

BR

DC_TES

T_BR71

VSS VSS

SB_DQ[5

0]

SB_DQ[5

1]

SB_DQ[5

2]

BP

SB_DQ[4

9]

SA_DQS

#[6]

SB_DQ[4

5]

SB_DQ[4

0]

SB_DQ[3

5]

SB_CS#[

0]

VSS

SM_RCO

MP[1]

BN

VSS

SB_DQ[5

4]

SA_DQ[5

0]

VSS

SA_DM[6

]

SA_DQ[4

9]

SA_DQ[4

7]

SA_DQ[4

1]

SA_DQ[40]SA_DQ[3

9]

SA_DQ[3

8]

SA_DQ[3

6]

SB_DQ[6

8]

BM

VSS

SA_DQS[

6]

SA_DQ[4

6]

VSS VSS

SA_DQ[3

3]

BL

VSS

SB_DQ[5

5]

VSS VSS VSS

SA_ODT[

1]

VSS

SA_RAS

#

BK

SB_DQ[6

0]

SB_DQ[6

1]

SA_DQ[5

4]

VSS

SA_DQ[5

5]

VSS VSS

SA_DQS

#[5]

SA_DQS[4]SA_CAS

#

SA_CK#[

1]

BJ

SB_DQ[5

6]

SB_DQS

[7]

SA_DQ[6

0]

VSS

SA_DQ[5

6]

SA_DQ[5

1]

SA_DQ[5

3]

SA_DQ[4

3]

SA_DQ[45]SA_CS#[

1]

SA_DQ[3

2]

SA_DQ[7

1]

BH

VSS

SA_DM[7

]

VSS VSS

SA_DQ[4

2]

SA_DQS[

5]

SA_DQ[4

4]

VSS

SA_DQS

#[4]

SA_DQ[3

7]

SA_CS#[

0]

SA_BS[1]

SA_CK[1

]

BG

SB_DQ[5

8]

SB_DQS

#[7]

SA_DM[5

]

VSS

SA_DM[4]SA_DQ[7

0]

VSS

BF

SB_DQ[5

7]

SB_DM[7

]

SA_DQ[61]SA_DQ[5

7]

VSS VTT0 VTT0

SA_DQ[5

2]

SA_DQ[4

8]

SA_DQ[35]SA_DQ[3

4]

SA_ODT[

0]

SA_MA[1

3]

SA_WE#

BE

RSVD VSS RSVD VSS

SA_DQS[

7]

SA_DQS

#[7]

BD

SB_DQ[6

2]

SB_DQ[6

3]

VTT 0 VTT0 VSS VC AP0 VSS VCAP 0 VS S VC AP0 VSS VCAP 1 VS S VC AP1 VSS VCAP 1

BC

SA_DQ[6

3]

SB_DQ[5

9]

BB

VSS RSVD

SA_DQ[5

9]

SA_DQ[5

8]

VSS VTT 0 VTT0 VSS VC AP0 VSS VCAP 0 VS S VC AP0 VSS VCAP 1 VS S VCAP1 VS S VC AP1

BA

VSS

AY

VSS RSVD VSS

SA_DQ[6

2]

VSS VTT 0 VSS VCAP0 VS S VC AP0 VSS VCAP0 VSS VC AP1 VSS VCAP1 VSS VCAP 1 VS S

AW

RSVD VSS VSS VT T0 VS S VC AP0 VSS VCAP 0 VS S VCAP0 VS S VC AP1 VSS VCAP 1 VS S VC AP1 VSS

AV

RSVD RSVD

PM_EXT

_TS#[0]

PM_EXT

_TS#[1]

AU

RSVD VSS RSVD VSS VTT 0 VTT0 VSS VC AP0 VSS VCAP 0 VS S VC AP0 VSS VCAP 1 VS S VCAP1 VS S VC AP1

AT

RSVD RSVD VSS

AR

RSVD RSVD VSS VT T0 VT T0 VSS VCAP 0 VS S VC AP0 VSS VC AP0 VSS VCAP 1 VS S VC AP1 VSS VCAP 1

AP

VSS RSVD VSS

AN

GFX_ VID

[4]

RSVD VSS VTT 0 VTT 0 VCAP 0 VS S VC AP0 VSS VCAP0 VSS VC AP1 VSS VCAP1 VSS VCAP 1 VS S

AM

GFX_ VID

[6]

GFX_ VID

[5]

RSVD VSS

AL

GFX_DP

RSLPVR

GFX_IM

ON

VSS VTT 0 VTT0 VCAP0 VS S VC AP0 VSS VCAP0 VSS VC AP1 VSS VCAP1 VSS VCAP 1 VS S

AK

RSVD VSS RSVD RSVD VSS VCAP 2 VCAP2 VC AP2 VCAP0 VS S VC AP0 VSS VCAP0 VSS VCAP 1 VS S VC AP1 VSS VC AP1 VSS

AJ

VSS

AH

GFX_ VID

[3]

GFX_ VR

_EN

RSVD VSS VCAP2 VCAP2 VSS VSS VS S VSS VSS VSS VS S VSS VSS VSS VSS VSS

AG

GFX_ VID

[2]

GFX_ VID

[1]

VSS

AF

GFX_ VID

[0]

VSS VSS VCAP2 VCAP2 VCC VCC VCC VCC VCC VC C VCC VCC VCC VCC VT T0 VTT 0

AE

VSS COMP0 VSS

AD

COMP3 COMP1 VSS VCAP2 VCAP2 VSS VC C VS S VC C VSS VCC VSS VCC VS S VCC VTT 0 VT T0

AC

RSVD COMP2 RSVD VSS VSS

Figure 5. Intel® Core

TM

i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel® Celeron® Processor P4505, U3405 Series Ballmap

(Top View, Upper-Left Quadrant)

323178-003 28

Page 29

Processor Ball and Signal Information

3534333231302928272625242322212019181716151413121110987654321

SB_CK#[0]SM_RCO

MP[0]

SB_MA[4

]

SB_MA[2

]

SB_MA[8]SB_MA[1

4]

SB_BS[2

]

SB_DQ[2

6]

SB_DQ[30]SB_DQ[2

9]

SB_DQ[2

2]

SB_DQ[1

9]

SB_DQS

[2]

SB_DQ[2

0]

SB_DQ[1

5]

RSVD_N