Page 1

Page# Page Title

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

Index

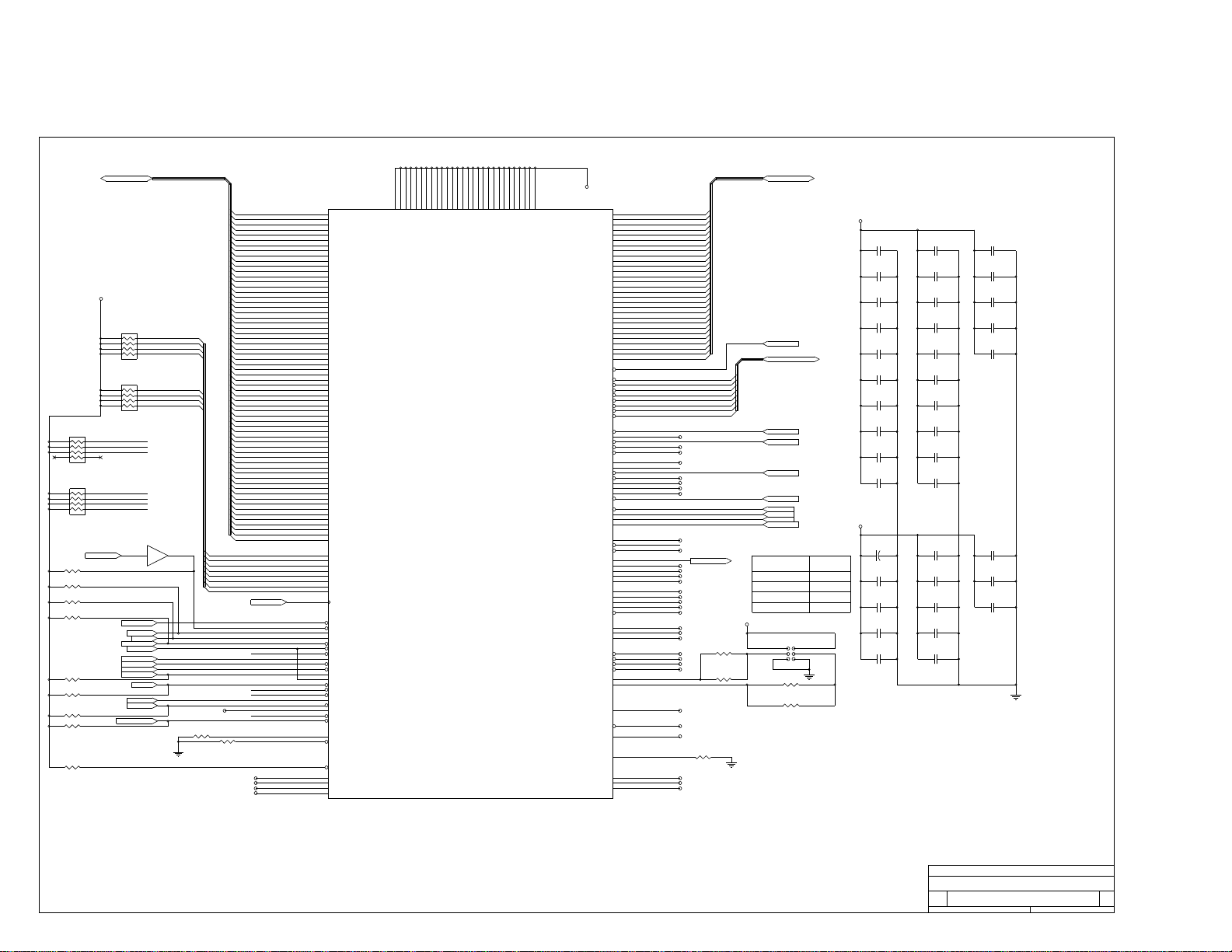

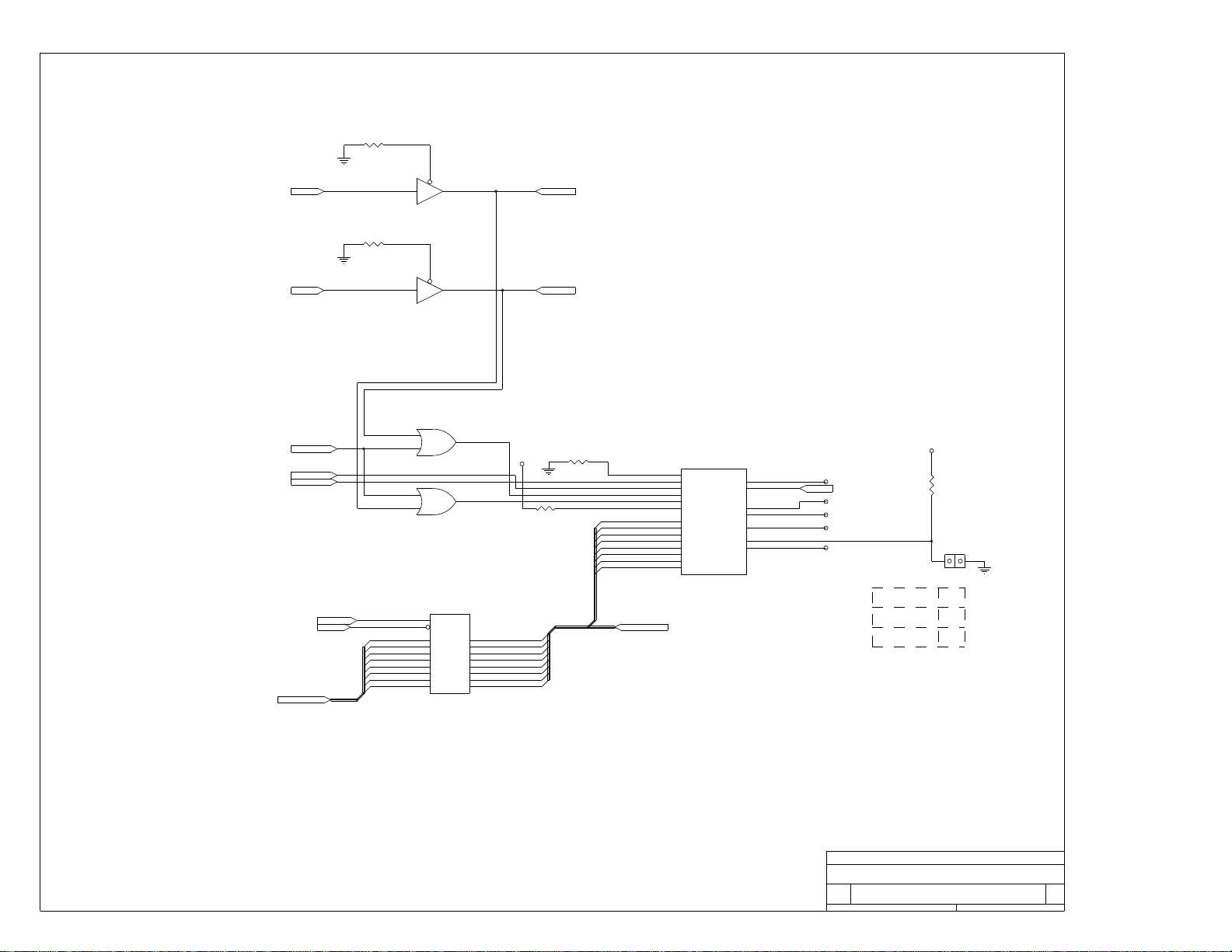

Primary CPU (Socket 7)

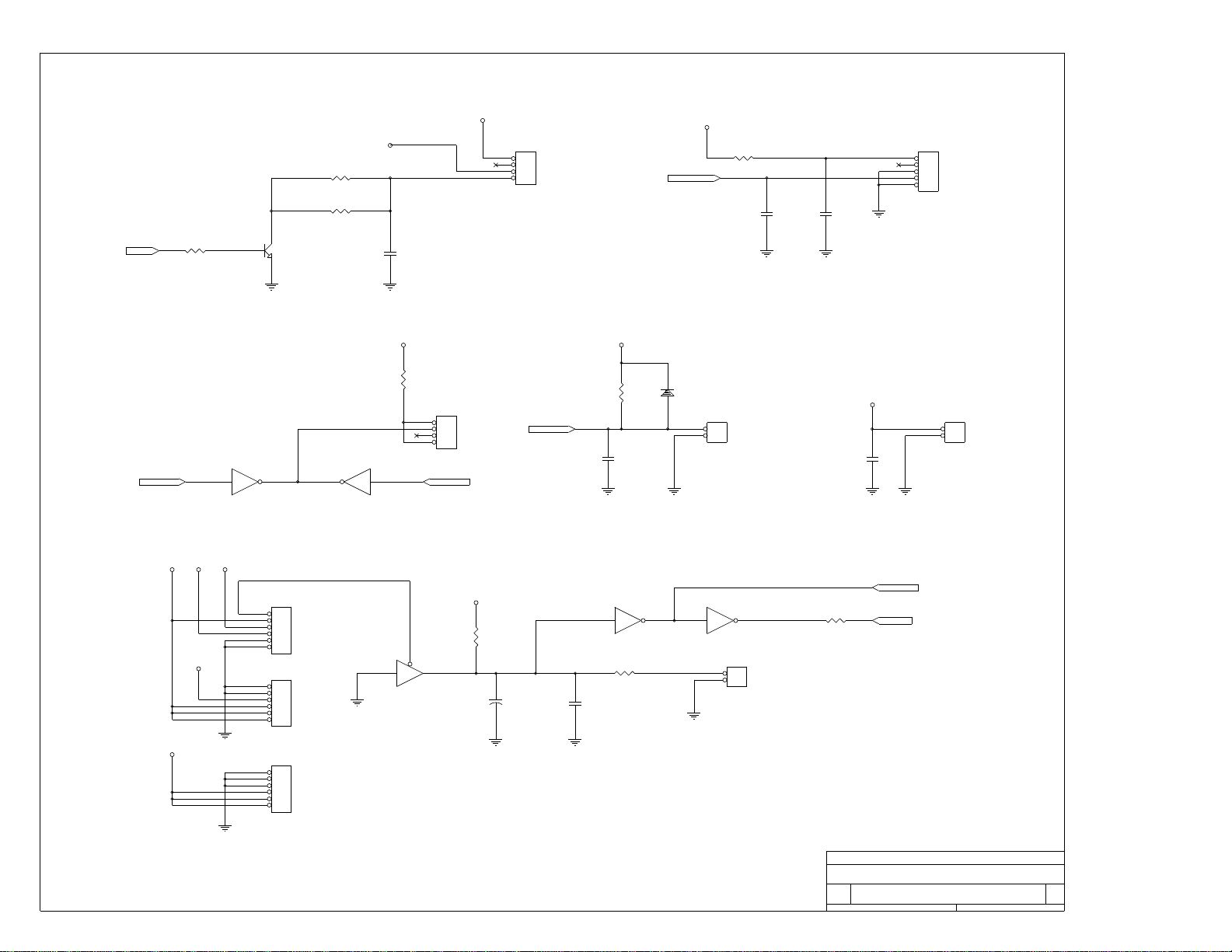

Clock Generator

Triton II controller (TXC)

Synchronous Cache, Lower 256K

Synchronous Cache, Upper 256K

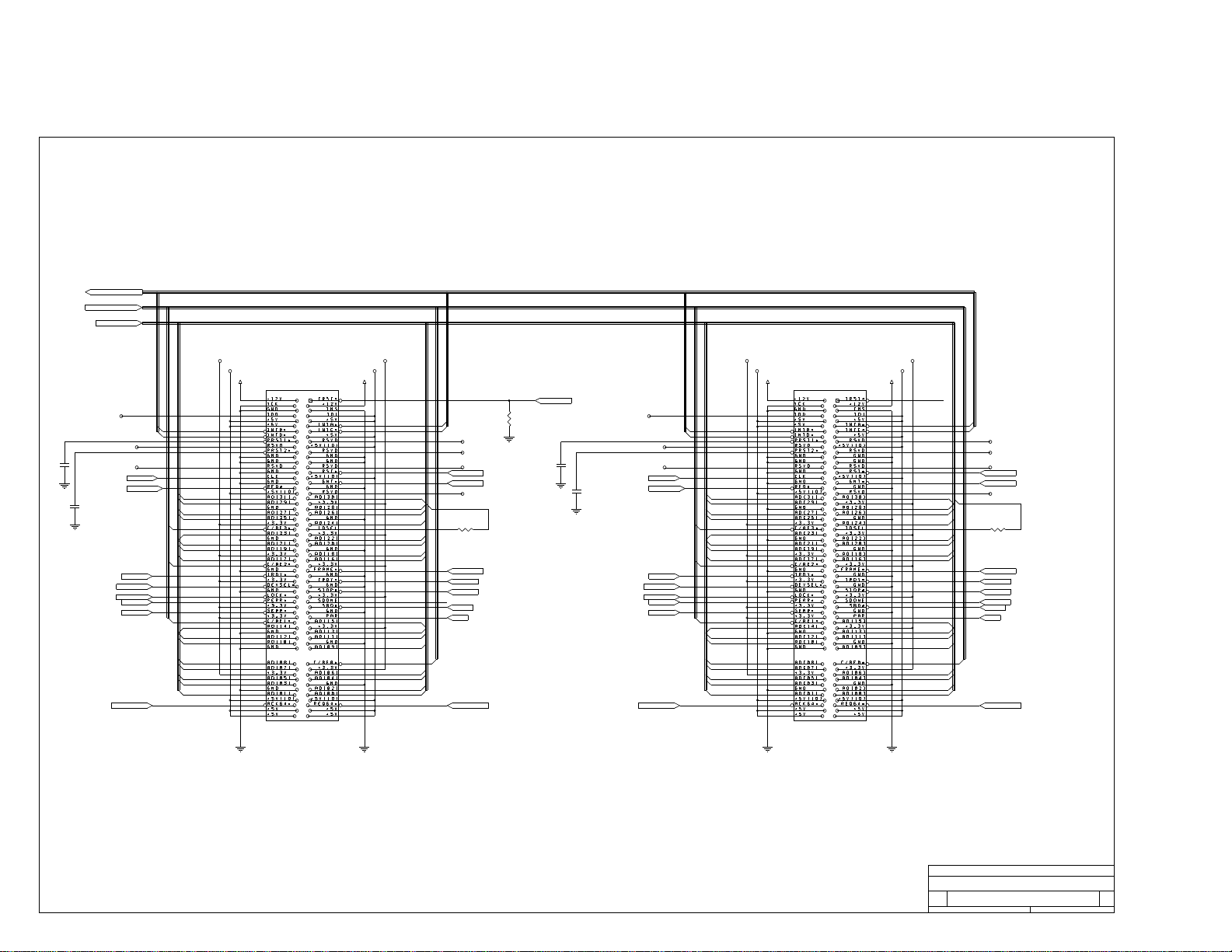

Memory Modules 0 & 1

Memory Modules 2 & 3

System ROM

PIIX3

PCI IDE Interface

AIP

Serial Ports, Floppy, USB

Parallel Ports

Keyboard/Mouse Ports

Battery, RTC Circuit

Front Panel

PCI Slots 1 and 2

PCI Slots 3 and 4

ISA Slots

Pullup/Pulldown Resistors

Switching Power Supply

Fiducials, Holes, Spare Gates

Decoupling Caps

Released Rev. B.1

THIS DRAWING CONTAINS INFORMATION

WHICH HAS NOT BEEN VERIFIED FOR

MANUFACTURING AN END USER PRODUCT.

INTEL IS NOT RESPONSIBLE FOR THE

MISUSE OF THIS INFORMATION.

INTEL CORP.

Title

Index

Size Document Number REV

A 82430HX B.1

Date: June 19, 1997 Sheet 1 of 24

Page 2

RP72

1 8

2 7

3 6

4 5

4.7K

RP75

1 8

2 7

3 6

4 5

4.7K

1 2

R100 4.7K

1 2

R98 4.7K

1 2

R111 4.7K

1 2

R97 4.7K

R86

330

1 2

R92 10K

1 2

R87

4.7K

1 2

1 2

R93

4.7k

R99

1 2

330

HD[0..63]

4..6

1

1

1

1

8

7

8

8

V

V

V

C

C

C

O

O

O

R

R

R

E

E

E

TP001

TP009

TP008

TP010

116

102

112

101

97

96

91

90

72

55

54

36

71

35

53

17

34

52

16

69

33

51

15

68

50

48

67

47

66

46

65

45

44

63

43

62

42

61

41

60

59

2

78

20

58

39

77

38

57

76

56

94

75

100

74

99

105

109

110

115

120

119

125

129

73

70

49

64

40

95

93

130

256

185

251

206

201

192

170

306

165

286

175

257

160

180

269

190

191

196

202

186

166

195

169

179

275

146

151

152

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

D30

D31

D32

D33

D34

D35

D36

D37

D38

D39

D40

D41

D42

D43

D44

D45

D46

D47

D48

D49

D50

D51

D52

D53

D54

D55

D56

D57

D58

D59

D60

D61

D62

D63

DP0

DP1

DP2

DP3

DP4

DP5

DP6

DP7

CLK

BOFF#

A20#

INTR

NMI

IGNNE#

KEN#

FLUSH#

AHOLD

EADS#

BRDY#

RESET

INV

NA#

BUSCHK#

WB/WT#

INIT

SMI#

R/S#

PEN#

STOPCLK#

HOLD

EWBE#

BRDYC#

NC/MPBOFF#

NC/BHOLD

NC/CHOLD

NC/DHOLD

U33

P5II

HD0

HD1

HD2

HD3

HD4

HD5

HD6

HD7

HD8

HD9

HD10

HD11

HD12

HD13

HD14

TP224

330

HDPA0

HDPA1

HDPA2

HDPA3

HDPA4

HDPA5

HDPA6

HDPA7

1 2

R131

330

1

TP225

TP226

TP227

TP228

HD15

HD16

HD17

HD18

HD19

HD20

HD21

HD22

HD23

HD24

HD25

HD26

HD27

HD28

HD29

HD30

HD31

HD32

HD33

HD34

HD35

HD36

HD37

HD38

HD39

HD40

HD41

HD42

HD43

HD44

HD45

HD46

HD47

HD48

HD49

HD50

HD51

HD52

HD53

HD54

HD55

HD56

HD57

HD58

HD59

HD60

HD61

HD62

HD63

HCLKCPU

3

HA20M3V#

HFLUSHA#

HBUSCHKA#

HWB/WTA#

TP003

HPENA#

HHOLDA

HEWBEA#

HBRDYC#

1

1

1

1

CPUVIO

RP71

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

HFRCMC#

HPENA#

HWB/WTA#

HAPA

HBUSCHKA#

HFLUSHA#

HSMIACT#

HA20M#

15

10

4.7K

RP69

4.7K

HBOFF#

4

10

HIGNNE#

10

HAHOLD

4

HEADS#

4

HBRDY#

4

HRESET

10

10

HSTPCLK#

10

4

4

HINTR

HKEN#

4

HINIT

HSMI#

HDPA0

HDPA1

HDPA2

HDPA3

HDPA7

HDPA6

HDPA5

HDPA4

U27D

9 8

7407S

HNMI

HNA#

R130

1 2

1

1

1

0

0

0

3

1

0

9

2

1

0

9

8

7

4

8

8

8

V

V

V

V

V

V

V

V

V

V

C

C

C

C

C

C

C

C

C

C

O

O

O

O

O

O

O

O

O

O

R

R

R

R

R

R

R

R

R

R

E

E

E

E

E

E

E

E

E

E

3

3

3

3

3

3

2

2

2

1

1

1

3

2

1

0

9

8

1

8

8

8

8

8

1

9

8

7

6

5

4

3

V

V

V

C

C

C

O

O

O

R

R

R

E

E

E

V

V

V

V

V

V

V

V

V

V

C

C

C

C

C

C

C

C

C

C

O

O

O

O

O

O

O

O

O

O

R

R

R

R

R

R

R

R

R

R

E

E

E

E

E

E

E

E

E

E

CPUVCORE

1

1

1

6

5

4

8

8

8

V

V

C

C

O

O

R

R

E

E

NC/SUSPACK#

ADSC#

FERR#

HITM#

PCHK#

LOCK#

APCHK#

CACHE#

FRCMC#

IERR#

SMIACT#

PM0/BP0

PM1/BP1

TRST#

PICCLK

PICD0

PICD1

PHITM#

PHIT#

PBGNT#

PBREQ#

UPVRM#

VCC2DET

CPUTYP

NC/TEST1

NC/TEST3

BE0#

BE1#

BE2#

BE3#

BE4#

BE5#

BE6#

BE7#

BREQ

HIT#

HLDA

PRDY

ADS#

D/C#

W/R#

M/IO

SCYC

D/P#

283

A3

301

A4

263

A5

319

A6

282

A7

300

A8

262

A9

318

A10

281

A11

280

A12

261

A13

279

A14

260

A15

278

A16

259

A17

277

A18

258

A19

276

A20

216

A21

228

A22

211

A23

222

A24

246

A25

227

A26

221

A27

265

A28

264

A29

302

A30

245

A31

285

270

252

271

253

272

254

273

255

140

229

268

250

215

230

248

AP

225

210

200

220

PCD

267

PWT

159

231

249

287

155

274

182

135

219

139

145

149

BP2

150

BP3

126

TCK

131

TDO

132

TDI

136

TMS

141

106

111

122

199

189

205

209

181

BF0

176

BF1

212

226

266

142

171

172

320

TP083

TP019

TP086

TP018

HAPA

TP085

TP092

TP012

TP013

TP084

HFRCMC#

TP011

TP087

TP088

TP090

TP089

TP007

TP091

TP006

TP005

TP004

TP002

TP014

TP021

TP020

TP015

TP017

TP016

HBF0

HBF1

TP093

TP901 1

TP097

HCPUTYPA

TP094

TP095

TP096

HA3

HA4

HA5

HA6

HA7

HA8

HA9

HA10

HA11

HA12

HA13

HA14

HA15

HA16

HA17

HA18

HA19

HA20

HA21

HA22

HA23

HA24

HA25

HA26

HA27

HA28

HA29

HA30

HA31

HBE#0

HBE#1

HBE#2

HBE#3

HBE#4

HBE#5

HBE#6

HBE#7

1

TP198

1

TP2

1

TP208

1

TP1

1

TP207

1

TP214

1

TP12

1

TP11

1

TP206

1

TP197

HSMIACT#

1

TP209

1

TP210

1

TP211

1

TP212

1

TP220

1

TP213

1

TP221

1

TP222

1

TP223

1

TP13

1

TP7

1

TP8

TP6

TP5

TP3

TP4

TP215

TP9

TP218

TP216

TP217

TP67

1 2

1 2

R115

330

R102

330

R104

330

1 2

1

1

1

1

1

1

1

1

1

HA[3..31]

HADSC#

HBE#[0..7]

HFERR#

HHITM#

HLOCK#

HCACHE#

HADS#

HD/C#

HW/R#

HM/IO#

4

CORE/BUS

SPEED RATIO

CPUVIO

1

3

HBF0R HBF1R

5

1 2

1 2

3/2X

2X

3X

5/2X

R110

R114

3..6

CPUVCORE

C195

1 2

1uF

C187

1 2

1uF

C218

1 2

1uF

C209

1 2

CPUVIO

C180

1 2

C194

1 2

C221

1 2

C207

1 2

C213

1 2

C174

1 2

C157

1 2

220uF

C172

1 2

0.1uF

C161

1 2

0.1uF

C159

1 2

0.1uF

C173

1 2

0.1uF

1uF

1uF

1uF

1uF

1uF

1uF

1uF

5,6

4..6

10

4

4

4

4

4

4..6

4

JB2

1-3,2-4

3-5,2-4

1-3,4-6

3-5,4-6

JB2

2

4

6

JB3

330

330

C196

1 2

C188

1 2

C186

1 2

C205

1 2

C177

1 2

C178

1 2

C179

1 2

C206

1 2

C217

1 2

C193

1 2

C154

1 2

0.1uF

C158

1 2

0.1uF

C155

1 2

0.1uF

C160

1 2

0.1uF

C163

1 2

0.1uF

C212

1 2

1uF

1uF

1uF

1uF

1uF

1uF

1uF

1uF

1uF

1uF

C219

1 2

C199

1 2

C200

1 2

C201

1 2

C162

1 2

0.1uF

C164

1 2

0.1uF

C130

1 2

0.1uF

1uF

1uF

1uF

1uF

1uF

THIS DRAWING CONTAINS INFORMATION

WHICH HAS NOT BEEN VERIFIED FOR

MANUFACTURING AN END USER PRODUCT.

INTEL IS NOT RESPONSIBLE FOR THE

MISUSE OF THIS INFORMATION.

Title

Size Document Number REV

C 82430HX B.1

Date: June 19, 1997Sheet 2 of 24

INTEL CORP.

PRIMARY CPU (Socket 7)

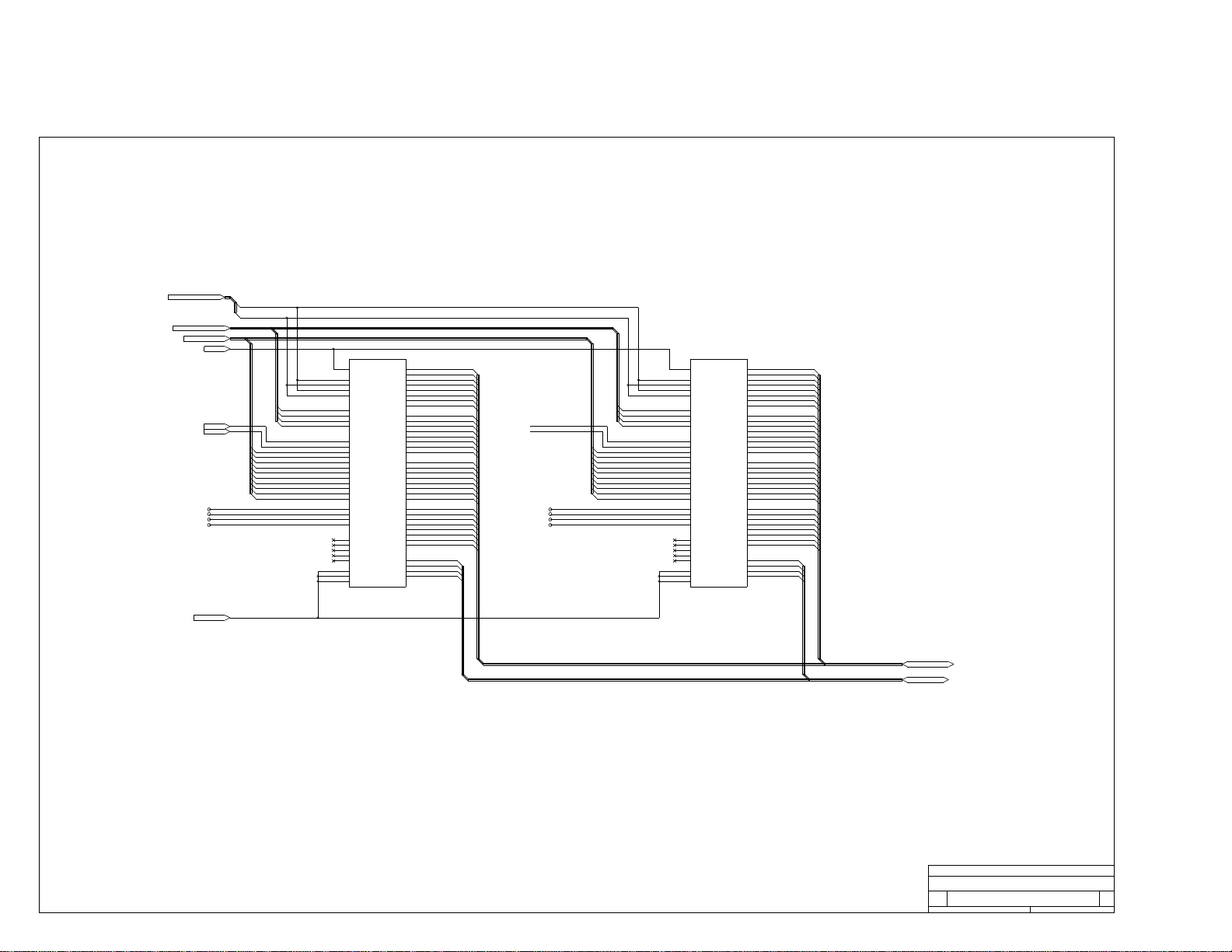

Page 3

2,4..6

HA27

1 2

HA27PU

1

2

R154

8.2K

1 2

14.31818MHz

C146

10pF

HA27PD

Y1

R88

4.7K

JUMPER 1

JUMPER 2

J25

1

2

3

JP3

1 2

1

2

JUMPER 3

J30

JP3

J29

JP3

C145

10pF

PIIX3OSC

CPUVIO

2

R89

4.7K

1

3

2

1

3

2

1

CLKSEL_PU

CPUVIO

C143

1 2

0.1uF

C147

0.1uF

C142

0.1uF

C136

0.1uF

C144

1 2

0.1uF

L13

1 2

1.5uH

1 2

1 2

1 2

CLKSEL0

CLKSEL1

ALWAYS STUFFED

PCLK(0:3)

50MHz

60MHz

66MHz

RESERVED

1 2

STUFF WITH 9169

12

11

BCLK(0:5) JUMPER 1

RESERVED

TP24

R80

0

48MCLKFB2

48MCLKPU

1

U26B

0

9

P

Q

D

R

CLK

C

8

Q

L

74ALS74AS

1

3

25MHz

30MHz

33MHz

XTAL1

XTAL2

1

CLKGENP1

CLKVCC3

TP029

2-3

2-3

1-2

1-2

5

13

12

2

3

1

14

20

26

8

2

3

JUMPER 2 JUMPER 3

2-3

1-2

2-3

1-2

R81

1 2

22

DO NOT STUFF

U28

OE

SEL0SEL1-

X1

X2

VCC3

VCC3

VCC3

VCC3

VCC3

ICS9159-02S

D

CLK

KBD_CLK1R

48MCLKFB1

4

P

Q

R

C

Q

L

1

ISA14MHZ

APIC14MHZ

HCLK0

HCLK1

HCLK2

HCLK3

PCLK0

PCLK1

PCLK2

PCLK3

PCLK4

PCLK5

24MHZ

12MHZ

1 2

U26A

5

6

74ALS74AS

48MFFOUT1

GND

GND

GND

GND

R70

10K

RAWOSC

2

R78

22

1

R2

1 2

220

OSCPULLDN

1

3

12 11

U3D

74LS125S

1 2

1 2

1 2

STUFF WITH 9159

R69

22

R66

22

R61

22

R62

22

R63

22

R64

22

R68

22

R71

22

R67

22

R72

22

R75

22

TP022

OSCR

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

R76

22

R73

22

1

X

1-2

2-3

2-3

1

R79

22

2

PIIX3OSCR

28

RAWOSCR

27

HCLKCPUR

6

HCLKSRAM0R

7

HCLKSRAM1R

9

10

PCLK0R

15

PCLK1R

16

PCLK2R

18

PCLK3R

19

PCLKTXCR

21

PCLKPIIX3R

22

AIPCLKR

24

KBD_CLKR

25

4

23

17

11

VCC

R77

1 2

22

R74

1 2

22

R5

1 2

22

HCLKSRAM0

HCLKSRAM1

TP922

PCLK0

PCLK1

PCLK2

PCLK3

PCLKTXC

PCLKPIIX3

USBCLK

AIPCLK

KBD_CLK

10

HCLKTXC

HCLKCPU

18

18

19

19

OSC

20

4

2

6

5

4

10

10

12

15

THIS DRAWING CONTAINS INFORMATION

WHICH HAS NOT BEEN VERIFIED FOR

MANUFACTURING AN END USER PRODUCT.

INTEL IS NOT RESPONSIBLE FOR THE

MISUSE OF THIS INFORMATION.

Title

Size Document Number REV

B 82430HX B.1

Date: June 19, 1997 Sheet 3 of 24

INTEL CORP.

Clock Generator

Page 4

7,8

MCAS#[0..7]

THIS DRAWING CONTAINS INFORMATION

WHICH HAS NOT BEEN VERIFIED FOR

MANUFACTURING AN END USER PRODUCT.

INTEL IS NOT RESPONSIBLE FOR THE

MISUSE OF THIS INFORMATION.

10

15

PIIX3INIT

KBRST#

MCAS#0

MCAS#4

MCAS#2

MCAS#6

MCAS#3

MCAS#7

MCAS#1

MCAS#5

2,3,5,6

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

7,8

7,8

7,8

7,8

3

2

HCACHE#

2

2

HSMIACT#

2

HADS#

2

2

2

2

2

3

HCLKTXC

RP67

10

RP68

10

HKEN#

HBRDY#

HNA#

HAHOLD

HEADS#

HBOFF#

HA[3..31]

MA[2..11]

MP[0..7]

MWE#

MD[0..63]

U2B

74HCT14S

4

7

7

8

8

R153

1 2

22

KBRST

MAA0

MAA1

MAB0

MAB1

1

2

MCAS#R0

MCAS#R1

MCAS#R2

MCAS#R3

MCAS#R4

MCAS#R5

MCAS#R6

MCAS#R7

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

HA3

HA4

HA5

HA6

HA7

HA8

HA9

HA10

HA11

HA12

HA13

HA14

HA15

HA16

HA17

HA18

HA19

HA20

HA21

HA22

HA23

HA24

HA25

HA26

HA27

HA28

HA29

HA30

HA31

MRAS#R0

MRAS#R1

MRAS#R2

MRAS#R3

TP027

TP026

TP025

TP024

MP0

MP1

MP2

MP3

MP4

MP5

MP6

MP7

MWE#R

U16A

74ALS32S

2

HLOCK#

2,5,6

HW/R#

2

HD/C#

2

HM/IO#

2

HHITM#

HBE#[0..7]

H

H

H

H

H

H

H

H

B

B

B

B

B

B

B

B

E

#

1

1

2

2

1

1

2

6

5

0

1

9

8

2

7

8

5

6

5

1

9

A

H

B

E

N

B

A

S

H

C

O

A

A

R

D

M

O

L

F

D

#

D

S

M

D

6

2

1

6

M

D

6

2

U27A

7407S

I

L

K

F

S

Y

#

A

D

I

#

#

#

C

N

T

#

M

M

M

M

M

M

M

M

M

D

D

D

D

D

D

D

D

D

5

5

5

5

5

5

5

6

6

3

4

5

6

7

8

9

0

1

1

1

1

7

4

3

1

3

6

4

0

9

0

9

8

7

2

7

0

M

M

M

M

M

M

M

M

D

D

D

D

D

D

D

D

5

5

5

5

5

5

6

6

4

5

6

7

8

9

0

1

CPUVIO

275

A3

315

A4

252

A5

316

A6

312

A7

272

A8

271

A9

311

A10

291

A11

251

A12

310

A13

270

A14

290

A15

250

A16

309

A17

289

A18

269

A19

249

A20

273

A21

254

A22

253

A23

294

A24

293

A25

274

A26

313

A27

314

A28

255

A29

295

A30

292

A31

121

RAS0#

110

RAS1#

109

RAS2#

96

RAS3#

187

RAS4#

197

RAS5#

186

RAS6#

196

RAS7#

145

CAS0#

159

CAS1#

131

CAS2#

173

CAS3#

130

CAS4#

144

CAS5#

120

CAS6#

172

CAS7#

276

MAA0

236

MAA1

296

MAB0

256

MAB1

317

MA2

297

MA3

277

MA4

257

MA5

237

MA6

298

MA7

258

MA8

319

MA9

318

MA10

278

MA11

133

MPD0

123

MPD1

146

MPD2

113

MPD3

132

MPD4

124

MPD5

134

MPD6

122

MPD7

HINITD

MWE#

M

D

6

3

5

5

M

D

6

3

1 2

235

3

7

1

2

2

2

1

1

1

2

1

2

3

3

3

5

3

1

3

7

9

1

3

4

3

9

8

2

7

M

D

W

K

C

H

H

B

B

/

/

/

E

A

L

I

E

E

I

C

R

N

C

O

T

7

6

O

#

#

#

H

C

M

#

#

#

/

E

K

#

I

#

#

N

V

M

M

M

M

M

M

M

M

M

M

D

D

D

D

D

D

D

D

D

D

4

4

4

4

4

4

4

5

5

5

3

4

5

6

7

8

9

0

1

2

7

5

7

5

2

2

2

2

1

1

7

6

5

4

8

4

2

1

9

8

4

2

3

1

9

8

M

M

M

M

M

M

M

M

M

M

D

D

D

D

D

D

D

D

D

D

4

4

4

4

4

4

5

5

5

5

4

5

6

7

8

9

0

1

2

3

2

R91

330

1

HINIT

H

H

E

E

E

E

E

E

E

D

D

#

#

#

#

#

#

#

6

6

0

1

2

3

4

5

6

2

3

1

1

1

1

1

1

1

6

6

6

6

5

5

5

2

6

5

4

3

2

1

0

1

1

H

B

B

B

B

B

B

H

H

D

E

E

E

E

E

E

D

D

6

5

4

3

2

1

0

6

6

1

#

#

#

#

#

#

3

2

M

M

M

M

M

M

M

M

M

M

D

D

D

D

D

D

D

D

D

D

3

3

3

3

3

3

3

4

4

4

3

4

5

6

7

8

9

0

1

2

2

2

2

1

1

1

1

9

6

2

4

2

0

9

7

6

1

8

0

0

4

1

9

0

5

0

2

M

M

M

M

M

M

M

M

M

M

D

D

D

D

D

D

D

D

D

D

3

3

3

3

3

3

4

4

4

4

4

5

6

7

8

9

0

1

2

3

2

H

H

H

H

H

H

H

H

H

H

D

D

D

D

D

5

5

5

6

6

7

8

9

0

1

6

6

4

4

4

3

2

1

2

3

H

H

H

H

D

D

D

D

5

5

5

6

7

8

9

0

M

M

M

M

D

D

D

D

2

3

3

3

9

0

1

2

1

7

3

2

2

7

6

4

8

6

3

3

M

M

M

M

M

D

D

D

D

D

2

3

3

3

3

9

0

1

2

3

H

H

H

H

D

D

D

D

D

D

D

D

D

5

5

5

5

5

4

4

5

5

2

3

4

5

6

8

9

0

1

1

1

1

1

0

1

0

0

8

8

8

6

8

1

6

4

3

1

4

2

1

3

H

H

H

H

H

H

H

H

H

H

D

D

D

D

D

D

D

D

D

D

4

4

4

5

5

5

5

5

5

5

7

8

9

0

1

2

3

4

5

6

M

M

M

M

M

M

M

M

M

M

D

D

D

D

D

D

D

D

D

D

1

2

2

2

2

2

2

2

2

2

9

0

1

2

3

4

5

6

7

8

2

1

1

1

9

9

7

1

5

0

8

7

4

9

7

8

9

7

0

9

4

8

M

M

M

M

M

M

M

M

M

D

D

D

D

D

D

D

D

D

2

2

2

2

2

2

2

2

2

4

5

6

7

8

0

1

2

3

H

H

D

D

4

4

6

7

1

1

2

0

7

2

H

D

4

6

M

D

1

8

2

2

2

0

2

8

M

M

D

D

1

1

8

9

H

H

H

D

D

D

4

4

4

3

4

5

1

1

1

1

2

1

7

8

4

H

H

H

D

D

D

4

4

4

3

4

5

M

M

M

D

D

D

1

1

1

5

6

7

5

2

2

3

6

6

2

4

M

M

M

D

D

D

1

1

1

5

6

7

MRAS#R[0..3]

H

H

H

H

H

D

D

D

D

D

3

3

4

4

4

8

9

0

1

2

1

1

1

1

1

3

2

2

1

3

8

5

6

5

7

H

H

H

H

H

D

D

D

D

D

3

3

4

4

4

8

9

0

1

2

M

M

M

M

M

D

D

D

D

D

1

1

1

1

1

0

1

2

3

4

5

5

3

3

3

9

8

8

6

5

M

M

M

M

M

D

D

D

D

D

1

1

1

1

1

0

1

2

3

4

H

H

H

H

H

H

H

H

H

D

D

D

D

D

D

D

D

D

2

3

3

3

3

3

3

3

3

9

0

1

2

3

4

5

6

7

1

1

1

1

1

1

1

1

1

9

9

9

7

7

4

8

3

3

3

2

4

9

8

9

0

6

5

H

H

H

H

H

H

H

H

H

D

D

D

D

D

D

D

D

D

2

3

3

3

3

3

3

3

3

9

0

1

2

3

4

5

6

7

M

M

M

M

M

M

M

M

M

D

D

D

D

D

D

D

D

D

1

2

3

4

5

6

7

8

9

2

2

2

2

1

1

1

1

8

4

4

2

1

9

7

6

1

0

1

3

4

0

8

6

1

1

M

M

M

M

M

M

M

M

M

D

D

D

D

D

D

D

D

D

1

2

3

4

5

6

7

8

9

H

D

2

8

M

D

0

H

D

2

8

2

0

4

H

D

2

7

3

0

4

M

D

0

H

H

D

D

2

2

6

7

2

1

0

9

2

1

H

H

D

D

2

2

5

6

C

C

A

A

D

D

V

S

#

#

2

7

9

MRAS#R0

MRAS#R2

MRAS#R1

MRAS#R3

H

H

H

H

H

H

D

D

D

D

D

D

2

2

2

2

2

2

0

1

2

3

4

5

2

2

2

2

2

2

2

1

2

0

1

0

8

3

6

1

5

3

H

H

H

H

H

H

D

D

D

D

D

D

1

2

2

2

2

2

9

0

1

2

3

4

C

C

G

B

C

O

W

W

S

E

E

E

#

#

#

#

2

3

2

3

3

9

0

5

2

2

9

0

9

0

1

H

H

H

H

H

H

H

H

H

H

D

D

D

D

D

D

D

D

D

D

1

1

1

1

1

1

1

1

1

1

0

1

2

3

4

5

6

7

8

9

2

2

2

2

2

2

2

2

2

2

6

8

2

6

4

6

4

2

4

1

7

8

5

8

7

6

8

7

6

4

H

H

H

H

H

H

H

H

H

H

D

D

D

D

D

D

D

D

D

D

9

1

1

1

1

1

1

1

1

1

0

1

2

3

4

5

6

7

8

T

T

T

T

T

T

T

T

T

I

I

I

I

I

I

I

I

I

O

O

O

O

O

O

O

O

O

1

2

3

4

5

6

7

8

9

0

2

2

2

3

3

3

3

3

8

3

8

0

2

0

2

2

1

8

2

2

2

3

3

4

C

C

C

C

C

C

C

C

T

T

T

T

T

T

T

T

A

A

A

A

A

A

A

A

G

G

G

G

G

G

G

G

1

9

8

3

4

5

6

7

0

RP66

1 8

2 7

3 6

4 5

10

H

H

H

H

H

H

H

H

H

H

D

D

D

D

D

D

D

D

D

D

0

1

2

3

4

5

6

7

8

9

3

3

3

3

2

2

2

2

2

2

0

0

0

0

8

8

6

1

4

8

2

5

7

H

H

H

D

D

D

6

7

8

T

T

I

I

O

O

0

1

2

2

2

0

6

6

7

0

1

C

C

C

T

T

T

A

A

A

G

G

G

0

1

2

6

5

H

D

5

T

W

E

#

2

8

0

MRAS#0

MRAS#2

MRAS#1

MRAS#3

8

5

H

H

D

D

3

4

PCLKIN

C/BE0#

C/BE1#

C/BE2#

C/BE3#

FRAME#

DEVSEL#

IRDY#

TRDY#

STOP#

LOCK#

REQ0#

REQ1#

REQ2#

REQ3#

GNT0#

GNT1#

GNT2#

GNT3#

PHLD#

PHLDA#

SERR#

TEST#

VDD5V

U23

5

7

6

H

H

H

D

D

D

0

1

2

90

15

AD0

14

AD1

33

AD2

13

AD3

52

AD4

32

AD5

12

AD6

51

AD7

11

AD8

50

AD9

30

AD10

10

AD11

49

AD12

29

AD13

9

AD14

48

AD15

47

AD16

27

AD17

7

AD18

46

AD19

26

AD20

6

AD21

45

AD22

25

AD23

66

AD24

44

AD25

24

AD26

4

AD27

23

AD28

3

AD29

22

AD30

2

AD31

31

C/BE#0

28

C/BE#1

8

C/BE#2

5

C/BE#3

86

89

87

88

91

85

PREQ#0

67

PREQ#1

69

PREQ#2

71

PREQ#3

73

PGNT#0

68

PGNT#1

70

PGNT#2

72

PGNT#3

74

64

65

92

93

239

TESTIN#

301

94

VDD5V

TXC

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

RST#

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

PAR

HD[0..63]

PCLKTXC

AD[0..31]

C/BE#[0..3]

PGNT#[0..3]

R37 10K

1 2

R52 10K

1 2

R57 10K

R56

100

1 2

1

C131

1.0uF

2

MRAS#[0..3]

Title

Size Document Number REV

C 82430HX B.1

Date: June 19, 1997Sheet 4 of 24

2,5,6

2,5,6

3

10,18,19

10,18,19

FRAME#

10,18,19,21

DEVSEL#

10,18,19,21

IRDY#

10,18,19,21

TRDY#

10,18,19,21

STOP#

10,18,19,21

PLOCK#

18,19,21

PREQ#0

4,18,19,21

PREQ#1

4,18,19,21

PREQ#2

4,18,19,21

PREQ#3

4,18,19,21

18,19,21

1 2

PHOLD#

10

PHLDA#

10

PAR

10,18,19,21

SERR#

10,18,19,21

5,6,10,18,19

PCIRST#

VCC

CTWE#

5

CTAG[0..10]

CBWE#

5,6

CGWE#

5,6

COE#

5,6

CCS#

5,6

CADS#

5,6

CADV#

5,6

7,8

INTEL CORP.

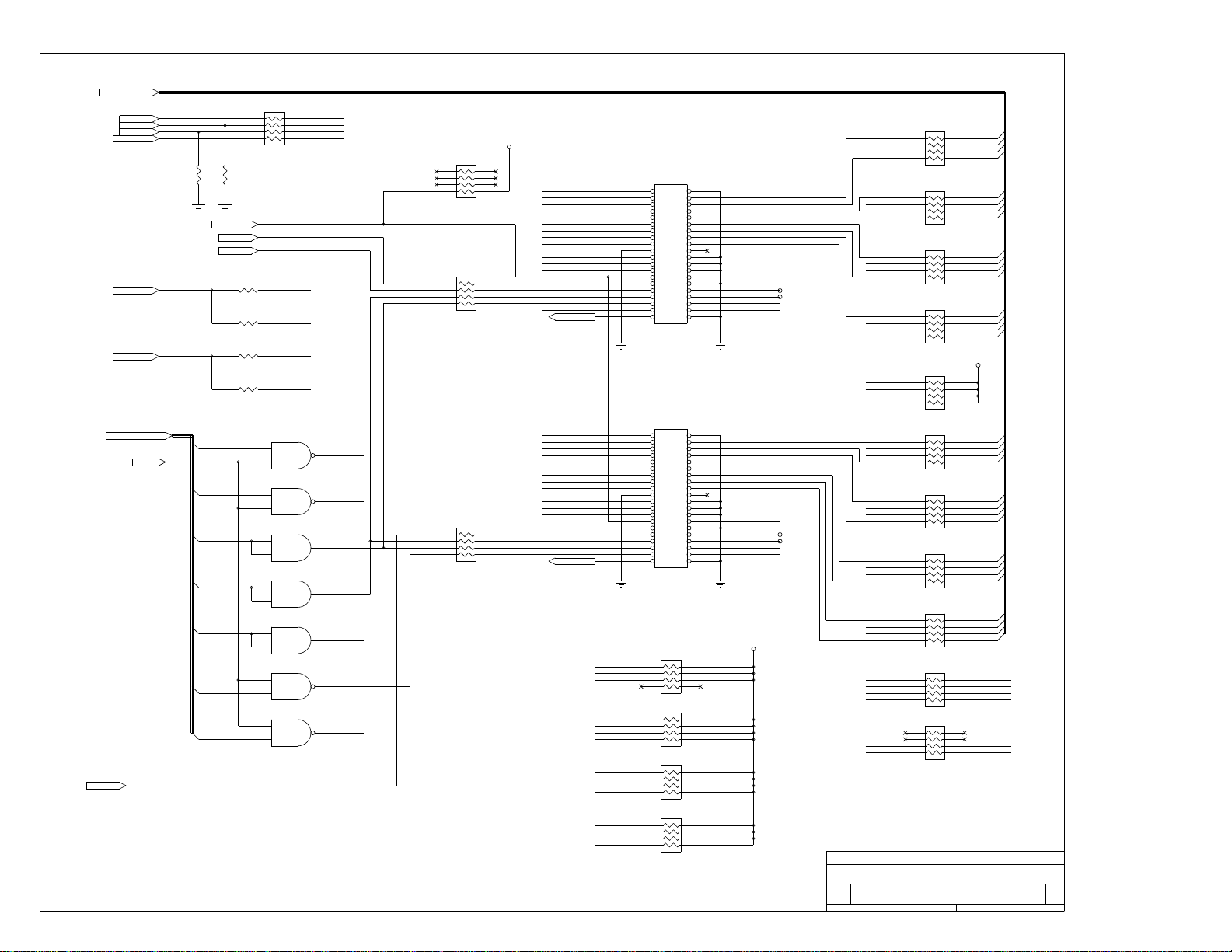

Triton II controller (TXC)

1 2

R54

330

5,6

VCC

CPUVIO

Page 5

2..4,6

2,4,6

4,6,10,18,19

CPUVIO

1 2

1 2

1 2

1 2

2,4,6

2,4,6

R106

4.7K

R101

4.7K

R84

4.7K

R95

4.7K

HD[0..63]

HA[3..18]

HBE#[0..7]

HCLKSRAM1

3

4,6

4,6

4,6

HADSC#

2,6

4,6

4,6

4,6

CBURST_SEQ2

6

CBURST_SEQ1

6

CRPU1

6

CPUVIOVCC

CRPU2

6

HW/R#

PCIRST#

CADV#

CADS#

CBWE#

CGWE#

HA28

HA29

HA30

HA31

CCS#

COE#

4

1 8

2 7

3 6

4 5

CTWE#

RP70

10K

HA18

HA28

HA29

HA30

HA31

R65

0

R107

1 2

4.7K

R103

1 2

4.7K

R94

4.7K

R96

4.7K

U22

HA3

37

A0

HA4

36

A1

HA5

35

A2

HA6

34

A3

HA7

33

A4

32

HA8

A5

100

HA9

A6

99

HA10

A7

82

HA11

A8

81

HA12

A9

44

HA13

A10

45

HA14

A11

46

HA15

A12

47

HA16

A13

48

HA17

A14

HBE#0

93

BW1#

HBE#1

94

BW2#

HBE#2

95

BW3#

HBE#3

96

BW4#

89

CLK

98

CE#

92

CE2#

97

CE2

86

OE#

83

ADV#

84

ADSP#

85

ADSC#

87

BWE#

88

GW#

64

ZZ

31

MODE

50

NC

51

NC

1

NC

80

NC

30

NC

49

NC

32KX32 SRAM

CRPD3

1 2

U24

10

HA13

HA14

HA15

HA17

HA7

HA5

HA12

HA10

HA9

1 2

1 2

HA8

HA16

HA6

HA11

DQ1

A0

9

DQ2

A1

8

DQ3

A2

7

DQ4

A3

6

DQ5

A4

5

DQ6

A5

4

DQ7

A6

3

DQ8

A7

25

A8

24

A9

21

A10

23

A11

2

A12

26

A13

1

A14

27

WE#

20

CE#

22

OE#

SRAM32KX8

52

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

VDD1

VDD2

RESET#

W/R#

NF1

NF2

FT#

11

CTAG0

12

CTAG1

13

CTAG2

15

CTAG3

16

CTAG4

17

CTAG5

18

CTAG6

19

CTAG7

HD0

53

HD1

56

HD2

57

HD3

58

HD4

59

HD5

62

HD6

63

HD7

68

HD8

69

HD9

72

HD10

73

HD11

74

HD12

75

HD13

78

HD14

79

HD15

2

HD16

3

HD17

HD18

HD19

HD20

HD21

HD22

HD23

HD24

HD25

HD26

HD27

HD28

HD29

HD30

HD31

VDD1A

VDD2A

PCIRST#D

HW/R#D

CTAG10D

NF2D

STUFFING OPTION

2

C228

1

0.01uF

12C227

1 2

6

7

8

9

12

13

18

19

22

23

24

25

28

29

16

66

38

39

42

43

14

CRPU2

1 2

1 2

0.01uF

R1450

R15210K

VCC

R1320

R1330

R1440

1 2

R1460

1 2

1 2

3.3uF

C229

HA13

HA14

HA15

HA17

HA7

HA5

HA12

HA10

HA9

HA8

HA16

HA6

HA11

1

2

2

C230

1

1uF

CPUVIO

CTAG10

CTAG10 1 2

U25

10

A0

9

A1

8

A2

7

A3

6

A4

5

A5

4

A6

3

A7

25

A8

24

A9

21

A10

23

A11

2

A12

26

A13

1

A14

27

WE#

20

CE#

22

OE#

SRAM32KX8

R155

0

STUFFING OPTION

11

DQ1

12

DQ2

13

DQ3

15

DQ4

16

DQ5

17

DQ6

18

DQ7

19

DQ8

CTAG8

CTAG9

CTAG10T

UNUSD11

UNUSD12

UNUSD13

UNUSD14

UNUSD15

HBE#4

HBE#5

HBE#6

HBE#7

2

R83

220

1

HA3

37

HA4

36

HA5

35

HA6

34

HA7

33

32

HA8

100

HA9

99

HA10

82

HA11

81

HA12

44

HA13

45

HA14

46

HA15

47

HA16

48

HA17

93

94

95

96

89

98

92

97

86

83

84

85

87

88

64

31

50

51

1

80

30

49

CTAG[0..10]

CTAG10

CONFIGURATION RESISTORS

U31

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

BW1#

BW2#

BW3#

BW4#

CLK

CE#

CE2#

CE2

OE#

ADV#

ADSP#

ADSC#

BWE#

GW#

ZZ

MODE

NC

NC

NC

NC

NC

NC

32KX32 SRAM

RP73

10K

4,6

1 8

2 7

3 6

4 5

R82

1 2

100K

R90

4.7K

RESET#

VCC

1 2

CA18

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

VDD1

VDD2

W/R#

52

HD32

DQ0

53

HD33

DQ1

56

HD34

DQ2

57

HD35

DQ3

58

HD36

DQ4

59

HD37

DQ5

62

HD38

DQ6

63

HD39

DQ7

68

HD40

DQ8

69

HD41

DQ9

72

HD42

73

HD43

74

HD44

75

HD45

78

HD46

HD47

HD48

HD49

HD50

HD51

HD52

HD53

HD54

HD55

HD56

HD57

HD58

HD59

HD60

HD61

HD62

HD63

VDD1B

VDD2B

PCIRST#C

HW/R#C

CTAG10C

NF2C

STUFFING OPTION

2

C232

0.01uF

2

1

79

2

3

6

7

8

9

12

13

18

19

22

23

24

25

28

29

16

66

38

39

42

NF1

43

NF2

14

FT#

CPUVIO

6

1 2

1 2

C231

0.01uF1

R1560

0

R157

1 2

R1580

R1491K

R1350

R1360

C233

3.3uF 1

1 2

1 2

1 2

VCC

C234

2

2

1uF

1

THIS DRAWING CONTAINS INFORMATION

WHICH HAS NOT BEEN VERIFIED FOR

MANUFACTURING AN END USER PRODUCT.

INTEL IS NOT RESPONSIBLE FOR THE

MISUSE OF THIS INFORMATION.

CACHE CONFIG HA31 HA30 HA29 HA28

NO SRAM

256K PBSRAM

512K PBSRAM

11X X

10 1 1

0010

Title

Size Document Number REV

C 82430HX B.1

Date: June 19, 1997Sheet 5 of 24

INTEL CORP.

Synchronous Cache, Lower 256K

Page 6

2..5

2,4,5

HA[3..17]

HBE#[0..7]

HCLKSRAM0

3

4,5

2,5

4,5

CBURST_SEQ1

5

4,5

4,5

4,5,10,18,19

2,4,5

4,5

4,5

5

4,5

CADV#

HADSC#

CADS#

CBWE#

CGWE#

HW/R#

CTAG10

CRPU1

5

CPUVIO

CCS#

CA18

COE#

1 8

2 7

3 6

4 5

PCIRST#

RP74

10K

HBE#0

HBE#1

HBE#2

HBE#3

CRPU3

HA3

HA4

HA5

HA6

HA7

HA8

HA9

HA10

HA11

HA12

HA13

HA14

HA15

HA16

HA17

CRPU3

U29

37

A0

36

A1

35

A2

34

A3

33

A4

32

A5

100

A6

99

A7

82

A8

81

A9

44

A10

45

A11

46

A12

47

A13

48

A14

93

BW1#

94

BW2#

95

BW3#

96

BW4#

89

CLK

98

CE#

92

CE2#

97

CE2

86

OE#

83

ADV#

84

ADSP#

85

ADSC#

87

BWE#

88

GW#

64

ZZ

31

MODE

50

NC

51

NC

1

NC

80

NC

30

NC

49

NC

32KX32 SRAM

CBURST_SEQ1

CRPU2

CBURST_SEQ2

37

36

35

34

33

32

100

99

82

81

44

45

46

47

48

93

94

95

96

89

98

92

97

86

83

84

85

87

88

64

31

50

51

1

80

30

49

U32

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

BW1#

BW2#

BW3#

BW4#

CLK

CE#

CE2#

CE2

OE#

ADV#

ADSP#

ADSC#

BWE#

GW#

ZZ

MODE

NC

NC

NC

NC

NC

NC

32KX32 SRAM

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

VDD1

VDD2

RESET#

W/R#

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

NF1

NF2

FT#

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

VDD1

VDD2

RESET#

W/R#

NF1

NF2

FT#

5

5

53

56

57

58

59

62

63

68

69

72

73

74

75

78

79

2

3

6

7

8

9

12

13

18

19

22

23

24

25

28

29

16

66

38

39

42

43

14

HD1

HD2

HD3

HD4

HD5

HD6

HD7

HD8

HD9

HD10

HD11

HD12

HD13

HD14

HD15

HD16

HD17

HD18

HD19

HD20

HD21

HD22

HD23

HD24

HD25

HD26

HD27

HD28

HD29

HD30

HD31

VDD1C

VDD2C

PCIRST#B

HW/R#B

CTAG10B

NF2B

1

2

R55

220

STUFFING OPTION

2

C236

1

0.01uF

2

1

C235

0.01uF

R1470

1 2

1 2

R1480

R1380

R1390

1 2

R1400

R1371K

C237

3.3uF

1 2

1 2

1 2

VCC

CTAG10

C238

2

2

1

1

1uF

HD0

52

HA3

HA4

HA5

HA6

HA7

HA8

HA9

HA10

HA11

HA12

HA13

HA14

HA15

HA16

HA17

HBE#4

HBE#5

HBE#6

HBE#7

HCLKSRAM0

CCS#

CA18

CRPU3

COE#

CADV#

HADSC#

CADS#

CRPD1

HD32

52

HD33

53

HD34

56

HD35

57

HD36

58

HD37

59

HD38

62

HD39

63

HD40

68

HD41

69

HD42

72

HD43

73

HD44

74

HD45

75

HD46

78

HD47

79

HD48

2

HD49

3

HD50

6

HD51

7

HD52

8

HD53

9

HD54

12

HD55

13

HD56

18

HD57

19

HD58

22

HD59

23

HD60

24

HD61

25

HD62

28

HD63

29

VDD1D

16

VDD2D

66

PCIRST#A 1 2

38

HW/R#A

39

CTAG10A

42

NF2A

43

14

STUFFING OPTION

C240

0.01uF

HD[0..63]

VCC

R1500

1 2

1 2

2

1

2,4,5

C239

0.01uF

R1341K

R1510

3.3uF

R1410

R1420

1 2

R1430

1 2

1 2

2

1

C241

C242

2

2

1

1

1uF

THIS DRAWING CONTAINS INFORMATION

WHICH HAS NOT BEEN VERIFIED FOR

MANUFACTURING AN END USER PRODUCT.

INTEL IS NOT RESPONSIBLE FOR THE

MISUSE OF THIS INFORMATION.

Title

Synchronous Cache, Upper 256K

Size Document Number REV

B 82430HX B.1

Date: June 19, 1997 Sheet 6 of 24

INTEL CORP.

Page 7

DRAM POWER

5 VOLTS 3.3 VOLTS

1-3,2-4 3-5,4-6

CPUVIO

VCC

4,8

4,8

MRAS#[0..3]

MCAS#[0..7]

MA[2..11]

4,8

4,8

JB1

1 2

3 4

5 6

JB3

MODULE 1 (BANK 1)MODULE 0 (BANK 1)

MRAS#0

MRAS#1

MWE#

MCAS#0

MCAS#1

MCAS#2

MAA0

4

MAA1

4

TP23

TP923

TP25

TP26

MCAS#3

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

TP039

1

TP038

1

TP041

1

1

TP040

47

44

45

34

33

40

43

41

42

12

13

14

15

16

17

18

28

31

32

19

29

67

68

69

70

11

46

48

66

71

10

30

59

U18

WRAS0-

RAS1RAS2RAS3-

CAS0CAS1CAS2CAS3-

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

ID1

ID2

ID3

ID4

RES1

RES2

RES3

RES4

RES5

VCC

VCC

VCC

32MX36SIMV

DQ8/P0

DQ17/P1

DQ26/P2

DQ35/P3

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

2

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ9

MD0

4

MD1

6

MD2

8

MD3

20

MD4

22

MD5

24

MD6

26

MD7

49

MD8

51

MD9

53

MD10

55

MD11

57

MD12

61

MD13

63

MD14

65

MD15

3

MD16

5

MD17

7

MD18

9

MD19

21

MD20

23

MD21

25

MD22

27

MD23

MD24

50

MD25

52

MD26

54

56

MD27

58

MD28

60

MD29

62

MD30

64

MD31

36

MP0

37

MP1

35

MP2

38

MP3

MAA0

MAA1

TP27

TP28

TP29

TP30

MCAS#4

MCAS#5

MCAS#6

MCAS#7

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

TP105

1

TP102

1

TP101

1

TP023

1

47

44

45

34

33

40

43

41

42

12

13

14

15

16

17

18

28

31

32

19

29

67

68

69

70

11

46

48

66

71

10

30

59

U19

WRAS0-

RAS1RAS2RAS3-

CAS0CAS1CAS2CAS3-

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

ID1

ID2

ID3

ID4

RES1

RES2

RES3

RES4

RES5

VCC

VCC

VCC

32MX36SIMV

DQ8/P0

DQ17/P1

DQ26/P2

DQ35/P3

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

2

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ9

MD32

4

MD33

6

MD34

8

MD35

20

MD36

22

MD37

24

MD38

26

MD39

49

MD40

51

MD41

53

MD42

55

MD43

57

MD44

61

MD45

63

MD46

65

MD47

3

MD48

5

MD49

7

MD50

9

MD51

21

MD52

23

MD53

25

MD54

27

MD55

MD56

50

MD57

52

MD58

54

56

MD59

58

MD60

60

MD61

62

MD62

64

MD63

36

MP4

37

MP5

35

MP6

38

MP7

DRAMVCC

8,24

MD[0..63]

MP[0..7]

4,8

4,8

THIS DRAWING CONTAINS INFORMATION

WHICH HAS NOT BEEN VERIFIED FOR

MANUFACTURING AN END USER PRODUCT.

INTEL IS NOT RESPONSIBLE FOR THE

MISUSE OF THIS INFORMATION.

Title

Size Document Number REV

C 82430HX B.1

Date: June 19, 1997Sheet 7 of 24

INTEL CORP.

Memory Modules 0 & 1

Page 8

4,7

4,7

MRAS#[0..3]

MCAS#[0..7]

MA[2..11]

4,7

4,7

TP41

TP42

TP43

TP44

7,24

4

4

DRAMVCC

MWE#

MAB0

MAB1

MODULE 3 (BANK 2)MODULE 2 (BANK 2)

MRAS#2

MRAS#3

U20

47

W-

44

RAS0-

45

RAS1-

34

RAS2-

33

40

43

41

42

12

13

14

15

16

17

18

28

31

32

19

29

67

68

69

70

11

46

48

66

71

10

30

59

RAS3-

CAS0CAS1CAS2CAS3-

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

ID1

ID2

ID3

ID4

RES1

RES2

RES3

RES4

RES5

VCC

VCC

VCC

32MX36SIMV

MCAS#0

MCAS#1

MCAS#2

MCAS#3

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

TP112

1

TP111

1

TP110

1

TP109

1

DQ8/P0

DQ17/P1

DQ26/P2

DQ35/P3

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

2

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ9

MD0

4

MD1

6

MD2

8

MD3

20

MD4

22

MD5

24

MD6

26

MD7

49

MD8

51

MD9

53

MD10

55

MD11

57

MD12

61

MD13

63

MD14

65

MD15

3

MD16

5

MD17

7

MD18

9

MD19

21

MD20

23

MD21

25

MD22

27

MD23

MD24

50

MD25

52

MD26

54

56

MD27

58

MD28

60

MD29

62

MD30

64

MD31

36

MP0

37

MP1

35

MP2

38

MP3

TP45

TP46

TP47

TP48

MAB0

MAB1

1

1

1

1

TP103

TP107

TP108

TP113

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MCAS#4

MCAS#5

MCAS#6

MCAS#7

47

44

45

34

33

40

43

41

42

12

13

14

15

16

17

18

28

31

32

19

29

67

68

69

70

11

46

48

66

71

10

30

59

U21

WRAS0-

RAS1RAS2RAS3-

CAS0CAS1CAS2CAS3-

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

ID1

ID2

ID3

ID4

RES1

RES2

RES3

RES4

RES5

VCC

VCC

VCC

32MX36SIMV

DQ8/P0

DQ17/P1

DQ26/P2

DQ35/P3

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

2

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ9

MD32

4

MD33

6

MD34

8

MD35

20

MD36

22

MD37

24

MD38

26

MD39

49

MD40

51

MD41

53

MD42

55

MD43

57

MD44

61

MD45

63

MD46

65

MD47

3

MD48

5

MD49

7

MD50

9

MD51

21

MD52

23

MD53

25

MD54

27

MD55

MD56

50

MD57

52

MD58

54

56

MD59

58

MD60

60

MD61

62

MD62

64

MD63

36

MP4

37

MP5

35

MP6

38

MP7

MD[0..63] 4,7

4,7

MP[0..7]

THIS DRAWING CONTAINS INFORMATION

WHICH HAS NOT BEEN VERIFIED FOR

MANUFACTURING AN END USER PRODUCT.

INTEL IS NOT RESPONSIBLE FOR THE

MISUSE OF THIS INFORMATION.

Title

Size Document Number REV

C 82430HX B.1

Date: June 19, 1997Sheet 8 of 24

INTEL CORP.

Memory Modules 2 & 3

Page 9

VCC

10,12,15,20,21

10,20,21

10,20,21

15,16

INSTALL IF

1M FLASH 1 2

INSTALL IF

2M FLASH 1 2

SA[0..19]

MEMW#

MEMR#

ROMCS#

10

U16D

12

10,16

XD[0..7]

XOE#

13

74ALS32S

SA15

SA14

SA13

SA12

SA11

SA10

SA9

SA8

SA7

SA6

SA5

SA4

SA3

SA2

SA1

SA0

1

2

U2C

5

74HCT14S

R9

0

R6

0

11

SA16/17#

6

SA16/17

SA16

SA17

R10

1 2

VCC

8.2K

J3

SA16

SA15

SA14

SA13

SA12

SA11

SA10

SA9

SA8

SA7

SA6

SA5

SA4

SA3

SA2

SA1

SA0

F002CE#

1

O

JP1

J11

1

2

3

JP3

BIOSMSB

U6

40

A17

1

A16

2

A15

3

A14

4

A13

5

A12

6

A11

36

A10

7

A9

8

A8

14

A7

15

A6

16

A5

17

A4

18

A3

19

A2

20

A1

21

A0

9

WE#

24

OE#

22

CE#

10

PWD#

28F002BXTSOP

OPTIONAL 2MB FLASH

FL2MPU

ALLOWS PROGRAMMING

OF BOOT BLOCK IN

MANUFACTURING

MODE POS

NORMAL 1-2

RECOVERY 2-3

25

DQ0

26

DQ1

27

DQ2

28

DQ3

32

DQ4

33

DQ5

34

DQ6

35

DQ7

13

NC

29

NC

37

NC

38

NC

11

VPP

1

C36

2

O.1uF

XD0

XD1

XD2

XD3

XD4

XD5

XD6

XD7

R14

8.2K

FL_VPP

FL_PNPPU

2

3

29

28

4

25

23

26

27

5

6

7

8

9

10

11

12

31

24

22

30

+12V

U7

A16

A15

A14

A13

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

WE#

OE#

CE#

PWD#

28F001BX

J12

1

2

3

JP3

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

VPP

13

14

15

17

18

19

20

21

1

MODE POS

PNP

NON-PNP

XD0

XD1

XD2

XD3

XD4

XD5

XD6

XD7

1-2

2-3

THIS DRAWING CONTAINS INFORMATION

WHICH HAS NOT BEEN VERIFIED FOR

MANUFACTURING AN END USER PRODUCT.

INTEL IS NOT RESPONSIBLE FOR THE

MISUSE OF THIS INFORMATION.

Title

Size Document Number REV

B 82430HX B.1

Date: June 19, 1997 Sheet 9 of 24

INTEL CORP.

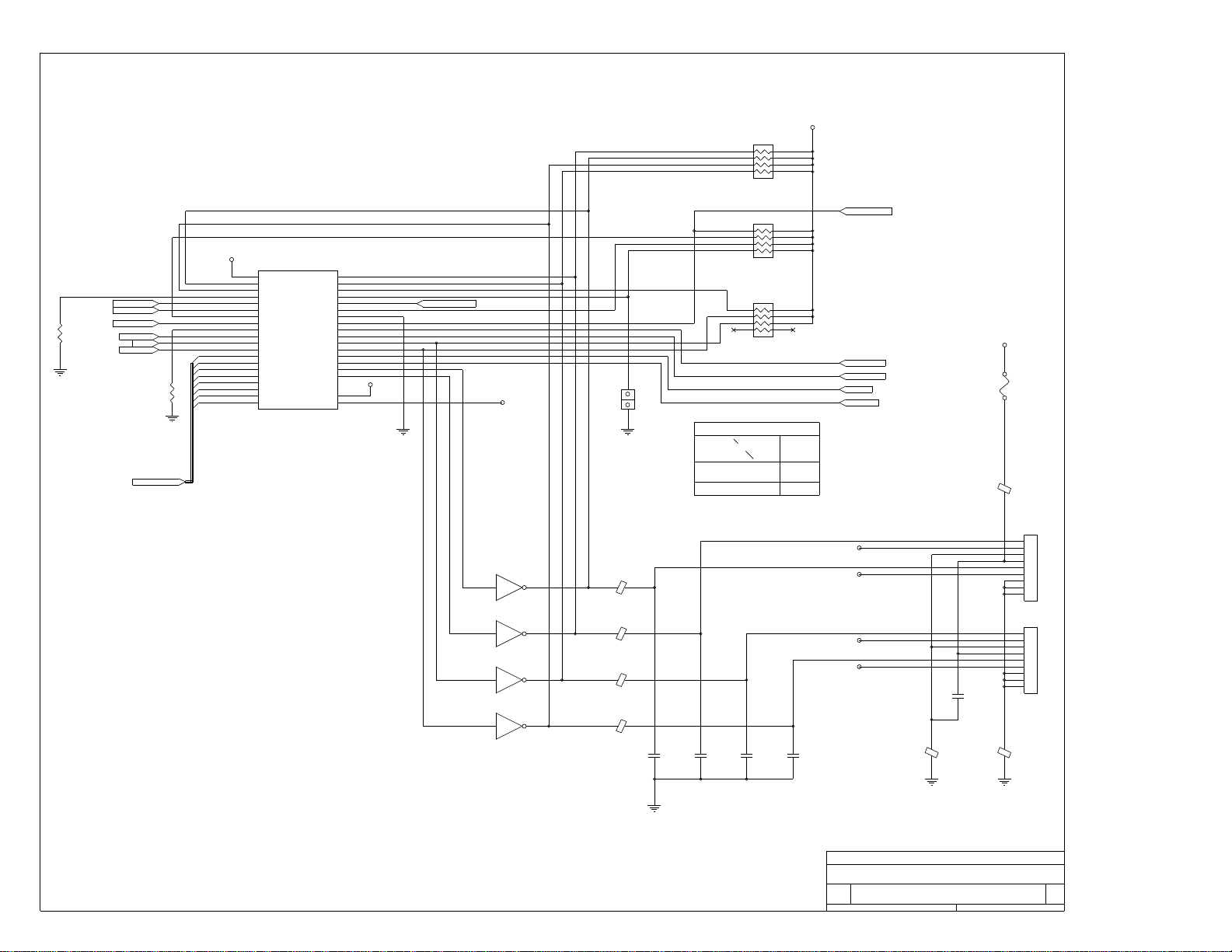

System ROM

Page 10

PWROK

17

PCLKPIIX3

3

PIIX3OSC

3

AD[0..31]

4,18,19

C/BE#[0..3]

4,18,19

4,18,19,21

4,18,19,21

4,18,19,21

220

4,18,19,21

R51

1 2

4,18,19,21

PIRQ#[0..3]

18,19,21

11,12,15,16,20,21

12,20,21

11,21

THIS DRAWING CONTAINS INFORMATION

WHICH HAS NOT BEEN VERIFIED FOR

MANUFACTURING AN END USER PRODUCT.

INTEL IS NOT RESPONSIBLE FOR THE

MISUSE OF THIS INFORMATION.

DDRQ[0..1]

11

IRQ[0..15]

DRQ[0..7]

DD[0..15]

DEVSEL#

4,18,19,21

12,20,21

20,21

20,21

2

17

FRAME#

PHLDA#

4

HFERR#

EXTSMI#

IOCS16#

IOCHK#

0WS#

C/BE#0

C/BE#1

C/BE#2

C/BE#3

TRDY#

IRDY#

STOP#

PXIDSELAD18

PIRQ#0

PIRQ#1

PIRQ#2

PIRQ#3

SERR#

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

IRQ1

IRQ3

IRQ4

IRQ5

IRQ6

IRQ7

IRQ8

IRQ9

IRQ10

IRQ11

IRQ12

IRQ14

IRQ15

DRQ0

DRQ1

DRQ2

DRQ3

DRQ5

DRQ6

DRQ7

DD0

DD1

DD2

DD3

DD4

DD5

DD6

DD7

DD8

DD9

DD10

DD11

DD12

DD13

DD14

DD15

DDRQ0

DDRQ1

126

132

136

206

205

204

203

202

201

200

199

197

194

193

192

191

190

189

188

177

176

175

174

173

172

171

168

166

165

164

163

162

161

160

159

198

187

178

167

179

181

180

185

154

184

149

150

151

152

3

110

4

58

56

34

33

32

5

10

73

75

77

83

81

120

125

87

30

12

25

91

95

99

71

6

15

55

50

49

48

47

46

45

44

43

41

40

39

38

37

36

35

108

111

U15

PWROK

PCICLK

OSC

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

C/BEOC/BE1C/BE2C/BE3-

FRAMETRDYIRDYSTOP-

IDSEL

DEVSELPIRQAPIRQBPIRQCPIRQDSERRPHLDA-

IRQ1

IRQ3

IRQ4

IRQ5

IRQ6

IRQ7

IRQ8IRQ9

IRQ10

IRQ11

IRQ12/M

IRQ14

IRQ15

FERREXTSMI-

DREQ0

DREQ1

DREQ2

DREQ3

DREQ5

DREQ6

DREQ7

IOCS16IOCHKZEROWS-

DD0/SA8

DD1/SA9

DD2/SA10

DD3/SA11

DD4/SA12

DD5/SA13

DD6/SA14

DD7/SA15

DD8/SA16

DD9/SA17

DD10/SA18

DD11/SA19

DD12/SBHEDD13

DD14/APICCSDD15/PCSDDRQ0

DDRQ1

PIIX3_0.2

PHOLDSYSCLK

LA17/DA0

LA18/DA1

LA19/DA2

LA20/CS3P

LA21/CS1P

LA22/CS3S

LA23/CS1S

USBP0USBP0+

USBP1USBP1+

USBCLK

MEMCS16-

SMEMW-

SMEMR-

IOCHRDY

VCC/VCC3

STPCLK-

IGNNEDACK0-

DACK1DACK2DACK3DACK5DACK6DACK7-

REFRESH-

RTCALE

BIOSCS-

RTCCSRSTDRV

DDAK0DDAK1-

PCIRST-/APICACKTESTIN-/APICREQ-

CPURST

BALE

MIRQ0

MEMW-

MEMR-

IORIOW-

SD10

SD11

SD12

SD13

SD14

SD15

INTR

SMI-

SPKR

XDIR-

XOE-

KBCS-

IORDY

DIORDIOW-

SOESDIR

INIT

SA[8..19]

U14

2

3

4

5

6

7

8

9

19

1

2

3

4

5

6

7

8

9

19

1

DDSAPU1

SYSCLKR

Title

Size Document Number REV

Date: June 19, 1997 Sheet 10 of 24

18

B1

17

B2

16

B3

15

B4

14

B5

13

B6

12

B7

11

B8

18

B1

17

B2

16

B3

15

B4

14

B5

13

B6

12

B7

11

B8

4 5

3 6

2 7

1 8

CLOSE = CLK/4

OPEN = CLK/3

SA8

SA15

SA14

SA13

SA12

SA11

SA10

SA9

SA16

SA17

SA18

SA19

DDSAPU2

DDSAPU3

DDSAPU4

1 2

11,15

20

INTEL CORP.

SBHE#

20,21

R50

SYSCLK

22

PIIX3

20

A1

A2

A3

A4

A5

A6

A7

A8

G

DIR

74ALS245

U17

A1

A2

A3

A4

A5

A6

A7

A8

G

DIR

74ALS245

RP57

10K

RP59

10K

U27E

7407S

J28

1

2

JP2

RSTDRV#

RSTISA

B 82430HX B.1

9,20,21

20,21

16,20,21

16,20,21

PWROK

1

9,10,12,15,20,21

DD0

DD7

DD6

DD5

DD4

DD3

DD2

DD1

DD14

DD15

DD8

DD9

DD10

DD11

DD12

VCC

VCC

1 8

2 7

3 6

4 5

11 10

U2A

2

74HCT14S

R32

22

R44

22

R33

22

R46

1 2

22

R42

22

R40

22

CPUVIO

VCC

RSTDRV

U11D

12

13

74ALS08S

4.7K

R43

1 2

DD[0..15]

SOE#

SDIR

1 2

1 2

SMEMW#

1 2

MEMR#

SMEMR#

1 2

IOR#

1 2

IOW#

DIVCLK

21

12

VCC

11

186

PAR

109

153

64

20

AEN

86

84

82

80

76

74

72

69

SA0

68

SA1

67

SA2

66

SA3

63

SA4

61

SA5

59

SA6

57

SA7

145

144

143

142

146

147

70

90

22

88

19

18

23

24

17

SD0

16

SD1

14

SD2

13

SD3

11

SD4

9

SD5

8

SD6

7

SD7

92

SD8

94

SD9

96

98

100

101

102

107

130

122

123

124

135

NMI

121

85

29

60

21

89

93

97

62

TC

31

117

141

140

148

137

138

139

28

114

113

112

115

116

119

118

127

128

134

129

SYSCLKR

BALER

AENR

LA17

LA18

LA19

LA20

LA21

LA22

LA23

SA0

SA1

SA2

SA3

SA4

SA5

SA6

SA7

USBP0USBP0+

USBP1USBP1+

MEMWR#

SMEMWR#

MEMRR#

SMEMRR#

IORR#

IOWR#

SD0

SD1

SD2

SD3

SD4

SD5

SD6

SD7

SD8

SD9

SD10

SD11

SD12

SD13

SD14

SD15

PBFVCC

DACK#0

DACK#1

DACK#2

DACK#3

DACK#5

DACK#6

DACK#7

T/CR

REFRESH#

SPKR

XDIR#

XOE#

RTCALE

ROMCS#

RTCCS#

ROM_KB#

ICHRDY

IIOR#R

IIOW#R

DDAK0

DDAK1

SDIR

TESTIN#

PAR

PHOLD#

MEMCS16#

IOCHRDY

SD[0..15]

HINTR

HSMI#

HSTPCLK#

HNMI

HIGNNE#

17

9,16

SOE#

HRESET

PCIRST#

PIIX3INIT

R34 22

LA[17..23]

SA[0..7]

13

13

13

13

MIRQ0

2

20,21

16

16

9

16

15

11

11

11

11

11

11

4,18,19,21

4

1 2

BALE

20,21

R45

1 2

AEN

22

VCC

2

R48

10K

1

USBCLK MEMW#

11,21

20,21 20,21

12,20,21

2

2

2

2

DACK#[0..7]

R3522

1 2

2

4..6,18,19

12,20

11,20,21

9,10,12,15,20,21

INSTALL FOR PIIX

3 9,20,21

12,16,20,21

R53

1 2

0

INSTALL FOR PIIX3

R39

1 2

0

INSTALL FOR PIIX

12,20

T/C

12,20

VCC

4

Page 11

DD[0..15]

10,21

DDAK1

10

DDRQ1

10,11

DDRQ0

10,11

RSTDRV#

10,15

R31

5.6K

10,12,15,16,20,21

IIOW#R

10

IIOR#R

10

LA[17..23]

10,20,21

SOE#

10

MIRQ0

10,21

THIS DRAWING CONTAINS INFORMATION

WHICH HAS NOT BEEN VERIFIED FOR

MANUFACTURING AN END USER PRODUCT.

INTEL IS NOT RESPONSIBLE FOR THE

MISUSE OF THIS INFORMATION.

2

1

10

10

LA21

LA20

LA17

LA18

LA19

LA23

LA22

2

1

ICHRDY

DDAK0

IRQ14

1 2

1 2

1 2

1 8

2 7

3 6

4 5

R30

5.6K

R28

1 2

47

R47

47

R29

47

R49

47

12

13

9

10

4

5

1

2

9

10

4

5

1

2

RP37

33

IIOWA#

IIOWB#

IIORA#

IIORB#

U12D

74ALS00S

U12C

74ALS00S

U11B

74ALS08S

U11A

74ALS08S

U11C

74ALS08S

U12B

74ALS00S

U12A

74ALS00S

SDDAK1

SDDRQ1

DRQ0R

IRSTA#

11

8

6

3

8

6

3

CS1P#

CS3P#

DA0

DA1

DA2

CS1S#

CS3S#

RP49

1.0K

RP32

33

RP62

33