Page 1

Intel® 41210 Serial to Parallel PCI Bridge

Design Guide

May 2005

Order Number: 278801-004

Page 2

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY

ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN

INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUM ES NO LIABILITY WHATSOEVER, AND INTEL DISCLAI MS

ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES

RELATING T O FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER

INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining applications.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling

1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Intel is a trademark or registered trademark of Intel Corporation or its subsidiaries in the United States and other countries.

*Other names and brands may be claimed as the property of others.

Copyright © Intel Corporation, 2005

ii Intel® 41210 Serial to Parallel PCI Bridge Design Guide

Page 3

Contents

Contents

1 About This Document ...................................................................................................................7

1.1 Terminology and Definitions .................................................................................................7

2 Introduction....................................................................................................................................9

2.1 PCI Express Interface Features............................................................................................9

2.2 PCI-X Interface Features......................................................................................................9

2.3 Power Management............................................................................................................10

2.4 SMBus Interface .................................................................................................................10

2.4.1 SMBus for configuration register initialization........................................................10

2.4.2 Microcontroller Connections to the 41210 Bridge..................................................11

2.5 JTAG...................................................................................................................................12

2.6 Related Documents ............................................................................................................12

2.7 Intel

3 Package Information ...................................................................................................................15

3.1 Package Specification ........................................................................................................15

4 Power Plane Layout ....................................................................................................................19

4.1 41210 Bridge Decoupling Guidelines .................................................................................19

4.2 Split Voltage Planes............................................................................................................21

®

41210 Serial to Parallel PCI Bridge Applications......................................................13

5 41210 Bridge Reset and Power Timing Considerations ..........................................................23

5.1 A_RST#,B_RST# and PERST# Timing Requirements ......................................................23

5.2 VCC15 and VCC33 Voltage Requirements........................................................................23

6 General Routing Guidelines .......................................................................................................25

6.1 General Routing Guidelines................................................................................................25

6.2 Crosstalk.............................................................................................................................25

6.3 EMI Considerations ............................................................................................................26

6.4 Power Distribution and Decoupling.....................................................................................27

6.4.1 Decoupling.............................................................................................................27

6.5 Trace Impedance................................................................................................................27

6.5.1 Differential Impedance...........................................................................................28

7 Board Layout Guidelines............................................................................................................29

7.1 Adapter Card Topology.. ....... ...... ....... ...... ....... ...... ...... ....... ...... ....... ....................................29

8 PCI-X Layout Guidelines.............................................................................................................31

8.1 Interrupts.............................................................................................................................31

8.1.1 Interrupt Routing for Devices Behind a Bridge.......................................................32

8.2 PCI Arbitration ....................................................................................................................32

8.2.1 PCI Resistor Compensation ..................................................................................33

8.3 PCI General Layout Guidelines ..........................................................................................33

8.3.1 PCI Pullup Resistors Not Required........................................................................34

8.4 PCI Clock Layout Guidelines ..............................................................................................35

8.5 PCI-X Topology Layout Guidelines.....................................................................................38

8.6 Intel

®

41210 Serial to Parallel PCI Bridge Design Guide Layout Analysis .........................38

Intel® 41210 Serial to Parallel PCI Bridge Design Guide iii

Page 4

Contents

8.6.1 Embedded PCI-X 133 MHz ...................................................................................39

8.6.2 Embedded PCI-X 100 MHz ...................................................................................40

8.6.3 PCI-X 66 MHz Embedded Topology......................................................................41

8.6.4 PCI 66 MHz Embedded Topology.........................................................................42

8.6.5 PCI 33 MHz Embedded Mode Topology...............................................................43

9 PCI Express Layout.....................................................................................................................45

9.1 General recommendations ................................ ...... ...... ....... ...... ....... ...... ....... ...... ..............45

9.2 PCI-Express Layout Guidelines..........................................................................................46

9.3 Adapter Card Layout Guidelines.........................................................................................46

10 Circuit Implementations..............................................................................................................49

10.1 41210 Bridge Analog Voltage Filters..................................................................................49

10.1.1 PCI Analog Voltage Filters.....................................................................................50

10.1.2 PCI Express Analog Voltage Filter ........................................................................50

10.1.3 Bandgap Analog Voltage Filter..............................................................................51

10.2 Intel® 41210 Serial to Parallel PCI Bridge Reference and Compensation Pins.................53

10.2.1 SM Bus..................................................................................................................54

11 41210 Bridge Customer Reference Boards...............................................................................55

11.1 Board Stack-up..................................................................... ...... ....... ...... ....... ...... ....... .......55

11.2 Material...............................................................................................................................56

11.3 Impedance..........................................................................................................................56

11.4 Board Outline.................... ....... ...... ....... ...... ....... ...... ...... ....... ...... ........................................57

12 Design Guide Checklist ..............................................................................................................59

Figures

1 41210 Bridge Microcontroller Block Diagram .............................................................................11

2 41210 Bridge Microcontroller Connections.................................................................................11

3 41210 Bridge Block Diagram......................................................................................................12

4Intel

5 Top View - 41210 Bridge 567-Ball FCBGA Package Dimensions..............................................15

6 Bottom View - 41210 Bridge 567-Ball FCBGA Package Dimensions ........................................16

7 Side View - 41210 Bridge 567-Ball FCBGA Package Dimensions.............................................17

8 Decoupling Placement for Core and PCI Express Voltage Planes ............................................19

9 Decoupling Placement for PCI/PCI-X 1.5V and 3.3V Voltage Planes........................................20

10 41210 Bridge Single-Layer Split Voltage Plane..........................................................................22

11 Crosstalk Effects on Trace Distance and Height........................................................................26

12 PCB Ground Layout Around Connectors ...................................................................................26

13 Cross Section of Differential Trace.............................................................................................28

14 Two-by-two Differential Impedance Matrix .................................................................................28

15 Adapter Card Stackup .............. ....... ...... ....... ...... ....... ...... ...... ....... ...... ....... ...... ...........................30

16 PCI RCOMP ...............................................................................................................................33

17 PCI Clock Distribution and Matching Requirements...................................................................36

18 Embedded PCI-X 133 MHz Topology ........................................................................................39

19 Embedded PCI-X 100 MHz Topology ........................................................................................40

20 PCI-X 66 MHz Embedded Routing Topology.............................................................................41

21 PCI 66 MHz Embedded Topology..............................................................................................42

®

41210 Bridge Adapter Card Block Diagram......................................................................13

iv Intel® 41210 Serial to Parallel PCI Bridge Design Guide

Page 5

Contents

22 PCI 33 MHz Embedded Mode Routing Topology.......................................................................43

23 PCI Analog Voltage Filter Circuit................................................................................................50

24 PCI Express Analog Voltage Filter Circuit ..................................................................................51

25 Bandgap Analog Voltage Filter Circuit........................................................................................52

26 Reference and Compensation Circuit Implementations .............................................................53

27 Proposed Mechanical Outline of the 41210 Bridge ....................................................................57

Tables

1 Terminology and Definitions.........................................................................................................7

2 41210 Bridge Decoupling Guidelines .........................................................................................21

3 Adapter Card Stack Up, Microstrip and Stripline ........................................................................29

4 INTx Routing Table.....................................................................................................................31

5 Interrupt Binding for Devices Behind a Bridge...........................................................................32

6 PCI-X Signals .............................................................................................................................34

7 PCI/PCI-X Frequency/Mode Straps............................................................................................34

8 PCI-X Clock Layout Requirements Summary.............................................................................37

9 PCI-X Slot Guidelines.................................................................................................................38

10 Embedded PCI-X 133 MHz Routing Recommendations............................................................39

11 Embedded PCI-X 100 MHz Routing Recommendations............................................................40

12 PCI-X 66 MHz Embedded Routing Recommendations..............................................................41

13 PCI 66 MHz Embedded Table....................................................................................................42

14 PCI 33 MHz Embedded Routing Recommendations..................................................................43

15 Adapter Card Routing Recommendations..................................................................................46

16 Recommended R, L and C Values for 41210 Bridge Analog Filter Circuits ...............................49

17 SMBUs Address Configuration...................................................................................................54

18 CRB Board Stackup....................................................................................................................56

19 PCI Express Interface Signals....................................................................................................59

20 PCI/PCI-X Interface Signals .......................................................................................................60

21 Miscellaneous Signals ................................................................................................................62

22 SMBus Interface Signals ............................................................................................................62

23 Power and Ground Signals.........................................................................................................63

24 JTAG Signals......................... ....... ...... ....... ...... ....................................... ...... ....... ...... .................64

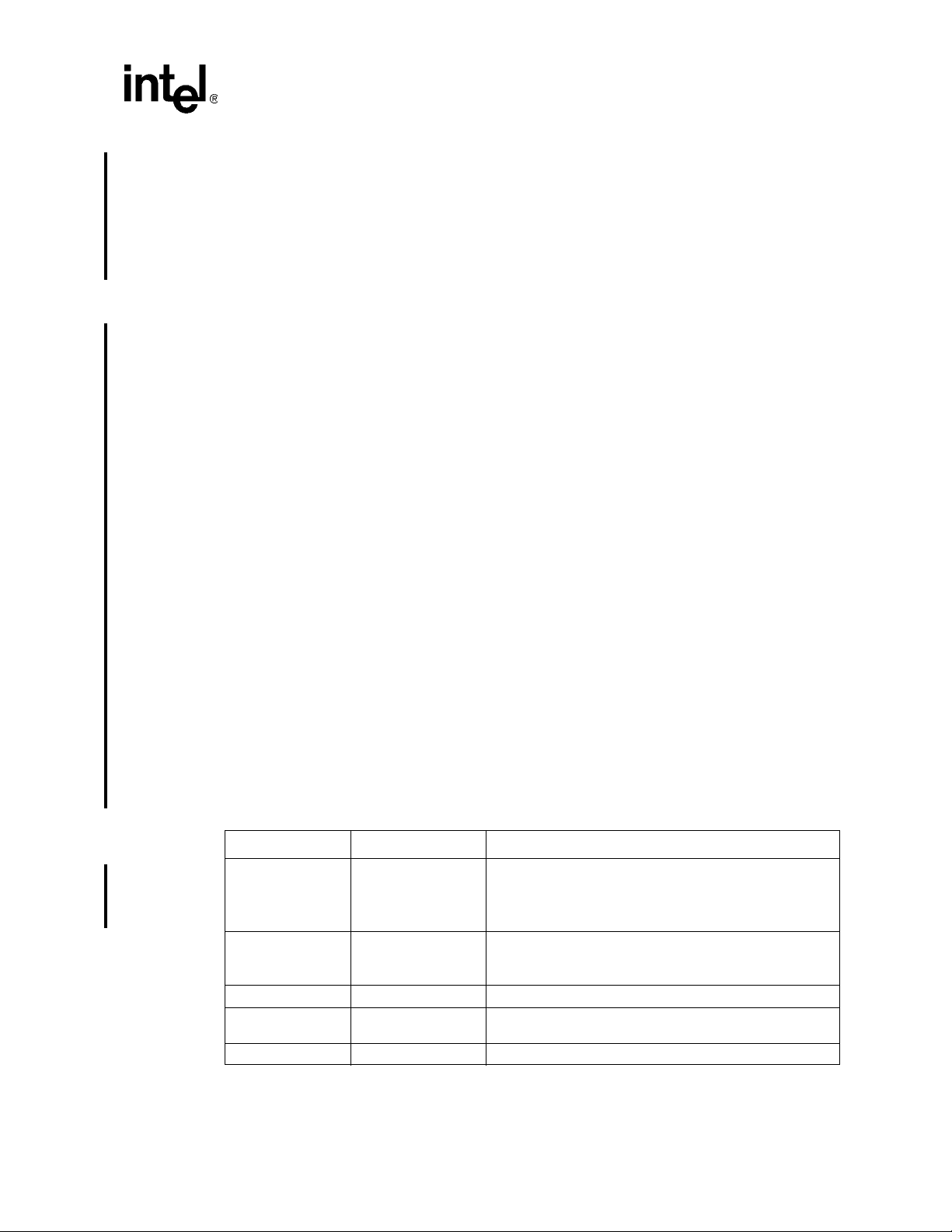

Revision History

Date Revision Description

Removed Section 5.3, VCCPE and REFCLKn/REFCLKp

May 2005 004

October 2004 003

July 2004 002 Updated Chapters 4, 5, and 12

October 2003 001

July 2003 000 First internal draft of this document.

Intel® 41210 Serial to Parallel PCI Bridge Design Guide v

Information

Added signals to Section 8.3.1

Updated Table 19, Table 20, and Table 21

Updated PCI Express operation information in Section 2.1 and

Table 19.

Added signal NC17 information in Table 21.

Updated content; second draft of this document; initial public

release of this document.

Page 6

Contents

This page intentionally left blank.

vi Intel® 41210 Serial to Parallel PCI Bridge Design Guide

Page 7

About This Document 1

This document provides layout i nformation and guide lines for designing p latform or add-in board

applications with the Intel

®

41210 Serial to Parall el PCI Br idge (also c alled the 41 210 Bridge). I t is

recommended that this document be used as a guideline. Intel r ecommen ds emp l oyi ng b est -k now n

design practices with board level simulation, signal integrity testing and validation for a robust

design.

Designers should note that this guide focuses upon specific design considerations for the 41210

Bridge and is not intended to be an all-inclusive list of all good design practices. Use this guide as

a starting point and use empirical data to optimize your particular design.

1.1 Terminology and Definitions

Table 1 provides a list of terms and definitions that may be useful when working with the 41210

Bridge product.

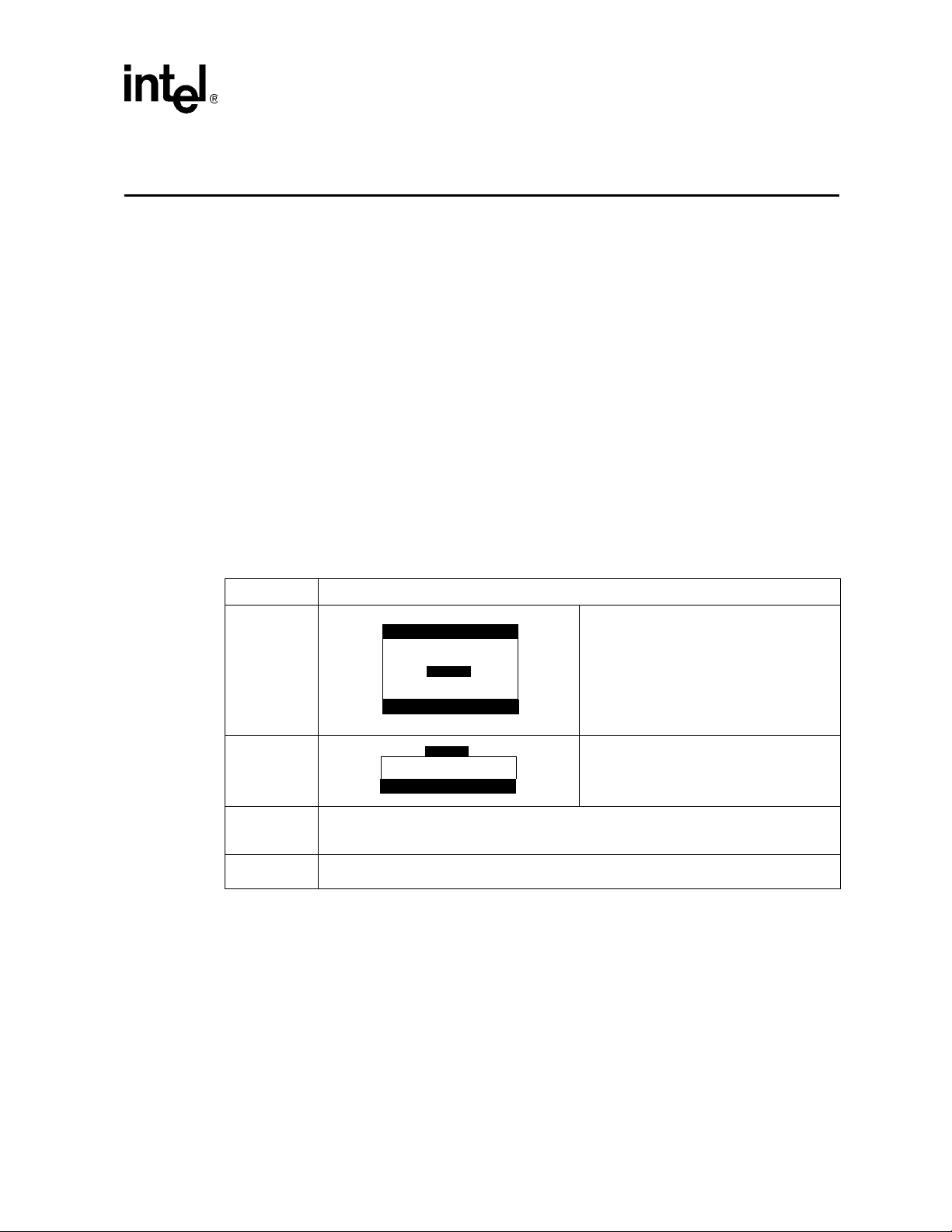

Table 1. Terminology and Definitions (Sheet 1 of 2)

Term Definition

Stripline

Stripline in a PCB is composed of the

conductor inserted in a dielectric with GND

planes to the top and bottom.

NOTE: An easy way to distinguish stripline

from microstrip is that you need to

strip away layers of the board to view

the trace on stripline.

Microstrip

Prepreg

Core

Intel® 41210 Serial to Parallel PCI Bridge Design Guide 7

Material used for the lamination process of manufacturing PCBs. It consists of a layer of

epoxy material that is placed between two cores. This layer melts into epoxy when heated and

forms around adjacent traces.

Material used for the lamination process of manufacturing PCBs. This material is two sided

laminate with copper on each side. The core is an internal layer that is etched.

Microstrip in a PCB is composed of the

conductor on the top layer above the dielectric

with a ground plane below

Page 8

About This Document

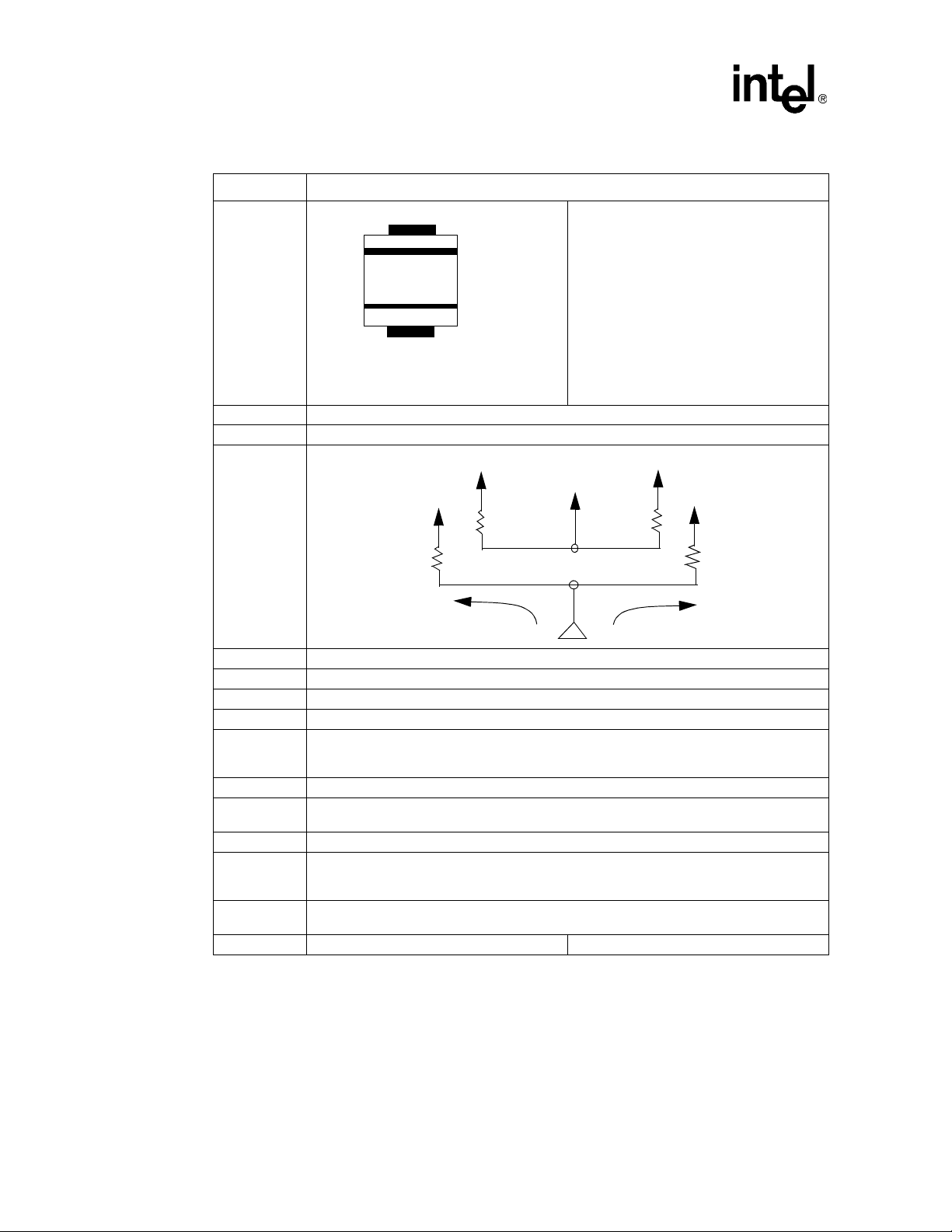

Table 1. Terminology and Definitions (Sheet 2 of 2)

Term Definition

Layer 1: copper

Prepreg

Layer 2: GND

Core

PCB

Example of a Four-Layer Stack

SSTL_2 Series Stub Terminated Logic for 2.5 V

JEDEC Provides standards for the semiconductor industry.

A network that transmits a coupled signal to another network is aggressor network.

Aggressor

Victim A network that receives a coupled cross-talk signal from another network is a victim network.

Network The trace of a PCB that completes an electrical connection between two or more components.

Stub Branch from a trunk terminating at the pad of an agent.

CRB Customer Reference Board

Downstream

Upstream

Local memory

DWORD 32-bit data word.

Flip Chip

Mode

Conversion

PCI-E PCI-Express

Downstream refers either to the relative position of an interconnect/system element (Link/

device) as something that is farther from the Root Complex, or to a direction of information

flow, i.e., when information is flowing away from the Root Complex.

Memory subsystem on the Intel XScale

busses.

FC-BGA (flip chip-ball grid array) chip packages are designed with processor core flipped up

on the back of the chip, facing away from the PCB. This allows more efficient cooling of the

package.

Mode Conversions are due to imperfections on the interconnect which transform differential

mode voltage to common mode voltage and common mode voltage to differential voltage.

Zo

Layer 3: VCC15

Prepreg

Layer 4: copper

Zo

Victim Network

Aggressor Network

Printed circuit board.

Example manufacturing process consists of

the following steps:

• Consists of alternating layers of core and

prepreg stacked

• The finished PCB is heated and cured.

• The via holes are drilled

• Plating covers holes and outer surfaces

• Etching removes unwanted copper

• Board is tinned, coated with solder mask

and silk screened

Zo

Zo

®

core DDR SDRAM or Peripheral Bus Interface

8 Intel® 41210 Serial to Parallel PCI Bridge Design Guide

Page 9

Introduction 2

The Intel®41210 Serial to Parallel PCI Bridge integrates two PCI Express-to-PCI bridges. Each

bridge follows the PCI-to-PCI Bridge programming model. The PCI Express port is compliant to

the PCI Express Specification, Revision 1.0. The two PCI bus interfaces are fully compliant to the

PCI Local Bus Specification, Revision 2.3.

2.1 PCI Express Interface Features

• PCI Express Specification, Revision 1.0b compliant.

• Support for single x8, single x4 or single x1 PCI Express operation.

• 64-bit addressing support.

• 32-bit CRC (cyclic redundancy checking) covering all transmitted data packets.

• 16-bit CRC on all link message information.

• Raw bit-rate on the data pins of 2.5 Gbit/s, resulting in a raw bandwidth per pin of 250 MB/s.

• Maximum realized bandwidth on PCI Express interface is 2 GB/s (in x8 mode) in each

direction simultaneously, for an aggregate of 4 GB/s .

2.2 PCI-X Interface Features

• PCI Local Bus Specification, Revision 2.3 compliant.

• PCI-to-PCI Bridge Specification, Revision 1.1 compliant.

• PCI-X Addendum to the PCI Local Bus Specification, Revision 1.0a compliant.

• 64-bit 66 MHz, 3.3 V, NOT 5 V tolerant.

• On Die Termination (ODT) with 8.2KΩ pull-up to 3.3V for PCI signals.

• Six external REQ/GNT Pairs for internal arbiter on segment A and B respectively.

• Programmable bus parking on either the last agent or always on Lanai.

• 2-level programmable round-robin internal arbiter with Multi-Transaction Timer (MTT)

• External PCI clock-feed support for asynchronous primary and secondary domain operation.

• 64-bit addressing for upstream and downstream transactions

• Downstream LOCK# support.

• No upstream LOCK# support.

• PCI fast Back-to-Back capable as target.

• Up to four active and four pending upstream memory read transactions

• Up to two downstream delayed (memory read, I/O read/write and configuration read/write)

transaction.

Intel® 41210 Serial to Parallel PCI Bridge Design Guide 9

Page 10

Introduction

• Tunable inbound read prefetch algorithm for PCI MRM/MRL commands

• Local initialization via SMBus

• Secondary side initialization via Type 0 configuration cycles.

2.3 Power Management

• Support for PCI Express Active State Power Management (ASPM) L0s link state

• Support for PCI PM 1.1 compatible D0, D3hot and D3cold device power states

• Support for PME# event propagation on behalf of PCI devices

2.4 SMBus Interface

• Compatible with System Management Bus Specification, Revision 2.0

• Slave mode operation only.

• Full read/write access to all configuration registers

2.4.1 SMBus for configuration register initialization

• Support for local initialization of the configuration registers can be implemented using a

microcontroller via SMB. Figure 1shows this SMBus and the data transfer that occurs between

the 41210 Bridge and the microcontroller.

• Configuration Register information is stored internally in a microcontroller and the

information is transferred to the product via System Managed Bus (SMBus) protocols when

the device receives power or reset.

• The requirements of the microcontroller are as follows:

2

— Supports I

— Has at least 256 Byte of internal EEprom space

— To facilitate this programming on the Customer Reference Board a Microchip part

PIC16F876A was used.

— Code space: estimated code size is ~2K words of program space and 32 words of RAM

C and SMBus Prot ocols

10 Intel® 41210 Serial to Parallel PCI Bridge Design Guide

Page 11

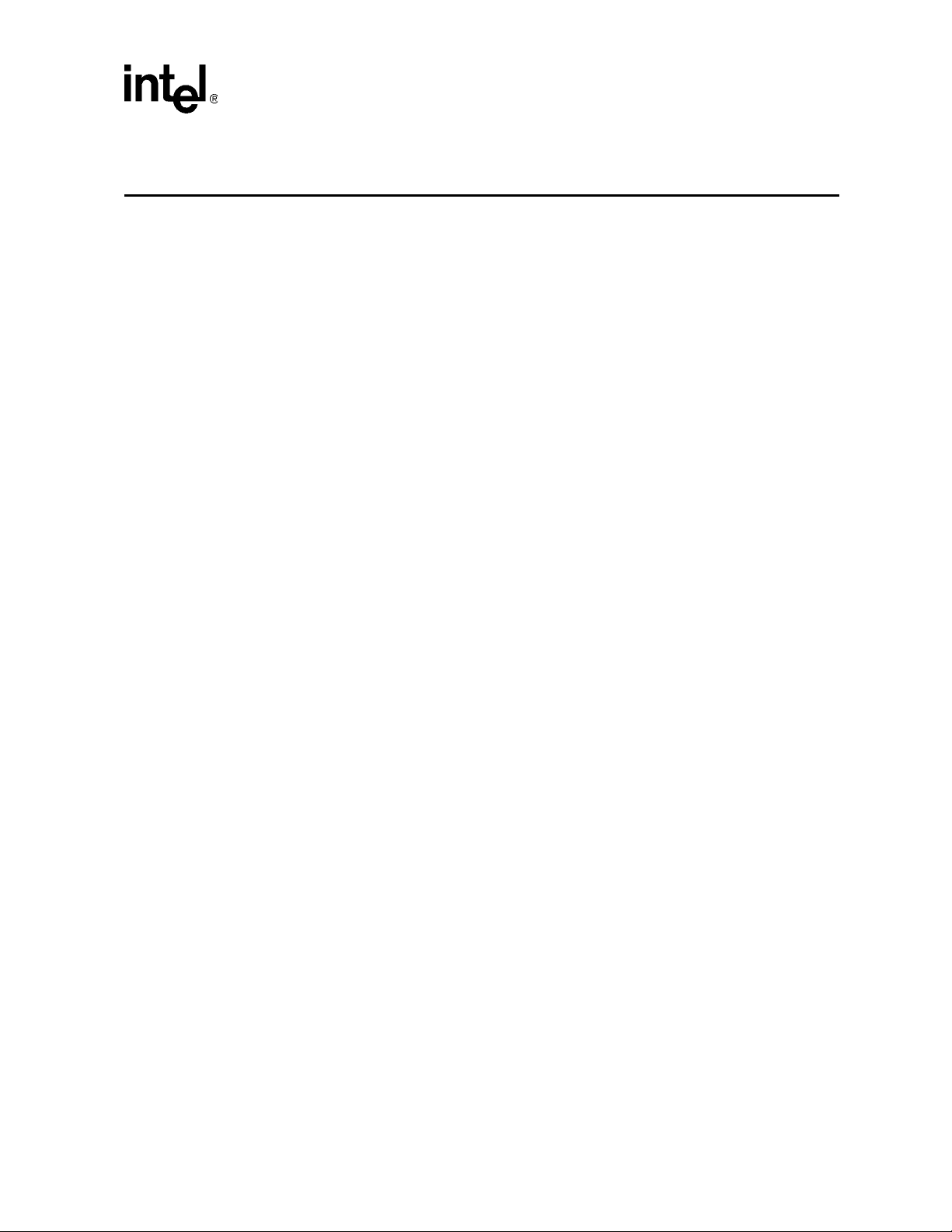

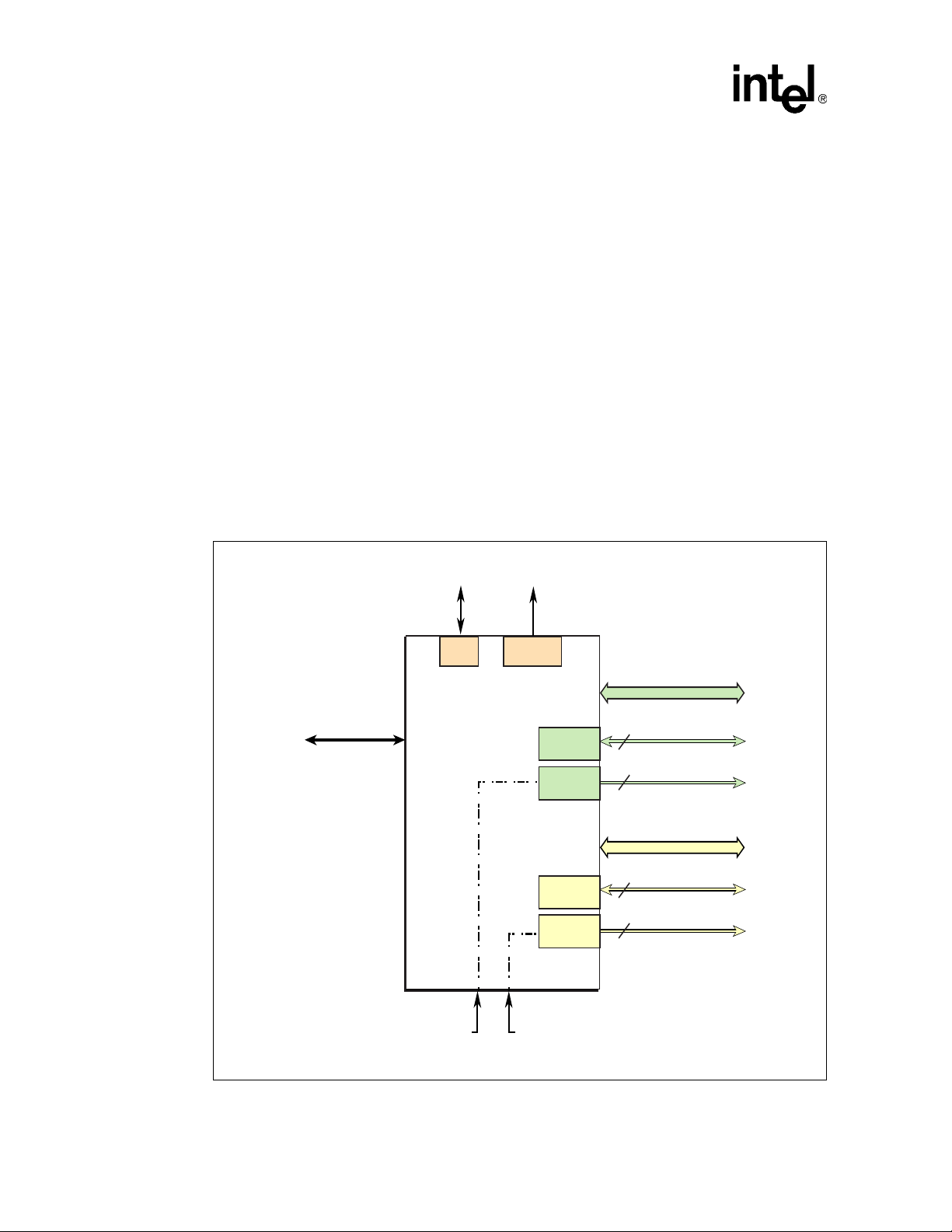

Figure 1. 41210 Bridge Microcontroller Block Diagram

SMBus 2.0

Introduction

Microcontroller

Configuration

Register

Data

Intelfi 41210 Bridge

Configuration

Register

Address Space

2.4.2 Microcontroller Connections to the 41210 Bridge

The following diagram shows the SMB interface from the 41210 Bridge to the microcontroller.

Figure 2. 41210 Bridge Microcontroller Connections

3.3 V

B2707-01

SDI / SDA

SCK / SCL

RC1

RBO / INT

PIC16F876A

OSC2 / CLKOUT

20 MHz

OSC1 / CLKIN

22 pF 22 pF

B2708-01

Intelfi 41210

Bridge

CFGRETRY

CFG_RST_N

SMBDAT

SMBCLK

SMDAT

SMCLK

CFG_RETRY

CFG_RESET

Intel® 41210 Serial to Parallel PCI Bridge Design Guide 11

Page 12

Introduction

2.5 JTAG

• Compliant with IEEE Standard Test Access Port and Boundary Scan Architecture 1149.1a

2.6 Related Documents

• Intel® 41210 Serial to Parallel PCI Bridge Design Specification (EDS), Revision 1.0.

• PCI Express Specification, Revision 1.0, from www.pci-sig.com.

• PCI Express Design Guide, Revision 0.5

• PCI Local Bus Specification, Revision 2.3, from www.pci-sig.com.

• PCI-X Addendum to the PCI Local Bus Specification, Revision 1.0a, from www.pci-sig.com.

• IEEE Standard Test Access Port and Boundary Scan Architecture 1149.1a

• System Management Bus Specification, Revision 2.0

Figure 3. 41210 Bridge Block Diagram

PCI-Express x8

JTAG SMB Bus

fi

Intel

41210 Bridge

B_PCLKIA_PCLKI

A

Bus Arbiter

A

Clock Buffer

B

Bus Arbiter

B

Clock Buffer

A Bus PCI-X 133MHz

6 REQ/GNT Pairs

6 A_PCLKO

B Bus PCI-X 133MHz

6 REQ/GNT Pairs

6 B_PCLKO

B2709-01

12 Intel® 41210 Serial to Parallel PCI Bridge Design Guide

Page 13

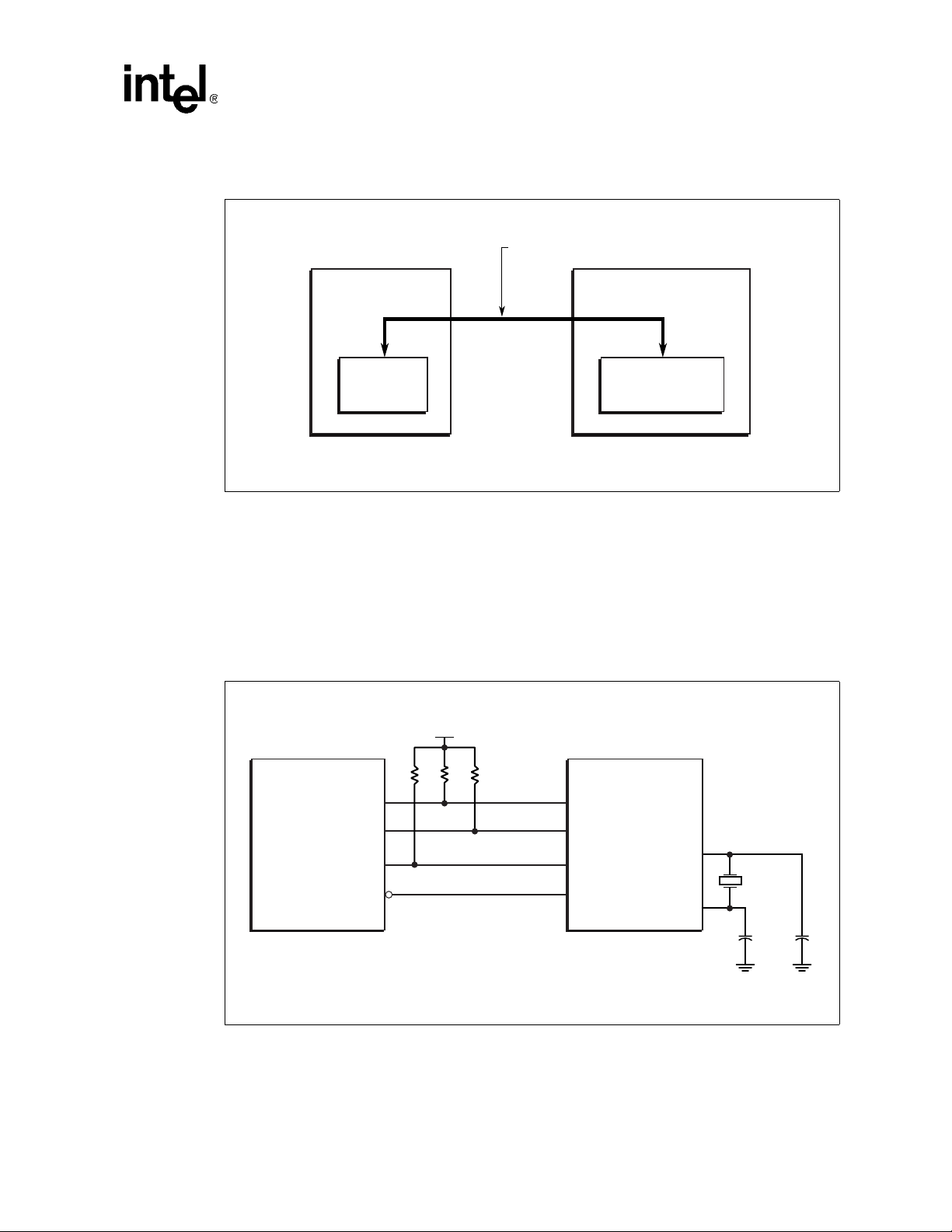

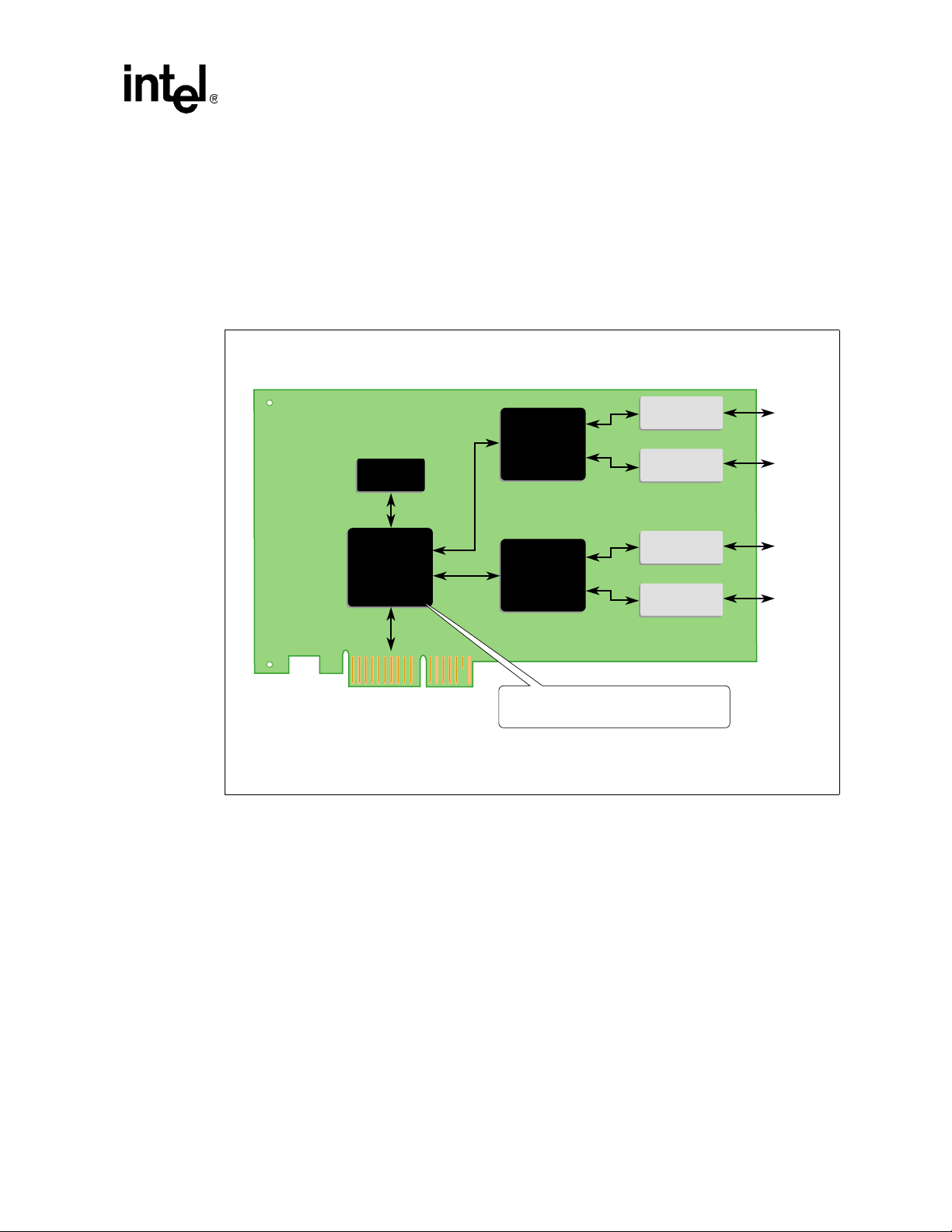

2.7 Intel®41210 Serial to Parallel PCI Bridge Applications

This section provides a block diagram for a typical the 41210 Bridge application. This application

shows a PCI-E adapter card with two Dual 2Gb Fibre Channel controllers. Each of the PCI-X bus

segments is connected to the Dual 2Gb Fibre Channel chip running at 133MHz. The two Dual FC

chips provides the four 2Gb/s outputs.

Figure 4. Intel

®

41210 Bridge Adapter Card Block Diagram

Introduction

I2C Micro

Controller

®

41210

Intel

Bridge

PCI-X to

PCI Express

PCI Express

(to Server)

SFP Optical

Dual 2Gb

FC

133 MHz

PCI-X

Dual 2Gb

FC

This is locally configurable from SMBus or

PCI-X interfaces (no BIOS support or Drivers

required)

SFP Optical

SFP Optical

SFP Optical

Module

Module

Module

Module

2 Gb/s

2 Gb/s

2 Gb/s

2 Gb/s

B1491-02

Intel® 41210 Serial to Parallel PCI Bridge Design Guide 13

Page 14

Introduction

This page intentionally left blank.

14 Intel® 41210 Serial to Parallel PCI Bridge Design Guide

Page 15

Package Information 3

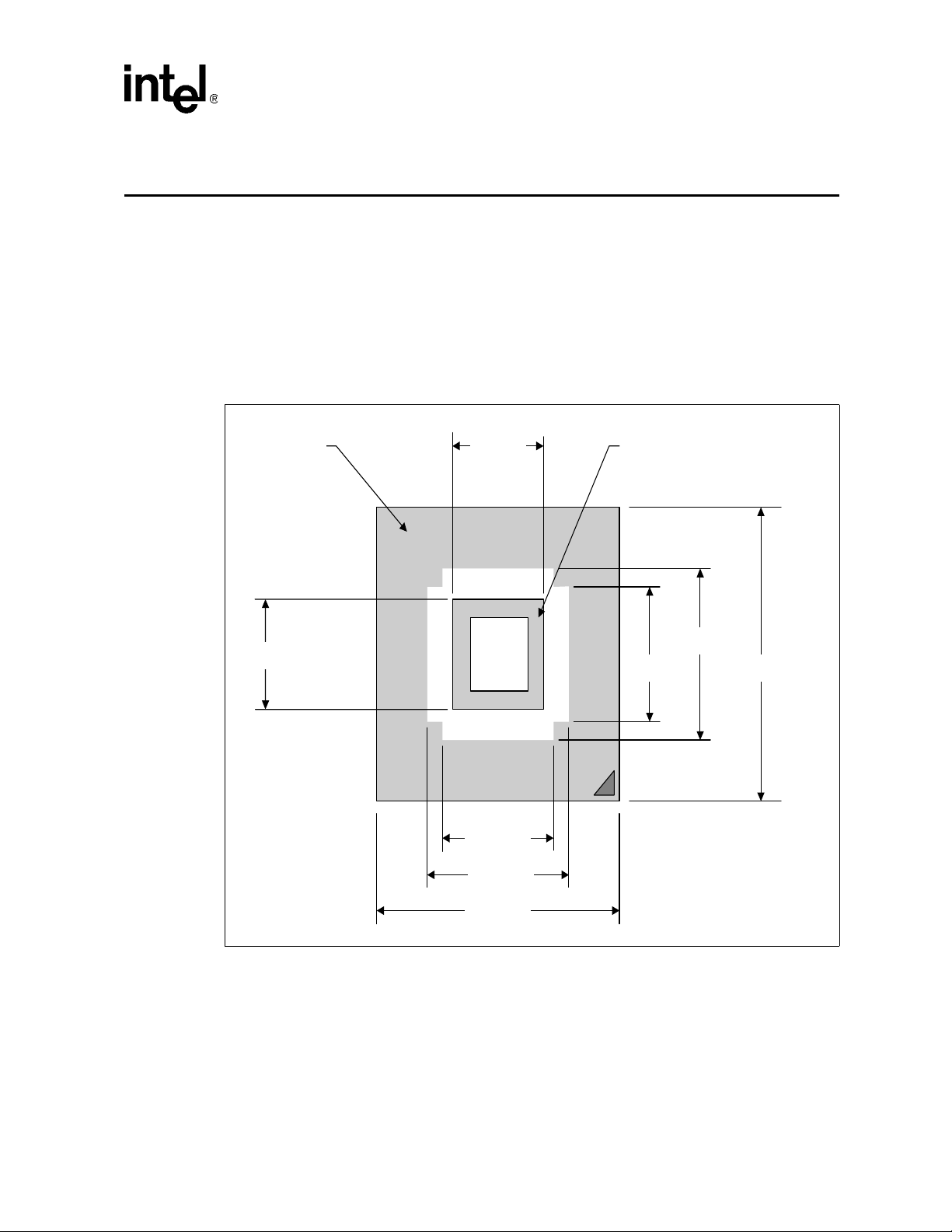

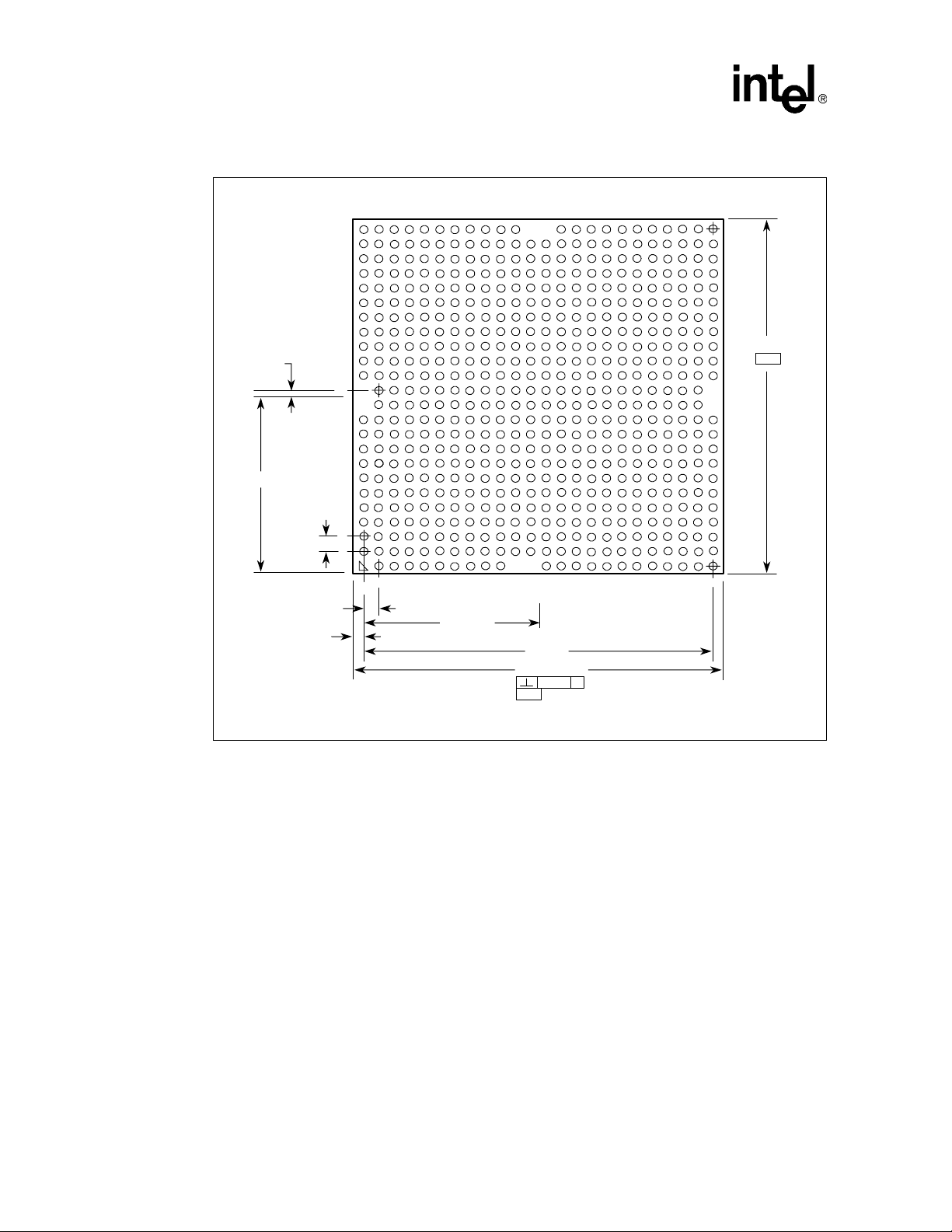

3.1 Package Specification

The 41210 Bridge is in a 567-ball FCBGA package, 31mm X 31mm in size, with a 1.27mm ball

pitch.

Figure 5. Top View - 41210 Bridge 567-Ball FCBGA Package Dimensions

Han d lin g

Exclusion

Area

0.550 in.

0.550 in.

17.00 mm

21.00 mm

Die Area

17.00 mm

21.00 mm

31.00 mm

31.00 mm

Pkg_567-Ball_Top

Intel® 41210 Serial to Parallel PCI Bridge Design Guide 15

Page 16

Package Information

Figure 6. Bottom View - 41210 Bridge 567-Ball FCBGA Package Dimensions

AD

AC

AB

AA

Y

W

V

U

T

4X 0.635

4X 15.500

23X 1.270

R

P

N

M

L

K

J

H

G

F

E

D

C

B

+

+

A

4681012 1618202224214

3 5 7 9 11 13 15 211 231917

23X 1.270

8X 14.605

(0.895)

29.2100

31.00 – 0.100

A

0.200

-B-

31.00 – 0.100

-A-

B2711-01

16 Intel® 41210 Serial to Parallel PCI Bridge Design Guide

Page 17

Figure 7. Side View - 41210 Bridge 567-Ball FCBGA Package Dimensions

Detail J

Underfill

Epoxy

Scale 5:1

FC BGA Substrate

Die

H

Detail H

Scale 5:1

1.170 – 0.085

0.600 – 0.100

J

Package Information

0.74 – 0.025

0.100 – 0.025

Die Solder

Bumps

1.940 – 0.150

BGA Solder Balls

B2712-01

Intel® 41210 Serial to Parallel PCI Bridge Design Guide 17

Page 18

Package Information

This page intentionally left blank.

18 Intel® 41210 Serial to Parallel PCI Bridge Design Guide

Page 19

Power Plane Layout 4

This chapter provides detail s on the decoupling and voltage plan es needed to b ias the 41210 Br idge

package.

4.1 41210 Bridge Decoupling Guidelines

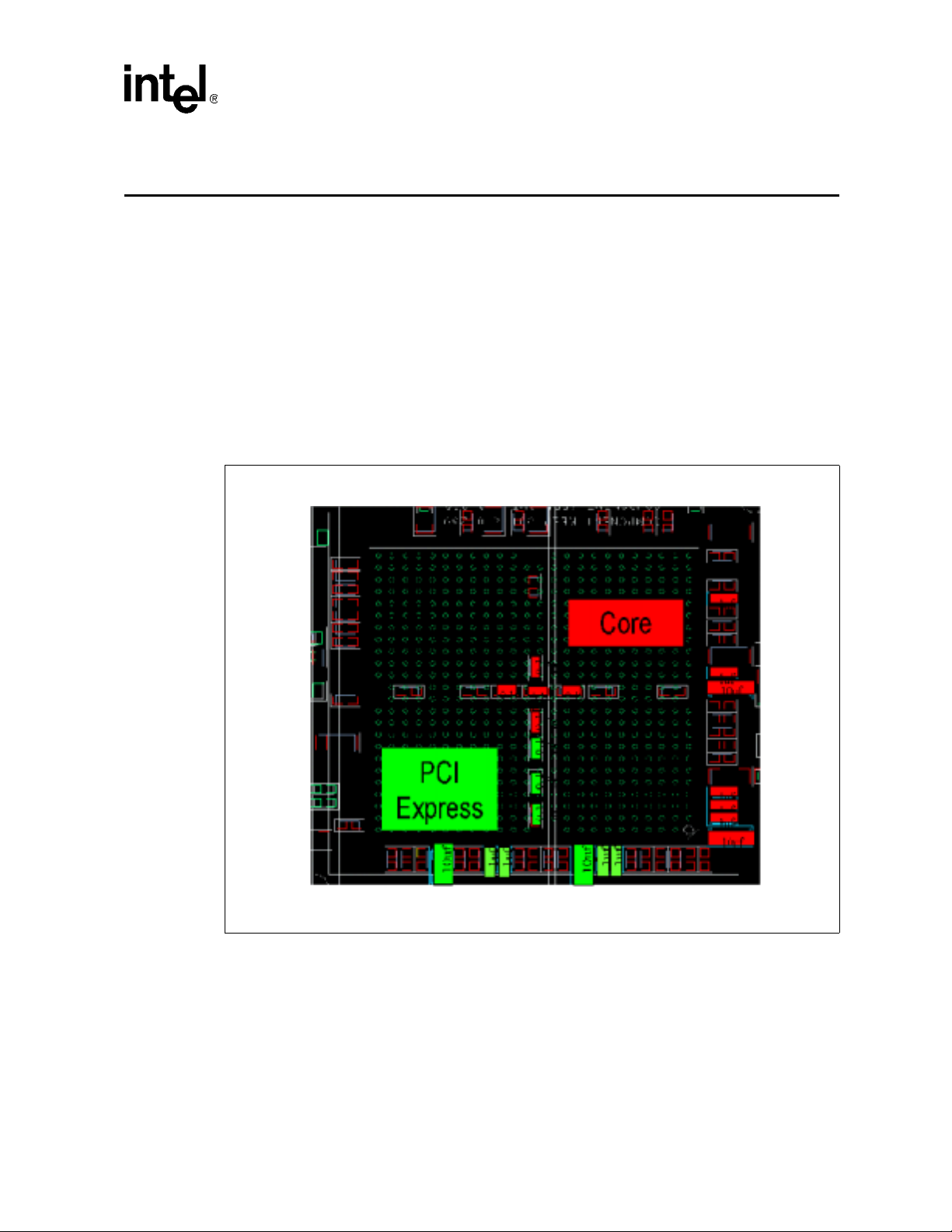

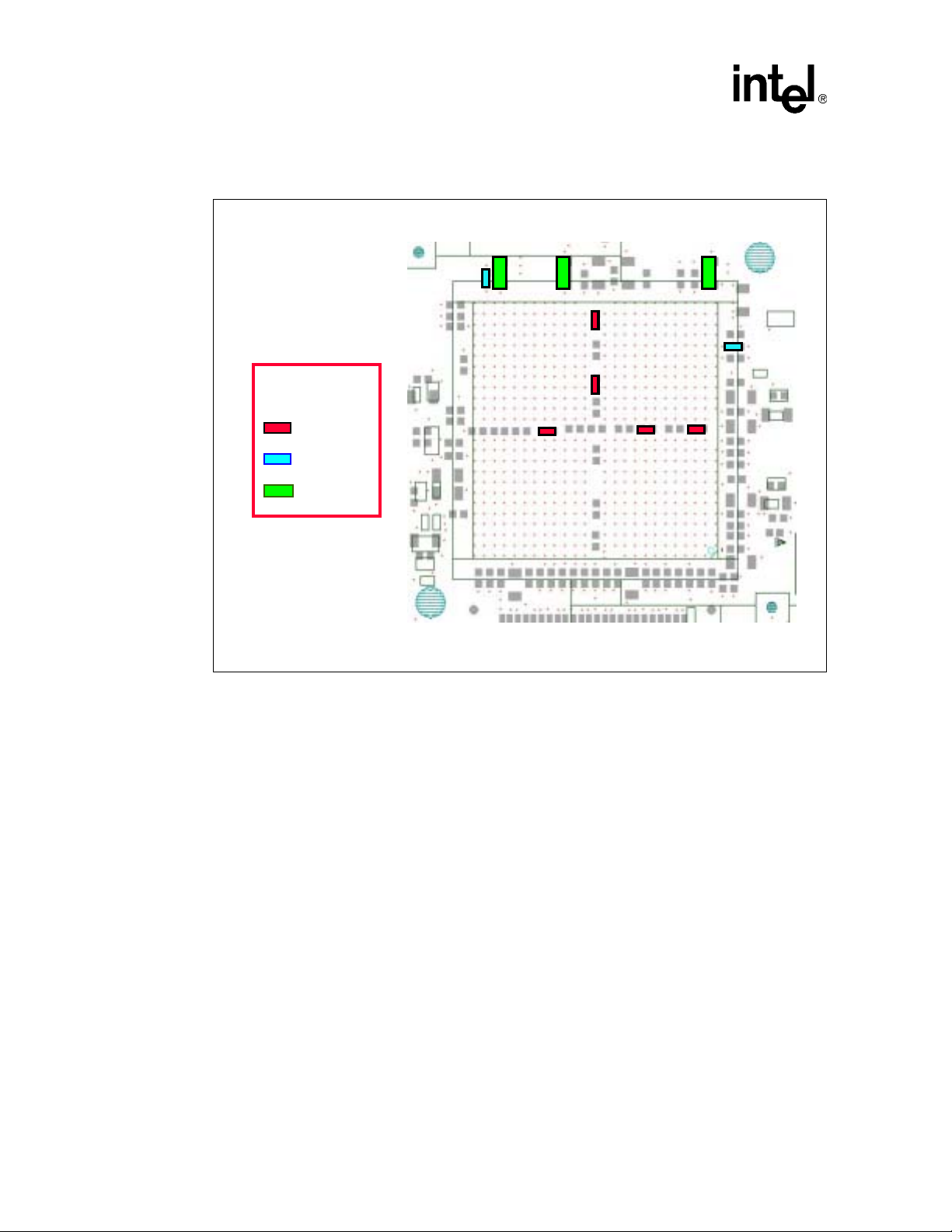

Table 2 lists the decoupling guidelines for the 41210 Bridge. Figure 8 and Figure 9 provide the

decoupling capacitors around the 41210 Bridge ball grid pins.

Figure 8. Decoupling Placement for Core and PCI Express Voltage Planes

B2713-01

Intel® 41210 Serial to Parallel PCI Bridge Design Guide 19

Page 20

Power Plane Layout

Figure 9. Decoupling Placement for PCI/PCI-X 1.5V and 3.3V Volt age Planes

Capacitor Legend

0603-0.1 F

0603-1 F

1206-10 F

B2714-01

20 Intel® 41210 Serial to Parallel PCI Bridge D esign Guide

Page 21

T a ble 2. 41210 Bridge Decoupling Guidelines

Power Plane Layout

Vol tage Plane Voltage

PCI/PCI-X

Voltage

PCI/PCI-X

Voltage

PCI/PCI-X

Voltage

Core Voltage 1.5V VCC15 0.1 0603 200 2.0 5

Core Voltage 1.5V VCC15 1.0 0805 200 2.3 5

Core Voltage 1.5V VCC15 10 1206 200 1.9 2

PCI Express

Voltage

PCI Express

Voltage

PCI Express

Voltage

3.3V VCC33 0.1 0603

3.3V VCC33 1.0 0603

3.3V VCC33 10 1206

1.5V VCCPE 0.1 0603 200 2.0 3

1.5V VCCPE 1 0805 200 2.3 4

1.5V VCCPE 10 1206 200 1.9 2

41210

Pins

C

(uF)

Package

ESR

(mΩ)

50-

300

50-

300

50-

300

ESL

(nH)

1.0-

3.0

1.0-

3.0

1.0-

3.0

Caps

# of

5

As close as design

2

41210 Bridge BGA

As close as design

3

41210 Bridge BGA

As close as design

41210 Bridge BGA

As close as design

41210 Bridge BGA

As close as design

41210 Bridge BGA

As close as design

41210 Bridge BGA

Location

Beneath 41210

Bridge BGA

rules will allow to

rules will allow to

Beneath 41210

Bridge BGA

rules will allow to

rules will allow to

Beneath 41210

Bridge BGA

rules will allow to

rules will allow to

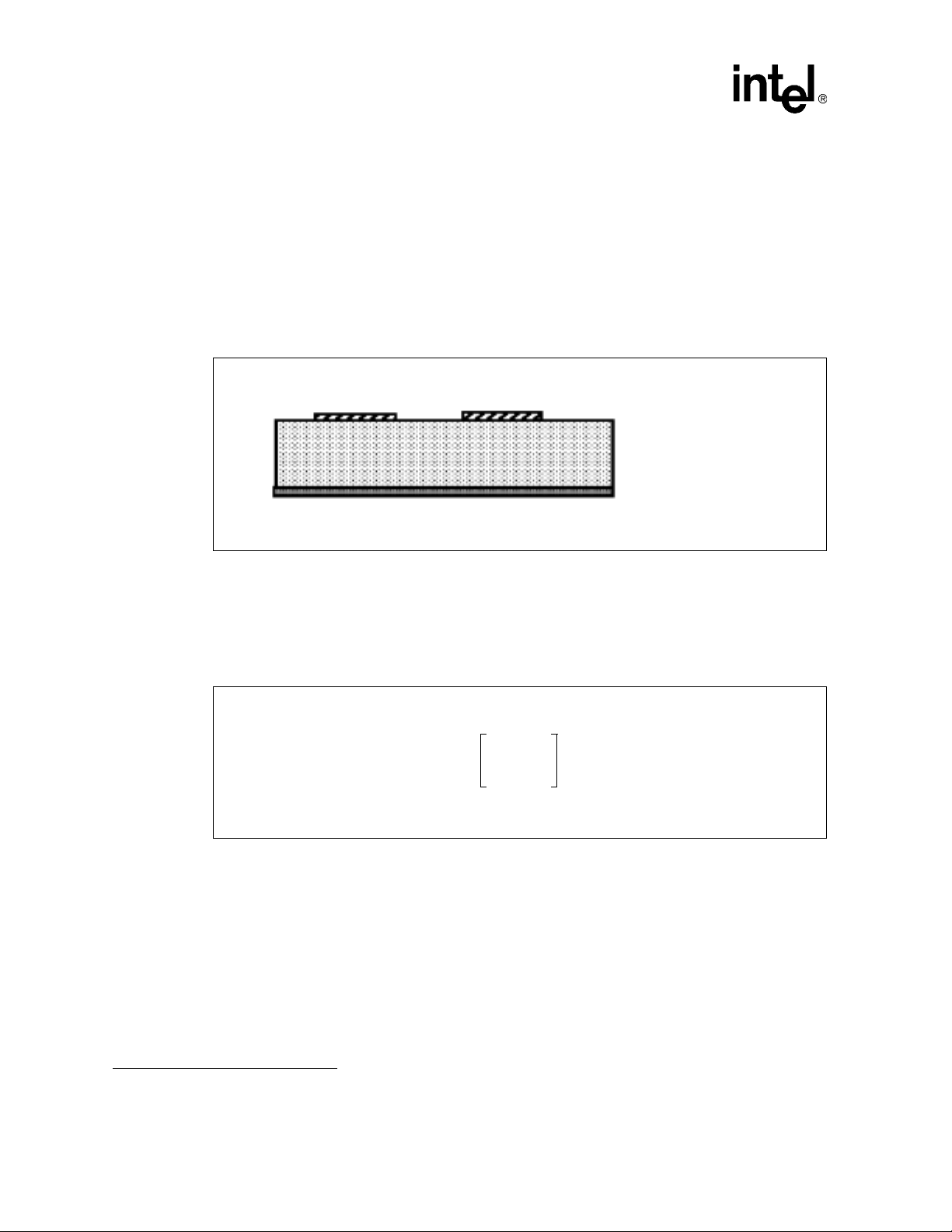

4.2 Split Voltage Planes

There are two 1.5V voltage planes that supply power to the 41210 Bridge:

• VCC15:1.5V ±5% (1.5V core voltage)

• VCCPE:1.5V ±3% (1.5V PCI Express voltage)

The 41210 Bridge core (VCC15), PCI-Express (VCCPE) voltages should be supplied by two

separate voltage regulators or a single regulator. If VCC15 and VCCPE is supplied by a single

voltage regulator the power planes should be split as shown in Figure 10.

Intel® 41210 Serial to Parallel PCI Bridge Design Guide 21

Page 22

Power Plane Layout

Note: Linear voltage regulators are recommended when using 1.5 Volt power supplies.

Figure 10. 41210 Bridge Single-Layer Split Voltage Plane

re

Core

PCI

Express

B2715-01

22 Intel® 41210 Serial to Parallel PCI Bridge D esign Guide

Page 23

41210 Bridge Reset and Power Timing

Considerations 5

This chapter describes the 41210 Bridge reset timing considerations.

5.1 A_RST#,B_RST# and PERST# Timing Requirements

The PCI-X Specification requires that there is a 100ms delay from valid power (PERST#) to reset

deassertion (A_RST#/B_RST#). 41210 Bridge will keep A_R ST# /B_ RS T # asserted for a

minimum of 320ms after PERST# is deasserted.

5.2 VCC15 and VCC33 Voltage Requirements

The following steps are the power sequencing requirements that must be followed with the

41210 Bridge:

1. The 41210 Bridge requires that the VCC33 voltage rail be no less than 0.5V below VCC15

(absolute voltage value) at all times during 41210 operation, including during system power

up and power down. In other words, the following must always be true:

VCC33 >= (VCC15 – 0.5V)

This can be accomplished by placing a diode (with a voltage drop <0.5V) between VCC15 and

VCC33. A node will be connected to VCC15 and cathode will be connected to VCC33.

If VCC15 (1.5V PCI-X I/O voltage) and VCC15 (1.5V core voltage) are tied together on the

platform, then both voltages must meet the above rule.

Note: Linear voltage regulators are recommended when using 1.5 Volt power supplies.

2. If a voltage regulator solution is used which shunts VCC15 to ground while VCC33 is

powered, the maximum all owa ble t ime that VCC15 can be shunted to ground whil e V C C33 is

fully powered is 20ms.

3. The maximum allowed time between VCC33 and VCC15 ramping is 525ms .

Note: There is no minimum sequencing time requirement other thanrequirements in Steps 2 and 3.

Intel® 41210 Serial to Parallel PCI Bridge Design Guide 23

Page 24

41210 Bridge Reset and Power Timing Considerations

This page intentionally left blank.

24 Intel® 41210 Serial to Parallel PCI Bridge D esign Guide

Page 25

General Routing Guidelines 6

This chapter provides some basic ro uting guidel ines for layout and design of a printed circuit board

using the 41210 Bridge. The high-speed clocking required when designing with the 41210 Bridge

requires special attention to signal integrity. In fact, it is highly recommended that the board design

be simulated to determine optimum layout for signal integrity. The information in this chapter

provides guidelines to aid the designer with board layout. Several factors influence the signal

integrity of a 41210 Bridge design. These factors include:

• power distribution

• minimizing crosstalk

• decoupling

• layout considerations when routing the PCI Express bus and PCI-X bus interfaces

6.1 General Routing Guidelines

This section details general routing guidelines for designing with the 41210 Bridge. The order in

which signals are routed varies from desi gner to designer. Some designers prefer to route all clock

signals first, while others prefer to route all high-speed bus signals first. Either order can be used,

provided the guidelines listed here are followed.

6.2 Crosstalk

Crosstalk is caused by capacitive and inductive coupling between signals. Crosstalk is composed of

both backward and forward cr osstalk comp onents. Back ward crosstalk cre ates an induced signal on

victim network that propagates in the opposite direction of the aggressor signal. Forward crosstalk

creates a signal that propagates in the same direction as the aggressor signal.

Circuit board analysis software is used to analyze your board layout for crosstalk problems.

Examples of 2D analysis tools include Parasitic Parameters from ANSOFT

*

Design

software is not available, the layout should be designed to maintain at least the minimum

recommended spacing for bus interfaces.

. Crosstalk problems occur when circuit etch lines run in parallel. When board analysis

• A general guideline to use is, that space distance between adjacent signals be a least 3.3 times

the distance from signal trace to the nearest return plane. The coupled noise between adjacent

traces decreases by the square of the distance between the adjacent traces.

• It is also recommended to specify the height of the above reference plane when laying out

traces and provide this parameter to the PCB manufacturer. By moving traces closer to the

nearest reference plane, the coupled noise decreases by the square of the distance to the

reference plane.

*

and XFS from Quad

Intel® 41210 Serial to Parallel PCI Bridge Design Guide 25

Page 26

General Routing Guidelines

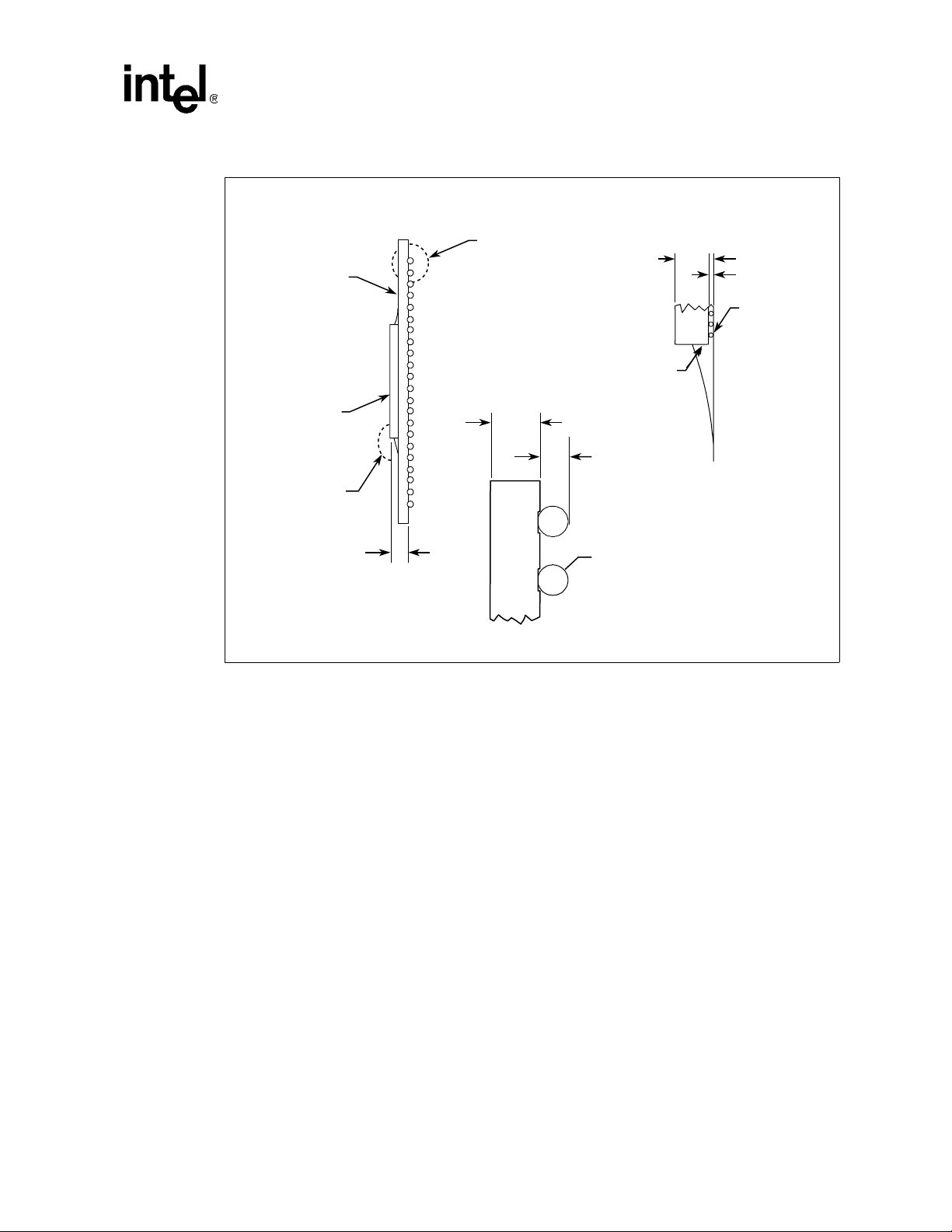

Figure 11. Crosstalk Effects on Tr ace Distance and Height

P

H

aggressor victim

• Avoid slots in the ground plane. Slots increases mutual inductance thus increasing crosstalk.

• Make sure that ground plane surrounding connector pin fields are not completely cleared out.

When this area is completely cleared out, around the connector pins, all the return current must

flow together around the pin field increasing crosstalk. The preferred method of laying out a

connector in the GND layer is shown in Figure 12.

Figure 12. PCB Ground Layout Around Connectors

Connector

Connector Pins

Reference Plane

Reduce Crosstalk:

- Maximize P

- Minimize H

A9259-01

GND PCB Layer

A. Incorrect method B. Correct method

A9260-01

6.3 EMI Considerations

It is highl y recommen ded that good EMI design practice s be followed when designing with th e

41210 Bridge.

• To minimize EMI on your PCB a useful technique is to not extend the power planes to the

edge of the board.

• Another technique is to surround the perimeter of your PCB layers with a GND trace. This

helps to shield the PCB with grounds minimizing radiation.

The below link can provide some useful general EMI guidelines considerations:

http://developer.intel.com/design/auto/mcs96/applnots/272673.htm

26 Intel® 41210 Serial to Parallel PCI Bridge D esign Guide

Page 27

6.4 Power Distribution and Decoupling

Have ample decoupling to ground, for the power planes, to minimize the effects of the switching

currents. Three types of decoupling are: the bulk, the high-frequency ceramic, and the inter-plane

capacitors.

• Bulk capacitance consist of electrolytic or tantalum capacitors. These capacitors supply large

reservoirs of charge, but they are useful only at lower frequencies due to lead inductance

effects. The bulk capacitors can be located anywhere on the board.

• For fast switching currents, high-frequency low-inductance capacitors are most ef fective.

Place these capacitors as close to the device being decoupled as possible. This minimizes the

parasitic resistance and inductance associated with board traces and vias.

• Use an inter-plane capacitor between power and ground planes to reduce the effective plane

impedance at high frequencies. The general guideline for placing capacitors is to place highfrequency ceramic capacitors as close as possible to the module.

6.4.1 Decoupling

Inadequate high-frequency decoupling results in intermittent and unreliable behavior.

General Routing Guidelines

A general guideline recommends that you use the largest easily available capacitor in the lowest

inductance package. For specific decoupling requirements for a 41210 Bridge application please

refer to Chapter 4.

6.5 Trace Impedance

All signal layers require contr olled impeda nce 60 Ω +/- 15%, microstrip or stripline f or add-in card

applications. Selecting the appropriate board stack-up to minimi ze impedan ce variation s is very

important. When calculating flight times, it is important to consider the minimum and maximum

trace impedance based on the switching neighboring traces. Use wider s paces between traces, since

this can minimize trace-to-trace coupling, and reduce cross talk.

When a different stack up is used the trace widths must be adjusted appropriately. When wider

traces are used, the trace spacing must be adjusted accordingly (linearly).

It is highly recommended that a 2D Field Solver be used to design the high-speed traces. The

following Impedance Calculator URL provide approximations for the trace impedance of various

topologies. They may be used to generate the starting point for a full 2D Field solver.

http://emclab.umr.edu/pcbtlc/

The following website link provides a useful basic guideline for calculating trace parameters:

http://www.ultracad.com/calc.htm

Intel® 41210 Serial to Parallel PCI Bridge Design Guide 27

Page 28

General Routing Guidelines

Note: Using stripline transmission lines may give better results than m icrostri p. This is due to th e

difficulty of precisely controlling the dielectric constant of the solder mask, and the difficulty in

limiting the plated thickness of microstrip conductors, which can substantially increase cross-talk.

6.5.1 Differential Impedance

The PCI Express standard defines a 100 Ω differential impedance. This sect ion provides some basi c

background information on the differential impedance calculations. In the cross section of

Figure 13 shows the cross section of two traces of a differential pair.

Figure 13. Cross Section of Different ial Trace

Ground reference plane

B2716 -01

To calculate the coupled impedance requires a 2x2 matrix. The diagonal values in the matrix

represent the impedance of the traces to ground and the off-diagonal values provide a measure of

how tightly the traces are coupled. The “differential impedance is the value of the line-to-line

resistor terminator that optimally terminates pure differential signals.” The two by two matrix is

shown below as:

Figure 14. Two-by-two Differential Impedance Matrix

Z11 Z12

=

Z

o

Z21 Z22

For a symmetric trace Z11 = Z22, the differential impedance can be calculated from this equation:

Z

differential

For two traces to be symmetric, they must have the same width, thickness and height above the

ground plane.

= 2(Z11-Z12)

1

With the traces terminated with the appropriate differential, impedance ringing is

minimized.

B2717 -01

1. “Terminating Differential Signals on PCBs”, Steve Kaufer and Kelee Crisafulli, Printed Circuit Design, March 1999

28 Intel® 41210 Serial to Parallel PCI Bridge D esign Guide

Page 29

Board Layout Guidelines 7

This chapter provides details on adapter card stackup suggestions. It is highly recommended that

signal integrity simulations be run to verify each 4 121 0 B ridge PCB layout es pecially if it dev iates

from the recommendations listed in these design guidelines.

7.1 Adapter Card Topology

The 41210 Bridge will be implemented on PCI-E adapter cards with an eight layer stackup PCB.

The specified impedance range for all adapter card implementations will be 60

Adjustments will be made for interfaces specified at other impedances. Table 3 defines the typical

layer geometries for eight layer boards.

T a ble 3. Adapter Card Stack Up, Microstrip and Stripline

Ω +/-15%.

Variable Type

Solder Mask Thickness (mil) N/A 0.8 0.6 1.0

Solder Mask E

Core Thickness (mil) N/A 2.8 3.0 3.2

Core E

Plane Thickness (mil)

Trace Height

Trace Thickness (mil)

Trace Width (mil) Microstrip 4.0 2.5 5.5

Total Thickness (mil) FR4 62.0 56.0 68.0

(mil)

Preg E

N/A 3.65 3.65 3.65

r

N/A 4.3 3.75 4.85 2113 material

r

Power 2.7 2.5 2.9

Ground 1.35 1.15 1.55

13.53.33.7

23.53.33.7

3 10.5 9. 9 11.1

Microstrip 4.30 3.75 4.85 2113 material

Stripline1 4.30 3.75 4.85 2113 material

r

Stripline2 4.3 3.75 4.85

Microstrip 1.75 1.2 2.3

Stripline 1.4 1.2 1.6

Stripline 4.0 2.5 5.5

Nominal

(mils)

Minimum

(mils)

Maximum

(mils)

Notes

The trace height will be determined to

achieve a nominal 60 Ω.

7628 material. Trace height 3 is composed

of one piece of 2113 and one piece of

7628.

Trace Spacing (using

microstrip E2E/C2C)

Trace Spacing (using

stripline E2E/C2C) [12]/[16]

Trace Impedance

[12]/[16]

Microstrip 60 51 69

Stripline 60 51 69

Intel® 41210 Serial to Parallel PCI Bridge Design Guide 29

Page 30

Board Layout Guidelines

NOTE: Each interface will set the trace spacing based on its signal integrity of differential impedance

requirements. For the purposes of the building the transmission line models, it is assumed the artwork is

very accurate and therefore a constant. Thus, all the variability in the trace spacing is the result of the

tolerances of the trace width.

Figure 15. Adapter Card Stackup

L1

L3

Total Thicken ss

Microstrip

Trace

Spacing

L4

L2 (GND)

L4 (VCC)

L5 (VCC)

L7 (GND)

L8

Stripline

Trace

Spacing

Microstrip

Trace

Width

L1

L3

Stripline

Trace

Width

Microstrip Trace Thickness

Solder Mask Thickness

Trace Height 1

Trace Height 2

Stripline Trace Thickness

Trace Height 3

Core Thickness

Plane Thickness

L4

B1436-01

30 Intel® 41210 Serial to Parallel PCI Bridge D esign Guide

Page 31

PCI-X Layout Guidelines 8

This chapter describes several factors to be considered with a 41210 Bridge PCI/PCI-X design.

These include the PCI IDSEL, PCI RCOMP, PCI Interrupts and PCI arbitration.

8.1 Interrupts

PCI Express provides interrupt messages that emulate the legacy wired mechanism. This allows IO

devices to signal PCI-style interrupts using a pair of ASSERT and DEASSERT messages This

message pairing preserves the level-sensitive semantics of the PCI interrupts on PCI Express.

The 41210 Bridge uses four interrupts - A_INTA:A_INTD on bus A segment and four interrupts

B_INTA:B_INTD that corresponding to the four interrupts defined in the PCI specification. The

41210 Bridge routes its PCI interrupt pins and the internal interrupts, to PCI Express INTx

interrupts according to Table 4.

Table 4. INTx Routing Table

A_INT# Interrupt Pins B_INT# Interrupt Pins PCI Express INTx Message

A_INTA B_INTA INTA

A_INTB B_INTB INTB

A_INTC B_INTC INTC

A_INTD B_INTD INTD

The 41210 Bridge will use its p rimary bus number and device number in the Requester ID field for

the PCI Express INTx messages. As stated in the PCI Express specification, the function number is

reserved for interrupt messages and will always be 0.

Intel® 41210 Serial to Parallel PCI Bridge Design Guide 31

Page 32

PCI-X Layout Guidelines

Note: PCI Express Assert_INTx/Deassert_INTx messages are not inhibited by the BME bit.

8.1.1 Interrupt Routing for Devices Behind a Bridge

Given the legacy interrupt sharing scheme shown in Table 4, to get the best legacy interrupt

performance (by reducing interrupt sharing), adapter boards have to select the appropriate

A_INTX#, B_INTX# (where X is A, B, C or D) input pin to use on each PCI bus segment. The

chosen interrupt input also imposes a PCI device number requirement for the interrupt source as

specified in the PCI-to-PCI Bridge specification and reproduced in Table 5

Table 5. Interrupt Binding for Devices Behind a Bridge

.

Device Number on

Secondary Bus

a

. 4, 8b, 12, 16, 20, 24, 28

-

b

1, 5, 9

, 13, 17, 21, 25, 29

b

2, 6, 10

3, 7, 11

a. Device number 0 is reserved for the Bridge and should not be assigned to secondary devices.

b. AD[27:24] which correspond to devices 11:8 should not be used for IDSEL# connections as these signals are used

, 14, 18, 22, 26, 30

b

, 15, 19, 23, 27, 31

when accessing the extended configuration space in the bridge from the secondary bus.

Interrupt Pin on Device Interrupt on 41210 Bridge

INTA# INTA#

INTB# INTB#

INTC# INTC#

INTD# INTD#

INTA# INTB#

INTB# INTC#

INTC# INTD#

INTD# INTA#

INTA# INTC#

INTB# INTD#

INTC# INTA#

INTD# INTB#

INTA# INTD#

INTB# INTA#

INTC# INTB#

INTD# INTC#

8.2 PCI Arbitration

The 41210 Bridge supports a high-performance internal PCI arbiter that supports up to seven

masters on each PCI segment A and B PCI Buses. The request inputs into the internal arbiter

include: six external request inputs and 1 internal request input. All request inputs to the internal

arbiter are split into two groups, a high priority group and a low priority group. Any master,

including the internal master , can be programmed to be in either of the two group s. This could also

mean that all the request inputs into the arbiter could be in one single group. Within a group,

priority is round-ro bi n. The ent i re lo w- priority group represents on e s l ot i n t he high priority group.

The 41210 Bridge provides a 16-bit arbiter control register to control two aspects of the internal

arbiter behavior:

32 Intel® 41210 Serial to Parallel PCI Bridge D esign Guide

Page 33

• Priority group for a master (i.e., whether a master is in low priority group or high priority

group).

• Bus parking on last PCI agent or the bridge.

By default the arbiter parks the bus on the bridge and drives the A/D, C/BE# and PAR lines to a

known value while the bus is idle.

8.2.1 PCI Resistor Compensation

Figure 16 provides the recommended resistor co mpensation pin termination for the PCI A and PCI

B buses.

Figure 16. PCI RCOMP

RCOMP

100

PCI-X Layout Guidelines

Ω

– 1%

8.3 PCI General Layout Guidelines

For acceptable signal integrity with bus speeds up to 133MHz it is important to PCB design layout

to have controlled impedance.

• Signal traces should have an unloaded impedance of 60 +/- 10% Ω.

• Signal trace velocity should be roughly 150 – 190ps/inch

There are a couple of general guidelines which should be used when routing your PCI bus signals:

• Av oid routing signals > 8”.

• The following signals have no length restrictions: A_INTA#, A_INTB#, A_INTC#,

A_INTD#, B_INTA#, B_INTB#, B_INTC#, B_INTD# and TCK, TDI, TDO, TMS and

TRST#. Most PCI-X signals are timing critical. These signals have length restrictions for

propagation, setup, and hold requirements. Table 6 shows the PCI-X signals.

B2718 -01

Intel® 41210 Serial to Parallel PCI Bridge Design Guide 33

Page 34

PCI-X Layout Guidelines

Table 6. PCI-X Signals

A PCI Bus Segment:

A_ACK64#, A_AD[63:0], A_C BE _ [7: 0] # , A_DEVSEL#, A_FRAME#,

A_GNT_[5:0]#, A_IRDY#, A_LOCK#, A_PAR64, A_REQ64#, A_REQ_[5:0]#,

Timing Critical Signals

Reset Signals

Non Timing Critica l

Signals

A_STOP#, A_TRDY#, A_CLKO [6: 0 ], A_C LKI

B PCI Bus Segment:

B_ACK64#, B_AD[63:0], B_C BE _ [7: 0] # , B_DEVSEL#, B_FRAME#,

B_GNT_[5:0]#, B_IRDY#, B_LOCK#, B_PAR64, B_REQ64#, B_REQ_[5:0]#,

B_STOP#,B_ TRDY#, B_CLKO[6:0], B_CLKI

A PCI Bus Segment:

A_RST#, A_PME#

B PCI Bus Segment:

B_RST#, B_PME#

A PCI Bus Segment:

A_133EN, A_IRQ[15:0]#, A_M 66EN, A_PCIXCAP, A_PERR#, A_SERR#

B PCI Bus Segment:

B_133EN, B_IRQ[15:0]#, B_M 66EN, B_PCIXCAP, B_PERR#, B_SERR#

Table 7. PCI/PCI-X Frequency/Mode Straps

A_PCIXCAP, B_PCIXCAP

00XPCI 33

01XPCI 66

PCI-X 66MHz cards connect this

signal to ground through a 10KΩ

±5% resistor in parallel with a

0.01uF ±10% capacitor.

PCI-X 133 MHz cards connect

PCIXCAP to ground through a

0.01uF ±10% capacitor.

PCI-X 133 MHz cards connect

PCIXCAP to ground through a

0.01uF ±10% capacitor.

A_M66EN,

B_M66EN

XXPCI-X 66

X0PCI-X 100

X1PCI-X 133

A_133EN,

B_133EN

(on board)

Note: All signals sampled on the rising edge of PERST#.

8.3.1 PCI Pullup Resistors Not Required

PCI control signals on the 41210 Bridge do NOT require pullup resistors on the adapter card to

ensure that they contain stable values when no agent is actively driving the bus. These include:

A_ACK64#, A_AD[63:32], A_CBE#[7:4], A_DEVSEL#, A_FRAME#, A_INTA#, A_INTB#,

A_INTC#, A_INTD#, A_IRDY#, A_PERR#, A_PAR, A_GNT#[5:0], A_REQ#[5:0], A_LOCK#,

A_PAR 64, A_RE Q6 4#, A_S ERR #, A_STOP#, A_TRDY#, B_ACK64#, B_AD[63:32],

Bus

Mode/

Freq

34 Intel® 41210 Serial to Parallel PCI Bridge D esign Guide

Page 35

B_CBE#[7:4], B_DEVSEL#, B_FRAME#, B_INTA#, B_INTB#, B_INTC#, B_INTD#,

B_IRDY#, B_PERR #, B_PAR, B_GNT #[5 :0], B_REQ#[5:0], B_LOCK#, B_PAR64, B_REQ64#,

B_SERR#, B_STOP# , and B_TRDY#.

8.4 PCI Clock Layout Guidelines

The PCI-X Addendum to the PCI Local Bus Specification, Revision 1.0b compliant, allows a

maximum of 0.5 ns clock skew timing for each of the PCI-X frequencies: 66 MHz, 100 MHz and

133 MHz. A typical PCI-X application may require separate clock point-to-point connections

distributed to each PCI device. The 41210 Bridge provides seven b uf f ered clocks on t he PC I bus to

connect to multiple PCI-X devices. The Figure 17 shows the use of four PCI “A” clock outputs and

length matching requirements. These same guidelines apply to the 41210 Bri dge PC I “B” clock

outputs. The recommended clock buffer layout are specifie d as fo llows:

• Match each of the used the 41210 Bridge output clock lengths A_CLK[6:0] and B_CLK[6:0]

to within 0.1” to help keep the timing within the 0.5 ns maximum budget.

• Keep the distance between the clock lines and other signals “d” at least 25 mils from each other.

• Keep the distance between the clock line and itself “a” at a minimum of 25mils apart (for

serpentine clock layout).

• A_CLKIN gets connected to A_CLKO6 through a 22Ω +/- 1% resistor and likewise for

B_CLKIN is connected to B_CLKO6 through a 22

PCI-X Layout Guidelines

Ω resistor.

• The 22 +/- 1% Ω resistor is within 500 mils of A_CLKO.

Intel® 41210 Serial to Parallel PCI Bridge Design Guide 35

Page 36

PCI-X Layout Guidelines

Figure 17. PCI Clock Distribution and Matching Requirements

22

9

A_CLKIN

a

®

Intel

41210

Bridge

A_CLKO0

A_CLKO1

A_CLKO2

A_CLKO3

A_CLKO4

A_CLKO6

9

22

22

9

d

9

22

22

9

X0

X1

X2

X3

PCI

Device 1

PCI

Device 2

PCI

Device 3

PCI

Device 4

PCI Bus

22 9

Notes:

– PCI Clock Lengths X0, X1, X2, X3 and X4 should be matched within 0.1 inch of each other.

– Minimum separation between two different CLKs, "d".

– Minimum separation between two segments of the same CLK line, "a".

X4

PCI

Device 5

B1499-04

36 Intel® 41210 Serial to Parallel PCI Bridge D esign Guide

Page 37

Table 8. PCI-X Clock Layout Requirements Summary

Parameter Routing Guidelines

Signal Group PCI Clocks B_CLKO[6:0], A_CLK[6:0]

Reference Plane Route over unbroken ground or power plane

Stripline Tr ace Width 4 mils

Stripline Trace Spacing: Separation between two

different clock lines, “d” clock lines

Stripline Trace Spacing: Separation between two

segments of the same clock line (on serpentine

layout), “a” dimension

Stripline Tr ace Sp acing: Separation between clocks

and other lines

Length Matching Requirements

Total Length of the 41210 Bridge PCI CLKs on the

adapter card

A_CLKIN, B_CLKIN Series Termination

A_CLK[6:0], B_CLK[6:0] Series Termination

Routing Guideline 1

Routing Guideline 2 Minimize number of vias

25 mils center to center from any other signal

25 mils center to center from any other signal

50 mils center to center from any other signal

All 41210 Bridge Output Clocks B_CLK0[6:0] and

A_CLK[6:0] connected to devices must be length

matched to 0.1 inch of each other.

The clock feedback line lengths from A_CLKOUT to

A_CLKIN and B_CLKOUT to B_CLKIN should be

length matched to all other clock lines within 0.1”.

10” -14”

Connect A_CLKIN to one end of a 22Ω +/- 1% resistor

and the other end connected to A_CLKOUT and

connect B_CLKIN to one end of a 22Ω resistor and

the other end connected to B_CLKOUT

Each of the clock outputs A_CLKO[6:0] and

B_CLK[6:0] should have series 22Ω resistor located

within 500 mils of the 41210 Bridge clock output.

Point to point signal routing should be used to keep

the reflections low.

PCI-X Layout Guidelines

Intel® 41210 Serial to Parallel PCI Bridge Design Guide 37

Page 38

PCI-X Layout Guidelines

8.5 PCI-X Topology Layout Guidelines

The PCI-X Addendum to the PCI Local Bus Specification, Revision 1.0b compliant, recommends

the following guidelines fo r the numb er of l oads for you r PCI-X des igns. A ny d eviation f rom t hese

maximum values requires close attention to layout with regard to loading and trace lengths.

Table 9. PCI-X Slot Guidelines

Frequency Maximum Loads Maximum Number of Slot s

66 MHz 8 4

100 MHz 4 2

133 MHz 2 1

8.6 Intel® 41210 Serial to Parallel PCI Bridge Design Guide Layout Analysis

The following sections describes layout recommendations based on the presilicon signal integrity

analysis. This analysis was conducted using the following parameters:

• Card stack up: 60 Ω +/- 15% single-ended impedance

• Driver Model 41210 Bridge IBIS

• Receiver Model: generic models for PCI-X and PCI

• Driver Package Model: Preliminary 41210 Bridge Model

• Cross talk and ISI impact on timing were not modeled

38 Intel® 41210 Serial to Parallel PCI Bridge D esign Guide

Page 39

8.6.1 Embedded PCI-X 133 MHz

This section lists the routing recommendations for PCI-X 133 MHz without a slot. Figure 18 shows

the block di agram of this topology and Table 10 describes the routing recommendations.

Figure 18. Embedded PCI-X 133 MHz Topology

TL1

PCI-X Layout Guidelines

EM1

TL_EM2 TL_EM1

EM2

Table 10. Embedded PCI-X 133 MHz Routing Recommendations

Parameter Routing Guideline for Lower AD Bus

Reference Plane Route over an unbroken ground plane

Board Impedance 60 Ω +/- 15%

Stripline Trace Spacing 12 mils from edge to edge

Microstrip Trace Spacing 18 mils, from edge to edge

Break Out 5 mils on 5 mils spacing. Maximum length of breakout region can be 500 mils

Group Spacing Spacing from other groups: 25 mils min, edge to edge

Trace Length 1 (TL1): From

41210 Bridge signal Ball to

first junction

Trace Length 3 junction of

TL_EM1 and TL_EM2 to the

embedded device

Length Matching

Requirements:

Number of vias 3 vias max per path

1.75” min - 4.0” max

1.25” min - 3.25” max

Clocks coming form the clock driver must be on the same layer and length

matched to within 25 mils.

B2719 -01

Intel® 41210 Serial to Parallel PCI Bridge Design Guide 39

Page 40

PCI-X Layout Guidelines

8.6.2 Embedded PCI-X 100 MHz

This section lists the embedded routing recommendations for PCI-X 100 MHz. Figure 19 shows

the block diagram of this topology and Table 11 describes the r outing reco mmendatio ns.

Figure 19. Embedded PCI-X 100 MHz Topology

TL1

EM1

TL_EM3

TL_EM2

TL_EM1

Table 11. Embedded PCI-X 100 MHz Routing Recommendations

Parameter Routing Guideline for Lower AD Bus

Reference Plane Route over an unbroken ground plane

Board Impedance 60 Ω +/- 15%

Stripline Trace Spacing 12 mils from edge to edge

Microstrip Trace Spacing 18 mils, from edge to edge

Break Out 5 mils on 5 mils spacing. Maximum length of breakout region can be 500 mils

Group Spacing Spacing from other groups: 25 mils min, edge to edge

Trace Length 1 (TL1): From

41210 Bridge signal Ball to

first junction

Trace Length: TL_EM1: from

41210 Bridge signal ball to

the first embedded device

Trace Length TL_EM2 TL_EM3: from junction to the

embedded device

Length Matching

Requirements:

Number of vias 4 vias max per path

0.5” min - 3.0” max

2.5” min - 3.5” max

1.5” min - 3.5” max

Clocks coming form the clock driver must be on the same layer and length

matched to within 25 mils.

EM3

EM2

B2720 -01

40 Intel® 41210 Serial to Parallel PCI Bridge D esign Guide

Page 41

8.6.3 PCI-X 66 MHz Embedded Topo logy

Figure 20 and Table 12 provide routing details for a topology with an embedded PCI-X 66 MHz

application.

Figure 20. PCI-X 66 MHz Embedded Routing Topology

PCI-X Layout Guidelines

TL1

EM1

TL2

TL_EM2 TL_EM1

EM2

EM3

TL3

TL_EM4 TL_EM3

EM4

Table 12. PCI-X 66 MHz Embedded Routing Recommendations

Parameter Routing Guideline for Lower AD Bus

Reference Plane Route over an unbroken ground plane

Board Impedance 60 Ω +/- 15%

Stripline Trace Spacing 12 mils edge to edge

Microstrip Trace Spacing 18 mils, edge to edge

Break Out 5 mils on 5 mils. Maximum length of breakout region can be 500 mils

Group Spacing Spacing from other groups: 25 mils min, edge to edge

Trace Length 1 (TL1): From

41210 Bridge signal Ball to

first junction

Trace Length TL2 to TL4 between junctions

Trace Length TL_EM1 to

TL_EM8 from junction

connector to the embedded

device

Length Matching

Requirements:

Number of vias 4 vias max.

1.0” - 5.0” max

1.0” min - 2.5” max

2.0” min - 3.0” max

Clocks coming form the clock driver must be length matched to within 25 mils

and routed identical in layers.

EM5

EM6

TL_EM6 TL_EM5

EM7

TL4

TL_EM8 TL_EM7

EM8

B2721 -01

Intel® 41210 Serial to Parallel PCI Bridge Design Guide 41

Page 42

PCI-X Layout Guidelines

8.6.4 PCI 66 MHz Embedded Topology

Figure 21 and Table 13 provide routing details for a topology with an embedded PCI 66 MHz

design.

Figure 21. PCI 66 MHz Embedded Topology

Table 13. PCI 66 MHz Embedded Table

Parameter Routing Guideline for Lower AD Bus

Reference Plane Route over an unbroken ground plane

Board Impedance 60 Ω +/- 15%

Microstrip Trace Spacing 18 mils center to center

Stripline Trace Spacing 12 mils center to center

Group Spacing Spacing from other groups: 25 mils min, edge to edge

Breakout

Trace Length 1 TL1: From 41210 Bridge signal Ball

to first junction

Trace Length TL2 between junctions 0.5” min - 3.5” max

Trace Length TL_EM1 to TL_EM4 from junction to

embedded devices

Length Matching Requirements

Number of vias 4 vias max.

P

TL1

EM1

TL2

TL_EM2 TL_EM1

EM2

5 mils on 5 mils spacing. Maximum length of breakout

region can be 500 mils.

5.0” max

2.0” min - 3.0” max

Clocks coming from the clock driver must be length

matched to within 25 mils.

EM3

TL_EM4 TL_EM3

EM4

B2722 -01

42 Intel® 41210 Serial to Parallel PCI Bridge D esign Guide

Page 43

8.6.5 PCI 33 MHz Embedded Mode Topology

Figure 22 and Table 14 provide routing details for a topology with an embedded PCI 33 MHz

design.

Figure 22. PCI 33 MHz Embedded Mode Routing Topology

PCI-X Layout Guidelines

TL1

EM1

TL2

TL_EM2 TL_EM1

EM2

EM3

TL_EM4 TL_EM3

EM4

EM5

TL3

EM6

Table 14. PCI 33 MHz Embedded Routing Recommendations

Parameter Routing Guideline for Lower AD Bus

Reference Plane Route over an unbroken ground plane

Board Impedance 60 Ω +/- 15%

Stripline Trace Spacing 12 mils, edge to edge

Microstrip Trace Spacing 18 mils edge to edge

Group Spacing Spacing from other groups: 25 mils min, edge to edge

Breakout 5 mils on 5 mils spacing. Maximum length of breakout region can be 500 mils.

Trace Length 1 TL1: From

41210 Bridge signal Ball to

first junction

Trace Length TL2 to TL5 between junctions

Trace Length TL_EM1 to

TL_EM10 from junction to

embedded devices

Length Matching

Requirements

5.0” max

0.5” min - 3.5” max

2.0” min - 3.0” max

Clocks coming from the clock driver must be length matched to within 25 mils.

TL_EM6 TL_EM5

TL4

EM7

EM8

TL_EM8 TL_EM7

EM9

TL5

TL_EM10 TL_EM9

EM10

B2723 -01

Intel® 41210 Serial to Parallel PCI Bridge Design Guide 43

Page 44

PCI-X Layout Guidelines

This page intentionally left blank.

44 Intel® 41210 Serial to Parallel PCI Bridge D esign Guide

Page 45

PCI Express Layout 9

This section provides an overview of the PCI-Express stackup recommended based on Intel

presimulation results. For additional information, refer to the Intel® 41210 Serial to Parallel PCI

Bridge Developer’s Manual or the PCI Express Specification, Revision 1.0a from the

www.pcisig.com

9.1 General recommendations

PCI Express is a serial differential low-voltage point-to-point interconnect. The PCI Express was

designed to support 20 inches between components with stand ard FR 4. The 41210 Bridge supports

x8 lanes. PCI-Express requires special considerations be made for interconnect losses, jitter, crosstalk

and mode conversions. The below list provides some general gui delines for t he layout of a PC IExpress trace:

1. Jitter: Trace lengths of a PCB trace can introduce around 1 to 5 ps of jitter and 0.35 to 0.5 dB

of loss per inch of differential pair. An add-in card the trace length from edge-finger pad to

device is limited to 3 inches.

2. Matching within pair: Trace lengths of matching differential pairs are required to be matched

within +/-5 mil delta. Each net within a differential pair should be length matched on a

segment-by-segment basis at point of discontinuity such as an breakout area, routes between

vias, routes between AC coupling capacitors and connector pins.

website.

3. Trac e Sym met ry: T race Symmetry is required between two traces of the same differential pair.

4. Vias: Vias contribute 0.5 to 1.0 dB/via toward the loss budget. Vias on an add-in card should

be limited to one near the breakout section of the pads and one near the edge finger.

5. Bends: Trace bends should be kept to a minimum. If bends are used they should be at a 45-

degree angle or smaller. The number of left and right bends should be matched as closely as

possible to even out the overall lengths of each segment of the differential pair.

6. AC Coupling capacitors: AC coupling capacitor with a value of 75nF to 200nF should line

up at the same location from one trace to the other within the pair. The 0402 size capacitor

with a small pad size is highly recommended. The breakout from the capacitor should be

symmetrical for both signal traces in the differential pair.

7. Connector pins: Length compensation for the connector pins of the differential pair being

offset from each other the PCB trace should be considered.

8. Ground Plane Refer encing: Ground plan e referencing is require d along the entire route of the

differential pair. Traces routed near the edge should maintain a 40 mil air gap to the edge.

Layer switching should also maintain the ground plane. Grounds between planes should be

connected with stitching vias (with one to three recommended per differential pair).

9. Breakout Areas: Breakout areas near a device package should be limited to 500 mils in lengths.

The necking down to a smaller trace width should be symmetrical on the differential pair.

Intel® 41210 Serial to Parallel PCI Bridge Design Guide 45

Page 46

PCI Express Layout

9.2 PCI-Express Layout Guidelines

The layout guidelines for PCI-Express were developed for an adapter card topologies. The models and

assumptions used in development of these guidelines were as follows:

• Add-In Card Stackup: 60 Ω single-ended impedance

• Target Differential Impedance: 100 Ω +/- 20%.

• Driver Model: 41210 Bridge PCI-E IBIS

• Receiver Model: 41210 Bridge PCI-E IBIS. Specification model did not meet specifications

• Driver Package Model: Preliminary 41210 Bridge model.

• No receiver package model used since specification eye is at package pin.

• Assumed that traces in a lane could be routed totally on microstrip, totally on stripline, or a

mixture of microstrip and stripline.

• AC coupling capacitors were modeled as a parasitic resistor and inductor in series.

• Add-in card was modeled as micro-strip routes only.

• No vias were modeled at this time.

• Only the receiver eye was evaluated. The next revision will evaluate the eye at the transmitter

and connector as well as the receiver.

9.3 Adapter Card Layout Gu idelines

Table 15. Adapter Card Routing Recommendations (Sheet 1 of 2)

Parameter Routing Guidelines

Reference Plane Route over an unbroken ground plane

Target Single Ended

Impedance

Target Differential

Impedance

Microstrip and Stripline Trace

Width

Microstrip Trace Spacing

Group Spacing Spacing from other groups: 25 mils minimum, center to center

Transmit Trace Length

(41210 Bridge signal pin to

AC coupling capacitor.)

Transmit Trace Length (AC

coupling capacitor to card

edge finger.)

60 Ω nominal

100 Ω +/- 20% Differential Impedance

4 mils

Intrapair: 10 mils center-to-center

Interpair: 30 mils center-to-center

22 mils. center to center (pair to pair).

Transmit and Receive pairs should be interleaved. If no interleaving, then inter

pair spacing should be increased to 50 mils (c2c). Center to center of inter pair is

defined as center of Positive of one pair to Center of Negative of the next or vice

versa

0.25”- 5.0” max

1.00”- 4.5” max

46 Intel® 41210 Serial to Parallel PCI Bridge D esign Guide

Page 47

Table 15. Adapter Card Routing Recommendations (Sheet 2 of 2)

Receive Trace Length (Card

edge finger to 41210 Bridge

receiver pin

Length Matching

Requirements:

Number of vias 4 max

1.0” min - 6.0” max

Total allowable intra-pair length mis-match must not exceed 25 mils. Each

routing segment should be matched as close as possible. Total skew across all

lanes must be less than 20 ns. See the PCI-Express Desktop Design Guidelines

for additional routing requirements

PCI Express Layout

Intel® 41210 Serial to Parallel PCI Bridge Design Guide 47

Page 48

PCI Express Layout

This page intentionally left blank.

48 Intel® 41210 Serial to Parallel PCI Bridge D esign Guide

Page 49

Circuit Implementations 10

This chapter describes 41210 Bridge circuit implementations.

10.1 41210 Bridge Analog Voltage Filters

The Intel® 41210 Serial to Parallel PCI Bridge requires several external analog voltage filter

circuits to be placed on the system board, three for the PCI interface, one for the PCI Express

interface, and one for the bandgap voltage. The 41210 Bridge lists the recommended filter values

for these filter circuits -- any one of the filter circuits can use any one of the four R, L and C

combinations shown in Table 16, except that configuration number 4 cannot be used for the PCI

Express analog voltage filter.

Table 16. Recommended R, L and C Values for 41210 Bridge Analog Filter Circuits

Config R L C

1

2

3

a

4

a. Configuration number 4 cannot be used for the PCI Express analog voltage filter.

0.5Ω ±1%

1/16W

0.5Ω ±1%

1/16W

0.5Ω ±1%

1/16W

1.0Ω ±1%

1/16W

4.7uH ±25%

PCI, PCI-E: 45mA

Bandgap: 30mA

4.7uH ±20

PCI, PCI-E: 45mA

Bandgap: 30mA%

4.7uH ±20%

PCI, PCI-E: 45mA

Bandgap: 30mA

4.7uH ±20%

PCI: 45mA

Bandgap: 30mA

33uF ±20%

6.3V

22uF ±20%

6.3V

2x10uF ±20%

6.3V

10uF ±20%

6.3V

Additional notes:

L (Inductor)

— L must be magnetically shielded

—ESR: max < 0.4

Ω

— rated at 45mA (or 30mA for bandgap circuit only)

C (Capacitor)

—ESR: max < 0.5

Ω

— ESL < 3.0nH

R (Resistor)

—1/16W

Intel® 41210 Serial to Parallel PCI Bridge Design Guide 49

Page 50

Circuit Implementations

10.1.1 PCI Analog Voltage Filters

The following filter circuit is recommended for the PCI interface. Three separate, identical

versions of this circuit should be placed on the system board, one for each VCCAPCI[2:0] pin on

the Intel® 41210 Serial to Parallel PCI Bridge.

Figure 23. PCI Analog Voltage Filter Circuit

Board Trace:

Trace Width > 25 mils

Trace Spacing < 10 mils

Trace Length < 600 mils

VCC

L

R

Board Route

Traces

C

Breakout

Traces

Breakout Trace:

Trace Width > 6 mils

Trace Spacing < 6 mils

Trace Length < 600 mils

VCCAPCI[2:0]

Intelfi 41210

Bridge

VSS

Note: Three of these PCI filter circuits must be placed on the system board, one for each of the

VCCAPCI[2:0] pins on the Intel® 41210 Serial to Parallel PCI Bridge.

• Place C as close as possible to package pin.

• R must be placed between VCC15 and L.

• Route VCCPCI[x] and VSS as differential traces.

• VCCPCI[x] and VSS traces must be ground referenced (No VCC15 references).

• Max total board trace length = 1.2”.

B2724 -01

• Min trace space to other nets = 30 mils.

10.1.2 PCI Express Analog Voltage Filter

Figure 24 shows the PCI Express Analog Voltage Circuit.

50 Intel® 41210 Serial to Parallel PCI Bridge D esign Guide

Page 51

Figure 24. PCI Express Analog Voltage Filter Circuit

Circuit Implementations

Note: .

Board Trace:

Trace Width > 25 mils

Trace Spacing < 10 mils

Trace Length < 600 mils

VCC

L

R

Board Route

Traces

C

Breakout

Traces

Breakout Trace:

Trace Width > 6 mils

Trace Spacing < 6 mils

Trace Length < 600 mils

VCCAPE

Intelfi 41210

Bridge

VSSAPE

• Place C as close as possible to package pin.

• R must be placed between VCC15 and L.

• Route VCCAPE and VSSAPE as differential traces.

• VCCAPE and VSSAPE traces must be ground referenced (No VCC15 references).

• Max total board trace length = 1.2”.

B2725 -01

• Min trace space to other nets = 30 mils.

10.1.3 Bandgap Analog Voltage Filter

Figure 25 Shows the Bandgap Analog Voltage Filter.

Intel® 41210 Serial to Parallel PCI Bridge Design Guide 51

Page 52

Circuit Implementations

Figure 25. Bandgap Analog Voltage Filter Circuit

Note: .

Board Trace:

Trace Width > 25 mils

Trace Spacing < 10 mils

Trace Length < 600 mils

2.5 V

Note: Ground VSSBGPE at capacitor

Board Route

Traces

L

R

C

VSS

Breakout